# Enpirion<sup>®</sup> Power Management Evaluation Board User Guide

ES1030 Four-Channel Sequencer with Digital Feedback

### **Description**

This document describes the connections to and the testing of the ES1030 four-channel power regulator sequencer evaluation board (EVB). The ES1030QI can be chained to provide nested sequencing for over 16 power regulators. The part comes in a tiny 2x3 mm Quad Flat No-lead (STQFN) package and uses the power good (PG) signals from the regulators to confirm the desired sequence is being produced. A complete sequencing solution requires only a few small signal components. A precise sequencing delay is set by a resistor divider from the internally provided reference.

### Introduction

The ES1030 sequencer EVB contains one fourchannel sequencer chip and component locations and jumpers for flexible connections to the four output ENABLE signals (OE1, OE2, OE3, OE4) and the four digital feedback signals (PG1, PG2, PG3, and PG4). The EVB also provides the chaining signals nFLT\_IN, nFLT\_O, OE\_O, NEXT\_IN, and NEXT\_O. You can connect multiple EVBs with these chaining signals to provide nested sequencing for additional channels.

Signals to the sequencer are available on the singlerow headers on the left and right edges of the EVB. The three-pin headers allow jumpered pull-ups or pass-through of the signals to the single-row headers. The resistor positions provide series and shunt locations for implementing pass-through, divider, or pull-down connections to the signals. The default population of the EVB is for a single four-channel sequencer. Chained operation of multiple EVBs requires some jumper and component changes.

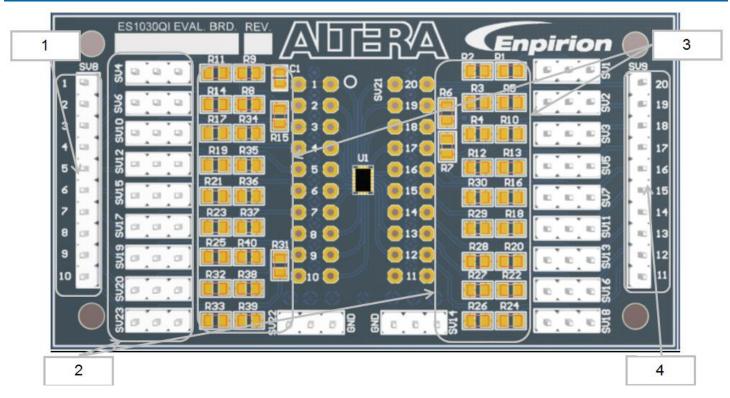

#### Figure 1: ES1030QI Evaluation Board

## **Evaluation Board Overview**

# **Evaluation Board Operating Instructions**

In the following instructions, the numbers in brackets [] correspond to the numbers in Figure 1.

**CAUTION**: This kit contains circuitry that is sensitive to static electricity. Please use anti-static precautions before touching or handling the EVB.

#### 1) Connect the EVB:

- Locate the ES1030 EVB in the kit and connect it to the equipment used for testing. The supply voltage (1.62-5.5V) is connected to SV8 Pin 1 [1] and ground at SV9 Pin 10 [4].

- For repeated triggering of the sequence, connect a square-wave signal generator to SV9 Pin1 (EN) and GND. The signal amplitude should match the nominal supply voltage (check the terminator requirements), and the frequency should be no more than 10 Hz.

- Connect the output enable signals (OEx) and power good signals (PGx) to the power regulators to be sequenced, and connect OEx and PGx to an oscilloscope or logic analyzer for observation. For demonstration without external regulators, connect PG1=OE1, PG2=OE2, and so on.

#### 2) Apply Power:

• Apply power to the VDD supply. The OE and PG signals should show a nested sequencing pattern (1-2-3-4 rising and 4-3-2-1 falling).

#### 3) Test the Module:

To adjust the time delay between successive enables and the qualification window for the PG signals from 0.033ms to 8.04ms, you can change the divider ratio formed by R7 and R40 (keep R7+R40>100kohms). If PG does not rise within the qualification window after the corresponding OE signal, a fault is produced (shown by LOW on nFAULT\_O) and the sequence reverses.

For more information, refer to the Enpirion Power Datasheet: ES1030 Power Rail Sequencer.

# Table of Connections

| HEADER/PIN<br># [1][4] | FUNCTION  | IC PIN # | DEFAULT JUMPERS<br>[2] | DEFAULT RESISTORS<br>[3] |

|------------------------|-----------|----------|------------------------|--------------------------|

| SV8/1                  | VCC/VDD   | 1        | NA                     | NA                       |

| SV8/2                  | nFAULT_IN | 2        | SV4 2-3                | R11=0, R15=0             |

| SV8/3                  | nFAULT_O  | 3        | SV6 1-2                | R14=100k                 |

| SV8/4                  | OE4       | 4        | SV10 2-3               | R17=0                    |

| SV8/5                  | OE3       | 5        | SV12 2-3               | R19=0                    |

| SV8/6                  | PG3       | 6        | SV15 2-3               | R21=0                    |

| SV8/7                  | PG4       | 7        | SV17 2-3               | R23=0                    |

| SV8/8                  | ACNTL     | 8        | NA                     | R7=100k, R40=100k        |

| SV8/9                  | NEXT_O    | 9        | NA                     | R31=0                    |

| SV8/10                 | NEXT_IN   | 10       | NA                     | NA                       |

| SV9/1                  | EN        | 20       | SV1 2-3                | R1=0                     |

| SV9/2                  | OE_O      | 19       | NA                     | NA                       |

| SV9/3                  | REF_O     | 18       | NA                     | NA                       |

| SV9/4                  | ALL_PG    | 17       | SV5 2-3                | R13=0                    |

| SV9/5                  | POR       | 16       | NA                     | R16=0                    |

| SV9/6                  | OE1       | 15       | SV11 2-3               | R18=0                    |

| SV9/7                  | OE2       | 14       | SV13 2-3               | R20=0                    |

| SV9/8                  | PG2       | 13       | SV16 2-3               | R22=0                    |

| SV9/9                  | PG1       | 12       | SV18 2-3               | R24=0                    |

| SV9/10                 | GND       | 11       | NA                     | NA                       |

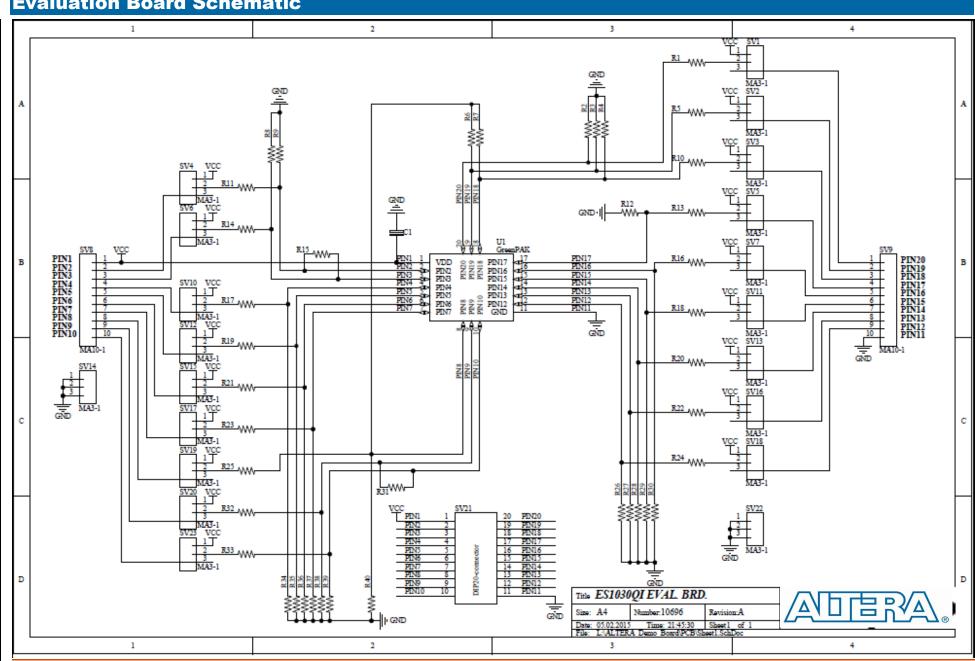

#### ES1030 Evaluation Board User Guide

**Evaluation Board Schematic**

www.altera.com/enpirion

# **Application Schematic for Four-Channel Nested Sequencer**

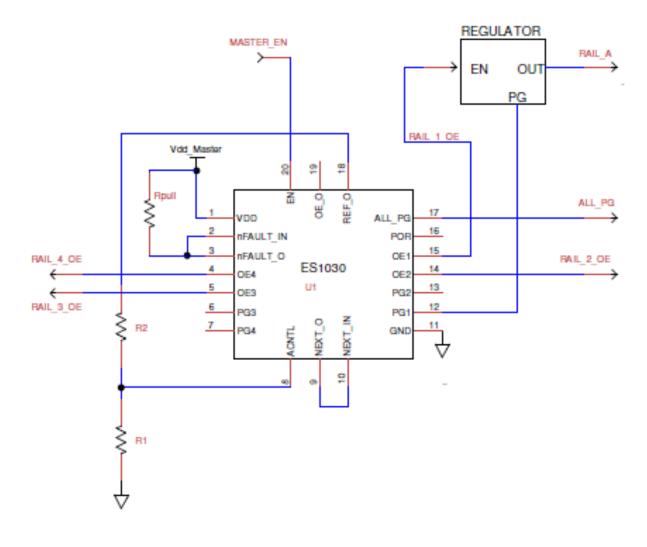

Figure 2: Stand Alone Operation

#### Notes to Figure 2:

- 1. Unused PG pins may be floated or tied to VDD.

- ACNTL controls delays based on voltage ratio relative to REF\_O: full scale delay (ACTRL at REF\_O) is 8.04ms; minimum delay (ACTRL at GND) is 33us.

- 3. For single device, connect NEXT\_O to NEXT\_IN.

- 4. Tie all nFAULT\_x pins of all chained devices together. When fault is detected in any device, the device pulls the nFAULT line low, triggering sequential power down starting with the end device. This is released by EN low until FAULT is cleared.

- 5. ALL\_PG is a push-pull output for the logical AND of all PG\_ signals.

# **Application Schematic for Chained Nested Sequencer**

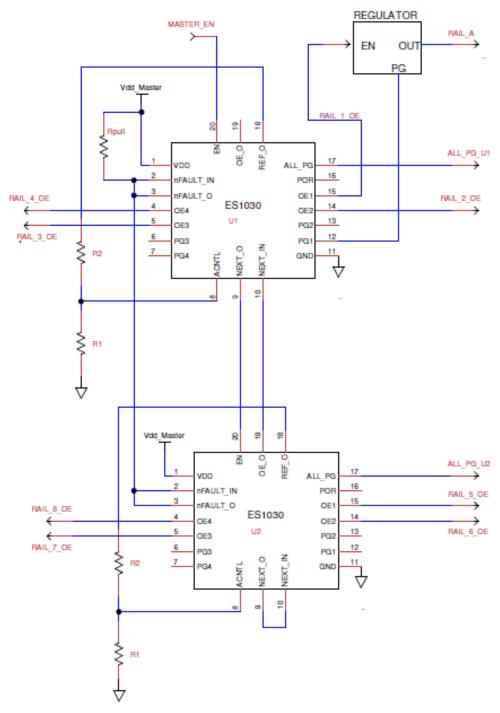

Figure 3: Chained Operation

#### Notes to Figure 3:

- 1. Connect NEXT\_O to NEXT\_IN on device at end of chain.

- 2. Tie all nFAULT\_x pins of all chained devices together. When fault is detected in any device, the device pulls the nFAULT line low, triggering sequential power down starting with the end device. This is released by EN low until FAULT is cleared.

- 3. Tie NEXT\_O to EN of following device. Tie NEXT\_IN to OE\_O of following device.

| Bill of Materials |                                     |                                                                   |                                              |                                                     |                                                                                          |                       |

|-------------------|-------------------------------------|-------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------|

| LEVEL             | ITEM NUMBER/<br>MANUFACTUER<br>NAME | ITEM REVISION/<br>ITEM DESCRIPTION/<br>MANUFACTUER<br>PART NUMBER | MANUFACTUE<br>R PART<br>DESCRIPTION          | QUANTITY/<br>MANUFACTUER<br>PART LIFECYCLE<br>PHASE | REFERENCE<br>DESCRIPTION/<br>REFERENCE<br>NOTES                                          | ITEM TYPE             |

| 0.1               | 10696                               | Schematic, ES1030<br>Evaluation Board                             |                                              | 1                                                   |                                                                                          | Document              |

| 0.1               | 10697                               | PCB, ES1030<br>Evaluation Board                                   |                                              | 11                                                  |                                                                                          | PCB                   |

| 0.1               | 2495/<br>Panasonic                  | RESISTOR ZERO<br>OHM 1/10W 5%<br>0402 SMD/<br>ERJ-2GE0R00x        | RESISTOR<br>ZERO OHM<br>1/10W 5%<br>0402 SMD | 14/Active                                           | R1, R11, R13,<br>R15, R16, R17,<br>R18, R19, R20,<br>R21, R22, R23,<br>R24, R31          | Resistor              |

| 0.1               | 6237/<br>Taiyo Yuden                | CAP CER 1.0UF<br>16V X5R 10% 0402/<br>EMK105BJ105KV-F             | CAP CER<br>1.0UF 16V<br>X5R 10%<br>0402      | 1/Active                                            | C1                                                                                       | Capacitor             |

| 0.1               | Panasonic                           | RES 100K OHM<br>1/16W 1% 0402<br>SMD/<br>ERJ-2GEJ103X             | RES 100K<br>OHM 1/16W<br>1% 0402 SMD         | 3/Active                                            | R7, R14, R40                                                                             | Resistor              |

| 0.1               | Altera                              | ES1030 Power Rail<br>Sequencer TQFN-<br>20                        | ES1030<br>Power Rail<br>Sequencer<br>TQFN-20 | 1/Active                                            | U1                                                                                       | Device                |

| 0.1               | 05118/<br>SAMTEC                    | CONN HEADER<br>3POS .100" SNGL<br>TIN/<br>TSW-103-07-T-S          | CONN<br>HEADER<br>3POS .100"<br>SNGL TIN     | 13/Active                                           | SV1, SV5, SV7,<br>SV10, SV11,<br>SV12, SV13,<br>SV14, SV15,<br>SV16, SV17,<br>SV18, SV22 | Connector/<br>Contact |

| 0.1               | SAMTEC                              | CONN HEADER<br>10POS .100" SNGL<br>TIN                            | CONN<br>HEADER<br>10POS .100"<br>SNGL TIN    | 2                                                   | SV8, SV9                                                                                 | Connector/<br>Contact |

| 0.1               |                                     | JUMPER, 0.100"                                                    |                                              | 14                                                  |                                                                                          | Connector/<br>Contact |

# **Test Recommendations**

To guarantee measurement accuracy, the following precautions should be observed:

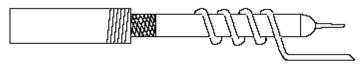

1. You should use a low-loop-inductance scope probe tip, similar to the probe tip illustrated in Figure 4, to measure signals.

Figure 4: Low-Loop-Inductance Scope Probe Tip

2. Logic signal rise and fall times should be much less than 1us and be monotonic.

### **Document Revision History**

| DATE          | DOCUMENT VERSION | CHANGES                                                        |

|---------------|------------------|----------------------------------------------------------------|

| April 2015    | 2.0              | Text of Instruction 3, Page 2 and Note 2, Page 5, Figures 2-3. |

| February 2015 | 1.0              | Initial release.                                               |

# **Contact Information**

Altera Corporation 101 Innovation Drive San Jose, CA 95134 Phone: 408-544-7000 www.altera.com

© 2015 Altera Corporation—Confidential. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Altera:

EVB-ES1030QI