# MAX 10 FPGA 10M50 Evaluation Kit User Guide

**UG-20006** 2016.02.29

101 Innovation Drive San Jose, CA 95134 www.altera.com

# Contents

| MAX 10 FPGA 10M50 Evaluation Kit Overview   | 1-1 |

|---------------------------------------------|-----|

| Board Component Blocks                      |     |

| Supported Items Not Included with the Kit   |     |

|                                             |     |

| Getting Started                             |     |

| Powering the Kit                            |     |

| Installing the USB-Blaster Driver           |     |

| Handling the Kit                            |     |

| Factory Default Switch and Jumper Settings  | 2-2 |

| Board Components                            |     |

| Board Overview                              |     |

| Featured Device: MAX 10 FPGA                |     |

| Configuration                               |     |

| Using the Quartus II Programmer             |     |

| Selecting the Internal Configuration Scheme |     |

| Status Elements                             |     |

| Setup Elements                              |     |

| General User Input/Output                   |     |

| Clock Circuitry                             |     |

| On-Board Oscillators                        |     |

| Off-Board Clock Input/Output                |     |

| Clock Control GUI                           |     |

| Components and Interfaces                   |     |

| HDMI Video Output                           |     |

| Pmod Connectors                             |     |

| Memory                                      |     |

| Flash                                       |     |

| MIPI CSI-2 Transmitter                      |     |

| MIPI CSI-2 Receiver                         |     |

| Power Supply                                |     |

| Document Revision History          |  |

|------------------------------------|--|

| Compliance & Conformity Statements |  |

| CE EMI Conformity Caution          |  |

|                                    |  |

# MAX 10 FPGA 10M50 Evaluation Kit Overview

| 2016.02.29 |                         |  |

|------------|-------------------------|--|

| UG-20006   | Subscribe Send Feedback |  |

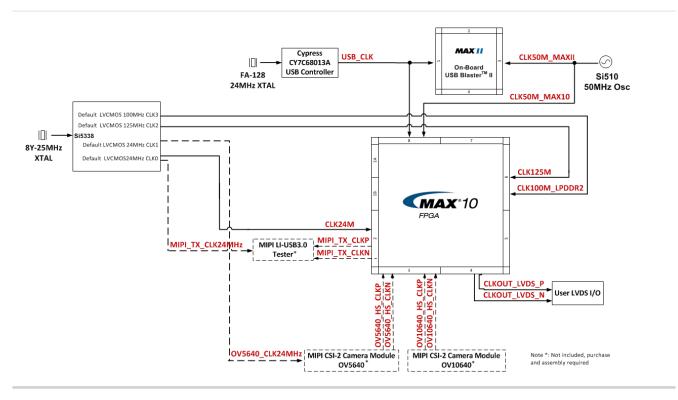

The MAX<sup>®</sup> 10 Evaluation Kit (P/N : EK-10M50F484) provides an easy-to-use platform for evaluating the MAX 10 FPGA technology and Enpirion<sup>®</sup> PowerSoC regulators. You can use this kit to do the following:

- Develop designs for the 10M50, F484 package FPGA

- Validate MIPI CSI-2 passive solution for both MIPI transmitter and receiver

- Demonstrate video applications together with HDMI

- Interface MAX 10 FPGAs to LPDDR2 memory at 200 MHz performance

- Interface to daughter cards and peripherals using Digilent Pmod<sup>™</sup> Compatible connectors

- Bridge to external devices through single-ended and LVDS through-hole vias

- Measure FPGA power (VCC\_CORE)

- Reuse the kit's PCB board and schematic as a model for your design

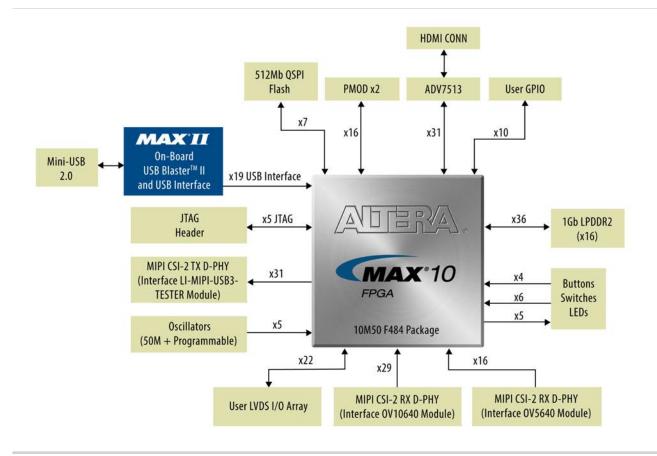

# **Board Component Blocks**

The MAX 10 FPGA 10M50 Evaluation Kit features the following major component blocks. For a detailed description of the board components, see "Board Components" section on Page 3-1.

- Featured Devices

- MAX 10 FPGA 10M50D, dual supply, F484 package (P/N: 10M50DAF484C6GES)

- MAX II CPLD EPM1270M256C4N (On-board USB Blaster II)

- Enpirion EP5348UI 400mA PowerSoC Synchronous Buck Regulator with Integrated Inductor

- Enpirion EP5358xUI 600mA PowerSoC DC-DC Step-Down Converters with Integrated Inductor

- Enpirion EN5329QI/EN5339QI 2A/3A PowerSoC Low Profile Synchronous Buck DC-DC Converter with Integrated Inductor

- FPGA configuration

- Embedded USB-Blaster II (JTAG)

- Optional JTAG direct via 10-pin header

- On Board clocking circuitry

- 25 MHz single-ended, external oscillator clock source

- Silicon Labs Si510 crystal oscillator

- Silicon Labs Si5338 clock generator with programmable frequency GUI

- Memory devices

- 64M x 16 1Gbits LPDDR2 with soft memory controller

- 512Mbits Quad Serial Peripheral Interface (Quad SPI) Flash

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

#### 1-2 Board Component Blocks

- Communication Ports

- One HDMI video output

- Two 12-pin Pmod connectors

- Two 36-pin MIPI FFC connectors and one 16-pin MIPI FFC connector

- General User I/O

- General-purpose single-ended through-hole vias (2x5)

- General-purpose LVDS through-hole vias (2 x 9 LVDS pairs, plus two clock pairs)

- 5 Green User-defined LEDs

- 4 User-defined push buttons

- User DIP Switches (SW1, SW2.1, SW2.2)

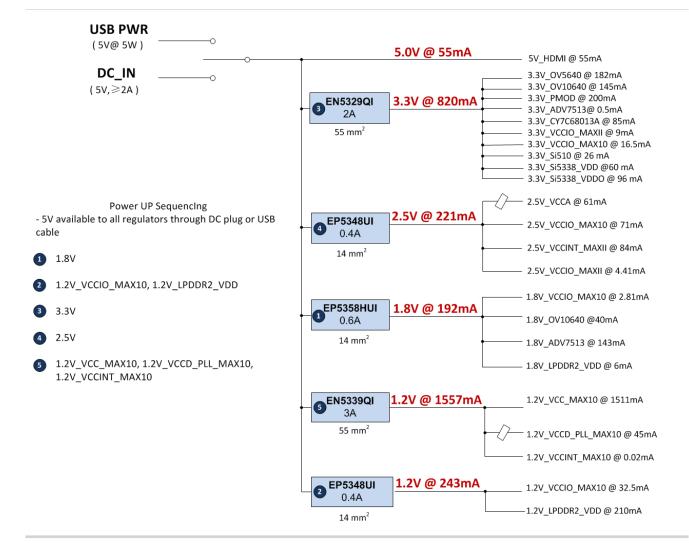

- Power

- Yellow Power-ON LEDs (D9, D10, D11)

- USB Y cable (USB Type-A to mini Type-B) for both on-board USB-Blaster II and 5V/1A power capability

- Support DC power adapter option, but 5V power supply and cord are not included in the kit

- Software

- Free Quartus<sup>®</sup> Prime Lite Edition design software (download software and license from http:// www.altera.com/download)

- Complete documentation

- User Guide, bill of material, schematic and board files

Send Feedback

#### Figure 1-1: MAX 10 10M50 FPGA Evaluation Kit Block Diagram

Related Information Board Components on page 3-1

## Supported Items Not Included with the Kit

The following items are not included in the kit but were designed to be used in conjunction with this kit. All of these items are sold separately.

Table 1-1: Additional Components Not Included with the Kit

| Board<br>Reference | Description                                         | Manufacturer                       | Manufacturing<br>Part Number          | Manufacturer Website                                           |

|--------------------|-----------------------------------------------------|------------------------------------|---------------------------------------|----------------------------------------------------------------|

| J1, J2             | Cable Flat Flex Top /<br>Top 36 POS 0.5 MM<br>pitch | Parlex<br>Molex<br>Leopard Imaging | 050R36-76B<br>0210200385<br>LI-FLEX03 | www.parlex.com<br>www.molex.com<br>www.leopardi-<br>maging.com |

| Board<br>Reference | Description                                             | Manufacturer               | Manufacturing<br>Part Number | Manufacturer Website                                                             |

|--------------------|---------------------------------------------------------|----------------------------|------------------------------|----------------------------------------------------------------------------------|

| J3                 | Cable Flat Flex Top/<br>Bottom 16 POS 0.5 MM<br>6inches | Wurth Electronics<br>Molex | 687716152002<br>02010200171  | www.we-online.com<br>www.molex.com                                               |

| J12, J13           | 2x10 0.1-inch headers<br>(for LVDS GPIO)                | Wurth Electronics          | 61302021121                  | www.we-online.com                                                                |

| J14                | 2x7 0.1-inch headers (for GPIO)                         | Wurth Electronics          | 61301421121                  | www.we-online.com                                                                |

| J5                 | USB-Blaster Download<br>Cable                           | Altera                     | PL-USB-<br>BLASTER-RCN       | https://www.altera.com/<br>products/boards_and_<br>kits/download-<br>cables.html |

| J5                 | USB-Blaster II<br>Download Cable                        | Altera                     | PL-USB2-<br>BLASTER          | https://www.altera.com/<br>products/boards_and_<br>kits/download-<br>cables.html |

| J10                | Standard 5V, 2.0A<br>Switching Power<br>Adapter         | LI Tone Electronics        | LTE12E-S1-316                | www.lte.com.tw                                                                   |

| J10                | Standard 5V, 3.0A<br>Switching Power<br>Adapter         | Huntkey                    | HKA08105030-<br>8B           | http://<br>dealer.huntkey.com/en/                                                |

| J1                 | LI-MIPI-USB-Tester<br>Daughter Card                     | Leopard Imaging            | LI-USB30-<br>MIPI-TESTER     | http://shop.leopardi-<br>maging.com                                              |

| J2                 | LI-CAM-OV10640-MIPI<br>Daughter Card                    | Leopard Imaging            | LI_CAM-<br>OV10640-MIPI      | http://shop.leopardi-<br>maging.com                                              |

| J3                 | MIPI 5MP AF Camera<br>Daughter Card                     | UDOO                       | MIPI 5MP IR<br>AF Camera     | http://shop.udoo.org                                                             |

MAX 10 FPGA 10M50 Evaluation Kit Overview

Send Feedback

# **Powering the Kit**

You can apply power to the MAX 10 FPGA Evaluation Kit by plugging in either the 5V DC power adapter to wall jack, or the USB cable to your PC. For low-power design, USB cable connection is suggested, and it can easily provide both power and on-board USB Blaster connection. For high-power design, 5V DC adapter solution is preferred to ensure device performance.

The board includes one Jumper (J11) for power option selection. When use DC power adapter, J11 needs to be placed at Position 1 and 2; while for using USB power, J11 needs to be placed at Position 2 and 3.

Resistors (R292 and R293) can be populated and used in place of the jumper if you want to hard wire the power option.

When powered correctly, D9, D10 and D11 will light.

**Caution:** Resistors R292 and R293 are designed for hard wiring the power selection. J11 must not be used when either R292 or R293 is populated.

# Installing the USB-Blaster Driver

The development board includes integrated USB-Blaster circuitry for FPGA programming. However, for the host computer and board to communicate, you must install the On-Board USB-Blaster II driver on the host computer.

Installation instructions for the On-Board USB-Blaster II driver for your operating system are available on the Altera website. On the Altera Programming Cable Driver Information page of the Altera website, locate the table entry for your configuration and click the link to access the instructions.

# Handling the Kit

When handling the board, it is important to observe the following static discharge precaution:

**Caution:** Without proper anti-static handling, the board can be damaged. Therefore, use anti-static handling precautions when touching the board.

ISO 9001:2008 Registered

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

The MAX 10 Evaluation Kit must be stored between  $-40^{\circ}$  C and  $100^{\circ}$  C. The recommended operating temperature is between  $0^{\circ}$  C and  $85^{\circ}$  C.

# **Factory Default Switch and Jumper Settings**

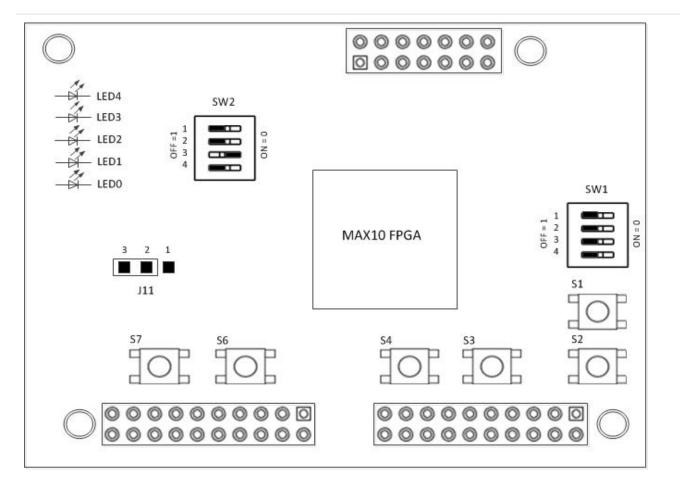

#### Figure 2-1: Switch Locations and Default Settings (Board Top)

#### Table 2-1: Default SW1 DIP Switch Settings

| Board Reference | Signal Name | Function     | Default Position |

|-----------------|-------------|--------------|------------------|

| SW1.1           | USER_DIPSW0 | User-Defined | HIGH (OFF =1)    |

| SW1.2           | USER_DIPSW1 | User-Defined | HIGH (OFF =1)    |

| SW1.3           | USER_DIPSW2 | User-Defined | HIGH (OFF =1)    |

| SW1.4           | USER_DIPSW3 | User-Defined | HIGH (OFF =1)    |

#### Table 2-2: Default SW2 DIP Switch Settings

| Board Reference | Signal Name | Function     | Default Position |

|-----------------|-------------|--------------|------------------|

| SW2.1           | USER_DIPSW4 | User-Defined | HIGH (OFF =1)    |

**Getting Started**

| 2 | -3 |  |

|---|----|--|

| ~ |    |  |

| Board Reference | Signal Name  | Function                                                                                                                                                                                                                                                                                                                                                                                    | Default Position |

|-----------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| SW2.2           | USER_DIPSW5  | User-Defined                                                                                                                                                                                                                                                                                                                                                                                | HIGH (OFF =1)    |

| SW2.3           | CONFIG_SEL   | CONFIG_SEL: Use this<br>pin to choose CFM0,<br>CFM1 or CFM2 image<br>as the first boot image<br>in dual-image configu-<br>ration. If the CONFIG_<br>SEL is set to low, the<br>first boot image is<br>CFM0 image. If<br>CONFIG_SEL is set o<br>high, the first boot<br>image is CFM1 or<br>CFM2 image. This pin<br>is read before user<br>mode and before the<br>nSTATUS pin is<br>asserted. | LOW (ON =0)      |

| SW2.4           | VTAP_BYPASSn | A virtual JTAG device<br>is provided within the<br>On-board USB-Blaster<br>II, it provides access to<br>diagnostic hardware<br>and board identifica-<br>tion information. The<br>device shows up as an<br>extra device on the<br>JTAG chain with ID:<br>020D10DD. This<br>switch removes the<br>virtual JTAG device<br>from the JTAG chain.                                                 | HIGH (OFF =1)    |

## Table 2-3: Default J11 Jumper Settings

| Jumper   | Function                                                                                                                | Setting      |

|----------|-------------------------------------------------------------------------------------------------------------------------|--------------|

| J11[1-2] | Jumper for board DC adapter<br>power option when R292 and<br>R293 not installed                                         | Pins 1 and 2 |

| J11[2-3] | Jumper for board USB power<br>option when R292 and R293<br>not installed. This is the<br>default power jumper position. | Pins 2 and 3 |

# Board Components 3

UG-20006 Subscribe Send Feedback

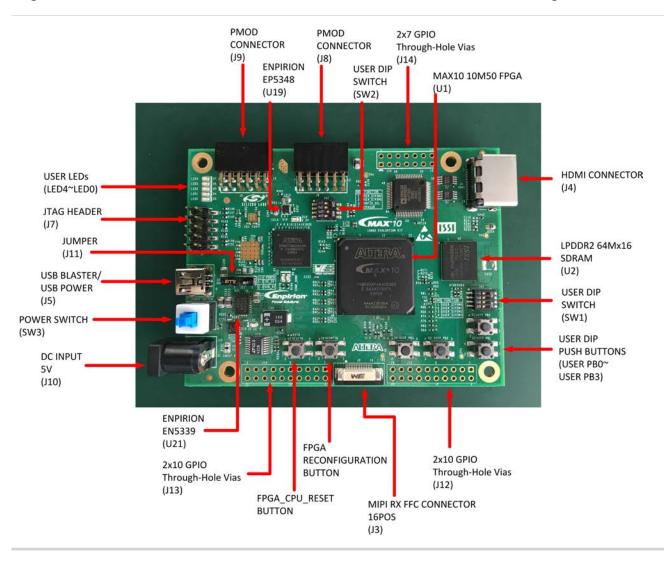

This chapter introduces all the important components on the evaluation kit. The *Overview of the MAX 10 FPGA Evaluation Kit Features* figure illustrates major component locations and *MAX 10M50 FPGA* (10M50, 484-FPGA) Evaluation Kit Components table in this chapter provides a brief description of all features of the board.

Related Information Board Component Blocks on page 1-1

# **Board Overview**

2016.02.29

This section provides an overview of the evaluation kit, including an annotated board image and component descriptions.

© 2016 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

#### Figure 3-1: Overview of the MAX 10 10M50 FPGA Evaluation Kit Features - Board Image (Front View)

**Board Components**

Send Feedback

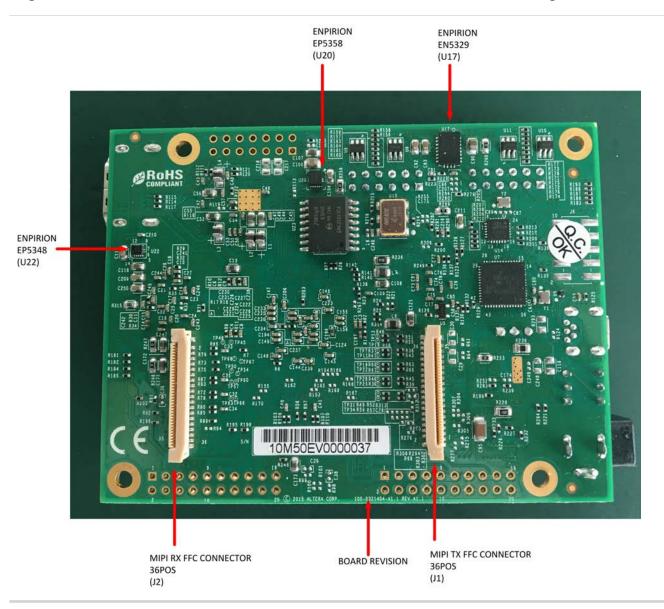

#### Figure 3-2: Overview of the MAX 10 10M50 FPGA Evaluation Kit Features - Board Image (Rear View)

#### Table 3-1: MAX 10 FPGA (10M50, 484-FPGA) Evaluation Kit Components

| Board Reference | Туре            | Description                                                                                                |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------|

| Featured Device |                 |                                                                                                            |

| U1              | FPGA            | MAX 10 FPGA 10M50DAF484C6GES,<br>50K LEs, F484 package, -6ES speed grade.                                  |

| U13             | CPLD            | MAX II EPM1270 256-MBGA, 2.5V/3.3V,<br>VCCINT for On-Board USB-Blaster II.                                 |

| U17             | Power Regulator | Enpirion EN5329QI 2A PowerSoC Low<br>Profile Synchronous Buck DC-DC<br>Converter with Integrated Inductor. |

**Board Components**

**Altera Corporation**

|                        |                                        | 2016                                                                                                                                                                       |

|------------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Board Reference        | Туре                                   | Description                                                                                                                                                                |

| U19, U22               | Power Regulator                        | Enpirion EP5348UI 400mA PowerSoC<br>Synchronous Buck Regulator with<br>Integrated Inductor.                                                                                |

| U20                    | Power Regulator                        | Enpirion EP5358HUI 600mA PowerSoC<br>Synchronous Buck Regulator with<br>Integrated Inductor.                                                                               |

| U21                    | Power Regulator                        | Enpirion EN5339QI 3A PowerSoC Low<br>Profile Synchronous Buck DC-DC<br>Converter with Integrated Inductor.                                                                 |

| Configuration and Setu | p Elements                             | -                                                                                                                                                                          |

| J5                     | On-Board (Embedded) USB-<br>Blaster II | Mini Type-B USB connector for program-<br>ming and debugging the FPGA.                                                                                                     |

| J7                     | 10-pin header                          | Optional JTAG direct via 10-pin header for external download cables.                                                                                                       |

| SW2                    | DIP configuration and user switch      | SW2 includes switches to control boot images and JTAG bypass.                                                                                                              |

| S6                     | MAX10 nCONFIG push<br>button           | Toggling this button causes the FPGA to<br>reconfigure from on-die Configuration<br>Flash Memory (CFM).                                                                    |

| S7                     | FPGA register push button              | Toggling this button resets all registers in the FPGA.                                                                                                                     |

| J11                    | Jumper for board power option          | Default connection is Pins 2 and 3 position,<br>which uses USB power supply. If needed,<br>change jumper position to Pins 1 and 2 for<br>DC adapter power supply solution. |

| Status Elements        |                                        | 1                                                                                                                                                                          |

| D8                     | Configuration done LED, green          | Illuminates when the FPGA is configured.                                                                                                                                   |

| D9                     | Power LED, yellow                      | Indicates that 5V is powered up success-<br>fully.                                                                                                                         |

| D10                    | Power LED, yellow                      | Indicates that 2.5V is powered up successfully.                                                                                                                            |

| D11                    | Power LED, yellow                      | Indicates that 1.2V is powered up successfully.                                                                                                                            |

| Clock Circuitry        |                                        |                                                                                                                                                                            |

| U14                    | Programmable Clock                     | Four channel programmable oscillator with default frequencies of 24, 24, 125,100 MHz.                                                                                      |

| U15                    | 50-MHz oscillator                      | 50-MHz crystal oscillator for general<br>purpose logic of MAX 10 and MAX II<br>devices                                                                                     |

devices.

General User Input and Output

**Board Components**

Board Overview

3-5

| Board Reference         | Туре                                              | Description                                                                                                                                                                       |

|-------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$1, \$2, \$3, \$4      | User push buttons                                 | Four user push buttons. Driven low when pressed.                                                                                                                                  |

| D3, D4, D5, D6, D7      | User LEDs, green                                  | Five user LEDs. Illuminate when driven low.                                                                                                                                       |

| SW1, SW2.1, SW2.2       | User DIP switches                                 | Quad user DIP switches.                                                                                                                                                           |

| Memory Devices          |                                                   |                                                                                                                                                                                   |

| U2                      | LPDDR2 SDRAM memory                               | 64 M x16                                                                                                                                                                          |

| U23                     | Quad serial peripheral interface (quad SPI) flash | 512 Mb                                                                                                                                                                            |

| Video and Display Ports | · · · · · · · · · · · · · · · · · · ·             | ·                                                                                                                                                                                 |

| J1                      | MIPI CSI-2 transmitter output                     | MIPI CSI-2 transmitter output to Leopard<br>Imaging LI-MIPI-USB3-Tester module.                                                                                                   |

| J2                      | MIPI CSI-2 receiver                               | MIPI CSI-2 receiver input from Leopard<br>Imaging LI-CAM-OV10640-MIPI module.                                                                                                     |

| J3                      | MIPI CSI-2 receiver                               | MIPI CSI-2 receiver input from UDOO<br>Camera Module OV5640.                                                                                                                      |

| J4                      | HDMI video output                                 | 19-pin HDMI connector which provides a<br>HDMIv1.4 video output of up to 1080p<br>through an ADI (Analog Devices, Inc)<br>HDMI transmitter (ADV7513).                             |

| I/O and Expansion Port  | S                                                 | ·                                                                                                                                                                                 |

| J8, J9                  | Two Diligent Pmod connectors                      | 12-pin interface with 8 I/O signal pins used<br>to connect low frequency, low I/O<br>peripheral modules.                                                                          |

| J12, J13                | Two 2x10 GPIO connectors,<br>user install         | You can use this area to connect or solder<br>additional components for connection of 9<br>true LVDS pairs with clock input and<br>output, or 22 single-ended I/O signals.        |

| J14                     | 2x7 GPIO connectors, user install                 | You can use this area to connect or solder<br>additional components for connection of<br>10 single-ended I/O signals.                                                             |

| Power Supply            |                                                   |                                                                                                                                                                                   |

| J10                     | DC input jack                                     | Accepts 5V DC power supply when USB power supply is not in use.                                                                                                                   |

| SW3                     | Power switch                                      | When using DC power adapter, switch to<br>power on or off the board when power is<br>supplied from the DC input jack. DC<br>adapter and USB power don't work at the<br>same time. |

| Board Reference | Туре          | Description                                                                                                                        |

|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------|

| J5              | USB connector | USB power supply. Use with USB Y cable<br>to provide 1A current. DC adapter power<br>and USB power don't work at the same<br>time. |

# Featured Device: MAX 10 FPGA

The MAX 10 FPGA development board features the MAX 10 10M50DAF484C6GES device (U1) in a 484-pin FineLine BGA package.

#### Table 3-2: MAX 10 FPGA 10M50DAF484C6GES Features

| Logic<br>Element<br>(LEs) | Internal<br>s Configura-<br>tion | M9K<br>Memory<br>(Kb) | User Flash<br>Memory<br>(KB) | 18-bit X 18-<br>bit<br>Multipliers | PLLs | ADC Blocks /<br>Temperature<br>Sensing<br>Diode | External Memory<br>Interfaces<br>Supported |

|---------------------------|----------------------------------|-----------------------|------------------------------|------------------------------------|------|-------------------------------------------------|--------------------------------------------|

| 50,00                     | ) Dual                           | 1,638                 | 736 Note 1                   | 144                                | 4    | 2/1                                             | DDR3,<br>DDR3L,<br>DDR2,<br>LPDDR2         |

**Note: 1.** The maximum possible value including user flash memory and configuration flash memory. For more information, refer to MAX 10 User Flash Memory User Guide.

# Configuration

The MAX 10 10M50 Evaluation Kit supports two configuration methods:

- Configuration by downloading a **.sof** file to the FPGA. Any subsequent power cycling of the FPGA or reconfiguration will power up the FPGA to a blank state.

- Programming of the on-die FPGA Configuration Flash Memory (CFM) via a **.pof** file. Any power cycling of the FPGA or reconfiguration will power up the FPGA in self-configuration mode, using the files stored in the CFM

You can use two different USB-Blaster hardware components to program the .sof or .pof files:

- Embedded USB-Blaster II, mini Type-B connector (J5)

- JTAG header (J7). Use an external USB-Blaster, USB-Blaster II, or Ethernet Blaster download cable. The external download cable connects to the board through the JTAG header.

## Using the Quartus II Programmer

You can use the Quartus II Programmer to configure the FPGA with a .sof.

Before configuring the FPGA:

- Ensure that the Quartus II Programmer and the USB-Blaster driver are installed on the host computer

- The USB cable is connected to the kit

- Power to the board is on, and no other applications that use the JTAG chain are running.

**Altera Corporation**

**Board Components**

To configure the MAX 10 FPGA:

- **1.** Start the Quartus II Programmer.

- 2. Click Add File and select the path to the desired .sof.

- 3. Turn on the Program/Configure option for the added file.

- 4. Click Start to download the selected file to the FPGA. Configuration is complete when the progress bar reaches 100%.

The Quartus II Convert Programming File (CPF) GUI can be used to generate a .sof file that can use for internal configuration. You can directly program the MAX 10 device's flash which includes Configuration Flash Memory (CFM) and User Flash Memory (UFM) by using a download cable with the Quartus II software programmer.

## Selecting the Internal Configuration Scheme

For all MAX 10 devices, except 10M02 device, there are total of 5 different modes you can select internal configuration. Please refer to Figure 2-2: Configuration Flash Memory Sectors Utilization for all MAX 10 Devices Except for 10M02 Device of MAX 10 FPGA Configuration User Guide. You can access the PDF of the MAX 10 FPGA Configuration User guide here.

The internal configuration scheme needs to be selected before design compilation. To select the configuration mode:

- 1. Open the Quartus II software and load a project using MAX 10 device family.

- 2. On the Assignments menu, click Settings. The Settings dialog box appears.

- 3. In the Category list, select **Device**. The **Device** page appears.

- 4. Click Device and Pin Options.

- 5. In the Device and Pin Options dialog box, click the Configuration tab.

- 6. In the Configuration Scheme list, select Internal Configuration.

- 7. In the **Configuration Mode** list, select 1 out of 5 configuration modes. For the dual-boot feature:

- **a.** Must have a Dual Boot IP in the design, for example, in a Qsys component.

- b. Choose Dual Compressed Images (512 Kbits UFM) for the Configuration Mode.

- c. Generate two .sof files above and convert them into one .pof file for CFM programming.

- 8. Turn on Generate compressed bit-streams if needed, and click OK.

## **Status Elements**

This topic lists the non-user status elements for the MAX 10 10M50 FPGA Evaluation Board.

#### Table 3-3: Status LED Signal Names

| Board Reference | Signal Name         | Colour | Device/Pin Number | I/O Standard |

|-----------------|---------------------|--------|-------------------|--------------|

| D8              | MAXII_CONF_<br>DONE | Green  | MAX II / Y10      | 3.3 V        |

| D9              | 5V_LED_R            | Yellow |                   |              |

| D10             | 2.5V_LED_R          | Yellow |                   |              |

| D11             | 1.2V_LED            | Yellow | MAX II / Y9       | 3.3 V        |

**Board Components**

3-7

# **Setup Elements**

#### Table 3-4: Board Settings DIP Switch and Jumper Schematic Signals

| Board Reference | Signal Name      | Device / Pin Number | I/O Standard |

|-----------------|------------------|---------------------|--------------|

| SW2.3           | MAX10_CONFIG_SEL | MAX 10 / H10        | 3.3V         |

| SW2.4           | MAX10_BYPASSn    | MAX II / B20        | 3.3V         |

#### **Table 3-5: Board Settings Push Button Signal Names**

| Board Reference | Signal Name   | MAX 10 FPGA Pin<br>Number | I/O Standard |

|-----------------|---------------|---------------------------|--------------|

| S6              | MAX10_nCONFIG | H9                        | 3.3V         |

| S7              | MAX10_RESETn  | D9                        | 3.3V         |

# **General User Input/Output**

User-defined I/O signal names, FPGA pin numbers, and I/O standards for the MAX 10 FPGA 10M50 Evaluation Board.

#### Table 3-6: User-Defined Push Button Signal Names

| Board Reference | Signal Name | MAX 10 FPGA Pin<br>Number | I/O Standard |

|-----------------|-------------|---------------------------|--------------|

| S1              | USER_PB0    | R20                       | 1.2 V        |

| S2              | USER_PB1    | Y20                       | 1.2 V        |

| S3              | USER_PB2    | Y21                       | 1.2 V        |

| S4              | USER_PB3    | U20                       | 1.2 V        |

#### Table 3-7: User-Defined DIP Switch Schematic Signal Names

| Board Reference | Signal Name | MAX 10 FPGA Pin<br>Number | I/O Standard |

|-----------------|-------------|---------------------------|--------------|

| SW1.1           | USER_DIPSW0 | R18                       | 1.2 V        |

| SW1.2           | USER_DIPSW1 | T19                       | 1.2 V        |

| SW1.3           | USER_DIPSW2 | T18                       | 1.2 V        |

| SW1.4           | USER_DIPSW3 | U19                       | 1.2 V        |

| SW2.1           | USER_DIPSW4 | G4                        | 3.3 V        |

**Board Components**

Send Feedback

| Board Reference | Signal Name | MAX 10 FPGA Pin<br>Number | I/O Standard |

|-----------------|-------------|---------------------------|--------------|

| SW2.2           | USER_DIPSW5 | F5                        | 3.3 V        |

## Table 3-8: User LED Schematic Signal Names

| Board Reference | Signal Name | Color | MAX 10 FPGA Pin<br>Number | I/O Standard |

|-----------------|-------------|-------|---------------------------|--------------|

| D3              | USER_LED0   | Green | C3                        | 3.3 V        |

| D4              | USER_LED1   | Green | C4                        | 3.3 V        |

| D5              | USER_LED2   | Green | C5                        | 3.3 V        |

| D6              | USER_LED3   | Green | D5                        | 3.3 V        |

| D7              | USER_LED4   | Green | C7                        | 3.3 V        |

## Table 3-9: User Defined I/O Through-Hole Vias

| Board Reference | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard <sup>Note 1</sup>    | Description                                                                                    |

|-----------------|--------------------------|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|

| J12.1           | 2.5V Power               |                           |                                   | Power Supply Connector<br>for J12                                                              |

| J12.2           | 2.5V Power               |                           |                                   | Power Supply Connector<br>for J12                                                              |

| J12.3           | USER_CLKIN_<br>IO_P      | K22                       | DIFFIO_RX_R40P<br>or CLK3P        | Dual purpose pin. Either<br>User I/O or Clock input<br>ref. for this group of<br>LVDS channels |

| J12.4           | USER_LVDS_P2             | Y17                       | DIFFIO_TX_RX_<br>B43P, High Speed | LVDS User I/O_2. Note 1                                                                        |

| J12.5           | USER_CLKIN_<br>IO_N      | K21                       | DIFFIO_RX_<br>R40N or CLK3N       | Dual purpose pin. Either<br>User I/O or Clock input<br>ref. for this group of<br>LVDS channels |

| J12.6           | USER_LVDS_N2             | AA17                      | DIFFIO_TX_RX_<br>B43N, High Speed | LVDS User I/O_2. Note 1                                                                        |

| J12.7           | GND                      |                           |                                   | Ground Reference for this group of I/Os                                                        |

| J12.8           | GND                      |                           |                                   | Ground Reference for this group of I/Os                                                        |

|                 |                          |                           |                                            | 2010.0                                                                                          |

|-----------------|--------------------------|---------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------|

| Board Reference | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard <sup>Note 1</sup>             | Description                                                                                     |

| J12.9           | USER_LVDS_P0             | AA10                      | DIFFIO_TX_RX_<br>B22P, High Speed          | LVDS User I/O_0. Note 1                                                                         |

| J12.10          | USER_LVDS_P3             | Y14                       | DIFFIO_TX_RX_<br>B37P, High Speed          | LVDS User I/O_3. Note 1                                                                         |

| J12.11          | USER_LVDS_N0             | Y10                       | DIFFIO_TX_RX_<br>B22N, High Speed          | LVDS User I/O_0. Note 1                                                                         |

| J12.12          | USER_LVDS_N3             | Y13                       | DIFFIO_TX_RX_<br>B37N, High Speed          | LVDS User I/O_3. Note 1                                                                         |

| J12.13          | GND                      |                           |                                            | Ground Reference for this group of I/Os                                                         |

| J12.14          | GND                      |                           |                                            | Ground Reference for this group of I/Os                                                         |

| J12.15          | USER_LVDS_P1             | W8                        | DIFFIO_TX_RX_<br>B13p, High Speed          | LVDS User I/O_1. Note 1                                                                         |

| J12.16          | CLKOUT_LVDS_<br>P        | V17                       | DIFFIO_TX_RX_<br>B57P or PLL_B_<br>CLKOUTP | Dual purpose pin. Either<br>User I/O or Clock output<br>ref. for this group of<br>LVDS channels |

| J12.17          | USER_LVDS_N1             | W7                        | DIFFIO_TX_RX_<br>B13n, High Speed          | LVDS User I/O_1. Note 1                                                                         |

| J12.18          | CLKOUT_LVDS_<br>N        | W17                       | DIFFIO_TX_RX_<br>B57N or PLL_B_<br>CLKOUTN | Dual purpose pin. Either<br>User I/O or Clock output<br>ref. for this group of<br>LVDS channels |

| J12.19          | GND                      |                           |                                            | Ground Reference for this group of I/Os                                                         |

| J12.20          | GND                      |                           |                                            | Ground Reference for this group of I/Os                                                         |

| J13.1           | 2.5V Power               |                           |                                            | Power Supply for<br>Connector J13                                                               |

| J13.2           | 2.5V Power               |                           |                                            | Power Supply for<br>Connector J13                                                               |

| J13.3           | USER_LVDS_P5             | V8                        | DIFFIO_TX_RX_<br>B7p, High Speed           | LVDS User I/O_5. Note 1                                                                         |

Altera Corporation

**Board Components**

UG-20006 2016.02.29

| .02.29          |                          |                           |                                   |                                         |

|-----------------|--------------------------|---------------------------|-----------------------------------|-----------------------------------------|

| Board Reference | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard <sup>Note 1</sup>    | Description                             |

| J13.4           | USER_LVDS_P8             | AA7                       | DIFFIO_TX_RX_<br>B16p, High Speed | LVDS User I/O_8. Note 1                 |

| J13.5           | USER_LVDS_N5             | V7                        | DIFFIO_TX_RX_<br>B7n, High Speed  | LVDS User I/O_5. Note 1                 |

| J13.6           | USER_LVDS_N8             | AA6                       | DIFFIO_TX_RX_<br>B16n, High Speed | LVDS User I/O_8. Note 1                 |

| J13.7           | GND                      |                           |                                   | Ground Reference for this group of I/Os |

| J13.8           | GND                      |                           |                                   | Ground Reference for this group of I/Os |

| J13.9           | USER_LVDS_P6             | W6                        | DIFFIO_TX_RX_<br>B1p, High Speed  | LVDS User I/O_6. Note 1                 |

| J13.10          | USER_LVDS_P4             | W10                       | DIFFIO_TX_RX_<br>B11p, High Speed | LVDS User I/O_4. Note 1                 |

| J13.11          | USER_LVDS_N6             | W5                        | DIFFIO_TX_RX_<br>B1n, High Speed  | LVDS User I/O_6. Note 1                 |

| J13.12          | USER_LVDS_N4             | W9                        | DIFFIO_TX_RX_<br>B11n, High Speed | LVDS User I/O_4. Note 1                 |

| J13.13          | GND                      |                           |                                   | Ground Reference for this group of I/Os |

| J13.14          | GND                      |                           |                                   | Ground Reference for this group of I/Os |

| J13.15          | USER_LVDS_P7             | W3                        | DIFFIO_TX_RX_<br>B5p, High Speed  | LVDS User I/O_7. Note 1                 |

| J13.16          | NC                       |                           |                                   | Not Connected                           |

| J13.17          | USER_LVDS_N7             | W4                        | DIFFIO_TX_RX_<br>B5n, High Speed  | LVDS User I/O_7. Note 1                 |

| J13.18          | NC                       |                           |                                   | Not Connected                           |

| J13.19          | GND                      |                           |                                   | Ground Reference for this group of I/Os |

| J13.20          | GND                      |                           |                                   | Ground Reference for this group of I/Os |

**Board Components**

**Altera Corporation**

|                 |                          |                           |                                | 2016.02.2                               |

|-----------------|--------------------------|---------------------------|--------------------------------|-----------------------------------------|

| Board Reference | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard <sup>Note 1</sup> | Description                             |

| J14.1           | USER_IO0                 | A17                       | DIFFIO_RX_<br>T10n, High Speed | User I/O_0                              |

| J14.2           | USER_IO5                 | A19                       | DIFFIO_RX_T8n,<br>High Speed   | User I/O_5                              |

| J14.3           | USER_IO1                 | B19                       | DIFFIO_RX_T6n,<br>High Speed   | User I/O_1                              |

| J14.4           | USER_IO6                 | A20                       | DIFFIO_RX_T8p,<br>High Speed   | User I/O_6                              |

| J14.5           | 3.3V power               |                           |                                | Power Supply for<br>Connector J14       |

| J14.6           | 3.3V power               |                           |                                | Power Supply for<br>Connector J14       |

| J14.7           | USER_IO2                 | E16                       | DIFFIO_RX_T1p,<br>High Speed   | User I/O_2                              |

| J14.8           | USER_IO7                 | C18                       | DIFFIO_RX_T7p,<br>High Speed   | User I/O_7                              |

| J14.9           | USER_IO3                 | C19                       | DIFFIO_RX_T6n,<br>High Speed   | User I/O_3                              |

| J14.10          | USER_IO8                 | C17                       | DIFFIO_RX_T2n,<br>High Speed   | User I/O_8                              |

| J14.11          | GND                      |                           |                                | Ground Reference for this group of I/Os |

| J14.12          | GND                      |                           |                                | Ground Reference for this group of I/Os |

| J14.13          | USER_IO4                 | F16                       | DIFFIO_RX_T5p,<br>High Speed   | User I/O_4                              |

| J14.14          | USER_IO9                 | D17                       | DIFFIO_RX_T2p,<br>High Speed   | User I/O_9                              |

**Note: 1.** Termination resistors are required to be installed by the user for proper high speed LVDS I/O use.

**Board Components**

# **Clock Circuitry**

The MAX 10 FPGA 10M50 Evaluation Board includes two oscillators:

- A four channel programmable oscillator with default frequency of 24-MHz, 24-MHz, 125-MHz, 100-MHz.

- A two channel crystal oscillator with default frequency of 50-MHz.

## **On-Board Oscillators**

#### Figure 3-3: MAX 10 10M50 FPGA Evaluation Kit Clocks

#### Table 3-10: On-Board Oscillators

| Source | Schematic Signal<br>Name | Frequency  | I/O<br>Standard | Device / Pin<br>Number             | Application                                        |

|--------|--------------------------|------------|-----------------|------------------------------------|----------------------------------------------------|

| U14    | CLK24M                   | 24.000 MHz | 1.8 V<br>CMOS   | MAX 10/M9                          | Programmable<br>default 24 MHz<br>clock for MAX 10 |

| U14    | OV5640_<br>CLK24MHz      | 24.000 MHz | 3.3 V<br>CMOS   | 16 POS FFC<br>connector /<br>J3.12 | Clock for MIPI RX<br>OV5640 module                 |

| Source | Schematic Signal<br>Name | Frequency   | l/O<br>Standard | Device / Pin<br>Number | Application                                                                                                  |

|--------|--------------------------|-------------|-----------------|------------------------|--------------------------------------------------------------------------------------------------------------|

| U14    | CLK125M                  | 125.000 MHz | 3.3 V<br>CMOS   | MAX 10/K22             | Programmable<br>default 125 MHz<br>clock for PLL<br>generating required<br>clocks for LVDS<br>GPIO interface |

| U14    | CLK100M_LPDDR2           | 100.000 MHz | 3.3 V<br>CMOS   | MAX 10/E10             | LPDDR2 clock                                                                                                 |

| U15    | CLK50M_MAX10             | 50.000 MHz  | 3.3 V<br>CMOS   | MAX 10/J10             | MAX 10 clock                                                                                                 |

| U15    | CLK50M_MAXII             | 50.000 MHz  | 3.3 V<br>CMOS   | MAX II/L1              | MAX II clock                                                                                                 |

## **Off-Board Clock Input/Output**

The MAX 10 10M50 Evaluation Board has input and output clocks which can be driven onto the board. Resistor reworking might be needed for specific application.

Table 3-11: Off-Board Clock Inputs and Outputs

| Source | Schematic Signal<br>Name | I/O Standard | MAX 10 FPGA | Description                                                                                            |

|--------|--------------------------|--------------|-------------|--------------------------------------------------------------------------------------------------------|

| J12    | USER_CLKIN_P_<br>MAX10   | 1.2 V        | K21         | Single-ended clock input,<br>or positive terminal for<br>differential clock inputs<br>from user GPIO   |

| J12    | USER_CLKIN_N_<br>MAX10   | 1.2 V        | K22         | Single-ended clock input,<br>or negative terminal for<br>differential clock inputs<br>from user GPIO   |

| J12    | CLKOUT_LVDS_<br>P        | 2.5 V        | V17         | Single-ended clock<br>output, or positive<br>terminal for differential<br>clock output to user<br>GPIO |

| J12    | CLKOUT_LVDS_<br>N        | 2.5 V        | W17         | Single-ended clock<br>output, or negative<br>terminal for differential<br>clock output to user<br>GPIO |

**Board Components**

Send Feedback

## **Clock Control GUI**

This kit includes a Clock Control GUI application.

The Clock Control GUI application communicates over the JTAG bus to a test design running in the FPGA. It shares the JTAG bus with other applications like the Nios II debugger and the SignalTap<sup>®</sup> II Embedded Logic Analyzer. Because the Quartus II Programmer uses most of the bandwidth of the JTAG bus, other applications using the JTAG bus might time out. Be sure to close the other applications before attempting to reconfigure the FPGA using the Quartus II Programmer.

#### **The Clock Control**

The MAX 10 FPGA 10M50 Evaluation Board Clock Control application sets the programmable oscillators to any frequency between 10 MHz and 200 MHz. It communicates with the MAX II device on the board through the JTAG bus. The programmable oscillators are connected to the MAX II device through a 2-wire serial bus.

To run the Clock Control GUI, perform the following steps:

- 1. Make sure Quartus II 14.1 or later version is installed.

- 2. Connect the USB cable to the MAX 10M50 FPGA Evaluation Board and power cycle the board.

- 3. Double click the **Clock Control GUI** application and the interface shows as in the figure below.

- **4.** Perform **Default** to set the default frequencies to the board: CLK0-24MHz, CLK1-24MHz, CLK2-125MHz, CLK3-100MHz

- 5. Peform **Read** operation to get the current frequency setup.

- 6. If necessary, input new frequencies to each clock frequency fill-in box and perform Set New Freq to set the board to the input clock frequency setup.

- 7. Select the **Disable** to disable any clock channel if needed.

#### Figure 3-4: The Si5338 Tab

| 15338    | 自论          | 70  |         |  |

|----------|-------------|-----|---------|--|

| _vco: 24 | 00.0000 MHz |     |         |  |

| CLK0     | 24.0000     | MHz | Disable |  |

| CLK1     | 24.0000     | MHz |         |  |

| CLK2     | 125.0000    | MHz |         |  |

| CLK3     | 100.0000    | MHz |         |  |

#### Table 3-12: The Clock Control Tab

| Control         | Description                                                                                                                                                                                                                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F_vco           | Displays the generating signal value of the voltage-controlled oscillator                                                                                                                                                                                                                                                     |

| Registers       | Display the current frequencies for each oscillator                                                                                                                                                                                                                                                                           |

| Frequency (MHz) | Allows you to specify the frequency of the clock                                                                                                                                                                                                                                                                              |

| Disable         | Disable each oscillators as required                                                                                                                                                                                                                                                                                          |

| Read            | Reads the current frequency setting for the oscillator associated with the active tab                                                                                                                                                                                                                                         |

| Default         | Sets the frequency for the oscillator associated with the active<br>tab back to its default value. This can be also be accompanied<br>by power cycling the board.                                                                                                                                                             |

| Set New Freq    | Sets the programmable oscillator frequency for the selected<br>clock to the value in the CLK0 and CLK3 controls. Frequency<br>changes might take several milliseconds to take effect. You<br>might see glitches on the clock during this time. Altera<br>recommends resetting the FPGA logic after changing frequen-<br>cies. |

|                 | Note: Changing CLK0 of Si5338 will affect the Clock/<br>Power GUI. Once clock from Port CLK0 is used to<br>drive the MAX II device which is working as a 2-<br>wire serial bus interface connected to Si570, Si5338<br>and power monitor.                                                                                     |

# **Components and Interfaces**

This section describes the evaluation board's ports and optional interface cards relative to the MAX 10 FPGA device.

## **HDMI Video Output**

The MAX 10 10M50 evaluation kit supports one HDMI transmitter and one HDMI receptacle. The transmitter incorporates HDMI v1.4 features, and is capable of supporting an input data rate up to 165 MHz (1080p @ 60Hz, UXGA @ 60Hz). The connection between HDMI transmitter and MAX 10 is established in Bank 7, and the communication can be done via I2C interface.

#### Table 3-13: HDMI Pin Assignments, Signal Names and Functions

| Board Reference<br>(U3) | Signal Name         | MAX 10 FPGA Pin<br>Number | I/O Standard | Description                    |

|-------------------------|---------------------|---------------------------|--------------|--------------------------------|

| U3.62                   | HDMI_VIDEO_<br>DIN0 | J12                       | 3.3 V        | HDMI digital video data<br>bus |

UG-20006 2016.02.29

| Board Reference<br>(U3) | Signal Name          | MAX 10 FPGA Pin<br>Number | I/O Standard | Description                    |

|-------------------------|----------------------|---------------------------|--------------|--------------------------------|

| U3.61                   | HDMI_VIDEO_<br>DIN1  | D13                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.60                   | HDMI_VIDEO_<br>DIN2  | E12                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.59                   | HDMI_VIDEO_<br>DIN3  | E13                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.58                   | HDMI_VIDEO_<br>DIN4  | D12                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.57                   | HDMI_VIDEO_<br>DIN5  | B16                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.56                   | HDMI_VIDEO_<br>DIN6  | A16                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.55                   | HDMI_VIDEO_<br>DIN7  | C15                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.54                   | HDMI_VIDEO_<br>DIN8  | B14                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.52                   | HDMI_VIDEO_<br>DIN9  | A14                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.50                   | HDMI_VIDEO_<br>DIN10 | A13                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.49                   | HDMI_VIDEO_<br>DIN11 | B12                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.48                   | HDMI_VIDEO_<br>DIN12 | A12                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.47                   | HDMI_VIDEO_<br>DIN13 | C12                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.46                   | HDMI_VIDEO_<br>DIN14 | A11                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.45                   | HDMI_VIDEO_<br>DIN15 | B11                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.44                   | HDMI_VIDEO_<br>DIN16 | A10                       | 3.3 V        | HDMI digital video data bus    |

| U3.43                   | HDMI_VIDEO_<br>DIN17 | C14                       | 3.3 V        | HDMI digital video data bus    |

| U3.42                   | HDMI_VIDEO_<br>DIN18 | E14                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.41                   | HDMI_VIDEO_<br>DIN19 | D14                       | 3.3 V        | HDMI digital video data<br>bus |

| U3.40                   | HDMI_VIDEO_<br>DIN20 | C13                       | 3.3 V        | HDMI digital video data<br>bus |

**Board Components**

**Altera Corporation**

| Board Reference<br>(U3) | Signal Name            | MAX 10 FPGA Pin<br>Number | I/O Standard | Description                     |

|-------------------------|------------------------|---------------------------|--------------|---------------------------------|

| U3.39                   | HDMI_VIDEO_<br>DIN21   | E15                       | 3.3 V        | HDMI digital video data<br>bus  |

| U3.38                   | HDMI_VIDEO_<br>DIN22   | F15                       | 3.3 V        | HDMI digital video data<br>bus  |

| U3.37                   | HDMI_VIDEO_<br>DIN23   | D15                       | 3.3 V        | HDMI digital video data<br>bus  |

| U3.53                   | HDMI_VIDEO_<br>CLK     | D6                        | 3.3 V        | Video clock                     |

| U3.63                   | HDMI_VIDEO_<br>DATA_EN | J13                       | 3.3 V        | Video data enable               |

| U3.64                   | HDMI_HSYNC             | H13                       | 3.3 V        | Vertical synchronization        |

| U3.2                    | HDMI_VSYNC             | H14                       | 3.3 V        | Horizontal synchroniza-<br>tion |

| U3.28                   | HDMI_INTR              | A18                       | 3.3 V        | Interrupt signal                |

| U3.35                   | HDMI_SCL               | C16                       | 3.3 V        | HDMI I2C clock                  |

| U3.36                   | HDMI_SDA               | B17                       | 3.3 V        | HDMI I2C data                   |

## **Pmod Connectors**

The MAX 10 10M50 Evaluation Kit features two Digilent Pmod<sup>™</sup> compatible headers, which are used to connect low frequency, low I/O pin count peripheral modules.

The 12-pin version Pmod connector used in this kit provides 8 I/O signal pins. The peripheral module interface also encompasses a variant using I2C interface, and two or four wire MTE cables. The Pmod signals are connected to Bank 8.

Table 3-14: Pmod A Pin Assignments, Signal Names and Functions

| Schematic Signal<br>Name | Schematic Share<br>Bus Signal Name | MAX 10 FPGA Pin<br>Number | I/O Standard | Description |

|--------------------------|------------------------------------|---------------------------|--------------|-------------|

| PMODA_D0                 | PMODA_IO0                          | A6                        | 3.3 V        | In/Out      |

| PMODA_D1                 | PMODA_IO1                          | E8                        | 3.3 V        | In/Out      |

| PMODA_D2                 | PMODA_IO2                          | B4                        | 3.3 V        | In/Out      |

| PMODA_D3                 | PMODA_IO3                          | A5                        | 3.3 V        | In/Out      |

| PMODA_D4                 | PMODA_IO4                          | B7                        | 3.3 V        | In/Out      |

| PMODA_D5                 | PMODA_IO5                          | E9                        | 3.3 V        | In/Out      |

| PMODA_D6                 | PMODA_IO6                          | A4                        | 3.3 V        | In/Out      |

| PMODA_D7                 | PMODA_IO7                          | B5                        | 3.3 V        | In/Out      |

|                          | VCC                                |                           | 3.3 V        | Power       |

**Board Components**

Send Feedback

| Schematic Signal<br>Name | Schematic Share<br>Bus Signal Name | MAX 10 FPGA Pin<br>Number | I/O Standard | Description |

|--------------------------|------------------------------------|---------------------------|--------------|-------------|

|                          | GND                                |                           |              | GND         |

#### Table 3-15: Pmod B Pin Assignments, Signal Names and Functions

| Schematic Signal<br>Name | Schematic Share<br>Bus Signal Name | MAX 10 FPGA Pin<br>Number | I/O Standard | Description |

|--------------------------|------------------------------------|---------------------------|--------------|-------------|

| PMODB_D0                 | PMODB_IO0                          | C8                        | 3.3 V        | In/Out      |

| PMODB_D1                 | PMODB_IO1                          | D8                        | 3.3 V        | In/Out      |

| PMODB_D2                 | PMODB_IO2                          | A3                        | 3.3 V        | In/Out      |

| PMODB_D3                 | PMODB_IO3                          | A2                        | 3.3 V        | In/Out      |

| PMODB_D4                 | PMODB_IO4                          | B3                        | 3.3 V        | In/Out      |

| PMODB_D5                 | PMODB_IO5                          | C2                        | 3.3 V        | In/Out      |

| PMODB_D6                 | PMODB_IO6                          | B1                        | 3.3 V        | In/Out      |

| PMODB_D7                 | PMODB_IO7                          | B2                        | 3.3 V        | In/Out      |

|                          | VCC                                |                           | 3.3 V        | Power       |

|                          | GND                                |                           |              | GND         |

### Memory

This section describes the evaluation board's memory interface support and also their signal names, types, and connectivity relative to the FPGA. A soft IP memory controller is required as part of the FPGA design. The memory controller can be a user supplied IP or IP available for purchase from Intel PSG (formerly Altera) or a partner.

#### LPDDR2

The MAX 10 FPGA provides full-speed support to a x16 LPDDR2 200-MHz interface by using a 1Gbit x 16 memory.

Table 3-16: LPDDR2 Pin Assignments, Signal Names, and Functions

| Board Reference<br>(U2) | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard | Description                  |

|-------------------------|--------------------------|---------------------------|--------------|------------------------------|

| U2.P3                   | LPDDR2_CA0               | J22                       | 1.2V HSUL    | Command/Address Bus<br>Input |

| U2.N3                   | LPDDR2_CA1               | J21                       | 1.2V HSUL    | Command/Address Bus<br>Input |

| U2.M3                   | LPDDR2_CA2               | F22                       | 1.2V HSUL    | Command/Address Bus<br>Input |

| U2.M2                   | LPDDR2_CA3               | H21                       | 1.2V HSUL    | Command/Address Bus<br>Input |

**Board Components**

**Altera Corporation**

| Board Reference<br>(U2) | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard              | Description                  |

|-------------------------|--------------------------|---------------------------|---------------------------|------------------------------|

| U2.M1                   | LPDDR2_CA4               | H22                       | 1.2V HSUL                 | Command/Address Bus<br>Input |

| U2.G2                   | LPDDR2_CA5               | D22                       | 1.2V HSUL                 | Command/Address Bus<br>Input |

| U2.F2                   | LPDDR2_CA6               | C22                       | 1.2V HSUL                 | Command/Address Bus<br>Input |

| U2.F3                   | LPDDR2_CA7               | E22                       | 1.2V HSUL                 | Command/Address Bus<br>Input |

| U2.E3                   | LPDDR2_CA8               | A21                       | 1.2V HSUL                 | Command/Address Bus<br>Input |

| U2.E2                   | LPDDR2_CA9               | B22                       | 1.2V HSUL                 | Command/Address Bus<br>Input |

| U2.K1                   | LPDDR2_CKE               | E21                       | 1.2V HSUL                 | Clock Enable                 |

| U2.L1                   | LPDDR2_CSn               | G22                       | 1.2V HSUL                 | Chip Select                  |

| U2.J3                   | LPDDR2_CK                | D18                       | Differential 1.2V<br>HSUL | Differential Input Clock     |

| U2.H3                   | LPDDR2_CKn               | E18                       | Differential 1.2V<br>HSUL | Differential Input Clock     |

| U2.N8                   | LPDDR2_DQ0               | N18                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.M8                   | LPDDR2_DQ1               | N20                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.M7                   | LPDDR2_DQ2               | M20                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.M9                   | LPDDR2_DQ3               | M14                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.M6                   | LPDDR2_DQ4               | M18                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.L7                   | LPDDR2_DQ5               | M15                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.L8                   | LPDDR2_DQ6               | L20                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.L9                   | LPDDR2_DQ7               | L18                       | 1.2V HSUL                 | Data Bus Byte Lane 0         |

| U2.G9                   | LPDDR2_DQ8               | K20                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.G8                   | LPDDR2_DQ9               | K19                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.G7                   | LPDDR2_DQ10              | K18                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.F6                   | LPDDR2_DQ11              | H19                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.F9                   | LPDDR2_DQ12              | H20                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.F7                   | LPDDR2_DQ13              | H18                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.F8                   | LPDDR2_DQ14              | J14                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.E8                   | LPDDR2_DQ15              | J18                       | 1.2V HSUL                 | Data Bus Byte Lane 1         |

| U2.L6                   | LPDDR2_DQS0              | L14                       | Differential 1.2V<br>HSUL | Data Strobe P Byte Lane 0    |

**Altera Corporation**

**Board Components**

| Board Reference<br>(U2) | Schematic Signal<br>Name | MAX 10 FPGA Pin<br>Number | I/O Standard              | Description                          |

|-------------------------|--------------------------|---------------------------|---------------------------|--------------------------------------|

| U2.L5                   | LPDDR2_DQS0n             | L15                       | Differential 1.2V<br>HSUL | Data Strobe N Byte Lane<br>0         |

| U2.G6                   | LPDDR2_DQS1              | K14                       | Differential 1.2V<br>HSUL | Data Strobe Byte P Lane 1            |

| U2.G5                   | LPDDR2_DQS1n             | K15                       | Differential 1.2V<br>HSUL | Data Strobe Byte N Lane<br>1         |

| U2.K5                   | LPDDR2_DM0               | N19                       | 1.2V HSUL                 | Input Data Mask Byte<br>Lane 0       |

| U2.H5                   | LPDDR2_DM1               | J15                       | 1.2V HSUL                 | Input Data Mask Byte<br>Lane 1       |

| U2.D3                   | LPDDR2_ZQ                | /                         | 1.2V HSUL                 | Output Drive Strength<br>Calibration |

**Caution:** When customers start their own design (with unique PCB layout) and still wish to use the LPDDR2 interface, they should target the 10M50DCF484I6G or 10M50DAF484I6G. For other MAX 10 parts that support LPDDR2 interfaces (include any 10M16 or higher density MAX 10 device, with dual supply, F256 or higher pin-count, and –i6 speed grade), Quartus access to these parts requires contacting the local Altera sales person to provide the designer with a special .INI variable.

## Flash

The MAX 10 10M50 Evaluation Kit provides a 512-Mb (megabit) quad SPI flash memory. Altera Generic QUAD SPI controller core is used by default to erase, read, and write quad SPI flash in reference designs of the Board Test System (BTS) installer.

If you use the parallel flash loader (PFL) IP to program the quad SPI flash, you need to generate a **.pof** (Programmer Object File) to configure the device.

Perform the following steps to generate a .pof file:

1. Create a byte-order Quartus.ini file with the setting:

PGMIO\_SWAP\_HEX\_BYTE\_DATA=ON

- 2. Copy the .ini file to the project root directory and open the project with Quartus

- 3. Open Convert Programming Files tool to generate the .pof file

#### Table 3-17: Default Memory Map of the 512-Mb Quad SPI Flash

| Block Description         | Size (KB) | Address Range             |

|---------------------------|-----------|---------------------------|

| Board Test System Scratch | 512       | 0x03F8.0000 - 0x03FF.FFFF |

| User Software             | 56640     | 0x0083.0000 - 0x03F7.FFFF |

| Factory Software          | 4096      | 0x0043.0000 - 0x0082.FFFF |