#### MAX38647B

#### **Benefits and Features**

- Extends Battery Life

- 440nA Ultra-Low Quiescent Supply Current

- 5nA Shutdown Current

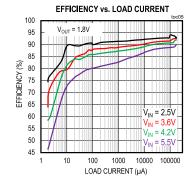

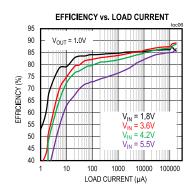

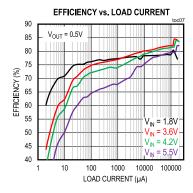

- 94% Peak Efficiency and Over 90% at 10µA

- Easy to Use-Addresses Popular Operation

- 1.8V to 5.5V Input Voltage Range

- 0.5V to 1.8V Output Voltage Range

- · Up to 175mA Output Current

- Protects System in Multiple Use Cases

- · Short-Circuit Protection

- · Internal Active Discharge

- Programmable Single Resistor (32 Settings)

- Four Output Voltage Levels for Each RSEL Setting Through Digitally Controlled VSEL1 and VSEL2 Pins

- EN Pin for Converter On/Off Control

- 100% Duty-Cycle Mode for Low Dropout Operation

- · Reduces Size and Increases Reliability

- -40°C to +125°C Operating Temperature Range

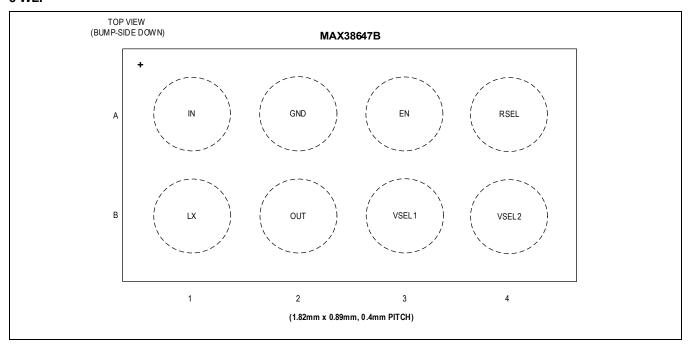

- 8-Bump WLP (1.82mm x 0.89mm, 0.4mm Pitch)

- 10-Pin TDFN (3mm x 3mm, 0.5mm Pitch)

# **Key Applications**

- Portable Space-Constrained Consumer Products

- Wearable Devices Ultra-Low-Power IoT, NB IoT, and Bluetooth® LE

- Single Li-ion and Coin-Cell Battery Products

- · Wired, Wireless Industrial Products

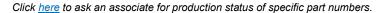

## **Simplified Application Circuit**

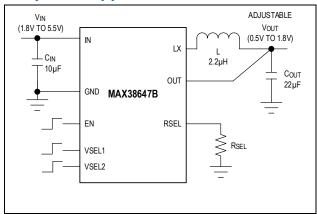

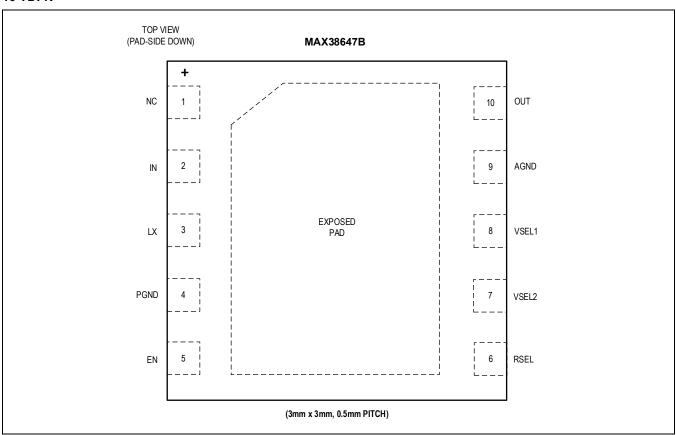

### **Pin Configurations**

#### 8 WLP

Bluetooth is a registered trademark of Bluetooth SIG, Inc.

Ordering Information appears at end of data sheet.

# **Absolute Maximum Ratings**

| VIN, VOUT, VSEL1, VSEL2, EN to GN                          | ND0.3V to +6V                  |

|------------------------------------------------------------|--------------------------------|

| RSEL to GND                                                | 0.3V to VIN + 0.3V             |

| LX RMS Current                                             | 1.6ARMS to +1.6ARMS            |

| LX to GND (Note 1)                                         | 0.3V to V <sub>IN</sub> + 0.3V |

| Continuous Power Dissipation (WLF 11.40mW/°C above +70°C ) |                                |

| Continuous Power Dissipation (TDFN, TA: 24.40mW/°C above +70°C) |                |

|-----------------------------------------------------------------|----------------|

| Operating Temperature Range                                     | 40°C to +125°C |

| Maximum Junction Temperature                                    | +150°C         |

| Storage Temperature Range                                       | 65°C to +150°C |

| Lead Temperature (Soldering, 10 seconds)                        | +300°C         |

| Soldering Temperature (reflow)                                  | +260°C         |

**Note 1:** The LX pin has internal clamps to GND and IN. These diodes may be forward biased during switching transitions. During these transitions, the max LX current should be within the maximum RMS current rating for safe operation.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **8 WLP**

| Package Code                                           | N80F1+1                        |

|--------------------------------------------------------|--------------------------------|

| Outline Number                                         | <u>21-100605</u>               |

| Land Pattern Number                                    | Refer to Application Note 1891 |

| THERMAL RESISTANCE, FOUR-LAYER BOARD:                  |                                |

| Junction-to-Ambient ( $\theta_{JA}$ )                  | 87.71°C/W                      |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | N/A                            |

#### **10 TDFN**

| Package Code                                           | T1033+1C       |

|--------------------------------------------------------|----------------|

| Outline Number                                         | <u>21-0137</u> |

| Land Pattern Number                                    | <u>90-0003</u> |

| THERMAL RESISTANCE, FOUR-LAYER BOARD:                  |                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 41°C/W         |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 9°C/W          |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermaltutorial">www.maximintegrated.com/thermaltutorial</a>.

### **Electrical Characteristics**

$(V_{IN} = 3.3V, V_{EN} = 3.3V, V_{OUT} = 1.8V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C, L = 2.2 \mu\text{H}, C_{OUT} = 22 \mu\text{F}, unless otherwise specified.}$

| PARAMETER                                     | SYMBOL                | COND                                                                            | ITIONS                                        | MIN  | TYP   | MAX  | UNITS |

|-----------------------------------------------|-----------------------|---------------------------------------------------------------------------------|-----------------------------------------------|------|-------|------|-------|

| Input Voltage Range                           | V <sub>IN</sub>       | Guaranteed by output                                                            | ut accuracy                                   | 1.8  |       | 5.5  | V     |

|                                               |                       | V <sub>IN</sub> rising V <sub>IN</sub> falling                                  |                                               |      | 1.75  | 1.8  |       |

| Input Voltage UVLO                            | V <sub>UVLO</sub>     |                                                                                 |                                               |      | 1.7   |      | V     |

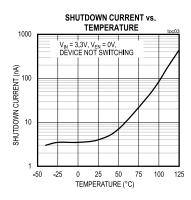

| Input Shutdown Current                        | I <sub>SD_IN</sub>    | V <sub>EN</sub> = 0V, T <sub>A</sub> = +25°                                     | С                                             |      | 0.005 | 0.1  | μA    |

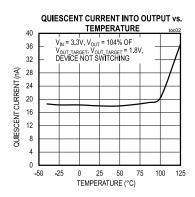

| Quiescent Supply                              |                       | V <sub>EN</sub> = V <sub>IN</sub> , not switch                                  | ning, V <sub>OUT</sub> = 104%                 |      | 4.40  |      |       |

| Current Into IN                               | I <sub>Q_IN</sub>     | of target voltage, TA                                                           | = +25°C                                       |      | 440   | 750  | nA    |

| Quiescent Supply                              | lo out                | V <sub>EN</sub> = V <sub>IN</sub> , not switch                                  | ning, V <sub>OUT</sub> = 104%                 |      | 17    |      | n 1   |

| Current Into OUT                              | IQ_OUT                | of target voltage, T <sub>A</sub>                                               | = +25°C                                       |      | 17    |      | nA    |

| Output Voltage Range                          | Vout                  | Guaranteed by output                                                            | ut accuracy                                   | 0.5  |       | 1.8  | V     |

| Output Accuracy                               | ACC                   | Vout falling when LX begins switching above 300kHz, VIN > Vout + 0.3V, (Note 3) | V <sub>OUT</sub> = 0.5V to<br>1.8V            | -1.5 |       | +1.5 | %     |

| Low-Power Mode Over-<br>Regulation Hysteresis | LPM_HYS               | Hysteresis measured as percent of target output voltage ( <i>Note 4</i> )       |                                               | +1.3 | +2.7  | +4   | %     |

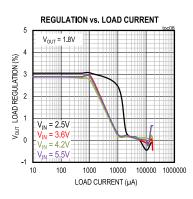

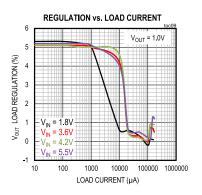

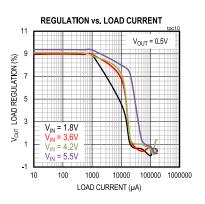

| DC Load Regulation                            | ACC <sub>LD_REG</sub> | I <sub>LOAD</sub> from 1mA to 8                                                 |                                               |      | ±2.5  |      | %     |

| Soft-Start Time                               | tss                   | V <sub>OUT</sub> = 1.8V, I <sub>OUT</sub> = 0mA                                 |                                               |      | 1     |      | ms    |

| Select-Resistor                               |                       |                                                                                 |                                               |      |       |      |       |

| Detection Time                                | t <sub>RSL</sub>      | C <sub>SEL</sub> < 2pF                                                          |                                               | 240  | 600   | 1320 | μs    |

| Required R <sub>SEL</sub> Resistor            | ACC <sub>RSEL</sub>   | Use nearest ±1% resistor from <i>Table 1</i>                                    |                                               | -1   |       | +1   | %     |

| Accuracy                                      | - KSEL                | Ose nearest ±1 /0 res                                                           | Ose flearest £1% fesistor from <u>Table 1</u> |      |       | ''   | 70    |

| Active Discharge<br>Resistor                  | R <sub>OUT_DIS</sub>  | V <sub>EN</sub> = 0V                                                            |                                               | 50   | 85    | 200  | Ω     |

| High-Side MOSFET Channel On Resistance        | R <sub>DS_H</sub>     | V <sub>IN</sub> = 3.3V                                                          |                                               |      | 320   | 600  | mΩ    |

| Low-Side MOSFET Channel On Resistance         | R <sub>DS_L</sub>     | V <sub>IN</sub> = 3.3V                                                          |                                               |      | 150   | 290  | mΩ    |

| LX Leakage Current                            | ILEAK_LX              | $V_{LX} = V_{OUT} = 5.5V,$<br>+25°C                                             | V <sub>EN</sub> = 0V, T <sub>A</sub> =        |      | 10    | 100  | nA    |

| Inductor Peak Current<br>Limit                | IPEAK_LX              | ( <u>Note 5</u> )                                                               |                                               | 0.2  | 0.25  | 0.3  | А     |

| Zero-Crossing Threshold                       | lzx_lx                | V <sub>OUT</sub> = 1.2V                                                         |                                               |      | 12.5  |      | mA    |

| EN Input Leakage<br>Current                   | ILEAK_EN              | V <sub>EN</sub> = 5.5V, T <sub>A</sub> = +25°C                                  |                                               |      | 1     | 100  | nA    |

| ENIX/:It Ti I                                 | VIH_EN                | V <sub>EN</sub> rising                                                          |                                               |      | 0.85  | 1.2  |       |

| EN Voltage Threshold                          | V <sub>IL_EN</sub>    | V <sub>EN</sub> falling                                                         |                                               | 0.4  | 0.725 |      | V     |

| VSEL Input Leakage<br>Current                 | ILEAK_VSEL            | Vvsel1, Vvsel2 = 5.5V, TA = +25°C                                               |                                               |      | 1     | 100  | nA    |

| VSEL Voltage                                  | VIH_VSEL              | Vvsel1, Vvsel2 risin                                                            | g                                             |      | 0.75  | 1.2  | ,,,   |

| Threshold                                     | VIL_VSEL              | Vysei 1. Vysei 2 fallir                                                         | VSEL1, VVSEL2 falling                         |      | 0.625 |      |       |

$(V_{IN} = 3.3V, V_{EN} = 3.3V, V_{OUT} = 1.8V, T_A = -40^{\circ}C$  to  $+125^{\circ}C, L = 2.2\mu H, C_{OUT} = 22\mu F$ , unless otherwise specified. (Note 2)

| PARAMETER                   | SYMBOL     | CONDITIONS                                                 | MIN | TYP | MAX | UNITS |

|-----------------------------|------------|------------------------------------------------------------|-----|-----|-----|-------|

| VSEL State Blanking<br>Time | tvsel_hold | V <sub>V</sub> SEL1, V <sub>V</sub> SEL2 high or low state | 1   | 2   | 6   | μs    |

| Thermal-Shutdown            | T          | T <sub>J</sub> rising when output turns off                |     | 165 |     | .0    |

| Threshold                   | Тѕнит      | T <sub>J</sub> falling when output turns on                |     | 150 | •   | °C    |

- **Note 2:** Limits over the specified operating temperature and supply voltage range are guaranteed by design and characterization, and production tested at room temperature only.

- Note 3: Output accuracy in low-power mode (LPM) does not include load, line, or ripple.

- **Note 4:** This LPM\_HYS percentage is only for 1.8V output voltage. For other output voltages, a typical value of 45mV can be considered as LPM\_HYS at +25°C.

- **Note 5:** This is a static measurement. The actual peak current limit depends upon V<sub>IN</sub>, V<sub>OUT</sub>, and the inductor due to propagation delays.

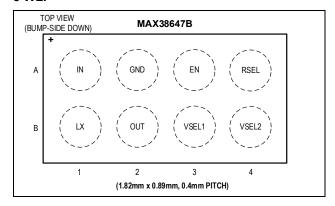

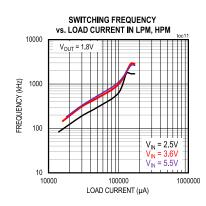

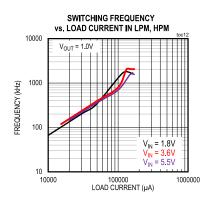

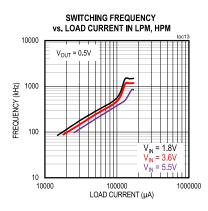

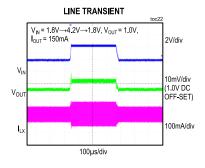

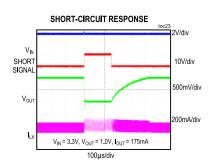

## **Typical Operating Characteristics**

$(MAX38647BANA+, V_{IN} = 3.6V, V_{OUT} = 1.8V, L = 2.2\mu H, C_{IN} = 10\mu F, C_{OUT} = 22\mu F, T_A = +25^{\circ}C, unless otherwise noted.)$

# **Pin Configurations (continued)**

#### **8 WLP**

#### **10 TDFN**

# **Pin Descriptions**

| PIN<br>MAX38647B MAX38647B<br>ANA+ ATB+ |    |       |                                                                                                                                                                               |

|-----------------------------------------|----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         |    | NAME  | FUNCTION                                                                                                                                                                      |

| _                                       | 1  | NC    | Not Connected. This pin is internally not connected. It can be left floating.                                                                                                 |

| A1                                      | 2  | IN    | Power Supply Input. Input supply range is from 1.8V to 5.5V. Bypass IN to GND with a minimum 10µF ceramic capacitor as close as possible to the device.                       |

| B1                                      | 3  | LX    | Switching Node. Connect an inductor between LX and the regulator output.                                                                                                      |

| _                                       | 4  | PGND  | Power Ground. Connect PGND to the power ground plane. Connect all the circuit ground connections together at a single point.                                                  |

| A2                                      | -  | GND   | Ground. Connect GND to the power ground plane. Connect all the circuit ground connections together at a single point.                                                         |

| A3                                      | 5  | EN    | Enable Input. Force this pin high to enable the buck converter. Force this pin low to disable the part and enter shutdown. Active discharge is enabled when EN is pulled low. |

| A4                                      | 6  | RSEL  | Output Voltage Select Input. Connect a resistor from RSEL to GND/AGND to program target output voltages.                                                                      |

| В3                                      | 8  | VSEL1 | Output Voltage Level Selection Input 1. The logic combinations shown in <u>Table 2</u> are used for selection of dynamic voltage levels.                                      |

| B4                                      | 7  | VSEL2 | Output Voltage Level Selection Input 2. The logic combinations shown in <u>Table 2</u> are used for selection of dynamic voltage levels.                                      |

| _                                       | 9  | AGND  | Analog Ground                                                                                                                                                                 |

| B2                                      | 10 | OUT   | Output Voltage Sense Input. Connect to the load at a point where accurate regulation (output capacitor) is required to eliminate resistive metal drops.                       |

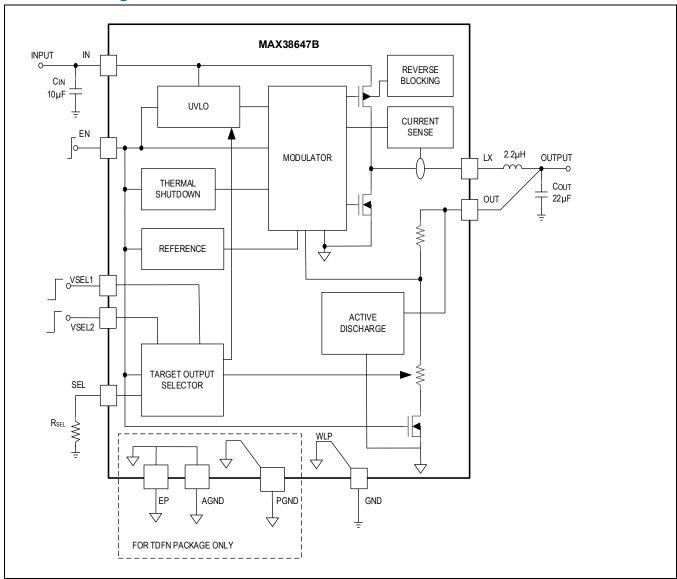

## **Functional Diagram**

### **Detailed Description**

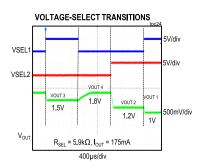

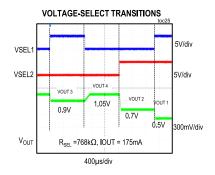

The MAX38647B is an ultra-low  $I_Q$  (440nA) buck converter that steps-down an input voltage range of 1.8V to 5.5V to a wide range of output voltages from 0.5V to 1.8V. Through a single external resistor ( $R_{SEL}$ ) on the RSEL pin, it is possible to program four different output voltages as given in <u>Table 1</u>. The output voltage can be changed dynamically between the selected four output voltages using two voltage select pins VSEL1 and VSEL2 by pulling them high or low. The four output voltages are determined during start-up. The output voltage transition from low voltage to high voltage is open-loop current-limit controlled. The voltage transition from high voltage to low voltage is purely dependent on the load.

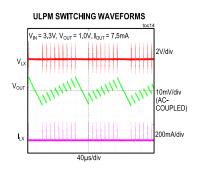

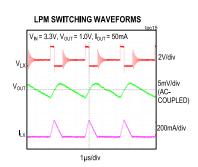

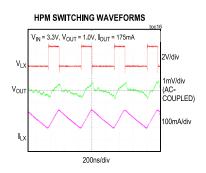

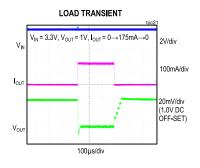

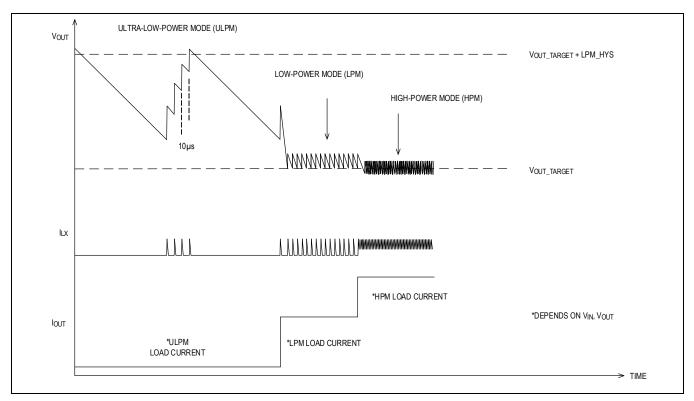

The buck converter automatically switches between ultra-low-power mode (ULPM), low-power mode (LPM) and high-power mode (HPM) to service the load at the highest possible efficiency depending on the load current. The buck converter overregulates in ULPM to allow the output capacitor to prevent output undershoot during load transients. See *Figure 1* for the MAX38647B mode transitions. The device supports 100% duty-cycle operation.

The active discharge resistor pulls OUT to ground when the part is in shutdown. In applications where the ambient temperature is more than +85°C, a load current of >10µA may be required to prevent the output from soaring due to power FET leakage.

Figure 1. MAX38647B Mode Transitions

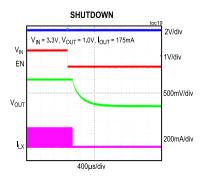

#### **Enabling the Device**

When  $V_{IN}$  is above the UVLO rising threshold and the EN pin is pulled high ( $V_{EN} > V_{IH\_EN}$ ), the part is enabled. There is a delay in reading the RSEL pin after which the soft-start circuit ramps the output voltage. When the EN pin is pulled low ( $V_{EN} < V_{IL\_EN}$ ), the MAX38647B shuts down. While in shutdown, 5nA (typ) of current is consumed from IN.

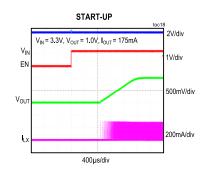

#### Start-Up

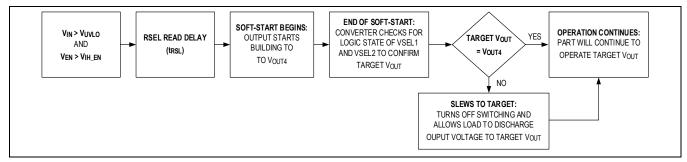

The MAX38647B has a built-in soft-start to avoid inrush current. It follows the sequence in Figure 2.

Figure 2. MAX38647B Start-Up Sequence

#### **Voltage Configuration**

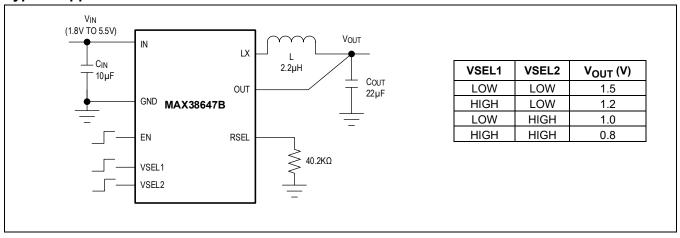

The MAX38647B includes an RSEL pin to configure the output voltages. For a given R<sub>SEL</sub> resistor, four output voltages are possible. The user needs to select the appropriate R<sub>SEL</sub> resistor value meeting their requirements from <u>Table 1</u>. Out of these four possible voltages, the steady-state target output is decided by the logic state of the VSEL pins given in <u>Table 2</u>. R<sub>SEL</sub> resistor with a tolerance of 1% (or better) should be chosen.

At start-up, the MAX38647B takes typically 600µs (t<sub>RSL</sub>) to read the R<sub>SEL</sub> value. Care must be taken that the total capacitance on this pin is less than 2pF. See the <u>PCB Layout Guidelines</u> for more information.

The RSEL output voltage selection method has many benefits:

- In conventional converters, current is drawn from the output continuously through a feedback resistor-divider. In the MAX38647B, 200µA of current is drawn only during startup, which helps to increase efficiency at light loads.

- The MAX38647B provides lower cost and smaller size, since only one resistor is needed versus two resistors in typical feedback connections. Moreover, only one resistor is needed to select all four voltages which are required for dynamic voltage change.

- The RSEL feature allows customers to stock just one part in their inventory system and use it in multiple projects with multiple combination of four different output voltages just by changing a single standard 1% resistor.

- The RSEL feature allows much higher internal feedback resistors instead of lower impedance external feedback resistors, thus enabling ultra-low-power applications.

Table 1. MAX38647B R<sub>SEL</sub> Selection Table

| D (I-O)               | TARGET OUTPUT VOLTAGES (V) |                   |                   |                   |

|-----------------------|----------------------------|-------------------|-------------------|-------------------|

| R <sub>SEL</sub> (kΩ) | V <sub>OUT1</sub>          | V <sub>OUT2</sub> | V <sub>OUT3</sub> | V <sub>OUT4</sub> |

| OPEN                  | 0.5                        | 0.6               | 0.8               | 0.9               |

| 900                   | 0.5                        | 0.7               | 0.8               | 1.0               |

| 768                   | 0.5                        | 0.7               | 0.9               | 1.05              |

| 634                   | 0.55                       | 0.65              | 0.8               | 0.9               |

| 536                   | 0.55                       | 0.7               | 0.9               | 1.0               |

| 452                   | 0.6                        | 0.7               | 0.8               | 0.9               |

| 383                   | 0.6                        | 0.75              | 0.9               | 1.05              |

| 324                   | 0.6                        | 0.8               | 0.95              | 1.1               |

| 267                   | 0.6                        | 0.8               | 1.0               | 1.2               |

| 226                   | 0.65                       | 0.8               | 0.9               | 1.05              |

| 191                   | 0.65                       | 0.8               | 1.0               | 1.2               |

| 162                   | 0.7                        | 0.75              | 0.8               | 0.9               |

| 133                   | 0.7                        | 0.8               | 0.9               | 1.0               |

| 113                   | 0.7                        | 0.8               | 0.95              | 1.1               |

| 95.3                  | 0.7                        | 0.85              | 0.9               | 1.2               |

| 80.6                  | 0.75                       | 0.8               | 0.9               | 1.0               |

| 66.5                  | 0.75                       | 0.85              | 1.0               | 1.2               |

| 56.2                  | 0.8                        | 0.85              | 0.9               | 1.0               |

| 47.5                  | 0.8                        | 0.9               | 1.05              | 1.2               |

| 40.2                  | 0.8                        | 1.0               | 1.2               | 1.5               |

| 34                    | 0.8                        | 1.2               | 1.5               | 1.8               |

| 28                    | 0.85                       | 1.0               | 1.1               | 1.2               |

| 23.7 | 0.85 | 1.05 | 1.2 | 1.5 |

|------|------|------|-----|-----|

| 20   | 0.9  | 1.0  | 1.1 | 1.2 |

| 16.9 | 0.9  | 1.0  | 1.2 | 1.5 |

| 14   | 0.9  | 1.2  | 1.5 | 1.8 |

| 11.8 | 0.95 | 1.0  | 1.1 | 1.2 |

| 10   | 0.95 | 1.1  | 1.2 | 1.5 |

| 8.45 | 1.0  | 1.1  | 1.2 | 1.5 |

| 7.15 | 1.0  | 1.2  | 1.4 | 1.5 |

| 5.9  | 1.0  | 1.2  | 1.5 | 1.8 |

| 4.99 | 1.05 | 1.2  | 1.4 | 1.5 |

#### **Short-Circuit Protection**

The MAX38647B has inbuilt protection against output short circuit by limiting the peak inductor current to avoid device damage. Once the fault (short circuit) is removed, the output recovers to the target output decided by the R<sub>SEL</sub> resistor and the logic state of the VSEL1 and VSEL2 pins. The input voltage does not need to be recycled for the output to recover after removal of the fault (short circuit) condition.

#### 100% Duty-Cycle Operation

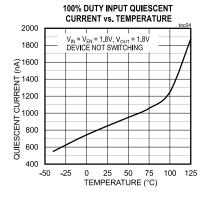

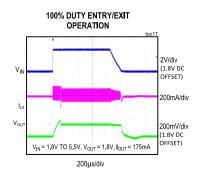

The MAX38647B features 100% duty-cycle operation. When the input voltage approaches the output voltage, the MAX38647B stops switching and enters 100% duty-cycle operation. In this mode, the part connects the output to input through the high-side power switch and the inductor. When the input voltage is increased again where it pulls VOUT to 5% above its target level, the converter exits 100% mode. At no load, the device consumes only 850nA (typ) of current in 100% duty-cycle mode while still protecting the inductor current from exceeding current limit.

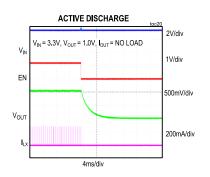

#### **Active Discharge**

The MAX38647B integrates a discharge resistor from the OUT pin to GND. This discharge resistor gets activated when the converter is disabled, which helps discharge the output capacitor quickly. The typical value of the discharge resistance is  $85\Omega$ .

#### **Dynamic Voltage Transition Using VSEL Pins**

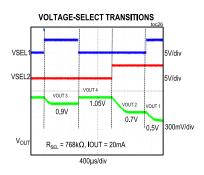

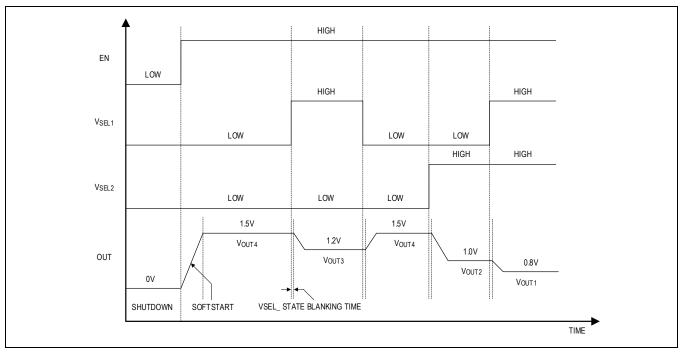

The MAX38647B has the ability to change voltage dynamically using two voltage-select pins. Based on the logic states of the voltage-select pins, one out of four possible output voltages can be selected. The states of the VSEL1 and VSEL2 pins and the corresponding output voltages,  $V_{OUT4}$  to  $V_{OUT4}$ , are given in <u>Table 2</u>. The typical operating waveforms of the dynamic voltage transitions for a given RSEL are shown in <u>Figure 3</u>.

Table 2. Output Voltage Selection Based on VSEL1 and VSEL2 Logic State

| VSEL1 | VSEL2 | OUTPUT VOLTAGES                     |

|-------|-------|-------------------------------------|

| Low   | Low   | V <sub>OUT4</sub> of <u>Table 1</u> |

| High  | Low   | V <sub>OUT3</sub> of <u>Table 1</u> |

| Low   | High  | V <sub>OUT2</sub> of <u>Table 1</u> |

| High  | High  | V <sub>OUT1</sub> of <u>Table 1</u> |

## **Applications Information**

#### **Typical Application Circuit**

Figure 3. MAX38647B Buck Converter Using Four Dynamic Voltages

Figure 4. MAX38647B Application Waveform with Output Voltage Transitions ( $R_{SEL}$  = 40.2k $\Omega$ )

#### Inductor Selection

The inductor value (L) for the MAX38647B affects the ripple current, the transition point from ULPM to LPM, and overall efficiency performance. It is recommended to use an inductor value of  $2.2\mu H$ . The saturation current rating of the inductor must be high enough to ensure that saturation can occur only above the peak current limit  $I_{PEAK}$  (250mA typ).

#### Input-Capacitor Selection

The input capacitor  $(C_{IN})$  reduces the peak current drawn from battery or input power source and reduces the switching noise in the IC. The impedance of  $C_{IN}$  at the switching frequency should be very low. Ceramic capacitors are

recommended with their small size and low equivalent series resistance (ESR). For most applications, a  $10\mu$ F ceramic capacitor with X7R temperature characteristics is recommended. For operations where ambient temperature is less than +85°C, an X5R ceramic capacitor can be used.

#### **Output-Capacitor Selection**

The output capacitor ( $C_{OUT}$ ) is required to keep the output voltage ripple small and to ensure loop stability.  $C_{OUT}$  must have low impedance at the switching frequency. Ceramic capacitors are recommended due to their small size and low equivalent series resistance (ESR). Make sure the capacitor does not degrade its capacitance significantly over temperature and DC bias. For most applications, a  $22\mu F$  ceramic capacitor with X7R temperature characteristics is recommended. For operations where ambient is less than +85°C, an X5R ceramic capacitor can be used. For high-duty applications (duty  $\geq 0.9$ ), it is recommended that the output capacitance is increased to 2 x  $22\mu F$ .

#### **PCB Layout Guidelines**

Careful PCB layout is especially important in nanoPower DC-DC converters. Poor layout can affect the IC performance causing electromagnetic interference (EMI), electromagnetic compatibility (EMC) issues, ground bounce, voltage drops, etc. Poor layout can also affect regulation and stability.

A good layout is implemented using the following rules:

- Place the inductor, input capacitor, and output capacitor close to the IC using short traces and/or copper pours. These

components carry high switching currents and long traces that act like antennas. The input capacitor placement is the

most important element in the PCB layout and should be placed directly next to the IC. The inductor and output

capacitor placement are secondary to the input capacitor's placement but should remain close to the IC.

- The connection from the bottom plate of the input capacitor, the output capacitor, and the ground pin of the device must be extremely short.

- Similarly, the top plate of input capacitor connection to the IN pin of the device must also be short.

- Minimize the surface area used for LX since this is the switching node.

- Keep VSEL1 and VSEL2 traces away from the LX node if these pins are driven externally.

- Keep the main power path from IN, LX, OUT, and GND as tight and short as possible.

- Maximize the size of the ground metal on the component side to help with thermal dissipation. Use a ground plane

with several vias connecting to the component-side ground to further reduce noise interference on sensitive circuit

nodes

- The trace used for the RSEL signal should neither be too long nor should it produce a capacitance of more than 2pF.

It is also recommended to refer to the MAX38647B EV kit layout.

## **Ordering Information**

| PART NUMBER     | OUTPUT VOLTAGE<br>RANGE (V) | PIN-PACKAGE      | FEATURES                                       |

|-----------------|-----------------------------|------------------|------------------------------------------------|

| MAX38647BANA+T  | 0.5–1.8                     | 8-Bump WLP       | 175mA Output Current, ULPM, LPM, HPM Operation |

| MAX38647BATB+T* | 0.5–1.8                     | 10-Pin TDFN-EP** | 175mA Output Current, ULPM, LPM, HPM Operation |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

T = Tape-and-reel.

<sup>\*</sup>Future part—contact factory for availability.

<sup>\*\*</sup>EP = Exposed pad.

#### MAX38647B

Tiny, 1.8V to 5.5V Input, 440nA IQ, 175mA nanoPower Buck Converter with Four-Level VSEL

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|------------------|-----------------|------------------|

| 0                  | 1/23             | Initial release |                  |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

MAX38647BANA+ MAX38647BANA+T MAX38647BEVK#WLP