Click here to ask an associate for production status of specific part numbers.

# ±0.1°C Accurate, Ultra-Small, Low-Power I<sup>2</sup>C Digital Temperature Sensor

### **General Description**

The MAX30210 operates from 1.7V to 2.0V supply voltage, and is a low-power, high-accuracy digital temperature sensor with  $\pm 0.1^{\circ}$ C accuracy from  $+20^{\circ}$ C to  $+50^{\circ}$ C and  $\pm 0.15^{\circ}$ C accuracy from  $-20^{\circ}$ C to  $+85^{\circ}$ C. The MAX30210 has a 16-bit resolution (0.005°C).

The device uses a standard I<sup>2</sup>C serial interface to communicate with a host controller. There are four functional I/Os. Those functions include a dedicated interrupt pin, a shared external convert and power-down functional pin, and two target address select pins.

The MAX30210 includes a 64-word FIFO for the temperature data and also includes high and low threshold digital temperature alarms along with FIFO full alert. The device is available in a 0.968mm x 0.968mm x 0.5mm, 9-pin WLP package.

### **Applications**

- Wearable Devices for Fitness, Wellness, and Medical Applications

- Medical Thermometers

- Hearing Aids

- Smart Clothing

### **Benefits and Features**

- High Accuracy and Precision

- ±0.1°C Accuracy from +20°C to +50°C

- ±0.15°C Accuracy from -20°C to +85°C

- Low-Power Consumption

- 1.7V to 2.0V Operating Voltage

- 61µA Operating Current during Measurement

- 0.75µA Standby Current

- 10nA Power-Down Current

- · 8ms Integration Time

- · Safety and Compliance

- · High and Low Temperature Alarms

- Digital Interface

- Shared External Convert Temperature and Power-Down Input Pin

- Dedicated Interrupt Output Pin

- · Autonomous Conversion Mode

- 16 Different I<sup>2</sup>C Target Address Options

- 48-Bit Unique ROM IDs Allow Device to be NIST Traceable

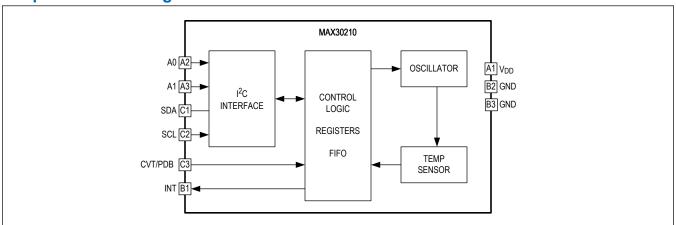

### Simplified Block Diagram

Ordering Information appears at end of data sheet.

19-101474; Rev 0; 12/22

### **TABLE OF CONTENTS**

| General Description                               | . 1 |

|---------------------------------------------------|-----|

| Applications                                      | . 1 |

| Benefits and Features                             | . 1 |

| Simplified Block Diagram                          | . 1 |

| Absolute Maximum Ratings                          | . 6 |

| Package Information                               | . 6 |

| 9-Pin WLP                                         | . 6 |

| Electrical Characteristics                        | . 6 |

| Typical Operating Characteristics                 | . 9 |

| Pin Configuration                                 | 10  |

| MAX30210                                          | 10  |

| Pin Description                                   | 10  |

| Functional Diagrams                               | 11  |

| Diagram 1                                         | 11  |

| Detailed Description                              | 12  |

| Measuring Temperature                             | 12  |

| External Convert Pin/Power-Down Input             | 13  |

| Autonomous Conversion Mode                        | 13  |

| MCU Interrupt Modes                               | 14  |

| High/Low Alarm                                    | 14  |

| Interrupt Mode                                    | 15  |

| Comparator Mode                                   | 16  |

| Rate-of-Change Alarm                              | 17  |

| Start-Up Timing                                   | 19  |

| FIFO Description                                  | 21  |

| FIFO Data Format                                  | 21  |

| FIFO Configuration Registers                      | 22  |

| FIFO_WR_PTR (address 0x04), Write Pointer         |     |

| FIFO_RD_PTR (address 0x05), Read Pointer          |     |

| OVF_COUNTER (address 0x06), Overflow Counter      | 22  |

| FIFO_DATA_COUNT (address 0x07), FIFO Data Counter | 22  |

| FIFO DATA (address 0x08), FIFO Data               | 22  |

| FIFO_A_FULL (address 0x09), FIFO Almost Full      | 22  |

| FIFO_RO (address 0x0A), FIFO Rollover             | 23  |

| A_FULL_TYPE (address 0x0A),Almost Full Type       |     |

| FIFO_STAT_CLR (address 0x0A), FIFO Status Clear   |     |

| FLUSH_FIFO (address 0x0A)                         |     |

| Serial Interface                                  |     |

| I <sup>2</sup> C Target Address                   |     |

|                                                   |     |

# TABLE OF CONTENTS (CONTINUED)

| I <sup>2</sup> C/SMBus Compatible Serial Interface                                | 24 |

|-----------------------------------------------------------------------------------|----|

| Detailed I <sup>2</sup> C Timing Diagram                                          | 24 |

| Bit Transfer                                                                      | 24 |

| START and STOP Conditions                                                         | 24 |

| Acknowledge Bit                                                                   | 25 |

| I <sup>2</sup> C Write Data Format                                                | 25 |

| I <sup>2</sup> C Read Data Format                                                 | 26 |

| Register Map                                                                      | 28 |

| User Register Map                                                                 | 28 |

| Register Details                                                                  | 29 |

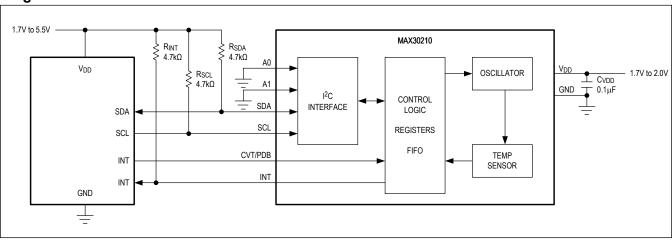

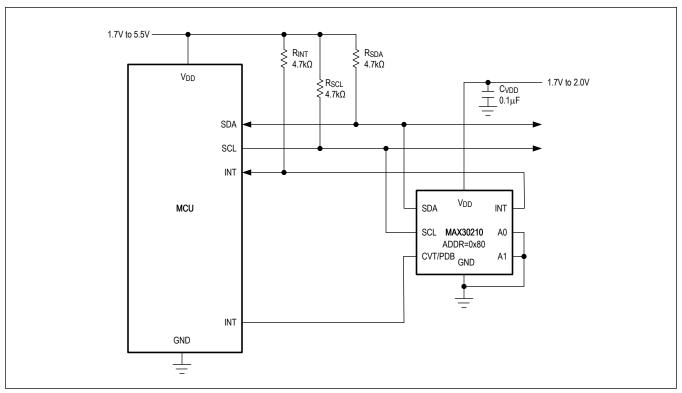

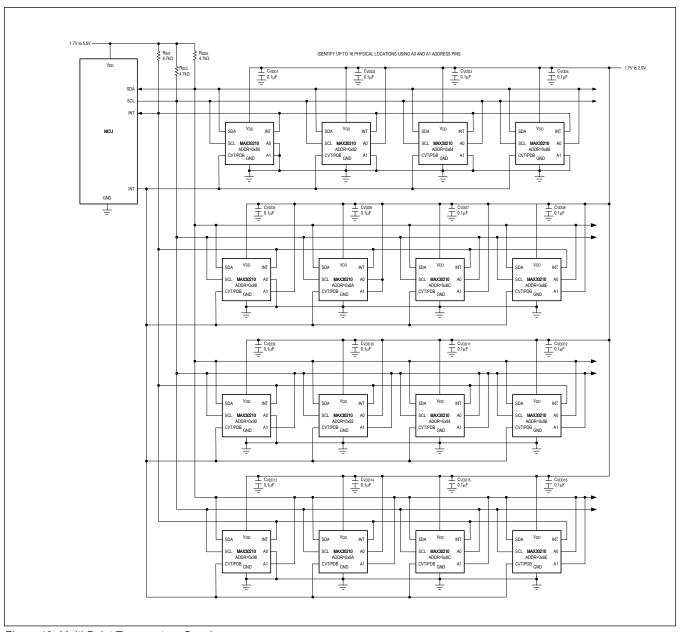

| Typical Application Circuits                                                      | 45 |

| MAX30210 Single-Point Temperature Sensing                                         | 45 |

| MAX30210 Multi-Point Temperature Sensing with up to 16 I <sup>2</sup> C Addresses | 46 |

| Ordering Information                                                              | 47 |

| Revision History                                                                  | 48 |

### LIST OF FIGURES

| Figure 1. Conversion Sample Period                                                  | 13 |

|-------------------------------------------------------------------------------------|----|

| Figure 2. High/Low Alarm Threshold Register Format                                  | 15 |

| Figure 3. Interrupt Mode Timing Diagram                                             | 16 |

| Figure 4. Comparator Mode Timing Diagram                                            | 17 |

| Figure 5. Rate-of-Change Filter Applied to Temperature Measurements                 | 18 |

| Figure 6. Power-Up Timing                                                           | 20 |

| Figure 7. Autonomous Conversion Mode                                                | 20 |

| Figure 8. Single-Shot Conversion Mode - through I <sup>2</sup> C                    | 20 |

| Figure 9. Single-Shot Conversion Mode - through CVT                                 | 21 |

| Figure 10. CVT Pulse Width Timing                                                   | 21 |

| Figure 11. Detailed I <sup>2</sup> C Timing Diagram                                 | 24 |

| Figure 12. I <sup>2</sup> C Start (S), Stop (P), and Repeated Start (Sr) Conditions | 25 |

| Figure 13. I <sup>2</sup> C Acknowledge Bit                                         | 25 |

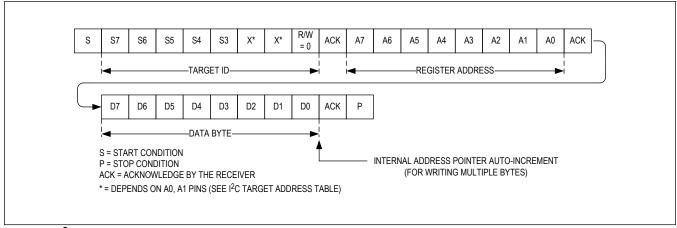

| Figure 14. I <sup>2</sup> C Single Byte Write Transaction                           | 26 |

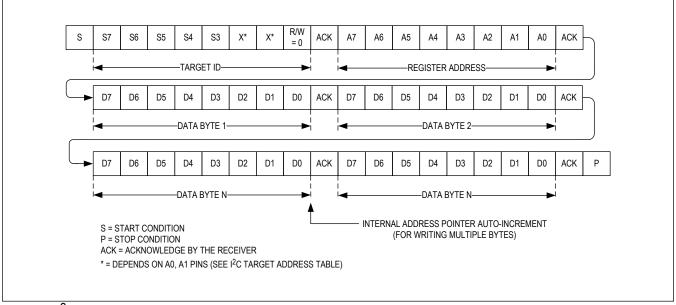

| Figure 15. I <sup>2</sup> C Multi-Byte Write Transaction                            | 26 |

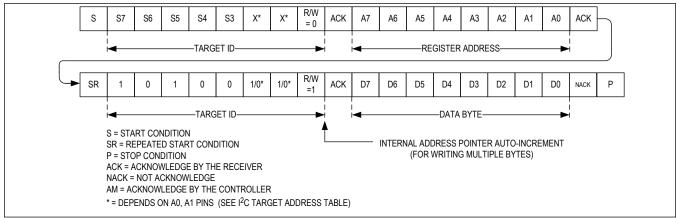

| Figure 16. I <sup>2</sup> C Single Byte Read Transaction                            | 27 |

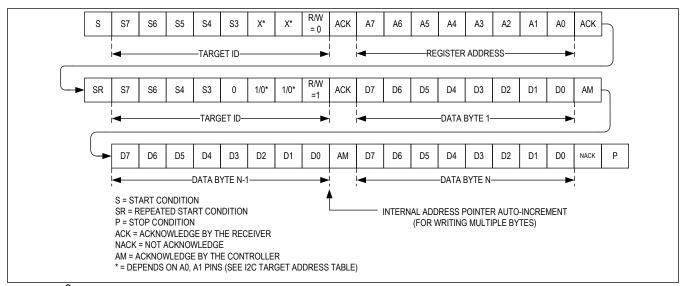

| Figure 17. I <sup>2</sup> C Multi-Byte Read Transaction                             | 27 |

| Figure 18. Single-Point Temperature Sensing                                         |    |

| Figure 19. Multi-Point Temperature Sensing                                          | 46 |

| LIST OF TABLES                                    |    |

|---------------------------------------------------|----|

| Table 1. FIFO Data Format                         | 12 |

| Table 2. CVT/PDB Pin Function                     | 13 |

| Table 3. Temperature Sample Rate                  | 14 |

| Table 4. Rate-of-Change Alarm Mode                | 18 |

| Table 5. Rate-of-Change Filter Settings           | 18 |

| Table 6. Change in Temperature Threshold Settings | 19 |

| Table 7. Rate of Change Alarm Examples            | 19 |

| Table 8. FIFO Data and Tags                       | 21 |

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +2.2V                | Storage Temperature Range55°C to +150°C |

|----------------------------------------------------|-----------------------------------------|

| SDA, SCL, A0, A1, CVT/PDB, INT to GND0.3V to +6.0V | Lead Temperature (soldering, 10s)+260°C |

| Operating Temperature Range40°C to +85°C           | Soldering Temperature (reflow)+260°C    |

| Junction Temperature +150°C                        |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 9-Pin WLP

| Package Code                           | N90A0+1                                                                               |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------|--|--|--|

| Outline Number                         | <u>21-100600</u>                                                                      |  |  |  |

| Land Pattern Number                    | Refer to the Application Note 1891: Wafer-Level Packaging (WLP) and Its Applications. |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                                                                       |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 94°C/W                                                                                |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{DD} = 1.8V, T_A = 25^{\circ}C, min/max are from T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.)$  (Note 1)

| PARAMETER                                 | SYMBOL           | CONE                                  | DITIONS                                  | MIN   | TYP   | MAX   | UNITS          |

|-------------------------------------------|------------------|---------------------------------------|------------------------------------------|-------|-------|-------|----------------|

| TEMPERATURE SENSOI                        | R                |                                       |                                          |       |       |       |                |

| Temperature                               |                  | +20°C to +50°C                        | post reflow, 3 sigma                     | -0.1  |       | +0.1  | - °C           |

| Measurement Error                         |                  | -20°C to +85°C                        | post reflow, 3 sigma                     | -0.15 |       | +0.15 |                |

| Resolution                                |                  | 16-Bit                                |                                          |       | 0.005 |       | °C             |

| Repeatability                             |                  | V <sub>DD</sub> = 1.8V, 1sps, 1       | 20 samples                               |       | 0.008 |       | °C RMS         |

| Integration Time                          | t <sub>INT</sub> |                                       |                                          |       | 8     |       | ms             |

| Long-Term Stability                       |                  | Mounted, T <sub>A</sub> = 70°C, 0% RH |                                          |       | 0.015 |       | °C/<br>1000hrs |

| Supply Voltage                            | $V_{DD}$         |                                       |                                          | 1.7   | 1.8   | 2.0   | V              |

| DC Power-Supply<br>Rejection Ratio (PSRR) | PSRR             | T <sub>A</sub> = +25°C, 1.7V <        | T <sub>A</sub> = +25°C, 1.7V < VDD <2.0V |       | 0.015 |       | °C/V           |

| Operating Current                         |                  | During Conversion                     | V <sub>DD</sub> = 1.8V                   |       | 61    | 80    | μA             |

| Standby Current (Note 2a)                 |                  | $V_{DD} = 1.8V, T_A = +2$             | 25°C                                     |       | 0.75  | 1.5   |                |

|                                           |                  | V <sub>DD</sub> = 1.8V                |                                          |       |       | 3.0   | μA             |

| Power-Down Current                        |                  | $V_{DD} = 1.8V, T_A = +2$             | 25°C                                     |       | 0.01  | 0.15  |                |

| (Note 2b)                                 |                  | V <sub>DD</sub> = 1.8V                |                                          |       |       | 0.3   | μA             |

## **Electrical Characteristics (continued)**

$(V_{DD} = 1.8V, T_A = 25^{\circ}C, min/max are from T_A = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.)$  (Note 1)

| PARAMETER                                             | SYMBOL              | COND                                    | ITIONS                                                | MIN                       | TYP   | MAX   | UNITS |

|-------------------------------------------------------|---------------------|-----------------------------------------|-------------------------------------------------------|---------------------------|-------|-------|-------|

| Power-On Reset                                        |                     | Rising Edge                             | Rising Edge                                           |                           | 1.530 |       | V     |

| Threshold                                             |                     | Falling Edge                            |                                                       |                           | 1.465 |       | ]     |

| DIGITAL I/O CHARACTE                                  | RISTICS             |                                         |                                                       | •                         |       |       |       |

| Input Voltage High                                    | V <sub>IH</sub>     | SDA, SCL, A0, A1, a                     | and CVT/PDB pins                                      | 1.4                       |       |       | V     |

| Input Voltage Low                                     | $V_{IL}$            | SDA, SCL, A0, A1, a                     | and CVT/PDB pins                                      |                           |       | 0.4   | V     |

| Input Hysteresis                                      | V <sub>HYS</sub>    | SDA, SCL, A0, A1, a                     | and CVT/PDB pins                                      |                           | 200   |       | mV    |

| Input Leakage Current                                 | I <sub>IN</sub>     | SDA, SCL, A0, A1, and CVT/PDB pins only | 0V < V <sub>IN</sub> < 5.5V,<br>T <sub>A</sub> = 25°C | - 0.1                     |       | + 0.1 | μA    |

| Input Capacitance                                     | C <sub>IN</sub>     | SDA, SCL, A0, A1, a                     | and CVT/PDB pins                                      |                           | 10    |       | pF    |

| Input Low-Pulse Width                                 |                     | CVT/PDB pin only                        |                                                       | 5                         |       |       | μs    |

| Output Voltage High                                   | V <sub>OH</sub>     | INT pin only                            | I <sub>SOURCE</sub> = 2mA                             | V <sub>DD</sub> -0.4      |       |       | V     |

| Output Voltage Low                                    | V <sub>OL</sub>     | INT pin only                            | I <sub>SINK</sub> = 2mA                               |                           |       | 0.4   | V     |

| Open-Drain Output Low<br>Voltage                      | V <sub>OL_OD</sub>  | SDA and INT pins only                   | I <sub>SINK</sub> = 6mA                               |                           |       | 0.4   | V     |

| I <sup>2</sup> C TIMING CHARACTER                     | RISTICS (Note 3     | B)                                      |                                                       |                           |       |       |       |

| Serial Clock Frequency                                | f <sub>SCL</sub>    |                                         |                                                       | 0                         |       | 400   | kHz   |

| Bus Free Time Between<br>STOP and START<br>Conditions | t <sub>BUF</sub>    |                                         |                                                       | 1.3                       |       |       | μs    |

| Hold Time START and<br>Repeat START<br>Condition      | t <sub>HD_STA</sub> |                                         |                                                       | 0.6                       |       |       | μѕ    |

| SCL Pulse-Width Low                                   | t <sub>LOW</sub>    |                                         |                                                       | 1.3                       |       |       | μs    |

| SCL Pulse-Width High                                  | t <sub>HIGH</sub>   |                                         |                                                       | 0.6                       |       |       | μs    |

| Setup Time for a<br>Repeated START<br>Condition       | tsu_sta             |                                         |                                                       | 0.6                       |       |       | μѕ    |

| Data Hold Time                                        | t <sub>HD_DAT</sub> |                                         |                                                       | 0                         |       | 900   | ns    |

| Data Setup Time                                       | t <sub>SU_DAT</sub> |                                         |                                                       | 100                       |       |       | ns    |

| Setup Time for STOP<br>Condition                      | tsu_sto             |                                         |                                                       | 0.6                       |       |       | μs    |

| Pulse Width of Sup-<br>pressed Spike                  | t <sub>SP</sub>     |                                         |                                                       |                           |       | 50    | ns    |

| Bus Capacitance                                       | C <sub>B</sub>      |                                         |                                                       |                           |       | 400   | pF    |

| SDA and SCL Receiving<br>Rise Time                    | t <sub>R</sub>      |                                         |                                                       | 20 +<br>0.1C <sub>B</sub> |       | 300   | ns    |

| SDA and SCL Receiving Fall Time                       | t <sub>F</sub>      |                                         |                                                       | 20 +<br>0.1C <sub>B</sub> |       | 300   | ns    |

### **Electrical Characteristics (continued)**

$(V_{DD}$  = 1.8V,  $T_A$  = 25°C, min/max are from  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Note 1)

| PARAMETER                  | SYMBOL          | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|----------------------------|-----------------|------------|---------------------------|-----|-----|-------|

| SDA Transmitting Fall Time | t <sub>TF</sub> |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

Note 1: All devices are 100% production tested at  $T_A$  = +25°C. Specifications over temperature limits are guaranteed by Maxim Integrated bench or proprietary automated test equipment (ATE) characterization.

Note 2: a) CVT/PDB = V<sub>DD</sub> and EXT\_CVT\_EN = 0 or EXT\_CVT\_EN = 1 and CVT/PDB = V<sub>DD</sub> or EXT\_CVT\_EN = 1 and CVT/PDB = GND b) CVT/PDB = GND and EXT\_CVT\_EN = 0

Note 3: Guaranteed by design and characterization. Not tested in production.

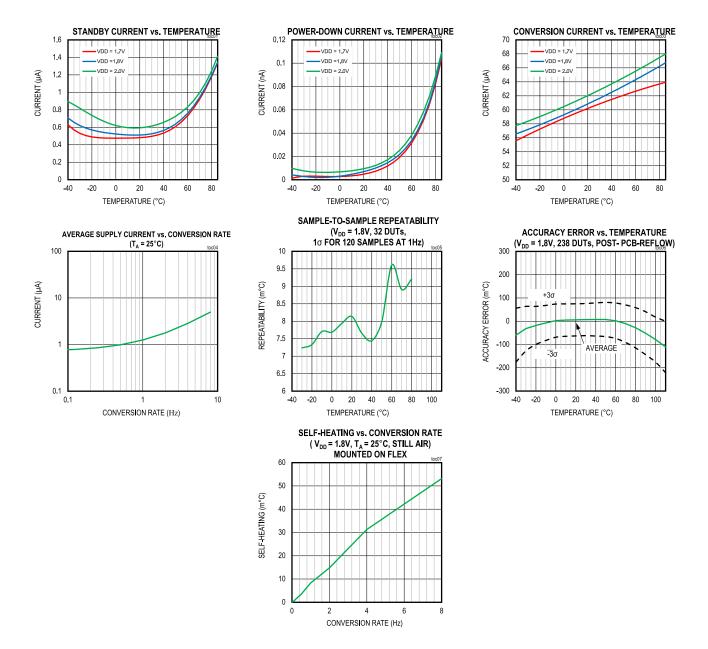

### **Typical Operating Characteristics**

$(V_{DD} = +1.8V, T_A = 25^{\circ}C, unless otherwise noted.)$

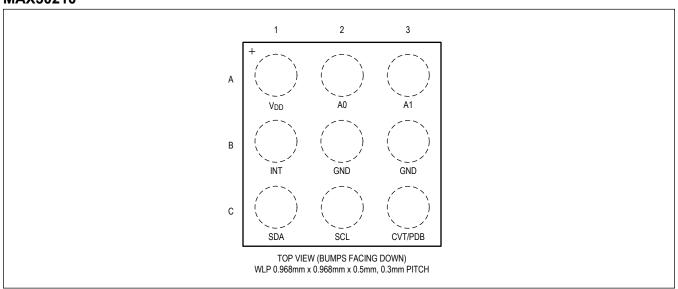

# **Pin Configuration**

### **MAX30210**

# **Pin Description**

| PIN                | NAME    | FUNCTION                                                                                            |

|--------------------|---------|-----------------------------------------------------------------------------------------------------|

| A1 V <sub>DD</sub> |         | +1.7V to +2.0V Power Supply. Bypass to GND with a 0.1µF capacitor as close to the bump as possible. |

| A2                 | A0      | Address select pin A0. Connect to GND, V <sub>DD</sub> , SDA, or SCL.                               |

| A3                 | A1      | Address select pin A1. Connect to GND, V <sub>DD</sub> , SDA, or SCL.                               |

| B1                 | INT     | Interrupt/Alert Output Pin.                                                                         |

| B2, B3             | GND     | Ground Reference.                                                                                   |

| C1                 | SDA     | I <sup>2</sup> C Data Input and Output.                                                             |

| C2                 | SCL     | I <sup>2</sup> C Clock.                                                                             |

| C3                 | CVT/PDB | Convert Input Pin/Power-Down Pin.                                                                   |

## **Functional Diagrams**

### Diagram 1

### **Detailed Description**

The MAX30210 temperature sensor measures temperature with ±0.1°C accuracy over a +20°C to +50°C temperature range and ±0.15°C accuracy over a -20°C to +85°C temperature range. The device communicates over a standard I<sup>2</sup>C interface with serial data (SDA) and serial clock (SCL) lines to read the FIFO, which contains up to 64, 2-byte temperature readings from a 16-bit ADC measurement. The device operates properly over a -40°C to +85°C temperature range without any damage. There are multiple ways to take a temperature measurement including single-shot mode, autonomous conversion mode, and using an external trigger through the CVT/PDB pin. In the autonomous conversion mode, the MAX30210 performs temperature conversions based on a programmable rate and stores the temperature result into the FIFO at the end of every active conversion. Once the data fills up the FIFO, the memory-mapped register contains a FIFO full alarm to be able to save all the data collected. The memory-mapped registers contain programmable high-alarm and low-alarm trigger registers as well. The Alarm High, Alarm Low, and Setup registers are volatile, and do not retain data when the device is powered down. The MAX30210 has four additional pins where three are of fixed function and the fourth is a shared functional pin. Two of the pins (A0, A1) are dedicated for the I2C target address which can be tied to V<sub>DD</sub>, SCL, SDA, and GND and provide up to 16 different I<sup>2</sup>C target address options. The final two pins are for interrupt (INT) and convert/power-down (CVT/PDB). The interrupt (INT) pin wakes up the microcontroller unit (MCU) during a qualified event and the convert/power-down (CVT/PDB) pin allows for either an external source to toggle the pin to start a conversion or power-down the part.

### **Measuring Temperature**

The device powers up in a low-power standby state. There are three different ways to initiate a temperature measurement:

- Controller writes a '1' to CONVERT T[0](0x2A) register.

- Falling/Rising edge trigger on CVT/PDB pin input (EXT\_CVT\_EN[7](0x12) = 1).

- Turn on autonomous conversion mode after setting up the registers.

In any of these methods, sampling should not exceed 20Hz to limit possible self-heating. Following the conversion, which takes 8ms (typ), the resulting temperature data is stored in the FIFO and the device returns to the standby state. CONVERT T automatically clears to '0' after the measurement is taken.

The output temperature data is calibrated in degrees Celsius. The temperature data is stored as a left-justified, 16-bit sign-extended two's complement number in the FIFO Data register (see <u>Table 1</u>). The data is two's complement where the most significant bit (MSB) determines the sign of the temperature with an MSB of 1 indicating a negative temperature and an MSB of 0 indicating a positive temperature.

To calculate the temperature from the measurement result, convert the two's complement value to the decimal value and use the following equation.

T = Decimal Value × 0.005

For example, if the result is 0x1CE8, convert to decimal to get 7400, then T = 7400 × 0.005 or  $37^{\circ}C$ . Table 1 gives examples of digital output data and the corresponding temperature reading.

Table 1. FIFO Data Format

| TEMPERATURE (°C) | DIGITAL OUTPUT (Binary) | DIGITAL OUTPUT (Hexadecimal) | DIGITAL OUTPUT (Decimal) |

|------------------|-------------------------|------------------------------|--------------------------|

| +70              | 0011 0110 1011 0000     | 36B0                         | 14000                    |

| +50              | 0010 0111 0001 0000     | 2710                         | 10000                    |

| +41              | 0010 0000 0000 1000     | 2008                         | 8200                     |

| +37              | 0001 1100 1110 1000     | 1CE8                         | 7400                     |

| +35.8            | 0001 1011 1111 1000     | 1BF8                         | 7160                     |

| +25              | 0001 0011 1000 1000     | 1388                         | 5000                     |

| +15              | 0000 1011 1011 1000     | 0BB8                         | 3000                     |

-10

-40

-200 -2000

-8000

|        | <b>\</b>            | •    |    |

|--------|---------------------|------|----|

| +0.04  | 0000 0000 0000 1000 | 0008 | 8  |

| +0.02  | 0000 0000 0000 0100 | 0004 | 4  |

| +0.01  | 0000 0000 0000 0010 | 0002 | 2  |

| +0.005 | 0000 0000 0000 0001 | 0001 | 1  |

| 0      | 0000 0000 0000 0000 | 0000 | 0  |

| -0.005 | 1111 1111 1111 1111 | FFFF | -1 |

FF38

F830

E0C0

**Table 1. FIFO Data Format (continued)**

### **External Convert Pin/Power-Down Input**

1111 1111 0011 1000

1111 1000 0011 0000

1110 0000 1100 0000

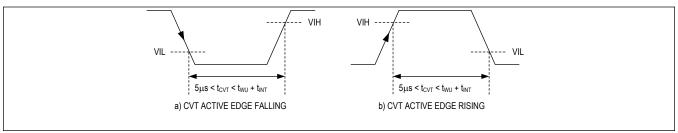

The MAX30210 features a pin that is used for both an external conversion input (CVT) and powering down (PDB) the part to reduce current in between temperature conversions. The CVT input offers the ability to trigger a conversion by either a rising or falling edge. There are more details of the timing in the <u>Start-Up Timing</u> section in <u>Figure 9</u> and <u>Figure 10</u>. To enable the CVT feature, set EXT\_CVT\_EN[7](0x12) = 1 and set the EXT\_CVT\_ICFG[6](0x12) bit to set the input active edge. The settings for both the CVT and the PDB features are listed in <u>Table 2</u>. Note, when PDB is brought high from Power Down to Power Up, all register contents restore to the power on reset values.

Table 2. CVT/PDB Pin Function

| EXT_CVT_EN | EXT_CVT_ICFG | CVT/PDB  | FUNCTION                                  |  |  |  |

|------------|--------------|----------|-------------------------------------------|--|--|--|

| 0          | X            | GND      | Power Down                                |  |  |  |

| 0          | X            | $V_{DD}$ | Power Up                                  |  |  |  |

| 1          | 0            | Pulse    | Power Up, CVT On, Falling Edge Conversion |  |  |  |

| 1          | 1            | Pulse    | Power Up, CVT On, Rising Edge Conversion  |  |  |  |

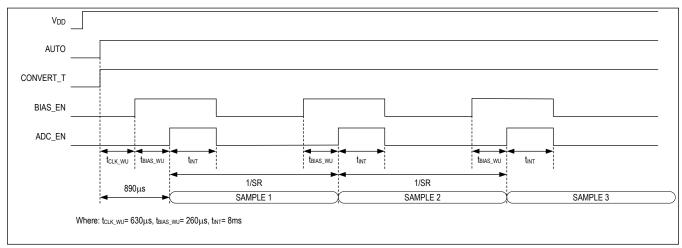

### **Autonomous Conversion Mode**

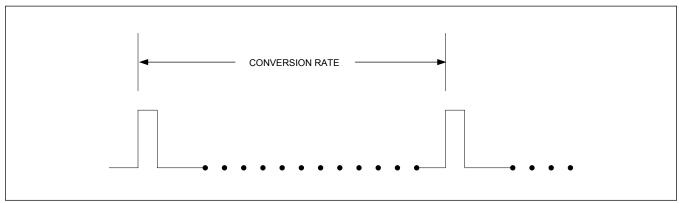

When the AUTO[1](0x2A) is set to 1, the MAX30210 operates in autonomous conversion mode. The MAX30210 continuously performs temperature conversions in this mode based on the TEMP\_PERIOD[3:0](0x29) settings and the resulting temperature measurement data is stored in the FIFO at the end of every active conversion. Every conversion cycle consists of an active conversion followed by a standby period. The device typically consumes 61µA during active conversion and 750nA in standby mode. Table 3 shares the corresponding bit settings and the sample rate.

Figure 1. Conversion Sample Period

**Table 3. Temperature Sample Rate**

| TEMP_PERIOD | SAMPLE RATE (Hz) | SAMPLE PERIOD (sec) |

|-------------|------------------|---------------------|

| 0x0         | 0.015625         | 64                  |

| 0x1         | 0.03125          | 32                  |

| 0x2         | 0.0625           | 16                  |

| 0x3         | 0.125            | 8                   |

| 0x4         | 0.25             | 4                   |

| 0x5         | 0.5              | 2                   |

| 0x6         | 1                | 1                   |

| 0x7         | 2                | 0.5                 |

| 0x8         | 4                | 0.25                |

| 0x9 to 0xF  | 8                | 0.125               |

### **MCU Interrupt Modes**

### **High/Low Alarm**

After the device performs a temperature conversion, the temperature value is compared with the user-defined two's complement alarm trigger values stored in the 2-byte ALARM\_HI[15:0](0x22, 0x23) and 2-byte ALARM\_LO[15:0](0x24,0x25) registers (see Figure 2). The default value for ALARM\_HI is 0x7FFF (+163.835°C) and the default value for ALARM\_LO is 0x8000 (-163.840°C). The MSB indicates if the value is positive or negative; for positive numbers the MSB is 0 and for negative numbers the MSB is 1. If the measured temperature is lower than ALARM\_LO or higher than ALARM\_HI, an alarm condition exists and corresponding status bit, TEMP\_LO[3](0x00) or TEMP\_HI[2](0x00) is set in the Status register. When the alarm condition is detected and the corresponding interrupt enable bit, TEMP\_LO\_EN[3](0x02) or TEMP\_HI\_EN[2](0x02) is set in the Interrupt Enable register and a hardware interrupt asserts on the INT pin, then the status bits, the alarm flag, and the hardware interrupt stay asserted until the Status register is read using the serial interface. The alarm flag only clears when STATUS is read. If the alarm flag is set and the next result does not trip the flag, then the flag remains set.

If the alarm settings change while the device is under an alarm condition, the alarm status must be cleared and another temperature conversion executed to update the alarm condition.

| ALARM HIGH THRESHOLD REGISTER FORMAT |                |                  |       |               |               |               |             |      |  |  |

|--------------------------------------|----------------|------------------|-------|---------------|---------------|---------------|-------------|------|--|--|

| _                                    | BIT15          | BIT14            | BIT13 | BIT12         | BIT11         | BIT10         | BIT9        | BIT8 |  |  |

| MSB                                  | AH15           | AH14             | AH13  | AH12          | AH11          | AH10          | AH9         | AH8  |  |  |

| _                                    | BIT7           | BIT6             | BIT5  | BIT4          | BIT3          | BIT2          | BIT1        | BIT0 |  |  |

| LSB                                  | AH7            | AH6              | AH5   | AH4           | AH3           | AH2           | AH1         | AH0  |  |  |

|                                      |                |                  |       |               |               |               |             |      |  |  |

| ALAR                                 | RM LOW THRESHO | LD REGISTER FORI | МАТ   |               |               |               |             |      |  |  |

| Г                                    | BIT15          | BIT14            | BIT13 | BIT12         | BIT11         | BIT10         | BIT9        | BIT8 |  |  |

| ALAR<br>MSB                          |                |                  |       | BIT12<br>AL12 | BIT11<br>AL11 | BIT10<br>AL10 | BIT9<br>AL9 | BIT8 |  |  |

| Г                                    | BIT15          | BIT14            | BIT13 |               |               |               |             |      |  |  |

Figure 2. High/Low Alarm Threshold Register Format

#### **Interrupt Mode**

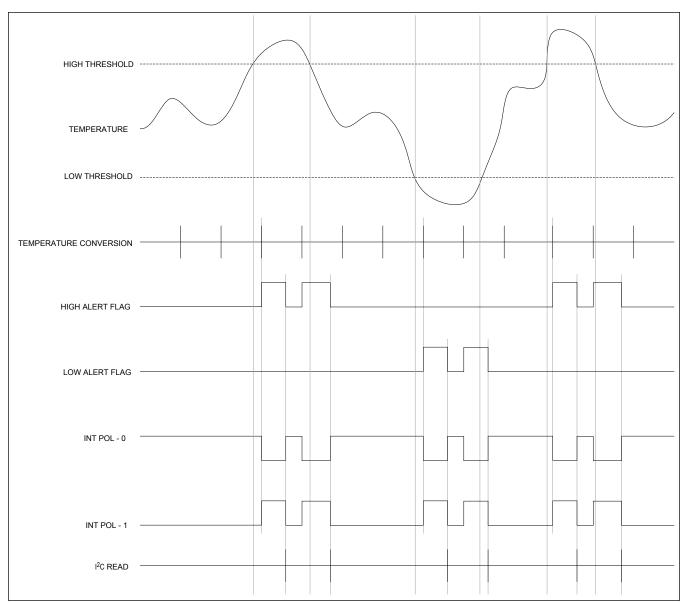

When the alert mode bit is set to 0 and autonomous conversion mode is enabled, the MAX30210 is set for interrupt mode alerts. In this mode, the MAX30210 sends an interrupt to the MCU when the temperature passes either the high temperature threshold or the low temperature threshold value. The alerts are cleared once the  $I^2C$  read occurs. Figure 3 shows how the mode works.

Figure 3. Interrupt Mode Timing Diagram

### **Comparator Mode**

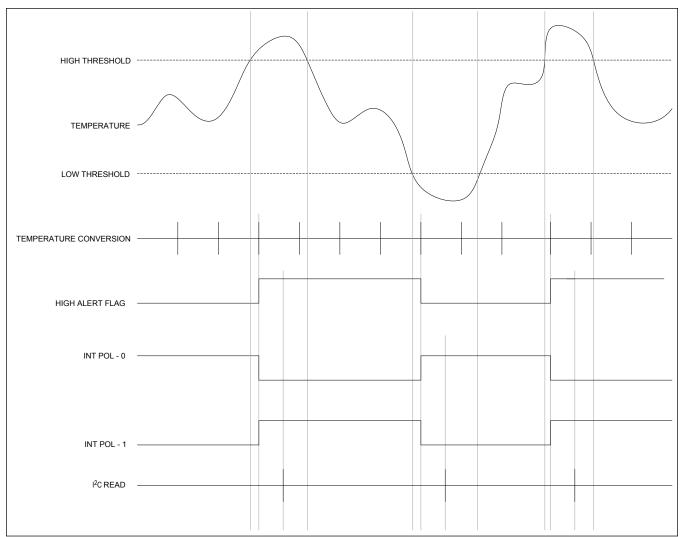

When the alert mode bit is set to 1 and autonomous conversion mode is enabled, the MAX30210 is set for comparator mode alerts. In this mode, the MAX30210 sends an interrupt to the MCU when the temperature is measured higher than the high temperature threshold. Both the high alert register and the interrupt pin stay asserted until the temperature falls below the set low temperature threshold value. The low alert flag is disabled and always read 0 in this mode. No alerts are cleared once the I<sup>2</sup>C read occurs. Figure 4 shows how the mode works.

Figure 4. Comparator Mode Timing Diagram

### Rate-of-Change Alarm

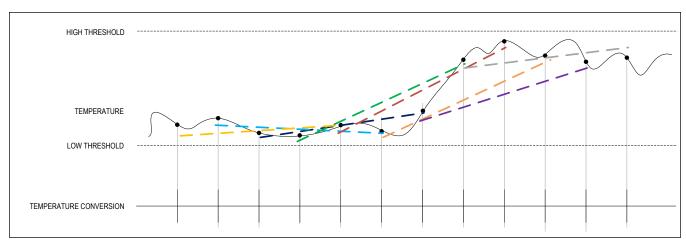

An on-chip filter, when enabled, measures the slope of the previous N samples, is available after N samples have been collected and then updated for each additional sample. In the following example, N is set to 5. If the slope exceeds the setting in TEMP\_INC\_THRESH[7:0](0x26), an interrupt is asserted. Likewise, if the slope is less than the setting in TEMP\_DEC\_THRESH[7:0](0x27), an interrupt is set. Figure 5 shows measured data with eight sequential slope measurements.

Figure 5. Rate-of-Change Filter Applied to Temperature Measurements

When autonomous mode is enabled (AUTO[1](0x2A) = 1) and CHG\_DET\_EN[3](0x28) is set to 1, the MAX30210 enables a rate-of-change mode. The mode is also enabled when CHG\_DET\_EN is set to 1 and EXT\_CVT\_EN[7](0x12) is set to 1. Table 4 summarizes how the mode is set.

**Table 4. Rate-of-Change Alarm Mode**

| AUTO | EXT_CVT_EN | CHG_DET_EN | RATE OF CHANGE MODE |

|------|------------|------------|---------------------|

| 0    | 0          | X          | Disabled            |

| X    | 1          | 0          | Disabled            |

| 1    | 0          | 0          | Disabled            |

| X    | 1          | 1          | Enabled             |

| 1    | 0          | 1          | Enabled             |

When the rate-of-change mode is enabled, the MAX30210 provides a slope value based on a set number of temperature measurement samples (m°C/Sample) and stores the 2's compliment value in the TEMP\_SLOPE[8:0](0x2D, 0x2E) registers. This value is compared to a user settable slope increase threshold TEMP\_INC\_THRESH[7:0](0x26) and the slope decrease threshold TEMP\_DEC\_THRESH[7:0](0x27). If the slope value is higher than the value in the TEMP\_INC\_THRESH, the TEMP\_INC\_FAST[4](0x00) bit is asserted. Likewise, if the slope value is lower than the value in the TEMP\_DEC\_THRESH, the TEMP\_DEC\_FAST[5](0x00) bit is asserted in the status register. There are interrupt options to send an interrupt to the INT pin if either the TEMP\_DEC\_FAST or the TEMP\_INC\_FAST bit is asserted by setting 1 to the TEMP\_DEC\_FAST\_EN[5](0x02) or TEMP\_INC\_FAST\_EN[4](0x02) bit, independently. One could choose to interrupt only on an increase slope threshold, a decrease slope threshold or choose to be interrupted by both. All interrupts and status bits are cleared upon I<sup>2</sup>C read.

These settings are dependent on the filter set in the RATE\_CHG\_FILTER[2:0](0x28) register. This register sets the length of the change in temperature FIR filter. The slope value is calculated based on the number of samples selected in this register and is stored in the TEMP\_SLOPE registers as described above. No slope value is stored until the number of samples in the RATE\_CHG\_FILTER register has been taken. The user needs to set the appropriate number of samples to fit the application needs.

**Table 5. Rate-of-Change Filter Settings**

| RATE_CHG_FILTER | TEMPERATURE SAMPLES |

|-----------------|---------------------|

| 0x0             | 2                   |

| 0x1             | 3                   |

| 0x2             | 5                   |

| 0x3             | 9                   |

**Table 5. Rate-of-Change Filter Settings (continued)**

| RATE_CHG_FILTER | TEMPERATURE SAMPLES |

|-----------------|---------------------|

| 0x4             | 17                  |

| 0x5             | 33                  |

| 0x6             | 65                  |

| 0x7             | 65                  |

The TEMP\_INC\_THRESH setting is based on a positive slope in units of  $5m^{\circ}C^{*}N/SAMPLE(S)$  where N = (0 to 255). Likewise, the TEMP\_DEC\_FAST\_THRESH setting is based on a negative slope in units of  $5m^{\circ}C^{*}N/SAMPLE(S)$  where N = (0 to 255).

### **Table 6. Change in Temperature Threshold Settings**

| VALUE | CHANGE IN TEMPERATURE/SAMPLE (m°C/SAMPLE) |

|-------|-------------------------------------------|

| 0x0   | 0                                         |

| 0x1   | 5                                         |

| 0x2   | 10                                        |

| 0x3   | 15                                        |

| 0x4   | 20                                        |

|       |                                           |

| 0xFF  | N*5 where N={0 to 255}                    |

To set the expected threshold, the slope needs to be set based on the configured sample rate. Here are some examples sharing how the calculation is completed.

## **Table 7. Rate of Change Alarm Examples**

| SAMPLE<br>RATE<br>(SPS) | TEMPERATURE<br>SAMPLES | CHANGE IN<br>TEMPERATURE/<br>SAMPLE<br>(m°C/sample) | CHANGE IN<br>TEMPERATURE<br>(m°C) | TIME<br>PERIOD<br>(SEC) | DESCRIPTION                                                    |

|-------------------------|------------------------|-----------------------------------------------------|-----------------------------------|-------------------------|----------------------------------------------------------------|

| 8                       | 9 [0x3]                | 5                                                   | 5*(9-1) = 40                      | (9-1)/8 = 1             | 40m°C slope increase threshold over a 1-second time period.    |

| 8                       | 65 [0x6, 0x7]          | 5                                                   | 5*(65-1) = 320                    | (65-1)/8 = 8            | 320m°C increase over an 8-second time period                   |

| 1                       | 5 [0x2]                | 50                                                  | 50*(5-1) = 200                    | (5-1)/1 = 4             | 200m°C slope increase threshold over a 4-second time period    |

| 1                       | 17 [0x4]               | 50                                                  | 50*(17-1) = 800                   | (17-1)/1 =<br>16        | 800m°C increase over a 16-second time period                   |

| 0.0625                  | 3 [0x1]                | 200                                                 | 200*(3-1) = 400                   | (3-1)/0.0625<br>= 32    | 400m°C slope increase threshold over a 48-second time period   |

| 0.0625                  | 9[0x3]                 | 200                                                 | 200*(9-1) = 1600                  | (9-1)/0.0625<br>= 128   | 1600m°C slope increase threshold over a 128-second time period |

### **Start-Up Timing**

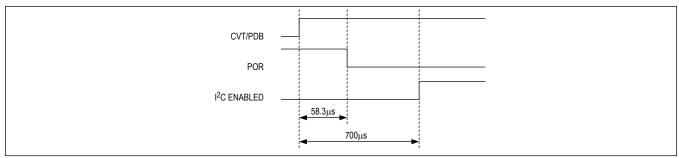

The start-up timing and delays for the MAX30210 are shown in the waveform below. Figure 6 shows the typical time taken for the MAX30210 to wake up and be ready for  $1^2$ C communication.

Figure 6. Power-Up Timing

Figure 7 shows the typical start-up delay when the MAX30210 is used in autonomous mode.

Figure 7. Autonomous Conversion Mode

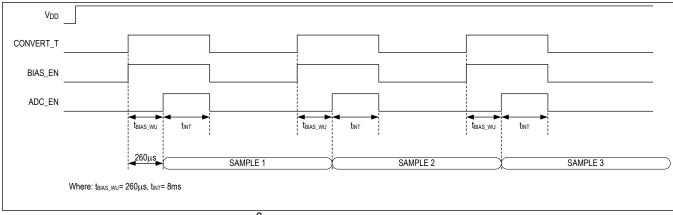

Figure 8 shows the typical start-up delay when the MAX30210 is used in single-shot mode initiated through I2C.

Figure 8. Single-Shot Conversion Mode - through I<sup>2</sup>C

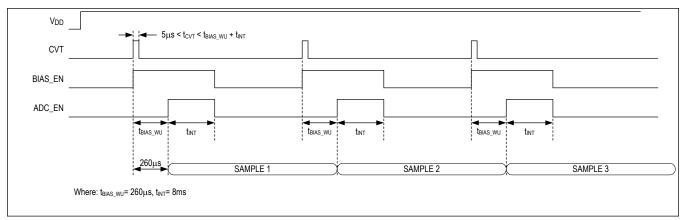

Figure 9 shows the typical start-up delay when the MAX30210 is used in single-shot mode initiated through the CVT pin.

Figure 9. Single-Shot Conversion Mode - through CVT

When using the CVT pin to initiate a conversion the pulse width of the CVT pin must meet the minimum requirements shown in Figure 10.

Figure 10. CVT Pulse Width Timing

### **FIFO Description**

### **FIFO Data Format**

The FIFO is 64 samples deep and is designed for 16-bit temperature data. The controller does a burst read of three bytes starting at register 0x08 to read one 16-bit temperature sample, referred to as a word, from the FIFO. The data read from the FIFO has an 8-bit tag and a 16-bit temperature data as shown in <u>Table 8</u>. The controller reads 3N bytes from the FIFO to get N samples.

When the rate change is too fast, a 9-bit temperature slope is saved in the FIFO along with the R[1:0] bits which indicate if the temperature rise or fall is too fast.

### **Table 8. FIFO Data and Tags**

|              | TAG | [23:1 | 16] |      |    |       |    |    | DAT | A[15     | :0]   |      |    |    |   |   |   |   |   |   |   |   |   |   |

|--------------|-----|-------|-----|------|----|-------|----|----|-----|----------|-------|------|----|----|---|---|---|---|---|---|---|---|---|---|

| Data Type    | 23  | 22    | 21  | 20   | 19 | 18    | 17 | 16 | 15  | 14       | 13    | 12   | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Reserved     | 0   | 0     | 0   | 0    | 0  | 0     | 0  | 0  | RES | RESERVED |       |      |    |    |   |   |   |   |   |   |   |   |   |   |

| Temperature  | 0   | C[1:  | 0]  | R[1: | 0] | T[1:0 | 0] | 1  | TEM | 1P_D/    | ATA[1 | 5:0] |    |    |   |   |   |   |   |   |   |   |   |   |

| Marker       | 1   | 1     | 1   | 1    | 1  | 1     | 1  | 1  | 1   | 1        | 1     | 1    | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| Invalid data | 1   | 1     | 1   | 1    | 1  | 1     | 1  | 1  | 1   | 1        | 1     | 1    | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| C[1:0] | Conversion Type |

|--------|-----------------|

| 00     | Internal Manual |

| 01     | Internal Auto   |

| 1x     |             | External                         |  |  |  |  |

|--------|-------------|----------------------------------|--|--|--|--|

| R[1:0] | Rate of Cha | nge of Temperature               |  |  |  |  |

| 0x     | Temperature | change is normal                 |  |  |  |  |

| 10     | Temperature | Temperature increase is too fast |  |  |  |  |

| 11     | Temperature | Temperature decrease is too fast |  |  |  |  |

| T[1:0] | Temperature | Data                             |  |  |  |  |

| 0x     | Temperature | is normal                        |  |  |  |  |

| 10     | Temperature | Temperature below low threshold  |  |  |  |  |

| 11     | Temperature | Temperature above high threshold |  |  |  |  |

### **FIFO Configuration Registers**

There are seven registers (address 0x04 to 0x0A) that control how the FIFO is configured and read out. Details of these registers are given as follows:

### FIFO\_WR\_PTR (address 0x04), Write Pointer

FIFO\_WR\_PTR[5:0] points to the FIFO location where the next word is written. This pointer advances for each word pushed on to the FIFO by the internal conversion process. The write pointer is updated from a 6-bit counter and wraps around to count 0x00 from count 0x3F.

### FIFO RD PTR (address 0x05), Read Pointer

FIFO\_RD\_PTR[5:0] points to the location where the next word of the FIFO is read using the I<sup>2</sup>C interface. This advances each time a word is read from the FIFO. The read pointer is updated from a 6-bit counter and wraps around to count 0x00 from count 0x3F.

### OVF\_COUNTER (address 0x06), Overflow Counter

OVF\_COUNTER[5:0] logs the number of words lost if new words are written after the FIFO is full. This counter saturates at count value 0x3F. Each time a complete word is popped from the FIFO, the OVF\_COUNTER is reset to zero. The counter is useful as a debug tool. It should be read immediately before reading the FIFO in order to check if an overflow condition has occurred.

### FIFO\_DATA\_COUNT (address 0x07), FIFO Data Counter

FIFO\_DATA\_COUNT[6:0] is a read-only register, which holds the number of words available in the FIFO for the controller to read. This increments when a new word is pushed to the FIFO, and decrements when the controller reads a word from the FIFO.

### FIFO\_DATA (address 0x08), FIFO Data

FIFO\_DATA[7:0] is a read-only register used to retrieve data from the FIFO. It is important to burst read the word from the FIFO. Each word is three bytes. Burst reading three bytes from the FIFO\_DATA register advances the FIFO\_RD\_PTR by one.

#### FIFO A FULL (address 0x09), FIFO Almost Full

The FIFO\_A\_FULL[5:0] register sets the watermark for the FIFO and determines when the A\_FULL[7](0x00) bit in the Status register is asserted. The A\_FULL bit is set when the FIFO contains 64 minus FIFO\_A\_FULL[5:0] words. For example, when FIFO\_A\_FULL is set to 2, the flag is set when the 62<sup>nd</sup> word is written to the FIFO. When the FIFO almost full condition is met, the A\_FULL bit is asserted in the Status register. If the A\_FULL\_EN[7](0x02) bit in the Interrupt Enable register is set and INT\_OCFG[1:0](0x12) and INT\_FCFG[3:2](0x12) are set in the Pin Configuration register, then the interrupt is asserted on the INT pin. This condition should prompt the applications processor to read samples from the FIFO before it fills.

The application processor reads the OVF\_COUNTER[5:0](0x06) and FIFO\_DATA\_COUNT[6:0](0x07) registers, to

determine how many data items are in the FIFO.

Alternatively, if the application always responds much faster than the selected sample rate, it could read 64 minus FIFO\_A\_FULL[5:0] number of data items every time it gets an A\_FULL interrupt and be assured that all data from the FIFO are read. This is the preferred way to minimize the traffic on the serial interface. FIFO\_WR\_PTR, FIFO\_RD\_PTR, FIFO\_DATA\_COUNT and OVF\_COUNTER registers are available for debug purposes, if needed.

### FIFO\_RO (address 0x0A), FIFO Rollover

The FIFO\_RO[1] bit in the FIFO Configuration 2 register determines whether a sample is pushed onto the FIFO or discarded when it is full. If FIFO\_RO is enabled when FIFO is full, old samples are overwritten. If FIFO\_RO is not set, the new sample is discarded and the FIFO is not updated.

### A\_FULL\_TYPE (address 0x0A),Almost Full Type

The A\_FULL\_TYPE[2] bit defines the behavior of the A\_FULL status bit. If the A\_FULL\_TYPE bit is set low, the A\_FULL[7](0x00) status bit is asserted when the A\_FULL condition is detected and cleared by a STATUS register read, then reasserts for every sample if the A\_FULL condition persists. If the A\_FULL\_TYPE bit is set high, the A\_FULL status bit is asserted only when a new A\_FULL condition is detected. The status bit is cleared by a STATUS register read and does not reassert for every sample until a new A\_FULL condition is detected.

### FIFO\_STAT\_CLR (address 0x0A), FIFO Status Clear

The FIFO\_STAT\_CLR[3] bit defines whether the A\_FULL[7](0x00) and TEMP\_RDY[6](0x00) status bits should clear by a FIFO\_DATA[7:0](0x08) register read. If FIFO\_STAT\_CLR is set low, A\_FULL and TEMP\_RDY status bits are not cleared by a FIFO\_DATA register read but are cleared by Status register read. If FIFO\_STAT\_CLR is set high, A\_FULL and TEMP\_RDY status bits are cleared by a FIFO\_DATA register read or a STATUS register read.

#### FLUSH\_FIFO (address 0x0A)

The FLUSH\_FIFO[4] bit is used for flushing the FIFO. The FIFO becomes empty and the FIFO\_WR\_PTR[5:0](0x04), FIFO\_RD\_PTR[5:0](0x05), FIFO\_DATA\_COUNT[6:0](0x07) and OVF\_COUNTER[5:0](0x06) are reset to zero. FLUSH FIFO is a self-clearing bit.

#### **Serial Interface**

### I<sup>2</sup>C Target Address

The device responds to its own I<sup>2</sup>C target address, which is selected using the A0 and A1 pins for the MAX30210. A0 and A1 can be connected to the supply voltage, ground, SDA, or SCL. This provides up to 16 unique addresses for the MAX30210 as shown in Table 9.

## Table 9. I<sup>2</sup>C Target Address

| A1                | A0              | ADDR |

|-------------------|-----------------|------|

| GND               | GND             | 0x80 |

| GND               | V <sub>DD</sub> | 0x82 |

| GND               | SCL             | 0x84 |

| GND               | SDA             | 0x86 |

| $V_{DD}$          | GND             | 0x88 |

| $V_{ m DD}$       | V <sub>DD</sub> | A8x0 |

| $V_{ m DD}$       | SCL             | 0x8C |

| $V_{\mathrm{DD}}$ | SDA             | 0x8E |

| SCL               | GND             | 0x90 |

| SCL               | V <sub>DD</sub> | 0x92 |

| SCL               | SCL             | 0x94 |

| SCL               | SDA             | 0x96 |

| Table 9. I <sup>2</sup> C Target Address (continued | <b>∠C Target Address (continued)</b> |

|-----------------------------------------------------|--------------------------------------|

|-----------------------------------------------------|--------------------------------------|

| A1  | A0       | ADDR |

|-----|----------|------|

| SDA | GND      | 0x98 |

| SDA | $V_{DD}$ | 0x9A |

| SDA | SCL      | 0x9C |

| SDA | SDA      | 0x9E |

### I<sup>2</sup>C/SMBus Compatible Serial Interface

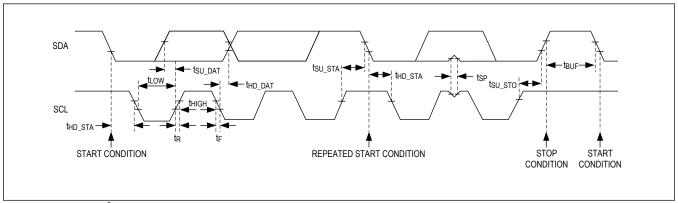

The MAX30210 features an I<sup>2</sup>C/SMBus-compatible, 2-wire serial interface consisting of an SDA and SCL. The SDA and SCL facilitate communication between the MAX30210 and the controller at clock rates up to 400kHz. Figure 11 shows the 2-wire interface timing diagram. The controller generates SCL and initiates data transfer on the bus. The controller device writes data to the MAX30210 by transmitting the proper target address followed by the register address and then the data word. Each transmit sequence is framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted to the MAX30210 is 8-bit long and is followed by an acknowledge clock pulse. A controller reading data from the MAX30210 transmits the proper target address followed by a series of nine SCL pulses. The MAX30210 transmits data on SDA in sync with the controller-generated SCL pulses. The controller acknowledges receipt of each byte of data. Each read sequence is framed by a START (S) or REPEATED START (Sr) condition, a not acknowledge, and a STOP (P) condition. The SDA operates as both an input and an open-drain output. A pullup resistor is required on SDA. The SCL operates only as an input. A pullup resistor is required on SCL if there are multiple controllers on the bus, or if the single controller has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX30210 from high voltage spikes on the bus lines and minimize crosstalk and undershoot of the bus signals.

### Detailed I<sup>2</sup>C Timing Diagram

The detailed timing diagram is shown in Figure 11.

Figure 11. Detailed I<sup>2</sup>C Timing Diagram

#### **Bit Transfer**

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section).

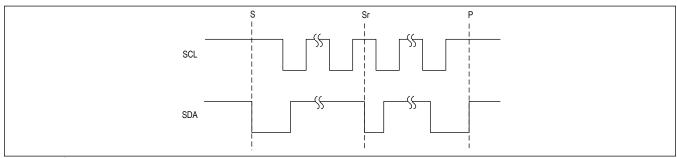

#### **START and STOP Conditions**

The SDA and SCL idle high when the bus is not in use. A controller initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 12). A START condition from the controller signals the beginning of a transmission to the MAX30210. The controller terminates transmission, and frees the bus, by issuing a STOP condition. The bus remains active if a REPEATED START condition is generated instead of a STOP condition.

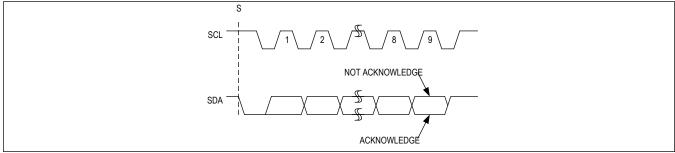

### **Acknowledge Bit**

The acknowledge bit (ACK) is a clocked 9th bit that the MAX30210 uses to handshake receipt of each byte of data when in write mode (Figure 13). The MAX30210 pulls down SDA during the entire controller-generated 9th clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus controller retries communication. The controller pulls down SDA during the 9th clock cycle to acknowledge receipt of data when the MAX30210 is in read mode. An acknowledge is sent by the controller after each read byte to allow data transfer to continue. A not acknowledge is sent when the controller reads the final byte of data from the MAX30210 followed by a STOP condition.

#### I<sup>2</sup>C Write Data Format

A write to the MAX30210 includes transmission of a START condition, the target address with the  $R/\overline{W}$  bit set to 0, one byte of data to configure the internal register address pointer, one or more bytes of data, and a STOP condition. Figure 14 illustrates the proper frame format for writing one byte of data to the MAX30210. Figure 15 illustrates the frame format for writing n-bytes of data to the MAX30210.

The controller first sends the target address with the R/W bit set to 0. This indicates that the controller intends to write data to the MAX30210. The MAX30210 acknowledges receipt of the address byte during the controller-generated 9th SCL pulse.

Figure 12. I<sup>2</sup>C Start (S), Stop (P), and Repeated Start (Sr) Conditions

Figure 13. I<sup>2</sup>C Acknowledge Bit

The second byte transmitted from the controller configures the MAX30210's internal register address pointer. The pointer tells the MAX30210 where to write the next byte of data. An acknowledge pulse is sent by the MAX30210 upon receipt of the address pointer data.

The third byte sent to the MAX30210 contains the data that is written to the chosen register. An acknowledge pulse from the MAX30210 signals receipt of the data byte. The address pointer auto increments to the next register address after each received data byte. This auto-increment feature allows a controller to write to sequential registers within one continuous frame. The controller signals the end of transmission by issuing a STOP condition. The auto-increment feature is disabled when there is an attempt to write to the FIFO DATA[7:0] (0x08) register.

#### I<sup>2</sup>C Read Data Format

The controller sends the target address with the  $R/\overline{W}$  bit set to 1 to initiate a read operation. The MAX30210 acknowledges receipt of its target address by pulling SDA low during the 9th SCL clock pulse. A START command followed by a read command resets the address pointer to register 0x00.

Figure 14. I<sup>2</sup>C Single Byte Write Transaction

Figure 15. I<sup>2</sup>C Multi-Byte Write Transaction

The first byte transmitted from the MAX30210 contains the data in register 0x00. Transmitted data is valid on the rising edge of SCL. The address pointer auto-increments after each read data byte. This auto-increment feature allows all registers to be read sequentially within one continuous frame. The auto-increment feature is disabled when there is an attempt to read from the FIFO\_DATA[7:0](0x08) register, and this allows for burst reading of the FIFO\_DATA register. A STOP condition can be issued after any number of read data bytes. If a STOP condition is issued followed by another read operation, the first data byte to be read is from register 0x00. The address pointer can be preset to a specific register before a read command is issued. The controller presets the address pointer by first sending the MAX30210 target address with the R/W bit set to 0 followed by the register address. A REPEATED START condition is then sent followed by the target address with the R/W bit set to 1. The MAX30210 then transmits the contents of the specified

register. The address pointer auto-increments after transmitting the first byte.

The controller acknowledges receipt of each read byte during the acknowledge clock pulse. The controller must acknowledge all correctly received bytes except the last byte. The final byte must be followed by a not acknowledge from the controller and then a STOP condition. Figure 16 illustrates the frame format for reading one byte from the MAX30210. Figure 17 illustrates the frame format for reading multiple bytes from the MAX30210.

Figure 16. I<sup>2</sup>C Single Byte Read Transaction

Figure 17. I<sup>2</sup>C Multi-Byte Read Transaction

# **Register Map**

### **User Register Map**

| ADDRESS        | NAME                          | MSB                                 |                            |                          |                          |                  |                |                   | LSB                      |  |

|----------------|-------------------------------|-------------------------------------|----------------------------|--------------------------|--------------------------|------------------|----------------|-------------------|--------------------------|--|

| Status         |                               |                                     |                            | l                        |                          |                  |                |                   |                          |  |

| 0x00           | Status[7:0]                   | A_FULL                              | TEMP_R<br>DY               | TEMP_D<br>EC_FAS<br>T    | TEMP_I<br>NC_FAS<br>T    | TEMP_L<br>O      | TEMP_H         | _                 | PWR_R<br>DY              |  |

| Interrupt Er   | nables                        |                                     |                            |                          |                          |                  | ı              |                   | l                        |  |

| 0x02           | Interrupt Enable[7:0]         | A_FULL<br>_EN                       | TEMP_R<br>DY_EN            | TEMP_D<br>EC_FAS<br>T_EN | TEMP_I<br>NC_FAS<br>T_EN | TEMP_L<br>O_EN   | TEMP_H<br>I_EN | _                 | _                        |  |

| FIFO           |                               |                                     |                            |                          |                          |                  |                |                   |                          |  |

| 0x04           | FIFO Write Pointer[7:0]       | _                                   | _                          |                          |                          | FIFO_WR          | _PTR[5:0]      |                   |                          |  |

| 0x05           | FIFO Read Pointer[7:0]        | _                                   | -                          |                          |                          | FIFO_RD          | _PTR[5:0]      |                   |                          |  |

| 0x06           | FIFO Counter 1[7:0]           | -                                   | _                          |                          |                          | OVF_COL          | INTER[5:0]     |                   |                          |  |

| 0x07           | FIFO Counter 2[7:0]           | -                                   |                            |                          | FIFO_I                   | DATA_COU         | NT[6:0]        |                   |                          |  |

| 0x08           | FIFO Data[7:0]                |                                     |                            |                          | FIFO_D                   | ATA[7:0]         |                |                   |                          |  |

| 0x09           | FIFO Configuration 1[7:0]     | FIFO_A_FULL[5:0]                    |                            |                          |                          |                  |                |                   |                          |  |

| 0x0A           | FIFO Configuration 2[7:0]     | _                                   | FLUSH_ FIFO_ST FIFO AT_CLR |                          |                          | A_FULL<br>_TYPE  | FIFO_R<br>O    | _                 |                          |  |

| SYSTEM CONTROL |                               |                                     |                            |                          |                          |                  |                |                   |                          |  |

| 0x11           | SYSTEM<br>CONFIGURATION[7:0]  | _                                   | _                          | _                        | _                        | _                | _              | _                 | RESET                    |  |

| 0x12           | PIN<br>CONFIGURATION[7:0]     | EXT_CV EXT_CV INT_FCFG[1:0] INT_OCF |                            |                          |                          | FG[1:0]          |                |                   |                          |  |

| TEMPERAT       | URE                           |                                     |                            |                          |                          |                  |                | •                 |                          |  |

| 0x20           | TEMP ALARM HIGH<br>SETUP[7:0] | TEMP_                               | HI_DET_CN                  | NTR[2:0]                 | _                        | TEMP_H<br>I_TRIP |                | _TRIP_CN<br>1:0]  | TEMP_R<br>ST_HI_C<br>NTR |  |

| 0x21           | TEMP ALARM LOW<br>SETUP[7:0]  | TEMP_I                              | _O_DET_C                   | NTR[2:0]                 | _                        | TEMP_L<br>O_TRIP |                | D_TRIP_C<br>[1:0] | TEMP_R<br>ST_LO_<br>CNTR |  |

| 0x22           | TEMP ALARM HIGH<br>MSB[7:0]   | ALARM_HI[15:8]                      |                            |                          |                          |                  |                |                   |                          |  |

| 0x23           | TEMP ALARM HIGH<br>LSB[7:0]   | ALARM_HI[7:0]                       |                            |                          |                          |                  |                |                   |                          |  |

| 0x24           | TEMP ALARM LOW<br>MSB[7:0]    | ALARM_LO[15:8]                      |                            |                          |                          |                  |                |                   |                          |  |

| 0x25           | TEMP ALARM LOW<br>LSB[7:0]    | ALARM_LO[7:0]                       |                            |                          |                          |                  |                |                   |                          |  |

| 0x26           | TEMP_INC_FAST_THR<br>ESH[7:0] |                                     |                            | Т                        | EMP_INC_                 | THRESH[7:        | 0]             |                   |                          |  |

| 0x27           | TEMP_DEC_FAST_TH<br>RESH[7:0] |                                     |                            | T                        | EMP_DEC_                 | THRESH[7:        | 0]             |                   |                          |  |

| ADDRESS    | NAME                            | MSB                      |   |   |         |            |                   |            | LSB           |

|------------|---------------------------------|--------------------------|---|---|---------|------------|-------------------|------------|---------------|

| 0x28       | TEMP<br>CONFIGURATION<br>1[7:0] | CHG_DE RATE_CHG_FILTER[2 |   |   |         | ER[2:0]    |                   |            |               |

| 0x29       | TEMP<br>CONFIGURATION<br>2[7:0] | ALERT_<br>MODE           | - | _ | _       |            | TEMP_PE           | ERIOD[3:0] |               |

| 0x2A       | TEMP CONVERT[7:0]               | ı                        | - | - | -       | -          | -                 | AUTO       | CONVE<br>RT_T |

| 0x2B       | TEMP DATA MSB[7:0]              | TEMP_DATA[15:8]          |   |   |         |            |                   |            |               |

| 0x2C       | TEMP DATA LSB[7:0]              | TEMP_DATA[7:0]           |   |   |         |            |                   |            |               |

| 0x2D       | TEMP SLOPE MSB[7:0]             |                          |   |   |         | _          | TEMP_S<br>LOPE[8] |            |               |

| 0x2E       | TEMP_SLOPE LSB[7:0]             |                          |   |   | TEMP_SI | LOPE[7:0]  |                   |            |               |

| UNIQUE ID  |                                 |                          |   |   |         |            |                   |            |               |

| 0x30       | UNIQUE ID1[7:0]                 |                          |   |   | UNIQUE_ | _ID_1[7:0] |                   |            |               |

| 0x31       | <u>UNIQUE ID2[7:0]</u>          |                          |   |   | UNIQUE_ | _ID_2[7:0] |                   |            |               |

| 0x32       | UNIQUE ID3[7:0]                 | UNIQUE_ID_3[7:0]         |   |   |         |            |                   |            |               |

| 0x33       | <u>UNIQUE ID4[7:0]</u>          | UNIQUE_ID_4[7:0]         |   |   |         |            |                   |            |               |

| 0x34       | UNIQUE ID5[7:0]                 | UNIQUE_ID_5[7:0]         |   |   |         |            |                   |            |               |

| 0x35       | UNIQUE ID6[7:0]                 | UNIQUE_ID_6[7:0]         |   |   |         |            |                   |            |               |

| IDENTIFIER | IDENTIFIERS                     |                          |   |   |         |            |                   |            |               |

| 0xFF       | PART IDENTIFIER[7:0]            |                          |   |   | PART_   | _ID[7:0]   |                   |            |               |

## **Register Details**

### Status (0x00)

| BIT            | 7         | 6         | 5                 | 4                 | 3         | 2         | 1 | 0         |

|----------------|-----------|-----------|-------------------|-------------------|-----------|-----------|---|-----------|

| Field          | A_FULL    | TEMP_RDY  | TEMP_DEC<br>_FAST | TEMP_INC<br>_FAST | TEMP_LO   | TEMP_HI   | _ | PWR_RDY   |

| Reset          | 0         | 0         | 0                 | 0                 | 0         | 0         | _ | 1         |

| Access<br>Type | Read Only | Read Only | Read Only         | Read Only         | Read Only | Read Only | - | Read Only |

| BITFIELD      | BITS | DESCRIPTION                                                                                                                                                                                                                                                                          |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A_FULL        | 7    | A_FULL is set to 1 when the FIFO has reached the threshold programmed in the FIFO_A_FULL[5:0](0x09). This is a read-only bit. This bit is cleared when the Status Register is read. It is also cleared when FIFO_DATA[7:0](0x08) register is read, if FIFO_STAT_CLR[3](0x0A) = 1.    |

| TEMP_RDY      | 6    | TEMP_RDY is asserted when a temperature sensor measurement has completed and new data is available to be read by the controller. This bit is cleared when the Status Register is read. It is also cleared when FIFO_DATA[7:0](0x08) register is read, if FIFO_STAT_CLR[3](0x0A) = 1. |

| TEMP_DEC_FAST | 5    | TEMP_DEC_FAST is asserted when the temperature decreases too fast. This is a read-only bit and it is cleared after the STATUS register is read.                                                                                                                                      |

| BITFIELD      | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEMP_INC_FAST | 4    | TEMP_INC_FAST is asserted when the temperature increases too fast. This is a read-only bit and it is cleared after the STATUS register is read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TEMP_LO       | 3    | TEMP_LO is asserted when the latest temperature sensor measurement is less than what is programmed in the Temperature Sensor Alarm Low (0x24,0x25) register. This is a read-only bit and it is cleared after the STATUS register is read.  TEMP_LO is not used when ALERT_MODE[7](0x29) is set for Comparator mode.                                                                                                                                                                                                                                                                                                                                                                                                     |

| TEMP_HI       | 2    | TEMP_HI is asserted when the latest temperature sensor measurement is greater than what is programmed in the Temperature Sensor Alarm High (0x22, 0x23) register. This is a read-only bit. When this bit is asserted and if the TEMP_HI_EN bit is set to 1 then it asserts the interrupt on the INT pin. The controller needs to read the status register to determine if the interrupt was asserted by the TEMP_HI status.  When ALERT_MODE[7](0x29) is set for Interrupt mode, TEMP_HI and the interrupt are cleared after the STATUS register is read. When ALERT_MODE is set for Comparator mode, TEMP_HI does not clear on STATUS register read, but the interrupt clears on STATUS register read. TEMP_HI remains |

|               |      | asserted until the latest temperature sensor measurement goes lower than what is programmed in the Temperature Sensor Alarm Low (0x24, 0x25) register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWR_RDY       | 0    | PWR_RDY is set to 1 when V <sub>DD</sub> goes below POR threshold, which is nominally 1.42V. If this condition occurs, all registers are reset to their POR state. This bit is not triggered by a soft reset. This is a read-only bit and it is cleared when the Status register is read.  PWR_RDY is a non-maskable interrupt, so it gets asserted on INT pin.                                                                                                                                                                                                                                                                                                                                                         |

### **Interrupt Enable (0x02)**

| BIT            | 7             | 6               | 5                    | 4                    | 3              | 2              | 1 | 0 |

|----------------|---------------|-----------------|----------------------|----------------------|----------------|----------------|---|---|

| Field          | A_FULL_E<br>N | TEMP_RDY<br>_EN | TEMP_DEC<br>_FAST_EN | TEMP_INC<br>_FAST_EN | TEMP_LO_<br>EN | TEMP_HI_<br>EN | _ | _ |

| Reset          | 0             | 0               | 0                    | 0                    | 0              | 0              | - | - |

| Access<br>Type | Write, Read   | Write, Read     | Write, Read          | Write, Read          | Write, Read    | Write, Read    | - | _ |

| BITFIELD         | BITS | DESCRIPTION                                                                   |

|------------------|------|-------------------------------------------------------------------------------|

| A_FULL_EN        | 7    | Enables A_FULL[7](0x00) status bit to be output to the INT output pin.        |

| TEMP_RDY_EN      | 6    | Enables TEMP_RDY[6](0x00) status bit to be output to the INT output pin.      |

| TEMP_DEC_FAST_EN | 5    | Enables TEMP_DEC_FAST[5](0x00)status bit to be output to the INT output pin.  |

| TEMP_INC_FAST_EN | 4    | Enables TEMP_INC_FAST[4](0x00) status bit to be output to the INT output pin. |

| BITFIELD   | BITS | DESCRIPTION                                                                                                                              |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------|