Click here to ask an associate for production status of specific part numbers.

# Ultra-Low Power, Single-Channel Integrated Biopotential (R-to-R Detection) AFE

**MAX30004**

### **General Description**

The MAX30004 is a complete, biopotential, analog frontend solution for wearable applications. It offers high performance for clinical and fitness applications, with ultra-low power for long battery life. The MAX30004 is a single biopotential channel providing heart rate detection.

The biopotential channel has ESD protection, EMI filtering, internal lead biasing, DC leads-off detection, ultra-low power leads-on detection during standby mode. Soft power-up sequencing ensures no large transients are injected into the electrodes. The biopotential channel also has high input impedance, low noise, high CMRR, programmable gain, various low-pass and high-pass filter options, and a high resolution analog-to-digital converter. The biopotential channel is DC coupled, can handle large electrode voltage offsets, and has a fast recovery mode to quickly recover from overdrive conditions, such as defibrillation and electrosurgery.

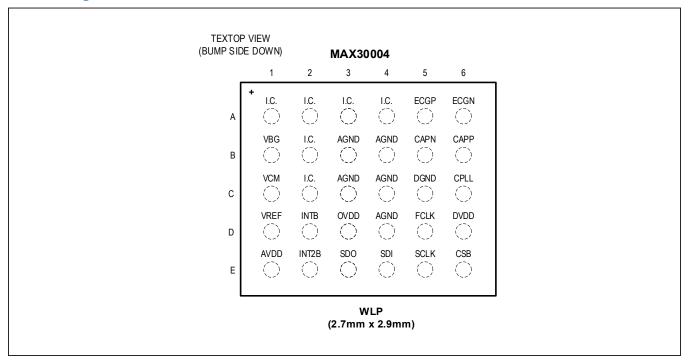

The MAX30004 is available in a 30-bump wafer-level package (WLP), operating over the 0°C to +70°C commercial temperature range.

### **Applications**

- Single Lead Wireless Patches for At-Home/ In-Hospital Monitoring

- Chest Band Heart Rate Monitors for Fitness Applications

Ordering Information appears at end of data sheet.

### **Benefits and Features**

- Heart Rate Detection with Interrupt Feature

Eliminates the Need to Extract and Process the ECG

Data on the Microcontroller

- Robust R-R Detection in High Motion Environment at Extremely Low Power

- Clinical-Grade Biopotential AFE with High-Resolution Data Converter

- 15.5 Bits Effective Resolution with 5µV<sub>P-P</sub> Noise

- Better Dry Starts Due to Much Improved Real World CMRR and High Input Impedance

- Fully Differential Input Structure with CMRR > 100dB

- Offers Better Common-Mode to Differential Mode Conversion Due to High Input Impedance

- High Input Impedance > 500MΩ for Extremely Low Common-to-Differential Mode Conversion

- Minimum Signal Attenuation at the Input During Dry Start Due to High Electrode Impedance

- High DC Offset Range of ±650mV (1.8V, typ) Allows to Be Used with Wide Variety of Electrodes

- High AC Dynamic Range of 65mV<sub>P-P</sub> Will Help the AFE Not Saturate in the Presence of Motion/Direct Electrode Hits

- Longer Battery Life Compared to Competing Solutions

85µW at 1.1V Supply Voltage

- Leads-On Interrupt Feature Keeps the μC in Deep Sleep Mode with RTC Off Until Valid Lead Condition is Detected

- Lead-On Detect Current: 0.7µA (typ)

- Configurable Interrupts Allows the μC Wake-Up Only on Every Heart Beat Reducing the Overall System Power

- High-Speed SPI Interface

- Shutdown Current of 0.5µA (typ)

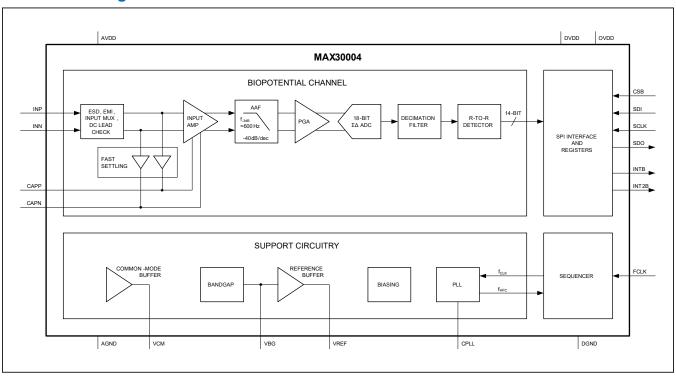

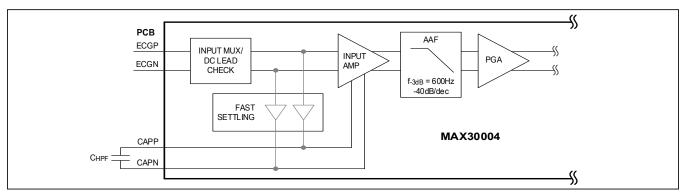

### **Functional Diagram**

### **Absolute Maximum Ratings**

| AV <sub>DD</sub> to AGND0.3V to +2.0V                       |

|-------------------------------------------------------------|

| DV <sub>DD</sub> to DGND0.3V to +2.0V                       |

| AV <sub>DD</sub> to DV <sub>DD</sub> 0.3V to +0.3V          |

| OV <sub>DD</sub> to DGND0.3V to +3.6V                       |

| AGND to DGND0.3V to +0.3V                                   |

| CSB, SCLK, SDI, FCLK to DGND0.3V to +3.6V                   |

| SDO, INTB, INT2B to                                         |

| DGND0.3V to the lower of (3.6V and $OV_{DD} + 0.3V$ )       |

| All other pins to                                           |

| AGND0.3V to the lower of (2.0V and AV <sub>DD</sub> + 0.3V) |

| Maximum Current into Any Pin±50mA                           |

| Continuous Power Dissipation ( $T_A = +70$ °C | )              |

|-----------------------------------------------|----------------|

| 30-Bump WLP (derate 24.3mW/°C                 |                |

| above +70°C)                                  | 1945.5mW       |

| Operating Temperature Range                   | 0°C to +70°C   |

| Junction Temperature                          | +150°C         |

| Storage Temperature Range                     | 65°C to +150°C |

| Lead Temperature (Soldering, 10sec)           | +300°C         |

| Soldering Temperature (reflow)                | +260°C         |

|                                               |                |

### **Package Thermal Characteristics (Note 1)**

WI P

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .......44°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, f_{FCLK} = 32.768 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, T_A = +25^{\circ}C.) \text{ (Note 2)}$

| PARAMETER                    | SYMBOL | CONDITIONS                                                                           |      | TYP   | MAX  | UNITS             |

|------------------------------|--------|--------------------------------------------------------------------------------------|------|-------|------|-------------------|

| BIOPOTENTIAL CHANNEL         |        |                                                                                      |      |       |      |                   |

| AC Differential Input Range  |        | V <sub>AVDD</sub> = +1.1V, THD < 0.3%                                                | -15  |       | +15  | m\/               |

| AC Differential input Natige |        | V <sub>AVDD</sub> = +1.8V, THD < 0.3%                                                |      | ±32.5 |      | mV <sub>p-p</sub> |

| DC Differential Input Range  |        | V <sub>AVDD</sub> = +1.1V, shift from nominal gain < 2%                              | -300 |       | +300 | mV                |

| DO Dillerential Input Nange  |        | V <sub>AVDD</sub> = +1.8V                                                            |      | ±650  |      | IIIV              |

| Common Mada Innut Danga      |        | V <sub>AVDD</sub> = +1.1V, from V <sub>MID</sub> , shift from nominal gain < 2%      | -150 |       | +150 | mV                |

| Common Mode Input Range      |        | V <sub>AVDD</sub> = +1.8V, from V <sub>MID</sub> , shift from nominal gain < 2% ±550 |      |       | IIIV |                   |

| Common Mode Rejection        | CMRR   | 0Ω source impedance, f = 64Hz (Note 3)                                               |      | 115   |      | dB                |

| Ratio                        | CIVIRR | With impedance mismatch (Note 4)                                                     |      | 77    |      | ub                |

|                              |        | BW = 0.05 - 150Hz, G <sub>CH</sub> = 20x                                             |      | 0.82  |      | μV <sub>RMS</sub> |

| Input Referred Naise         |        | BW - 0.03 - 130Hz, GCH - 20X                                                         |      | 5.4   |      | μV <sub>p-p</sub> |

| Input Referred Noise         |        | PW = 0.05 40Hz Co = 20v (Note 2)                                                     |      | 0.53  | 1.0  | μV <sub>RMS</sub> |

|                              |        | BW = 0.05 - 40Hz, G <sub>CH</sub> = 20x (Note 3)                                     |      | 3.5   | 6.6  | μV <sub>p-p</sub> |

| Input Leakage Current        |        | T <sub>A</sub> = +25°C                                                               | -1   | 0.1   | +1   | nA                |

| Input Impodance (INA)        |        | Common-mode, DC                                                                      |      | 45    |      | GΩ                |

| Input Impedance (INA)        |        | Differential, DC                                                                     |      | 1500  |      | МΩ                |

### **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, \ V_{OVDD} = +1.65V \text{ to } +3.6V, \ f_{FCLK} = 32.768kHz, \ T_A = T_{MIN} \text{ to } T_{MAX}, \ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, \ V_{OVDD} = +2.5V, \ T_A = +25^{\circ}C.) \ (Note 2)$

| PARAMETER                            | SYMBOL           | CONDITIONS                                                                            |                                                                                                                  | MIN  | TYP           | MAX  | UNITS       |

|--------------------------------------|------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|---------------|------|-------------|

| Tatal Harmania Diatartian            | THD              | F <sub>IN</sub> = 64Hz, G                                                             | $V_{AVDD}$ = +1.80V, $V_{IN}$ = 65m $V_{p-p}$ ,<br>$F_{IN}$ = 64Hz, $G_{CH}$ = 20x,<br>electrode offset = ±300mV |      |               |      | %           |

| Total Harmonic Distortion            | THU              | V <sub>AVDD</sub> = +1.1 <sup>v</sup><br>F <sub>IN</sub> = 64Hz, G<br>electrode offse |                                                                                                                  |      |               | 0.3  | 70          |

| Gain Setting                         | G <sub>CH</sub>  | Programmable                                                                          | e, see GAIN[1:0]                                                                                                 |      | 20 to<br>160  |      | V/V         |

| Gain Error                           |                  | V <sub>AVDD</sub> = +1.8°<br>INP = INN = V                                            |                                                                                                                  | -2.5 |               | +2.5 | %           |

| Gaill Elloi                          |                  | V <sub>AVDD</sub> = +1.1 <sup>v</sup><br>INP = INN = V                                |                                                                                                                  | -4.5 |               | +4.5 | %           |

| Offset Error                         |                  | (Note 5)                                                                              |                                                                                                                  |      | 0.1           |      | % of<br>FSR |

| ADC Resolution                       |                  |                                                                                       |                                                                                                                  |      | 18            |      | Bits        |

| ADC Sample Rate                      |                  | Programmable                                                                          | e, see RATE[1:0]                                                                                                 |      | 125 to<br>512 |      | SPS         |

| CAPP to CAPN Impedance               | R <sub>HPF</sub> | FHP = 1/(2Π x capacitance be                                                          | 320                                                                                                              | 450  | 600           | kΩ   |             |

|                                      |                  | Fast recovery                                                                         | Fast recovery enabled (1.8V)                                                                                     |      |               |      |             |

| Analog High-Pass Filter Slew Current |                  | Fast recovery                                                                         | Fast recovery enabled (1.1V)                                                                                     |      |               |      | μΑ          |

| Guirent                              |                  | Fast recovery                                                                         |                                                                                                                  | 0.09 |               |      |             |

| Fast Settling Recovery Time          |                  | C <sub>HPF</sub> = 10µF                                                               |                                                                                                                  |      | 500           |      | ms          |

|                                      |                  | Linear phase                                                                          | DLPF[0:1] = 01                                                                                                   |      | 40            |      |             |

| Digital Low Pass Filter              |                  | FIR filter,<br>ECG_RATE                                                               | DLPF[0:1] = 10                                                                                                   |      | 100           |      | Hz          |

|                                      |                  | = 00, 01                                                                              | DLPF[0:1] = 11                                                                                                   |      | 150           |      |             |

| Digital High Pass Filter             |                  | Phase-correcte                                                                        | ed 1st-order IIR filter. DHPF = 1                                                                                |      | 0.5           |      | Hz          |

| Power Supply Pajection               | PSRR             | Lead bias disa                                                                        | bled, DC                                                                                                         |      | 107           |      | dB          |

| Power Supply Rejection               | FOINI            | Lead bias disa                                                                        | bled, f = 64Hz                                                                                                   |      | 110           |      | чь          |

| INPUT MUX                            |                  |                                                                                       |                                                                                                                  |      |               |      |             |

|                                      |                  |                                                                                       | DCLOFF_IMAG[2:0] = 001                                                                                           |      | 5             |      |             |

|                                      |                  | Dullers /                                                                             | DCLOFF_IMAG[2:0] = 010                                                                                           |      | 10            |      |             |

| DC Lead Off Check                    |                  | Pullup/<br>pulldown                                                                   | DCLOFF_IMAG[2:0] = 011                                                                                           |      | 20            |      | nA          |

|                                      |                  | ·                                                                                     | DCLOFF_IMAG[2:0] = 100                                                                                           |      | 50            |      |             |

|                                      |                  |                                                                                       | DCLOFF_IMAG[2:0] = 101                                                                                           |      | 100           |      |             |

### **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, \ V_{OVDD} = +1.65V \text{ to } +3.6V, \ f_{FCLK} = 32.768kHz, \ T_A = T_{MIN} \text{ to } T_{MAX}, \ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, \ V_{OVDD} = +2.5V, \ T_A = +25^{\circ}C.) \ (Note 2)$

| PARAMETER                                          | SYMBOL            | CONDITIONS                    |                            | MIN                                              | TYP                         | MAX                        | UNITS  |     |

|----------------------------------------------------|-------------------|-------------------------------|----------------------------|--------------------------------------------------|-----------------------------|----------------------------|--------|-----|

|                                                    |                   | DCLOFF_VTH                    | DFF_VTH[1:0] = 11 (Note 6) |                                                  | V <sub>MID</sub> - 0.50     | )                          |        |     |

| DC Lead Off Comparator Low                         |                   | DCLOFF_VTH[1:0] = 10 (Note 7) |                            | DCLOFF_VTH[1:0] = 10 (Note 7) V <sub>MID</sub> - |                             | V <sub>MID</sub> - 0.45    | ;      | ] , |

| Threshold                                          |                   | DCLOFF_VTH                    | I[1:0] = 01 (Note 8)       | ,                                                | V <sub>MID</sub> - 0.40     | )                          | V      |     |

|                                                    |                   | DCLOFF_VTH                    | H[1:0] = 00                | ,                                                | V <sub>MID</sub> - 0.30     |                            |        |     |

|                                                    |                   | DCLOFF_VTH                    | I[1:0] = 11 (Note 6)       | \                                                | √ <sub>MID</sub> + 0.50     | )                          |        |     |

| DC Lead Off Comparator                             |                   | DCLOFF_VTH                    | I[1:0] = 10 (Note 7)       | \                                                | √ <sub>MID</sub> + 0.45     | 5                          | ,,     |     |

| High Threshold                                     |                   | DCLOFF_VTH                    | I[1:0] = 01 (Note 8)       | \                                                | √ <sub>MID</sub> + 0.40     | )                          | V      |     |

|                                                    |                   | DCLOFF_VTH                    | H[1:0] = 00                | \                                                | √ <sub>MID</sub> + 0.30     | )                          |        |     |

|                                                    |                   |                               | RBIASV[1:0] = 00           |                                                  | 50                          |                            |        |     |

| Lead Bias Impedance                                |                   | Lead bias enabled             | RBIASV[1:0] = 01           |                                                  | 100                         |                            | МΩ     |     |

|                                                    |                   | enabled                       | RBIASV[1:0] = 10           |                                                  | 200                         |                            |        |     |

| Lead Bias Voltage                                  | V <sub>MID</sub>  | Lead bias ena                 | bled                       |                                                  | V <sub>AVDD</sub> /<br>2.15 |                            | V      |     |

| INTERNAL REFERENCE/COM                             | IMON-MODE         |                               |                            |                                                  |                             |                            |        |     |

| V <sub>BG</sub> Output Voltage                     | V <sub>BG</sub>   |                               |                            |                                                  | 0.650                       |                            | V      |     |

| V <sub>BG</sub> Output Impedance                   |                   |                               |                            |                                                  | 100                         |                            | kΩ     |     |

| External V <sub>BG</sub> Compensation<br>Capacitor | C <sub>VBG</sub>  |                               |                            | 1                                                |                             |                            | μF     |     |

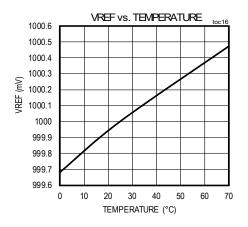

| V <sub>REF</sub> Output Voltage                    | V <sub>REF</sub>  | T <sub>A</sub> = +25°C        |                            | 0.995                                            | 1.000                       | 1.005                      | V      |     |

| V <sub>REF</sub> Temperature Coefficient           | TC <sub>REF</sub> | $T_A = 0$ °C to +7            | 70°C                       |                                                  | 10                          |                            | ppm/°C |     |

| V <sub>REF</sub> Buffer Line Regulation            |                   |                               |                            |                                                  | 330                         |                            | μV/V   |     |

| V <sub>REF</sub> Buffer Load<br>Regulation         |                   | I <sub>LOAD</sub> = 0 to 1    | 00μΑ                       |                                                  | 25                          |                            | μV/μΑ  |     |

| External V <sub>REF</sub> Compensation Capacitor   | C <sub>REF</sub>  |                               |                            | 1                                                | 10                          |                            | μF     |     |

| V <sub>CM</sub> Output Voltage                     | V <sub>CM</sub>   |                               |                            |                                                  | 0.650                       |                            | V      |     |

| External V <sub>CM</sub> Compensation<br>Capacitor | C <sub>CM</sub>   |                               |                            | 1                                                | 10                          |                            | μF     |     |

| DIGITAL INPUTS (SDI, SCLK,                         | CSB, FCLK)        | •                             |                            |                                                  |                             |                            |        |     |

| Input-Voltage High                                 | V <sub>IH</sub>   |                               |                            | 0.7 ×<br>V <sub>OVDD</sub>                       |                             |                            | V      |     |

| Input-Voltage Low                                  | V <sub>IL</sub>   |                               |                            |                                                  |                             | 0.3 ×<br>V <sub>OVDD</sub> | V      |     |

| Input Hysteresis                                   | V <sub>HYS</sub>  |                               |                            |                                                  | 0.05 ×<br>V <sub>OVDD</sub> |                            | V      |     |

### **Electrical Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, f_{FCLK} = 32.768 \text{kHz}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = +2.5V, T_A = +25^{\circ}C.) \text{ (Note 2)}$

| PARAMETER                      | SYMBOL                                   |                                                   | CONDITIONS                                         | MIN                       | TYP  | MAX | UNITS |

|--------------------------------|------------------------------------------|---------------------------------------------------|----------------------------------------------------|---------------------------|------|-----|-------|

| Input Capacitance              | C <sub>IN</sub>                          |                                                   |                                                    |                           | 10   |     | pF    |

| Input Current                  | I <sub>IN</sub>                          |                                                   |                                                    | -1                        |      | +1  | μA    |

| DIGITAL OUTPUTS (SDO, INT      | B, INT2B)                                |                                                   |                                                    | '                         |      |     |       |

| Output Voltage High            | V <sub>OH</sub>                          | I <sub>SOURCE</sub> = 1r                          | nA                                                 | V <sub>OVDD</sub><br>-0.4 |      |     | V     |

| Output Voltage Low             | V <sub>OL</sub>                          | I <sub>SINK</sub> = 1mA                           |                                                    |                           |      | 0.4 | V     |

| Three-State Leakage Current    |                                          |                                                   |                                                    | -1                        |      | +1  | μA    |

| Three-State Output Capacitance |                                          |                                                   |                                                    |                           | 15   |     | pF    |

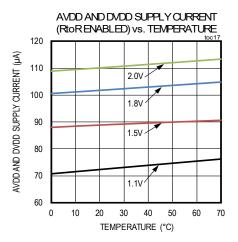

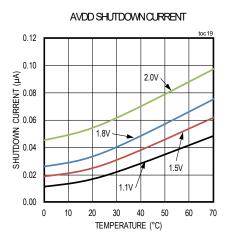

| POWER SUPPLY                   |                                          |                                                   |                                                    |                           |      |     |       |

| Analog Supply Voltage          | V <sub>AVDD</sub>                        | Connect V <sub>AVI</sub>                          | <sub>DD</sub> to V <sub>DVDD</sub>                 | 1.1                       |      | 2.0 | V     |

| Digital Supply Voltage         | V <sub>DVDD</sub>                        | Connect V <sub>DVI</sub>                          | DD to V <sub>AVDD</sub>                            | 1.1                       |      | 2.0 | V     |

| Interface Supply Voltage       | V <sub>OVDD</sub>                        | Power for I/O                                     | drivers only                                       | 1.65                      |      | 3.6 | V     |

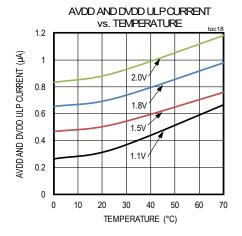

|                                |                                          |                                                   | V <sub>AVDD</sub> = V <sub>DVDD</sub> = +1.1V      |                           | 76   |     |       |

|                                |                                          | R-R<br>Operation                                  | V <sub>AVDD</sub> = V <sub>DVDD</sub> = +1.8V      |                           | 100  |     | μΑ    |

| Supply Current                 | I <sub>AVDD</sub> +<br>I <sub>DVDD</sub> |                                                   | V <sub>AVDD</sub> = V <sub>DVDD</sub> = +2.0V      |                           | 110  | 122 |       |

|                                |                                          | ULP Lead                                          | T <sub>A</sub> = +70°C                             |                           | 0.98 |     |       |

|                                |                                          | On Detect                                         | T <sub>A</sub> = +25°C                             |                           | 0.73 | 2.5 |       |

|                                |                                          | V <sub>OVDD</sub> = +1.6                          | V <sub>OVDD</sub> = +1.65V, ADC at 512sps (Note 9) |                           | 0.2  |     |       |

| Interface Supply Current       | lovdd                                    | V <sub>OVDD</sub> = +3.6V, ADC at 512sps (Note 9) |                                                    |                           | 0.6  | 1.6 | μΑ    |

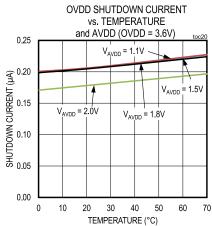

|                                | I <sub>SAVDD</sub> +                     | V <sub>AVDD</sub> =                               | T <sub>A</sub> = +70°C                             |                           | 0.79 |     |       |

| Shutdown Current               | I <sub>SDVDD</sub>                       | V <sub>DVDD</sub> = 2.0V                          | T <sub>A</sub> = +25°C                             |                           | 0.51 | 2.5 | μA    |

|                                | I <sub>SOVDD</sub>                       | V <sub>OVDD</sub> = +3.6                          |                                                    |                           | 1.1  |     |       |

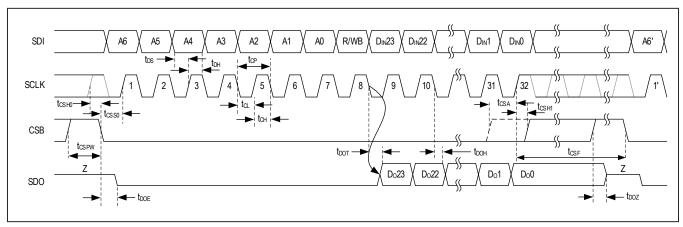

### **Timing Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, \ V_{OVDD} = +1.65V \text{ to } +3.6V, \ T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DVDD} = +1.8V, \ V_{OVDD} = +2.5V, \ T_A = +25^{\circ}C.) \text{ (Notes 2, 3)}$

| PARAMETER                           | SYMBOL            | CONDITIONS                                                                | MIN | TYP | MAX | UNITS |

|-------------------------------------|-------------------|---------------------------------------------------------------------------|-----|-----|-----|-------|

| TIMING CHARACTERISTICS              | 1                 |                                                                           |     |     |     |       |

| SCLK Frequency                      | f <sub>SCLK</sub> |                                                                           | 0   |     | 12  | MHz   |

| SCLK Period                         | t <sub>CP</sub>   |                                                                           | 83  |     |     | ns    |

| SCLK Pulse Width High               | t <sub>CH</sub>   |                                                                           | 15  |     |     | ns    |

| SCLK Pulse Width Low                | t <sub>CL</sub>   |                                                                           | 15  |     |     | ns    |

| CSB Fall to SCLK Rise<br>Setup Time | t <sub>CSS0</sub> | To 1st SCLK rising edge (RE)                                              | 15  |     |     | ns    |

| CSB Fall to SCLK Rise<br>Hold Time  | t <sub>CSH0</sub> | Applies to inactive RE preceding 1st RE                                   | 0   |     |     | ns    |

| CSB Rise to SCLK Rise<br>Hold Time  | t <sub>CSH1</sub> | Applies to 32nd RE, executed write                                        | 10  |     |     | ns    |

| CSB Rise to SCLK Rise               | t <sub>CSA</sub>  | Applies to 32nd RE, aborted write sequence                                | 15  |     |     | ns    |

| SCLK Rise to CSB Fall               | t <sub>CSF</sub>  | Applies to 32nd RE                                                        | 100 |     |     | ns    |

| CSB Pulse-Width High                | t <sub>CSPW</sub> |                                                                           | 20  |     |     | ns    |

| SDI-to-SCLK Rise Setup Time         | t <sub>DS</sub>   |                                                                           | 8   |     |     | ns    |

| SDI to SCLK Rise Hold Time          | t <sub>DH</sub>   |                                                                           | 8   |     |     | ns    |

|                                     |                   | C <sub>LOAD</sub> = 20pf                                                  |     |     | 40  | ns    |

| SCLK Fall to SDO Transition         | t <sub>DOT</sub>  | $C_{LOAD}$ = 20pf, $V_{AVDD}$ = $V_{DVDD} \ge 1.8V$ , $V_{OVDD} \ge 2.5V$ |     |     | 20  | ns    |

| SCLK Fall to SDO Hold               | t <sub>DOH</sub>  | C <sub>LOAD</sub> = 20pf                                                  | 2   |     |     | ns    |

| CSB Fall to SDO Fall                | t <sub>DOE</sub>  | Enable time, C <sub>LOAD</sub> = 20pf                                     |     |     | 30  | ns    |

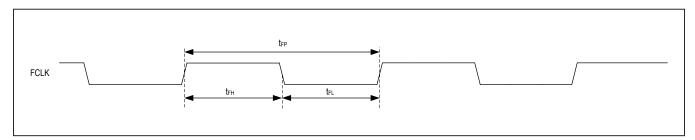

### **Timing Characteristics (continued)**

$(V_{DVDD} = V_{AVDD} = +1.1V \text{ to } +2.0V, V_{OVDD} = +1.65V \text{ to } +3.6V, T_A = T_{MIN} \text{ to } T_{MAX}, unless otherwise noted. Typical values are at$  $V_{DVDD}$  = +1.8V,  $V_{OVDD}$  = +2.5V,  $T_A$  = +25°C.) (Notes 2, 3)

| PARAMETER             | SYMBOL            | CONDITIONS               | MIN    | TYP   | MAX | UNITS |

|-----------------------|-------------------|--------------------------|--------|-------|-----|-------|

| CSB Rise to SDO Hi-Z  | t <sub>DOZ</sub>  | Disable time             |        |       | 35  | ns    |

| FCLK Frequency        | f <sub>FCLK</sub> | External reference clock | 32.768 |       |     | kHz   |

| FCLK Period           | t <sub>FP</sub>   |                          |        | 30.52 |     | μs    |

| FCLK Pulse-Width High | t <sub>FH</sub>   | 50% duty cycle assumed   |        | 15.26 |     | μs    |

| FCLK Pulse-Width Low  | t <sub>FL</sub>   | 50% duty cycle assumed   |        | 15.26 |     | μs    |

- Note 2: Limits are 100% tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

- Note 3: Guaranteed by design and characterization. Not tested in production.

- **Note 4:** One electrode drive with <10 $\Omega$  source impedance, the other driven with 51k $\Omega$  in parallel with a 47nF per IEC60601-2-47.

- **Note 5:** Inputs connected to  $51k\Omega$  in parallel with a 47nF to  $V_{CM}$ .

- **Note 6:** Use this setting only for  $V_{AVDD} = V_{DVDD} \ge 1.65V$ .

- Note 7: Use this setting only for  $V_{AVDD} = V_{DVDD} \ge 1.55V$ . Note 8: Use this setting only for  $V_{AVDD} = V_{DVDD} \ge 1.45V$ . Note 9:  $f_{SCLK} = 4MHz$ , burst mode, EFIT = 8,  $C_{SDO} = C_{INTB} = 50pF$ .

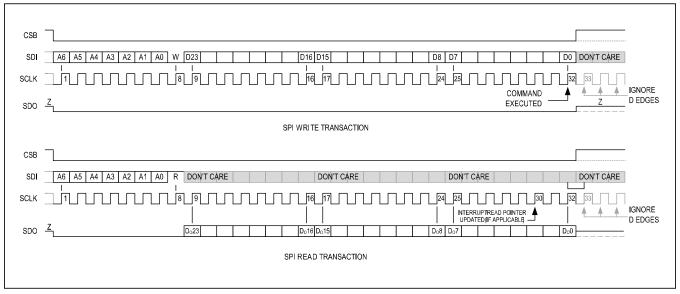

Figure 1a. SPI Timing Diagram

Figure 1b. FCLK Timing Diagram

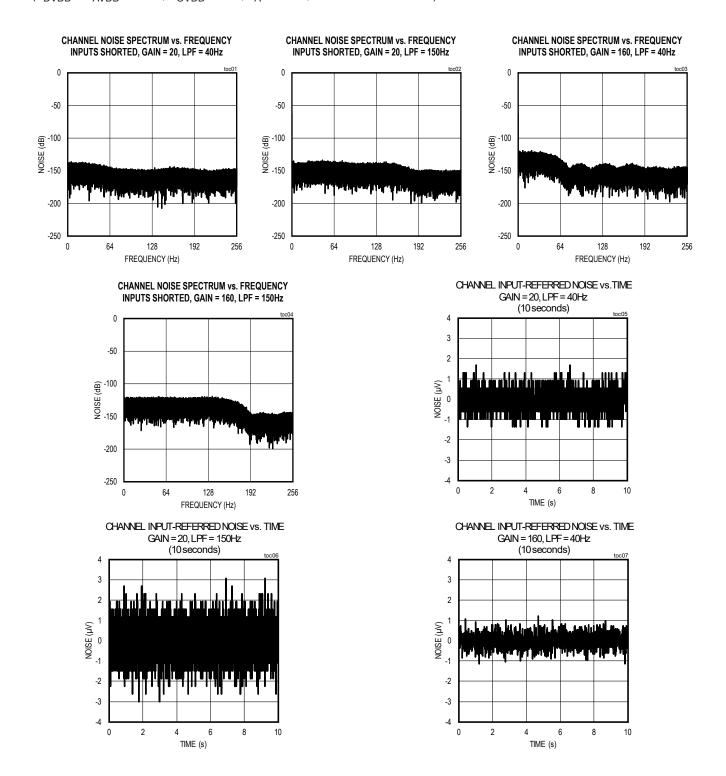

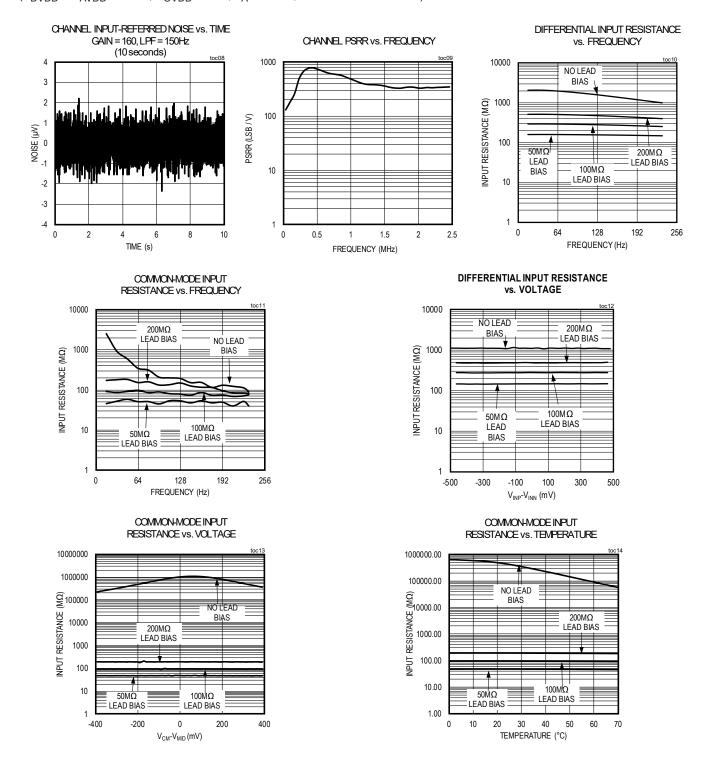

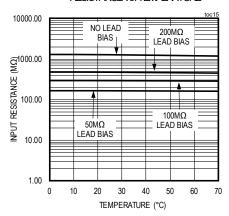

### **Typical Operating Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = 2.5V, T_A = +25$ °C, unless otherwise noted.)

### **Typical Operating Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = 2.5V, T_A = +25$ °C, unless otherwise noted.)

### **Typical Operating Characteristics**

$(V_{DVDD} = V_{AVDD} = +1.8V, V_{OVDD} = 2.5V, T_A = +25$ °C, unless otherwise noted.)

### DIFFERENTIAL INPUT RESISTANCE vs. TEMPERATURE

### **Pin Configuration**

### **Pin Description**

| BUMP                      | NAME | FUNCTION                                                                                                                                   |

|---------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| WLP                       | NAME | FUNCTION                                                                                                                                   |

| A1, A2, A3, A4,<br>B2, C2 | I.C. | Internally Connected. Connect to AGND.                                                                                                     |

| B3, B4, C3, C4,<br>D4     | AGND | Analog Power and Reference Ground. Connect into the printed circuit board ground plane.                                                    |

| A5                        | INP  | Positive Input                                                                                                                             |

| A6                        | INN  | Negative Input                                                                                                                             |

| В6                        | CAPP | Analog High-Pass Filter Input. Connect a 1µF X7R capacitor (CHPF) between CAPP and CAPN to form a 0.5Hz high-pass response in the channel. |

| B5                        | CAPN | Analog High-Pass Filter Input. Connect a 1µF X7R capacitor (CHPF) between CAPP and CAPN to form a 0.5Hz high-pass response in the channel. |

| C6                        | CPLL | PLL Loop Filter Input. Connect 1nf C0G ceramic capacitor between CPLL and AGND.                                                            |

### **Pin Description (continued)**

| вимр |       |                                                                                                                              |

|------|-------|------------------------------------------------------------------------------------------------------------------------------|

| WLP  | NAME  | FUNCTION                                                                                                                     |

| C5   | DGND  | Digital Ground for Both Digital Core and I/O Pad Drivers. Recommended to connect to AGND plane.                              |

| D6   | DVDD  | Digital Core Supply Voltage. Connect to AVDD                                                                                 |

| D5   | FCLK  | External 32.768kHz Clock that Controls the Sampling of the Internal Sigma-Delta Converters and Decimator.                    |

| E6   | CSB   | Active-Low Chip-Select Input. Enables the serial interface.                                                                  |

| E5   | SCLK  | Serial Clock Input. Clocks data in and out of the serial interface when CSB is low.                                          |

| E4   | SDI   | Serial Data Input. SDI is sampled into the device on the rising edge of SCLK when CSB is low.                                |

| E3   | SDO   | Serial Data Output. SDO will change state on the falling edge of SCLK when CSB is low. SDO is three-stated when CSB is high. |

| D3   | OVDD  | Logic Interface Supply Voltage                                                                                               |

| E2   | INT2B | Interrupt 2 Output. INT2B is an active-low status output. It can be used to interrupt an external device.                    |

| D2   | INTB  | Interrupt Output. INTB is an active low status output. It can be used to interrupt an external device.                       |

| E1   | AVDD  | Analog Core Supply Voltage. Connect to DVDD.                                                                                 |

| D1   | VREF  | ADC Reference Buffer Output. Connect a 10µF X7R ceramic capacitor between VREF and AGND.                                     |

| C1   | VCM   | Common Mode Buffer Output. Connect a 10µF X5R ceramic capacitor between VCM and AGND.                                        |

| B1   | VBG   | Bandgap Noise Filter Output. Connect a 1.0μF X7R ceramic capacitor between VBG and AGND.                                     |

### **Detailed Description**

### **ESD Protection**

|                |  | IEC61000-4-2 Contact Discharge (Note 10) | ±8   |    |

|----------------|--|------------------------------------------|------|----|

| INP, INN       |  | IEC61000-4-2 Air-Gap Discharge (Note 10) | ±15  | kV |

|                |  | HMM (Human Metal Model)                  | ±8   |    |

| All Other Pins |  | JEDEC JESD22-A114 HBM Transient Pulse    | ±2.5 | kV |

Note 10:ESD test performed with  $1k\Omega$  series resistor designed to withstand 8kV surge voltage.

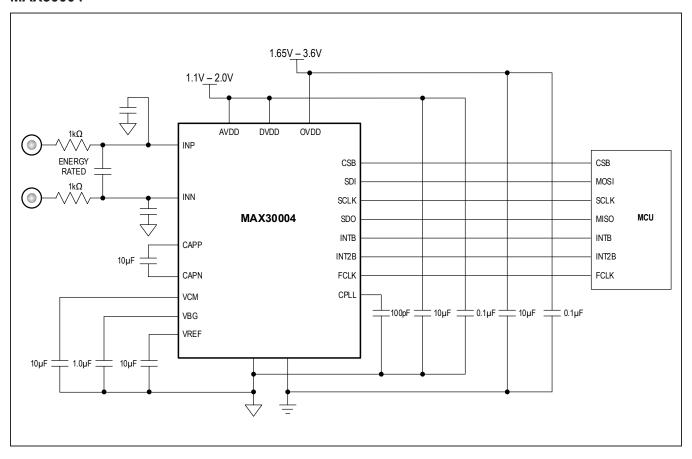

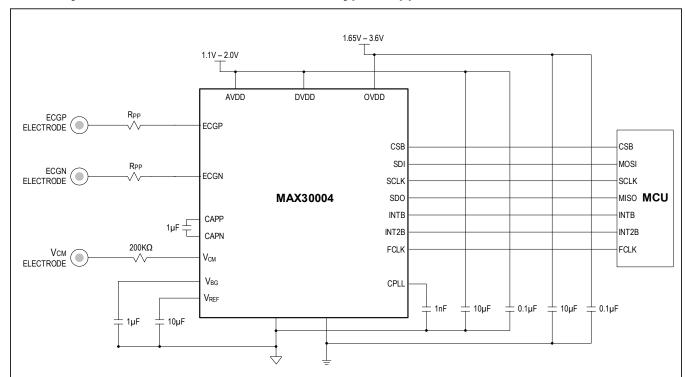

### **Biopotential Channel**

Figure 2 illustrates the biopotential channel block diagram, excluding the ADC. The channel comprises an input MUX, a fast-recovering instrumentation amplifier, an antialias filter, and a programmable gain amplifier. The MUX includes several features such as ESD protection, EMI filtering, lead biasing, leads off checking, and ultra-low

power leads-on checking. The output of this analog channel drives an 18-bit Sigma-Delta ADC.

### **Input MUX**

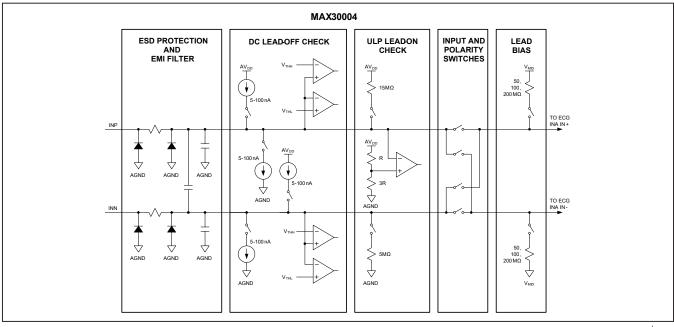

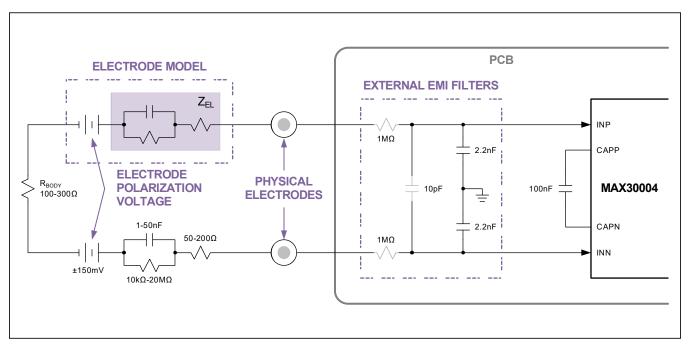

The input MUX shown in <u>Figure 3</u> contains integrated ESD and EMI protection, DC leads off detect current sources, lead-on detect, series isolation switches, and lead biasing.

Figure 2. Channel Input Amplifier and PGA Excluding the ADC

Winguræn Blolop patmMUX Analog Devices │ 14

### **EMI Filtering and ESD Protection**

EMI filtering of the INP and INN inputs consists of a single pole, low pass, differential, and common mode filter with the pole located at approximately 32MHz. The INP and INN inputs also have input clamps that protect the inputs from ESD events.

- ±8kV using the Contact Discharge method specified in IEC61000-4-2 ESD

- ±15kV using the Air Gap Discharge method specified in IEC61000-4-2 ESD

- ±8kV HBM

- For IEC61000-4-2 ESD protection, use 1kΩ series resistors on INP and INN that are rated to withstand 8kV surge voltages.

### DC Leads-Off Detection and ULP Leads-On Detection

The input MUX leads-off detect circuitry consists of programmable sink/source DC current sources that allow for DC leads-off detection while the channel is powered up in normal operation and an ultra-low-power (ULP) leads-on detect while the channel is powered down.

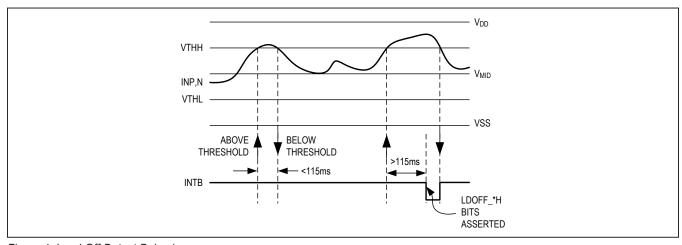

The MAX30004 accomplishes DC leads-off detection by applying a DC current to pull the input voltage up to above V<sub>MID</sub> + V<sub>TH</sub> or down to below V<sub>MID</sub> - V<sub>TH</sub>. The current sources have user selectable values of 0nA, 5nA, 10nA, 20nA, 50nA, and 100nA that allow coverage of dry and wet electrode impedance ranges. Supported thresholds are V<sub>MID</sub>  $\pm$  0.30V (recommended), V<sub>MID</sub>  $\pm$  0.40V, V<sub>MID</sub>  $\pm$  0.45V, and V<sub>MID</sub>  $\pm$  0.50V. A threshold of 400mV, 450mV, and 500mV should only be used when V<sub>AVDD</sub>  $\geq$  1.45V, 1.55V, and 1.65V, respectively. A dynamic comparator protects against false flags generated by the input amplifier and input chopping. The comparator checks for a minimum continuous violation (or threshold exceeded) of 115ms to

140ms depending on the setting of FMSTR[1:0] before asserting any one of the LDOFF\_\* interrupt flags (Figure 4). See registers CNFG\_GEN (0x10) and CNFG\_MUX 0x14) for configuration settings and see Table 1 for recommended values given electrode type and supply voltage. The 0nA setting can also be used with the V<sub>MID</sub>  $\pm$  300mV threshold to monitor the input compliance of the INA when DC leads-off detection is not needed.

The ULP lead on detect operates by pulling INN low with a pulldown resistance larger than  $5m\Omega$  and pulling INP high with a pullup resistance larger than  $15m\Omega.$  A low-power comparator determines if INP is pulled below a predefined threshold that occurs when both electrodes make contact with the body. When the impedance between INP and INN is less than  $40M\Omega,$  an interrupt LONINT is asserted, alerting the  $\mu C$  to a leads-on condition.

### **Lead Bias**

The MAX30004 limits the INP and INN DC input common mode range to  $V_{MID}$  ±150mV at  $V_{AVDD}$  = 1.1V or  $V_{MID}$  ±550mV (typ) at  $V_{AVDD}$  = 1.8V. This range can be maintained either through external/internal lead-biasing.

Internal DC lead-biasing consists of  $50M\Omega$ ,  $100M\Omega$ , or  $200M\Omega$  selectable resistors to  $V_{MID}$  that drive the electrodes within the input common mode requirements of the channel and can drive the connected body to the proper common mode voltage level. See register CNFG\_GEN (0x10) to select a configuration. The common-mode voltage,  $V_{CM}$ , can optionally be used as a body bias to drive the body to the common-mode voltage by connecting  $V_{CM}$  to a separate electrode on the body through a  $200k\Omega$  or higher resistor to limit current into the body, according to IEC 60601-1:2005, 8.7.3. If this is utilized, the internal lead bias resistors to  $V_{MID}$  can be disabled.

Figure 4. Lead-Off Detect Behavior

Table 1. Recommended Lead Bias (Rb), Current Source Values, and Thresholds for Electrode Impedances

|                                    |        |                                                                                                                                                                                                        |                  | ELECTRODE      | IMPEDANC     | E             |               |                |  |  |  |

|------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|--------------|---------------|---------------|----------------|--|--|--|

| I <sub>DC</sub><br>V <sub>TH</sub> | <100kΩ | 100kΩ -<br>200kΩ                                                                                                                                                                                       | 200kΩ -<br>400kΩ | 400kΩ -<br>1MΩ | 1MΩ -<br>2MΩ | 2MΩ - 4<br>MΩ | 4MΩ -<br>10MΩ | 10MΩ -<br>20MΩ |  |  |  |

| I <sub>DC</sub> = 10nA             |        | All settings of $R_b$ $V_{TH} = V_{MID}$ $\pm 300 \text{mV}, \pm 400 \text{mV}$                                                                                                                        |                  |                |              |               |               |                |  |  |  |

| I <sub>DC</sub> = 20nA             |        | All settings of R <sub>b</sub><br>All settings of V <sub>TH</sub>                                                                                                                                      |                  |                |              |               |               |                |  |  |  |

| I <sub>DC</sub> = 50nA             |        | All settings of $R_b$ of $R_b$ $V_{TH} = V_{MID}$ $\pm 450 \text{mV}$ , $\pm 500 \text{mV}$                                                                                                            |                  |                |              |               |               |                |  |  |  |

| I <sub>DC</sub> = 100nA            |        | $\begin{array}{c} & \text{All settings} \\ \text{of Rb} \\ \text{All settings of R}_b \\ \text{All settings of V}_T \\ & \pm 400 \text{mV}, \\ \pm 450 \text{mV}, \\ \pm 500 \text{mV} \\ \end{array}$ |                  |                |              |               |               |                |  |  |  |

### **Isolation Switches**

The series switches in the MAX30004 isolate INP and INN pins (subject) from the internal signal path, the series switches are disabled by default. They must be enabled to record R-to-R data.

### **Gain Settings and Input Range**

The device's biopotential channel contains an input instrumentation amplifier that provides low-noise, fixed 20V/V gain amplification of the differential signal, rejects differential DC voltage due to electrode polarization, rejects common-mode interference primarily due to AC mains interference, and provides high input impedance to guarantee high CMRR even in the presence of severe electrode impedance mismatch (see Figure 2). The differential DC rejection corner frequency is set by an external capacitor (CHPF) placed between pins CAPP and CAPN, refer to Table 2 for appropriate value selection. There are three recommended options for the cutoff frequency: 5Hz, 0.5Hz, and 0.05Hz. Setting the cutoff frequency to 5Hz provides the most motion artifact rejection, making it best

suited for heart rate monitoring. 0.5Hz and 0.05Hz can be used for applications requiring moderate and no motion artifact rejection respectively. The high-pass corner frequency is calculated by the following equation:

$1/(2\pi \times R_{HPF} \times C_{HPF})$

RHPF is specified in the *Electrical Characteristics* table. Following the instrumentation amplifier is a 2-pole active anti-aliasing filter with a 600Hz -3dB frequency that provides 57dB of attenuation at half the modulator sampling rate (approximately 16kHz) and a PGA with programmable gains of 1, 2, 4, and 8V/V for an overall gain of 20, 40, 80, and 160V/V. The instrumentation amplifier and PGA are chopped to minimize offset and 1/f noise. Gain settings are configured through the CNFG\_CH (0x15) register. The useable common-mode range is V<sub>MID</sub> ±150mV at V<sub>AVDD</sub> = 1.1V or V<sub>MID</sub> ±550mV (typ) at V<sub>AVDD</sub> = 1.8V. Internal lead biasing can be used to meet this requirement. The useable DC differential range is ±300mV at V<sub>AVDD</sub> = 1.1V or  $\pm 650$ mV (typ) at  $V_{AVDD}$  = 1.8V to allow for electrode polarization voltages on each electrode. The input AC differential range is ±32.5mV or ±65mV<sub>P-P</sub>.

Table 2. Analog HPF Corner Frequency Selection

| C <sub>HPF</sub> | HPF CORNER FREQUENCY |

|------------------|----------------------|

| 0.1µ             | ≤ 5Hz                |

| 1.0µ             | ≤ 0.5Hz              |

| 10µ              | ≤ 0.05Hz             |

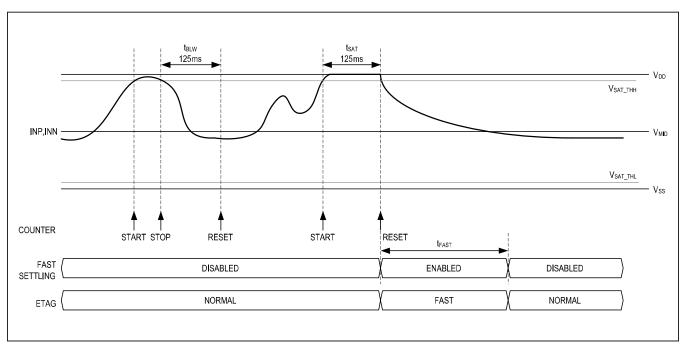

### **Fast Recovery Mode**

The input instrumentation amplifier has the ability to rapidly recover from an excessive overdrive event such as a defibrillation pulse, high-voltage external pacing, and electro-surgery interference. There are two modes of recovery that can be used: automatic or manual recovery. The mode is programmed by the FAST[1:0] bits in the MNGR\_DYN (0x05) register.

Automatic mode engages once the saturation counter exceeds approximately 125ms (t<sub>SAT</sub>). The counter is activated the first time the ADC output exceeds the symmetrical threshold defined by the FAST\_TH[5:0] bits

in the MNGR\_DYN (0x05) register and accumulates the time that the ADC output exceeds either the positive or negative threshold. If the saturation counter exceeds 125ms, it triggers the fast settling mode (if enabled) and resets. The saturation counter can also be reset prior to triggering the fast settling mode if the ADC output falls below the threshold continuously for 125ms (t<sub>BLW</sub>). This feature is designed to avoid false triggers due to the QRS complex. Once triggered, fast settling mode will be engaged for 500ms, see Figure 5.

In manual mode, a user algorithm running on the host microcontroller or an external stimulus input will generate the trigger to enter fast recovery mode. The host microcontroller then enables the manual fast recovery mode in the MNGR\_DYN (0x05) register. The manual fast recovery mode can be of a much shorter duration than the automatic mode and allows for more rapid recovery. One such example is recovery from external high-voltage pacing signals in a few milliseconds to allow the observation of a subsequent p-wave.

Figure 5. Automatic Fast Settling Behavior

### R-to-R Detection

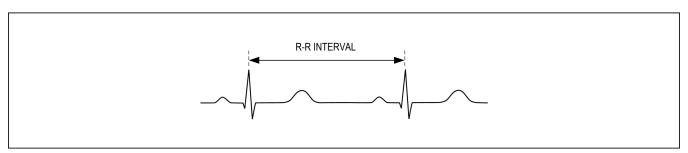

The MAX30004 contains built-in hardware to detect R-to-R intervals using an adaptation of the Pan-Tompkins QRS detection algorithm<sup>1</sup>. The timing resolution of the R-R interval is approximately 8ms and depends on the setting of FMSTR [1:0] in CNFG\_GEN (0x10) register. See Table 19 for the timing resolution of each setting.

When an R event is identified, the RRINT status bit is asserted and the RTOR\_REG (0x25) register is updated with the count seen since the last R event. Figure 6 illustrates the R-R interval on a QRS complex. Refer to registers CNFG\_RTOR1 (0x1D) and CNFG\_RTOR2 (0x1E) for configuration details.

The latency of the R-to-R value written to the RTOR Interval Memory Register is the sum of the R-to-R decimation delay and the R-to-R detection delay blocks. The R-to-R decimation factor is fixed at 256 and the decimation delay (t<sub>R2R\_DEC</sub>) is always 3,370 FMSTR clocks, as shown in Table 3.

The detection circuit consists of several digital filters and signal processing delays. These depend on the

WNDW[3:0] bits in the CNFG\_RTOR (0x1D) register. The detection delay (t<sub>R2R\_DET</sub>) is described by the following equation:

$t_{R2R\_DET}$  = 5,376 + 256 x WNDW in FMSTR clocks where WNDW is an integer from 0 to 15 and the total latency ( $t_{R2R\_DEL}$ ) is the sum of the two delays and summarized in the equation below:

$t_{R2R\_DEL} = t_{R2R\_DEC} + t_{R2R\_DET} = 3,370 + 5,376 + 256 x WNDW in FMSTR clocks where WNDW is an integer from 0 to 15.$

### **Reference and Common Mode Buffer**

The MAX30004 features internally generated reference voltages. The bandgap output ( $V_{BG}$ ) pin requires an external 1.0µF capacitor to AGND and the reference output ( $V_{REF}$ ) pin requires a 10µF external capacitor to AGND for compensation and noise filtering.

A common-mode buffer is provided to buffer 650mV which is used to drive common mode voltages for internal blocks. Use a  $10\mu\text{F}$  external capacitor between  $V_{CM}$  to AGND to provide compensation and noise filtering.

Figure 6. R-to-R Interval Illustration

Table 3. R-to-R Decimation Delay in ms and FMSTR CLK vs. Register Settings, FCLK = 32.768Hz

| FMSTR | FMSTR FREQ     | FMSTR     | DECIMATION | RTOR TIME       | DELAY IN R-TO- | R DECIMATION |

|-------|----------------|-----------|------------|-----------------|----------------|--------------|

| [1:0] | IN FCLKs       | FREQ (Hz) | DECIMATION | RESOLUTION (ms) | IN FMSTR CLKs  | IN ms        |

| 00    | FCLK           | 32,768    | 256        | 7.8125          | 3370           | 102.844      |

| 01    | FCLK x 625/640 | 32,000    | 256        | 8.0             | 3370           | 105.313      |

| 10    | FCLK x 625/640 | 32,000    | 256        | 8.0             | 3370           | 105.313      |

| 11    | FCLK x 640/656 | 31,968.78 | 256        | 8.0078          | 3370           | 105.415      |

<sup>&</sup>lt;sup>1</sup>J. Pan and W.J. Tompkins, "A Real-Time QRS Detection Algorithm," IEEE Trans. Biomed. Eng., vol. 32, pp. 230-236

### Sample Synchronization Pulse

The MAX30004 offers a sample synchronization pulse that allows the direct observation of the channel sample instant for either synchronization between multiple devices or as a monitoring feature during debug. When enabled (EN SAMP in either register EN INT or EN INT2), the MAX30004 generates an interrupt either every sample instant, or every second, fourth, or 16th sample instant, based on the setting of SAMP\_IT[1:0] in register MNGR\_ INT. The sample instants are defined by the channel ADC, and are not R-to-R samples. Therefore, the interval between individual sample instants is dependent on the channel data rate as defined by FMSTR[1:0] and RATE[1:0]. The clear behavior of the sample synchronization pulse is affected by the CLR SAMP bit in register MNGR INT. When this feature is used, it is recommended to use a dedicated interrupt output for just the sample synchronization pulse.

## SPI Interface Description 32-Bit Read/Write Sequences

The MAX30004 interface is SPI/QSPI/Micro-wire/DSP compatible. The operation of the SPI interface is shown in Figure 1. Data is strobed into the MAX30004 on SCLK rising edges. The device is programmed and accessed by a 32 cycle SPI instruction framed by a CSB low interval. The content of the SPI operation consists of a one byte

command word (comprised of a seven bit address and a Read/Write mode indicator (i.e., A[6:0] + R/W) followed by a three-byte data word. The MAX30004 is compatible with the CPOL = 0/CPHA = 0 and CPOL = 1/CPHA = 1 modes of operation.

Write mode operations will be executed on the 32nd SCLK rising edge using the first four bytes of data available. In write mode, any data supplied after the 32nd SCLK rising edge will be ignored. Subsequent writes require CSB to de-assert high and then assert low for the next write command. In order to abort a command sequence, the rise of CSB must precede the updating (32nd) rising-edge of SCLK, meeting the  $t_{\rm CSA}$  requirement.

Read mode operations will access the requested data on the 8th SCLK rising edge, and present the MSB of the requested data on the following SCLK falling edge, allowing the  $\mu$ C to sample the data MSB on the 9th SCLK rising edge. Configuration and status data are all available via normal mode read back sequences. If more than 32 SCLK rising edges are provided in a normal read sequence then the excess edges will be ignored and the device will read back zeros.

If accessing the STATUS register, all interrupt updates will be made in response to the 30th SCLK rising edge, allowing for internal synchronization operations to occur.

Figure 7. SPI Normal Mode Transaction Diagrams

# **User Command and Register Map**

| REG          |                   | W/W   |                 |              |               | DATAINDE                               | DATA INDEX (DINDEX) |              |                |               |

|--------------|-------------------|-------|-----------------|--------------|---------------|----------------------------------------|---------------------|--------------|----------------|---------------|

| [0:9]        | NAME              | MODE  | 23/15/7         | 22 / 14 / 6  | 21/13/5       | 20 / 12 / 4                            | 19/11/3             | 18/10/2      | 17/9/1         | 16/8/0        |

| 0x00         | NO-OP             | R/W   | ×/×/×           | ×/×/×        | ×/×/×         | ×/×/×                                  | ×/×/×               | ×/×/×        | ×/×/×          | ×/×/×         |

|              | i<br>i            | ſ     | ×               | ×            | FSTINT        | DCLO                                   | ×                   | ×            | ×              | ×             |

| 0x01         | SIAIUS            | Υ<br> | ×               | ×            | ×             | ×                                      | LONINT              | RRINT        | SAMP           | PLLINT        |

|              |                   |       | 0               | 0            | ×             | ×                                      | LOFF_PH             | LOFF_PL      | LOFF_NH        | LOFF_NL       |

| (            |                   |       | ×               | ×            | EN_<br>FSTINT | EN_<br>DCLOFFINT                       | ×                   | ×            | ×              | ×             |

| 0x02<br>0x03 | EN_INT<br>EN_INT2 | R/W   | ×               | ×            | ×             | ×                                      | EN_<br>LONINT       | EN_<br>RRINT | EN_SAMP        | EN_<br>PLLINT |

|              |                   |       | ×               | ×            | ×             | ×                                      | ×                   | ×            | INTB_TYPE[1:0] | /PE[1:0]      |

|              |                   |       | ×               | ×            | ×             | ×                                      | ×                   | ×            | ×              | ×             |

| 0x04         | MNGR              | Z.W   | ×               | ×            | ×             | ×                                      | ×                   | ×            | X              | ×             |

|              | L<br>Z            |       | ×               | CLR_<br>FAST | CLR_F         | CLR_RRINT[1:0]                         | ×                   | CLR_<br>SAMP | SAMP_IT[3:0]   | [П[3:0]       |

|              |                   |       | FAST[1:0]       | [1:0]        |               |                                        | FAST                | FAST_TH[5:0] |                |               |

| 0x05         | MNGR_<br>DYN_     | RW    | ×               | ×            | ×             | ×                                      | ×                   | ×            | ×              | ×             |

|              |                   |       | ×               | ×            | ×             | ×                                      | ×                   | ×            | ×              | ×             |

| 0×08         | SW_RST            | W     |                 |              | De            | Data Required for Execution = 0x000000 | xecution = 0x0      | 00000        |                |               |

| 60×0         | RESTART           | W     |                 |              | Dê            | Data Required for Execution = 0x000000 | xecution = 0x0      | 00000        |                |               |

| 0x0A         | RTOR_<br>RST      | >     |                 |              | D             | Data Required for Execution = 0x000000 | xecution = 0x0      | 00000        |                |               |

|              |                   |       | 0               | 1            | 0             | 1                                      |                     | REV          | REV_ID[3:0]    |               |

| 0x0F         | INFO              | ٣     | ×               | ×            | 0             | 0                                      | ×                   | ×            | ×              | ×             |

|              |                   |       | ×               | ×            | ×             | ×                                      | ×                   | ×            | ×              | ×             |

|              | (<br>!            |       | EN_ULP_LON[1:0] | LON[1:0]     | FMS           | =MSTR[1:0]                             | EN_CH               | ×            | ×              | ×             |

| 0x10         | ONFG.             | RW    | ×               | ×            | EN_DC         | EN_DCLOFF[1:0]                         | IPOL                |              | IMAG[2:0]      |               |

|              |                   |       | VTH[1:0]        | 1:0]         | EN_R          | EN_RBIAS[1:0]                          | RBIAS               | RBIASV[1:0]  | RBIASP         | RBIASN        |

# User Command and Register Map (continued)

| REG   |                | R/W  |             |                 |                                    | DATA IND    | DATA INDEX (D <sub>INDEX</sub> ) |           |                                       |        |

|-------|----------------|------|-------------|-----------------|------------------------------------|-------------|----------------------------------|-----------|---------------------------------------|--------|

| [6:0] |                | MODE | 23 / 15 / 7 | 22 / 14 / 6     | 21/13/5                            | 20 / 12 / 4 | 19 / 11 / 3                      | 18/10/2   | 17/9/1                                | 16/8/0 |

|       | !              |      | POL         | ×               | OPENP                              | OPENN       | ×                                | ×         | ×                                     | ×      |

| 0x14  | CNFG<br>MUX    | RW   | ×           | ×               | ×                                  | ×           | ×                                | ×         | X                                     | ×      |

|       |                |      | ×           | ×               | ×                                  | ×           | ×                                | ×         | ×                                     | ×      |

|       |                |      | RATE[1:0]   | [1:0]           | ×                                  | ×           | ×                                | ×         | GAIN[1:0]                             | 1[1:0] |

| 0x15  | CNFG_          | RW   | ×           | DHPF            | DLP                                | DLPF[1:0]   | ×                                | ×         | ×                                     | ×      |

|       |                |      | ×           | ×               | ×                                  | ×           | ×                                | ×         | ×                                     | ×      |

|       |                |      |             | WNE             | WNDW[3:0]                          |             |                                  | RG,       | RGAIN[3:0]                            |        |

| 0x1D  | CNFG_<br>RTOR1 | RW   | EN_RTOR     | ×               | PAV                                | PAVG[1:0]   |                                  | PT        | PTSF[3:0]                             |        |

|       |                |      | ×           | ×               | ×                                  | ×           | ×                                | ×         | ×                                     | ×      |

|       | !              |      | ×           | ×               |                                    |             | HOF                              | HOFF[5:0] |                                       |        |

| 0x1E  | CNFG_<br>RTOR2 | RW   | ×           | ×               | RAV                                | RAVG[1:0]   | ×                                |           | RHSF[2:0]                             |        |

|       |                |      | ×           | ×               | ×                                  | ×           | ×                                | ×         | ×                                     | ×      |

| 0x25  | RTOR           | 8    | Ч           | to-R Interval R | R-to-R Interval Register Read Back | ack         | See                              | RTOR DATA | See RTOR DATA description for details | etails |

| 0x7F  | NO-OP          | R/W  | x/x/x       | x/x/x           | x/x/x                              | x/x/x       | x/x/x                            | x/x/x     | x/x/x                                 | x/x/x  |

### **Register Descriptions**

### NO\_OP (0x00 and 0x7F) Registers

No Operation (NO\_OP) registers are read-write registers that have no internal effect on the device. If these registers are read back, DOUT remains zero for the entire SPI transaction. Any attempt to write to these registers is ignored without impact to internal operation.

### STATUS (0x01) Register

STATUS is a read-only register that provides a comprehensive overview of the current status of the device. The first two bytes indicate the state of all interrupt terms (regardless of whether interrupts are enabled in registers EN\_INT (0x02) or EN\_INT2 (0x03)). All interrupt terms are active high. The last byte includes detailed status information for conditions associated with the interrupt terms.

Table 4. STATUS (0x01) Register Map

| REG  | NAME   | R/W | 23 / 15 / 7 | 22 / 14 / 6 | 21 / 13 / 5 | 20 / 12 / 4   | 19 / 11 / 3  | 18 / 10 / 2  | 17 / 9 / 1   | 16/8/0       |

|------|--------|-----|-------------|-------------|-------------|---------------|--------------|--------------|--------------|--------------|

|      |        |     | x           | х           | FSTINT      | DCLOFF<br>INT | х            | х            | х            | х            |

| 0x01 | STATUS | R   | х           | х           | х           | х             | LONINT       | RRINT        | SAMP         | PLLINT       |

|      |        |     | х           | х           | х           | х             | LDOFF_<br>PH | LDOFF_<br>PL | LDOFF_<br>NH | LDOFF_<br>NL |

### Table 5. Status (0x01) Register Meaning

| INDEX | NAME      | MEANING                                                                                                                                                                                                                                                                       |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[21] | FSTINT    | Fast Recovery Mode. Issued when the Fast Recovery Mode is engaged (either manually or automatically). Status and Interrupt Clear behavior is defined by CLR_FAST, see MNGR_INT for details.                                                                                   |

| D[20] | DCLOFFINT | DC Lead-Off Detection Interrupt. Indicates that the MAX30004 has determined it is in leads off condition (as selected in CNFG_GEN) for more than 115ms.  Remains active as long as the leads-off condition persists, then held until cleared by STATUS read back (32nd SCLK). |

**Table 5. Status (0x01) Register Meaning (continued)**

| INDEX | NAME     | MEANING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[11] | LONINT   | Ultra-Low Power (ULP) Leads-On Detection Interrupt. Indicates that the MAX30004 has determined it is in a leads-on condition (as selected in CNFG_GEN).  LONINT is asserted whenever EN_ULP_LON[1:0] in register CNFG_GEN is set to either 0b01 or 0b10 to indicate that the ULP leads on detection mode has been enabled. The STATUS register has to be read back once after ULP leads-on detection mode has been activated to clear LONINT and enable leads-on detection.  LONINT remains active while the leads-on condition persists, then held until cleared by STATUS read back (32nd SCLK). |

| D[10] | RRINT    | R-to-R Detector R Event Interrupt. Issued when the R-to-R detector has identified a new R event. Clear behavior is defined by CLR_RRINT[1:0]; see MNGR_INT for details.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D[9]  | SAMP     | Sample Synchronization Pulse. Issued on the ADC base-rate sampling instant, for use in assisting µC monitoring and synchronizing other peripheral operations and data, generally recommended for use as a dedicated interrupt.  Frequency is selected by SAMP_IT[1:0], see MNGR_INT for details.  Clear behavior is defined by CLR_SAMP, see MNGR_INT for details.                                                                                                                                                                                                                                 |

| D[8]  | PLLINT   | PLL Unlocked Interrupt. Indicates that the PLL has not yet achieved or has lost its phase lock. PLLINT will only be asserted when the PLL is powered up and active (Channel enabled). Remains asserted while the PLL unlocked condition persists, then held until cleared by STATUS read back (32nd SCLK).                                                                                                                                                                                                                                                                                         |

| D[3]  | LDOFF_PH | DC Lead Off Detection Detailed Status. Indicates that the MAX30004 has determined (as selected by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| D[2]  | LDOFF_PL | CNFG_GEN): INP is above the high threshold (V <sub>THH</sub> ), INP is below the low threshold (V <sub>THL</sub> ),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D[1]  | LDOFF_NH | INN is above the high threshold (V <sub>THL</sub> ), INN is below the low threshold (V <sub>THL</sub> ), respectively.  Remains active as long as the leads-off detection is active and the leads-off condition persists, then held until cleared by STATUS read back (32nd SCLK). LDOFF_PH to LDOFF_NL are detailed status                                                                                                                                                                                                                                                                        |

| D[0]  | LDOFF_NL | bits that are asserted at the same time as DCLOFFINT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### EN\_INT (0x02) and EN\_INT2 (0x03) Registers

EN\_INT and EN\_INT2 are read/write registers that govern the operation of the INTB output and INT2B output, respectively. The first two bytes indicate which interrupt input terms are included in the interrupt output OR term (ex. a one in an EN\_INT register indicates that the corresponding input term is included in the INTB interrupt output OR term). See the STATUS register for detailed descriptions of the interrupt terms. The power-on reset state of all EN\_INT terms is 0 (ignored by INT).

EN\_INT and EN\_INT2 can also be used to mask persistent interrupt conditions in order to perform other interrupt-driven operations until the persistent conditions are resolved.

INTB\_TYPE[1:0] allows the user to select between a CMOS or an open-drain NMOS mode INTB output. If using open-drain mode, an option for an internal  $125k\Omega$  pullup resistor is also offered.

All INTB and INT2B types are active-low (INTB low indicates the device requires servicing by the  $\mu$ C); however, the open-drain mode allows the INTB line to be shared with other devices in a wired-or configuration.

In general, it is suggested that INT2B be used to support specialized/dedicated interrupts of use in specific applications, such as the self-clearing versions of SAMP or RRINT.

Table 6. EN INT (0x02) and EN INT2 (0x03) Register Maps

| REG          | NAME              | R/W | 23 / 15 / 7 | 22 / 14 / 6 | 21 / 13 / 5   | 20 / 12 / 4      | 19 / 11 / 3   | 18 / 10 / 2  | 17 / 9 / 1  | 16 / 8 / 0    |

|--------------|-------------------|-----|-------------|-------------|---------------|------------------|---------------|--------------|-------------|---------------|