#### MAX25608

### 12-Switch, High-Brightness LED Matrix Manager for Automotive Front Lights

#### **General Description**

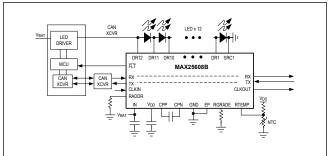

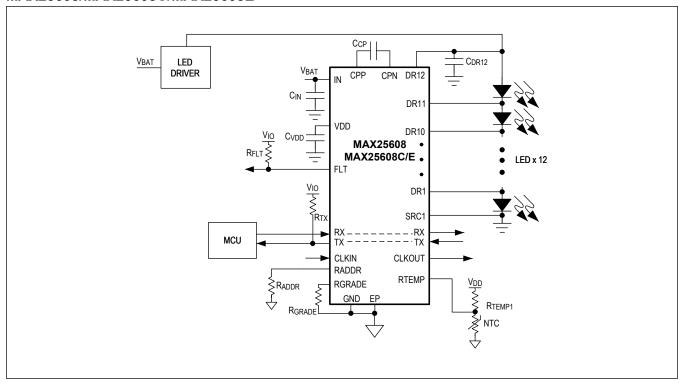

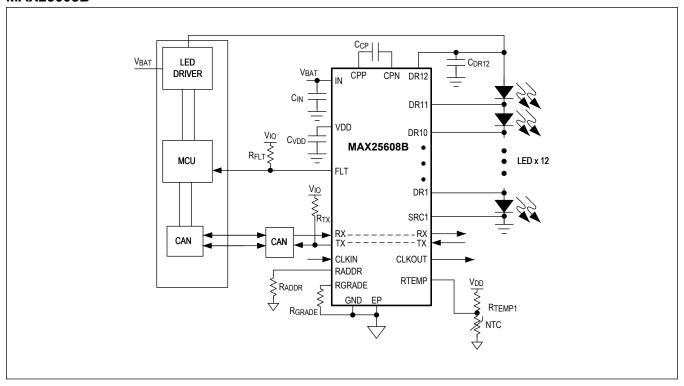

The MAX25608/MAX25608B/MAX25608C/MAX25608E 12-switch matrix manager ICs for automotive lighting applications include a 12-switch array for bypassing individual LEDs in a single- or dual-string application. They feature 12 individually controlled n-channel MOSFET switches rated for 14V with an on-resistance of  $0.06\Omega$ . A single current source can be used to power all of the LEDs connected in series. Individual LEDs can be dimmed by turning on and off the bypass switches across each LED. The devices can also be configured in dual-string applications with six switches in series per string. Each switch can be connected across one, two, or three LEDs in series. These devices also allow for parallel connection of two switches to bypass high-current LEDs. The ICs also include an internal charge pump that provides power for the gate drive for the LED bypass switches.

The MAX25608/MAX25608B/MAX25608C/MAX25608E feature a serial interface (UART) for serial communication. The MAX25608/MAX25608C/MAX25608E can be used in full-duplex applications, and the MAX25608B can be used in half-duplex applications, such as with CAN transceivers. The MAX25608 has spread spectrum enabled on the charge pump clock, and the MAX25608B/MAX25608C/MAX25608E have spread spectrum disabled on the charge pump clock. Each switch can be turned fully on, fully off, or dimmed with or without fade transitions through the serial interface. The ICs feature open-LED protection as well as open- and short-LED fault reporting through the serial interface. The devices are available in a 28-pin TSSOP package with exposed pad.

### **Applications**

- Automotive Matrix LED Systems

- Adaptive Drive Beam Lights

#### **Benefits and Features**

- Automotive Ready: AEC-Q100 Qualified

- Flexible Configuration

- · Up to 12 Switches in Series for Single String

- · Two Sub Strings of Six Series Switches per String

- Robust Serial Interface

- Multidrop UART Communication Interface

- Up to 16 Addressable Devices

- Compatible with CAN Physical Layer (MAX25608B)

- Optimal PWM Dimming Arrangement Provides Excellent Dimming Performance

- · Programmable 12-Bit PWM Dimming

- · Fade Transition Between PWM Dimming States

- Internal or External Clock for PWM Dimming

- · Programmable Slew Rate for EMI Control

- Protection Features and Package Improve Reliability

- · Open-LED Protection

- NTC Temperature Monitor

- Programmable Open- and Short-LED Threshold

- · Open and Shorted-LED Fault Reporting

- Open-Trace Fault Reporting (MAX25608E)

- Thermally Enhanced, 28-Pin TSSOP-EP

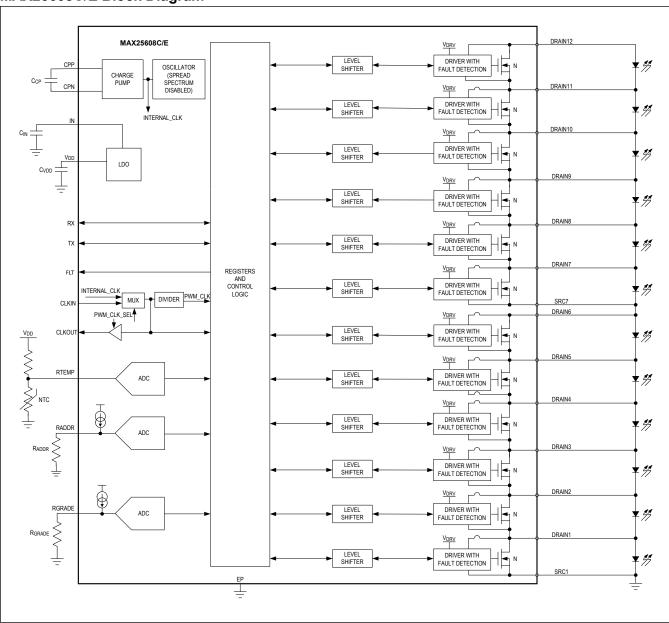

### **Simplified Block Diagram**

#### **TABLE OF CONTENTS**

| General Description                                                          | 1  |

|------------------------------------------------------------------------------|----|

| Applications                                                                 | 1  |

| Benefits and Features                                                        | 1  |

| Simplified Block Diagram                                                     | 1  |

| Absolute Maximum Ratings                                                     | 6  |

| Package Information                                                          | 6  |

| 28 TSSOP                                                                     | 6  |

| Electrical Characteristics                                                   | 7  |

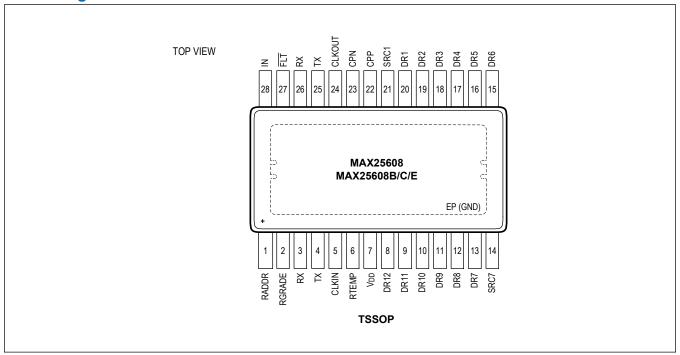

| Pin Configuration                                                            | 9  |

| Pin Description                                                              | 10 |

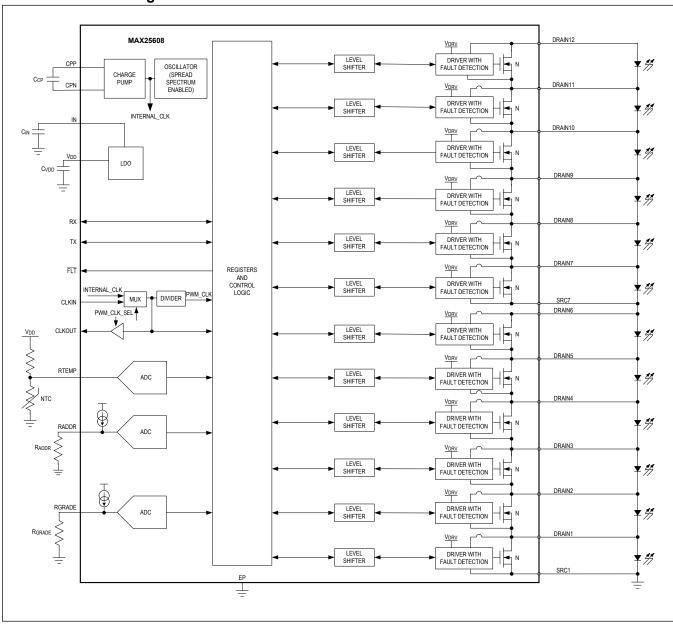

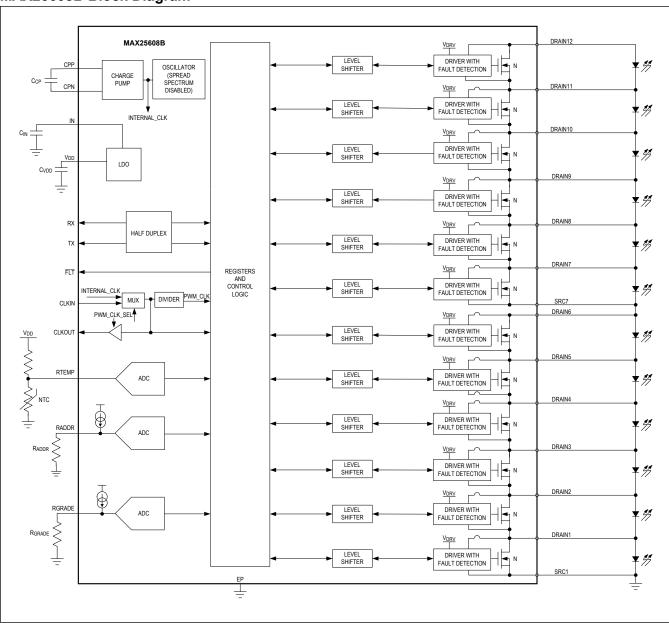

| Functional Diagrams                                                          | 11 |

| MAX25608 Block Diagram                                                       | 11 |

| MAX25608B Block Diagram                                                      | 12 |

| MAX25608C/E Block Diagram                                                    | 13 |

| Detailed Description                                                         | 14 |

| Power-on Reset and VDD_UVLO                                                  | 14 |

| Internal Switches                                                            | 14 |

| Power-up Sequence                                                            | 14 |

| Spread Spectrum                                                              | 14 |

| Programming Options                                                          | 14 |

| Pin Resistor Decode Table                                                    | 14 |

| Resistor Programming Table                                                   | 15 |

| PWM Dimming                                                                  | 15 |

| PWM Clock and Synchronous Operation with Multiple Devices                    | 16 |

| Dimming With and Without Fade                                                | 16 |

| RTEMP                                                                        | 18 |

| Fault Pin Behaviour                                                          | 19 |

| LED Fault Detection and Protection                                           | 19 |

| LED Open-Fault Detection and Protection                                      | 19 |

| Resetting Slew Rate, Open, and Short Threshold Registers with VIN Cold Crank | 19 |

| LED Short Detection                                                          | 19 |

| Open-Trace Detection (MAX25608E Only)                                        | 19 |

| Unused Switches and Pins                                                     | 20 |

| Thermal Shutdown                                                             | 20 |

| PCB Layout                                                                   | 21 |

| UART Serial Interface                                                        | 21 |

| Overview                                                                     | 21 |

| Device Connections                                                           | 21 |

| UART Packet Format                                                           | 21 |

## TABLE OF CONTENTS (CONTINUED)

| UART Frame and Interframe Format       | 22 |

|----------------------------------------|----|

| Rx Rise and Fall Times                 |    |

| Synchronization and Acknowledge Frames |    |

| Device ID and Address Frame Format     |    |

| Write Transactions                     |    |

| Read Transactions                      |    |

| CRC Error Checking                     |    |

| UART Watchdog Function                 |    |

| UART Communication Error Handling      |    |

| UART Timeout Conditions                |    |

| UART Timeout Flowchart                 |    |

| Register Map                           |    |

| MAX25608/MAX25608B/MAX25608C/MAX25608E |    |

| Register Details                       |    |

| Typical Application Circuits           |    |

| MAX25608/MAX25608C/MAX25608E           |    |

| MAX25608B                              | 66 |

| Ordering Information                   |    |

| Revision History                       | 67 |

#### LIST OF FIGURES

| Figure 1. PWM Dimming                                                      | 16   |

|----------------------------------------------------------------------------|------|

| Figure 2. Starting from 10% Duty, Updating Every Four PWM Cycles           | . 17 |

| Figure 3. Up-Transition Curve                                              | 18   |

| Figure 4. Down-Transition Curve                                            | . 18 |

| Figure 5. Open-Trace Detection in MAX25608E                                | 20   |

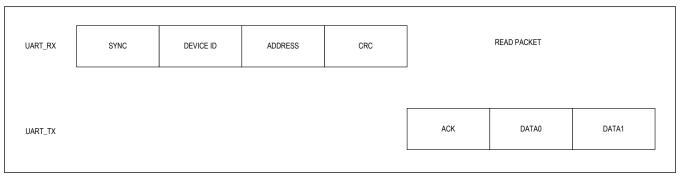

| Figure 6. Back-to-Back Write/Read Packets for MAX25608/MAX25608C/MAX25608E | 22   |

| Figure 7. Back-to-Back Read Packet Format for MAX25608B                    | 22   |

| Figure 8. Back-to-Back Write Packet Format for MAX25608B                   | 22   |

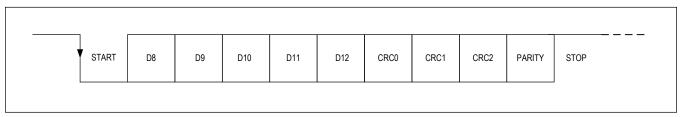

| Figure 9. Frame Format                                                     | 23   |

| Figure 10. Interframe Format                                               | 23   |

| Figure 11. Rx Rise Time and Fall Time                                      | 23   |

| Figure 12. SYNC Frame                                                      | 24   |

| Figure 13. ACK Frame                                                       | 24   |

| Figure 14. Device ID and Address Frame                                     | 25   |

| Figure 15. Write Packet                                                    | 25   |

| Figure 16. Read Packet                                                     | 25   |

| Figure 17. Final Frame                                                     |      |

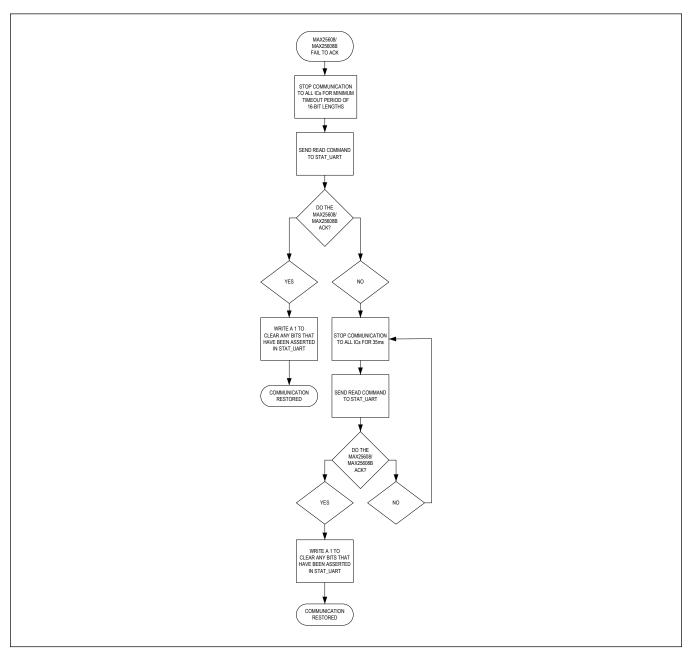

| Figure 18. Timeout Flowchart                                               |      |

|                                                                            |      |

### MAX25608

# 12-Switch, High-Brightness LED Matrix Manager for Automotive Front Lights

| LIST OF TABLES                           |    |

|------------------------------------------|----|

| Table 1. Device ID Table                 | 14 |

| Table 2. RADDR/RGRADE Recommended Values | 15 |

### **Absolute Maximum Ratings**

| IN to GND              | 0.3V to +65V  | RTEMP, RGRADE, CLKIN, CLKOUT, R           | ADDR to GND0.3V to               |

|------------------------|---------------|-------------------------------------------|----------------------------------|

| V <sub>DD</sub> to GND | 0.3V to +2.5V |                                           | V <sub>VDD</sub> + 0.3V          |

| CPN to GND             |               | RX, TX, FLT to GND                        | 0.3V to +6V                      |

| CPP to GND             | 0.3V to +70V  | Continuous Power Dissipation (multilated) | yer board) $(T_A = 70^{\circ}C,$ |

| CPP to CPN             | 0.3V to +6V   | derate 40.57mW/°C above +70°C)            | 3245.44mW                        |

| CPP to DRx             | 0.3V to +70V  | Operating Temperature Range               |                                  |

| DR12 to GND            | 0.3V to +65V  | Junction Temperature                      | +150°C                           |

| DRx to DR(x-1)         | 0.3V to +16V  | Storage Temperature Range                 |                                  |

| DR6 to GND             | 0.3V to +65V  | Soldering Temperature (reflow)            |                                  |

| SRCx to GND            | 0.3V to +65V  | · , , ,                                   |                                  |

|                        |               |                                           |                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **28 TSSOP**

| Package Code                           | U28E+6C   |

|----------------------------------------|-----------|

| Outline Number                         | 21-0108   |

| Land Pattern Number                    | 90-100175 |

|                                        | 30-100170 |

| Thermal Resistance, Four-Layer Board:  |           |

| Junction to Ambient (θ <sub>JA</sub> ) | 24.6°C/W  |

| Junction to Case (θ <sub>JC</sub> )    | 1.5°C/W   |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = 5V, T_A = T_J = -40^{\circ}C$  to +125°C (<u>Note 1</u>), unless otherwise noted. Limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                      | MIN  | TYP    | MAX  | UNITS |

|--------------------------------------------------|---------------------|-----------------------------------------------------------------|------|--------|------|-------|

| SUPPLY VOLTAGES                                  |                     |                                                                 |      |        |      |       |

| Supply Voltage                                   | V <sub>IN</sub>     | Operating voltage range                                         | 4.0  |        | 60   | V     |

| Input Current                                    | I <sub>IN</sub>     | V <sub>IN</sub> = 5V                                            |      | 4.2    | 6    | mA    |

| Input POR Threshold                              | V <sub>IN-POR</sub> | V <sub>IN</sub> rising                                          | 3.6  |        | 3.9  | V     |

| Charge Pump DRAINn<br>Input Current              | I <sub>INQP</sub>   |                                                                 |      |        | 6    | mA    |

| Charge-Pump Operating Voltage                    | V <sub>CPP</sub>    |                                                                 |      |        | 65   | V     |

| VDD_UVLO Rising<br>Threshold                     | UVLO_R_TH           |                                                                 | 1.61 |        | 1.69 | V     |

| VDD_UVLO Falling<br>Threshold                    | UVLO_F_TH           |                                                                 | 1.54 |        | 1.63 | V     |

| LED DIMMING                                      |                     |                                                                 | •    |        |      |       |

| Internal Oscillator<br>Frequency                 | fosc                | Used for charge pump and PWM dimming of LEDs                    |      | 16.384 |      | MHz   |

| LED PWM Dimming<br>Frequency Range               | f <sub>DIM</sub>    |                                                                 | 100  |        | 2000 | Hz    |

| LED SWITCHES                                     |                     |                                                                 | •    |        |      |       |

| Single-Switch On-<br>Resistance                  | R <sub>DSON</sub>   |                                                                 |      | 0.060  |      | Ω     |

| On-Resistance with<br>Series Switches 6–1 on     |                     |                                                                 |      | 0.36   | 0.75 | Ω     |

| On-Resistance with<br>Series Switches 12–7<br>on |                     |                                                                 |      | 0.36   | 0.75 | Ω     |

| Open LED Threshold                               | VOTH                | VOTH code = 0x0                                                 | 12.0 | 14.0   | 15.0 | V     |

| (Rising)                                         | VOTH                | VOTH code = 0x1                                                 | 8.3  | 9.33   | 10.0 | V     |

|                                                  |                     | VSTH code = 000                                                 | 1.26 | 1.40   | 1.54 |       |

|                                                  |                     | VSTH code = 001                                                 | 3.24 | 3.6    | 3.96 |       |

|                                                  |                     | VSTH code = 010                                                 | 3.6  | 4.00   | 4.4  |       |

| Short LED Threshold                              | VSTH                | VSTH code = 011                                                 | 4.95 | 5.5    | 6.05 | - V   |

| (Rising)                                         | ٧٥١١١               | VSTH code = 100                                                 | 5.4  | 6.0    | 6.6  |       |

|                                                  |                     | VSTH code = 101                                                 | 5.94 | 6.6    | 7.26 |       |

|                                                  |                     | VSTH code = 110                                                 | 6.48 | 7.2    | 7.92 |       |

|                                                  |                     | VSTH code = 111                                                 | 6.93 | 7.70   | 8.47 |       |

| Maximum Switch<br>Current                        | I <sub>SW</sub>     | Thermally limited                                               |      | 1.6    |      | А     |

| LED Slew-Rate Setting 0                          | SR_LED_0            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x0 |      | 160    |      | μs    |

| LED Slew-Rate Setting 1                          | SR_LED_1            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x1 |      | 81     |      | μs    |

| LED Slew-Rate Setting 2                          | SR_LED_2            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x2 |      | 48     |      | μs    |

### **Electrical Characteristics (continued)**

$(V_{IN} = 5V, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$  (<u>Note 1</u>), unless otherwise noted. Limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.)

| , -                                  |                     |                                                                 |                          |        |      |       |

|--------------------------------------|---------------------|-----------------------------------------------------------------|--------------------------|--------|------|-------|

| PARAMETER                            | SYMBOL              | CONDITIONS                                                      | MIN                      | TYP    | MAX  | UNITS |

| LED Slew-Rate Setting 3              | SR_LED_3            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x3 |                          | 26     |      | μs    |

| LED Slew-Rate Setting 4              | SR_LED_4            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x4 |                          | 17     |      | μs    |

| LED Slew-Rate Setting 5              | SR_LED_5            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x5 |                          | 10     |      | μs    |

| LED Slew-Rate Setting 6              | SR_LED_6            | 0 to 6V step, 10% to 90% rise/fall time,<br>LED_SLEW[2:0] = 0x6 |                          | 5.0    |      | μs    |

| Open Trace Threshold                 |                     | Minimum current required to detect open trace (MAX25608E)       |                          |        | 260  | mA    |

| DIGITAL INPUTS - CLKI                | N, Rx               |                                                                 |                          |        |      |       |

| Input High Voltage                   | V <sub>IH</sub>     |                                                                 | 1.4                      |        | _    | V     |

| Input Low Voltage                    | V <sub>IL</sub>     |                                                                 |                          |        | 0.4  | V     |

| CLKIN Input Frequency                | f <sub>CLK</sub>    |                                                                 | 0.30                     |        | 20.0 | MHz   |

| DIGITAL OUTPUTS - Tx                 |                     | Τ                                                               |                          |        |      | •     |

| Output Low Voltage                   | V <sub>OL</sub>     | I <sub>SINK</sub> = 2mA                                         |                          |        | 0.4  | V     |

| CLKOUT High Voltage                  | V <sub>OH</sub>     | I <sub>SRC</sub> = 2mA                                          | V <sub>DD</sub> -<br>0.4 |        |      | V     |

| THERMAL SHUTDOWN                     |                     |                                                                 |                          |        |      |       |

| Thermal Warning<br>Threshold         | TH_WARN             | Rising temperature                                              |                          | 140    |      | °C    |

| Thermal Warning<br>Hysteresis        |                     |                                                                 |                          | 15     |      | °C    |

| Thermal Shutdown                     | TH_SHDN             | Rising temperature                                              |                          | 165    |      | °C    |

| Thermal Shutdown<br>Hysteresis       | HYS_SHDN            |                                                                 |                          | 15     |      | °C    |

| CHARGE PUMP                          |                     |                                                                 |                          |        |      |       |

| Charge-Pump<br>Frequency             | f <sub>CPP</sub>    |                                                                 |                          | 16.384 |      | MHz   |

| Charge-Pump Output<br>Voltage        | V <sub>O</sub>      | V <sub>CPP</sub> - V <sub>CPN,</sub> I <sub>CPP</sub> = 350μA   | 3.7                      |        | 6.0  | V     |

| Charge-Pump Power-<br>Good Threshold | V <sub>CPP_OK</sub> | Rising threshold                                                |                          | 4.0    |      | V     |

| UART TIMING                          |                     |                                                                 |                          |        |      |       |

| UART Write Bit Rate                  | F <sub>UART</sub>   | MAX25608/MAX25608B/MAX25608C/<br>MAX25608E                      | 10                       |        | 950  | kbps  |

| LIART Road Dit Rate                  | <b>F</b>            | MAX25608/MAX25608C/MAX25608E                                    | 10                       |        | 950  | lehno |

| UART Read Bit Rate F <sub>UART</sub> | MAX25608B 10        |                                                                 | 10                       | 580    |      | kbps  |

Note 1: The MAX25608 and MAX25608B/C/E are designed for continuous operation up to  $T_J$  = +125°C for 95,000 hours and  $T_J$  = +150°C for 5000 hours.

## **Pin Configuration**

## **Pin Description**

| PIN   | NAME            | FUNCTION                                                                                                                                                                             |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | RADDR           | Device ID Resistor. Connect a resistor value from RADDR to GND to set the UART Device ID.                                                                                            |

| 2     | RGRADE          | LED Binning Resistor Connection. Connect a LED binning resistor from this pin to GND.                                                                                                |

| 3, 26 | RX              | UART Receive Input. If the driver to this pin is CMOS output, no pull-up resistor is needed. If the driver to this pin is open drain, add a $1.5 \mathrm{k}\Omega$ pull-up resistor. |

| 4, 25 | TX              | UART Transmit Output. Add a 1.5kΩ pull-up resistor.                                                                                                                                  |

| 5     | CLKIN           | CLK Input. Can be optionally used to sync the device with an external digital clock signal.                                                                                          |

| 6     | RTEMP           | NTC Divider ADC Input. Connect to NTC resistor divider to enable remote temperature sensing.                                                                                         |

| 7     | V <sub>DD</sub> | LDO Output. Nominal voltage is 1.8V. Connect a bypass capacitor between V <sub>DD</sub> and GND.                                                                                     |

| 8     | DR12            | Drain of Internal Switch 12. Add a 0.1µF capacitor from DR12 to GND.                                                                                                                 |

| 9     | DR11            | Drain of Internal Switch 11.                                                                                                                                                         |

| 10    | DR10            | Drain of Internal Switch 10.                                                                                                                                                         |

| 11    | DR9             | Drain of Internal Switch 9.                                                                                                                                                          |

| 12    | DR8             | Drain of Internal Switch 8.                                                                                                                                                          |

| 13    | DR7             | Drain of Internal Switch 7.                                                                                                                                                          |

| 14    | SRC7            | Source of Internal Switch 7.                                                                                                                                                         |

| 15    | DR6             | Drain of Internal Switch 6. For two-string applications, connect a 0.1µF ceramic capacitor from DR6 to GND.                                                                          |

| 16    | DR5             | Drain of Internal Switch 5.                                                                                                                                                          |

| 17    | DR4             | Drain of Internal Switch 4.                                                                                                                                                          |

| 18    | DR3             | Drain of Internal Switch 3.                                                                                                                                                          |

| 19    | DR2             | Drain of Internal Switch 2.                                                                                                                                                          |

| 20    | DR1             | Drain of Internal Switch 1.                                                                                                                                                          |

| 21    | SRC1            | Source of Internal Switch 1.                                                                                                                                                         |

| 22    | CPP             | Charge Pump Capacitor Positive Connection. Connect a 0.1µF ceramic capacitor from CPP to CPN.                                                                                        |

| 23    | CPN             | Charge Pump Capacitor Negative Connection. Connect a 0.1µF from CPP to CPN.                                                                                                          |

| 24    | CLKOUT          | After startup, can be optionally configured with UART to drive a clock signal to other devices, or act as a pass-through for the CLKIN input.                                        |

| 27    | FLT             | Open-Drain Fault Indicator. Goes low when a fault condition is present.                                                                                                              |

| 28    | IN              | Connect external bypass capacitor to GND.                                                                                                                                            |

| _     | EP/GND          | Exposed Pad Ground Connection. Connect this pad to a contiguous ground plane.                                                                                                        |

### **Functional Diagrams**

#### MAX25608 Block Diagram

#### MAX25608B Block Diagram

#### MAX25608C/E Block Diagram

#### **Detailed Description**

#### Power-on Reset and VDD UVLO

Once the IC is powered, an internal power-on reset (POR) signal sets all the registers to their default states. All twelve switches are in the on state upon a POR (all LEDs are off). The LEDs remain off until a command is received by the UART. To ensure reliable operation, the IN supply voltage ( $V_{IN}$ ) must be greater than  $V_{IN-POR}$ . If  $V_{IN}$  falls below  $V_{IN-POR}$  and the  $V_{DD}$  regulator output falls below VDD\_UVLO, the registers reset to their default state. The IN voltage must be greater than  $V_{IN-POR}$  and  $V_{DD}$  must be above VDD\_UVLO for proper operation. The bypass switches remain in their default on state until the UART is used to enable LED dimming.

#### Internal Switches

Each switch connected between DRAINn and DRAINn-1 has a typical on-resistance of  $0.06\Omega$ . This measurement includes the on-resistance of the internal switch and the resistance of the bond wires to the DRAINn and DRAINn-1 pads. Each bypass switch, when driven to an off state, allows the string current to flow through the corresponding parallel-connected LED, turning the LEDs on. Driving the bypass switch to an on state shunts the current through the bypass switch and turns the LEDs off. Each bypass switch can have one, two, or three LEDs in series across it.

#### **Power-up Sequence**

To avoid LED flash while turning ON the power in the system, proper power up sequence has to be followed. First, the matrix manager device MAX25608/MAX25608B/MAX25608C/MAX25608E power must be applied. The device comes up with all the switches ON as soon as it is powered up. The bit SW\_GO\_EN in register SW\_GO (0x01) is 0. The current source driving the LEDs should be enabled after that and so now the current will flow through the closed switches of the device and LEDs will not light up. After that, the required PWM duty cycle can be set up through the UART interface and then the SW\_GO\_EN is set to 1. This way, the LEDs light up with the required duty cycle.

When the device is running and if the LED current source is disconnected/broken for some reason, the LEDs can light up because of the bias currents flowing through the source/drain pins of the device. The total bias current seen can be close to  $180\mu A$  on the bottom-most switch drain pin. To avoid the lighting up of the LEDs,  $10k\Omega$  resistors can be added across the switches, if needed. This case of undesired LED lighting up can also be managed by setting the SW\_GO\_EN bit to 0 when there is a fault from the current source.

#### Spread Spectrum

The MAX25608 has spread spectrum turned on in the charge pump oscillator clock for better EMI performance. The MAX25608B/C/E have spread spectrum turned off on the charge pump oscillator. The proprietary charge pump design gives a good EMI performance even without the spread spectrum option. Spread spectrum is internally turned OFF when a UART transaction happens. When an external clock is used, spread spectrum is used only for the charge pump in the spread-spectrum enabled device (MAX25608). PWM uses the external clock when the external clock is applied instead of internal clock.

The MAX25608 device that has spread spectrum on may show flicker at a duty cycle of <5%. For <5% duty cycle applications with full duplex UART communication, use the MAX25608C/E to avoid flicker.

#### **Programming Options**

#### Pin Resistor Decode Table

Multiple devices can be used in a multidrop UART bus with an external  $\mu$ C acting as the controller. The resistor on RADDR is used to program the UART device ID.

#### **Table 1. Device ID Table**

| DECODED VALUE OF RADDR RESISTOR | DEVICE ID |

|---------------------------------|-----------|

| 0x0                             | 0x0       |

| 0x1                             | 0x1       |

**Table 1. Device ID Table (continued)**

| DECODED VALUE OF RADDR RESISTOR | DEVICE ID |

|---------------------------------|-----------|

|                                 |           |

| 0xF                             | 0xF       |

#### **Resistor Programming Table**

A resistor connected between pins RADDR and GND is used to configure the device ID, and the resistor connected between pins RGRADE and GND is used for LED binning. The IC provides 16 levels of detection between 0 and 1.2V on RADDR/RGRADE pins. The pins source  $400\mu\text{A}$ , allowing the use of an external resistor between RADDR/RGRADE and GND to set the voltage level. See Table 2 for recommended RGRADE/RADDR resistor values.

Table 2. RADDR/RGRADE Recommended Values

| RGRADE/RADDR[3:0] DECODE VALUE | RGRADE/RADDR RESISTOR VALUE (Ω, 1%) |

|--------------------------------|-------------------------------------|

| 0000                           | 95                                  |

| 0001                           | 200                                 |

| 0010                           | 309                                 |

| 0011                           | 422                                 |

| 0100                           | 536                                 |

| 0101                           | 649                                 |

| 0110                           | 768                                 |

| 0111                           | 909                                 |

| 1000                           | 1050                                |

| 1001                           | 1210                                |

| 1010                           | 1400                                |

| 1011                           | 1620                                |

| 1100                           | 1870                                |

| 1101                           | 2150                                |

| 1110                           | 2490                                |

| 1111                           | 2870                                |

#### **PWM Dimming**

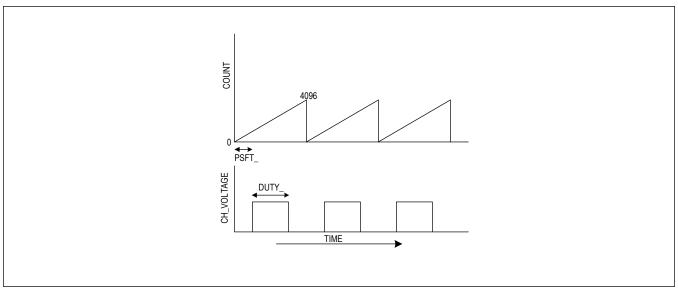

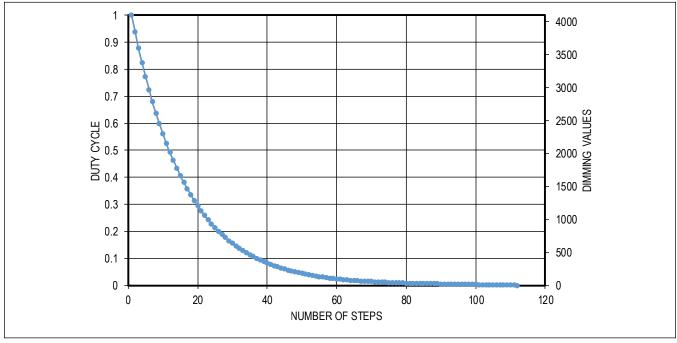

The IC provides 12-bit programmable dimming on each individual switch. An internal 12-bit counter (COUNT) is generated according to the clock settings. The switch turns off when COUNT is equal to the delay set by the corresponding PSFT register and stays off until the COUNT exceeds the sum of PSFT and PWM duty-control registers. In this way, the duty cycle and relative phase shift of the individual switches can be set independently (see Figure 1).

Figure 1. PWM Dimming

#### **PWM Clock and Synchronous Operation with Multiple Devices**

The PWM clock for the IC can be selected from the internal oscillator or from an external clock source driving the CLKIN pin. When an external clock is applied, only the PWM generation uses this clock. The CLKOUT pin can be configured to pass either the CLKIN or the internal oscillator as an output to other devices. In this manner, a single clock signal can be used to synchronize all devices. The PWM clock source and CLKIN/CLKOUT function are configured through PWM\_CLK[1:0] in the CNFG\_GEN (0x02) register. The default value is from the internal oscillator with the CLKIN and CLKOUT disabled. When the part is configured for external clock and if the external clock is missing, the part automatically switches to the internal clock.

PWM dimming frequency is programmable by setting the value of the DIV[1:0] bits in the CNFG\_GEN (0x02) register, which sets the divide ratio for both the internal (16.38MHz) and external clock sources. Note that if a different external clock source is used, the PWM frequency will scale as a ratio of internal (16.38MHz) to external clock frequency for a fixed frequency divider value.

Synchronized operation with multiple devices is achieved through the following steps:

- 1. Set the SW GO EN bit to 0.

- 2. Select the controller device based on the resistor on RADDR pin and set the PWM\_CLK[1:0] bits in the CNFG\_GEN (0x02) register to use the internal oscillator and CLKOUT active.

- 3. Select the peripheral devices individually based on the resistor on RADDR pin and set the PWM\_CLK[1:0] bits in the CNFG\_GEN (0x02) register to keep the CLKIN and CLKOUT active. Connect the CLKOUT of the controller device to the CLKIN of the first peripheral device and the CLKOUT of the first peripheral device to the CLKIN of the 2nd peripheral device and so on.

- 4. Use the Global write command to set the SW\_GO\_EN bit to 1. All the PWM clocks of the devices will be synchronized now.

#### **Dimming With and Without Fade**

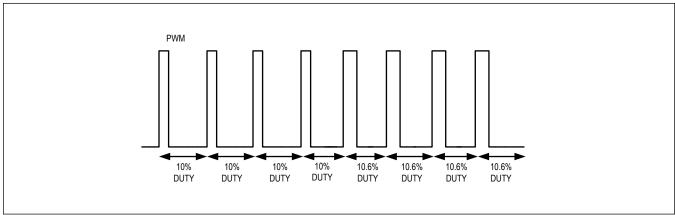

Each switch of the IC can be independently programmed to perform dimming without fade transition or dimming with fade transition. For dimming without fade transition, the dimming changes from the initial value to the target value in one dimming cycle. For dimming with fade transition, the dimming changes transitionally step by step, starting from the initial value to the target value in multiple dimming cycles, following a predetermined exponential curve.

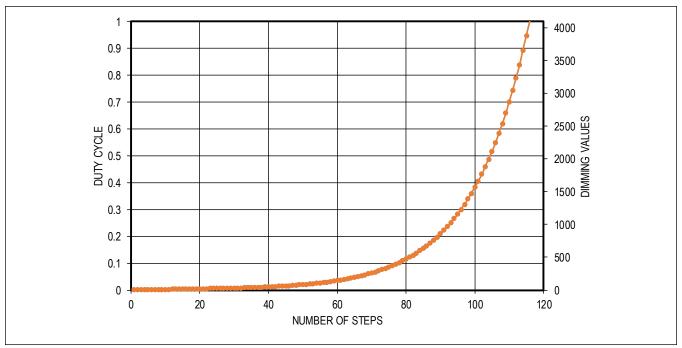

To enable dimming with fade transition, set the FADE bit to 1 and the DUTY bits to the target value for the specific switches. Each transitional step value is calculated using 12 bits according to the following formula:

DUTYnext = DUTYnow x CF

where DUTY is the duty cycle expressed as an integer value between 1 and 4096 (12-bit resolution), and CF is the constant factor.

CF = 1.0625 and CF = 0.9375 for an up transition and down transition, respectively.

DUTYnext continues to be updated according to the formula until DUTYnext reaches the target value.

For example, as shown in Figure 2, if a command is sent to increase the duty cycle from 10% to 20% updating every four PWM cycles, then the next duty cycle will be 409 x 1.0625 = 434, or 10.6% duty. This value will be held for four PWM cycles, and then would be updated again to 461 (11.25% duty).

Figure 2. Starting from 10% Duty, Updating Every Four PWM Cycles

The number of dimming cycles that the duty cycle is held for is defined by the TDIM\_ register for the switch. The number of transitional steps depends on the distance between the initial value and the target value. The maximum number of transitional steps from 1/4096 to 4096/4096 is 146 steps. See <u>Figure 3</u> for the up-transition curve. The maximum number of transitional steps from 4096/4096 to 1/4096 is 123 steps. See <u>Figure 4</u> for the down-transition curve.

Each step runs TDIM\_PWM dimming cycles, and each dimming cycle consists of 8,192 clock cycles by default, therefore t<sub>STEP</sub> = TDIM\_x 8,192. The 8,192 clock cycles timer can also be changed to 16,384, 32,768, or 65,536 clock cycles by programming bits [3:2] in register address 0x02.

Figure 3. Up-Transition Curve

Figure 4. Down-Transition Curve

#### **RTEMP**

The RTEMP pin is an auxiliary 8-bit ADC input that is suitable for use with an external NTC resistive divider for monitoring external temperature. In this way, a remote NTC resistor can be used to monitor the external LED temperature for current derating and system monitoring. The 8-bit code is updated with a period of 200 microseconds and can be read back

using the UART RTEMP register (0x15).

#### **Fault Pin Behaviour**

The FLT pin will assert whenever one or more of these conditions is present:

- One or more floating domain gate drivers have detected an open-LED fault; in this case, the switch(es) with Open LED faults remain closed until the power is reset

- One or more floating domain gate drivers have detected a short-LED fault condition

- Thermal warning/shutdown

- RGRADE pin is open, shorted to ground, or out of range

- UART errors happen

#### **LED Fault Detection and Protection**

The IC is able to detect a shorted LED and an open LED. To detect and report a LED fault, several conditions must be met. First, the LED switch must be operating, then the duty cycle must be greater than 0 since both LED-open and LED-short detection require the switch to be open. Open-fault detection is possible with a PWM duty cycle of 100% and short detection is not possible with 100% PWM duty cycle. For 100% PWM duty cycle requirements, the duty cycle may be set to 99.9% or lower to detect short LED faults. In general, it takes up to one dimming cycle to make sure these conditions have been met after a fault condition is applied. This period depends on the PWM dimming frequency.

#### **LED Open-Fault Detection and Protection**

An open-LED fault is triggered when the voltage between the individual LED switch DRAIN node and switch SOURCE node exceeds V<sub>OTH</sub> and is reported in register OPEN\_LED\_STAT (0x13). The switch is closed when an open-LED is detected and remains closed. By default, the open fault results in the FLT pin being driven low; however, open faults can be masked by writing 0b1 to the MSK\_OPEN\_LED bit in the CNFG\_MSK (0x0C) register. If an open-LED fault is detected multiple times, it is recommended that the OPEN\_LED\_OVRD (0x09) register be updated to force the corresponding LED switch to remain closed continuously to provide a bypass for the faulty LED.

For applications with 1 LED across the switch, use the open threshold setting as either 9.33V (typ) or 14V (typ). For applications with 2 or 3 LEDs across each switch, use the open threshold setting of 14V (typ).

#### Resetting Slew Rate, Open, and Short Threshold Registers with VIN Cold Crank

When a cold-crank event happens, the input supply to the IC can go down to around 1.5V and come back up. The slew rate, open, and short threshold registers need to be reset properly in this condition.

After a  $V_{IN}$  cold-crank event, send a write command to the CNFG\_GEN\_1 register that has a change in at least 1 bit, and then resend the required data. This ensures that the part operates with the intended register values after a cold-crank event.

#### **LED Short Detection**

A short-LED fault is triggered when the voltage between the switch DRAIN node and the switch SOURCE node is below  $V_{STH}$  for an open switch condition, and is reported in the SHRT\_LED\_STAT (0x12) register. The LED short comparator is sampled at the end of each LED pulse to avoid false detections during the beginning of the pulse. No action is taken with the switch in response to detecting a short-LED fault, thus continuing to operate as programmed. The short fault, by default, results in FLT being driven low; however, short faults can be masked by writing 0b1 to MSK\_SHRT\_LED in the CFG\_MSK (0x0C) register.

The Low Duty Threshold register (0x16) is used to filter out LED fault signals during short duty cycles when the voltage across the switch might not settle to a final value, causing an invalid detection of the Short LED condition. When the DUTY register of a switch is less than LOW\_DUTY\_TH, the SHORT\_LED signal is masked and SHORT\_LED\_STAT is not asserted for that switch.

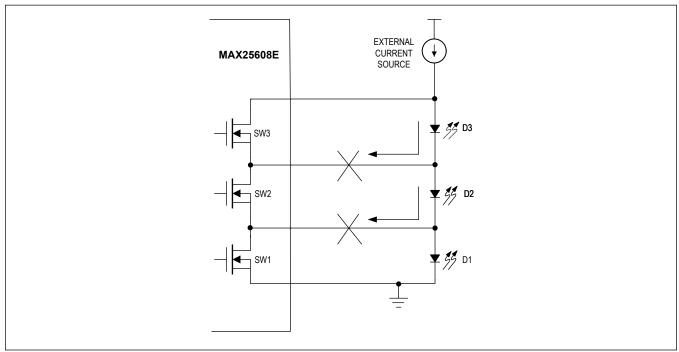

#### Open-Trace Detection (MAX25608E Only)

An open-trace fault is triggered when the current through the closed switch is less than 230mA (max) and is reported in the OPEN\_TRACE\_STAT (0x14) register. No action is taken with the channel switch in response to detecting an open trace with it continuing to operate as programmed. By default, the open-trace fault results in the FLT output being

driven low; however, open-trace faults can be masked by writing 0b1 to MSK\_OPEN\_TRACE in the CNFG\_MSK (0x0C) register.

The open-trace fault is sampled before the rising PWM edge, which is the edge turning the switch from on to off. If there is an open trace to the drain side of the switch, the switch above it has to be open during the PWM rising edge of the switch that is detecting the condition. For example, if there is an open trace on the drain side of SW2, as shown in <a href="Figure 5">Figure 5</a>, then switch SW3 must be open when SW2 is turning off and, similarly, for detecting an open-trace condition on the drain of SW1 (SW2 must be open when SW1 is turning off). For the top-most switch SW3 drain connection and the bottom most switch source connection, there is no constraint to detect the open-trace condition.

Figure 5. Open-Trace Detection in MAX25608E

#### **Unused Switches and Pins**

If some of the switches in the IC are unused, it is recommended to SHORT the pins of the unused switches together and leave it open (do not connect to ground). All of the faults associated with these unused switches should be masked using the appropriate bits in CNFG\_MSK\_LED.

If the RTEMP/RGRADE pin is unused, connect it to ground.

The CLKIN pin should be grounded, except for the applications when it is needed to synchronize to an external clock.

The CLKOUT pin should be left floating if the part is used independently. For applications with more than one part, see the *PWM Clock and Synchronous Operation with Multiple Devices* section.

#### Thermal Shutdown

The IC features an on-chip temperature-protection circuit to prevent the device from overheating.

When the die temperature rises above the thermal-warning threshold (+140°C), the TH\_WARN bit is set, causing the FLT pin to be asserted but no action taken with the switches. If asserted, the FLT pin remains asserted until the die temperature drops below the thermal-warning threshold, and the TH\_WARN register bit is cleared by writing a 1. To clear the TH\_WARN bit, the die temperature must be below the thermal-warning threshold. The UART communication works as usual when the part hits thermal warning threshold.

When the die temperature rises above the thermal-shutdown threshold (+160°C), the TH SHDN bit in STAT GEN

register (0x10) is set, causing the FLT pin to be asserted and all switches to either be closed (LEDs turned off) or opened (LEDs turned on), depending on the value of the TH\_SHDN\_ACT bit in CNFG\_MSK\_GEN (0x0C) register. The UART communication is active but the switches remain either open or closed till the thermal shutdown hysteresis level is reached. When the device recovers from thermal shutdown, it resumes operation from where it was before the thermal shutdown. The FLT pin remains asserted until the die temperature drops below the thermal-warning threshold, and both the TH\_WARN and TH\_SHDN bits are cleared in the STAT\_GEN (0x10) register by writing 1 to both bits. The TH\_WARN and TH\_SHDN status bits are cleared on write.

#### **PCB Layout**

Careful PCB layout is critical to achieve clean, stable operation. Follow these guidelines for good PCB layout:

- 1. The bypass capacitors on pins IN and VDD should be close to the devices. The exposed pad is the ground of the device, and the bypass capacitors should be connected to this ground.

- 2. The charge pump capacitor between pins CPP and CPN should be close to the device and traces should be short.

- 3. Connect a 100nF decoupling capacitor on DR12 pin for single-string application. Connect a 100nF decoupling capacitor on DR12 and DR6 pins for dual-string applications.

- 4. The connection from the current source (LED driver) to the LEDs should be done so that the high LED currents do not flow in the ground of the MAX25608 matrix IC board. For example, if the LEDs and the MAX25608 IC are on the same board, the return LED current from the bottom-most LED or the bottom switch between DR1 and SRC1 should be returned through a separate trace to the connector going to the LED driver board. This ensures that high LED currents do not flow in the MAX25608 IC board. Do not connect the SRC1 pin to the ground of the MAX25608 IC board.

- 5. For applications where the current source is in the same board as the MAX25608 IC, do not connect SRC1 pin to the exposed pad ground of the MAX25608 IC. The SRC1 pin switch current should return to the LED driver current source through a ground plane without affecting the ground of the MAX25608 IC.

#### **UART Serial Interface**

#### Overview

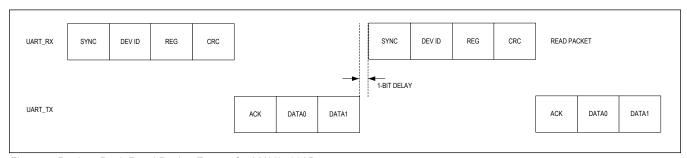

The MAX25608/MAX25608C/MAX25608E include a full-duplex UART serial interface and the MAX25608B includes a half-duplex (supports CAN physical layer) UART serial interface to enable fully programmable matrix manager functionality. The system ECU/MCU acts as the UART controller, driving read/write packets on the Rx line and receiving packets on the Tx line. The Rx and Tx lines can connect up to 16 devices on a common bus using a star topology. The device address of each IC is pin-programmable using an external resistor to ground on the RADDR pin. Devices can be addressed individually using their Device ID[3:0]. They can also be simultaneously addressed using the General Call ID or by using the programmable Cluster Call ID value.

The baud rate of incoming UART packets on Rx is automatically detected by the device, from a minimum of 10kbps up to a maximum of 950kbps. The device then returns frames on the Tx line at the same baud rate, according to the packet format described in the <u>UART Frame Format</u> section.

#### **Device Connections**

The UART interface ensures compatibility with standard microcontrollers from a variety of manufacturers. The MAX25608B also enables the use of CAN transceivers for applications where the matrix manager is remote from the microcontroller. The Rx line should be driven by the microcontroller controller. It can be connected to an individual device or to multiple devices in a star topology. The Tx line is an open-drain output. Multiple devices can share the same Tx connection as well. No external timing reference is required, the device automatically detects the bit rate on each Rx packet and adjusts the bit rate of the Tx response accordingly.

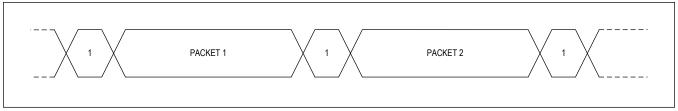

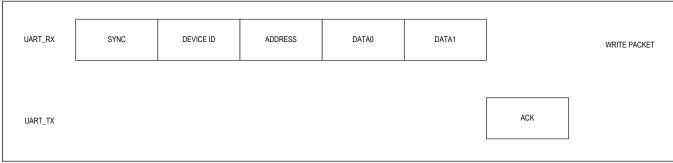

#### **UART Packet Format**

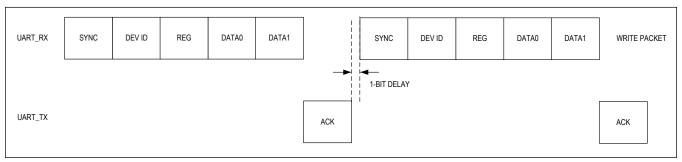

The MAX25608/MAX25608E features full-duplex UART communication capabilities—it is able to send and receive data at the same time. Read and write packets can be sent back to back with a minimum delay of at least one bit period between each packet, as shown in <u>Figure 6</u>. This format should also be followed for global/cluster commands for the MAX25608B. The 1-bit length delay is not needed if using two stop bits.

Spacing of one stop bit (1-bit length) between packets is needed.

Figure 6. Back-to-Back Write/Read Packets for MAX25608/MAX25608C/MAX25608E

For the MAX25608B version, if using individual write or read commands, the next message may be sent only after the response frames have concluded and after a delay of 1-bit length. This means that for an individual write command, the next message may be sent after the ACK frame has concluded and after a 1-bit length delay, while for a read command the next message may be sent after the three response frames have been sent and a 1-bit delay length. This format is illustrated in Figure 7 and Figure 8.

Figure 7. Back-to-Back Read Packet Format for MAX25608B

Figure 8. Back-to-Back Write Packet Format for MAX25608B

#### **UART Frame and Interframe Format**

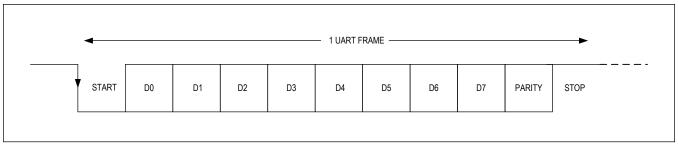

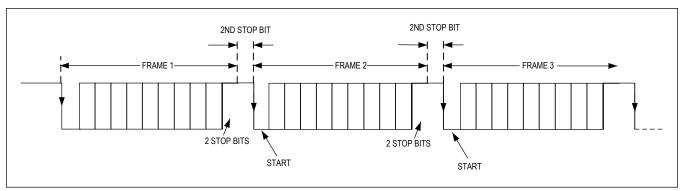

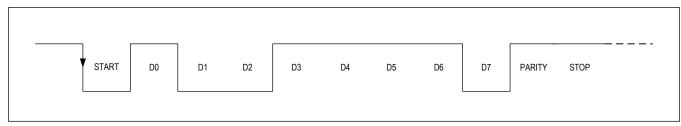

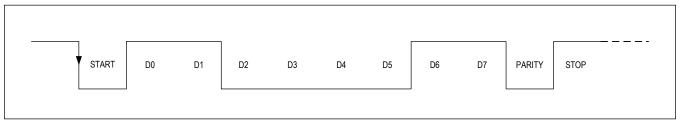

Read/write packets are composed from multiple UART frames. Each frame consists of one start bit, eight data bits, one parity bit (even), and two stop bits. The parity bit will be high if the number of ones in the data bits is odd, otherwise it will be low.

Figure 9. Frame Format

Figure 10. Interframe Format

Between frames, there should be no delay between the second STOP bit and the start of the next frame START bit. If there is a delay between second STOP bit and the start of the next frame START bit, the delay should not exceed 0.5x the bit length minus 350ns. For example, if the baud rate is 950kbps, the delay should not exceed 176ns, and for a baud rate of 500kbps the delay should not exceed 650ns. If these conditions are violated, a bit-sampling error may occur. This will result in a failure to ACK and an assertion of one or more of the following STAT\_UART bits: RX\_CRC\_ERR, RX\_PL\_STOP\_ERR.

#### **Rx Rise and Fall Times**

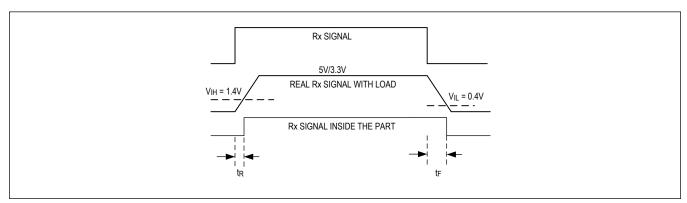

When the Rx line is driving many of the devices (16x maximum devices can be connected), the capacitive loading on the Rx line becomes high, causing the rise and fall times to become longer. As shown in Figure 11, the Rx bit length generated inside the part is different than the real Rx bit length. If the difference between  $t_R$  and  $t_F$  starts to become longer than 30ns, the device will extract a slower baud rate. If longer rise and fall times cannot be avoided, a lower baud rate may be selected, or a buffer may be used to reduce the rise and fall times.

Figure 11. Rx Rise Time and Fall Time

#### **Synchronization and Acknowledge Frames**

Each read/write packet must begin with a special Synchronization (SYNC) frame. This is a UART frame containing the data x79. The device synchronizes to the baud rate starting with the start bit of the SYNC frame. Once the falling edge of the start bit is detected, an internal frame counter is started. This counter counts the number of system clocks throughout the SYNC frame. Once the rising edge of D0 is detected, a second level counter starts and counts the number of system clocks until the next level shift. Once the system detects the falling edge of D0, the level counter is compared to one half of the frame counter. The level counter gets reset on the falling edge of D0, and the number of clocks from D1 to the rising edge of D3 are counted. Once the rising edge of D3 is detected, the system compares the level counter again to one half of the frame counter. This process is then repeated a third time for bits D3 through D6. The level counter and half of the frame counter are compared a third time. If all three comparisons are positive, the SYNC frame is accepted as valid, and the baud rate is determined as the frame counter divided by 8.

Figure 12. SYNC Frame

Each response packet always begins with a special Acknowledge (ACK) frame. This is a UART frame containing the data xC3.

Figure 13. ACK Frame

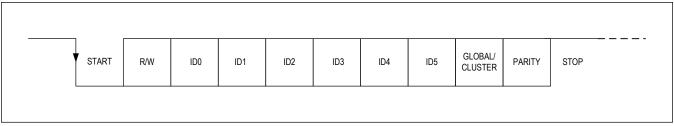

#### **Device ID and Address Frame Format**

Each device in the star configuration should be assigned a unique device ID number using the resistor connected to the RADDR pin. There are 16 possible device IDs that can be assigned in this way, from x00 to x0F (see Table 2).

In addition to addressing devices individually, the device also supports Global Call and Cluster Call write commands. A Global write command addresses all devices on the bus. A Cluster call addresses all devices with a matching cluster call ID in the CNFG\_UART register. To perform a Cluster call, first an individual write transaction must occur to assign a Cluster ID (CID) to a particular device (see CNFG\_UART (0x07)). After each device of interest is given a CID, a Cluster call may be performed by setting the Global/Cluster bit to 1, setting the R/W bit to 0, and writing the 6-bit CID. Data can then be written to all devices with a matching CID. To perform a Global call, set the Global/Cluster bit to 1, the R/W bit to 0, and the address bits to 0x00. This will address all devices on the bus. When performing a Global/Cluster call, the device will not respond with an ACK frame. Back-to-back Global/Cluster call write packets with a 1-bit length delay can be sent with the MAX25608B device. Read commands cannot use the Global/Cluster Call option and must be addressed to a specific device ID.

The address frame data bits are assigned as follows: the MSB is the Global/Cluster call bit, the next 6 bits are the device ID, and the LSB is the Read/Write bit.

Figure 14. Device ID and Address Frame

#### **Write Transactions**

Each write packet consists of five UART frames on the Rx pin. The first frame is the SYNC frame. The second frame consists of the Global/Cluster call flag, then the 6-bit device ID, and then the R/W bit. The R/W bit is low for a write command. The third frame is the register of the address being written to. The fourth frame is the lower byte of the data being written. The fifth and final frame includes the upper 5 bits of the data being written along with the 3-bit CRC code. Upon receiving a valid write packet, the device responds with an ACK frame on the Tx pin for an individual write.

Figure 15. Write Packet

#### **Read Transactions**

Each read command consists of four UART frames on the Rx pin. The first frame is the SYNC frame. The second frame consists of the Global/Cluster call bit set low, then the 6-bit device ID, and then the R/W bit set high. The third frame is the register address being written to, which is set by the RADDR value. The fourth and final frame includes the 3-bit CRC code, with the remaining 5 data bits set to 0. Upon receiving a valid read command, the device responds with three frames on the Tx pin. The first frame is the ACK frame. The second frame is the lower 8 data bits of the register being read. The third frame is the 3-bit CRC code, followed by the 5 MSBs of the register being read.

Figure 16. Read Packet

#### **CRC Error Checking**

Read/Write transactions are protected using a 3-bit cyclic redundancy check (CRC) on the packet. The CRC is provided

by the controller on last 3 data bits of each UART\_RX packet. For a write transaction, the CRC is calculated using: the 6 data bits of the second frame along with the Global/Cluster bit and the R/W bit, the data byte of the third frame, the data byte of the fourth frame, and the 5 data bits of the fifth frame for a write transaction. For a read transaction, the same process is followed, excluding the fifth frame of data as it is not included during a read transaction. Concerning the calculation of the CRC itself, the 3 bits to be appended are calculated using the LSB of each frame first in a descending order. Meaning that, starting with the second frame, the CRC is calculated starting with the LSB of the data bits of the frame, then moves on to the third, and then stops at the fourth (for a read transaction) or at the fifth (for a write transaction). For response frames on read packets, the device appends its own 3-bit CRC code to the 13-bit read data using the same polynomial.

The CRC calculation uses the polynomial  $x^3 + x^1 + 1$  with a starting value of 000.

Figure 17. Final Frame

The final frame contains the upper 5 bits of data and the 3 CRC bits.

#### **UART Watchdog Function**

The device UART Watchdog feature sets the switches into a preconfigured state in the event of UART communication bus failures. If the CNFG\_WATCHDOG bits are set to a nonzero value set, the device asserts a UART\_WATCHDOG fault when the UART\_RX pin has been inactive for more than the time set by the CNFG\_WATCHDOG bits. For lower baud rate applications, the watchdog timer should be configured to be longer than the spacing between the packets. The watchdog timer begins counting when there is no communication on the Rx line, including the space needed between the packets for the MAX25608B. When the UART\_WATCHDOG fault is set, the FLT output is asserted low, and the state of the channel switches is set to the value of the WD\_LED\_STATE register. The default value of WD\_LED\_STATE is x00, which opens all 12 switches in the event of a watchdog fault. The fault can be masked by setting the MSK\_UART\_ERR bit in the CNFG\_MASK\_GEN register. The fault status is cleared by writing a 1 to the UART\_WATCHDOG bit. When the fault status is cleared, the switches resume operation according to the values of the PWM registers.

#### **UART Communication Error Handling**

In the event that there is an error in communication on UART\_RX, it asserts the relevant fault status bit in STAT\_UART (x11) and asserts the FLT output. The UART communications faults can be masked by setting the MSK\_UART\_ERR bit. Faults are cleared by writing 1 to the STAT\_UART bits. The following communications errors result in fault assertion:

- UART Watchdog Timeout: UART\_RX stops transitioning for more than the time set by the CNFG\_WATCHDOG bits in the CONFG\_UART register.

- RX\_TIMEOUT\_ERR: If there is no communication on the Rx line for more than a 16-bit length between frames, this

bit will be asserted. If a watchdog timer is set by CNFG\_UART, the part will enter into the default LED state set by

CNFG\_WATCHDOG. Write a 1 to clear this fault to continue normal communication.

- RX\_CRC\_ERR: Invalid CRC code detected on a UART transaction.

- RX\_SYNC\_PERR: Parity error in the SYNC frame

- RX PL PERR: Parity error in the payload frame

- RX\_SYNC\_STOP\_ERR: Rx SYNC frame stop bit error.

- RX\_PL\_STOP\_ERR: Stop error bit detected in Rx data frames.

- RX\_PL\_START\_ERR: Start error bit detected in Rx data frames.

- Delay between frames exceeds half of a bit length minus 350ns.

#### **UART Timeout Conditions**

Timeout is defined as a period of time where the MAX25608/MAX25608B/MAX25608E do not acknowledge

#### MAX25608

### 12-Switch, High-Brightness LED Matrix Manager for Automotive Front Lights

any inputs from the Rx line. If the part has received an invalid SYNC frame, timeout will last the default 35ms. If the part has received a valid SYNC frame, but the interframe gap has exceeded 16 times the bit length, then timeout will last for only 16 times the bit length. When the MAX25608/MAX25608B/MAX25608C/MAX25608E enters timeout, any communication sent on the Rx line will cause the timeout period to reset. To bring the part out of timeout, no communication should be sent for the duration of the timeout period. After this time, communication can resume as normal. (See the Figure 18 flowchart for guidance on timeout conditions.) The following list shows under what conditions timeout will occur.

#### 35ms Timeout:

- RX\_SYNC\_PERR RX\_SYNC\_STOP

- Incorrect SYNC frame

#### 16x Bit Length Timeout:

RX TIMEOUT ERR-- This error will cause the switches to go to the state set by the WD LED STATE bits in the CNFG WATCHDOG register.

#### No Timeout:

- RX PL PERR

- RX\_PL\_START\_ERR

- RX PL STOP ERR

- RX\_CRC\_ERR

Analog Devices | 27 www.analog.com

#### **UART Timeout Flowchart**

Figure 18. Timeout Flowchart

### **Register Map**

#### MAX25608/MAX25608B/MAX25608C/MAX25608E

| ADDRESS  | NAME                     | MSB                  |                  |                        |                      |                       |                  |                  | LSB             |  |

|----------|--------------------------|----------------------|------------------|------------------------|----------------------|-----------------------|------------------|------------------|-----------------|--|

| USER COM | MANDS                    |                      |                  |                        |                      |                       |                  | •                |                 |  |

| 0,00     | NO_OP[15:8]              |                      |                  |                        |                      |                       | REV_ID[4:0       | ]                |                 |  |

| 0x00     | NO_OP[7:0]               | -                    | -                | -                      |                      | CONS                  | STANT_TES        | ST[4:0]          |                 |  |

|          | SW_GO[15:8]              |                      |                  |                        | _                    | _                     | _                | _                | _               |  |

| 0x01     | SW_GO[7:0]               | _                    | _                | ı                      | _                    | _                     | _                | _                | SW_GO<br>_EN    |  |

| 0x02     | CNFG_GEN_1[15:8]         |                      |                  |                        | _                    | -                     | _                | _                | VOTH[1]         |  |

| 0.02     | CNFG_GEN_1[7:0]          | VOTH[0]              | LE               | D_SLEW[2               | :0]                  | DIV                   | [1:0]            | PWM_CLI          | K_SEL[1:0]      |  |

| 0x04     | CNFG_GEN_2[15:8]         |                      |                  |                        |                      | ,                     | VSTH_4[2:0       | )]               | VSTH_3[<br>2]   |  |

|          | CNFG_GEN_2[7:0]          | VSTH                 | VSTH_3[1:0] V    |                        |                      | ]                     | ,                | VSTH_1[2:0       | ]               |  |

| 0x05     | CNFG_GEN_3[15:8]         |                      |                  |                        | _                    | ,                     | VSTH_8[2:0       | )]               | VSTH_7[<br>2]   |  |

|          | CNFG_GEN_3[7:0]          | VSTH.                | _7[1:0]          | ,                      | VSTH_6[2:0           | ]                     | ,                | VSTH_5[2:0       | ]               |  |

| 0x06     | CNFG_GEN_4[15:8]         |                      |                  |                        | _                    | VSTH_12[2:0]          |                  |                  | VSTH_1<br>1[2]  |  |

|          | CNFG_GEN_4[7:0]          | VSTH_                | _11[1:0]         | \                      | /STH_10[2:0          | 0]                    | ,                | VSTH_9[2:0       | )]              |  |

| 0x07     | CNFG_UART[15:8]          |                      |                  |                        | _                    | _                     | _                |                  | ATCHDOG<br>:2]  |  |

| 0.07     | CNFG_UART[7:0]           |                      | ATCHDOG<br>:0]   |                        |                      | CID                   | [5:0]            |                  |                 |  |

| 0x08     | CNFG_WATCHDOG[15 :8]     |                      |                  |                        | -                    | WD_LED_STATE[11:8]    |                  |                  |                 |  |

| UXUO     | CNFG_WATCHDOG[7: 0]      |                      |                  |                        | WD_LED_STATE[7:0]    |                       |                  |                  |                 |  |

| 0x09     | CNFG_OPEN_OVRD[1<br>5:8] |                      |                  |                        | - OPEN_LED_OVR[11:8] |                       |                  |                  | ]               |  |

| 0x09     | CNFG_OPEN_OVRD[7: 0]     |                      |                  |                        | OPEN_LE              | D_OVR[7:0]            |                  |                  |                 |  |

| 0x0A     | CNFG_GROUPA[15:8]        |                      |                  |                        | _                    |                       | GROUPA           | _SEL[11:8]       |                 |  |

| UXUA     | CNFG_GROUPA[7:0]         |                      |                  |                        | GROUPA               | _SEL[7:0]             |                  |                  |                 |  |

| 0x0B     | CNFG_GROUPB[15:8]        |                      |                  |                        | _                    |                       | GROUPB.          | _SEL[11:8]       |                 |  |

| 0,00     | CNFG_GROUPB[7:0]         |                      |                  |                        | GROUPB               | _SEL[7:0]             |                  |                  |                 |  |

|          | CNFG_MSK_GEN[15:8]       |                      |                  |                        | TH_SHD<br>N_ACT      | _                     | _                | _                | _               |  |

| 0x0C     | CNFG_MSK_GEN[7:0]        | _                    | MSK_UA<br>RT_ERR | MSK_OP<br>EN_TRA<br>CE | MSK_OP<br>EN_LED     | MSK_SH<br>ORT_LE<br>D | MSK_CP<br>_RDY_N | MSK_RA<br>DC_ERR | MSK_TH<br>_WARN |  |

| 0,00     | CNFG_MSK_LED[15:8]       | - CNFG_MSK_LED[11:8] |                  |                        |                      |                       | ]                |                  |                 |  |

| 0x0D     | CNFG_MSK_LED[7:0]        |                      |                  |                        | CNFG_MSK_LED[7:0]    |                       |                  |                  |                 |  |

| 0x0E     | STAT_RADC[15:8]          |                      |                  |                        | _                    | _                     | _                | _                |                 |  |

| ADDRESS | NAME                     | MSB                    |                       |                  |                |                          |                           |                           | LSB                            |

|---------|--------------------------|------------------------|-----------------------|------------------|----------------|--------------------------|---------------------------|---------------------------|--------------------------------|

|         | STAT_RADC[7:0]           | -                      | -                     | -                | RADC_D<br>ONE  | RADDR_<br>OVER_R<br>ANGE | RGRAD<br>E_OVER<br>_RANGE | RADDR_<br>UNDER_<br>RANGE | RGRAD<br>E_UNDE<br>R_RANG<br>E |

| 0x0F    | STAT_RES_CODE[15:8]      |                        |                       |                  | _              | _                        | _                         | _                         | -                              |

|         | STAT_RES_CODE[7:0]       |                        | DEV_                  | ID[3:0]          |                | RGRADE[3:0]              |                           |                           |                                |

| 0x10    | STAT_GEN[15:8]           |                        |                       |                  | _              | -                        | OTP_CR<br>C_ERR           | CONFIG<br>_NOT_D<br>ONE   | RADC_E<br>RR                   |

|         | STAT_GEN[7:0]            | EXT_CL<br>K_ERR        | UART_E<br>RR          | OPEN_T<br>RACE   | OPEN_L<br>ED   | SHORT_<br>LED            | CP_RDY<br>_N              | TH_SHD<br>N               | TH_WA<br>RN                    |

| 0x11    | STAT_UART[15:8]          |                        |                       |                  | -              | _                        | _                         | -                         | UART_<br>WATCH<br>DOG          |

| OXII    | STAT_UART[7:0]           | RX_TIM<br>EOUT_E<br>RR | RX_CRC<br>_ERR        | RX_SYN<br>C_PERR | RX_PL_<br>PERR | RX_SYN<br>C_STOP<br>_ERR | RX_PL_<br>STOP_E<br>RR    | RX_PL_<br>START_<br>ERR   | -                              |

| 0.42    | STAT_SHORT_LED[15: 8]    |                        |                       |                  | _              | S                        | HORT_LED                  | )_STAT[11:8               | 3]                             |

| 0x12    | STAT_SHORT_LED[7:0       |                        | SHORT_LED_STAT[7:0]   |                  |                |                          |                           |                           |                                |

| 0x13    | STAT_OPEN_LED[15:8]      |                        | - OPEN_LED_STAT[11:8] |                  |                |                          |                           |                           | ]                              |

|         | STAT_OPEN_LED[7:0]       | OPEN_LED_STAT[7:0]     |                       |                  |                |                          |                           |                           |                                |

| 0x14    | STAT_OPEN_TRACE[1 5:8]   |                        |                       |                  | _              | OI                       | PEN_TRAC                  | E_STAT[11                 | :8]                            |

| 0.814   | STAT_OPEN_TRACE[7 :0]    |                        |                       | С                | PEN_TRAC       | CE_STAT[7:               | 0]                        |                           |                                |

| 0x15    | RTEMP[15:8]              |                        |                       |                  | _              | _                        | _                         | _                         | _                              |

| OX 10   | RTEMP[7:0]               |                        |                       |                  | RTEM           | IP[7:0]                  |                           |                           |                                |

| 0x16    | LOW_DUTY_TH[15:8]        |                        |                       |                  | _              |                          | LOW_DUT                   | Y_TH[11:8]                |                                |

|         | LOW_DUTY_TH[7:0]         |                        |                       |                  | LOW_DU1        | Y_TH[7:0]                | ı                         | ı                         |                                |

| 0x20    | PSFT_GRP[15:8]           |                        |                       |                  | _              | _                        | _                         | PSFT_GF                   | ROUP[1:0]                      |

|         | PSFT_GRP[7:0]            |                        |                       |                  | PSF            | Γ[7:0]                   |                           |                           |                                |

| 0x21    | PSFT_1[15:8]             |                        |                       |                  |                | 457.01                   | -                         | -                         | =                              |

|         | PSFT_1[7:0]              |                        |                       |                  | PSFI_          | _1[7:0]                  |                           |                           |                                |

| 0x22    | PSFT_2[15:8] PSFT_2[7:0] |                        |                       |                  | POET.          |                          | _                         | _                         | _                              |

|         | PSFT_3[15:8]             |                        |                       |                  | <u> </u>       | _2[1.0]                  | _                         | _                         | _                              |

| 0x23    | PSFT 3[7:0]              |                        |                       |                  | l .            | _3[7:0]                  |                           |                           |                                |

|         | PSFT 4[15:8]             |                        |                       |                  | _              |                          | _                         | _                         | _                              |

| 0x24    | PSFT_4[7:0]              |                        |                       |                  |                |                          | l                         |                           | <u> </u>                       |

|         | PSFT_5[15:8]             |                        |                       |                  | _              |                          | _                         | _                         | _                              |

| 0x25    | PSFT_5[7:0]              |                        |                       |                  | PSFT           | _5[7:0]                  | ı                         | l .                       | 1                              |