### MAX22516

## IO-Link Data Link Controller with Transceiver and Integrated DC-DC

#### **General Description**

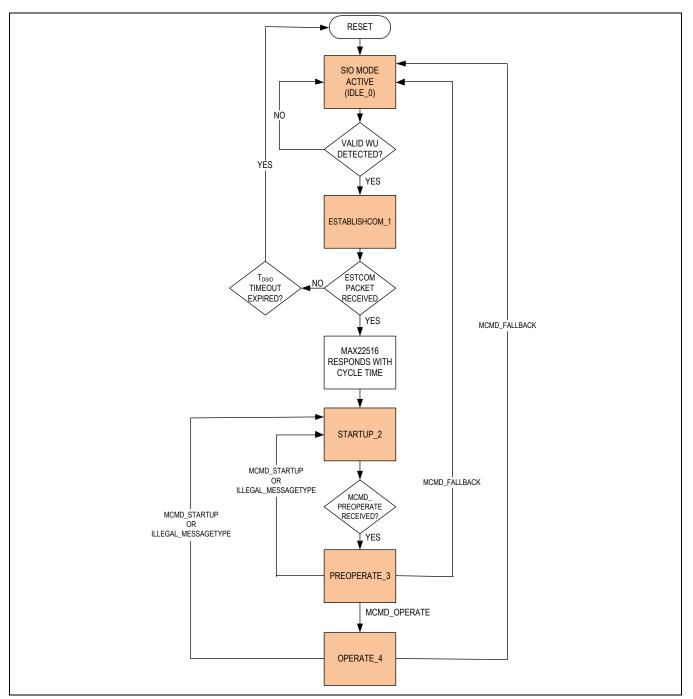

The MAX22516 IO-Link data link controller integrates a 24V C/Q transceiver, an auxiliary digital input and output, an integrated DC-DC, 5V and 3.3V linear regulators, and a full-feature IO-Link data link controller.

Once configured, the MAX22516 data link controller operates the IO-Link transceiver and requires no intervention from the external microcontroller during normal operation. Alternatively, the IO-Link transceiver can be controlled using the UART interface (TXEN, TX, and RX) directly, or through the serial-peripheral interface (SPI). The data link controller supports and includes, receive and transmit buffers for IO-link communication. Buffers for maximum size process data, ISDU, event, and page data reduce the need for timecritical microcontroller intervention, which allows the microcontroller to focus on the application layer task.

The MAX22516 features extensive integrated protection to ensure robust communication in harsh industrial environments. All IO-Link interface pins (V<sub>24</sub>, C/Q, DO, DI, and GND), are reverse voltage protected, short-circuit protected, and feature integrated  $\pm$ 1kV/500 $\Omega$  surge protection.

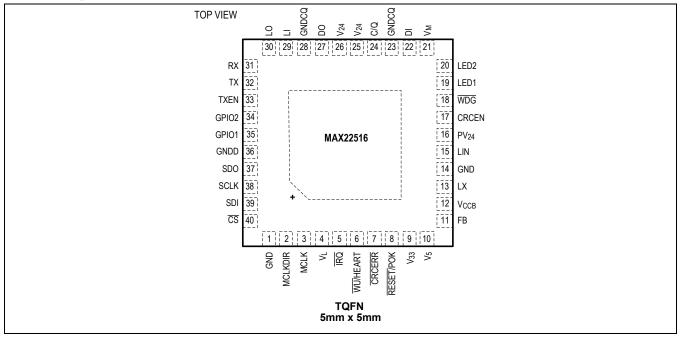

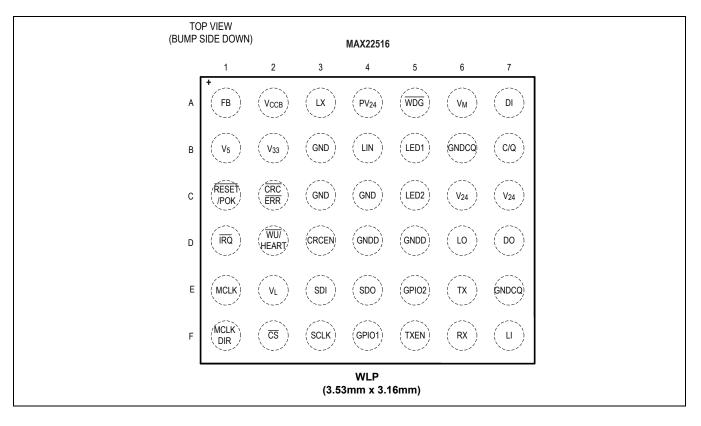

The MAX22516 is available in a tiny WLP package (3.53 mm x 3.16 mm) or 40-pin TQFN-EP package (5mm x 5mm) and operates over the -40°C to +125°C temperature range.

## **Key Applications**

- IO-Link Sensor and Actuator Devices

- Industrial Sensors

#### **Benefits and Features**

- Easily Enhance IO-Link Communication

- COM3: 400µs (min) Cycle Time Support

- Data Link Controller Autonomously Answers All Master Message Requests

- · Deterministic Device Answer Delay

- Highly Integrated Solution

- Complete Data Link Layer Includes

- Message Handler

- ISDU Handler

- Page Handler

- Event Handler

- Mode Handler

- Startup Handler

- 15MHz SPI with Burst Mode

- High Efficiency 200mA DC-DC with Adjustable

Output

- High Accuracy 3.3V and 5V Linear Regulators

- Flexible Application

- Transparent (TX, RX, TXEN) Mode Option

- LED Drivers with Programmable Sequence

- COM1, COM2, and COM3 Data Rates

- Robust and Reliable Design

- Integrated ±1kV/500Ω Surge Protection

- Optimized for Small Sensor Designs

- Available in Small WLP (3.53mm x 3.16mm) and 40-pin TQFN-EP (5mm x 5mm) Packages

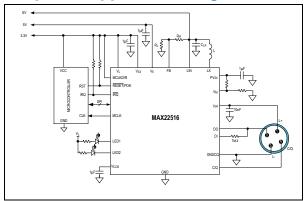

### **Simplified Application Diagram**

Ordering Information appears at end of data sheet.

## MAX22516

## **Absolute Maximum Ratings**

| All voltages referenced to GND, unless otherwise noted.<br>POWER                          |

|-------------------------------------------------------------------------------------------|

| V <sub>24</sub> (Continuous)36V to +36V                                                   |

| V <sub>24</sub> (Peak, 100µs)52V to +65V                                                  |

| PV <sub>24</sub> (Continuous)0.3V to +36V                                                 |

| $PV_{24}$ (Peak, 100µs)MAX(-0.3V, $V_{24}$ - 52V) to MIN(+52V, $V_{24}$ + 52V)            |

| $V_5,V_L,V_M,FB,V_{CCB}$ -0.3V to +6V                                                     |

| $V_{33}$ 0.3V to (V <sub>5</sub> + 0.3V)                                                  |

| LX0.3V to (PV <sub>24</sub> + 0.3V)                                                       |

| LIN (Continuous) MAX(-0.3V, V $_{5}$ - 0.3V) to +36V                                      |

| LIN (Peak, 100µs) MAX(-0.3V, V <sub>5</sub> - 0.3V) to +52V                               |

| 24V I/O                                                                                   |

| C/Q, DO (Continuous)MAX(-36V, V <sub>24</sub> - 36V) to MIN(+36V, V <sub>24</sub> + 36V)  |

| C/Q, DO (Peak, 100µs)MAX(-52V, V <sub>24</sub> - 60V) to MIN(+52V, V <sub>24</sub> + 60V) |

| CQGND0.3V to +0.3V                                                                        |

| DI (Continuous)36V to +36V                                                                |

| DI (peak 100µs)52V to +52V                                                                |

|                                                                                           |

| $\overline{\text{CS}},$ SCLK, SDI, TX, TXEN, LO, CRCEN, MCLKDIR-0.3V to (VL + 0.3V)       |

| LOGIC OUTPUTS                                                      |

|--------------------------------------------------------------------|

| SDO, RX, MCLK, LI0.3V to (VL + 0.3V)                               |

| IRQ, WU/HEART, LED1, LED2, CRCERR, WDG,<br>RESET/POK               |

| GPIO1, GPIO20.3V to (VL + 0.3V)                                    |

| CURRENT                                                            |

| Continuous Current into V24, LX, GND, or GNDCQ±1A                  |

| Continuous Current into PV <sub>24</sub> ±200mA                    |

| Peak Current into PV <sub>24</sub> (100µs)±1A                      |

| Continuous Current into C/Q±500mA                                  |

| Continuous Current into Any Other Pin±50mA                         |

| CONTINUOUS POWER DISSIPATION                                       |

| 40-pin TQFN-EP (T <sub>A</sub> = +70°C, derates at 28mw/°C above   |

| +70°C)                                                             |

| 42-bump WLP (T <sub>A</sub> = +70°C, derates at 27.5mw/°C above    |

| +70°C)1510mW                                                       |

| TEMPERATURE                                                        |

| Operating Temperature Range40°C to +125°C                          |

| Maximum Junction Range+150°C                                       |

| Storage Temperature Range40°C to +150°C                            |

| Soldering Temperature (Reflow) (TQFN only, soldering 10 sec)+300°C |

|                                                                    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 40 TQFN-EP

| Package Code                                          | T4055+1C       |  |  |  |

|-------------------------------------------------------|----------------|--|--|--|

| Outline Number                                        | <u>21-0140</u> |  |  |  |

| Land Pattern Number                                   | <u>90-0016</u> |  |  |  |

| Thermal Resistance, Single Layer Board:               |                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 45°C/W         |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2°C/W          |  |  |  |

| Thermal Resistance, Four Layer Board:                 |                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 28°C/W         |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2°C/W          |  |  |  |

#### 42 WLP

| Package Code                           | W423H3+1                                                                                |

|----------------------------------------|-----------------------------------------------------------------------------------------|

| Outline Number                         | <u>21-100631</u>                                                                        |

| Land Pattern Number                    | Refer to the Application Note 1891: Wafer-Level Packaging<br>(WLP) and Its Applications |

| Thermal Resistance, Four Layer Board:  |                                                                                         |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 36.38°C/W                                                                               |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-</u> <u>tutorial</u>.

## **Electrical Characteristics**

$(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V<sub>L</sub> or GND, Typical values are = at V<sub>24</sub> = 24V, V<sub>5</sub> = 5V, V<sub>L</sub> = 3.3V and T<sub>A</sub> = +25°C, unless otherwise noted (<u>Note 1</u>))

| PARAMETER                                                       | SYMBOL                        | COND                                                                                                                        | TIONS                                                | MIN    | TYP   | MAX    | UNITS |  |

|-----------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------|-------|--------|-------|--|

| DC CHARACTERISTICS                                              | 5                             |                                                                                                                             |                                                      |        |       |        |       |  |

| POWER SUPPLY                                                    |                               |                                                                                                                             |                                                      |        |       |        |       |  |

| V <sub>24</sub> Supply Voltage                                  | V <sub>24</sub>               |                                                                                                                             |                                                      | 8      |       | 36     | V     |  |

| V <sub>24</sub> Undervoltage                                    |                               | V <sub>24</sub> rising                                                                                                      |                                                      | 7      | 7.5   | 8      |       |  |

| Lockout Threshold                                               | V <sub>24UVLO</sub>           | V <sub>24</sub> falling                                                                                                     |                                                      | 6.3    | 6.9   | 7.5    | V     |  |

| V <sub>24</sub> Undervoltage<br>Lockout Threshold<br>Hysteresis | V <sub>24UVLO_</sub> HYS<br>T |                                                                                                                             |                                                      |        | 530   |        | mV    |  |

|                                                                 |                               | No load on C/Q,<br>DO, V <sub>5</sub> powered                                                                               | C/Q, DO disabled, $V_{33}$ enabled                   | 0.01   | 0.05  | 0.10   |       |  |

| V <sub>24</sub> Supply Current                                  | I <sub>24</sub>               | externally, DC-DC<br>disabled, MCLK<br>disabled                                                                             | C/Q, DO in push-<br>pull, and is high or<br>low      | 0.42   | 0.6   | 0.75   | mA    |  |

|                                                                 |                               | V <sub>5</sub> powered<br>externally, DC-DC<br>enabled, MCLK<br>enabled                                                     | C/Q, DO in push-<br>pull and is high or<br>low       | 0.60   | 0.75  | 0.95   |       |  |

| V <sub>5</sub> Supply Voltage                                   | V <sub>5</sub>                | V <sub>5</sub> supplied external                                                                                            | у                                                    | 4.85   |       | 5.5    | V     |  |

| V <sub>5</sub> Undervoltage                                     |                               | V <sub>5</sub> rising                                                                                                       |                                                      | 3.15   | 3.27  | 3.40   | N/    |  |

| Lockout Threshold                                               | V <sub>5UVLO</sub>            | V <sub>5</sub> falling                                                                                                      |                                                      | 3.10   | 3.22  | 3.35   | V     |  |

|                                                                 |                               | V <sub>5</sub> powered                                                                                                      | C/Q, DO disabled                                     | 1.5    | 2.4   | 3.0    | mA    |  |

| V <sub>5</sub> Supply Current                                   | I <sub>5</sub>                | externally, DC-DC disabled, MCLK disabled, $V_{33}$ enabled, no load on $V_{33}$                                            | C/Q, DO in push-<br>pull mode, no load<br>on C/Q, DO | 2.1    | 3     | 3.7    |       |  |

|                                                                 |                               | V <sub>5</sub> powered external                                                                                             | set to 29.48MHz, C/Q                                 | 2.9    | 4     | 5      |       |  |

| V <sub>L</sub> Logic Level Supply<br>Voltage                    | VL                            |                                                                                                                             |                                                      | 2.5    |       | 5.5    | V     |  |

| V <sub>L</sub> Undervoltage                                     | V <sub>LUVLO</sub>            | $V_L$ rising                                                                                                                |                                                      |        |       | 1.35   | V     |  |

| Threshold                                                       | *LUVLO                        | V <sub>L</sub> falling                                                                                                      |                                                      | 0.45   |       |        | v     |  |

| V <sub>L</sub> Logic Level Supply                               | ١L                            | All logic inputs at GND or $V_L$ , no load on any logic outputs, MCLK disabled                                              |                                                      |        |       | 10     | μA    |  |

| Current<br>DC-DC SWITCHING RE                                   | GULATOR                       | any logic outputs, MC                                                                                                       |                                                      |        |       |        |       |  |

| Input Voltage Range                                             | V <sub>24_DC</sub>            | V <sub>24</sub> is the input to the                                                                                         | e DC-DC                                              | 7      |       | 36     | V     |  |

| DC-DC Turn-on Delay                                             | tDC_ON                        | Delay from $V_{24}$ crossing $V_{24UVLO}$<br>threshold until the DC-DC regulator<br>finishes soft-start and RESET/POK rises |                                                      | ,      | 2.22  | 30     | ms    |  |

|                                                                 | <sup>f</sup> DC_H             | BuckSS = 0                                                                                                                  | INCOLIFOR IISES                                      | 1.140  | 1.229 | 1.330  | +     |  |

| Switching Frequency                                             | fDC_HSPRD                     | BuckSS = 0                                                                                                                  |                                                      | 1.170  | 1.229 | 1.000  | MHz   |  |

| Spread Spectrum                                                 | Δf <sub>DC_SPRD</sub>         | BuckSS = 1                                                                                                                  |                                                      | -11.5  |       | +13.5  | %     |  |

| Feedback (FB)<br>Regulation Voltage                             | V <sub>DC_FB</sub>            |                                                                                                                             |                                                      | 0.8865 | 0.9   | 0.9135 | V     |  |

| $(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V <sub>L</sub> or GND, Typical values are |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| = at V <sub>24</sub> = 24V, V <sub>5</sub> = 5V, V <sub>L</sub> = 3.3V and T <sub>A</sub> = +25°C, unless otherwise noted ( <u>Note 1</u> ))                                        |  |

| PARAMETER                              | SYMBOL                      | COND                                                      | ITIONS                 | MIN  | TYP  | MAX  | UNITS                   |

|----------------------------------------|-----------------------------|-----------------------------------------------------------|------------------------|------|------|------|-------------------------|

| Output Voltage<br>Accuracy             | ACC <sub>DCFB</sub>         |                                                           |                        | -1.5 | 0    | +1.5 | %                       |

| Feedback (FB) OK<br>Threshold          | V <sub>DC_FBOK</sub>        |                                                           |                        | 92   | 95   | 98   | %V <sub>DC_F</sub><br>B |

| Feedback (FB) Low<br>Threshold         | V <sub>DC_FBTHLO</sub><br>W |                                                           |                        | 61   | 65   | 70   | %V <sub>DC_F</sub><br>B |

| LX On-Resistance<br>(High Side)        | $R_{DC_{HS}}$               | From V <sub>24</sub> to LX, LX<br>( <u>Note 2</u> )       | is sinking current     |      | 2.2  | 3.9  | Ω                       |

| LX On-Resistance<br>(Low Side)         | $R_{DC_{LS}}$               | From LX to GND (M                                         | <u>ote 2</u> )         |      | 1.3  | 2.8  | Ω                       |

| Active Diode On-<br>Resistance         | R <sub>DC_ACT</sub>         | DC current ( <u>Note 2</u> )                              |                        |      | 3.0  | 5.5  | Ω                       |

| Maximum Peak Current into Active Diode | IDC_ACTMAX                  |                                                           |                        | 300  |      |      | mA                      |

| Maximum LX Current<br>Ripple           | $\Delta I_{DC_{LX}}$        |                                                           |                        |      | 100  |      | %                       |

| High-Side Peak Current<br>Limit        | I <sub>DC_HSLIM</sub>       |                                                           |                        | +350 | +390 | +440 | mA                      |

| Low-Side Current Limit                 | IDC_LSMAX                   |                                                           |                        | -240 | -190 | -150 | mA                      |

| DC-DC Autoretry Period                 | <sup>t</sup> DCRETRY        |                                                           |                        |      | 22   |      | ms                      |

| External Capacitance on $PV_{24}$      | C <sub>DC_PV24</sub>        |                                                           |                        |      | 1    |      | μF                      |

| LX Leakage Current                     | I <sub>LX_LKG</sub>         | 0V < V <sub>LX</sub> < 36V                                |                        | -1   |      | +1   | μA                      |

| FB Input Bias Current                  | I <sub>FB_LKG</sub>         | $0 \le V_{FB} \le 1V, T_A = 25^{\circ}C$                  |                        | -100 |      | +100 | nA                      |

| FB Threshold for POK                   | N/                          | V <sub>FB</sub> falling                                   |                        | 89   | 92   | 95   | 0/1/                    |

| Assertion                              | V <sub>FBOK_</sub> F        | V <sub>FB</sub> rising                                    |                        | 92   | 95   | 98   | %V <sub>FB</sub>        |

| FB Undervoltage Trip<br>Threshold      | V <sub>FB_LOW</sub>         |                                                           |                        | 61   | 64.5 | 70   | %V <sub>FB</sub>        |

| LX Minimum On-Time                     | t <sub>LX_MINON</sub>       | ( <u>Note 2</u> )                                         |                        |      | 64   | 92   | ns                      |

| LX Minimum Off-Time                    | <sup>t</sup> LX_MINOFF      | ( <u>Note 2</u> )                                         |                        |      | 32   | 60   | ns                      |

| V <sub>CCB</sub> LINEAR REGULAT        | OR (V <sub>CCB</sub> )      | ·                                                         |                        |      |      |      |                         |

| V <sub>CCB</sub> Output Voltage        | V <sub>CCB</sub>            | $8V \le V_{PV24} \le 36V$ ,<br>$0mA \le I_{LOAD} \le 5mA$ |                        | 4.85 | 5    | 5.15 | V                       |

| V <sub>CCB</sub> Current Limit         | ICCB_MAX                    | V <sub>PV24</sub> = 8V                                    |                        | 10   |      |      | mA                      |

| <b>5V LINEAR REGULATOR</b>             | R (V <sub>5</sub> )         | ·                                                         |                        |      |      |      | -                       |

| V <sub>5</sub> Input Supply Voltage    | V <sub>LIN</sub>            |                                                           |                        | 6    |      | 36   | V                       |

| V <sub>5</sub> Output Voltage          | V <sub>5</sub>              | 6V ≤ V <sub>LIN</sub> ≤ 36V, no                           | load on V <sub>5</sub> | 4.85 | 5    | 5.15 | V                       |

| V <sub>5</sub> Load Regulation         | $\Delta V5_{LDR}$           | V <sub>LIN</sub> = 24V, 1mA ≤ I                           | <sub>LOAD</sub> ≤ 50mA |      | 0.6  | 2.0  | %                       |

| V <sub>5</sub> Line Regulation         | $\Delta V5_{LNR}$           | $6V \le V_{LIN} \le 36V$ , $I_{LOAD} = 1mA$               |                        |      | 0.05 | 0.2  | mV/V                    |

| V <sub>5</sub> Load Capacitance        | C <sub>V5</sub>             | External capacitance on $V_5$                             |                        |      | 1    |      | μF                      |

| 3.3V LINEAR REGULAT                    | OR (V <sub>33</sub> )       | 1                                                         |                        |      |      |      |                         |

| V <sub>33</sub> Output Voltage         | V <sub>33</sub>             | No load                                                   |                        | 3.15 | 3.3  | 3.45 | V                       |

| V <sub>33</sub> Load Regulation        | $\Delta V_{33}_{LR}$        | 1mA ≤ I <sub>LOAD</sub> ≤<br>100mA                        | LIN and $V_5$ shorted  | 0    | 0.9  | 3    | %                       |

| V <sub>33</sub> Load Capacitance       | C <sub>V33</sub>            | External capacitance                                      | e on V <sub>33</sub>   |      | 1    |      | μF                      |

| C/Q, DO DRIVERS                        |                             | 1                                                         |                        |      |      |      | 1 -                     |

$(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V<sub>L</sub> or GND, Typical values are = at V<sub>24</sub> = 24V, V<sub>5</sub> = 5V, V<sub>1</sub> = 3.3V and T<sub>A</sub> = +25°C, unless otherwise noted (*Note* 1))

| PARAMETER                                  | SYMBOL                | COND                                                                                                                                             | ITIONS                                                                                                                | MIN      | TYP  | MAX        | UNITS                 |

|--------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------|------|------------|-----------------------|

| C/Q, DO Driver High-<br>Side On-Resistance | R <sub>CQOH</sub>     | High-side enabled, CQ_CL[1:0] or<br>DO_CL[1:0] = 01, I <sub>LOAD</sub> = +150mA ( <u>Note</u><br>2)                                              |                                                                                                                       |          | 2.4  | 4.4        | Ω                     |

| C/Q, DO Driver Low-<br>Side On-Resistance  | R <sub>CQLO</sub>     | Low-side enabled, C<br>DO_CL[1:0] = 01, IL<br>2)                                                                                                 | C_CL[1:0] or<br>CAD = -150mA ( <u>Note</u>                                                                            |          | 2.0  | 4.0        | Ω                     |

|                                            |                       |                                                                                                                                                  | CQ_CL[1:0] or<br>DO_CL[1:0] = 00                                                                                      | 50       | 60   | 70         |                       |

| C/Q, DO Driver Current                     | L.                    | V <sub>DROP</sub> = 3V ( <u>Note</u>                                                                                                             | CQ_CL[1:0] or<br>DO_CL[1:0] = 01                                                                                      | 100      | 120  | 140        |                       |

| Limit                                      | I <sub>CL</sub>       | <u>3</u> )                                                                                                                                       | CQ_CL[1:0] or<br>DO_CL[1:0] = 10                                                                                      | 200      | 230  | 260        | mA                    |

|                                            |                       |                                                                                                                                                  | CQ_CL[1:0] or<br>DO_CL[1:0] = 11                                                                                      | 250      | 289  | 330        |                       |

| C/Q Leakage Current                        | I <sub>LEAK_</sub> CQ | $V_{24} = 24V, (V_{24} - 36V) \le V_{C/Q, DO} \le 36V, Driver disabled, C/Q receiver disabled$                                                   | C/Q driver                                                                                                            | -32      |      | +40        | μΑ                    |

| DO Leakage Current                         | ILEAK_DO              | $V_{24} = 24V, (V_{24} - 36V) \le V_{DO} \le 36V,$<br>Driver disabled                                                                            | DO driver                                                                                                             | -22      |      | +4         | μA                    |

| C/Q, DO Output<br>Reverse Current          | I <sub>REV_CQ</sub>   | Driver enabled and in push-pull,<br>$V_{C/Q, DO} = (V_{24} + 5V)$ or $(V_{GND} - 5V)$                                                            |                                                                                                                       | -90      |      | +375       | μΑ                    |

| C/Q, DO Weak Pull-<br>Down Current         | ICQPD                 | Driver disabled, $V_{C/Q, DO} > 5V$ ,<br>$CQ_PD = 1 \text{ or } DO_PD = 1, CQ_PU = 0$<br>or $DO_PU = 0, CQPu2mA = 0 \text{ or}$<br>DOPu2mA = 0   |                                                                                                                       | -220     | -193 | -160       | μA                    |

| C/Q, DO Weak Pull-Up<br>Current            | ICQPU                 | Driver disabled, V <sub>C/0</sub><br>CQ_PD = 0 or DO_                                                                                            | Driver disabled, $V_{C/Q, DO} = (V_{24} - 5V)$ ,<br>CQ_PD = 0 or DO_PD = 0, CQ_PU = 1<br>or DO_PD = 1, CQPu2mA = 0 or |          | +200 | +260       | μA                    |

| C/Q, DO 2mA Pull-<br>Down Current          | I <sub>CQPD2</sub>    | CQ_PD = 1 or DO_<br>or DO_PU = 0, CQP<br>DOPu2mA = 1                                                                                             | Driver disabled, $V_{C/Q, DO} > 5V$ ,<br>CQ_PD = 1 or DO_PD = 1, CQ_PU = 0<br>or DO_PU = 0, CQPu2mA = 1 or            |          | -2.2 | -2.0       | mA                    |

| C/Q, DO 2mA Pull-Up<br>Current             | I <sub>CQPU2</sub>    | Driver disabled, $V_{C/Q, DO} = (V_{24} - 5V)$ ,<br>$CQ_PD = 0$ or $DO_PD = 0$ , $CQ_PU = 1$<br>or $DO_PU = 1$ , $CQPu2mA = 1$ or<br>DOPu2mA = 1 |                                                                                                                       | 2.0      | 2.2  | 2.5        | mA                    |

| C/Q, DI RECEIVERS                          |                       | -                                                                                                                                                |                                                                                                                       |          |      |            |                       |

| Input Voltage Range                        | V <sub>RIN</sub>      | For valid RX /LI logic                                                                                                                           | For valid RX /LI logic                                                                                                |          |      | 36         | V                     |

| Input Threshold High                       | V <sub>THR</sub>      | Receiver enabled                                                                                                                                 | V <sub>24</sub> ≥ 18V<br>V <sub>24</sub> < 18V                                                                        | 11<br>54 |      | 12.5<br>80 | V<br>%V <sub>24</sub> |

| Input Threshold Low                        | V <sub>TLR</sub>      | Receiver enabled                                                                                                                                 | V <sub>24</sub> ≥ 18V                                                                                                 | 9        |      | 10.5       | V                     |

|                                            | · ILK                 |                                                                                                                                                  | V <sub>24</sub> < 18V                                                                                                 | 45       |      | 68.1       | %V <sub>24</sub>      |

| Input Hysteresis                           | V <sub>HYSR</sub>     | Receiver enabled                                                                                                                                 | V <sub>24</sub> ≥ 18V                                                                                                 |          | 2    |            | V                     |

| ,,                                         |                       | V <sub>24</sub> < 18V                                                                                                                            |                                                                                                                       |          | 11   |            | %V <sub>24</sub>      |

| $(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V <sub>L</sub> or GND, Typical values are |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| = at V <sub>24</sub> = 24V, V <sub>5</sub> = 5V, V <sub>1</sub> = 3.3V and T <sub>A</sub> = +25°C, unless otherwise noted ( <i>Note 1</i> ))                                        |  |

| PARAMETER                                       | SYMBOL               | CONDITIONS                                           | MIN                  | ТҮР     | MAX                      | UNITS |

|-------------------------------------------------|----------------------|------------------------------------------------------|----------------------|---------|--------------------------|-------|

| C/Q Input Threshold<br>High (TTL Mode)          | V <sub>TH_TTL</sub>  | C/Q driver disabled, RXTTL = 1                       | 2.10                 |         | 3.45                     | V     |

| C/Q Input Threshold<br>Low (TTL Mode)           | $V_{TL}_{TTL}$       | C/Q driver disabled, RXTTL = 1                       | 1.1                  |         | 1.8                      | V     |

| Input Hysteresis (TTL<br>Mode)                  | V <sub>HYSTTL</sub>  | Driver disabled, RXTTL = 1                           |                      | 1.38    |                          | V     |

| C/Q Receiver Input<br>Capacitance               | C <sub>IN_CQ</sub>   | Driver disabled, CQ_PD = 0, CQ_PU = 0,<br>f = 100kHz |                      | 35      |                          | pF    |

| DI Receiver Input<br>Capacitance                | C <sub>IN_DI</sub>   |                                                      |                      | 2       |                          | pF    |

| VOLTAGE MONITOR INF                             | TUY                  |                                                      |                      |         |                          |       |

| V <sub>M</sub> Voltage Range                    | VM                   |                                                      | 0                    |         | 5.5                      | V     |

| V <sub>M</sub> Threshold Voltage                | $V_{M_R}$            | Rising                                               | 0.87                 | 0.9     | 0.93                     | V     |

|                                                 | V <sub>M_F</sub>     | Falling                                              | 0.83                 | 0.86    | 0.89                     | v     |

| V <sub>M</sub> Threshold<br>Hysteresis          | V <sub>M_HYS</sub>   |                                                      |                      | 0.04    |                          | V     |

| V <sub>M</sub> Input Current                    | IM                   |                                                      | -1                   |         | +1                       | μA    |

| RESET/POWER OK (RES                             |                      |                                                      |                      |         |                          |       |

| RESET/POK Input                                 | V <sub>RSTIL</sub>   |                                                      | 0.4                  |         |                          | V     |

| Voltage Low<br>RESET/POK Input                  | V <sub>RSTIH</sub>   |                                                      |                      |         | 1.3                      | V     |

| Voltage High<br>RESET/POK Output<br>Voltage Low | V <sub>POKLOW</sub>  | I <sub>LOAD</sub> = -5mA                             |                      |         | +0.12                    | V     |

| RESET/POK High<br>Impedance Leakage<br>Current  | IRST_OD              | RESET/POK not asserted                               | -1                   |         | +1                       | μA    |

|                                                 | .K, SDI, TX, TXE     | EN, LO, GPIO1, GPIO2, MCLK, MCLKDIR, (               | CRCEN)               |         |                          |       |

| Logic Input Voltage Low<br>Threshold            | V <sub>IL</sub>      |                                                      | ,                    |         | 0.31 x<br>V <sub>L</sub> | V     |

| Logic Input Voltage High<br>Threshold           | V <sub>IH</sub>      |                                                      | 0.68 x<br>VL         |         |                          | V     |

| Logic Input Leakage<br>Current                  | ILEAK                | Logic input = GND or V <sub>L</sub>                  | -1                   |         | +1                       | μA    |

| GPIO_ Pull-Up<br>Resistance                     | R <sub>GPIO_UP</sub> |                                                      | 200                  | 330     | 460                      | kΩ    |

| GPIO_ Pull-Down<br>Resistance                   | R <sub>GPIO_DN</sub> |                                                      | 200                  | 330     | 460                      | kΩ    |

| LOGIC OUTPUTS (WU/H                             | EART, IRQ, SD        | O, RX, LI, MCLK, GPIO1, GPIO2, LED1, LE              | D2, CRCER            | R, WDG) |                          |       |

| Logic Output Voltage<br>Low                     | V <sub>OL</sub>      | I <sub>LOAD</sub> = -5mA                             |                      |         | 0.4                      | V     |

| Logic Output Voltage<br>High                    | V <sub>OH</sub>      | SDO, RX, LI,<br>MCLK, GPIO1,<br>GPIO2                | V <sub>L</sub> - 0.4 |         |                          | V     |

| Open-Drain High<br>Impedance Leakage<br>Current | I <sub>LK_OD</sub>   | IRQ, WU/HEART, CRCERR, LED1 and LED2, not asserted   | -1                   |         | +1                       | μA    |

| SDO Leakage Current                             | I <sub>LK_SDO</sub>  | CS = high                                            | -1                   |         | +1                       | μA    |

| RX Leakage Current                              | I <sub>LK_RX</sub>   | $RX = GND \text{ or } V_1$                           | -1                   |         | +1                       | μA    |

$(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V<sub>L</sub> or GND, Typical values are = at V<sub>24</sub> = 24V, V<sub>5</sub> = 5V, V<sub>L</sub> = 3.3V and T<sub>A</sub> = +25°C, unless otherwise noted (<u>Note 1</u>))

| PARAMETER                                          | SYMBOL                   | CONE                                                                      | DITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------|--------------------------|---------------------------------------------------------------------------|-------------------------------------------------|------|------|------|-------|

| INTERNAL THERMAL S                                 | ENSOR                    |                                                                           |                                                 |      |      |      |       |

| Programmable Thermal<br>Warning Threshold<br>Range | T <sub>WRN_RNG</sub>     | Typical range                                                             | Typical range                                   |      |      | +174 | °C    |

| Programmable Thermal<br>Warning Threshold Step     | T <sub>WRN_LSB</sub>     | 1 LSB                                                                     |                                                 |      | 3    |      | °C    |

| Thermal ADC<br>Resolution                          | T <sub>WRN_RES</sub>     |                                                                           |                                                 |      | 6    |      | bit   |

| Thermal ADC Accuracy                               | $\Delta T_{PREC_{25C}}$  | T <sub>J</sub> = 25°C ( <u>Note 2</u> )                                   |                                                 | -8   | 0    | +8   | °C    |

|                                                    | $\Delta T_{PREC_{125C}}$ | T <sub>J</sub> = 125°C ( <u>Note 2</u> )                                  |                                                 | -7   | 3    | +12  | C     |

| Thermal ADC<br>Conversion Time                     | <sup>t</sup> ADC_CONV    |                                                                           |                                                 |      | 450  |      | μs    |

| THERMAL PROTECTION                                 | N                        |                                                                           |                                                 |      |      |      |       |

| C/Q, DO Driver<br>Shutdown Temperature             | T <sub>SHUT_DRV</sub>    | Driver temperature is set and driver is d                                 | •                                               |      | +165 |      | °C    |

| C/Q, DO Driver<br>Shutdown Hysteresis              | TSHUT_DHYS               | Driver temperature f<br>automatically re-ena<br>TSHOFFEN = 0              | ibled,                                          |      | 9    |      | °C    |

| IC Thermal Warning<br>Threshold                    | T <sub>WRN</sub>         | Die temperature risi<br>bits are set                                      | ng, ThW and ThWInt                              |      | +135 |      | °C    |

| IC Thermal Warning<br>Threshold Hysteresis         | T <sub>WRN_HYS</sub>     | Die temperature fall<br>cleared                                           | Die temperature falling, ThW bit is<br>cleared  |      | 9    |      | °C    |

| IC Thermal Shutdown<br>Threshold                   | T <sub>SHUT_IC</sub>     | Die temperature rising, ThShd bit set                                     |                                                 |      | +175 |      | °C    |

| IC Thermal Shutdown<br>Hysteresis                  | T <sub>SHUT_ICHYS</sub>  | Die temperature falling, ThShd bit is<br>cleared                          |                                                 |      | 26   |      | °C    |

| AC ELECTRICAL CHAR                                 | ACTERISTICS              |                                                                           |                                                 |      |      |      |       |

| C/Q, DO DRIVERS                                    |                          |                                                                           |                                                 |      |      |      |       |

| C/Q, DO Driver Low-to-                             | <sup>t</sup> PDLH_PP     | CQ_SLEW[1:0] =<br>00 or<br>DO_SLEW[1:0] =<br>00, <u>Figure 1</u>          | Push-pull or PNP<br>mode                        | 0.32 | 0.61 | 0.90 |       |

| High Propagation Delay                             | <sup>t</sup> PDLH_OC     | CQ_SLEW[1:0] =<br>00 or<br>DO_SLEW[1:0] =<br>00, <u>Figure 1</u>          | NPN mode                                        |      | 1    |      | - µs  |

| C/Q, DO Driver High-to-                            | <sup>t</sup> PDHL_PP     | CQ_SLEW[1:0] =<br>00 or<br>DO_SLEW[1:0] =<br>00, <u>Figure 1</u>          | Push-pull or NPN<br>mode                        | 0.41 | 0.65 | 0.92 |       |

| Low Propagation Delay                              | <sup>t</sup> PDHL_OC     | CQ_SLEW[1:0] =<br>00 or<br>DO_SLEW[1:0] =<br>00, <u>Figure 1</u>          | PNP mode                                        |      | 1    |      | μs    |

| C/Q, DO Driver Skew                                | t <sub>SKEW</sub>        | t <sub>PDLH</sub> - t <sub>PDHL</sub>  , CQ<br>DO_SLEW[1:0] = 00          |                                                 | -0.2 |      | +0.2 | μs    |

| C/Q, DO Driver Rise<br>Time                        | trise                    | Push-pull or PNP<br>mode, V <sub>24</sub> (max) =<br>30V, <u>Figure 1</u> | CQ_SLEW[1:0] =<br>00 or<br>DO_SLEW[1:0] =<br>00 | 0.2  | 0.36 | 0.56 | μs    |

| $(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V <sub>L</sub> or GND, Typical values are |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| = at V <sub>24</sub> = 24V, V <sub>5</sub> = 5V, V <sub>L</sub> = 3.3V and T <sub>A</sub> = +25°C, unless otherwise noted ( <u>Note 1</u> ))                                        |

| PARAMETER                            | SYMBOL            | CONE                                                                      | DITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|-------------------|---------------------------------------------------------------------------|-------------------------------------------------|------|------|------|-------|

|                                      |                   |                                                                           | CQ_SLEW[1:0] =<br>01 or<br>DO_SLEW[1:0] =<br>01 | 0.38 | 0.69 | 1.04 |       |

|                                      |                   | Push-pull or PNP<br>mode, V <sub>24</sub> (max) =<br>30V, <u>Figure 1</u> | CQ_SLEW[1:0] =<br>10 or<br>DO_SLEW[1:0] =<br>10 | 0.80 | 1.63 | 2.65 |       |

|                                      |                   |                                                                           | CQ_SLEW[1:0] =<br>11 or<br>DO_SLEW[1:0] =<br>11 | 2.2  | 6.3  | 11.5 |       |

|                                      |                   | Push-pull or NPN<br>mode, V <sub>24</sub> (max) =<br>30V, <u>Figure 1</u> | CQ_SLEW[1:0] =<br>00 or<br>DO_SLEW[1:0] =<br>00 | 0.18 | 0.32 | 0.50 |       |

| C/Q, DO Driver Fall                  |                   |                                                                           | CQ_SLEW[1:0] =<br>01 or<br>DO_SLEW[1:0] =<br>01 | 0.38 | 0.63 | 1.00 | μs    |

| Time                                 |                   | Push-pull or NPN<br>mode, V <sub>24</sub> (max) =<br>30V, <u>Figure 1</u> | CQ_SLEW[1:0] =<br>10 or<br>DO_SLEW[1:0] =<br>10 | 1    | 1.56 | 2.5  |       |

|                                      |                   |                                                                           | CQ_SLEW[1:0] =<br>11 or<br>DO_SLEW[1:0] =<br>11 | 4    | 7.32 | 12   |       |

| C/Q, DO Driver Enable<br>Time High   | <sup>t</sup> ENH  | Push-pull or PNP m                                                        | ode, <u>Figure 3</u>                            | 0.35 | 0.64 | 0.94 | μs    |

| C/Q, DO Driver Enable<br>Time Low    | t <sub>ENL</sub>  | Push-pull or NPN m                                                        | ode, <u>Figure 2</u>                            | 0.27 | 0.43 | 0.67 | μs    |

| C/Q, DO Driver Disable<br>Time High  | <sup>t</sup> DISH | Push-pull or PNP m                                                        | ode, <u>Figure 3</u>                            | 1.2  | 1.8  | 2.4  | μs    |

| C/Q, DO Driver Disable<br>Time Low   | t <sub>DISL</sub> | Push-pull or NPN m                                                        | ode, <u>Figure 2</u>                            | 1.2  | 1.93 | 2.6  | μs    |

| C/Q, DI RECEIVERS                    |                   | ·                                                                         |                                                 |      |      |      |       |

| C/Q Receiver Low-to-                 | <b>t</b>          |                                                                           | RXFilter = 1                                    | 0.83 | 1.28 | 1.8  |       |

| High Propagation Delay               | <sup>t</sup> PRLH | <u>Figure 4</u>                                                           | RXFilter = 0                                    | 0.27 | 0.39 | 0.51 | μs    |

| C/Q Receiver High-to-                |                   |                                                                           | RXFilter = 1                                    | 0.75 | 1.16 | 1.7  |       |

| Low Propagation Delay                | <sup>t</sup> PRHL | <u>Figure 4</u>                                                           | RXFilter = 0                                    | 0.18 | 0.28 | 0.38 | μs    |

| DI Receiver Low-to-High              |                   |                                                                           | RXFilter = 1                                    | 0.97 |      | 2.30 |       |

| Propagation Delay                    | <sup>t</sup> PRLH | <u>Figure 4</u>                                                           | RXFilter = 0                                    | 0.45 |      | 1.05 | μs    |

| DI Receiver High-to-Low              |                   |                                                                           | RXFilter = 1                                    | 0.85 |      | 2.05 |       |

| Propagation Delay                    | t <sub>PRHL</sub> | <u>Figure 4</u>                                                           | RXFilter = 0                                    | 0.35 |      | 0.78 | μs    |

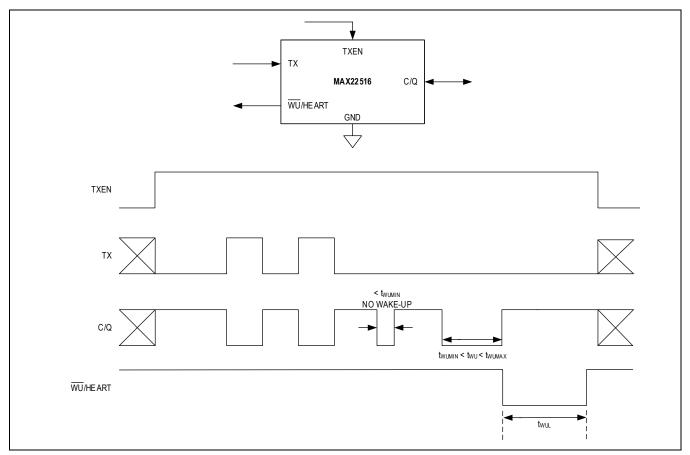

| WAKE-UP DETECTION (                  | Figure 5          |                                                                           |                                                 |      |      |      |       |

| Wake-Up Input<br>Minimum Pulse Width | twumin            | C/Q load capacitanc                                                       | ce = 3nF                                        | 60   | 66   | 70   | μs    |

$(V_{24} = 7V \text{ to } 36V, V_5 = 4.85V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, V_{GNDCQ} = V_{GND} = 0V$ , All logic inputs at V<sub>L</sub> or GND, Typical values are = at V<sub>24</sub> = 24V, V<sub>5</sub> = 5V, V<sub>L</sub> = 3.3V and T<sub>A</sub> = +25°C, unless otherwise noted (*Note 1*))

| PARAMETER                                                        | SYMBOL                  | CON                                              | DITIONS            | MIN  | ТҮР   | MAX  | UNITS |

|------------------------------------------------------------------|-------------------------|--------------------------------------------------|--------------------|------|-------|------|-------|

| Wake-Up Input<br>Maximum Pulse Width                             | t <sub>WUMAX</sub>      |                                                  |                    | 85   | 95    | 110  | μs    |

| WU/HEART Output Low<br>Time                                      | twul                    | Valid wake-up cond<br>WU/HEART configu<br>output | 150                | 200  | 250   | μs   |       |

| MCLK CLOCK                                                       |                         |                                                  |                    |      |       |      |       |

|                                                                  |                         |                                                  | ClkDiv[2:0] = 000  | 3.55 | 3.684 | 3.81 |       |

|                                                                  |                         |                                                  | ClkDiv [2:0] = 001 | 7.10 | 7.37  | 7.62 |       |

| MCLK Output<br>Frequency                                         | <b>f</b> MCLK           | MCLKDIR = high                                   | ClkDiv [2:0] = 010 | 14.1 | 14.71 | 15.3 | MHz   |

| Frequency                                                        |                         |                                                  | ClkDiv [2:0] = 011 | 28   | 29.4  | 31   |       |

|                                                                  |                         |                                                  | ClkDiv [2:0] = 100 | 1.78 | 1.843 | 1.91 |       |

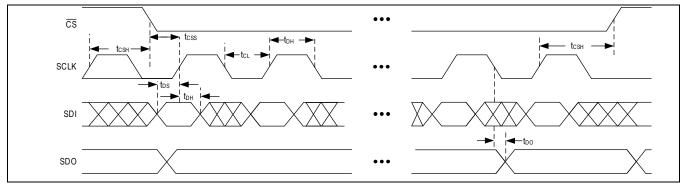

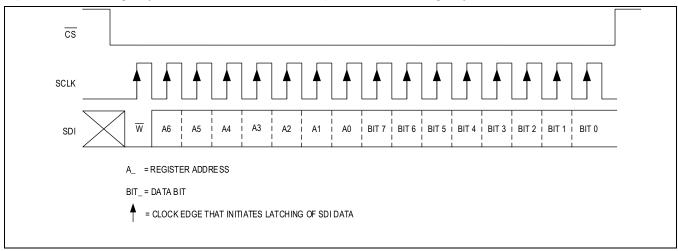

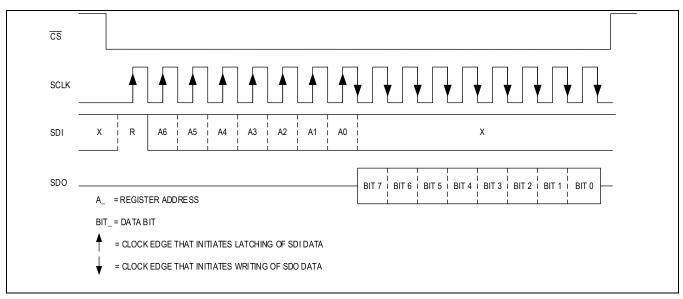

| SPI TIMING (CS, SCLK, S                                          | SDI, SDO) ( <u>Figu</u> | <u>re 6</u> )                                    |                    |      |       |      | -     |

| Maximum SCLK<br>Frequency                                        | fSPI_MAX                | With 50% duty cycl                               | e on SCLK          |      |       | 15   | MHz   |

| SCLK Clock Period                                                | t <sub>CH+CL</sub>      |                                                  |                    | 40   |       |      | ns    |

| SCLK Pulse Width High                                            | tсн                     |                                                  |                    | 8    |       |      | ns    |

| SCLK Pulse Width Low                                             | t <sub>CL</sub>         |                                                  |                    | 32   |       |      | ns    |

| CS Fall to SCLK Rise<br>Time                                     | t <sub>CSS</sub>        |                                                  |                    | 9    |       |      | ns    |

| SCLK Rise to $\overline{CS}$ Rise<br>Hold Time                   | t <sub>CSH</sub>        |                                                  |                    | 11   |       |      | ns    |

| SDI Hold Time                                                    | t <sub>DH</sub>         |                                                  |                    | 6    |       |      | ns    |

| SDI Setup Time                                                   | t <sub>DS</sub>         |                                                  |                    | 8    |       |      | ns    |

| SDO Output Data<br>Propagation Delay                             | t <sub>DO</sub>         |                                                  |                    |      |       | 20   | ns    |

| SDO Rise and Fall<br>Times                                       | t <sub>FT</sub>         |                                                  |                    |      | 0.5   | 4    | ns    |

| Minimum $\overline{\text{CS}}$ Pulse                             | tcsw                    |                                                  |                    |      | 20    |      | ns    |

| EMC TOLERANCE                                                    |                         |                                                  |                    |      |       |      |       |

| ESD Protection<br>(V <sub>24</sub> , C/Q, DO, DI Pins<br>to GND) |                         | IEC 61000-4-2 con                                | tact discharge     |      | ±3    |      | kV    |

| ESD Protection<br>(All Other Pins)                               |                         | Human body model                                 |                    |      | ±2    |      | kV    |

| Surge Protection<br>(V <sub>24</sub> , C/Q, DO, DI Pins)         | V <sub>SRG</sub>        | 500Ω 8/20µs surge                                | to ground          |      | ±1.2  |      | kV    |

Note 1: All devices 100% production tested at T<sub>A</sub> = 25°C. Limits over the operating temperature range are guaranteed by design.

Note 2: Not production tested. Guaranteed by design.

**Note 3:** V<sub>DROP</sub> is measured as the voltage from the driver output to GND (V<sub>DRIVER</sub> - V<sub>GND</sub>) when measuring the low-side driver current limit and as (V<sub>24</sub> - V<sub>DRIVER</sub>) when measuring the high-side current limit.

MAX22516

## MAX22516

## **Timing Diagrams**

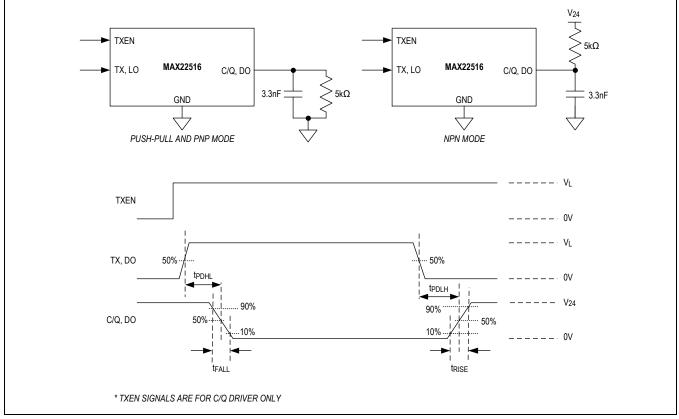

Figure 1. C/Q Driver Propagation Delays

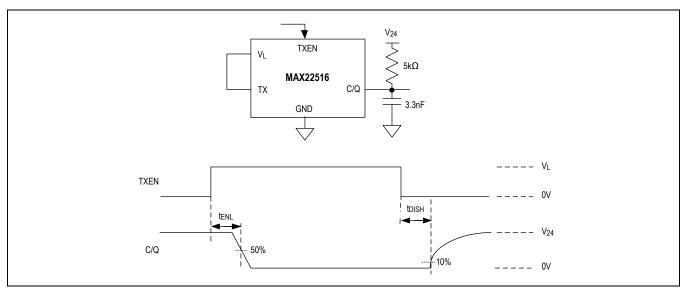

Figure 2. C/Q Driver Enable Low and Disable High Timing

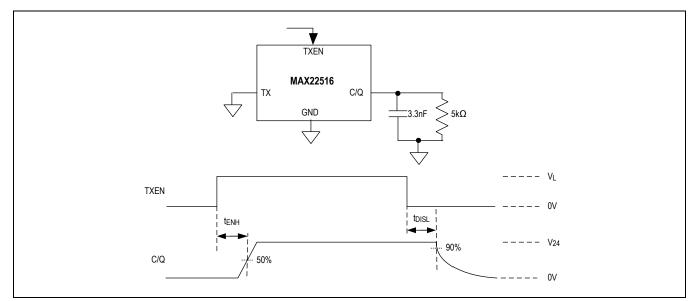

Figure 3. C/Q Driver Enable High and Disable Low Timing

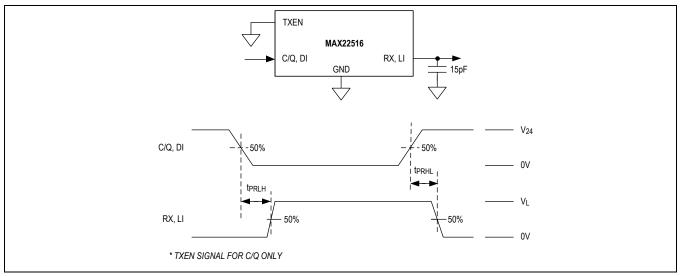

Figure 4. C/Q Receiver Timing

Figure 5. Wake-Up Detection

Figure 6. SPI Timing Diagram

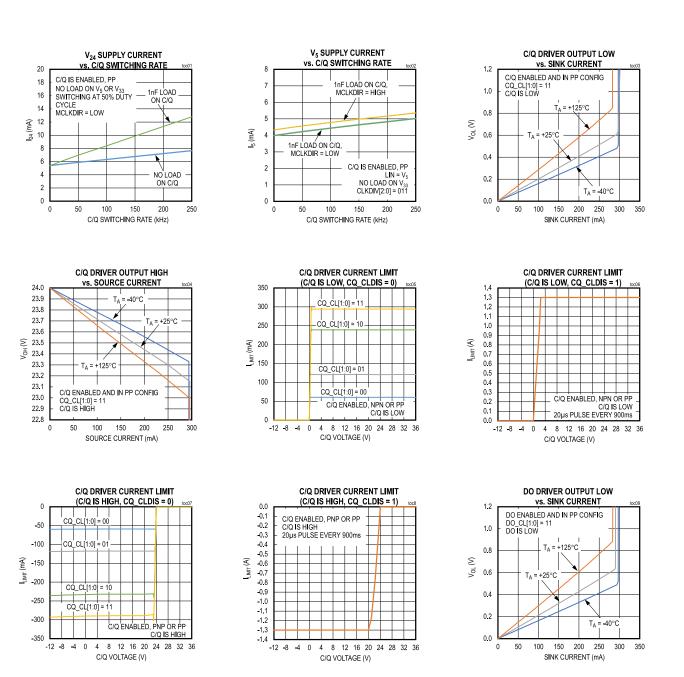

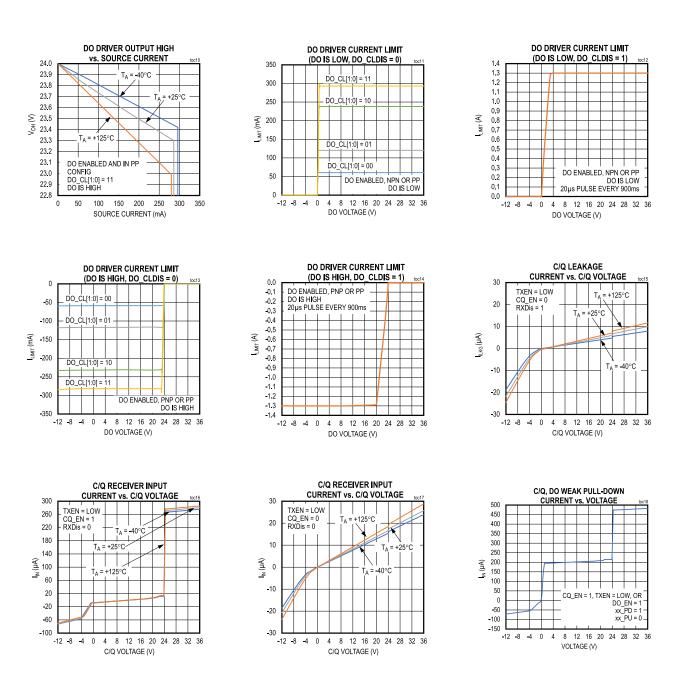

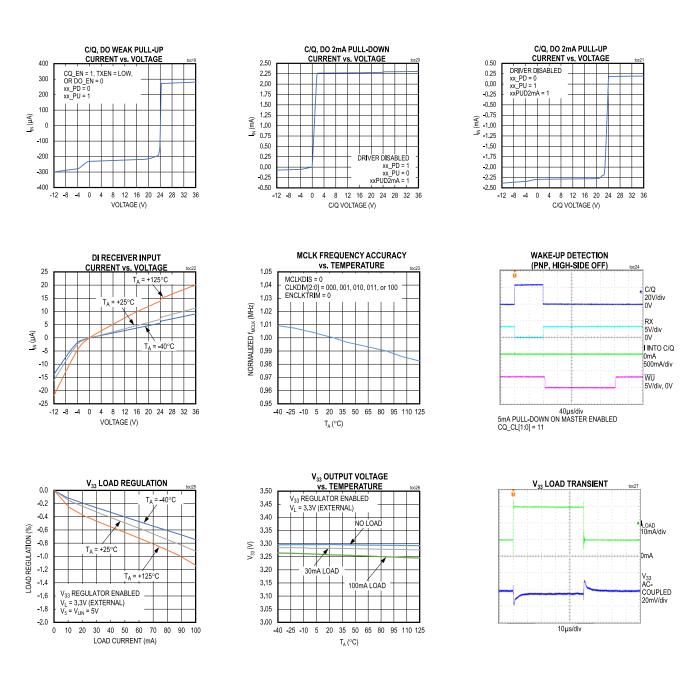

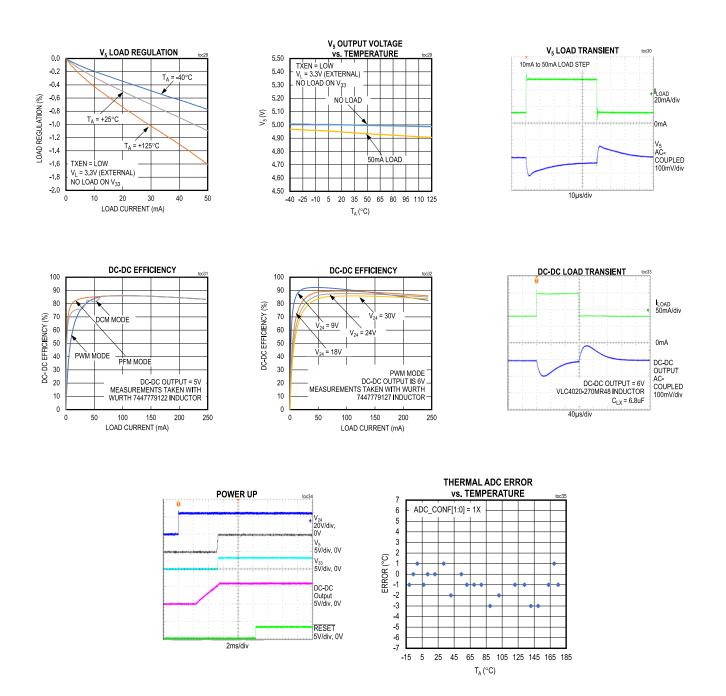

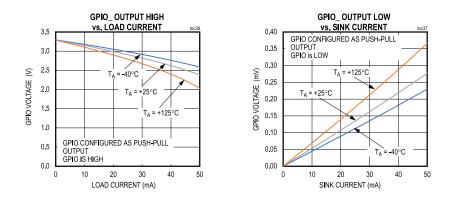

## **Typical Operating Characteristics**

www.analog.com

## **Pin Configurations**

## **Pin Descriptions**

| F           | PIN        |                  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|-------------|------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TQFN        | WLP        | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| POWER       |            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 12          | A2         | V <sub>CCB</sub> | Internal 5V Supply Regulator Output. Bypass V <sub>CCB</sub> to GND with a 1 $\mu$ F capacitor as close to the device as possible. V <sub>CCB</sub> can supply an external load up to 5mA.                                                                                                                                                                                                                                   |  |  |  |  |

| 16          | A4         | PV <sub>24</sub> | Active Diode Output and DC-DC Input. Bypass PV <sub>24</sub> with an external 1µF capacitor as close to the device as possible.                                                                                                                                                                                                                                                                                              |  |  |  |  |

|             |            |                  | 5V Linear Regulator Input. Connect LIN to the output of the DC-DC circuit, to the $PV_{24}$                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 15          | B4         | LIN              | supply, or to an external supply between 6V and 36V. Bypass LIN to GND with a $1\mu$ F capacitor. Connect LIN to V <sub>5</sub> to disable the 5V linear regulator.                                                                                                                                                                                                                                                          |  |  |  |  |

| 10          | B1         | V <sub>5</sub>   | 5V Linear Regulator Output/ Supply Input. V <sub>5</sub> is the output of the internal 5V linear regulator. Bypass V <sub>5</sub> to GND with a 1 $\mu$ F capacitor as close to the device as possible. To disable the 5V linear regulator, connect LIN to V <sub>5</sub> .<br>5V is required on V <sub>5</sub> for normal operation. If the 5V regulator is disabled, apply an external 5V power supply to V <sub>5</sub> . |  |  |  |  |

| 25, 26      | C6, C7     | V <sub>24</sub>  | Supply Voltage Input. Connect all $V_{24}$ pins together. Connect $V_{24}$ to the L+ terminal of the IO-Link connector, or to an external supply. Bypass $V_{24}$ to GND with a 10nF capacitor as close to the device as possible.                                                                                                                                                                                           |  |  |  |  |

| 23, 28      | B6, E7     | GNDCQ            | C/Q Driver IO-Link Ground. Connect GNDCQ to the L- terminal of the IO-Link connector<br>and to GND. For more information, see the <u>Layout and Grounding</u> section.                                                                                                                                                                                                                                                       |  |  |  |  |

| 4           | E2         | VL               | Logic IO Supply Input. Bypass V <sub>L</sub> to GND with a 1 $\mu$ F capacitor as close to the device as possible. V <sub>L</sub> sets the logic levels for all logic signals. Connect V <sub>L</sub> to V <sub>33</sub> , V <sub>5</sub> , or to an external voltage between 2.5V and 5.5V.                                                                                                                                 |  |  |  |  |

| 1, 14       | B3, C3, C4 | GND              | Ground. Connect GND to GNDCQ.<br>All GND pins must be connected. For more information, see the <u>Layout and Grounding</u> section.                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 36          | D4, D5     | GNDD             | Digital Ground. Connect GNDD to GND.<br>All GND pins must be connected. For more information, see the <u>Layout and Grounding</u> section.                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 9           | B2         | V <sub>33</sub>  | 3.3V Linear Regulator Output. Bypass V <sub>33</sub> to GND with a 1 $\mu$ F capacitor as close to the device as possible. A bypass capacitor is not required for applications where V <sub>33</sub> is disabled.                                                                                                                                                                                                            |  |  |  |  |

| EP          | -          | EP               | Exposed Pad. Connect EP to GND. For more information, see the Layout and Grounding section.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| DC-DC RE    | GULATOR    |                  |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

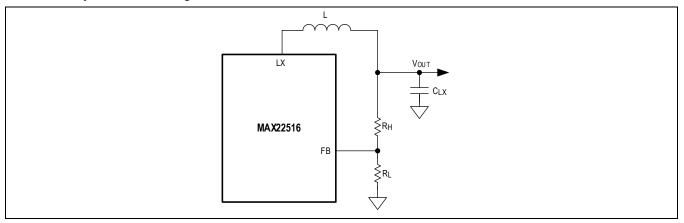

| 13          | A3         | LX               | Switching Output of the Integrated DC-DC Converter. Connect an inductor between LX and the output capacitor to generate a voltage with the DC-DC circuit. For more information, see the <u>Integrated DC-DC Regulator</u> section.                                                                                                                                                                                           |  |  |  |  |

| 11          | A1         | FB               | DC-DC Buck Regulator Feedback Input. Connect FB to the tap of a resistor divider<br>between the output of the DC-DC and GND. For more information, see the <u>Integrated DC-DC Regulator</u> section.<br><u>DC Regulator</u> section.<br>Connect FB to V <sub>CCB</sub> if the DC-DC is not used.                                                                                                                            |  |  |  |  |

| 24V I/O LIN |            | E                |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 24          | B7         | C/Q              | C/Q IO-Link Transceiver Input/ Output. Drive TXEN high and set CQ_EN = 1 to enable the C/Q driver. The logic on C/Q is the logic inverse of the signal on TX and RX, by default.                                                                                                                                                                                                                                             |  |  |  |  |

| 27          | D7         | DO               | DO Auxiliary Driver Output. Set DO_EN = 1 to enable the DO driver output. DO is the logic inverse of the LO input. DO is high impedance when DO_EN = 0.                                                                                                                                                                                                                                                                      |  |  |  |  |

| 22          | A7         | DI               | Auxiliary Digital Input. LI is the logic inverse of the signal on the DI input. The DI receiver is always enabled.<br>Connect a $1k\Omega$ series resistor between the signal and DI pin.                                                                                                                                                                                                                                    |  |  |  |  |

| AUXILIAR    |            |                  |                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 30          | D6         | LO               | DO Driver Logic Input. DO is the logic inverse of the signal on LO when DO is enabled.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 00          | 50         | 10               | Do Briter Logio input. Do is the logio inverse of the signal of LO when DO is enabled.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 29         | F7          | LI             | DI Receiver Logic Output. LI is the logic inverse of the signal on the DI input. LI is always enabled.                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI INTERF | ACE         |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 37         | E4          | SDO            | Serial Data Output. Connect SDO on the MAX22516 to the serial data input on the SPI host controller. SDO is high impedance when $\overline{CS}$ is high.                                                                                                                                                                                                                                                                                                                                                     |

| 38         | F3          | SCLK           | Serial Clock Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 39         | E3          | SDI            | Serial Data Input. Connect SDI on the MAX22516 to the serial data output on the SPI host controller.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 40         | F2          | CS             | SPI Chip-Select Input. Drive $\overline{CS}$ low to start a read/write cycle. The cycle ends when $\overline{CS}$ is driven high.                                                                                                                                                                                                                                                                                                                                                                            |

| 17         | D3          | CRCEN          | CRC Enable for SPI interface. Connect CRCEN to V <sub>L</sub> to enable the CRC for the SPI interface.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7          | C2          | CRCERR         | Open-Drain SPI CRC Error Output. CRCERR asserts low when a CRC error has been detected in the last SPI communication.                                                                                                                                                                                                                                                                                                                                                                                        |

| VOLTAGE I  | MONITOR     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

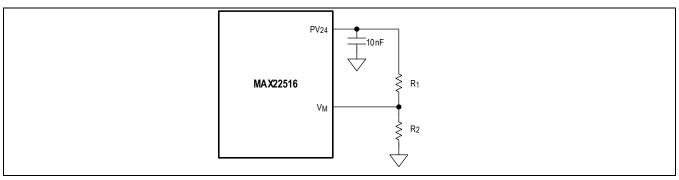

| 21         | A6          | V <sub>M</sub> | Voltage Monitor Input. Connect a resistor divider between the monitored supply voltage (for example, $PV_{24}$ ) and GND to define the power-OK threshold for the monitored voltage. For more information, see the <u>Voltage Monitor Input</u> section.                                                                                                                                                                                                                                                     |

| INTERRUP   | TS AND INDI | CATORS         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |