#### MAX20355

Click <u>here</u> to ask an associate for production status of specific part numbers.

Power Line Communication with ModelGauge Fuel Gauge and Buck-Boost Converter

### **General Description**

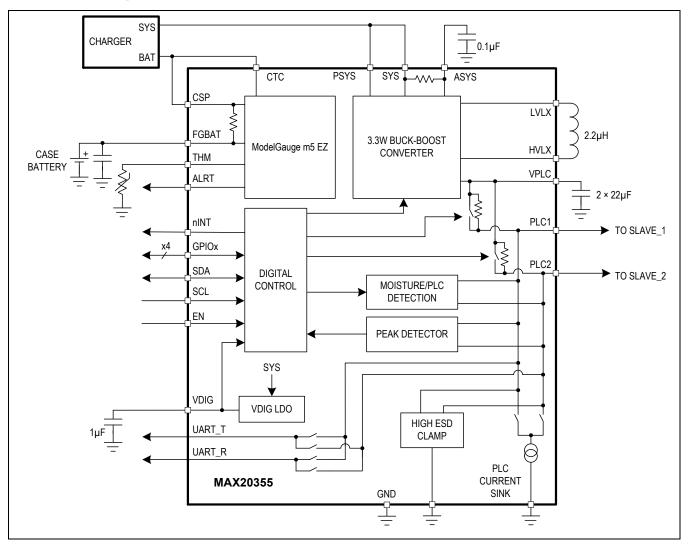

The MAX20355 is a Power Line Communication (PLC) master with ModelGauge<sup>TM</sup> m5 EZ fuel gauge and buckboost converter. The MAX20355 and MAX20357 provide a complete system solution for charging and data transfer between a charging case and a battery-powered device over a single contact.

The PLC interface is capable of 100kpbs throughput while simultaneously providing 400mA of total charging/system current. A 4Mbaud half-duplex data-only UART mode provides an easy and fast method for firmware updates, debugging interface, and factory modes.

MAX20355 utilizes a 3.3W buck-boost converter with dynamic voltage scaling (DVS) to automatically manage the charging voltage based on the slave device MAX20357 control signal.

Additional features include comprehensive slave device insertion and removal notifications, moisture detection, overcurrent protection, and 8kV contact rated ESD protection on the PLC outputs.

### **Applications**

- TWS Headphones

- Augmented Reality Glasses

- Wearable Devices

#### **Benefits and Features**

- Power Line Communication (PLC) Interface

- 100kpbs System Throughput

- · 166.7kbps Bit Rate

- · 200mA per Output Charging Current

- Automatic Earbud Insertion/Removal Detection

- 4Mbaud, Half-Duplex, Data-Only UART Mode

- PLC Controllable GPIOs, Reset and Shipping Mode

- High-Efficiency Autonomous Charging System

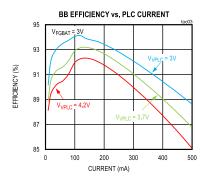

- 90% End-to-End Charging Efficiency from Master to Slave Battery

- · 200mA per Output Charging/System Current

- Integrated 3.3W Buck-Boost

- Automatic DVS for each Earbud to Optimize Charging Efficiency

- Robust PLC Output Protection Features

- Highly Flexible Moisture Detection Block

- · Programmable Overcurrent Protection

- · 8kV Contact ESD Protection

- · Small Solution Size

- · Small Single 1608 Inductor

- 3.08mm x 2.83mm, 42-Bump Wafer-Level Package (WLP)

Ordering Information appears at end of data sheet.

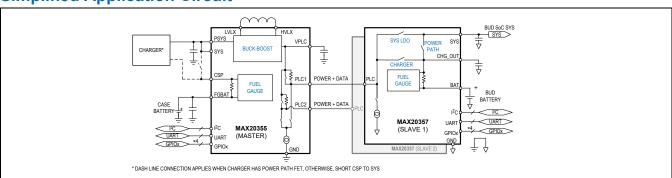

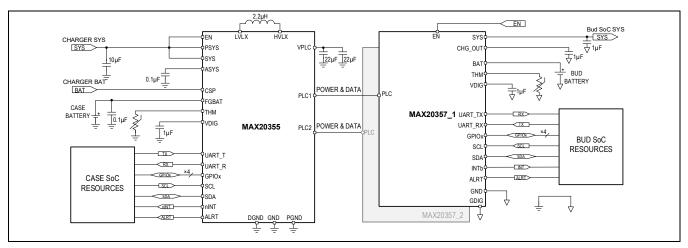

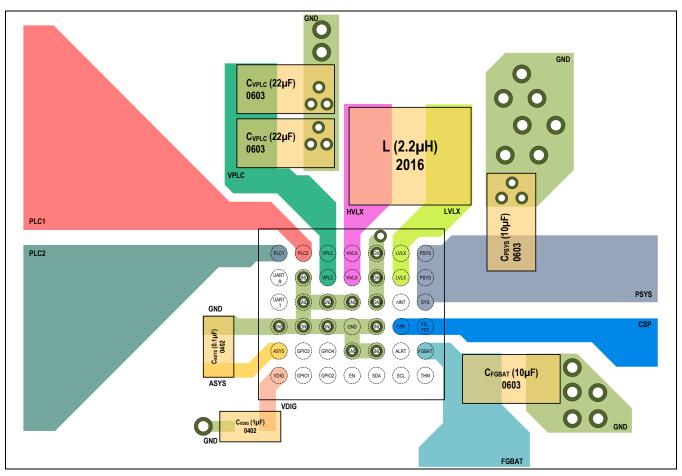

### **Simplified Application Circuit**

ModelGauge is a trademark of Maxim Integrated Products, Inc.

### **TABLE OF CONTENTS**

| General Description                                        | 1  |

|------------------------------------------------------------|----|

| Applications                                               | 1  |

| Benefits and Features                                      | 1  |

| Simplified Application Circuit                             | 1  |

| Absolute Maximum Ratings                                   | 6  |

| Package Information                                        | 6  |

| Electrical Characteristics                                 | 6  |

| Typical Operating Characteristics                          | 12 |

| Pin Configuration                                          | 15 |

| Pin Descriptions                                           | 15 |

| Functional Diagram                                         | 17 |

| Detailed Description                                       | 17 |

| Power Line Communication (PLC)                             | 18 |

| PLC PING                                                   | 18 |

| LISTEN Command and Continuously Updated Information        | 19 |

| Master Commands                                            | 19 |

| Slave Commands                                             | 20 |

| Mailbox Data Transfer (DOUT_REQ)                           | 21 |

| Bulk Data Transfer (FIFO)                                  | 22 |

| Half-Duplex UART Passthrough Interface                     | 25 |

| Autonomous Optimized Battery Charging                      | 27 |

| Charger Battery Voltage Tracking Loop                      | 27 |

| Charger Voltage Tracking Algorithm                         | 29 |

| Mono-Slave and Dual-Slave Mode                             | 30 |

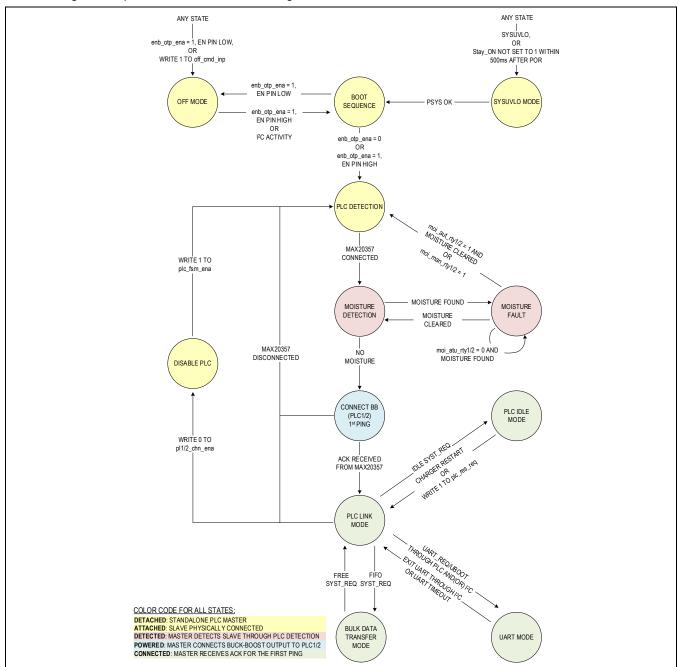

| PLC Operation Modes                                        | 32 |

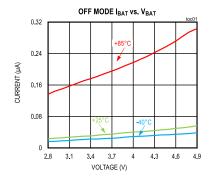

| OFF Mode                                                   | 33 |

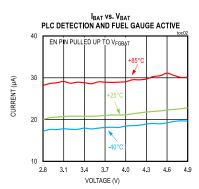

| PLC Detection Mode                                         | 33 |

| Moisture Detection                                         | 35 |

| PLC IDLE Mode                                              | 37 |

| Master/Slave Resets and UBOOT Mode                         | 38 |

| General Purpose Input Output (GPIO)                        | 38 |

| Integrated Protection Features                             | 38 |

| Current Limited PLC Outputs                                | 38 |

| High ESD Protected ESD Outputs                             | 38 |

| ModelGauge M5 EZ Fuel Gauge with Integrated Sense Resistor | 39 |

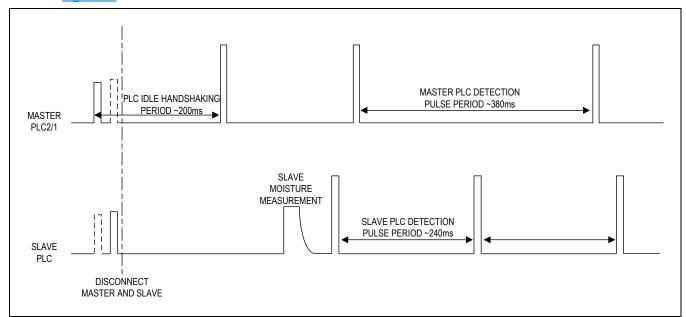

| ModelGauge m5 EZ Performance                               | 39 |

| Application Notes                                          | 40 |

| Standard Register Formats                  | 40 |

|--------------------------------------------|----|

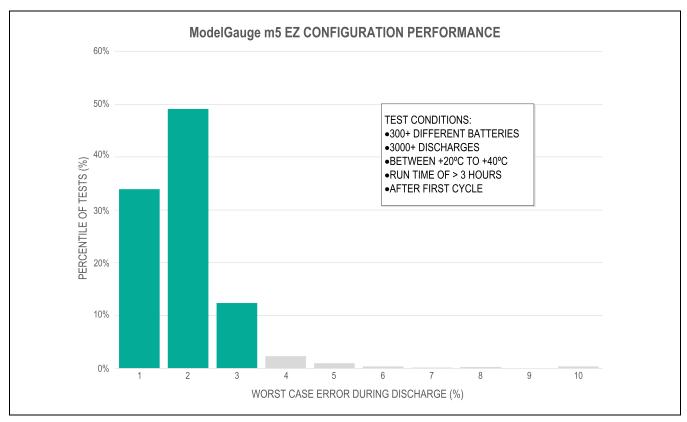

| ModelGauge m5 Algorithm                    | 41 |

| Analog Measurements                        | 42 |

| Voltage Measurement                        | 42 |

| MaxMinVolt Register (0x1B)                 | 42 |

| Current Measurement                        | 42 |

| Temperature Measurement                    | 43 |

| Temp Register (0x08)                       | 43 |

| MaxMinTemp Register (0x1A)                 | 43 |

| Power Measurement                          | 43 |

| Alert Function                             | 43 |

| Serial Number Feature                      | 44 |

| ModelGauge m5 Memory Space                 | 44 |

| I <sup>2</sup> C Serial Communication      | 45 |

| General Description                        | 45 |

| Features                                   | 45 |

| I <sup>2</sup> C Simplified Block Diagram  | 45 |

| I <sup>2</sup> C System Configuration      | 45 |

| I <sup>2</sup> C Interface Power           | 46 |

| I <sup>2</sup> C Data Transfer             | 46 |

| I <sup>2</sup> C Start and Stop Conditions | 46 |

| I <sup>2</sup> C Acknowledge Bit           | 46 |

| I <sup>2</sup> C Slave Address             | 47 |

| I <sup>2</sup> C Clock Stretching          | 47 |

| I <sup>2</sup> C General Call Address      | 47 |

| I <sup>2</sup> C Device ID                 | 47 |

| I <sup>2</sup> C Communication Speed       | 47 |

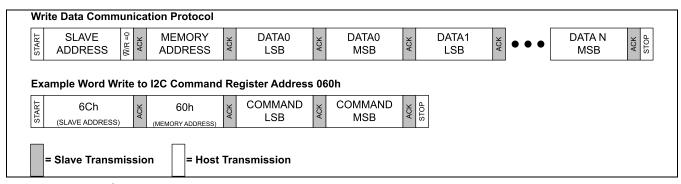

| I <sup>2</sup> C Communication Protocols   | 48 |

| Reading from a Single Register             |    |

| Reading from Sequential Registers          | 51 |

| Applications Information                   | 52 |

| PLC Current Sink and Detection Threshold   |    |

| Typical Application Circuit                | 53 |

| PCB Layout Guidelines                      | 53 |

| Register Map                               | 54 |

| Ordering Information                       | 91 |

### **LIST OF FIGURES**

| Figure 1. Simplified Scheme of Power Line Communication (PLC)                | 18 |

|------------------------------------------------------------------------------|----|

| Figure 2. Periodic PING                                                      |    |

| Figure 3. Sending Commands from the Slave                                    |    |

| Figure 4. Master to Slave Mailbox Data Transfer                              | 21 |

| Figure 5. Slave to Master Mailbox Data Transfer                              | 22 |

| Figure 6. Bulk Data Transfer Implementation                                  |    |

| Figure 7. Master to Slave Bulk Data Transfer                                 |    |

| Figure 8. Slave to Master Bulk Data Transfer                                 | 25 |

| Figure 9. UART Interface                                                     |    |

| Figure 10. UART Automatic Exit Through UART Timeout                          | 27 |

| Figure 11. Polling Structure of Automatic Charging Algorithm                 | 28 |

| Figure 12. Slave Voltage Control Algorithm                                   | 29 |

| Figure 13. Buck-Boost Converter Block Diagram                                |    |

| Figure 14. MAX20355 Operating Modes                                          | 32 |

| Figure 15. PLC and Moisture Detection Block Diagrams                         | 33 |

| Figure 16. Active Master and Active Slave Connection                         |    |

| Figure 17. Active Master and Dead Slave Connection                           |    |

| Figure 18. Dead Master and Active Slave Connection                           |    |

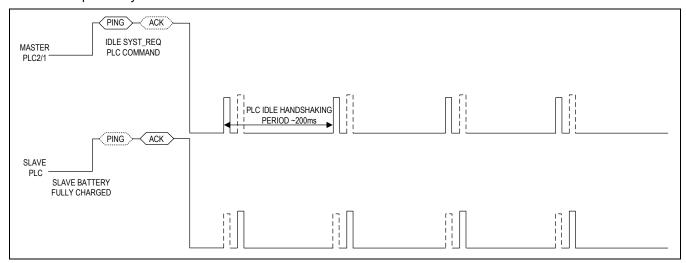

| Figure 19. Enter PLC IDLE Mode After Slave Battery is Fully Charged          |    |

| Figure 20. Master and Slave Disconnection While in PLC IDLE Mode             |    |

| Figure 21. ModelGauge m5 EZ Configuration Performance                        |    |

| Figure 22. ModelGauge m5 Algorithm                                           |    |

| Figure 23. I <sup>2</sup> C Simplified Block Diagram                         | 45 |

| Figure 24. I <sup>2</sup> C System Configuration                             | 46 |

| Figure 25. I <sup>2</sup> C Start and Stop Conditions                        |    |

| Figure 26. Acknowledge Bit                                                   | 47 |

| Figure 27. Slave Address Example                                             | 47 |

| Figure 28. Writing to a Single 8-bit Register with the Write Byte Protocol   | 48 |

| Figure 29. Writing to Sequential Registers X to N                            | 49 |

| Figure 30. Example I <sup>2</sup> C Write 16-bit Data Communication Sequence | 50 |

| Figure 31. Reading from a Single Register with the Read Byte Protocol        | 50 |

| Figure 32. Reading Continuously from Sequential Registers X to N             |    |

| Figure 33. PLC Current Sink and Detection Threshold                          | 52 |

| Figure 34. Typical Application Circuit                                       | 53 |

| Figure 35. Layout Guideline                                                  | 54 |

#### MAX20355

### Power Line Communication with ModelGauge Fuel Gauge and Buck-Boost Converter

#### **LIST OF TABLES** Table 1. Table 2. Table 3. Table 4. Table 5. Table 6. Optimized Battery Voltage Tracking.......30 Table 7. Table 8. Table 9. Table 10. Table 11. Table 12. ModelGauge m5 Register Memory Map .......44 Table 13. Table 14. PLC Detection Pair (MAX20357 Data Packet)......52

### **Absolute Maximum Ratings**

| FGBAT, PSYS, SYS to GND             | 0.3V to +6V   |

|-------------------------------------|---------------|

| CSP to FGBAT                        | 10mV to +10mV |

| ASYS to SYS                         | 0.1V to +0.1V |

| VDIG to GND                         | 0.3V to +2V   |

| LVLX to GND                         | 0.3V to +6V   |

| LVLX to PSYS                        | +0.3V         |

| HVLX to GND                         | 0.3V to +6V   |

| HVLX to VPLC                        | +0.3V         |

| PLC1, PLC2 to GND                   | 0.3V to +6V   |

| VPLC to GND                         | 0.3V to +6V   |

| SDA, SCL, INTb to GND               | 0.3V to +6V   |

| EN, GPIO1, GPIO2, GPIO3, GPIO4 to G | ND0.3V to +6V |

| THM to GND                          | 0.3V to +6V   |

| THM to FGBAT                        | +0.3V         |

|                                     |               |

| ALRT to GND                                                                         | 0.3V to +17V        |

|-------------------------------------------------------------------------------------|---------------------|

| UART_R, UART_T                                                                      | 0.3V to +6V         |

| CTC to GND                                                                          | 0.3V                |

| CTC to FGBAT                                                                        | +0.3V               |

| GND, PGND, DGND                                                                     | 0.3V to +0.3V       |

| Operating Temperature Range                                                         | 40°C to +85°C       |

| Junction Temperature                                                                | +150°C              |

| Storage Temperature Range                                                           | 40°C to +150°C      |

| Soldering Temperature (reflow)                                                      | +260°C              |

| FGBAT to CSP sense resistor current 100k hours)                                     |                     |

| FGBAT to CSP sense resistor curred, 250ms maximum pulse widt cycle, 1% utilization) | h, 10% maximum duty |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### WLP

| Package Code                                           | W422B3+1                       |

|--------------------------------------------------------|--------------------------------|

| Outline Number                                         | <u>21-100524</u>               |

| Land Pattern Number                                    | Refer to Application Note 1891 |

| Thermal Resistance, Four Layer Board:                  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 44.11°C/W                      |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | NA                             |

### **Electrical Characteristics**

$(T_A = -40$ °C to +85°C, FGBAT = +2.7V to +4.9V, SYS = +2.8V to 5.5V,  $C_{SYS} = 10\mu F$ ,  $C_{DIG} = 1\mu F$ ,  $L_{VLX} = 2.2\mu H$  (ESR < 200mΩ),  $C_{ASYS} = 0.1\mu F$ ,  $C_{VPLC} = 8\mu F$ ,  $C_{FGBAT} = 10\mu F$ , dual-slave configuration if not otherwise specified)

| PARAMETER                         | SYMBOL                  | CONDITIONS     | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------|-------------------------|----------------|------|------|------|-------|

| POWER SUPPLY (SYS,                | PSYS, ASYS, FG          | BBAT, VDIG)    |      |      |      |       |

| V <sub>SYS</sub> Voltage Range    | V <sub>SYS</sub>        |                | 2.8  |      | 5.5  | V     |

| V <sub>SYS</sub> Start-Up Voltage | V <sub>SYS_STUP</sub>   |                | 3.1  |      |      | V     |

| FGBAT Voltage Range               | V <sub>FGBAT</sub>      |                | 2.7  |      | 4.9  | V     |

| FGBAT Start-Up<br>Voltage         | V <sub>FGBAT_STUP</sub> |                | 3.1  |      |      | V     |

| CVC DOD Throubold                 | V <sub>SYS_POR_R</sub>  | Supply rising  |      | 2.47 | 2.69 | .,    |

| SYS POR Threshold                 | V <sub>SYS_POR_F</sub>  | Supply falling | 2.25 | 2.41 |      | V     |

| Vsys_uvlo_r Su                    | Supply rising           |                | 2.75 | 2.85 |      |       |

| SYS UVLO Threshold                | V <sub>SYS UVLO F</sub> | Supply falling | 2.6  | 2.70 |      | V     |

$(T_A = -40$ °C to +85°C, FGBAT = +2.7V to +4.9V, SYS = +2.8V to 5.5V,  $C_{SYS} = 10\mu F$ ,  $C_{DIG} = 1\mu F$ ,  $L_{VLX} = 2.2\mu H$  (ESR < 200mΩ),  $C_{ASYS} = 0.1\mu F$ ,  $C_{VPLC} = 8\mu F$ ,  $C_{FGBAT} = 10\mu F$ , dual-slave configuration if not otherwise specified)

| PARAMETER                              | SYMBOL                       | CONE                            | DITIONS                                                                         | MIN  | TYP  | MAX        | UNITS    |

|----------------------------------------|------------------------------|---------------------------------|---------------------------------------------------------------------------------|------|------|------------|----------|

| FGBAT UVLO                             | V <sub>FGAT_UVLO_</sub><br>R | Supply rising                   |                                                                                 |      | 2.5  | 2.7        | .,       |

| Threshold                              | V <sub>FGAT_UVLO_</sub>      | Supply falling                  |                                                                                 | 2.2  | 2.4  |            | V        |

| VDIG POR Threshold                     | V <sub>DIG_POR_R</sub>       | Supply rising                   |                                                                                 |      | 1.42 | 1.51       | V        |

| VDIG POR Threshold                     | VDIG_POR_F                   | Supply falling                  |                                                                                 | 1.16 | 1.34 |            | V        |

|                                        |                              | Low_pwr_ena = 1                 | EN = 1,<br>master/slave<br>detection<br>EN = 1, idle mode<br>(low-current PU/PU |      | 4    |            | μA       |

| Supply Current                         | I <sub>SYS</sub>             | V <sub>OVLO</sub> = 5.5V;       | ping-pong)  EN = 1, PLC lines powered, PING active                              |      | 300  |            | <b>,</b> |

|                                        |                              | SYS = 3.6V                      | EN = 1, PLC lines<br>powered, active<br>data transmission<br>with min I PLC     |      | 72   |            | mA       |

| Shutdown Supply<br>Current             | I <sub>SYS_SHDN</sub>        | EN = 0, device disabled         |                                                                                 |      | 0.1  | 1          | μΑ       |

| BUCK-BOOST CONVER                      |                              | X, VPLC)                        |                                                                                 |      |      |            | ·        |

| Output Voltage Range                   | V <sub>OUT</sub>             |                                 |                                                                                 | 2.5  |      | $V_{OVLO}$ | V        |

| Programmable Output Voltage Resolution | V <sub>OUT_STEP</sub>        |                                 |                                                                                 |      | 13.7 |            | mV       |

| Max Inductor Current                   | I <sub>L_MAX</sub>           |                                 |                                                                                 |      | 2    |            | Α        |

| Max Output Power                       | P <sub>MAX</sub>             | V <sub>SYS</sub> ≥ 2.9V; i2c_zc | ccm_enb = 0                                                                     | 3.3  |      |            | W        |

| Overvoltage Threshold                  | V <sub>OVLO</sub>            | Programmable in 10              | 00mV steps                                                                      | 4.8  |      | 5.5        | V        |

| POWER LINE COMMUN                      | ICATION (PLC1,               | PLC2)                           |                                                                                 |      |      |            |          |

| Data Throughput                        | T <sub>Pdat</sub>            | Maximum output cu               | rrent                                                                           |      | >100 |            | kbps     |

|                                        |                              |                                 |                                                                                 |      | 0.2  | 0.4        |          |

| PLC RCHG                               | R <sub>CHG</sub>             | Mono-slave PLC1 = shorted       | PLC2 internally                                                                 |      | 0.1  | 0.2        | Ω        |

|                                        |                              | I_PLC = 200mA                   |                                                                                 | 1.8  | 2    | 2.2        |          |

| PLC RTX                                | R <sub>TX</sub>              | I_PLC = 400mA                   | Mono-slave PLC1<br>= PLC2 internally<br>shorted                                 | 0.9  | 1    | 1.1        | Ω        |

| Receiver Threshold R <sub>TX_T</sub>   |                              |                                 | PLC_CONFIG0[1:0<br>] = 00                                                       |      | -40  |            | mV       |

|                                        | R=v =::                      | DI C1/2 - 4\/                   | PLC_CONFIG0[1:0<br>] = 01                                                       |      | -56  |            |          |

|                                        | INIX_FH                      | $R_{TX\_TH}$ PLC1/2 = 4V        | PLC_CONFIG0[1:0<br>] = 10                                                       |      | -70  |            |          |

|                                        |                              |                                 | PLC_CONFIG0[1:0<br>] = 11                                                       |      | -84  |            |          |

| OVERCURRENT PROTE                      | CTION                        |                                 |                                                                                 |      |      | _          |          |

$(T_A = -40$ °C to +85°C, FGBAT = +2.7V to +4.9V, SYS = +2.8V to 5.5V,  $C_{SYS} = 10\mu F$ ,  $C_{DIG} = 1\mu F$ ,  $L_{VLX} = 2.2\mu H$  (ESR < 200mΩ),  $C_{ASYS} = 0.1\mu F$ ,  $C_{VPLC} = 8\mu F$ ,  $C_{FGBAT} = 10\mu F$ , dual-slave configuration if not otherwise specified)

| PARAMETER                              | SYMBOL                       | CON                     | DITIONS                                      | MIN  | TYP                | MAX                            | UNITS |

|----------------------------------------|------------------------------|-------------------------|----------------------------------------------|------|--------------------|--------------------------------|-------|

| D                                      |                              |                         |                                              | 100  |                    | 400                            |       |

| Programmable Overcurrent Range         | I <sub>LIMIT</sub>           | Mono-slave PLC1 shorted | = PLC2 internally                            | 200  |                    | 800                            | mA    |

| Programmable<br>Overcurrent Resolution | I <sub>LIMIT_</sub> STEP     | Mono-slave PLC1 shorted | = PLC2 internally                            |      | 50<br>100          |                                | mA    |

| Overcurrent Accuracy                   | ILIMIT_ACC                   | PLC RCHG<br>PLC RTX     |                                              |      |                    | 20<br>30                       | %     |

| Overcurrent Response Time              | I <sub>LIMIT_DEL</sub>       |                         |                                              |      | 16                 |                                | μs    |

| MOISTURE DETECTION                     | 1                            |                         |                                              |      |                    |                                |       |

| Impedance<br>Measurement Range         | R <sub>MOIST_RANG</sub><br>E |                         |                                              | 6    |                    | 1400                           | kΩ    |

| Impedance<br>Measurement Accuracy      | R <sub>MOIST_ACC</sub>       |                         |                                              |      | 10                 |                                | %     |

| Current Source<br>Accuracy             | ID_ACC                       | PLC1/2 = 1.5V           | I <sub>ID</sub> = 1, 4, 16, 64μΑ             | -5.5 |                    | +5.5                           | %     |

| Current Source                         | I <sub>ID</sub>              |                         |                                              |      | 1<br>4<br>16<br>64 |                                | μΑ    |

| ADC Resolution                         | ADC_RES                      |                         |                                              |      | 8                  |                                | bit   |

| ADC Voltage Step                       | ADC_STEP                     |                         |                                              |      | 5.9                |                                | mV    |

| ADC Full-Scale Error                   | ADC_ERR                      |                         |                                              | -2   | 0.0                | +2                             |       |

| ADC Noise Filtering                    | ADC NOISE                    |                         |                                              |      | 100                |                                | μs    |

| ADC Full Scale                         | ADC SCALE                    |                         |                                              |      | 1.5                |                                |       |

| PLC COMMUNICATION                      | _                            |                         | L                                            |      |                    |                                |       |

| Current Sink Accuracy                  | I <sub>SINK_ACC</sub>        |                         |                                              | -14  |                    | +14                            | %     |

|                                        |                              |                         | PLC_CONFIG0[7:6]<br>= 00                     |      | 85                 |                                |       |

| Current Sink                           | I <sub>SINK</sub>            | PLC1/2 = 4V             | PLC_CONFIG0[7:6]<br>= 01                     |      | 102                |                                | mA    |

|                                        |                              |                         | PLC_CONFIG0[7:6]<br>= 10<br>PLC_CONFIG0[7:6] |      | 119.4              |                                |       |

|                                        |                              |                         | = 11                                         |      | 136                |                                |       |

| UART SWITCH                            | T                            | T                       |                                              |      |                    |                                |       |

| Analog Signal Range                    | V <sub>UART_RNG</sub>        |                         |                                              | 0    |                    | MIN(3.3,<br>V <sub>SYS</sub> ) | V     |

| On-Resistance                          | R <sub>ONUART</sub>          |                         |                                              |      | 12                 | 24                             | Ω     |

| On-Resistance Flatness                 | R <sub>FLATUART</sub>        |                         |                                              |      | 0.1                | 0.3                            | Ω     |

| Off-Leakage Current                    | I <sub>LUART</sub> (OFF)     |                         |                                              |      |                    | 1                              | μΑ    |

$(T_A = -40$ °C to +85°C, FGBAT = +2.7V to +4.9V, SYS = +2.8V to 5.5V,  $C_{SYS} = 10\mu F$ ,  $C_{DIG} = 1\mu F$ ,  $L_{VLX} = 2.2\mu H$  (ESR < 200mΩ),  $C_{ASYS} = 0.1\mu F$ ,  $C_{VPLC} = 8\mu F$ ,  $C_{FGBAT} = 10\mu F$ , dual-slave configuration if not otherwise specified)

|                                                     |                       | 0μF, dual-slave configuration if not otherwise                                   |           |         |      | T               |

|-----------------------------------------------------|-----------------------|----------------------------------------------------------------------------------|-----------|---------|------|-----------------|

| PARAMETER                                           | SYMBOL                | CONDITIONS                                                                       | MIN       | TYP     | MAX  | UNITS           |

| FUEL GAUGE POWER S                                  | SUPPLY (FGBAT         | ·)                                                                               |           |         |      | T               |

| Shutdown Supply<br>Current                          | I <sub>DD0</sub>      |                                                                                  |           | 0.5     |      | μA              |

| Hibernate Supply<br>Current                         | I <sub>DD1</sub>      | Average current                                                                  |           | 5.1     |      | μA              |

| Active Supply Current                               | I <sub>DD2</sub>      | Average current not including thermistor measurement current                     |           | 15      |      | μΑ              |

| FUEL GAUGE ANALOG                                   | -TO-DIGITAL CO        | ONVERSION                                                                        |           |         |      |                 |

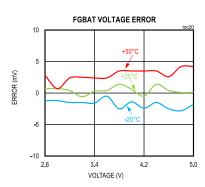

| FGBAT Measurement                                   | V                     | T <sub>A</sub> = +25°C                                                           | -7.5 +7.5 |         | .,   |                 |

| Error                                               | V <sub>GERR</sub>     | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                   | -20       |         | +20  | mV              |

| FGBAT Measurement Resolution                        | V <sub>LSB</sub>      |                                                                                  |           | 78.125  |      | μV              |

| FGBAT Measurement<br>Range                          | V <sub>FS</sub>       |                                                                                  | 2.7       |         | 4.9  | V               |

| Sense Resistance                                    | R <sub>SNS</sub>      | T <sub>A</sub> = +25°C                                                           |           | 15      |      | mΩ              |

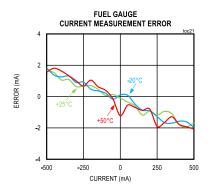

| Current Measurement<br>Offset Error                 | I <sub>OERR</sub>     | Long term average without load current                                           |           | ±1      |      | mA              |

| Current Measurement Resolution                      | I <sub>LSB</sub>      |                                                                                  |           | 104.167 |      | μΑ              |

| Current Measurement Gain Error                      | I <sub>GERR</sub>     | (Note 1)                                                                         |           | ±2.5    |      | % of<br>Reading |

| Current Measurement<br>Error                        | I <sub>ERR</sub>      | 0.25A and 0.5A (Note 1)                                                          | -3        |         | +3   | % of<br>Reading |

| Internal Temperature<br>Measurement Error           | TI <sub>GERR</sub>    | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                   |           | ±1      |      | °C              |

| Internal Temperature<br>Measurement<br>Resolution   | TI <sub>LSB</sub>     |                                                                                  |           | 0.00391 |      | °C              |

| FUEL GAUGE INPUT/OU                                 | JTPUT                 |                                                                                  |           |         |      |                 |

| External Thermistance                               | R <sub>EXT10</sub>    | Config.R100 = 0                                                                  |           | 10      |      | 1.0             |

| Resistance                                          | R <sub>EXT100</sub>   | Config.R100 = 1                                                                  |           | 100     |      | kΩ              |

| Input Logic High, ALRT                              | V <sub>IH</sub>       |                                                                                  | 1.5       |         |      | V               |

| Input Logic Low, ALRT                               | V <sub>IL</sub>       |                                                                                  |           |         | 0.5  | V               |

| Battery-Detach Detection Threshold                  | V <sub>DET</sub>      | Measured as a fraction of V <sub>FGBAT</sub> on TH rising                        | 91        | 96.2    | 99   | %               |

| Battery-Detach<br>Detection Threshold<br>Hysteresis | V <sub>DET-HYS</sub>  | Measured as a fraction of V <sub>FGBAT</sub> on TH falling                       |           | 1       |      | %               |

| Battery-Detach<br>Comparator Delay                  | t <sub>TOFF</sub>     | TH step from 70% to 100% of V <sub>FGBAT</sub> (Alrtp = 0, EnAIN = 1, FTHRM = 1) |           |         | 100  | μs              |

| FUEL GAUGE LEAKAGE                                  | E                     |                                                                                  |           |         |      |                 |

| Leakage Current, THM                                | I <sub>LEAK_THM</sub> |                                                                                  | -500      |         | +500 | nA              |

| FUEL GAUGE TIMING                                   |                       |                                                                                  |           |         |      | 1               |

|                                                     | ,                     | T <sub>A</sub> = +25°C                                                           | -1        |         | +1   |                 |

| Time-Base Accuracy                                  | t <sub>ERR</sub>      | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                   | -5        |         | +5   | %               |

| TH Pre-charge Time                                  | t <sub>PRE</sub>      |                                                                                  | 8.48      |         | -    | ms              |

| DIGITAL SIGNALS (SDA                                | , SCL, nINT, EN       | , GPIO1, GPIO2, GPIO3, GPIO4, UART_T, L                                          | JART_R, A | ALRT)   |      |                 |

$(T_A = -40$ °C to +85°C, FGBAT = +2.7V to +4.9V, SYS = +2.8V to 5.5V,  $C_{SYS} = 10\mu F$ ,  $C_{DIG} = 1\mu F$ ,  $L_{VLX} = 2.2\mu H$  (ESR < 200mΩ),  $C_{ASYS} = 0.1\mu F$ ,  $C_{VPLC} = 8\mu F$ ,  $C_{FGBAT} = 10\mu F$ , dual-slave configuration if not otherwise specified)

| $C_{ASYS} = 0.1 \mu F, C_{VPLC} = 8$                                                  |                      |                            |                                     |     |              |     | T     |

|---------------------------------------------------------------------------------------|----------------------|----------------------------|-------------------------------------|-----|--------------|-----|-------|

| PARAMETER                                                                             | SYMBOL               | COI                        | NDITIONS                            | MIN | TYP          | MAX | UNITS |

| SDA, SCL, nINT, EN,<br>GPIO1, GPIO2, GPIO3,<br>GPIO4, UART_T,<br>UART_R Input leakage | I <sub>LK_IO</sub>   | Input pullup/down          | Input pullup/down resistor disabled |     |              | +1  | μΑ    |

| ALRT Input Leakage                                                                    | I <sub>LK_ALRT</sub> | V <sub>ALRT &lt; 15V</sub> |                                     | -1  |              | +1  | μA    |

| SDA, SCL, EN Input<br>Logic low                                                       | V <sub>IL_IO</sub>   |                            |                                     |     |              | 0.4 | V     |

| SDA, SCL, EN Input<br>Logic high                                                      | V <sub>IL_IH</sub>   |                            |                                     |     |              |     | V     |

| GPIO1, GPIO2, GPIO3,<br>GPIO4 Input CMOS<br>Logic low                                 | V <sub>IL_IO_C</sub> | GPIOCmosEn = 1             | GPIOCmosEn = 1                      |     | 0.3 x<br>SYS |     | V     |

| GPIO1, GPIO2, GPIO3,<br>GPIO4 Input CMOS<br>Logic high                                | V <sub>IL_IH_C</sub> | GPIOCmosEn = 1             |                                     |     | 0.7 x<br>SYS |     | V     |

| GPIO1,GPIO2,<br>GPIO3,GPIO4 Input<br>TTL Logic low                                    | V <sub>IL_IO_T</sub> | GPIOCmosEn = 0             |                                     |     |              | 0.4 | V     |

| GPIO1, GPIO2, GPIO3,<br>GPIO4 Input TTL Logic<br>high                                 | V <sub>IL_IH_T</sub> | GPIOCmosEn = 0             |                                     | 1.4 |              |     | V     |

| SDA, nINT, ALRT<br>GPIO1, GPIO2, GPIO3,<br>GPIO4 Output Logic<br>Low                  | V <sub>OL</sub>      | I = 4mA                    |                                     |     |              | 0.4 | V     |

| I <sup>2</sup> C TIMING (SDA, SCL)                                                    |                      |                            |                                     |     |              |     |       |

| SCL Clock Frequency                                                                   | f <sub>SCL</sub>     | (Note 2)                   |                                     | 0   |              | 400 | kHz   |

| Bus Free Time Between<br>a STOP and START<br>Condition                                | <sup>t</sup> BUF     |                            |                                     | 1.3 |              |     | μs    |

| Hold Time (Repeated)<br>START Condition                                               | thd:STA              | (Note 3)                   |                                     | 0.6 |              |     | μs    |

| Low Period of SCL<br>Clock                                                            | t <sub>LOW</sub>     |                            |                                     | 1.3 |              |     | μs    |

| High Period of SCL<br>Clock                                                           | <sup>t</sup> HIGH    |                            |                                     | 0.6 |              |     | μs    |

| Setup Time for a<br>Repeated START<br>Condition                                       | t <sub>SU:STA</sub>  |                            |                                     | 0.6 |              |     | μs    |

| Data Hold Time                                                                        | t <sub>HD:DAT</sub>  | (Note 4, Note 5)           |                                     | 0   |              | 0.9 | μs    |

| Data Setup Time                                                                       | t <sub>SU:DAT</sub>  | (Note 4)                   |                                     | 100 |              |     | ns    |

| Setup Time for STOP<br>Condition                                                      | t <sub>SU:STO</sub>  |                            |                                     | 0.6 |              |     | μs    |

| Spike Pulse Width<br>Suppressed by Input<br>Filter                                    | t <sub>SP</sub>      | (Note 6)                   |                                     |     |              | 50  | ns    |

| ESD PROTECTION                                                                        |                      |                            |                                     |     |              |     |       |

| ESD Protection Rating                                                                 |                      | PLC1, PLC2                 | Contact discharge                   | 8   |              |     | kV    |

|                                                                                       | _                    | All other pins             | All other pins HBM 2                |     | 2            |     |       |

| THERMAL PROTECTION                                                                    | l .                  |                            |                                     |     |              |     |       |

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ FGBAT} = +2.7 \text{V to } +4.9 \text{V}, \text{ SYS} = +2.8 \text{V to } 5.5 \text{V}, C_{SYS} = 10 \mu\text{F}, C_{DIG} = 1 \mu\text{F}, L_{VLX} = 2.2 \mu\text{H} \text{ (ESR < } 200 \text{m}\Omega), C_{ASYS} = 0.1 \mu\text{F}, C_{VPLC} = 8 \mu\text{F}, C_{FGBAT} = 10 \mu\text{F}, dual-slave configuration if not otherwise specified)}$

| PARAMETER                    | SYMBOL             | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------|--------------------|------------|-----|-----|-----|-------|

| Overtemperature<br>Threshold | TH <sub>OVER</sub> |            |     | 150 |     | °C    |

- Note 1: GBD and not production tested.

- **Note 2:** Timing must be fast enough to prevent the IC from entering shutdown mode due to bus low for a period greater than the shutdown timer setting.

- Note 3: f<sub>SCI</sub> must meet the minimum clock low time plus the rise/fall times.

- Note 4: The maximum  $t_{HD\ DAT}$  has only to be met if the device does not stretch the low period  $(t_{LOW})$  of the SCL signal.

- **Note 5:** This device internally provides a hold time of at least 100ns for the SDA signal (see the minimum V<sub>IH</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 6: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

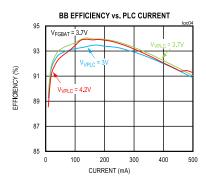

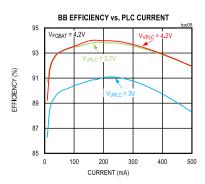

### **Typical Operating Characteristics**

(T<sub>A</sub> = +25°C, unless otherwise noted.)

(T<sub>A</sub> = +25°C, unless otherwise noted.)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

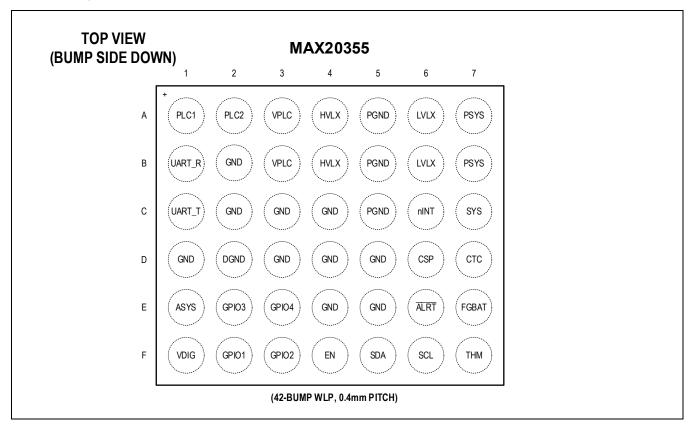

### **Pin Configuration**

### **Pin Descriptions**

| PIN        | NAME   | FUNCTION                                                                                                                   |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| A1         | PLC1   | PLC1 Power Output. Connect to PLC pin on MAX20357.                                                                         |

| A2         | PLC2   | PLC2 Power Output. Connect to PLC pin on MAX20357.                                                                         |

| A3, B3     | VPLC   | PLC Voltage Supply. Bypass with 2 x 22μF capacitor to GND.                                                                 |

| A4, B4     | HVLX   | Buck-Boost High Voltage Switching Node. Connect to inductor.                                                               |

| A5, B5, C5 | PGND   | Power GND                                                                                                                  |

| A6, B6     | LVLX   | Buck-Boost Low Voltage Switching Node. Connect to inductor.                                                                |

| A7, B7     | PSYS   | Power SYS. Buck-Boost input. Connect 10µF to GND.                                                                          |

| B1         | UART_R | UART RX Node. Connect to system processor UART RX.                                                                         |

| C1         | UART_T | UART_TX Node. Connect to system processor UART TX.                                                                         |

| C6         | nINT   | Open Drain Interrupt. Active low.                                                                                          |

| C7         | SYS    | SYS. Connect to PSYS.                                                                                                      |

| D2         | DGND   | Digital Ground                                                                                                             |

| D6         | CSP    | Sense Resistor Input Pin                                                                                                   |

| D7         | СТС    | Short to CSP                                                                                                               |

| E1         | ASYS   | Analog Sensitive Circuit Supply. Internally connected to SYS by means of a $100\Omega$ resistor. Connect 0.1µF cap to GND. |

| E2         | GPIO3  | Programmable GPIO3. May be configured as a digital input or open drain output.                                             |

MAX20355

# Power Line Communication with ModelGauge Fuel Gauge and Buck-Boost Converter

| E3                                                 | GPIO4 | Programmable GPIO4. May be configured as a digital input or open drain output.                                       |

|----------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------|

| E6                                                 | ALRT  | Alert Output. The ALRT pin is open-drain active-low output which indicates FG alerts. Connect it to GND if not used. |

| E7                                                 | FGBAT | Power Supply and Battery Sense Input. Connect it to positive terminal of a battery cell. Bypass it with 10µF cap.    |

| F1                                                 | VDIG  | Internal 1.8V Supply. Bypass it with 1µF cap to GND.                                                                 |

| F2                                                 | GPIO1 | Programmable GPIO1. May be configured as a digital input or open drain output.                                       |

| F3                                                 | GPIO2 | Programmable GPIO2. May be configured as a digital input or open drain output.                                       |

| F4                                                 | EN    | Chip Enable                                                                                                          |

| F5                                                 | SDA   | I <sup>2</sup> C SDA                                                                                                 |

| F6                                                 | SCL   | I <sup>2</sup> C SCL                                                                                                 |

| F7                                                 | THM   | Battery temperature thermistor measurement input.                                                                    |

| C3, C4,<br>D1, D3,<br>D4, D5,<br>E4, E5,<br>C2, B2 | GND   | Ground                                                                                                               |

### **Functional Diagram**

### **Detailed Description**

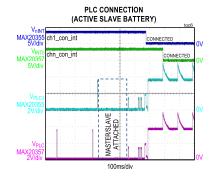

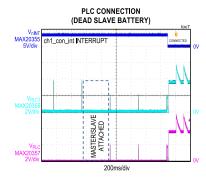

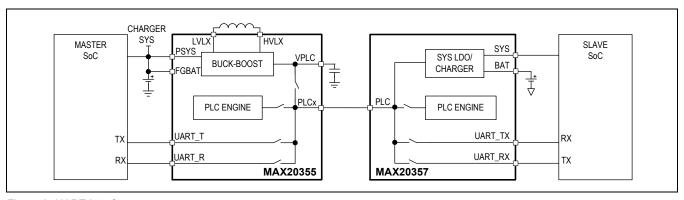

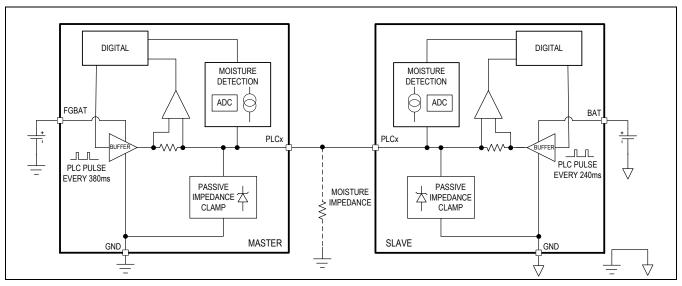

The MAX20355, together with the MAX20357, form an integrated Power Line Communication (PLC) and automated charging system. These devices provide a complete system solution for efficient charging and data transfer between a charging case and wireless earbuds over a single contact.

The MAX20355 and MAX20357 feature data transfers while simultaneously delivering 200mA of charge/system current per output. Both devices support a 166.7kbps bit rate while charging. With a 166.7kbps bit rate, the PLC protocol can achieve up to 130kpbs of throughput using the bulk data transfer feature. Additionally, a 4Mbaud half-duplex data-only UART mode provides an easy and fast method for firmware updates, debug interface, and factory modes. Finally, dedicated hardware PLC commands allow both devices to control GPIOs and enter various power modes, such as ultra-low current ship mode, through the PLC link.

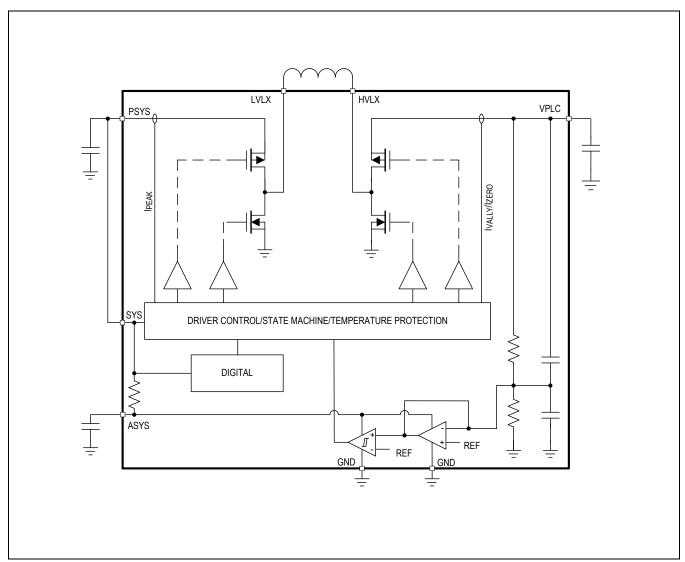

The MAX20355 integrates a completely autonomous charging system that utilizes a 3.3W buck-boost with dynamic voltage scaling (DVS) to provide an optimized charge voltage to the earbuds. An integrated digital state machine automatically manages the dynamic voltage adjustment based on the earbud battery voltage to minimize earbud power dissipation and maximize charging efficiency.

Additional features include comprehensive earbud insertion and removal notifications, even in dead case or bud battery scenarios, and moisture detection on the PLC outputs to prevent contact corrosion. The PLC pins are protected from overcurrent events by an integrated current limiting circuit and ESD events by integrated 8kV contact-rated ESD protection structures.

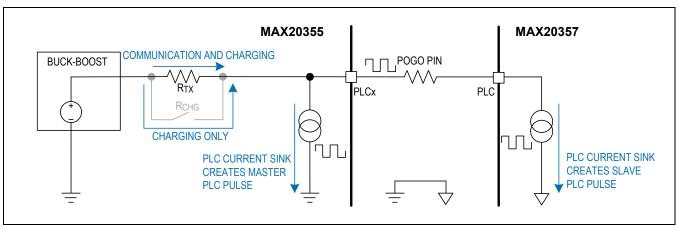

#### **Power Line Communication (PLC)**

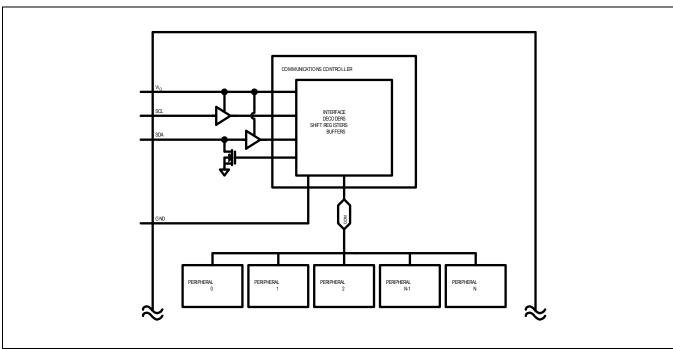

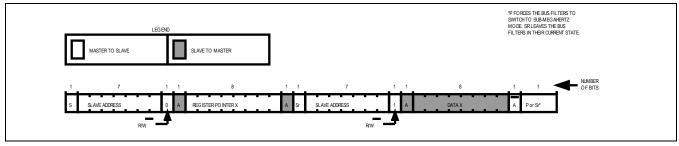

The MAX20355/MAX20357 PLC interface offers a means by which charging and exchange of data can occur simultaneously on a single wire connection. The interface can accommodate 100kbps of throughput and can do so while delivering up to 200mA of current per channel in dual slave mode and up to 400mA in mono slave mode. The MAX20355 has an integrated current sink and resistor  $R_{TX}$  as shown in <u>Figure 1</u>. During communication, the MAX20355 utilizes the pulses generated by the PLC current sink over resistor  $R_{TX}$  to create PLC pulses on the PLC line. The MAX20355 uses PLC pulses to transfer information to the MAX20357. At the same time, the charging function is not affected. The MAX20357 uses a similar approach to create PLC pulses and transfer information over the PLC line. When there is no ongoing PLC communication,  $R_{TX}$  is shorted by a bypass switch to achieve higher overall power transfer efficiency.

Figure 1. Simplified Scheme of Power Line Communication (PLC)

The PLC interface balances between robustness and throughput. Synchronization mechanisms and checksums offer robust data transfer, but this is also balanced against protocol overhead. With a 166.67kbps bit rate, this careful balance allows a low error rate while achieving throughput up to 130kbps in bulk data transfer mode. To overcome limitations on throughput due to the I<sup>2</sup>C interface, the MAX20355/MAX20357 integrates two 128-byte FIFOs. This allows the system to keep I<sup>2</sup>C overhead low utilizing bulk writes. The MAX20355 also features a 4Mbaud, data-only, half-duplex UART passthrough mode. This mode uses a simple switch that connects UART ports from master to slave for firmware updates, factory mode, and debug mode over a single PLC line.

The following sections describe the PLC PING (PLC command/mailbox data transfer), FIFO (bulk data transfer), and UART interface in detail.

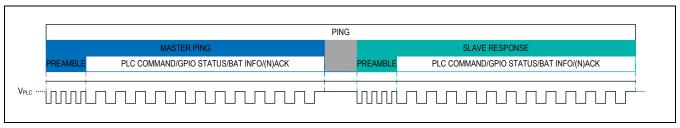

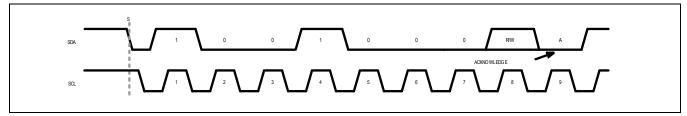

#### **PLC PING**

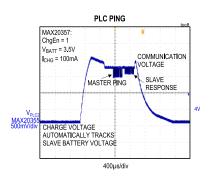

The PLC interface between master and slave follows a master-initiated scheme. There are two data transfer types—PING and bulk data transfer. PINGs begin with a transfer from master to slave to send data across the interface, request data from the slave, offer the slave a chance to make requests, and sometimes issue commands to the slave. <u>Figure 2</u> shows the basic structure of the master to slave PING packet. Master initiates the transmission with a preamble which synchronizes the link and then transmits data. The slave responds in the same manner within a response timeout period. PLC PINGs are automatically generated and transmitted through the PLC line every telemetry period.

Figure 2. Periodic PING

### **LISTEN Command and Continuously Updated Information**

Each PLC PING contains one PLC command. Most PLC commands are initiated by an I<sup>2</sup>C write from the system. However, the MAX20355 features automatic LISTEN command, which is sent periodically independent of input from the I<sup>2</sup>C interface. When there is no customer PLC command issued through I<sup>2</sup>C, LISTEN command is automatically sent through the PING, the slave has the option to send its command back to the master using its command field. In response to the master's PING, the slave sends the appropriate data based on the contents of the master PING. The contents of the command and data fields are filled according to the requirements of the command sent from the master. The periodic PING offers the following features:

- 1. Send master PLC command from master to slave (Table 1).

- 2. Give slave an opportunity to send slave PLC commands to master (Table 2).

- 3. Transmit GPIO status between master and slave.

- 4. Exchange master/slave battery information: master battery voltage, slave battery voltage, slave SoC, and slave charging status.

- 5. Automatic PLC voltage adjustment to track slave battery voltage and minimize power consumption. Details are described in the <a href="https://documents.org/learning-loop">Charger Battery Voltage Tracking Loop</a> section.

- Automatic disconnection detection. Master detects slave is disconnected if there is no proper slave response for master PING.

The exchanged GPIO status and battery information between master and slave are ready to read from the master and slave local registers.

#### **Master Commands**

In addition to the LISTEN command, which is handled automatically, the master can execute other commands manually as well. Master's command field determines what type of transaction occurs on the PLC interface. Commands over the PLC interface are requested by I<sup>2</sup>C. <u>Table 1</u> describes the various commands master can send and what data and statuses are exchanged. Note that many commands can be sent from master to slave or from slave to master. However, it is only in response to a LISTEN command where the slave may send its commands. Master commands are initiated by writing to the plc\_command1/2 and triggered by plc\_run\_trg1/2 through master I<sup>2</sup>C. In the command argument register plc cmd arg1/2, details on how the command is processed are available for the user to specify.

#### Table 1. MAX20355 Commands

| MASTER<br>COMMANDS | plc_command1/2 | plc_cmd_arg1/2                       |                                                                                 |  |

|--------------------|----------------|--------------------------------------|---------------------------------------------------------------------------------|--|

| LISTEN             | N/A            | N/A                                  |                                                                                 |  |

| SET_GPIO           | 0x3            | New slave GPIO setting               | g                                                                               |  |

| DOUT_REQ           | 0x5            | Number of bytes (up to               | 128 bytes)                                                                      |  |

| UART_REQ           | 0x6            | slave uart sw[1:0]                   |                                                                                 |  |

|                    |                | 0x00                                 | SEAL request. Puts slave in SEAL mode.                                          |  |

|                    |                | 0x01                                 | Soft reset request. Resets slave's registers.                                   |  |

|                    |                | 0x02                                 | Hard reset request. Cycle the power on the slave's SYS node.                    |  |

|                    |                | 0x03                                 | Fuel gauge reset request. Resets fuel gauge block.                              |  |

|                    |                | 0x04                                 | FIFO request. Puts system into bulk data transfer mode.                         |  |

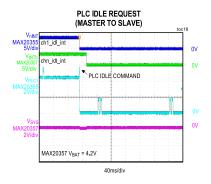

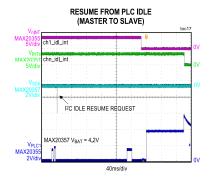

| SYST_REQ           | REQ 0x0        | 0x05                                 | Free request. Stop bulk data transfer and free the data line.                   |  |

|                    |                | 0x06                                 | IDLE mode request. Sends system into PLC IDLE mode.                             |  |

|                    |                | 0x07                                 | Hard + Soft reset request. Reset all registers, FSM and cycle the power at SYS. |  |

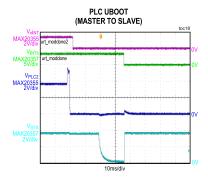

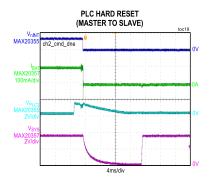

|                    |                | {0x3F, slave_uart_tx, slave_uart_rx} | UBOOT request. Hard resets slave and puts slave in UART mode.                   |  |

#### **Slave Commands**

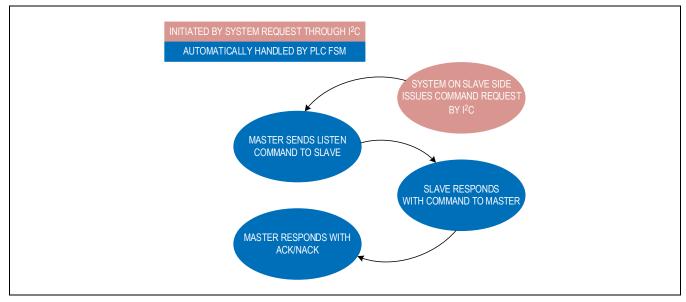

The slave can also issue commands to the master. The slave similarly issues the commands based on I<sup>2</sup>C input, but it must wait for a master LISTEN command before the command can be sent back to the master. Once the LISTEN command is received, the slave then sends its command using the COMMAND field. *Figure 3* shows the method by which the slave can send a command. Slave commands are initiated with a write to plc\_command and triggered by plc\_run\_trg through master I<sup>2</sup>C. In the command argument register plc\_cmd\_arg, details on how to process the PLC commands are available for the user to specify.

Figure 3. Sending Commands from the Slave

#### **Table 2. Slave Commands**

| SLAVE COMMAND* | plc_command | plc_cmd_arg (DATA)                                                     |  |  |

|----------------|-------------|------------------------------------------------------------------------|--|--|

| SET_GPIO       | 0x3         | New master GPIO setting                                                |  |  |

| DOUT_REQ       | 0x5         | Number of bytes (up to 128 bytes)                                      |  |  |

| UART_REQ       | 0x6         | master_uart_sw[3:0]                                                    |  |  |

|                |             | 0x01 Soft reset request. Resets master's registers.                    |  |  |

|                |             | 0x03 Fuel gauge reset request. Resets master's fuel gauge block.       |  |  |

| SYST_REQ       | Qx0         | 0x04 FIFO request. Puts master and slave into bulk data transfer mode. |  |  |

|                |             | 0x05 Free request. Stop bulk data transfer and free the data line.     |  |  |

|                |             | 0x06 Idle mode request. Sends master into idle mode.                   |  |  |

<sup>\*</sup>Always sent in response to the "LISTEN" command from the master shown in Table 1.

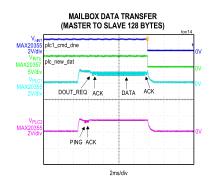

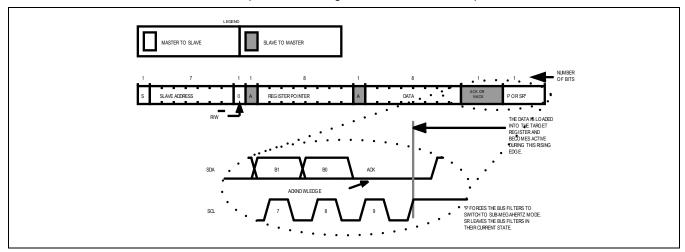

#### Mailbox Data Transfer (DOUT\_REQ)

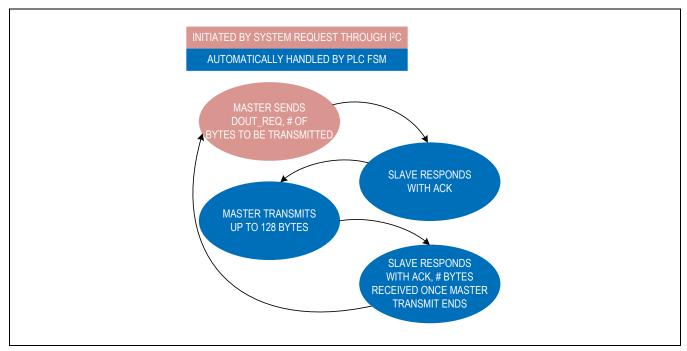

#### From Master to Slave

Mailbox data transfers are used to exchange one data packet, up to 128 bytes, from master to slave. A mailbox data transfer begins with a data out request (DOUT\_REQ) master command. Fill the data packet into the master RAM, write the number of bytes to be transferred in the command argument field plc\_cmd\_arg1/2, then trigger the DOUT\_REQ command. If slave responds ACK to DOUT\_REQ command, data in RAM is transferred to slave automatically. After slave successfully receives data, plc\_new\_dat interrupt is asserted and RAM\_is\_full is set to 1. Once RAM\_is\_full is set to 1, slave RAM is protected from PLC and it sends NACK to master's DOUT\_REQ command until RAM\_is\_full is write cleared. Make sure to read data in RAM before clearing RAM\_is\_full to avoid data loss. Note that although both PLC devices have two integrated 128-byte RAMs, only one RAM is used in mailbox data transfer. Figure 4 shows the flow of data during a master to slave write.

Figure 4. Master to Slave Mailbox Data Transfer

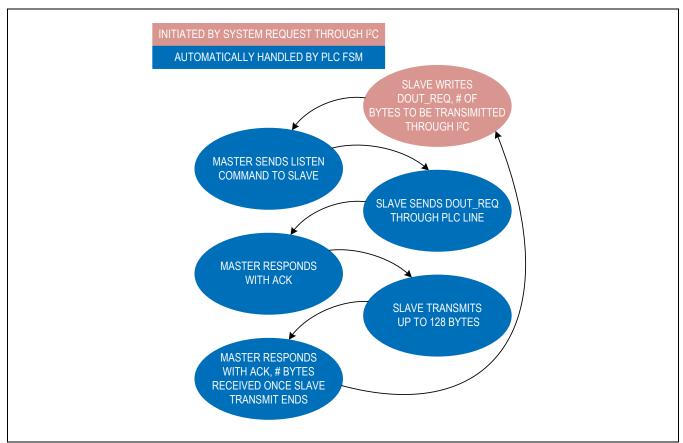

#### From Slave to Master

A similar scheme is used to send a packet of data, up to 128 bytes, from slave to master. A mailbox data transfer begins with a data out request (DOUT\_REQ) slave command. Write the number of bytes to be transferred in the command argument field plc\_cmd\_arg. Fill the data packet into the slave RAM, write the number of bytes to be transferred in the command argument field plc\_cmd\_arg, then trigger the DOUT\_REQ command. Since the system follows master initiated scheme, the slave triggers the DOUT\_REQ command when it receives the master Listen command. After the master receives DOUT\_REQ and responds to ACK, data in RAM is transferred to the slave automatically. After master successfully receives data, plc\_new\_dat interrupt is asserted and RAM\_is\_full is set to 1. Once RAM\_is\_full is set to 1, master RAM is protected from PLC and it sends NACK to slave's DOUT\_REQ command until RAM\_is\_full is write cleared. Make sure to read data in RAM before clearing RAM\_is\_full to avoid data loss. Note that although both PLC devices have two integrated 128-byte RAMs, only one RAM is used in mailbox data transfer. Figure 5 shows the flow of data during a slave to master write.

Figure 5. Slave to Master Mailbox Data Transfer

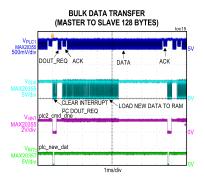

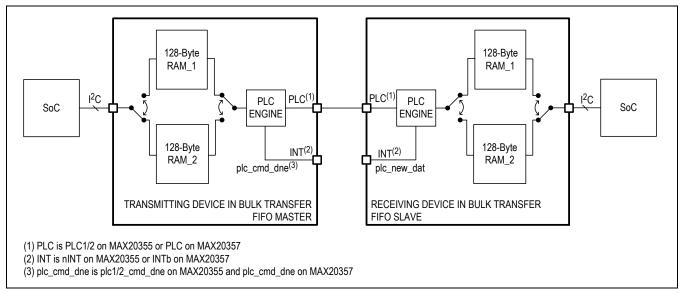

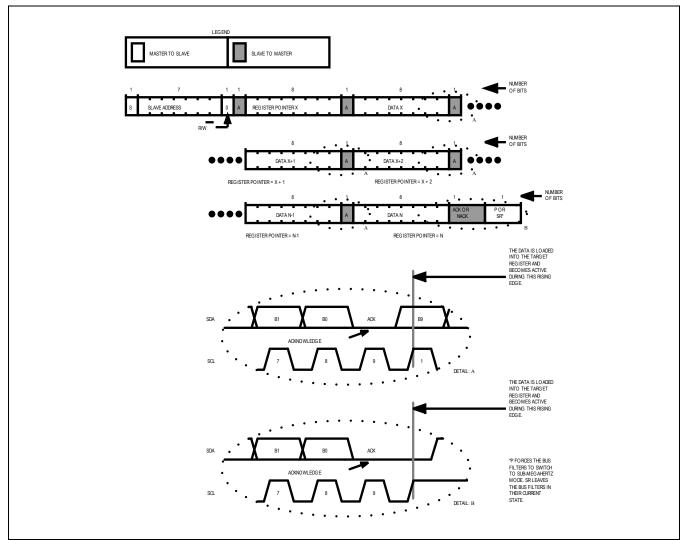

### **Bulk Data Transfer (FIFO)**

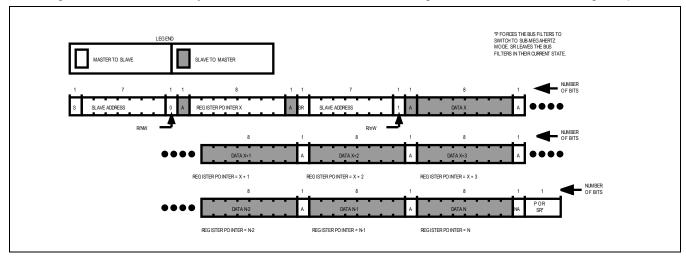

To minimize the impact of I<sup>2</sup>C protocol overhead on the achievable throughput, MAX20355 and MAX20357 integrate two 128-byte RAMs for bulk data transfer. The bulk data transfer scheme is shown in *Figure 6*. The I<sup>2</sup>C bus connects first to the RAM\_1 to load data with I<sup>2</sup>C bulk writes at data rates up to 400kbps. Once the DOUT\_REQ command is triggered, the I<sup>2</sup>C bus and PLC line are swapped, I<sup>2</sup>C bus from RAM\_1 to RAM\_2 and PLC from RAM\_2 to RAM\_1. While RAM\_1 is being emptied by the PLC engine, the next set of data can be loaded by I<sup>2</sup>C bulk write again into the RAM\_2. An interrupt is sent to the system after RAM\_1 is completely emptied. Repeat the same process to swap the I<sup>2</sup>C bus and PLC back and forth to load and transmit data simultaneously. Similar implementation on receiving side swaps I<sup>2</sup>C bus and PLC back and forth to receive and read data to receiver's microcontroller. Dual-RAM architecture reduces I<sup>2</sup>C protocol overhead and enhances achievable throughput. Packets of any size up to 128 bytes can be sent by this method.

Figure 6. Bulk Data Transfer Implementation

#### From Master to Slave

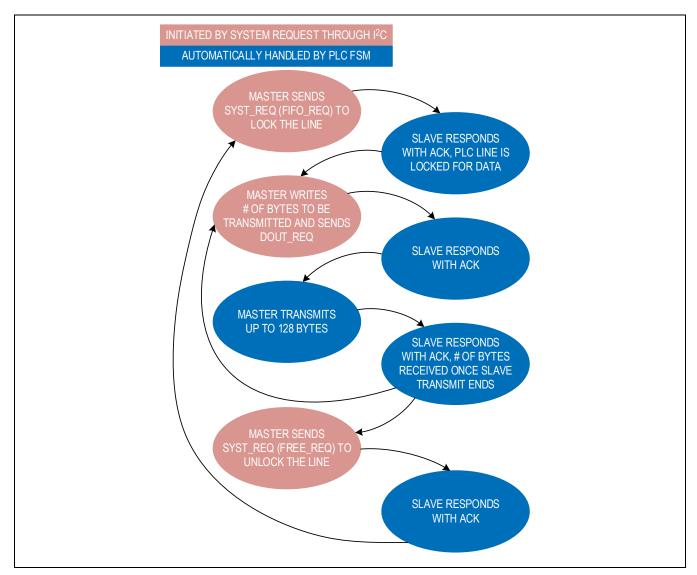

Bulk data transfers from master to slave begin with a system request (SYST\_REQ) master command. In the command argument of SYST\_REQ, the master needs to send a FIFO request. Once receiving an ACK from the slave, PLC voltage is pulled up to communication voltage and the PLC line is locked for bulk data transfer. Before triggering the data transfer, the data packet needs to be filled into the master RAM through I<sup>2</sup>C. Similar to mailbox data transfer, write the number of bytes to be transferred to plc\_cmd\_trg1/2, then trigger the DOUT\_REQ command and wait for plc1/2\_cmd\_dne interrupt. Repeat DOUT\_REQ and wait for plc1/2\_cmd\_dne to interrupt multiple times as needed. After all data packets are transferred, issue a FREE request from the master side to unlock the line and return to normal PLC mode. Note that master bulk data transfer is designed to transfer data only from master to slave. Figure 7 shows the flow of data during a master to slave write.

Figure 7. Master to Slave Bulk Data Transfer

#### From Slave to Master

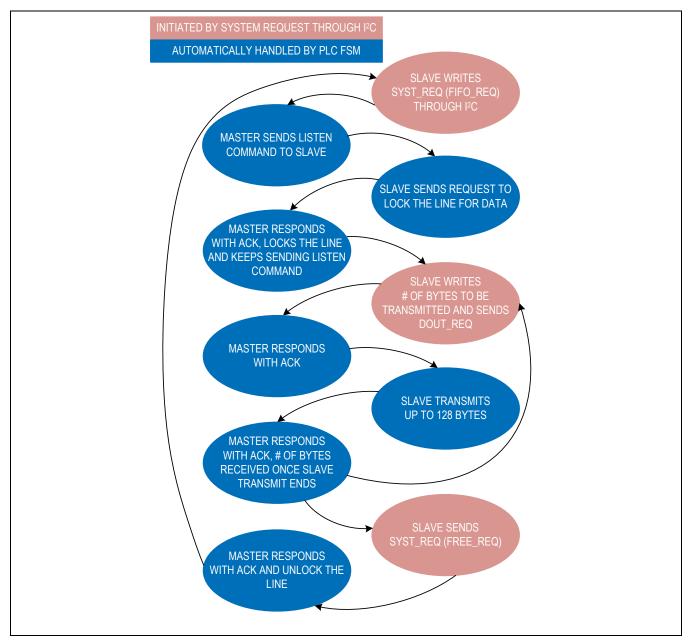

Bulk data transfers from slave to master begin with a system request (SYST\_REQ) slave command. In the command argument of SYST\_REQ, the slave needs to write a FIFO request. The slave waits until the master's LISTEN command to send out a FIFO request through the PLC line. Once receiving an ACK from the master, the master locks the PLC line and enters bulk data transfer mode. Before triggering the data transfer, the data packet needs to be filled into the slave RAM. Similar to mailbox data transfer, write the number of bytes to be transferred to plc\_cmd\_arg, then trigger the DOUT\_REQ command and wait for plc\_cmd\_dne interrupt. Repeat DOUT\_REQ and wait for plc\_cmd\_dne to interrupt multiple times as needed. After all data packets are transferred, issue a FREE request from the slave side to unlock the line and return to normal PLC mode. Note that slave bulk data transfer is designed to transfer data only from slave to master. Figure 8 shows the flow of data during a slave to master write.

Figure 8. Slave to Master Bulk Data Transfer

#### Half-Duplex UART Passthrough Interface

The MAX20355 and MAX20357 feature a 4Mbaud, data-only, half-duplex UART passthrough mode. This mode is a simple switch that connects either the TX or RX for firmware updates, factory mode, and debug mode over the single PLC line. A UART command can be sent through the PLC interface to send either device into UART mode in a particular configuration. Internal switches allow the user to separate UART TX and UART RX. The configuration can be seen in *Figure 9*. The user can use the I<sup>2</sup>C command to switch roles from TX to RX or vice versa on master and slave. The slave provides one additional feature to detect incoming data automatically through its UART\_RX pin. In this mode, once the slave enters UART mode, it closes its UART\_TX switch by default. Once it detects a rising/falling edge on its UART\_RX pin from the slave microcontroller, it toggles the switch from UART\_TX to UART\_RX automatically. After the data transfer is completed in receiving direction, switch toggles back from UART\_RX to UART\_TX automatically after a programmable blanking time. This feature allows the user to send and receive data through UART when the slave I<sup>2</sup>C is not available.

Figure 9. UART Interface

#### From Master to Slave

The master can put the slave into UART mode by using the UART\_REQ master command. The direction of UART communication is set in the command argument. Corresponding master and slave switches are closed once the UART command is successfully triggered. The switch settings are shown in <u>Table 3</u>. If the user wants to control UART switches manually in UART mode, all the master/slave UART switch settings can be changed through I<sup>2</sup>C.

Table 3. UART Switch Settings in Master PLC Command Argument

| slave_uart_sw[1:0] | MASTER UART_T | MASTER UART_R | SLAVE UART_TX | SLAVE UART_RX |

|--------------------|---------------|---------------|---------------|---------------|

| 0b00               | ×             | ×             | ×             | ×             |

| 0b01               | ×             | $\sqrt{}$     | ×             | $\sqrt{}$     |

| 0b10               | V             | ×             | √             | ×             |

| 0b11               | V             | √             | √             | √             |

<sup>&</sup>quot;\" represents the switch is ON and "x" represents the switch is OFF

#### From Slave to Master

The slave can put the master into UART mode by using the UART\_REQ slave command. Corresponding master switches are closed once the UART command is successfully triggered. The switch settings are shown in <u>Table 4</u>. No slave switch is closed after UART\_REQ. The slave UART\_TX and UART\_RX switches need to be closed through the slave I<sup>2</sup>C write. If the user wants to control UART switches manually in UART mode, all the master/slave UART switch settings can be changed through the master/slave I<sup>2</sup>C.

Table 4. UART Switch Settings in Slave PLC Command Argument

| master_uart_sw[3:0] | MASTER PLC2<br>UART_T | MASTER PLC2<br>UART_R | MASTER PLC1<br>UART_T | MASTER PLC1<br>UART_R |

|---------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 0b0000              | ×                     | ×                     | ×                     | ×                     |

| 0b0001              | ×                     | ×                     | ×                     | $\sqrt{}$             |

| 0b0010              | ×                     | ×                     | V                     | ×                     |

| 0b0011              | ×                     | ×                     | V                     | $\sqrt{}$             |

| 0b0100              | ×                     | $\sqrt{}$             | ×                     | ×                     |

| 0b1000              | $\sqrt{}$             | ×                     | ×                     | ×                     |

| 0b1100              | V                     | V                     | ×                     | ×                     |

<sup>&</sup>quot;√" represents the switch is ON and "x" represents the switch is OFF

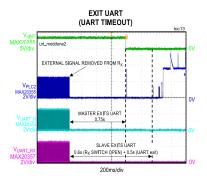

#### **Exit UART Mode**

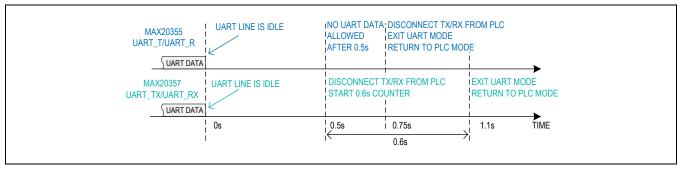

There are two ways to quit UART mode: 1. Master/slave can quit UART mode by disabling UART mode and disconnecting the UART switch through the master/slave I<sup>2</sup>C; 2. Use master and slave UART timeout counter and wait for UART timeout interrupt. Enable timeout counter through tmo\_tmr\_ena1/2 on master and tmo\_tmr\_ena on slave before entering UART mode. Once the TX/RX line is idle for 0.5s, the slave turns off its UART switch, disconnect UART\_TX or UART\_RX from the PLC line and start a counter to count for 0.6s. After a 0.6s delay, the slave exits UART mode, connects the PLC line to the PLC engine, and returns to the PLC detection mode. Meanwhile, once the line is idle for 0.75s, the master turns off its UART switch, disconnects UART\_T or UART\_R from the PLC line, connects to the PLC engine, and returns to the

PLC detection mode. Note that once the slave disconnects its UART switch at time point 0.5s, it enters an automatic UART exit process and this process is irreversible. It is not allowed to send data from master through UART after time point 0.5s. If data resumes from the master between time point 0.5s and 0.75s, the master UART timeout counter is cleared, and it holds the master in UART mode for another 0.75s. This causes an issue because the slave exits UART mode at time point 1.1s and starts to send PLC detection pulse immediately. If master is still in UART mode after slave exits UART mode, slave's PLC detection pulse may hold master in UART mode.

Figure 10. UART Automatic Exit Through UART Timeout

### **Autonomous Optimized Battery Charging**

The MAX20355 interacts with MAX20357 to create an autonomous, closed-loop battery voltage tracking charging system. This system utilizes a dynamic voltage scaling (DVS) buck-boost on the MAX20355 in conjunction with an ultra-low dropout charger (ULDO) on the MAX20357. The PLC interface closes the loop allowing the buck-boost to adjust its output voltage to accommodate the minimum required headroom on the charger. This method allows for excellent 90% efficient energy transfer from the case battery to the earbud battery without the need to place bulky inductors on the tiny form factor ear buds. The excellent efficiency and extremely low heat generation of this charging system offer an increase in the number of charging cycles that can be supported by the case battery as well as the option to increase the rate of charge and deliver faster recharge times to the end customer.

#### **Charger Battery Voltage Tracking Loop**

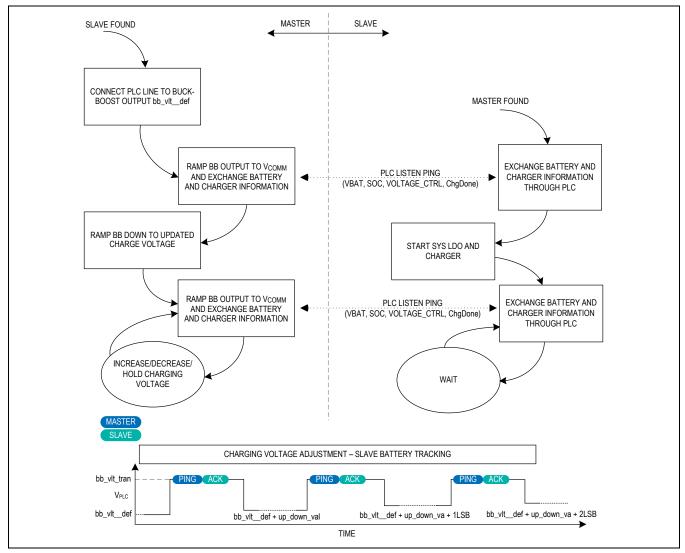

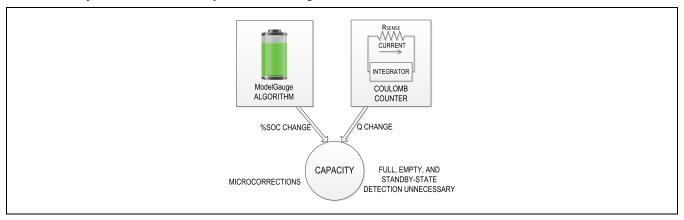

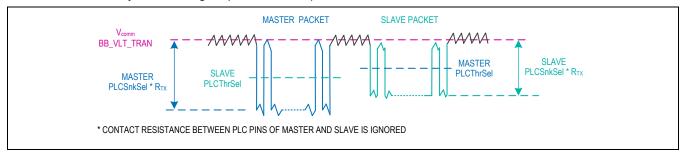

Figure 11 shows the structure of the automatic charger battery voltage tracking algorithm. The charger battery voltage tracking algorithm is accomplished with data exchanges initiated by the master and responded to by the slave(s). Once the connection is built between master and slave(s), the master connects the buck-boost regulator to the PLC line and holds PLC voltage to bb\_vlt\_\_def (3.5V by default) for 100ms. Then pull PLC line to communication voltage (5.5V by default) and starts to PING. The communication voltage is programmable through bb\_vlt\_tran. Slave responds with ACK packet after master sends the first LISTEN command during PING. Slave's ACK packet contains information including slave GPIO status, battery information, charging status, and PLC voltage up/down request. Master adjusts buck-boost output based on the PLC voltage up/down request received from slave(s).

Figure 11. Polling Structure of Automatic Charging Algorithm

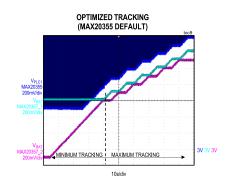

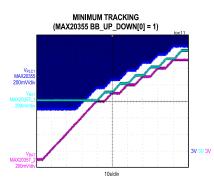

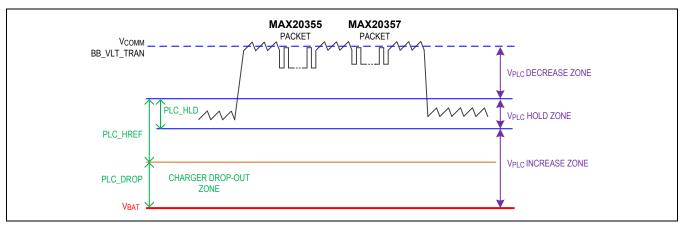

Slave compares battery voltage with PLC line voltage. If the PLC input voltage is above the programmed upper threshold (PLC voltage is in decrease zone), the slave sends a "decrease" signal during PING. Similarly, if PLC voltage is below the lower limit (increase zone) or within the limit (hold zone), it sends an "increase" or "hold" signal accordingly. The voltage thresholds are fully programmable through the parameters shown in <u>Figure 12</u>. The minimum step of voltage adjustment is programmable through I<sup>2</sup>C register bits up\_down\_val.

Figure 12. Slave Voltage Control Algorithm

#### **Charger Voltage Tracking Algorithm**

When the system works in dual slave mode, the two slaves attached at PLC1 and PLC2 are not guaranteed to have matching battery voltages. The automatic charging voltage adjustment algorithm offers multiple options for which battery should be given preference. System designers have three choices:

- Minimum Voltage Tracking: always target the lower of the two voltages. This approach maximizes efficiency since

the voltage drop on the charger is minimized in all cases. The cost is that it increases the time it takes to charge the

higher voltage battery since it cannot be charged until the two batteries reach the same voltage.

- **Maximum Voltage Tracking:** always target the higher of the two voltages. This approach sacrifices some efficiency in exchange for the fastest charge time for both batteries.

- Optimized Battery Voltage Tracking: target the lower battery until the batteries get within a certain voltage avg\_t\_delta of each other. avg\_t\_delta is programmable and can be tuned based on designer preferences. This algorithm offers a good balance between efficiency and charge time.

The three algorithm options are demonstrated in <u>Table 5</u> and <u>Table 6</u>. Note that the battery voltage mentioned above is the average battery voltage reported from the MAX20357 fuel gauge, which is read-only register AVGVCELL\_byte\_1 and AVGVCELL byte 0 through I<sup>2</sup>C, not real-time slave battery voltage.

Table 5. Maximum and Minimum Battery Voltage Tracking

| MINIMUM TRACKING bb_alg_min | MAXIMUM TRACKING<br>bbalg_max | CHARGER1 | CHARGER2 | PLC CHARGE VOLTAGE VPLC |

|-----------------------------|-------------------------------|----------|----------|-------------------------|

| 1                           | 0                             | Hold     | Hold     | Hold                    |

| 1                           | 0                             | Hold     | Decrease | Decrease                |

| 1                           | 0                             | Hold     | Increase | Hold                    |

| 1                           | 0                             | Decrease | Х        | Decrease                |

| 1                           | 0                             | Increase | Hold     | Hold                    |

| 1                           | 0                             | Increase | Decrease | Decrease                |

| 1                           | 0                             | Increase | Increase | Increase                |

| 0                           | 1                             | Hold     | Hold     | Hold                    |

| 0                           | 1                             | Hold     | Decrease | Hold                    |

| 0                           | 1                             | Hold     | Increase | Increase                |

| 0                           | 1                             | Decrease | Hold     | Hold                    |

| 0                           | 1                             | Decrease | Decrease | Decrease                |

| 0                           | 1                             | Decrease | Increase | Increase                |

| 0                           | 1                             | Increase | X        | Increase                |

Table 6. Optimized Battery Voltage Tracking

| V <sub>BAT1</sub> -V <sub>BAT2</sub>   < avg_t_delta | bbalg_min | bbalg_max | BATTERY TRACKING ALGORITHM |

|------------------------------------------------------|-----------|-----------|----------------------------|

| False                                                | 1         | 1         | Minimum Tracking           |

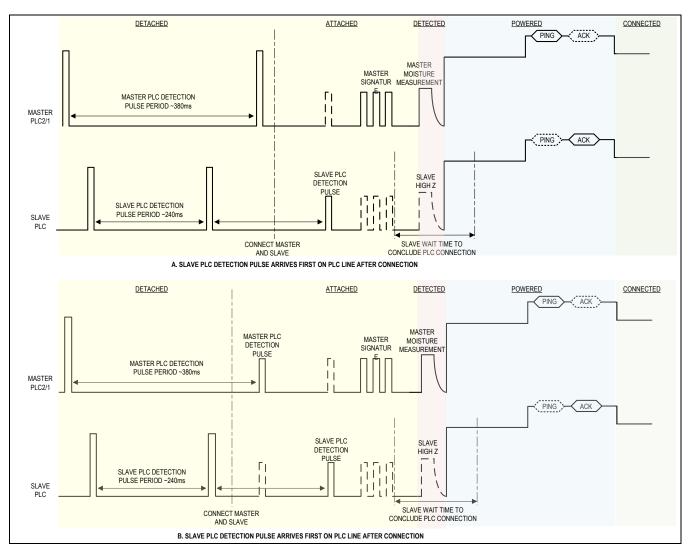

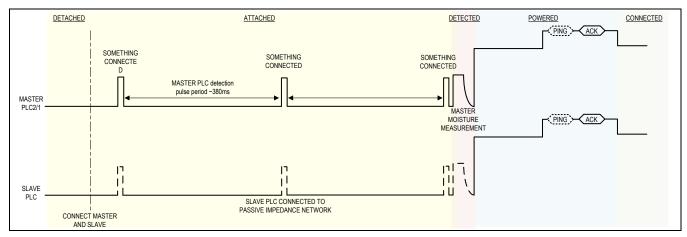

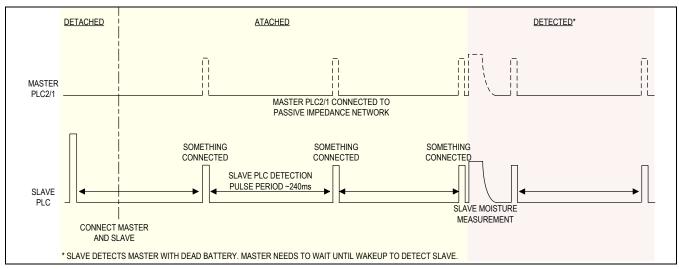

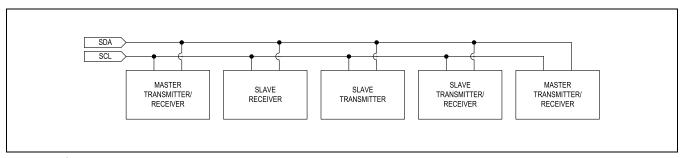

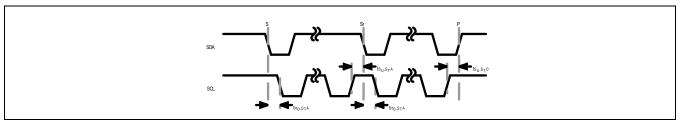

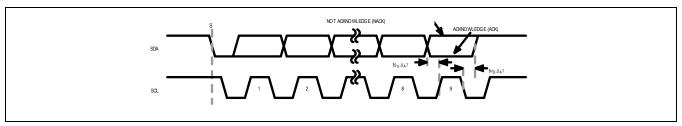

| False                                                | 0         | 0         | Minimum Tracking           |