# HMC1065LP4E

03 0915

### **Typical Applications**

The HMC1065LP4E is ideal for:

- Point-to-Point and Point-to-Multi-Point Radios

- Satellite Communications

- Sensors

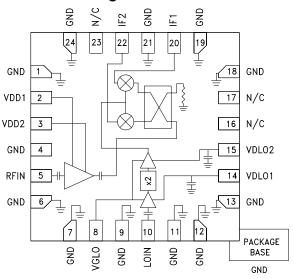

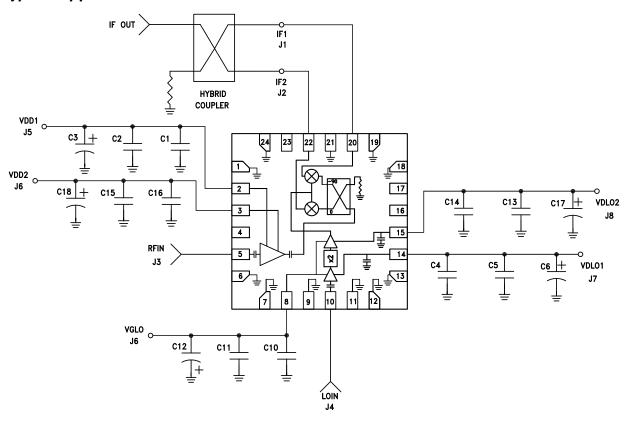

#### **Functional Diagram**

## GaAs MMIC I/Q DOWNCONVERTER 27 - 34 GHz

#### **Features**

Conversion Gain: 13 dB Image Rejection: 17 dBc

Input Third-Order Intercept (IP3): -2 dBm

LO Drive Range: -4 dBm to +4 dBm 24 Lead 4 mm x 4 mm SMT Package

#### **General Description**

The HMC1065LP4E is a compact GaAs MMIC Image Reject Low Noise Converter in a leadless RoHS compliant SMT package. This device provides a small signal conversion gain of 13 dB with 17 dBc of image rejection and 2 dBm of Input IP3. The HMC1065LP4E utilizes an RF LNA followed by an I/Q mixer which is driven by an active x2 multiplier. IF1 and IF2 mixer outputs are provided and an external 90° hybrid is needed to select the required sideband. The I/Q mixer topology reduces the need for filtering of the unwanted sideband. The HMC1065LP4E is a much smaller alternative to hybrid style image reject downconverter assemblies and it eliminates the need for wire bonding by allowing the use of surface mount manufacturing techniques.

## Electrical Specifications,

$T_{\Delta}$  = +25°C, IF = 2000 MHz, LO = +2 dBm, VDLO1 = VDLO2 = 3 V, VDD1 = VDD2 = 3 V, USB [1]

| Parameter                               | Min. | Тур. | Max. | Units |

|-----------------------------------------|------|------|------|-------|

| RF Frequency Range                      | 27   |      | 34   | GHz   |

| LO Frequency Range                      | 11.5 |      | 19   | GHz   |

| IF Frequency Range                      | DC   |      | 4    | GHz   |

| LO Drive Range                          | -4   |      | +4   | dBm   |

| Conversion Gain                         | 9    | 12   |      | dB    |

| Noise Figure                            |      | 3    |      | dB    |

| Image Rejection                         | 12   | 17   |      | dBc   |

| Input Power for 1 dB Compression (P1dB) |      | -9   |      | dBm   |

| Input Third-Order Intercept (IIP3)      |      | -2   |      | dBm   |

| Output Third-Order Intercept (OIP3)     |      | 14   |      | dBm   |

| 2x LO / RF Isolation                    | 35   | 45   |      | dB    |

| 2x LO / IF Isolation                    |      | 20   |      | dB    |

| Amplitude Balance [2]                   |      | -1   |      | dB    |

| Phase Balance [2]                       |      | 7    |      | deg   |

| Supply Current (IDLO) [3]               |      | 150  |      | mA    |

| Supply Current (IDD)                    |      | 90   |      | mA    |

<sup>[1]</sup> All measurements performed with upper sideband selected and external 90° hybrid at the IF ports, unless otherwise noted.

<sup>[2]</sup> Data taken without external 90° hybrid, IF = 1000 MHz.

<sup>[3]</sup> Adjust VGLO1 and VGLO2 between -2 V and 0 V to achieve total quiescent current (IDLO1 + IDLO2) = 150 mA.

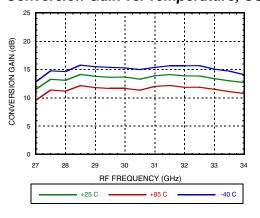

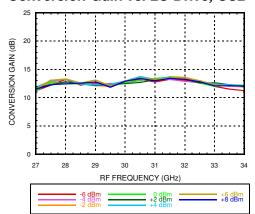

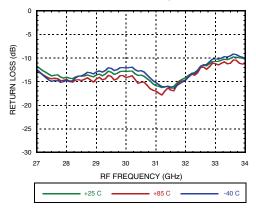

## Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 2000 MHz

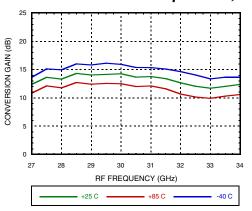

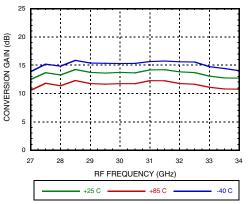

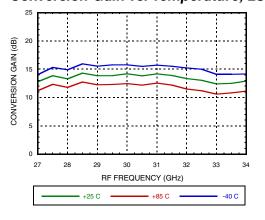

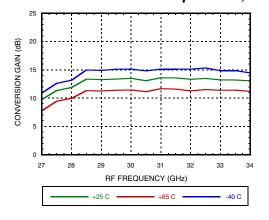

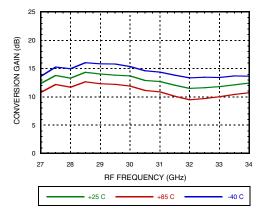

#### Conversion Gain vs. Temperature, USB

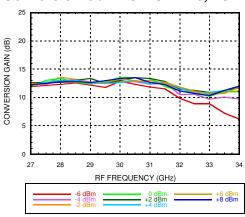

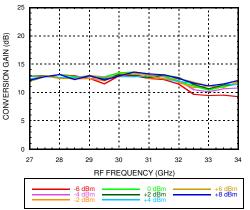

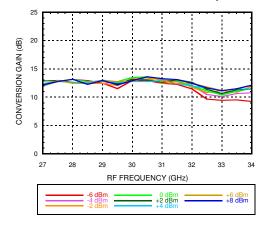

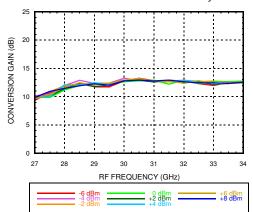

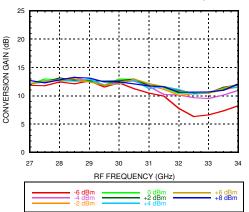

#### Conversion Gain vs. LO Drive, USB

#### RF Return Loss vs. Temperature

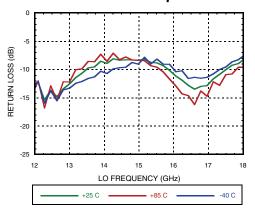

#### LO Return Loss vs. Temperature

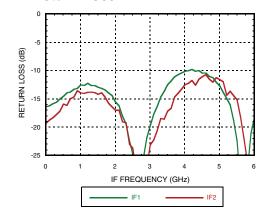

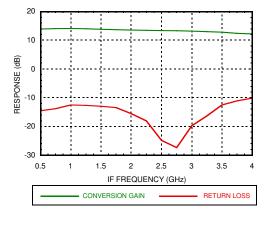

#### IF Return Loss [1]

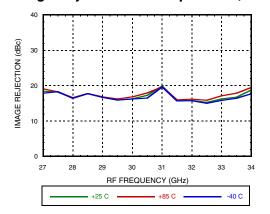

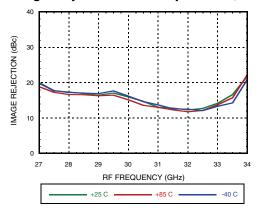

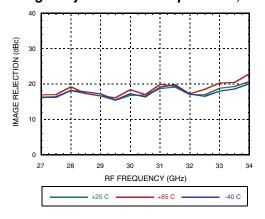

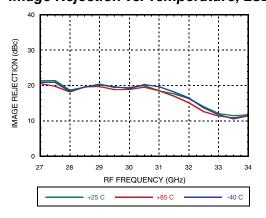

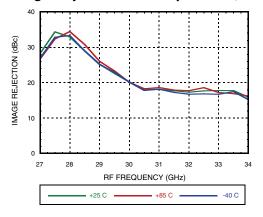

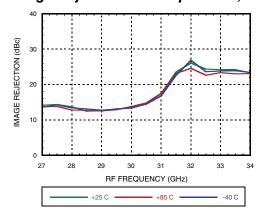

#### Image Rejection vs. Temperature, USB

#### [1] Data taken without external IF 90° hybrid

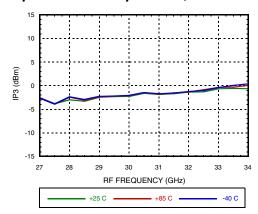

## Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 2000 MHz

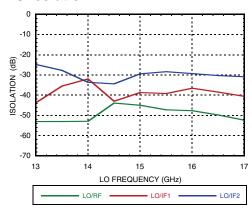

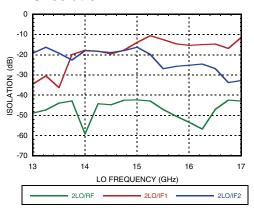

#### LO Isolation [1]

#### 2x LO Isolation [1]

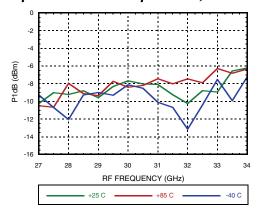

#### Input P1dB vs. Temperature, USB

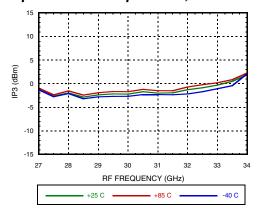

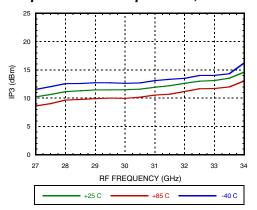

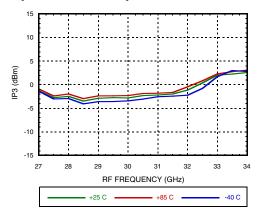

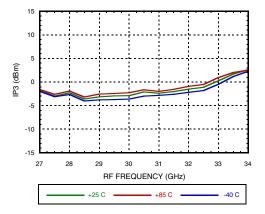

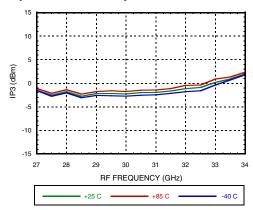

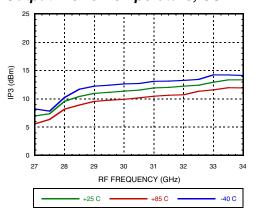

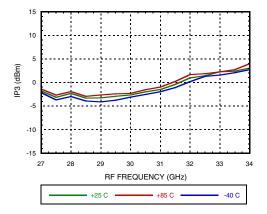

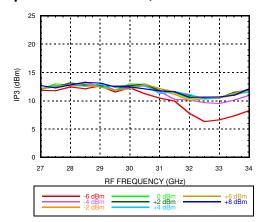

Input IP3 vs. Temperature, USB

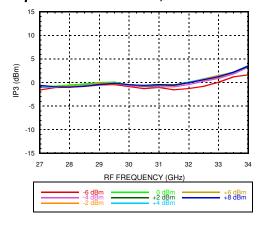

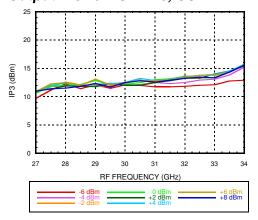

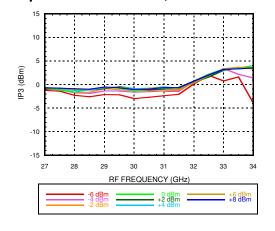

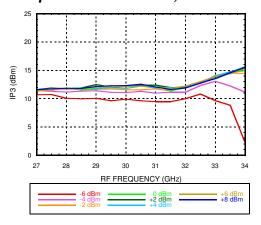

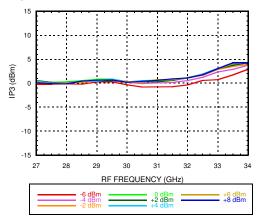

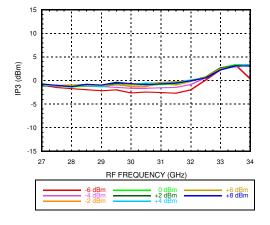

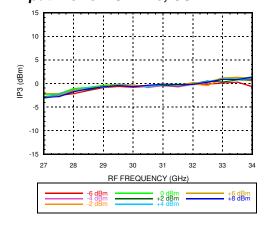

#### Input IP3 vs. LO Drive, USB

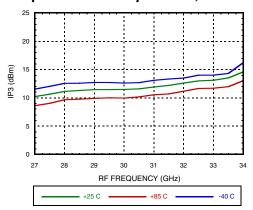

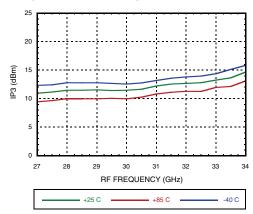

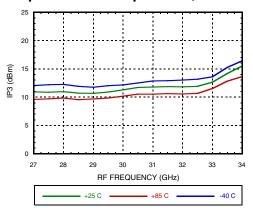

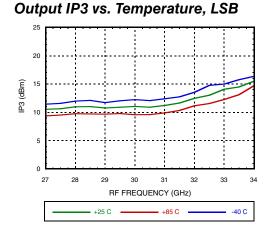

#### Output IP3 vs. Temperature, USB

[1] Data taken without external IF 90° hybrid

Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 2000 MHz

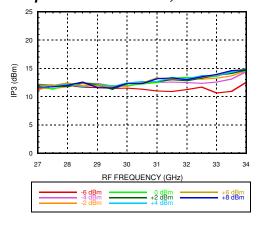

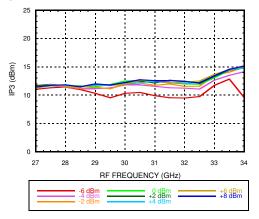

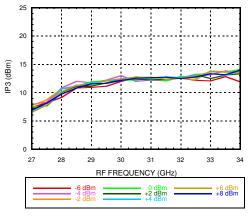

#### Output IP3 vs. LO Drive, USB

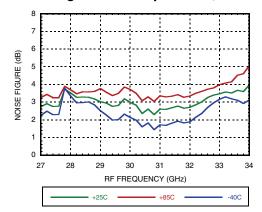

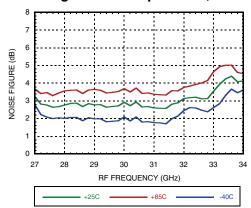

#### Noise Figure vs. Temperature, USB

#### IF Bandwidth [1]

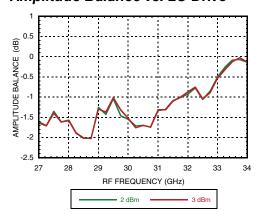

#### Amplitude Balance vs. LO Drive [1] [2]

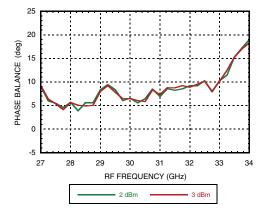

#### Phase Balance vs. LO Drive [1] [2]

- [1] Data taken without external  $90^{\circ}$  hybrid.

- [2] Data taken with IF = 1000MHz.

### Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 2000 MHz

#### Conversion Gain vs. Temperature, LSB

#### Conversion Gain vs. LO Drive, LSB

#### Image Rejection vs. Temperature, LSB

Input IP3 vs. Temperature, LSB

#### Input IP3 vs. LO Drive, LSB

Output IP3 vs. Temperature, LSB

# Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 2000 MHz Output IP3 vs. LO Drive, LSB

# Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 1000 MHz

### Conversion Gain vs. Temperature, USB

## Conversion Gain vs. LO Drive, USB

#### Image Rejection vs. Temperature, USB

#### Input IP3 vs. Temperature, USB

# Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 1000 MHz Input IP3 vs. LO Drive, USB Output IP3 vs. Temperature, USB

#### Output IP3 vs. LO Drive, USB

#### Noise Figure vs. Temperature, USB

#### Conversion Gain vs. Temperature, LSB

#### Conversion Gain vs. LO Drive, LSB

# Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 1000 MHz Image Rejection vs. Temperature, LSB Input IP3 vs. Temperature, LSB

#### Input IP3 vs. LO Drive LSB

#### Output IP3 vs. Temperature, LSB

#### Output IP3 vs. LO Drive, LSB

Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 3300 MHz

#### Conversion Gain vs. Temperature, USB

#### Conversion Gain vs. LO Drive, USB

#### Image Rejection vs. Temperature, USB

Input IP3 vs. Temperature, USB

#### Input IP3 vs. LO Drive, USB

#### Output IP3 vs. Temperature, USB

Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 3300 MHz

Output IP3 vs. LO Drive, USB

Noise Figure vs. Temperature, USB

#### Conversion Gain vs. Temperature, LSB

#### Conversion Gain vs. LO Drive, LSB

#### Image Rejection vs. Temperature, LSB

#### Input IP3 vs. Temperature, LSB

Data Taken as SSB Downconverter with External IF 90° Hybrid, IF = 3300 MHz

Input IP3 vs. LO Drive, LSB

Output IP3 vs. Temperature, LSB

#### Output IP3 vs. LO Drive, LSB

# v03.0915 GaAs MMIC I/Q DOWNCONVERTER

27 - 34 GHz

#### MxN Spurious Outputs, IF = 1 GHz [1]

|     | nLO |    |    |    |    |

|-----|-----|----|----|----|----|

| mRF | 0   | 1  | 2  | 3  | 4  |

| 0   | х   | 35 | 18 | 49 |    |

| 1   | 7   | 41 | 0  | 48 | 28 |

| 2   |     | 59 | 52 | 64 | 35 |

| 3   |     |    |    | 85 | 69 |

RF = 30 GHz @ -8 dBm

LO = 14.5 GHz @ +2 dBm

All values in dBc below IF power level (1RF -2LO)

Spur values are (M x RF) + (N x LO)

## MxN Spurious Outputs, IF = 2 GHz [1]

|     | nLO |    |    |    |    |

|-----|-----|----|----|----|----|

| mRF | 0   | 1  | 2  | 3  | 4  |

| 0   | х   | 32 | 18 | 52 |    |

| 1   | 8   | 48 | 0  | 47 | 31 |

| 2   |     | 64 | 61 | 65 | 37 |

| 3   |     |    |    | 86 | 68 |

RF = 30 GHz @ -8 dBm

LO = 14.0 GHz @ +2 dBm

All values in dBc below IF power level (1RF -2LO)

Spur values are (M x RF) + (N x LO)

#### MxN Spurious Outputs, IF = 3.3 GHz [1]

|     | nLO |    |    |    |    |

|-----|-----|----|----|----|----|

| mRF | 0   | 1  | 2  | 3  | 4  |

| 0   |     | 42 | 23 | 46 |    |

| 1   | 7   | 50 | 0  | 38 | 28 |

| 2   |     | 79 | 60 | 67 | 43 |

| 3   |     |    |    | 88 | 63 |

RF = 30 GHz @ -8 dBm

LO = 13.35 GHz @ +2 dBm

All values in dBc below IF power level (1RF -2LO)

Spur values are  $(M \times RF) + (N \times LO)$

#### Typical Application

| C1, C4, C10, C14, C16 | 100 pF Capacitor, 0402 Pkg.   |  |

|-----------------------|-------------------------------|--|

| C2, C5, C11, C13, C15 | 0.1 uF Capacitor, 0402 Pkg.   |  |

| C3, C6, C12, C17, C18 | 4.7 μF Capacitor, Case A Pkg. |  |

#### **Pin Descriptions**

| Pin Number                                      | Function | Description                                                                                                                                                                                 | Interface Schematic |

|-------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1, 4, 6, 7, 9, 11,<br>12, 13, 18, 19,<br>21, 24 | GND      | Ground Connect. These pins and exposed ground paddle must be connected to RF/DC ground.                                                                                                     | → GND<br>—          |

| 2                                               | VDD1     | Drain Bias for the low noise amplifier. The recommended                                                                                                                                     | OVDD1, VDD2         |

| 3                                               | VDD2     | DC voltage is 3 V. Refer to the typical application circuit for required external components.                                                                                               |                     |

| 5                                               | RFIN     | Radio Frequency Input. This pin is AC coupled and matched to 50 Ohms.                                                                                                                       | RFIN O              |

| 8                                               | VGLO     | Gate Bias for the Local Oscillator. Adjust VGLO from -2 V to 0 V to set total VDLO1 and VDLO2 current to 150mA.  Refer to the typical application circuit for required external components. | VGLOO =             |

| 10                                              | LOIN     | Local Oscillator Input. This pin is AC coupled and matched to 50 Ohms.                                                                                                                      | LOIN O              |

| 14                                              | VDLO1    | Drain Bias for the Multiplier Input Buffer Amp. The recommended DC voltage is 3V. Refer to the typical application circuit for required external components.                                | OVDLO1, VDLO2       |

| 15                                              | VDLO2    | Drain Bias for the Multiplier output Buffer Amp. The recommended DC voltage is 3V. Refer to the typical application circuit for required external components.                               |                     |

| 16, 17, 23                                      | N/C      | No connection required. The pins are not connected inter-<br>nally. However, all data shown herein was measured with<br>these pins connected to RF/DC ground externally.                    |                     |

| 20                                              | IF1      | Quadrature Intermediate Frequency Inputs. These pins are DC coupled. For applications not requiring operation to DC, use an off chip DC blocking capacitor. For operation to DC,            | IF1,IF2 0—77        |

| 22                                              | IF2      | these pins must not source/sink more than 3 mA of current or device non-function and failure may result.                                                                                    |                     |

### **Absolute Maximum Ratings**

| RF Input                                                      | +8 dBm           |

|---------------------------------------------------------------|------------------|

| LO Input                                                      | +8 dBm           |

| Drain Bias Voltage (Vdd)                                      | +3.5 V           |

| Channel Temperature                                           | 175 °C           |

| Continuous Pdiss (T = 85°C)<br>(derate 18.5 mW/°C above 85°C) | 1.66 W           |

| Thermal Resistance (channel to ground paddle)                 | 54.1 °C/W        |

| Storage Temperature Range                                     | -65 to +150 °C   |

| Operating Temperature Range                                   | -40 to +85 °C    |

| ESD Sensitivity (HBM)                                         | 250 V (Class 1A) |

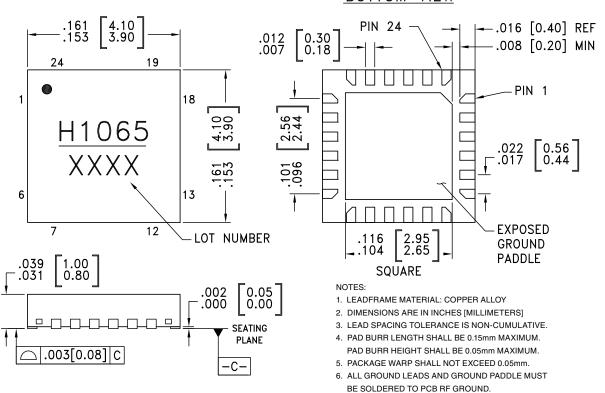

#### **Outline Drawing**

#### **BOTTOM VIEW**

#### **Package Information**

| Part Number | Package Body Material                              | Lead Finish           | MSL Rating | Package Marking [2]  |

|-------------|----------------------------------------------------|-----------------------|------------|----------------------|

| HMC1065LP4E | RoHS-compliant Low Stress Injection Molded Plastic | 100% Sn 10 micron min | MSL1 [1]   | <u>H1065</u><br>XXXX |

<sup>[1]</sup> Max peak reflow temperature of 260 °C

7. REFER TO HITTITE APPLICATION NOTE FOR

SUGGESTED LAND PATTERN.

<sup>[2] 4-</sup>Digit lot number XXXX

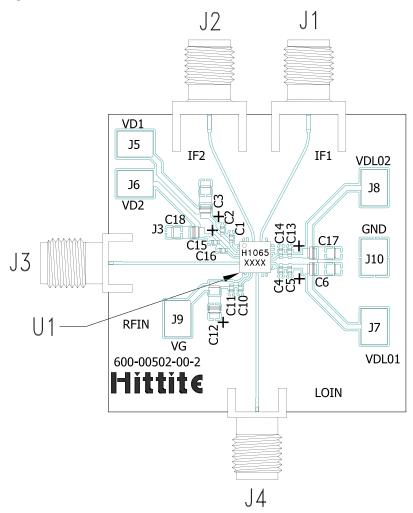

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB Eval01-HMC1065LP4 [1]

| Item                  | Description                   |

|-----------------------|-------------------------------|

| J1, J2                | SMA SRI                       |

| J3, J4                | K-Connector SRI               |

| J5 - J10              | DC Pins                       |

| C1, C4, C10, C14, C16 | 100 pF Capacitor, 0402 Pkg.   |

| C2, C5, C11, C13, C15 | 0.1 uF Capacitor, 0402 Pkg.   |

| C3, C6, C12, C17, C18 | 4.7 μF Capacitor, Case A      |

| U1                    | HMC1065LP4E Downconverter     |

| PCB [2]               | 600-00502-00 Evaluation Board |

$\label{eq:complete} \ensuremath{\text{[1]}} \ensuremath{\,\text{Reference this number when ordering complete evaluation PCB}}$

[2] Circuit Board Material: Arlon 25FR, FR4 or Rogers 4350

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Analog Devices upon request.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

HMC1065LP4E EVAL01-HMC1065LP4