LT6554

#### DESCRIPTION

Demonstration Circuit 794 is a Triple High Speed Video Buffer featuring the LT6554. This circuit is designed to demonstrate DC-coupled performance in either split- or single-supply operation. Table 1 indi-

cates the performance that is achieved with this evaluation board.

Design files for this circuit board are available. Call the LTC factory.

Table 1. Performance Summary  $(T_A = 25^{\circ}C)$

| PARAMETER                          | CONDITION                                              | VALUE                             |

|------------------------------------|--------------------------------------------------------|-----------------------------------|

| Cupply Voltage                     | Split supply operation, Min/Max                        | ±2.3V/±6V                         |

| Supply Voltage                     | Single supply operation, Min/Max                       | +4.5/+12V                         |

| Input Impedance, INR, ING, INB     |                                                        | $75\Omega$ , dc-coupled to ground |

| Output Impedance, OUTR, OUTG, OUTB |                                                        | 75Ω, dc-coupled                   |

| CAL trace Impedance                |                                                        | 75Ω nominal                       |

| Onin                               | Outputs terminated into $75\Omega$                     | -6dB nominal                      |

| Gain                               | Outputs terminated into High impedance                 | 0dB nominal                       |

| Bandwidth                          | –3dB, outputs terminated in 75 $\Omega$ , -13dBm input | 450MHz typical                    |

| Croostall                          | Worst-case All Hostile, 10MHz                          | -75dB typical                     |

| Crosstalk                          | Worst-case All Hostile, 100MHz                         | -50dB typical                     |

|                                    | ±3.3V Split Supply, No Output Clipping, Hi-Z loading   | ±2.0V                             |

| Input Signal Voltage Range         | ±5.0V Split Supply, No Output Clipping, Hi-Z loading   | ±3.7V                             |

|                                    | +9.0V Single Supply, No Output Clipping, Hi-Z loading  | +1.3 to +7.7V                     |

| On/Off Control Innut               | Logic Low Voltage (Amplifiers ON), DGND = 0V           | ≤0.8V                             |

| On/Off Control Input               | Logic High Voltage (Amplifiers OFF), DGND = 0V         | ≥2.0V (5.5V max)                  |

### **OPERATING PRINCIPLES**

DC794 provides three identical channels of wideband signal buffering suitable for driving HDTV or high-resolution RGB video multiplexers or digitizers. Each buffer section of the LT6554 provides a fixed gain of 1 to a destination load. Each input is terminated to analog ground to properly load the input signal cables.

To minimize ingress of external digital ground noise, the DGND logic reference input is decoupled from analog ground within the LT6554. DC794 includes a jumper, JP2, which allows the DGND to be strapped

to the local analog ground (AGND); for example, when the logic source is floating or none is used during the evaluation. DGND may be left uncommitted with JP2 in the FLOAT position.

Another jumper, JP1, allows the LT6554 to be forced to an ENABLE condition. If JP1 is left in the EXTernal position, then enabling the LT6554 is accomplished by pulling down the EN connection to a level near that of DGND via connection to E1 or J1. A pull-up resistor internal to the LT6554 will provide a default shutdown mode of operation if the control input is left

1

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 794 TRIPLE HIGH SPEED VIDEO BUFFER

open-circuit. NOTE: DO NOT open-circuit EN if V+ is more than 5.5V above DGND; refer to LT6554 data-sheet for application details in this situation.

A CAL trace is also provided on DC794 to provide a means of precision calibration for a Network Analyzer (use the CAL connections when performing the "THRU" transmission calibration). The CAL trace has the same electrical performance and delay as the transmission lines of the three signal channels, thereby allowing circuit board and connector effects

to be eliminated from the transmission measurements.

JP3 is provided as a convenience to eliminate having to externally short V— to GND in the case of SINGLE supply operation. Leave JP3 in the DUAL position when using split supplies.

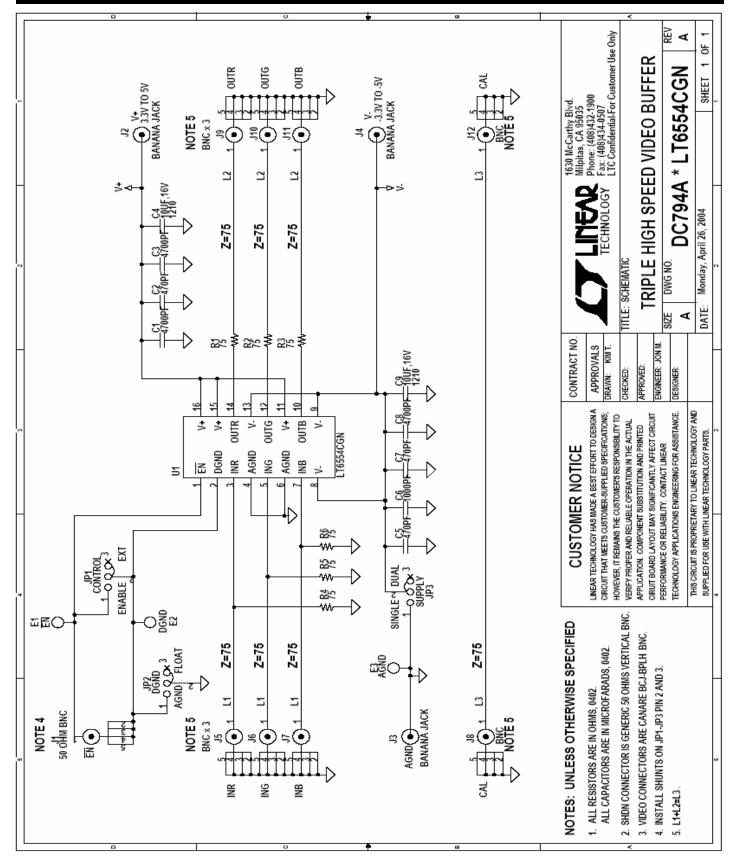

Figure 4 shows the material list of the components used by DC794, and Figure 5 shows the electrical interconnection.

#### **QUICK START PROCEDURE**

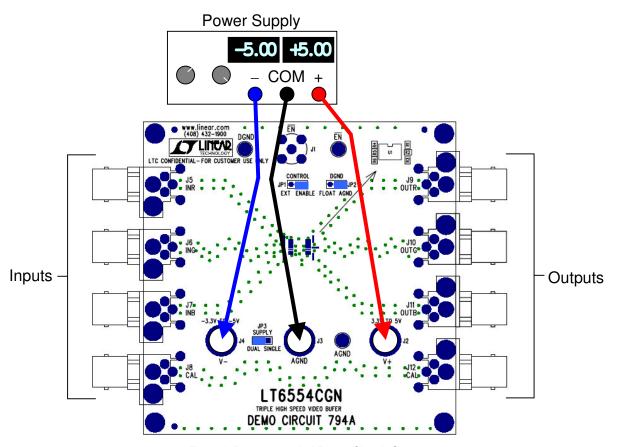

Demonstration Circuit 794 is easy to set up to evaluate the performance of the LT6554. Refer to Figure 1 for proper measurement equipment setup and follow the procedure below:

**NOTE**: Due to the Ultra High Frequencies (UHF) involved, RF measurement practices are required to accurately evaluate the performance of the LT6554.

- 1. Place jumpers in the following positions:

- JP1 ENABLE

- JP2 AGND

- JP3 DUAL

- Prior to connecting the power supply, preset the output voltages to ±5V, or to the desired level, if different.

- 3. With power off, connect the power supplies to V+, V-, and GND using banana-plug cables.

- 4. Energize the power supply.

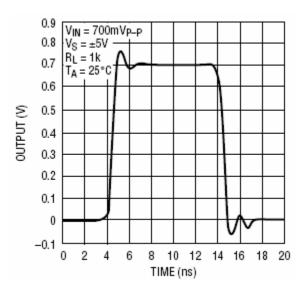

- 5. For video-signal evaluation, connect a componentvideo signal source to the inputs and a high input impedance video analyzer to the outputs, using

- equal-length  $75\Omega$  cabling amongst the three video channels. Figure 3 shows a typical pulse response.

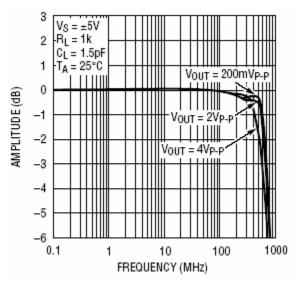

- 6. If using a Network Analyzer, perform the THRU transmission calibration with all cabling, adapters, impedance converters, etc. in place, and using the DC794 CAL trace as the reference OdB path.

- 7. Connect a Network Analyzer (if used) to the appropriate channels to measure frequency response and crosstalk as desired. Figure 2 shows a typical transmission plot for 1k loading. Use of  $75\Omega$  loading with the DC794 as shipped will reduce the -3dB response to about 450MHz (and show a passband loss of -6dB). If the analyzer has only a low-impedance input, then the  $R_L$ =1k $\Omega$  condition can be simulated by installing 953 $\Omega$  resistors in R1, R2, and R3 and providing a 26.05dB correction to the  $50\Omega$  analyzer reading (or 22.74dB for a  $75\Omega$  instrument).

- 8. To evaluate the shutdown mode, disconnect or relocate the JP1 jumper to the EXT position (with no connections made at EN, or if present, a logic high provided).

Figure 1. Recommended Demo Circuit Setup

Figure 2. Typical Transmission Frequency Response

Figure 3. Typical Time-Domain Transmission Response

| Item | Qty | Reference                        | Part Description                    | Manufacture / Part #       |

|------|-----|----------------------------------|-------------------------------------|----------------------------|

| 1    | 3   | C1,C3,C8                         | CAP., X7R, 4700PF 50V, 10%, 0402    | AVX, 04025C472KAT1A        |

| 2    | 3   | C2,C5,C7                         | CAP., NPO, 470PF 25V, 10%, 0402     | AVX, 04023A471KAT1A        |

| 3    | 2   | C4,C9                            | CAP., X5R, 10uF 16V, 20%, 1210      | TAIYO YUDEN, EMK325BJ106MN |

| 4    | 1   | C6                               |                                     | AVX, 04023C102KAT1A        |

| 5    | 3   | E1,E2,E3                         | TP, TURRET, .094"                   | MILL-MAX, 2501-2           |

| 6    | 3   | JP1,JP2,JP3                      | JMP, 3PIN 1 ROW .079CC              | COMM-CON, 2802S-03-G1      |

| 7    | 3   | SHUNTS FOR JP1-JP3 (PIN 2 AND 3) | SHUNT, .079" CENTER                 | COMM-CON CCIJ2MM-138G      |

| 8    | 1   | J1                               | CONN, BNC, 5 PINS                   | CONNEX, 112404             |

| 9    | 3   | J2,J3,J4                         | JACK, BANANA,KEY-575                | KEYSTONE, 575-4            |

| 10   | 8   | J5-J12                           | CONN, BNC, RIGHT ANGLE              | CANARE, BCJ-BPLH           |

| 11   | 6   | R1,R2,R3,R4,R5,R6                | RES., CHIP, 75 OHMS, 1/16W, 5% 0402 | AAC, CR05-750JM            |

| 12   | 1   | U1                               | IC., LT6554CGN, SSOP16GN            | LINEAR, LT6554CGN          |

| 13   | 4   | FOR 4 MTG                        | SCREW, #4-40, 1/4"                  | ANY                        |

| 14   | 4   | FOR 4 MTG                        | STANDOFF, #4-40 1/4"                | MICRO PLASTICS 14HTSP101   |

Figure 4. DC794 Bill of Material

## QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 794 TRIPLE HIGH SPEED VIDEO BUFFER

Figure 5. DC794 Electrical Schematic Diagram

### **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: