# CMOS, 170 MHz, Triple, 10-Bit High Speed Video DAC

Enhanced Product ADV7123-EP

#### **FEATURES**

170 MSPS throughput rate

Triple, 10-bit digital-to-analog converters (DACs)

SEDR

$-70 \text{ dB at } f_{CLK} = 50 \text{ MHz}; f_{OUT} = 1 \text{ MHz}$

-53 dB at  $f_{CLK} = 140$  MHz;  $f_{OUT} = 40$  MHz

RS-343A-/RS-170-compatible output

**Complementary outputs**

DAC output current range: 2.0 mA to 26.5 mA

TTL-compatible inputs Internal reference: 1.235 V Single-supply 3.3 V operation 48-lead LFCSP package

Low power dissipation: 30 mW minimum at 3 V Low power standby mode: 6 mW typical at 3 V

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard)

Military temperature range: -55°C to +105°C

Controlled manufacturing baseline

One assembly/test site

One fabrication site

Product change notification

Qualification data available on request

#### **APPLICATIONS**

Digital video systems

High resolution color graphics

Digital radio modulation

Image processing

Instrumentation

Video signal reconstruction

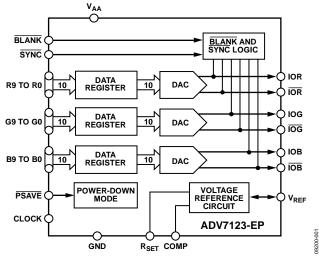

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### **GENERAL DESCRIPTION**

The ADV7123-EP is a triple, high speed digital-to-analog converter (DAC) on a single monolithic chip. It consists of three high speed, 10-bit video DACs with complementary outputs, a standard TTL input interface, and a high impedance, analog output current source.

The ADV7123-EP has three separate 10-bit-wide input ports. A single 3.3 V power supply and clock are the only components required to make the part functional. The ADV7123-EP has additional video control signals: composite SYNC and BLANK. The ADV7123-EP also has a power save mode.

The ADV7123-EP is fabricated in a 5 V CMOS process. Its monolithic CMOS construction ensures greater functionality with lower power dissipation. The ADV7123-EP is available in a 48-lead LFCSP package.

Full details about this enhanced product are available in the ADV7123 data sheet, which should be consulted in conjunction with this data sheet.

#### **PRODUCT HIGHLIGHTS**

- 1. Guaranteed monotonic to 10 bits.

- Compatible with a wide variety of high resolution color graphics systems, including RS-343A and RS-170.

## TABLE OF CONTENTS

| reatures                                | 1 |

|-----------------------------------------|---|

| Enhanced Product Features               | 1 |

| Applications                            | 1 |

| Functional Block Diagram                | 1 |

| General Description                     | 1 |

| Product Highlights                      | 1 |

| Revision History                        | 2 |

| Specifications                          | 3 |

| REVISION HISTORY                        |   |

| 5/2018—Rev. 0 to Rev. A                 |   |

| Changes to Features Section             | 1 |

| Added Enhanced Product Features Section |   |

7/2010—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{AA} = 3.0 \text{ V}$  to 3.6 V,  $V_{REF} = 1.235 \text{ V}$ ,  $R_{SET} = 560 \Omega$ ,  $C_L = 10 \text{ pF}$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted;  $T_{JMAX} = 110^{\circ}\text{C}$ .

Table 1.

| Parameter <sup>2</sup>               | Min  | Тур   | Max  | Unit  | Test Conditions/Comments <sup>1</sup>                                        |  |  |

|--------------------------------------|------|-------|------|-------|------------------------------------------------------------------------------|--|--|

| STATIC PERFORMANCE                   |      |       |      |       |                                                                              |  |  |

| Resolution (Each DAC)                |      |       | 10   | Bits  | $R_{SET} = 680 \Omega$                                                       |  |  |

| Integral Nonlinearity (BSL)          | -1   | +0.5  | +1   | LSB   | $R_{SET} = 680 \Omega$                                                       |  |  |

| Differential Nonlinearity            | -1   | +0.25 | +1   | LSB   | $R_{SET} = 680 \Omega$                                                       |  |  |

| DIGITAL AND CONTROL INPUTS           |      |       |      |       |                                                                              |  |  |

| Input High Voltage, V <sub>IH</sub>  | 2.0  |       |      | V     |                                                                              |  |  |

| Input Low Voltage, V <sub>IL</sub>   |      | 0.8   |      | V     |                                                                              |  |  |

| Input Current, I <sub>IN</sub>       | -1   |       | +1   | μΑ    | $V_{IN} = 0.0  V  or  V_{DD}$                                                |  |  |

| PSAVE Pull-Up Current                |      | 20    |      | μΑ    |                                                                              |  |  |

| Input Capacitance, C <sub>IN</sub>   |      | 10    |      | pF    |                                                                              |  |  |

| ANALOG OUTPUTS                       |      |       |      |       |                                                                              |  |  |

| Output Current                       | 2.0  |       | 26.5 | mA    | Green DAC, $\overline{SYNC}$ = high                                          |  |  |

| •                                    | 2.0  |       | 18.5 | mA    | RGB DAC, $\overline{\text{SYNC}} = \text{low}$                               |  |  |

| DAC-to-DAC Matching                  |      | 1.0   |      | %     |                                                                              |  |  |

| Output Compliance Range, Voc         | 0    |       | 1.4  | V     |                                                                              |  |  |

| Output Impedance, R <sub>OUT</sub>   |      | 70    |      | kΩ    |                                                                              |  |  |

| Output Capacitance, C <sub>OUT</sub> |      | 10    |      | pF    |                                                                              |  |  |

| Offset Error                         |      | 0     | 0    | % FSR | Tested with DAC output = 0 V                                                 |  |  |

| Gain Error <sup>3</sup>              |      | 0     |      | % FSR | FSR = 17.62 mA                                                               |  |  |

| VOLTAGE REFERENCE, EXTERNAL          |      |       |      |       |                                                                              |  |  |

| Reference Range, V <sub>REF</sub>    | 1.12 | 1.235 | 1.35 | V     |                                                                              |  |  |

| VOLTAGE REFERENCE, INTERNAL          |      |       |      |       |                                                                              |  |  |

| Voltage Reference, V <sub>REF</sub>  |      | 1.235 |      | V     |                                                                              |  |  |

| POWER DISSIPATION                    |      |       |      |       |                                                                              |  |  |

| Digital Supply Current⁴              |      | 2.2   | 5.0  | mA    | $f_{CLK} = 50 \text{ MHz}$                                                   |  |  |

|                                      |      | 6.5   | 12.0 | mA    | $f_{CLK} = 140 \text{ MHz}$                                                  |  |  |

|                                      |      | 7.5   | 13.5 | mA    | $f_{CLK} = 170 \text{ MHz}$                                                  |  |  |

| Analog Supply Current                |      | 67    | 72   | mA    | $R_{SET} = 560 \Omega$                                                       |  |  |

|                                      |      | 8     |      | mA    | $R_{SET} = 4933 \Omega$                                                      |  |  |

| Standby Supply Current               |      | 2.1   | 5.0  | mA    | $\overline{\text{PSAVE}} = \text{low, digital and control inputs at V}_{DD}$ |  |  |

| Power Supply Rejection Ratio         |      | 0.1   | 0.5  | %/%   |                                                                              |  |  |

$<sup>^{1}</sup>$  Temperature range  $T_{MIN}$  to  $T_{MAX}$ :  $-55^{\circ}C$  to  $+105^{\circ}C.$

$<sup>^2\</sup>mbox{These}$  maximum/minimum specifications are guaranteed by characterization over the 3.0 V to 3.6 V range.

$<sup>^3</sup>$  Gain error = {(Measured (FSC)/Ideal (FSC) - 1)  $\times$  100}, where Ideal (FSC) =  $V_{REF}/R_{SET} \times K \times (0x3FFH)$  and K = 7.9896.

$<sup>^4</sup>$  Digital supply is measured with a continuous clock that has data input corresponding to a ramp pattern and with an input level at 0 V and  $V_{DD}$ .

## **DYNAMIC SPECIFICATIONS**

$V_{AA} = 3.0 \text{ V to } 3.6 \text{ V}, V_{REF} = 1.235 \text{ V}, R_{SET} = 680 \Omega, C_L = 10 \text{ pF. All specifications are at } T_A = 25 ^{\circ}\text{C}, \text{ unless otherwise noted; } T_{JMAX} = 110 ^{\circ}\text{C}.$

Table 2.

| Parameter <sup>1</sup>                                                     | Min Typ Ma | x Unit |

|----------------------------------------------------------------------------|------------|--------|

| AC LINEARITY                                                               |            |        |

| Spurious-Free Dynamic Range to Nyquist <sup>2</sup>                        |            |        |

| Single-Ended Output                                                        |            |        |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 1.00 \text{ MHz}$                  | 67         | dBc    |

| $f_{CLK} = 50 \text{ MHz}; f_{OUT} = 2.51 \text{ MHz}$                     | 67         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$                  | 63         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 20.2 \text{ MHz}$                  | 55         | dBc    |

| $f_{CLK} = 100 \text{ MHz}$ ; $f_{OUT} = 2.51 \text{ MHz}$                 | 62         | dBc    |

| $f_{CLK} = 100 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$                 | 60         | dBc    |

| $f_{CLK} = 100 \text{ MHz}; f_{OUT} = 20.2 \text{ MHz}$                    | 54         | dBc    |

| $f_{CLK} = 100 \text{ MHz}$ ; $f_{OUT} = 40.4 \text{ MHz}$                 | 48         | dBc    |

| $f_{CLK} = 140 \text{ MHz}; f_{OUT} = 2.51 \text{ MHz}$                    | 57         | dBc    |

| $f_{CLK} = 140 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$                 | 58         | dBc    |

| $f_{CLK} = 140 \text{ MHz}; f_{OUT} = 20.2 \text{ MHz}$                    | 52         | dBc    |

| $f_{CLK} = 140 \text{ MHz}; f_{OUT} = 40.4 \text{ MHz}$                    | 41         | dBc    |

| Double-Ended Output                                                        |            |        |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 1.00 \text{ MHz}$                  | 70         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 2.51 \text{ MHz}$                  | 70         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$                  | 65         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 20.2 \text{ MHz}$                  | 54         | dBc    |

| $f_{CLK} = 100 \text{ MHz}; f_{OUT} = 2.51 \text{ MHz}$                    | 67         | dBc    |

| $f_{CLK} = 100 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$                 | 63         | dBc    |

| $f_{CLK} = 100 \text{ MHz}; f_{OUT} = 20.2 \text{ MHz}$                    | 58         | dBc    |

| $f_{CLK} = 100 \text{ MHz}$ ; $f_{OUT} = 40.4 \text{ MHz}$                 | 52         | dBc    |

| $f_{CLK} = 140 \text{ MHz}; f_{OUT} = 2.51 \text{ MHz}$                    | 62         | dBc    |

| $f_{CLK} = 140 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$                 | 61         | dBc    |

| $f_{CLK} = 140 \text{ MHz}; f_{OUT} = 20.2 \text{ MHz}$                    | 55         | dBc    |

| $f_{CLK} = 140 \text{ MHz}; f_{OUT} = 40.4 \text{ MHz}$                    | 53         | dBc    |

| Spurious-Free Dynamic Range Within a Window                                |            |        |

| Single-Ended Output                                                        |            |        |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 1.00 \text{ MHz}$ ; 1 MHz Span     | 77         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$ ; 2 MHz Span     | 73         | dBc    |

| $f_{CLK} = 140 \text{ MHz}$ ; $f_{OUT} = 5.04 \text{ MHz}$ ; 4 MHz Span    | 64         | dBc    |

| Double-Ended Output                                                        |            |        |

| $f_{CLK} = 50 \text{ MHz}; f_{OUT} = 1.00 \text{ MHz}; 1 \text{ MHz Span}$ | 74         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 5.00 \text{ MHz}$ ; 2 MHz Span     | 73         | dBc    |

| $f_{CLK} = 140 \text{ MHz}$ ; $f_{OUT} = 5.00 \text{ MHz}$ ; 4 MHz Span    | 60         | dBc    |

| Total Harmonic Distortion                                                  |            |        |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 1.00 \text{ MHz}$                  |            |        |

| $T_A = 25^{\circ}C$                                                        | 66         | dBc    |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                       | 65         | dBc    |

| $f_{CLK} = 50 \text{ MHz}$ ; $f_{OUT} = 2.00 \text{ MHz}$                  | 64         | dBc    |

| $f_{CLK} = 100 \text{ MHz}$ ; $f_{OUT} = 2.00 \text{ MHz}$                 | 64         | dBc    |

| $f_{CLK} = 140 \text{ MHz}$ ; $f_{OUT} = 2.00 \text{ MHz}$                 | 55         | dBc    |

| Parameter <sup>1</sup>            | Min | Тур | Max | Unit   |

|-----------------------------------|-----|-----|-----|--------|

| DAC PERFORMANCE                   |     |     |     |        |

| Glitch Impulse                    |     | 10  |     | pV-sec |

| DAC-to-DAC Crosstalk <sup>3</sup> |     | 23  |     | dB     |

| Data Feedthrough <sup>4, 5</sup>  |     | 22  |     | dB     |

| Clock Feedthrough <sup>4, 5</sup> |     | 33  |     | dB     |

<sup>&</sup>lt;sup>1</sup> These maximum/minimum specifications are guaranteed by characterization over the 3.0 V to 3.6 V range.

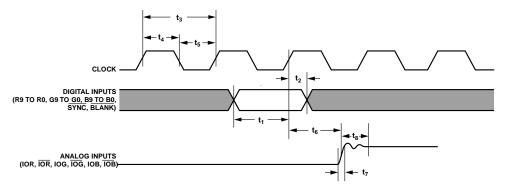

### **TIMING SPECIFICATIONS**

$V_{AA} = 3.0 \text{ V}$  to 3.6 V,  $V_{REF} = 1.235 \text{ V}$ ,  $R_{SET} = 560 \Omega$ ,  $C_L = 10 \text{ pF}$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted;  $T_{JMAX} = 110^{\circ} C$ .

Table 3.

| Parameter <sup>2, 3</sup>           | Symbol                | Min  | Тур | Max | Unit         | Test Conditions/Comments       |

|-------------------------------------|-----------------------|------|-----|-----|--------------|--------------------------------|

| ANALOG OUTPUTS                      |                       |      |     |     |              |                                |

| Analog Output Delay                 | t <sub>6</sub>        |      | 7.5 |     | ns           |                                |

| Analog Output Rise/Fall Time⁴       | t <sub>7</sub>        |      | 1.0 |     | ns           |                                |

| Analog Output Transition Time⁵      | t <sub>8</sub>        |      | 15  |     | ns           |                                |

| Analog Output Skew <sup>6</sup>     | <b>t</b> 9            |      | 1   | 2   | ns           |                                |

| CLOCK CONTROL                       |                       |      |     |     |              |                                |

| CLOCK Frequency <sup>7</sup>        | f <sub>CLK</sub>      |      |     | 170 | MHz          |                                |

| Data and Control Setup              | t <sub>1</sub>        | 0.68 |     |     | ns           |                                |

| Data and Control Hold               | t <sub>2</sub>        | 2.9  |     |     | ns           |                                |

| CLOCK Period                        | t <sub>3</sub>        | 5.88 |     |     | ns           |                                |

| CLOCK Pulse Width High <sup>6</sup> | t <sub>4</sub>        | 2.6  |     |     | ns           | f <sub>CLK_MAX</sub> = 170 MHz |

| CLOCK Pulse Width Low <sup>6</sup>  | <b>t</b> <sub>5</sub> | 2.6  |     |     | ns           | f <sub>CLK_MAX</sub> = 170 MHz |

| Pipeline Delay <sup>6</sup>         | <b>t</b> PD           | 1.0  | 1.0 | 1.0 | Clock cycles |                                |

| PSAVE Up Time <sup>6</sup>          | t <sub>10</sub>       |      | 4   | 10  | ns           |                                |

$<sup>^1</sup>$  Temperature range  $T_{MIN}$  to  $T_{MAX}\!:\!-55^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$  .

$<sup>^2</sup>$  The ADV7123-EP exhibits high performance when operating with an internal voltage reference,  $V_{\text{REF}}$ .

<sup>&</sup>lt;sup>3</sup> DAC-to-DAC crosstalk is measured by holding one DAC high while the other two DACs are making low-to-high and high-to-low transitions.

Clock and data feedthrough is a function of the amount of overshoot and undershoot on the digital inputs. Glitch impulse includes clock and data feedthrough.

<sup>&</sup>lt;sup>5</sup> TTL input values are 0 V to 3 V, with input rise/fall times of 3 ns, measured at the 10% and 90% points. Timing reference points are 50% for inputs and outputs.

<sup>&</sup>lt;sup>2</sup> These maximum/minimum specifications are guaranteed by characterization over the 3.0 V to 3.6 V range.

$<sup>^3</sup>$  Timing specifications are measured with input levels of 3.0  $\acute{V}$  (V $_{IH}$ ) and 0 V (V $_{IL}$ ).

A Rise time was measured from the 10% to 90% point of zero to full-scale transition, fall time from the 90% to 10% point of a full-scale transition.

$<sup>^{5}</sup>$  Measured from the 50% point of full-scale transition to within 2% of the final output value.

<sup>&</sup>lt;sup>6</sup> Guaranteed by characterization.

<sup>&</sup>lt;sup>7</sup> f<sub>CLK</sub> maximum specification production tested at 125 MHz.

- NOTES 1. OUTPUT DELAY  $(t_6)$  MEASURED FROM THE 50% POINT OF THE RISING EDGE OF CLOCKTO THE 50% POINT OF FULL-SCALE TRANSITION. 2. OUTPUT RISE-FALL TIME  $(t_7)$  MEASURED BETWEEN THE 10% AND 90% POINTS OF FULL-SCALE TRANSITION. 3. TRANSITION TIME  $(t_8)$  MEASURED FROM THE 50% POINT OF FULL-SCALE TRANSITION TO WITHIN 2% OF THE FINAL OUTPUT VALUE.

Figure 2. Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1         |                                 |

|-------------------------------------------------|---------------------------------|

| Parameter                                       | Rating                          |

| V <sub>AA</sub> to GND                          | 7 V                             |

| Voltage on Any Digital Pin                      | $GND - 0.5 V to V_{AA} + 0.5 V$ |

| Ambient Operating Temperature (T <sub>A</sub> ) | −55°C to +105°C                 |

| Storage Temperature (Ts)                        | −65°C to +150°C                 |

| Junction Temperature (T <sub>J</sub> )          | 150°C                           |

| Lead Temperature (Soldering, 10 sec)            | 300°C                           |

| Vapor Phase Soldering (1 Minute)                | 220°C                           |

| I <sub>OUT</sub> to GND <sup>1</sup>            | $0V$ to $V_{AA}$                |

<sup>&</sup>lt;sup>1</sup> Analog output short circuit to any power supply or common GND can be of an indefinite duration.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

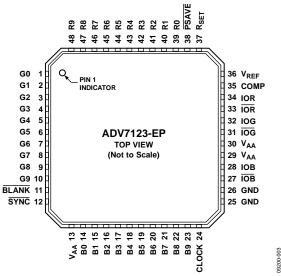

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

Figure 3. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.               | Mnemonic              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 10,              | G0 to G9,             | Red, Green, and Blue Pixel Data Inputs (TTL Compatible). Pixel data is latched on the rising edge of CLOCK.                                                                                                                                                                                                                                                                                                                                                      |

| 14 to 23,<br>39 to 48 | B0 to B9,<br>R0 to R9 | R0, G0, and B0 are the least significant data bits. Unused pixel data inputs should be connected to either the regular printed circuit board (PCB) power or ground plane.                                                                                                                                                                                                                                                                                        |

| 11                    | BLANK                 | Composite Blank Control Input (TTL Compatible). A Logic 0 on this control input drives the analog outputs—IOR, IOB, and IOG—to the blanking level. The BLANK signal is latched on the rising edge of CLOCK. When BLANK is a Logic 0, the R0 to R9, G0 to G9, and B0 to B9 pixel inputs are ignored.                                                                                                                                                              |

| 12                    | SYNC                  | Composite Sync Control Input (TTL Compatible). A Logic 0 on the SYNC input switches off a 40 IRE current source. The sync current is internally connected to the IOG analog output. SYNC does not override any other control or data input; therefore, it should only be asserted during the blanking interval. SYNC is latched on the rising edge of CLOCK. If sync information is not required on the green channel, the SYNC input should be tied to Logic 0. |

| 13, 29, 30            | V <sub>AA</sub>       | Analog Power Supply (3.3 V $\pm$ 10%). All V <sub>AA</sub> pins on the ADV7123-EP must be connected.                                                                                                                                                                                                                                                                                                                                                             |

| 24                    | CLOCK                 | Clock Input (TTL Compatible). The rising edge of CLOCK latches the R0 to R9, G0 to G9, B0 to B9, SYNC, and BLANK pixel and control inputs. Typically, the CLOCK input is the pixel clock rate of the video system. CLOCK should be driven by a dedicated TTL buffer.                                                                                                                                                                                             |

| 25, 26                | GND                   | Ground. The GND pins must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 27, 31, 33            | IOB, IOG, IOR         | Differential Red, Green, and Blue Current Outputs (High Impedance Current Sources). These RGB video outputs are specified to directly drive RS-343A and RS-170 video levels into a doubly terminated 75 $\Omega$ coaxial cable. If the complementary outputs are not required, these outputs should be tied to ground.                                                                                                                                           |

| 28, 32, 34            | IOB, IOG, IOR         | Red, Green, and Blue Current Outputs (High Impedance Current Sources). These RGB video outputs are specified to directly drive RS-343A and RS-170 video levels into a doubly terminated 75 $\Omega$ coaxial cable. All three current outputs should have similar output loads whether or not they are all being used.                                                                                                                                            |

| 35                    | COMP                  | Compensation Pin for the Internal Reference Amplifier. A 0.1 $\mu$ F ceramic capacitor must be connected between COMP and $V_{AA}$ .                                                                                                                                                                                                                                                                                                                             |

| 36                    | V <sub>REF</sub>      | Voltage Reference Input for DACs or Voltage Reference Output (1.235 V). The $V_{REF}$ pin is normally terminated to $V_{AA}$ through a 0.1 $\mu$ F capacitor. However, the ADV7123-EP can be overdriven by an external 1.23 V reference (AD1580), if required.                                                                                                                                                                                                   |

<sup>1.</sup> THE EXPOSED PADDLE ON THE UNDERSIDE OF THE PACKAGE MUST BE SOLDERED TO THE GROUND PLANE TO INCREASE THE RELIABILITY OF THE SOLDER JOINTS AND TO MAXIMIZE THE THERMAL CAPABILITY OF THE PACKAGE.

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                  |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37      | R <sub>SET</sub> | A resistor ( $R_{SET}$ ) connected between this pin and GND controls the magnitude of the full-scale video signal. Note that the IRE relationships are maintained, regardless of the full-scale output current. For nominal video levels into a doubly terminated 75 $\Omega$ load, $R_{SET} = 530 \Omega$ . |

|         |                  | The relationship between R <sub>SET</sub> and the full-scale output current on IOG (assuming I <sub>SYNC</sub> is connected to IOG) is given by                                                                                                                                                              |

|         |                  | $R_{SET}(\Omega) = 11,445 \times V_{REF}(V)/IOG \text{ (mA)}$                                                                                                                                                                                                                                                |

|         |                  | The relationship between R <sub>SET</sub> and the full-scale output current on IOR, IOG, and IOB is given by                                                                                                                                                                                                 |

|         |                  | $IOG (mA) = 11,445 \times V_{REF} (V)/R_{SET} (\Omega) (\overline{SYNC} \text{ being asserted})$                                                                                                                                                                                                             |

|         |                  | $IOR$ , $IOB$ (mA) = 7989.6 $\times V_{REF}$ (V)/ $R_{SET}$ ( $\Omega$ )                                                                                                                                                                                                                                     |

|         |                  | The equation for IOG is the same as that for IOR and IOB when SYNC is not being used, that is, SYNC is tied permanently low.                                                                                                                                                                                 |

| 38      | PSAVE            | Power Save Control Pin. Reduced power consumption is available on the ADV7123-EP when this pin is active.                                                                                                                                                                                                    |

| EP      | Exposed Pad      | The exposed paddle on the underside of the package must be soldered to the ground plane to increase the reliability of the solder joints and to maximize the thermal capability of the package.                                                                                                              |

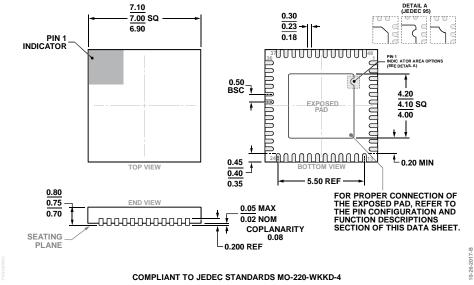

## **OUTLINE DIMENSIONS**

Figure 4. 48-Lead Lead Frame Chip Scale Package [LFCSP] 7 mm × 7 mm Body and 0.75 mm Package Height (CP-48-5) Dimensions shown in millimeters

**ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature Range | Speed Option | Package Description | Package Option |

|-----------------------|-------------------|--------------|---------------------|----------------|

| ADV7123SCP170EP-RL    | −55°C to +105°C   | 170 MHz      | 48-Lead LFCSP       | CP-48-5        |

| ADV7123SCP170ZEPRL    | −55°C to +105°C   | 170 MHz      | 48-Lead LFCSP       | CP-48-5        |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

$<sup>^{\</sup>rm 2}$  Available in 3.3 V version only.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## **Analog Devices Inc.:**

<u>ADV7123JSTZ240 ADV7123JSTZ240-RL ADV7123JSTZ330 ADV7123KSTZ140 ADV7123KSTZ140-RL ADV7123KSTZ50 ADV7123SCP170ZEPRL</u>