# 46 dBm (40 W), 0.9 GHz to 1.6 GHz, GaN Power Amplifier

### **Data Sheet**

#### FEATURES

Output power with  $P_{IN} = 19$  dBm: 46 dBm typical Small signal gain: 34.5 dB typical at 0.9 GHz to 1.4 GHz Power gain with  $P_{IN} = 19$  dBm: 27 dB typical Bandwidth: 0.9 GHz to 1.6 GHz PAE with  $P_{IN} = 19$  dBm: 60% typical at 0.9 GHz to 1.4 GHz Supply voltage:  $V_{DD} = 50$  V at 400 mA on 10% duty cycle 32-Lead, 5 mm × 5 mm, LFSCP\_CAV package

#### **APPLICATIONS**

Weather radar Marine radar Military radar

# ADPA1105

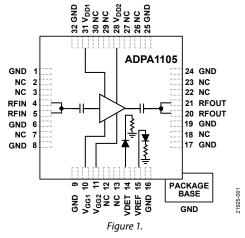

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The ADPA1105 is a gallium nitride (GaN), broadband power amplifier that delivers 46 dBm (40 W) with 60% typical power added efficiency (PAE) across a bandwidth of 0.9 GHz to 1.4 GHz. The ADPA1105 provides  $\pm$ 0.5 dB gain flatness across a bandwidth of 0.9 GHz to 1.4 GHz.

The ADPA1105 is ideal for pulsed applications such as wireless infrastructure, radar, public mobile radio, and general-purpose amplifications.

The ADPA1105 comes in a 32-lead, lead frame chip scale package, premolded cavity (LFCSP\_CAV).

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                              | 1 |

|---------------------------------------|---|

| Applications                          | 1 |

| Functional Block Diagram              | 1 |

| General Description                   | 1 |

| Revision History                      | 2 |

| Specifications                        | 3 |

| Electrical Specifications             | 3 |

| Absolute Maximum Ratings              | 4 |

| Thermal Resistance                    | 4 |

| Electrostatic Discharge (ESD) Ratings | 4 |

| ESD Caution                           | 4 |

| Pin Configuration and Function Descriptions | .5 |

|---------------------------------------------|----|

| Interface Schematics                        | .5 |

| Typical Performance Characteristics         | .6 |

| Theory of Operation 1                       | 3  |

| Applications Information 1                  | 4  |

| Basic Connections1                          | 4  |

| Thermal Management 1                        | 5  |

| Outline Dimensions1                         | 6  |

| Ordering Guide 1                            | 6  |

#### **REVISION HISTORY**

10/2020—Revision 0: Initial Version

### **SPECIFICATIONS**

#### **ELECTRICAL SPECIFICATIONS**

$T_A = 25^{\circ}$ C, supply voltage ( $V_{DD}$ ) = 50 V,  $I_{DQ}$  = 400 mA, pulse width = 100  $\mu$ s, 10% duty cycle, and frequency range = 0.9 GHz to 1.4 GHz, unless otherwise noted.

#### Table 1.

| Parameter                               | Symbol          | Min | Тур  | Max | Unit | Test Conditions/Comments                                                                                                                          |

|-----------------------------------------|-----------------|-----|------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| FREQUENCY RANGE                         |                 | 0.9 |      | 1.4 | GHz  |                                                                                                                                                   |

| GAIN                                    |                 |     |      |     |      |                                                                                                                                                   |

| Small Signal Gain                       |                 | 32  | 34.5 |     | dB   |                                                                                                                                                   |

| Gain Flatness                           |                 |     | ±0.5 |     | dB   |                                                                                                                                                   |

| RETURN LOSS                             |                 |     |      |     |      |                                                                                                                                                   |

| Input                                   |                 |     | 16   |     | dB   |                                                                                                                                                   |

| Output                                  |                 |     | 9    |     | dB   |                                                                                                                                                   |

| POWER                                   |                 |     |      |     |      |                                                                                                                                                   |

| Output Power (Pout)                     |                 |     |      |     |      |                                                                                                                                                   |

| Input Power (P <sub>IN</sub> ) = 19 dBm |                 | 44  | 46   |     | dBm  |                                                                                                                                                   |

| Power Gain                              |                 |     |      |     |      |                                                                                                                                                   |

| $P_{IN} = 19 \text{ dBm}$               |                 | 25  | 27   |     | dB   |                                                                                                                                                   |

| PAE                                     |                 |     |      |     |      |                                                                                                                                                   |

| $P_{IN} = 19 \text{ dBm}$               |                 |     | 60   |     | %    |                                                                                                                                                   |

| TARGET QUIESCENT CURRENT                | I <sub>DQ</sub> |     | 400  |     | mA   | Adjust the gate control voltage (V <sub>GG1</sub> , V <sub>GG2</sub> ) to be between $-4$ V and 0 V to achieve an $I_{DQ}$ = 400 mA typical value |

$T_A = 25^{\circ}$ C,  $V_{DD} = 50$  V,  $I_{DQ} = 400$  mA, pulse width = 100  $\mu$ s, 10% duty cycle, and frequency range = 1.4 GHz to 1.6 GHz, unless otherwise noted.

| Parameter                 | Symbol          | Min  | Тур  | Max | Unit | Test Conditions/Comments                                                                                                             |

|---------------------------|-----------------|------|------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------|

| FREQUENCY RANGE           |                 | 1.4  |      | 1.6 | GHz  |                                                                                                                                      |

| GAIN                      |                 |      |      |     |      |                                                                                                                                      |

| Small Signal Gain         |                 | 30.5 | 32.5 |     | dB   |                                                                                                                                      |

| Gain Flatness             |                 |      | ±0.9 |     | dB   |                                                                                                                                      |

| RETURN LOSS               |                 |      |      |     |      |                                                                                                                                      |

| Input                     |                 |      | 11   |     | dB   |                                                                                                                                      |

| Output                    |                 |      | 14   |     | dB   |                                                                                                                                      |

| POWER                     |                 |      |      |     |      |                                                                                                                                      |

| Роит                      |                 |      |      |     |      |                                                                                                                                      |

| $P_{IN} = 19 \text{ dBm}$ |                 | 44   | 46   |     | dBm  |                                                                                                                                      |

| Power Gain                |                 |      |      |     |      |                                                                                                                                      |

| $P_{IN} = 19 \text{ dBm}$ |                 | 25   | 27   |     | dB   |                                                                                                                                      |

| PAE                       |                 |      |      |     |      |                                                                                                                                      |

| $P_{IN} = 19 \text{ dBm}$ |                 |      | 57   |     | %    |                                                                                                                                      |

| TARGET QUIESCENT CURRENT  | I <sub>DQ</sub> |      | 400  |     | mA   | Adjust the gate control voltage ( $V_{GG1}$ , $V_{GG2}$ ) to be between $-4$ V and 0 V to achieve an $I_{DQ} = 400$ mA typical value |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 1                                                                                                                                                                                            |                    |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|--|--|

| Parameter                                                                                                                                                                                    | Rating             |  |  |  |  |  |  |

| Drain Bias Voltage (V <sub>DD1</sub> , V <sub>DD2</sub> )                                                                                                                                    | 55 V dc            |  |  |  |  |  |  |

| Gate Bias Voltage (V <sub>GG1</sub> , V <sub>GG2</sub> )                                                                                                                                     | –5 V to 0 V dc     |  |  |  |  |  |  |

| Radio Frequency Input Power (RFIN)                                                                                                                                                           | 30 dBm             |  |  |  |  |  |  |

| Maximum Drain Bias                                                                                                                                                                           |                    |  |  |  |  |  |  |

| Pulse Width                                                                                                                                                                                  | 500 µs             |  |  |  |  |  |  |

| Duty Cycle                                                                                                                                                                                   | 20%                |  |  |  |  |  |  |

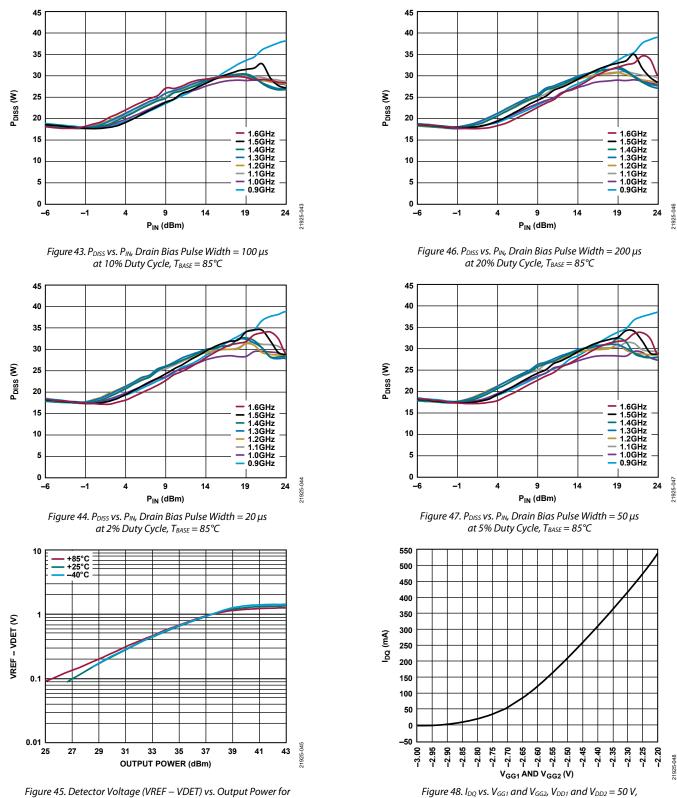

| Drain Bias Pulse Width = $100 \mu s$ at $10\%$ Duty Cycle                                                                                                                                    |                    |  |  |  |  |  |  |

| Maximum Pulsed Power Dissipation (P <sub>DISS</sub> ),<br>Base Temperature (T <sub>BASE</sub> ) = 85°C, Derate<br>473 mW/°C Above 85°C                                                       | 54.5 W             |  |  |  |  |  |  |

| Nominal Pulsed Peak Channel Temperature,<br>$P_{IN} = 19 \text{ dBm}$ , $P_{DISS} = 33.6 \text{ W}$ at 0.9 GHz                                                                               | 155.9°C            |  |  |  |  |  |  |

| Drain Bias Pulse Width = 200 μs at 20% Duty Cycle<br>Maximum Pulsed Power Dissipation (P <sub>DISS</sub> )<br>(Base Temperature (T <sub>BASE</sub> ) = 85°C, Derate<br>355 mW/°C Above 85°C) | 40.8 W             |  |  |  |  |  |  |

| Nominal Pulsed Peak Channel Temperature $P_{IN} = 19 \text{ dBm}, P_{DISS} = 33.6 \text{ W}$ at 0.9 GHz <sup>1</sup>                                                                         | 179.7°C            |  |  |  |  |  |  |

| Maximum Channel Temperature                                                                                                                                                                  | 200°C              |  |  |  |  |  |  |

| Maximum Peak Reflow Temperature                                                                                                                                                              | 260°C              |  |  |  |  |  |  |

| Storage Temperature Range                                                                                                                                                                    | −60°C to<br>+125°C |  |  |  |  |  |  |

| Operating Temperature Range                                                                                                                                                                  | –40°C to +85°C     |  |  |  |  |  |  |

<sup>1</sup> Worst case frequency for P<sub>DISS</sub>.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to the PCB thermal design is required.

$\theta_{JC}$  is the junction to case thermal resistance (°C/W) of the device.

#### Table 4. Thermal Resistance

| Package Type <sup>1</sup>                         | θις  | Unit |

|---------------------------------------------------|------|------|

| CG-32-2                                           |      |      |

| Drain Bias Pulse Width = 100 $\mu$ s <sup>2</sup> | 2.11 | °C/W |

| Drain Bias Pulse Width = 200 $\mu$ s <sup>3</sup> | 2.82 | °C/W |

<sup>1</sup> The  $\theta_{JC}$  value was determined by measuring  $\theta_{JC}$  under the following conditions: the heat transfer is solely because of the thermal conduction from the channel through the ground pad to the PCB, and the ground pad is held constant at the operating temperature of 85°C. <sup>2</sup> At 10% duty cycle.

<sup>3</sup> At 20% duty cycle.

#### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

#### ESD Ratings for ADPA1105

#### Table 5. ADPA1105, 32-Lead LFCSP\_CAV

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 250                     | 1A    |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

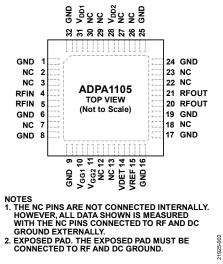

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### Table 6. Pin Function Descriptions

| Pin No.                                        | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 8, 9, 16, 17, 19,<br>24, 25, 32          | GND              | The GND pins must be connected to RF and dc ground. See Figure 6 for the interface schematic.                                                                                                                                                                                                                                     |

| 2, 3, 7, 12, 13, 18, 22,<br>23, 26, 27, 29, 30 | NC               | The NC pins are not connected internally. However, all data shown is measured with the NC pins connected to RF and dc ground externally.                                                                                                                                                                                          |

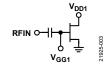

| 4, 5                                           | RFIN             | RF Input. The RFIN pins are ac-coupled and are matched to 50 $\Omega$ . See Figure 3 for the interface schematic.                                                                                                                                                                                                                 |

| 10                                             | V <sub>GG1</sub> | Gate Control, First Stage Gate Bias. See Figure 3 for the interface schematic.                                                                                                                                                                                                                                                    |

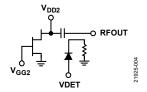

| 11                                             | V <sub>GG2</sub> | Gate Control, Second Stage Gate Bias. See Figure 4 for the interface schematic.                                                                                                                                                                                                                                                   |

| 14                                             | VDET             | Detector Diode to Measure RF Output Power. Output power detection via VDET requires the application of a dc bias voltage through an external series resistor. Used in combination with the VREF pin, the difference in voltage (VREF – VDET) is a temperature compensated dc voltage that is proportional to the RF output power. |

| 15                                             | VREF             | Reference Diode for Temperature Compensation of VDET RF Output Power Measurements. VREF requires the application of a dc bias voltage through an external series resistor.                                                                                                                                                        |

| 20, 21                                         | RFOUT            | RF Output. The RFOUT pins are ac-coupled and are matched to 50 $\Omega$ . See Figure 4 for the interface schematic.                                                                                                                                                                                                               |

| 28                                             | V <sub>DD2</sub> | Amplifier Power Supply Voltage, Second Stage Drain Bias. See Figure 4 for the interface schematic.                                                                                                                                                                                                                                |

| 31                                             | V <sub>DD1</sub> | Amplifier Power Supply Voltage, First Stage Drain Bias. See Figure 3 for the interface schematic.                                                                                                                                                                                                                                 |

|                                                | EPAD             | Exposed Pad. The exposed pad must be connected to RF and dc ground.                                                                                                                                                                                                                                                               |

#### **INTERFACE SCHEMATICS**

Figure 3. RFIN,  $V_{GG1}$ , and  $V_{DD1}$  Interface

Figure 4. RFOUT, V<sub>GG2</sub>, V<sub>DD2</sub>, and VDET Interface

Figure 5. VREF Interface

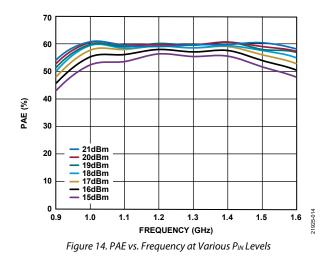

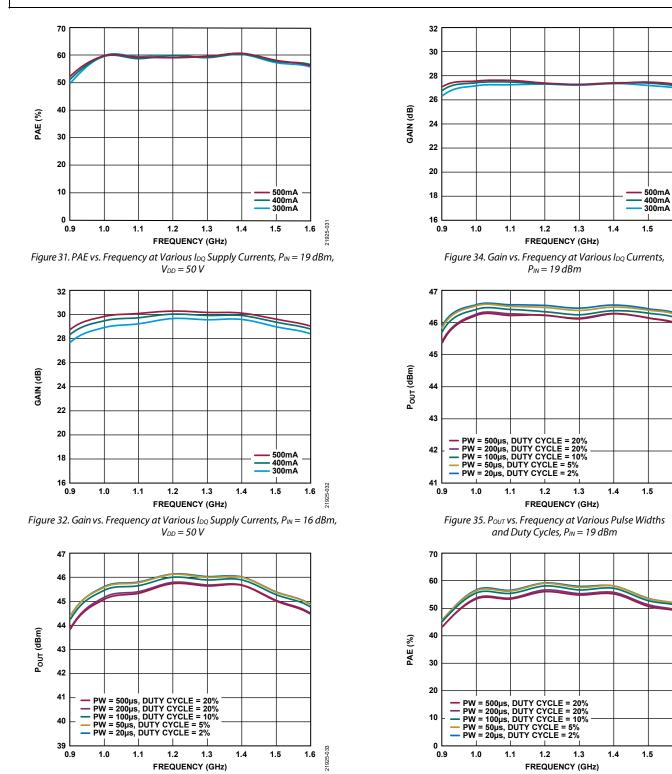

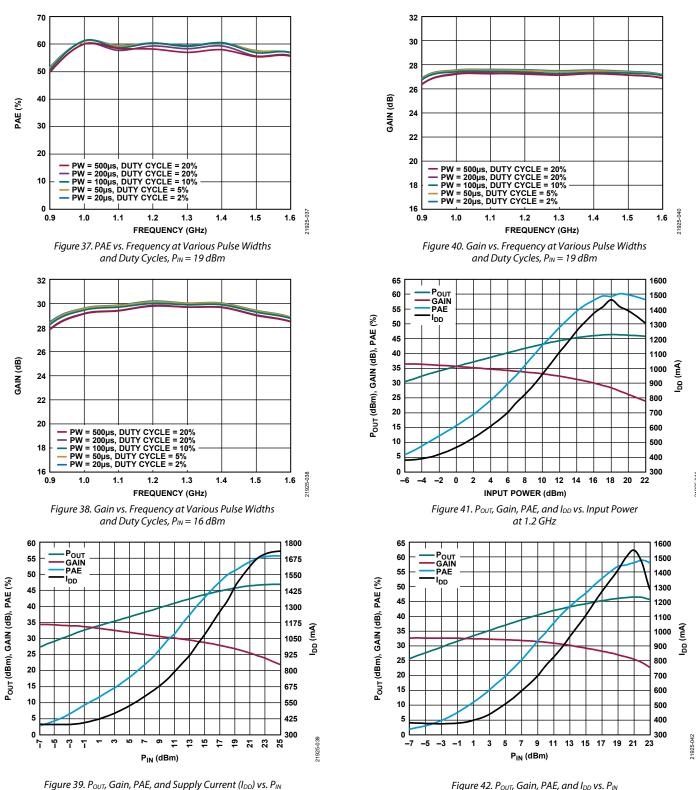

### **TYPICAL PERFORMANCE CHARACTERISTICS**

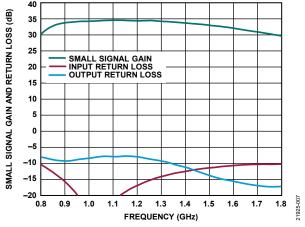

Figure 7. Small Signal Gain and Return Loss vs. Frequency

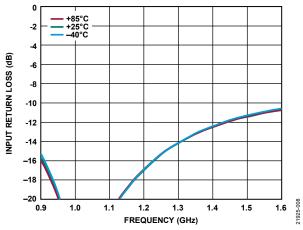

Figure 8. Input Return Loss vs. Frequency at Various Temperatures

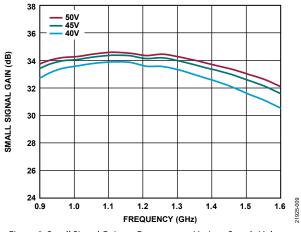

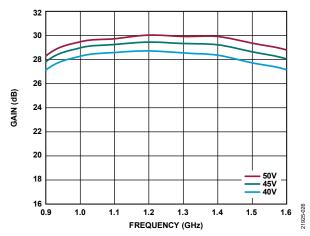

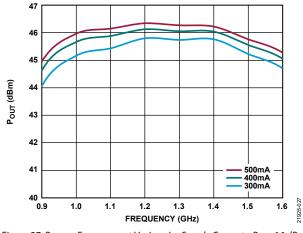

Figure 9. Small Signal Gain vs. Frequency at Various Supply Voltages,  $I_{DQ} = 400 \text{ mA}$

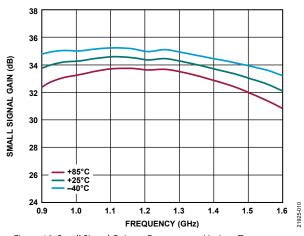

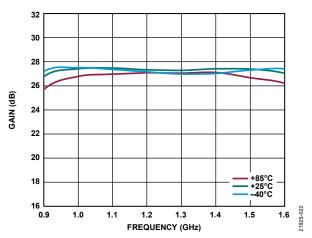

Figure 10. Small Signal Gain vs. Frequency at Various Temperatures

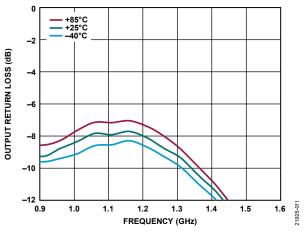

Figure 11. Output Return Loss vs. Frequency at Various Temperatures

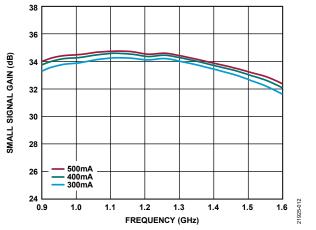

Figure 12. Small Signal Gain vs. Frequency at Various  $I_{DQ}$ ,  $V_{DD1}$  and  $V_{DD2} = 50 V$

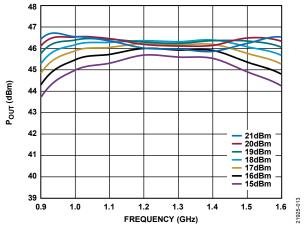

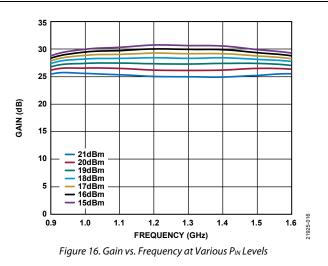

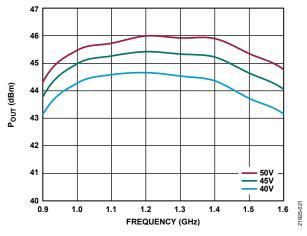

Figure 13. Output Power ( $P_{OUT}$ ) vs. Frequency at Various  $P_{IN}$  Levels

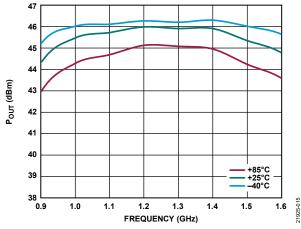

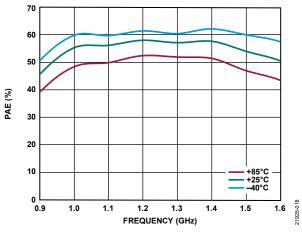

Figure 15.  $P_{OUT}$  vs. Frequency at Various Temperatures,  $P_{IN} = 16 \text{ dBm}$

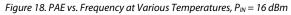

Figure 19. PAE vs. Frequency at Various Temperatures,  $P_{IN} = 19 \, dBm$

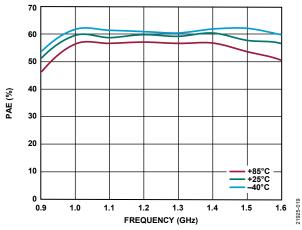

Figure 20. Gain vs. Frequency at Various Temperatures, P<sub>IN</sub> = 16 dBm

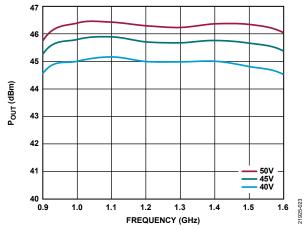

Figure 21.  $P_{OUT}$  vs. Frequency at Various Supply Voltages,  $P_{IN} = 16$  dBm,  $I_{DQ} = 400$  mA

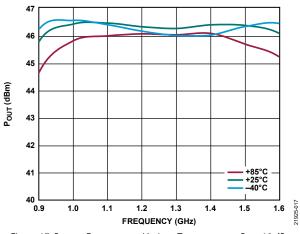

Figure 22. Gain vs. Frequency at Various Temperatures,  $P_{IN} = 19 \, dBm$

Figure 23.  $P_{OUT}$  vs. Frequency at Various Supply Voltages,  $P_{IN} = 19$  dBm,  $I_{DQ} = 400$  mA

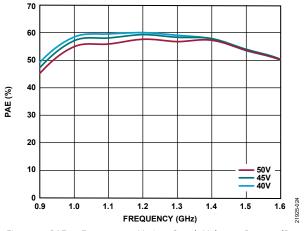

Figure 24. PAE vs. Frequency at Various Supply Voltages,  $P_{IN} = 16 \text{ dBm}$ ,  $I_{DQ} = 400 \text{ mA}$

70 60 50 40 PAE (%) 30 20 50V 45V 40V 10 0 21925-025 0.9 1.0 1.1 1.2 1.3 1.4 1.5 1.6 FREQUENCY (GHz)

Figure 25. PAE vs. Frequency at Various Supply Voltages,  $P_{IN} = 19 \, dBm$ ,  $I_{DQ} = 400 \, mA$

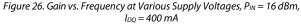

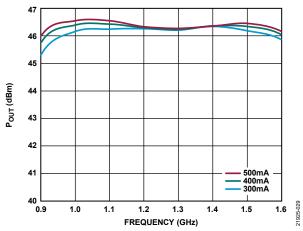

Figure 27.  $P_{OUT}$  vs. Frequency at Various  $I_{DQ}$  Supply Currents,  $P_{IN} = 16$  dBm,  $V_{DD} = 50$  V

Figure 28. Gain vs. Frequency at Various Supply Voltages,  $P_{\rm IN} = 19$  dBm,  $I_{\rm DQ} = 400$  mA

Figure 29.  $P_{OUT}$  vs. Frequency at Various  $I_{DQ}$  Supply Currents,  $P_{IN} = 19$  dBm,  $V_{DD} = 50$  V

Figure 30. PAE vs. Frequency at Various  $I_{DQ}$  Supply Currents,  $P_{\rm IN}=16$  dBm,  $V_{\rm DD}=50$  V

21925-034

21925-035

21925-036

1.6

1.6

1.6

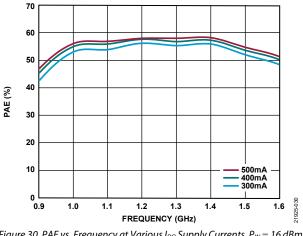

Figure 36. PAE vs. Frequency at Various Pulse Widths and Duty Cycles, P<sub>IN</sub> = 16 dBm

Figure 33.  $P_{OUT}$  vs. Frequency at Various Pulse Widths (PW) and Duty Cycles,  $P_{IN} = 16 \text{ dBm}$

ADPA1105

21925-041

Figure 42. P<sub>OUT</sub>, Gain, PAE, and I<sub>DD</sub> vs. P<sub>IN</sub> at 1.6 GHz

at 0.9 GHz

Figure 48.  $I_{DQ}$  vs.  $V_{GG1}$  and  $V_{GG2}$ ,  $V_{DD1}$  and  $V_{DD2} = 50$  V, Representative of a Typical Device

Various Temperatures at 1.2 GHz

### THEORY OF OPERATION

The ADPA1105 is a GaN power amplifier that delivers 46 dBm (40 W) of pulsed power. The device consists of two cascaded gain stages. A simplified view of this architecture is shown in the basic block diagram in Figure 49.

The ADPA1105 has single-ended RFIN and RFOUT ports that are dc blocked. The impedances of these ports are nominally 50  $\Omega$  over the 0.9 GHz to 1.6 GHz operating frequency range. Consequently, the ADPA1105 can be directly inserted into a 50  $\Omega$  system without the need for external impedance matching components or ac coupling capacitors.

The pulsed bias voltages applied to the  $V_{DD1}$  and  $V_{DD2}$  pins bias the drains of the first and second gain stages, respectively (a single common supply voltage must be used). The negative dc voltages applied to the  $V_{GG1}$  and  $V_{GG2}$  pins bias the gates of the first and second gain stages, respectively, to allow control of the drain currents for each stage (a single common gate voltage must be used). The recommended dc biasing results in a typical pulsed RF output power and PAE of 46 dBm and 60%, respectively, at 1.5 GHz when the input power is 19 dBm.

A portion of the RF output signal is directionally coupled to a diode to detect the RF output power. When the diode is dc biased, the diode rectifies the RF power and makes the RF power available for measurement as a dc voltage at the VDET pin. A symmetrical diode circuit that is not coupled to the RF output, which contains a dc voltage output at the VREF pin, is referenced to accomplish temperature compensation. The difference of VREF – VDET provides a temperature compensated signal that is proportional to the RF output.

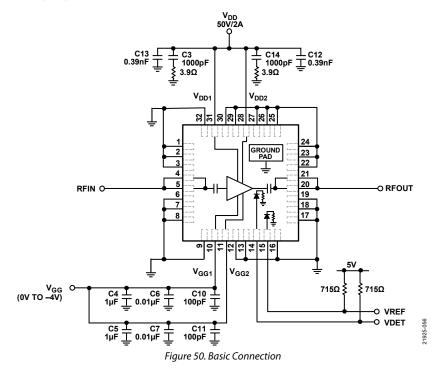

### APPLICATIONS INFORMATION BASIC CONNECTIONS

The basic connections for operating the ADPA1105 are shown in Figure 50. Apply a power supply voltage between 20 V and 50 V to the V<sub>DD1</sub> and V<sub>DD2</sub> pins. Decouple each pin with the capacitor values shown in Figure 50. Place 3.9  $\Omega$  resistors in series with the two 1000 pF power supply decoupling capacitors connected to Pin 28 and Pin 31 (V<sub>DD2</sub> and V<sub>DD1</sub>). Tie together the two gate voltage pins, V<sub>GG1</sub> and V<sub>GG2</sub>, and drive the pins as shown in Figure 50. Pin 2, Pin 3, Pin 7, Pin 12, Pin 13, Pin 18, Pin 22, Pin 23, Pin 26, Pin 27, Pin 29, and Pin 30 are designated as no connect (NC) pins. Although these pins are not internally connected, the pins were all connected to ground during the characterization of the device and provide some additional thermal relief.

The decoupling capacitors on the  $V_{DD1}$ ,  $V_{DD2}$ ,  $V_{GG1}$ , and  $V_{GG2}$ lines represent the configuration that was used to characterize and qualify the ADPA1105. The user can reduce the number of capacitors, but the result varies from system to system. General guidance is to first remove or combine the largest capacitors that are farthest from the device.

External bias is provided to the on-chip RF detection circuit via two 715  $\Omega$  resistors that are pulled up to 5 V, which results in a current draw of approximately 12 mA. An operation amplifier configured as a differential amplifier can be used to subtract VDET from VREF to yield a temperature compensated voltage that is proportional to the RF output power. Apply a voltage between 0 V and -4 V to the V<sub>GG1</sub> and V<sub>GG2</sub> lines to set the bias level and drain current. Because the ADPA1105 cannot support continuous operation, the device must be operated in pulsed mode by pulsing either the gate voltage or the drain voltage.

In gate pulsed mode,  $V_{DD}$  is held at a fixed level (nominally +50 V) while the gate voltage is pulsed between -4 V (off) and approximately -2.3 V (on). The exact on level can be adjusted to achieve the desired quiescent drain current.

In drain pulsed mode, the  $V_{DD}$  voltage is pulsed on and off while the gate voltage is held at a fixed negative level between 0 V and -4 V. Because high currents and voltages are being switched on and off, a metal-oxide semiconductor field effect transistor (MOSFET) and a MOSFET switch driver are required in the circuit. Large capacitors are also required, which act as local reservoirs of charge and help provide the drain current required by the ADPA1105 while maintaining a steady drain voltage during the on time of the pulse.

The ADPA1105-EVALZ evaluation board package includes a plugin pulser board that contains the required circuitry to implement drain pulsed mode. See the ADPA1105-EVALZ for more information.

#### THERMAL MANAGEMENT

Proper thermal management is critical to achieve the specified performance and rated operating life. Pulsed biasing is required to limit the average power dissipated and maintain a safe channel temperature. The channel (or die) temperature correlates closely with the mean time to failure.

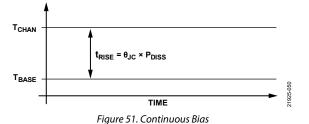

Consider a continuous bias case (see Figure 51). When bias is applied, the channel temperature ( $T_{CHAN}$ ) of the device rises through a turn on transient interval and eventually settles to a steady state value. Calculate the  $\theta_{JC}$  thermal resistance of the device as the rise in  $T_{CHAN}$  above the starting  $T_{BASE}$  divided by the total device  $P_{DISS}$  with the following equation:

$$\theta_{JC} = t_{RISE} / P_{DISS} \tag{1}$$

where:

$t_{RISE}$  is the peak rise in the T<sub>CHAN</sub> of the device above the T<sub>BASE</sub> (°C).  $P_{DISS}$  is the power dissipation (W) of the device.

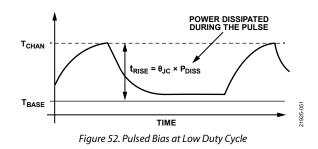

Next, consider a pulsed bias case at low duty cycle (see Figure 52). When bias is applied, the  $T_{CHAN}$  of the device can be described as a series of exponentially rising and decaying pulses. The peak channel temperature reached during consecutive pulses increases during the turn on transient interval, and eventually settles to a steady state condition where peak channel temperatures from pulse to pulse stabilize.

Transient thermal measurements were performed on the ADPA1105 amplifier at several different bias pulse widths and duty cycles to obtain the thermal resistance values listed in Table 7.

| Pulse            |                |                        |

|------------------|----------------|------------------------|

| Pulse Width (µs) | Duty Cycle (%) | θ <sub>JC</sub> (°C/W) |

| 100              | 10             | 2.11                   |

| 200              | 20             | 2.82                   |

| 300              | 30             | 3.54                   |

Narrower pulse widths and/or lower duty cycles can result in greater reliability.

The ADPA1105 amplifier is designed for low duty cycle pulsed applications. However, there can be brief periods of time when the device operates (perhaps accidently) under continuous bias conditions. The thermal resistance increases to  $6.5^{\circ}$ C/W under these conditions. Even at the nominal quiescent bias  $V_{DD1}$  and  $V_{DD2} = 50$  V and  $I_{DD} = 0.4$  A), the 20 W power dissipation results in a 130°C channel temperature rise above the base temperature. Use extreme caution in this case to ensure that the device does not exceed the device maximum reliable channel temperature of 200°C.

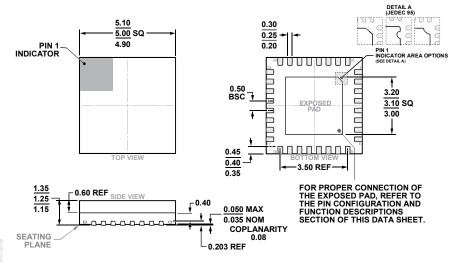

### **OUTLINE DIMENSIONS**

Figure 53. 32-Lead Lead frame Chip Scale Package, Premolded Cavity [LFCSP\_CAV] 5 mm × 5 mm Body and 1.25 mm Package Height (CG-32-2) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1, 2, 3</sup> | Temperature       | MSL Rating <sup>4</sup> | Package Description                                                    | Package Option |

|--------------------------|-------------------|-------------------------|------------------------------------------------------------------------|----------------|

| ADPA1105ACGZN            | –40°C to<br>+85°C | MSL3                    | 32-Lead Lead Frame Chip Scale Package, Premolded Cavity [LFCSP_CAV]    | CG-32-2        |

| ADPA1105ACGZN-R7         | –40°C to<br>+85°C | MSL3                    | 32-Lead Lead Frame Chip Scale Package, Premolded Cavity<br>[LFCSP_CAV] | CG-32-2        |

| ADPA1105-EVALZ           |                   |                         | Evaluation Board                                                       |                |

<sup>1</sup> All models are RoHS compliant parts.

<sup>2</sup> The lead finish of the ADPA1105ACGZN and the ADPA1105ACGZN-R7 is nickel palladium gold (NiPdAu).

<sup>3</sup> When ordering the evaluation board, use the reference model number ADPA1105-EVALZ.

<sup>4</sup> See the Absolute Maximum Ratings section for more information.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

ADPA1105ACGZN ADPA1105ACGZN-R7 ADPA1105-EVALZ