# 5.7 kV rms/1.5 kV rms, Quad-Channel LVDS 2.5 Gigabit Isolators

### **FEATURES**

- ▶ 5.7 kV rms and 1.5 kV rms LVDS isolators

- ▶ Complies with TIA/EIA-644-A LVDS signal levels

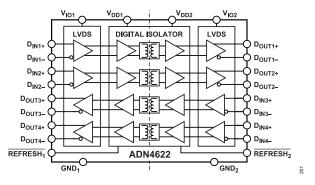

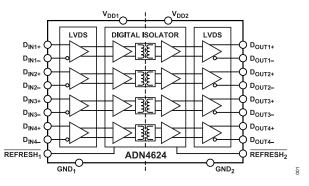

- ▶ Quad-channel configuration (ADN4622: 2 + 2, ADN4624: 4 + 0)

- ▶ Any data rate up to 2.5 Gbps switching with low jitter

- ▶ 10 Gbps total bandwidth across four channels

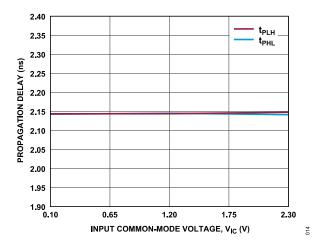

- ▶ 2.15 ns typical propagation delay

- ▶ Typical jitter: 0.82 ps rms random, 40 ps total peak

- ▶ Lower power 1.8 V supplies

- ▶ ±8 kV IEC 61000-4-2 ESD protection across isolation barrier

- ▶ High common-mode transient immunity: 100 kV/µs typical

- ► Safety and regulatory approvals (28-lead SOIC W FP package)

- ▶ UL (pending): 5700 V rms for 1 minute per UL 1577

- CSA Component Acceptance Notice 5A (pending)

- VDE certificate of conformity (pending)

- ▶ DIN V VDE V 0884-11 (VDE V 0884-11):2017-01

- ► V<sub>IORM</sub> = 849 V<sub>PEAK</sub> (working voltage)

- ▶ Enable or disable refresh (low-speed output correctness check)

- ▶ Operating temperature range: -40°C to +125°C

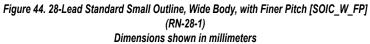

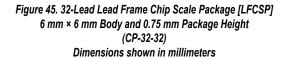

- 28-lead, wide-body, finer pitch SOIC\_W\_FP package with 8.3 mm creepage and clearance or 6 mm × 6 mm LFCSP package with 1.27 mm creepage and clearance

## **APPLICATIONS**

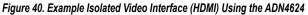

- Isolated video and imaging data

- Analog front-end isolation

- Data plane isolation

- Isolated high speed clock and data links

- Multi-gigabit SERDES

- Board-to-board optical replacement (for example, short reach fiber)

### FUNCTIONAL BLOCK DIAGRAMS

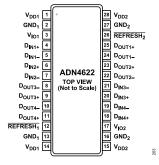

Figure 1. ADN4622 Functional Block Diagram with Two Forward and Two Reverse Channels

#### **GENERAL DESCRIPTION**

The ADN4622/ADN4624<sup>1</sup> are quad-channel, signal isolated, lowvoltage differential signaling (LVDS) buffers that operate at up to 2.5 Gbps with very low jitter. The devices integrate Analog Devices, Inc., *i*Coupler<sup>®</sup> technology, enhanced for high-speed operation to provide drop-in galvanic isolation of LVDS signal chains. AC coupling and/or level shifting to the LVDS receivers and from the LVDS drivers allows isolation of other high-speed signals such as current-mode logic (CML).

The ADN4622/ADN4624 include a refresh mechanism to monitor the input and output states and ensure they remain the same in the absence of data transitions. For lower power consumption and high-speed operation with low jitter, the LVDS and isolator circuits rely on 1.8 V supplies. The ADN4622/ADN4624 are fully specified over a wide industrial temperature range and are available in a 28-lead, wide-body, finer pitch SOIC\_W\_FP package with 8.3 mm creepage and clearance (for 5.7 kV rms or 8 kV<sub>PEAK</sub> surge and impulse voltages and reinforced insulation at AC mains voltages) or 6 mm × 6 mm LFCSP package with 1.27 mm creepage and clearance (for basic/functional isolation).

<sup>1</sup> Protected by U.S. Patents 7,075,329; 9,941,565; and 10,205,442. Other patents are pending.

Rev. B

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                     | 1    |

|----------------------------------------------|------|

| Applications                                 | 1    |

| Functional Block Diagrams                    | 1    |

| General Description                          | 1    |

| Specifications                               | 4    |

| Receiver Input Threshold Test Voltages       | 5    |

| Timing Specifications                        | 5    |

| Insulation and Safety Related Specifications | 6    |

| Package Characteristics                      | 7    |

| Regulatory Information                       | 7    |

| DIN V VDE V 0884-11 (VDE V 0884-11)          |      |

| Insulation Characteristics (Pending)         | 8    |

| Recommended Operating Conditions             | 9    |

| Absolute Maximum Ratings                     | . 10 |

| Thermal Resistance                           | 10   |

| Electrostatic Discharge (ESD) Ratings        | . 11 |

|                                              |      |

| ESD Caution                                  | 11 |

|----------------------------------------------|----|

| Pin Configurations and Function Descriptions | 12 |

| Typical Performance Characteristics          | 15 |

| Test Circuits and Switching Characteristics  | 20 |

| Theory of Operation                          | 21 |

| Isolation and Refresh                        | 21 |

| Truth Table                                  | 21 |

| Applications Information                     | 22 |

| PCB Layout                                   | 22 |

| Application Examples                         | 22 |

| Magnetic Field Immunity                      | 23 |

| Insulation Lifetime                          | 24 |

| Outline Dimensions                           | 26 |

| Ordering Guide                               | 26 |

| Evaluation Boards                            | 27 |

|                                              |    |

## **REVISION HISTORY**

## 10/2022—Rev. A to Rev. B

| Added ADN4622 and Figure 1; Renumbered Sequentially                       | 1    |

|---------------------------------------------------------------------------|------|

| Changes to Features Section and Figure 2 Caption                          |      |

| Changes to Specifications Section and Table 1 Section                     |      |

| Changes to Channel to Channel Parameter, Table 3                          | 5    |

| Changes to CSA (Pending), Standard Certification/Approval Column, Table 7 | 7    |

| Changes to Table 11                                                       | 9    |

| Changes to Table 11<br>Added Table 12                                     | . 10 |

| Added Figure 5 and Table 18; Renumbered Sequentially                      | . 12 |

| Changes to Figure 6 Caption and Table 19                                  | . 13 |

| Changes to Figure 7 Caption and Table 20                                  | . 14 |

| Added Figure 8, Figure 9, Figure 11, and Figure 12                        | . 15 |

| Added Figure 14 and Figure 15                                             | . 16 |

| Changes to PCB Layout Section and Application Examples Section            | . 22 |

| Changes to Surface Tracking Section                                       | 24   |

| Changes to Calculation and Use of Parameters Example Section              | 25   |

| Changes to Ordering Guide                                                 | .26  |

| Changes to Evaluation Boards                                              | . 27 |

#### 10/2021-Rev. 0 to Rev. A

| Added 32-Lead LFCSP                                                                  | 1  |

|--------------------------------------------------------------------------------------|----|

| Changes to Features Section and General Description Section                          | 1  |

| Changes to Channel to Channel Parameter and Additive Phase Jitter Parameter, Table 3 | 5  |

| Added Table 5; Renumbered Sequentially                                               | 6  |

| Changes to Table 6                                                                   | 7  |

| Added Table 8                                                                        | 7  |

| Change to Figure 2 Caption                                                           | 8  |

| Added Table 10 and Figure 3; Renumbered Sequentially                                 | 9  |

| Added Table 14                                                                       | 10 |

| Changes to Table 15                                                                  | 10 |

|                                                                                      |    |

## TABLE OF CONTENTS

| Added Table 17                 | 11 |

|--------------------------------|----|

| Added Figure 5 and Table 19    |    |

| Jpdated Outline Dimensions     | 26 |

| ,<br>Changes to Ordering Guide | 26 |

|                                |    |

## 4/2021—Revision 0: Initial Version

For all minimum and maximum specifications,  $V_{DD1} = 1.7 \text{ V}$  to 1.9 V,  $V_{DD2} = 1.7 \text{ V}$  to 1.9 V,  $V_{IO1} = 3 \text{ V}$  to 3.6 V,  $V_{IO2} = 3 \text{ V}$  to 3.6 V, and  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ , unless otherwise noted. For all typical specifications,  $V_{DD1} = V_{DD2} = 1.8 \text{ V}$ ,  $V_{IO1} = V_{IO2} = 3.3 \text{ V}$ , and  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted. For all specifications, REFRESH<sub>1</sub> = GND<sub>1</sub> and REFRESH<sub>2</sub> = GND<sub>2</sub>, unless otherwise noted.

| Parameter                                      | Symbol                               | Min                   | Тур  | Мах                       | Unit  | Test Conditions/Comments                                                                                                        |

|------------------------------------------------|--------------------------------------|-----------------------|------|---------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| INPUTS (RECEIVERS)                             |                                      |                       |      |                           |       |                                                                                                                                 |

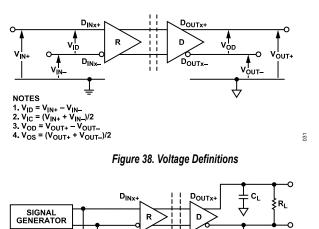

| Input Threshold                                |                                      |                       |      |                           |       | See Figure 38 and Table 2                                                                                                       |

| High                                           | V <sub>TH</sub>                      |                       |      | 100                       | mV    |                                                                                                                                 |

| Low                                            | V <sub>TL</sub>                      | -100                  |      |                           | mV    |                                                                                                                                 |

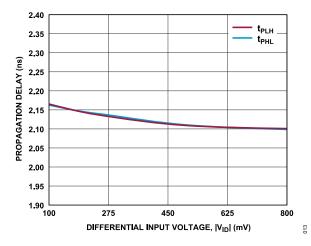

| Differential Input Voltage                     | V <sub>ID</sub>                      | 100                   |      |                           | mV    | See Figure 38 and Table 2                                                                                                       |

| Input Common-Mode Voltage                      | VIC                                  | 0.5 V <sub>ID</sub>   |      | 2.4 – 0.5 V <sub>ID</sub> | V     | See Figure 38 and Table 2                                                                                                       |

| Input Current, High and Low                    | I <sub>IH</sub> , I <sub>IL</sub>    | -5                    |      | +5                        | μA    | One $D_{INx\pm}$ = 2.4 V or 0 V, another $D_{INx\pm}$ = 1.2 V, $V_{DDx}$ = 1.8 V or 0 V, and $V_{IOx}$ = 3.3 V or 0 V           |

| Differential Input Capacitance <sup>1</sup>    | C <sub>INx±</sub>                    |                       | 1.7  |                           | pF    | One $D_{INx\pm}$ = 0.4 sin(30 × 10^6 $\pi t)$ V + 0.5 V and another $D_{INx\pm}$ = 1.2 $V^2$                                    |

| LOGIC INPUTS                                   |                                      |                       |      |                           |       | $V_{DDx} = V_{DD1}$ for $\overline{REFRESH_1}$ , $V_{DDx} = V_{DD2}$ for $\overline{REFRESH_2}$                                 |

| Input High Voltage                             | V <sub>INH</sub>                     | 0.65 V <sub>DDx</sub> |      |                           | V     |                                                                                                                                 |

| Input Low Voltage                              | V <sub>INL</sub>                     |                       |      | 0.35 V <sub>DDx</sub>     | V     |                                                                                                                                 |

| Input-Current High                             | I <sub>INH</sub>                     |                       |      | 1                         | μA    | $\overline{\text{REFRESH}_{x}} = V_{DDx}$                                                                                       |

|                                                |                                      |                       |      | 25                        | μA    | $\overline{\text{REFRESH}_x}$ = 1.9 V, V <sub>DDx</sub> = 0 V                                                                   |

| Input-Current Low                              | I <sub>INL</sub>                     |                       |      | 16                        | μA    | REFRESH <sub>x</sub> = 0 V                                                                                                      |

| OUTPUTS (DRIVERS)                              |                                      |                       |      |                           |       |                                                                                                                                 |

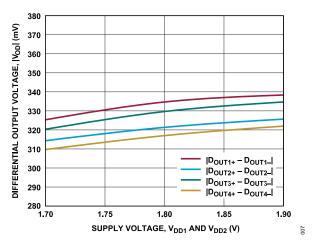

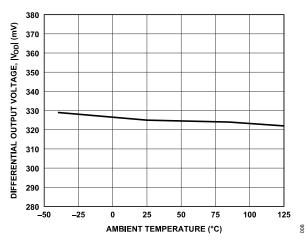

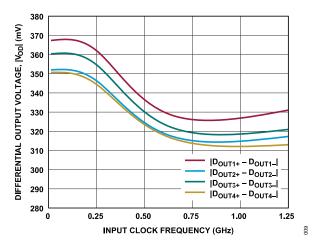

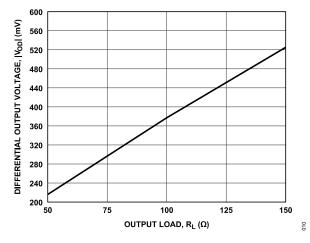

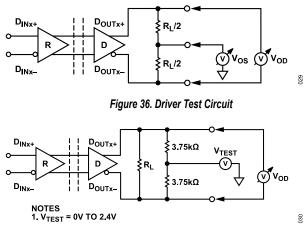

| Differential Output Voltage                    | V <sub>OD</sub>                      | 250                   | 310  | 450                       | mV    | See Figure 36 and Figure 37, load resistance ( $R_L$ ) = 100 $\Omega$                                                           |

| V <sub>OD</sub> Magnitude Change               | Δ V <sub>OD</sub>                    |                       |      | 50                        | mV    | See Figure 36 and Figure 37, $R_L$ = 100 $\Omega$                                                                               |

| Offset Voltage                                 | V <sub>OS</sub>                      | 1.125                 | 1.17 | 1.375                     | V     | See Figure 36, $R_L = 100 \Omega$                                                                                               |

| V <sub>OS</sub> Magnitude Change               | ΔV <sub>OS</sub>                     |                       |      | 50                        | mV    | See Figure 36, $R_L$ = 100 $\Omega$                                                                                             |

| V <sub>OS</sub> , Peak-to-Peak <sup>1</sup>    | V <sub>OS(PP)</sub>                  |                       |      | 150                       | mV    | See Figure 36, $R_L$ = 100 $\Omega$                                                                                             |

| Output Short-Circuit Current                   | I <sub>OS</sub>                      |                       |      | -20                       | mA    | D <sub>OUTx±</sub> = 0 V                                                                                                        |

|                                                |                                      |                       |      | 12                        | mA    | V <sub>OD</sub>   = 0 V                                                                                                         |

| Differential Output Capacitance <sup>1</sup>   | C <sub>OUTx±</sub>                   |                       | 5    |                           | pF    | One $D_{OUTx\pm}$ = 0.4 sin(30 × 10 <sup>6</sup> πt) V + 0.5 V, another $D_{OUTx\pm}$ = 1.2 V, and $V_{DD1}$ or $V_{DD2}$ = 0 V |

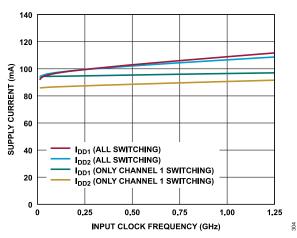

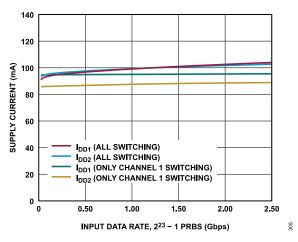

| ADN4622 SUPPLY CURRENT                         |                                      |                       |      |                           |       |                                                                                                                                 |

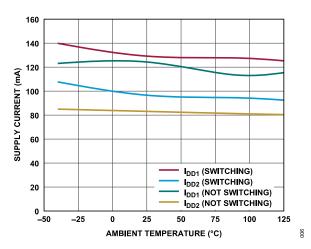

| Supply Current Side 1                          | I <sub>DD1</sub>                     |                       | 116  | 135                       | mA    | Frequency (f) = 1.25 GHz, $R_L$ = 100 $\Omega$                                                                                  |

|                                                |                                      |                       | 102  | 125                       |       | f = 1.25 GHz, R <sub>L</sub> = 100 Ω, REFRESH <sub>1</sub> = V <sub>DD1</sub>                                                   |

| Supply Current Side 2                          | I <sub>DD2</sub>                     |                       | 113  | 133                       | mA    | f = 1.25 GHz, R <sub>L</sub> = 100 Ω                                                                                            |

|                                                |                                      |                       | 99   | 121                       | mA    | f = 1.25 GHz, R <sub>L</sub> = 100 Ω, $\overline{\text{REFRESH}_2}$ = V <sub>DD2</sub>                                          |

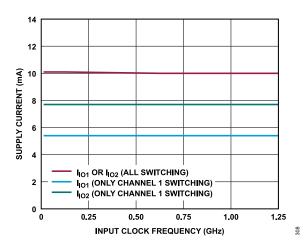

| V <sub>IO1</sub> or V <sub>IO2</sub> Supply    | I <sub>IO1</sub> or I <sub>IO2</sub> |                       | 11   | 14                        | mA    | f = 1.25 GHz                                                                                                                    |

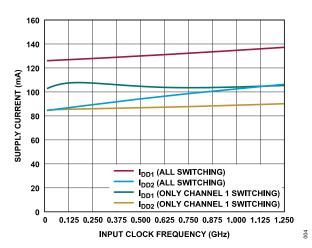

| ADN4624 SUPPLY CURRENT                         |                                      |                       |      |                           |       |                                                                                                                                 |

| Supply Current Side 1                          | I <sub>DD1</sub>                     |                       | 140  | 175                       | mA    | f = 1.25 GHz                                                                                                                    |

| Supply Current Side 2                          | I <sub>DD2</sub>                     |                       |      |                           |       |                                                                                                                                 |

|                                                |                                      |                       | 115  | 140                       | mA    | f = 1.25 GHz, R <sub>L</sub> = 100 Ω                                                                                            |

|                                                |                                      |                       | 95   | 135                       | mA    | f = 1.25 GHz, R <sub>L</sub> = 100 Ω, $\overline{\text{REFRESH}_2}$ = V <sub>DD2</sub>                                          |

| COMMON-MODE TRANSIENT<br>IMMUNITY <sup>3</sup> | CM                                   | 40                    | 100  |                           | kV/µs | Common-mode voltage ( $V_{CM}$ ) = 1000 V, transient magnitude = 800 V                                                          |

<sup>1</sup> These specifications are guaranteed by design and characterization.

<sup>2</sup> t denotes time.

<sup>3</sup> |CM| is the maximum common-mode voltage slew rate that can be sustained while maintaining any D<sub>OUTx+</sub> or D<sub>OUTx-</sub> pin in the same state as the corresponding D<sub>INx+</sub> or D<sub>INx-</sub> pin (no change in output) or producing the expected transition on any D<sub>OUTx+</sub> or D<sub>OUTx-</sub> pin if the applied common-mode transient edge is coincident with a data transition on the corresponding D<sub>INx+</sub> or D<sub>INx-</sub> pin. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges.

## **RECEIVER INPUT THRESHOLD TEST VOLTAGES**

| Applie                | ed Voltages           |                                                  |                                                 |                                                  |

|-----------------------|-----------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------------------|

| D <sub>INx+</sub> (V) | D <sub>INx-</sub> (V) | Input Voltage, Differential, V <sub>ID</sub> (V) | Input Voltage, Common-Mode, V <sub>IC</sub> (V) | Driver Output, Differential V <sub>OD</sub> (mV) |

| 1.25                  | 1.15                  | 0.1                                              | 1.2                                             | >250                                             |

| 1.15                  | 1.25                  | -0.1                                             | +1.2                                            | <-250                                            |

| 2.4                   | 2.3                   | 0.1                                              | 2.35                                            | >250                                             |

| 2.3                   | 2.4                   | -0.1                                             | +2.35                                           | <-250                                            |

| 0.1                   | 0                     | 0.1                                              | 0.05                                            | >250                                             |

| 0                     | 0.1                   | -0.1                                             | +0.05                                           | <-250                                            |

| 1.5                   | 0.9                   | 0.6                                              | 1.2                                             | >250                                             |

| 0.9                   | 1.5                   | -0.6                                             | +1.2                                            | <-250                                            |

| 2.4                   | 1.8                   | 0.6                                              | 2.1                                             | >250                                             |

| 1.8                   | 2.4                   | -0.6                                             | +2.1                                            | <-250                                            |

| 0.6                   | 0                     | 0.6                                              | 0.3                                             | >250                                             |

| 0                     | 0.6                   | -0.6                                             | +0.3                                            | <-250                                            |

#### Table 2. Test Voltages for Receiver Operation

#### TIMING SPECIFICATIONS

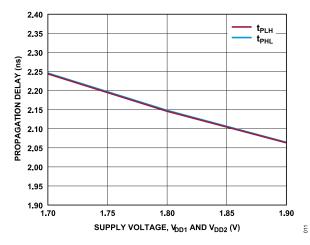

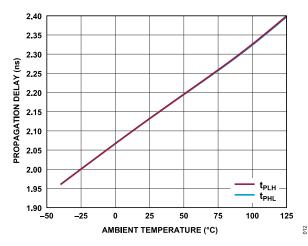

For all minimum and maximum specifications,  $V_{DD1} = V_{DD2} = 1.7$  V to 1.9 V and  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted. For all typical specifications,  $V_{DD1} = V_{DD2} = 1.8$  V and  $T_A = 25^{\circ}$ C. For all specifications,  $\overline{REFRESH_1} = V_{DD1}$  and  $\overline{REFRESH_2} = V_{DD2}$ , unless otherwise noted.

#### Table 3. Timing Specifications

| Parameter                                                                 | Symbol                              | Min | Тур  | Max <sup>1</sup> | Unit   | Test Conditions/Comments                                                                                                                                      |

|---------------------------------------------------------------------------|-------------------------------------|-----|------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

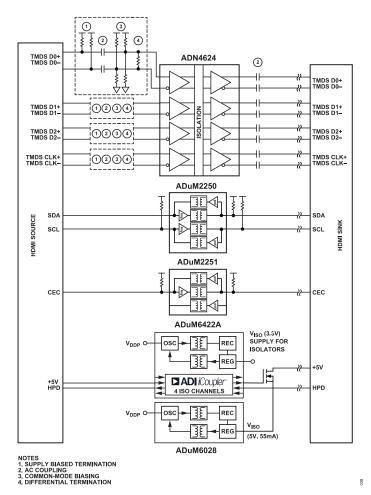

| PROPAGATION DELAY                                                         | t <sub>PLH</sub> , t <sub>PHL</sub> |     | 2.15 | 2.8              | ns     | See Figure 39, from any D <sub>INx+</sub> and D <sub>INx-</sub> to D <sub>OUTx+</sub> and D <sub>OUTx-</sub>                                                  |

| SKEW                                                                      |                                     |     |      |                  |        | See Figure 39, across all D <sub>OUTx+</sub> and D <sub>OUTx-</sub>                                                                                           |

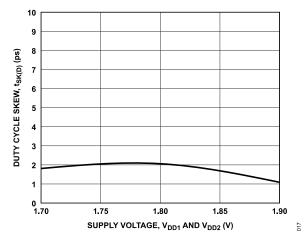

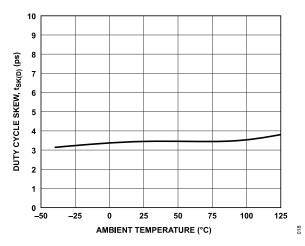

| Duty Cycle <sup>2</sup>                                                   | t <sub>SK(D)</sub>                  |     | 2    | 16               | ps     |                                                                                                                                                               |

| Channel to Channel <sup>3</sup>                                           | t <sub>SK(CH)</sub>                 |     | 40   | 120              | ps     | ADN4622 SOIC_W_FPpackage                                                                                                                                      |

|                                                                           |                                     |     | 38   | 92               | ps     | ADN4624 SOIC_W_FP package                                                                                                                                     |

|                                                                           |                                     |     | 40   | 114              | ps     | ADN4622 LFCSP package                                                                                                                                         |

|                                                                           |                                     |     | 29   | 67               | ps     | ADN4624 LFCSP package                                                                                                                                         |

|                                                                           |                                     |     | 20   | 60               | ps     | ADN4622 Channel 1 to Channel 2, or Channel 3 to Channel 4 only                                                                                                |

| Part to Part <sup>4</sup>                                                 | t <sub>SK(PP)</sub>                 |     | 150  | 300              | ps     |                                                                                                                                                               |

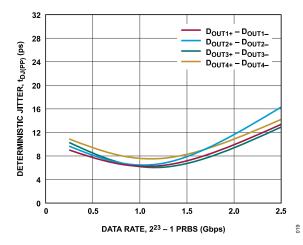

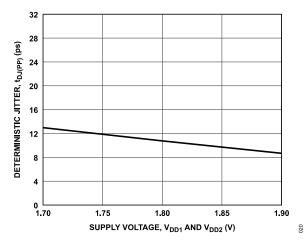

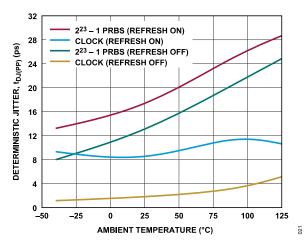

| JITTER <sup>5</sup>                                                       |                                     |     |      |                  |        | See Figure 39, for any D <sub>OUTx+</sub> and D <sub>OUTx-</sub>                                                                                              |

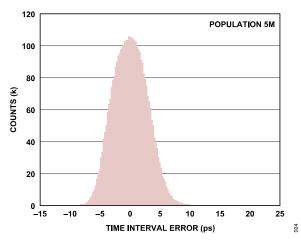

| Random Jitter, RMS <sup>6</sup> (1 $\sigma$ )                             | t <sub>RJ(RMS)</sub>                |     | 0.82 | 1.44             | ps rms | 1.25 GHz clock input                                                                                                                                          |

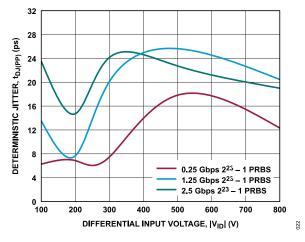

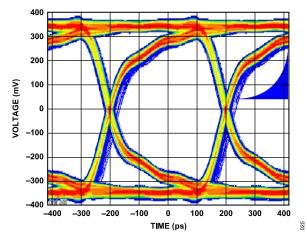

| Deterministic Jitter, Peak-to-Peak <sup>6, 7</sup>                        | t <sub>DJ(PP)</sub>                 |     | 28   | 54               | ps     | 2.5 Gbps, 2 <sup>23</sup> – 1 pseudorandom bit stream (PRBS)                                                                                                  |

| Total Jitter, Peak-to-Peak, at Bit Error Rate (BER) 1 × 10 <sup>-12</sup> | t <sub>TJ(PP)</sub>                 |     | 40   | 70               | ps     | 1.25 GHz/2.5 Gbps, 2 <sup>23</sup> – 1 PRBS <sup>8</sup>                                                                                                      |

| With Crosstalk                                                            |                                     |     | 50   |                  | ps     | 1.25 GHz/2.5 Gbps, 2 <sup>23</sup> – 1 PRBS all channels <sup>8</sup>                                                                                         |

| With Crosstalk and Refresh                                                |                                     |     | 55   |                  | ps     | 1.25 GHz/2.5 Gbps, $2^{23}$ – 1 PRBS all channels, $\overline{\text{REFRESH}_1}$ = GND <sub>1</sub> ,<br>REFRESH <sub>2</sub> = GND <sub>2</sub> <sup>8</sup> |

| Additive Phase Jitter                                                     | t <sub>ADDJ</sub>                   |     |      |                  |        |                                                                                                                                                               |

| SOIC_W_FP Package                                                         |                                     |     | 225  |                  | fs rms | 100 Hz to 100 kHz, output frequency (f <sub>OUT</sub> ) = 10 MHz <sup>9</sup>                                                                                 |

|                                                                           |                                     |     | 270  |                  | fs rms | 100 Hz to 100 kHz, $f_{OUT}$ = 10 MHz, $\overline{REFRESH_1}$ = GND <sub>1</sub> , $\overline{REFRESH_2}$ = GND <sub>2</sub> <sup>9</sup>                     |

|                                                                           |                                     |     | 85   |                  | fs rms | 12 kHz to 20 MHz, f <sub>OUT</sub> = 1.25 GHz <sup>10</sup>                                                                                                   |

|                                                                           |                                     |     | 200  |                  | fs rms | 12 kHz to 20 MHz, $f_{OUT} = 1.25$ GHz, $\overline{REFRESH_1} = GND_1$ , $\overline{REFRESH_2}$ GND <sub>2</sub> <sup>10</sup>                                |

| LFCSP Package                                                             |                                     |     | 152  |                  | fs rms | 100 Hz to 100 kHz, output frequency (f <sub>OUT</sub> ) = 10 MHz <sup>9</sup>                                                                                 |

|                                                                           |                                     |     | 182  |                  | fs rms | 100 Hz to 100 kHz, $f_{OUT}$ = 10 MHz, $\overline{REFRESH_1}$ = $GND_1$ , $\overline{REFRESH_2}$ = $GND_2^9$                                                  |

#### Table 3. Timing Specifications

| Parameter          | Symbol                          | Min | Тур | Max <sup>1</sup> | Unit   | Test Conditions/Comments                                                                                                                    |

|--------------------|---------------------------------|-----|-----|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                                 |     | 152 |                  | fs rms | 12 kHz to 20 MHz, f <sub>OUT</sub> = 1.25 GHz <sup>10</sup>                                                                                 |

|                    |                                 |     | 348 |                  | fs rms | 12 kHz to 20 MHz, $f_{OUT}$ = 1.25 GHz, $\overline{REFRESH_1}$ = GND <sub>1</sub> , $\overline{REFRESH_2}$ = GND <sub>2</sub> <sup>10</sup> |

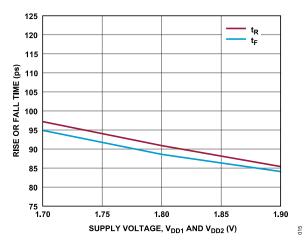

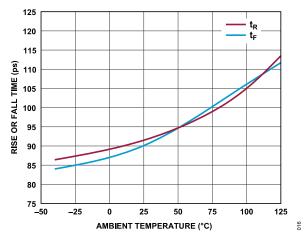

| RISE AND FALL TIME | t <sub>R</sub> , t <sub>F</sub> |     |     | 180              | ps     | See Figure 39, 1.25 GHz clock input, any $D_{OUTx+}$ and $D_{OUTx-}$ , 20% to 80%, $R_L$ = 100 $\Omega$ , load capacitance ( $C_L$ ) = 5 pF |

| MAXIMUM DATA RATE  |                                 | 2.5 |     |                  | Gbps   |                                                                                                                                             |

<sup>1</sup> These specifications are guaranteed by design and characterization.

<sup>2</sup> Duty cycle or pulse skew is the magnitude of the maximum difference between t<sub>PLH</sub> and t<sub>PHL</sub> for any Channel x of a device (where x = 1, 2, 3, or 4), that is, |t<sub>PLHx</sub> - t<sub>PHLx</sub>|.

- <sup>3</sup> Channel to channel or output skew is the difference between the largest and smallest values of t<sub>PLHx</sub> within a device or the difference between the largest and smallest values of t<sub>PLHx</sub> within a device, whichever of the two is greater.

- <sup>4</sup> Part to part output skew is the difference between the largest and smallest values of t<sub>PLHx</sub> across multiple devices or the difference between the largest and smallest values of t<sub>PHLx</sub> across multiple devices, whichever of the two is greater.

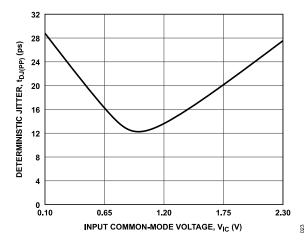

- <sup>5</sup> Jitter parameters are guaranteed by design and characterization. Values do not include stimulus jitter. V<sub>ID</sub> = 400 mV p-p, V<sub>IC</sub> = 1.2 V, and t<sub>R</sub> / t<sub>F</sub> < 0.05 ns (20% to 80%).

- <sup>6</sup> This specification is measured over a population of ~3,000,000 edges.

- <sup>7</sup> Peak-to-peak jitter specifications include jitter due to pulse skew (t<sub>SK(D)</sub>).

- <sup>8</sup> Using the following formula:  $t_{TJ(PP)} = 14 \times t_{RJ(RMS)} + t_{DJ(PP)}$ .

- <sup>9</sup> With an input phase jitter of 340 fs rms subtracted.

- <sup>10</sup> With an input phase jitter of 155 fs rms subtracted.

# INSULATION AND SAFETY RELATED SPECIFICATIONS

For additional information, see www.analog.com/icouplersafety.

#### Table 4. RN-28-1 Wide Body with Finer Pitch [SOIC\_W\_FP] Package

| Parameter                                                                   | Symbol  | Value | Unit   | Test Conditions/Comments                                                                                                   |

|-----------------------------------------------------------------------------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                         |         | 5.7   | kV rms | 1 minute duration                                                                                                          |

| Minimum External Air Gap (Clearance)                                        | L (I01) | 8.3   | mm min | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage)                                        | L (102) | 8.3   | mm min | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB Clearance) | L (PCB) | 8.1   | mm min | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                   |         | 25.5  | µm min | Insulation distance through insulation                                                                                     |

| Tracking Resistance (Comparative Tracking Index)                            | CTI     | >600  | V      | Tested in accordance to IEC 60112                                                                                          |

| Material Group                                                              |         | 1     |        | Material Group per IEC 60664-1                                                                                             |

#### Table 5. CP-32-32 Lead Frame Chip-Scale Package [LFCSP]

| Parameter                                                                   | Symbol  | Value | Unit   | Test Conditions/Comments                                                                                                   |

|-----------------------------------------------------------------------------|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                         |         | 1.5   | kV rms | 1 minute duration                                                                                                          |

| Minimum External Air Gap (Clearance)                                        | L (I01) | 1.27  | mm min | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage)                                        | L (102) | 1.27  | mm min | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB Clearance) | L (PCB) | 1.27  | mm min | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                   |         | 25.5  | µm min | Insulation distance through insulation                                                                                     |

| Tracking Resistance (Comparative Tracking Index)                            | CTI     | >600  | V      | Tested in accordance to IEC 60112                                                                                          |

| Material Group                                                              |         | 1     |        | Material Group per IEC 60664-1                                                                                             |

## PACKAGE CHARACTERISTICS

#### Table 6. RN-28-1 Wide Body with Finer Pitch [SOIC\_W\_FP] Package and CP-32-32 Lead Frame Chip-Scale Package [LFCSP]

| Parameter                                  | Symbol           | Min | Тур              | Max | Unit | Test Conditions/Comments                                 |

|--------------------------------------------|------------------|-----|------------------|-----|------|----------------------------------------------------------|

| Resistance (Input to Output) <sup>1</sup>  | R <sub>I-O</sub> |     | 10 <sup>13</sup> |     | Ω    | Voltage (input to output) (V <sub>I-O</sub> ) = 500 V DC |

| Capacitance (Input to Output) <sup>1</sup> | CI-O             |     | 2.2              |     | pF   | f = 1 MHz                                                |

| Input Capacitance <sup>2</sup>             | CI               |     | 3.4              |     | pF   |                                                          |

<sup>1</sup> The device is considered a 2-terminal device: Pin 1 through Pin 14 are shorted together (Pin 1 through Pin 16 for LFCSP), and Pin 15 through Pin 28 are shorted together (Pin 17 through Pin 32 for LFCSP).

<sup>2</sup> Input capacitance is from any input data pin to ground.

## **REGULATORY INFORMATION**

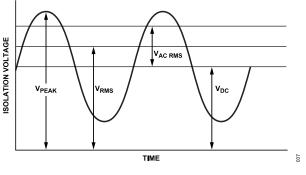

See Table 14 and the Insulation Lifetime section for details regarding the recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

| Regulatory Agency          | Standard Certification/Approval                                                                               | File              |

|----------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|

| UL (Pending)               | To be recognized under UL 1577 Component Recognition Program <sup>1</sup>                                     | E214100           |

|                            | Single protection, 5700 V rms isolation voltage                                                               |                   |

| CSA (Pending) <sup>2</sup> | To be approved under CSA Component Acceptance Notice 5A                                                       | 205078            |

|                            | CSA 62368-1-19, EN 62368-1:2020 and IEC 62368-1:2018 third edition                                            |                   |

|                            | Basic insulation at 830 V rms                                                                                 |                   |

|                            | Reinforced insulation at 415 V rms                                                                            |                   |

|                            | CSA 61010-1-12+A1 and IEC 61010-1 third edition                                                               |                   |

|                            | Basic insulation at 600 V rms                                                                                 |                   |

|                            | Reinforced insulation at 300 V rms                                                                            |                   |

|                            | CSA 60601-1:14 and IEC60601-1 third edition+A1                                                                |                   |

|                            | 1 means of patient protection (MOPP) for 261 V rms                                                            |                   |

| VDE (Pending)              | To be certified according to DIN V VDE V 0884-11 (VDE V 0884-11):2017-01 <sup>3</sup>                         | 2471900-4880-0001 |

|                            | Reinforced insulation, V <sub>IORM</sub> = 849 V <sub>PEAK</sub> , V <sub>IOSM</sub> = 8000 V <sub>PEAK</sub> |                   |

| CQC (Pending)              | To be certified according to GB4943.1-2011 per CQC11-471543-2015                                              | Pending           |

|                            | Basic insulation at 820 V rms (1159 V <sub>PEAK</sub> )                                                       |                   |

|                            | Reinforced insulation at 410 V rms (578 V <sub>PEAK</sub> )                                                   |                   |

#### Table 7. RN-28-1 Wide-Body with Finer Pitch [SOIC W FP] Package

<sup>1</sup> In accordance with UL 1577, each ADN4622/ADN4624 is proof tested by applying an insulation test voltage ≥6840 V rms for 1 sec.

<sup>2</sup> Working voltages are quoted for Pollution Degree 2, Material Group III. ADN4622/ADN4624 case material has been evaluated by CSA as Material Group I.

<sup>3</sup> In accordance with DIN V VDE V 0884-11, each ADN4622/ADN4624 is proof tested by applying an insulation test voltage ≥1592 V<sub>PEAK</sub> for 1 sec (partial discharge detection limit = 5 pC).

#### Table 8. CP-32-32 Lead Frame Chip-Scale Package [LFCSP]

| Regulatory Agency | Standard Certification/Approval                                                                               | File              |

|-------------------|---------------------------------------------------------------------------------------------------------------|-------------------|

| UL (Pending)      | To be recognized under UL 1577 Component Recognition Program <sup>1</sup>                                     | E214100           |

|                   | Single protection, 1500 V rms isolation voltage                                                               |                   |

| CSA (Pending)     | To be approved under CSA Component Acceptance Notice 5A                                                       | 205078            |

| VDE (Pending)     | To be certified according to DIN V VDE V 0884-11 (VDE V 0884-11):2017-01 <sup>2</sup>                         | 2471900-4880-0001 |

|                   | Reinforced insulation, V <sub>IORM</sub> = 560 V <sub>PEAK</sub> , V <sub>IOSM</sub> = 8000 V <sub>PEAK</sub> |                   |

| CQC (Pending)     | To be certified according to GB4943.1-2011 per CQC11-471543-2015                                              | Pending           |

<sup>1</sup> In accordance with UL 1577, each ADN4622/ADN4624 is proof tested by applying an insulation test voltage ≥1800 V rms for 1 sec.

<sup>2</sup> In accordance with DIN V VDE V 0884-11, each ADN4622/ADN4624 is proof tested by applying an insulation test voltage ≥1050 V<sub>PEAK</sub> for 1 sec (partial discharge detection limit = 5 pC).

## DIN V VDE V 0884-11 (VDE V 0884-11) INSULATION CHARACTERISTICS (PENDING)

This isolator is suitable for reinforced electrical isolation only within the safety limit data. Protective circuits ensure the maintenance of the safety data.

| Description                                          | Test Conditions/Comments <sup>1</sup>                                                                          | Symbol              | Characteristic   | Unit              |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|------------------|-------------------|

| Installation Classification per DIN VDE 0110         |                                                                                                                |                     |                  |                   |

| For Rated Mains Voltage ≤ 150 V rms                  |                                                                                                                |                     | I to IV          |                   |

| For Rated Mains Voltage ≤ 300 V rms                  |                                                                                                                |                     | I to IV          |                   |

| For Rated Mains Voltage ≤ 600 V rms                  |                                                                                                                |                     | I to IV          |                   |

| Climatic Classification                              |                                                                                                                |                     | 40/125/21        |                   |

| Pollution Degree per DIN VDE 0110, Table 1           |                                                                                                                |                     | 2                |                   |

| Maximum Working Insulation Voltage                   |                                                                                                                | VIORM               | 849              | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method B1              | $V_{IORM} \times 1.875 = V_{PD (M)}$ , 100% production test, $t_{INI} = t_M = 1$ sec, partial discharge < 5 pC | V <sub>PD (m)</sub> | 1592             | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method A               |                                                                                                                | V <sub>PD (m)</sub> |                  |                   |

| After Environmental Tests Subgroup 1                 | $V_{IORM} \times 1.5 = V_{PD (M)}$ , $t_{INI} = 60$ sec, $t_M = 10$ sec, partial discharge < 5 pC              |                     | 1274             | V <sub>PEAK</sub> |

| After Input or Safety Test Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PD (M)}$ , $t_{INI} = 60$ sec, $t_M = 10$ sec, partial discharge < 5 pC              |                     | 1019             | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage                        |                                                                                                                | VIOTM               | 8000             | V <sub>PEAK</sub> |

| Surge Isolation Voltage                              |                                                                                                                |                     |                  |                   |

| Basic                                                | V <sub>PEAK</sub> = 16 kV, 1.2 μs rise time, 50 μs, 50% fall time                                              | VIOSM               | 16,000           | V <sub>PEAK</sub> |

| Reinforced                                           | V <sub>PEAK</sub> = 16 kV, 1.2 μs rise time, 50 μs, 50% fall time                                              | VIOSM               | 10000            | V <sub>PEAK</sub> |

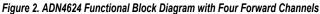

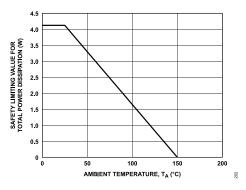

| Safety Limiting Values                               | Maximum value allowed in the event of a failure (see Figure 4)                                                 |                     |                  |                   |

| Maximum Junction Temperature                         |                                                                                                                | Ts                  | 150              | °C                |

| Total Power Dissipation at 25°C                      |                                                                                                                | Ps                  | 2.74             | W                 |

| Insulation Resistance at T <sub>S</sub>              | V <sub>IO</sub> = 500 V                                                                                        | Rs                  | >10 <sup>9</sup> | Ω                 |

$^1~$  For information about  $t_{M},\,t_{INI},$  and  $V_{IO},$  see DIN V VDE V 0884-11.

Figure 3. Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature per DIN V VDE V 0884-11, SOIC\_W\_FP

#### Table 10. CP-32-32 Lead Frame Chip-Scale Package [LFCSP]

| Description                                          | Test Conditions/Comments <sup>1</sup>                                                                          | Symbol              | Characteristic   | Unit              |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------|------------------|-------------------|

| Installation Classification per DIN VDE 0110         |                                                                                                                |                     |                  |                   |

| For Rated Mains Voltage ≤ 150 V rms                  |                                                                                                                |                     | I to III         |                   |

| For Rated Mains Voltage ≤ 300 V rms                  |                                                                                                                |                     | I to II          |                   |

| For Rated Mains Voltage ≤ 400 V rms                  |                                                                                                                |                     | 1                |                   |

| Climatic Classification                              |                                                                                                                |                     | 40/125/21        |                   |

| Pollution Degree per DIN VDE 0110, Table 1           |                                                                                                                |                     | 2                |                   |

| Maximum Working Insulation Voltage                   |                                                                                                                | VIORM               | 560              | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method B1              | $V_{IORM} \times 1.875 = V_{PD (M)}$ , 100% production test, $t_{INI} = t_M = 1$ sec, partial discharge < 5 pC | V <sub>PD (m)</sub> | 1050             | V <sub>PEAK</sub> |

| Input to Output Test Voltage, Method A               |                                                                                                                | V <sub>PD (m)</sub> |                  |                   |

| After Environmental Tests Subgroup 1                 | $V_{IORM} \times 1.5 = V_{PD (M)}$ , $t_{INI} = 60$ sec, $t_M = 10$ sec, partial discharge < 5 pC              |                     | 840              | V <sub>PEAK</sub> |

| After Input or Safety Test Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PD (M)}$ , $t_{INI} = 60$ sec, $t_M = 10$ sec, partial discharge < 5 pC              |                     | 672              | V <sub>PEAK</sub> |

| Highest Allowable Overvoltage                        |                                                                                                                | VIOTM               | 2500             | V <sub>PEAK</sub> |

| Surge Isolation Voltage                              |                                                                                                                |                     |                  |                   |

| Basic                                                | V <sub>PEAK</sub> = 16 kV, 1.2 μs rise time, 50 μs, 50% fall time                                              | VIOSM               | 16,000           | V <sub>PEAK</sub> |

| Reinforced                                           | V <sub>PEAK</sub> = 16 kV, 1.2 μs rise time, 50 μs, 50% fall time                                              | VIOSM               | 10000            | V <sub>PEAK</sub> |

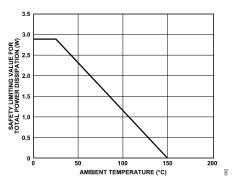

| Safety Limiting Values                               | Maximum value allowed in the event of a failure (see Figure 4)                                                 |                     |                  |                   |

| Maximum Junction Temperature                         |                                                                                                                | T <sub>S</sub>      | 150              | °C                |

| Total Power Dissipation at 25°C                      |                                                                                                                | Ps                  | 4.12             | W                 |

| Insulation Resistance at T <sub>S</sub>              | V <sub>IO</sub> = 500 V                                                                                        | R <sub>S</sub>      | >10 <sup>9</sup> | Ω                 |

$^1~$  For information about  $t_{M},\,t_{INI},\,and\,V_{IO},\,see$  DIN V VDE V 0884-11.

Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values with Ambient Temperature per DIN V VDE V 0884-11, LFCSP

## **RECOMMENDED OPERATING CONDITIONS**

#### Table 11. Recommended Operating Conditions

| Parameter                                        | Symbol                              | Rating          |

|--------------------------------------------------|-------------------------------------|-----------------|

| Operating Temperature                            | T <sub>A</sub>                      | -40°C to +125°C |

| V <sub>DDx</sub> Supply Voltage Side 1 or Side 2 | V <sub>DD1</sub> , V <sub>DD2</sub> | 1.7 V to 1.9 V  |

| V <sub>IOx</sub> Supply Voltage Side 1 or Side 2 | V <sub>IO1</sub> , V <sub>IO2</sub> | 3 V to 3.6 V    |

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 12. Absolute Maximum Ratings

| Parameter                                                                                                       | Rating                                                     |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| V <sub>DD1</sub> to GND <sub>1</sub> , V <sub>DD2</sub> to GND <sub>2</sub>                                     | -0.3 V to +2 V                                             |

| $V_{IO1}$ to $GND_1$ , $V_{IO2}$ to $GND_2$                                                                     | -0.3 V to +4 V                                             |

| Input Voltage $\overline{\text{REFRESH}_1}$ to $\text{GND}_1$ , $\overline{\text{REFRESH}_2}$ to $\text{GND}_2$ | -0.3 V to +2 V                                             |

| Input Voltage ( $D_{INx+}$ , $D_{INx-}$ ) to $GND_x$ on the Same Side                                           | -0.3 V to +4 V                                             |

| Output Voltage (D $_{OUTx^+}$ , D $_{OUTx^-}$ ) to $GND_x$ on the Same Side                                     | -0.3 V to +2 V                                             |

| Short-Circuit Duration ( $D_{OUTx+}$ , $D_{OUTx-}$ ) to $GND_x$ on the Same Side                                | Continuous                                                 |

| Operating Temperature Range                                                                                     | -40°C to +125°C                                            |

| Storage Temperature Range                                                                                       | -65°C to +150°C                                            |

| Junction Temperature (T <sub>J</sub> Maximum)                                                                   | 150°C                                                      |

| Power Dissipation                                                                                               | (T <sub>J</sub> maximum − T <sub>A</sub> )/θ <sub>JA</sub> |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# Table 13. Maximum Continuous Working Voltage, RN-28-1 Standard Small Outline, Wide Body, with Finer Pitch [SOIC\_W\_FP] Package

| Parameter <sup>1</sup> | Rating                 | Constraint                                                                                                               |

|------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|

| AC Voltage             |                        |                                                                                                                          |

| Bipolar Waveform       |                        |                                                                                                                          |

| Basic Insulation       | 650 V rms              | Basic insulation rating per<br>IEC60747-17. Accumulative failure<br>rate over lifetime (FROL) ≤ 1000 ppm<br>at 20 years. |

| Reinforced Insulation  | 600 V rms              | Reinforced insulation rating per<br>IEC60747-17. Accumulative FROL ≤<br>1 ppm at 26 years.                               |

| Unipolar Waveform      |                        |                                                                                                                          |

| Basic Insulation       | 1782 V <sub>PEAK</sub> | Rating limited by AC bipolar<br>waveform accumulative FROL ≤<br>1000 ppm at 20 years.                                    |

| Reinforced Insulation  | 1330 V <sub>PEAK</sub> | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment.                              |

| DC Voltage             |                        |                                                                                                                          |

| Basic Insulation       | 1660 V DC              | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment.                              |

| Reinforced Insulation  | 830 V DC               | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment.                              |

<sup>1</sup> Maximum continuous working voltage refers to the continuous voltage magnitude imposed across the isolation barrier in a Pollution Degree 2 environment. See the Insulation Lifetime section for more details.

| Parameter <sup>1</sup> | Rating                | Constraint                                                                                  |

|------------------------|-----------------------|---------------------------------------------------------------------------------------------|

| AC Voltage             |                       |                                                                                             |

| Bipolar Waveform       |                       |                                                                                             |

| Basic Insulation       | 253 V rms             | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment. |

| Reinforced Insulation  | 63 V rms              | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment. |

| Unipolar Waveform      |                       |                                                                                             |

| Basic Insulation       | 413 V <sub>PEAK</sub> | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment. |

| Reinforced Insulation  | 102 V <sub>PEAK</sub> | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment. |

| DC Voltage             |                       |                                                                                             |

| Basic Insulation       | 253 V DC              | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment. |

| Reinforced Insulation  | 63 V DC               | Rating limited by package creepage<br>per IEC 60664-1 in Pollution Degree<br>2 environment. |

Table 14. Maximum Continuous Working Voltage, CP-32-32 Lead Frame Chip-

<sup>1</sup> Maximum continuous working voltage refers to the continuous voltage magnitude imposed across the isolation barrier in a Pollution Degree 2 environment. See the Insulation Lifetime section for more details.

## THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operation environment. Close attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

#### Table 15. Thermal Resistance

| Package Type <sup>1</sup> | θ <sub>JA</sub> | Unit |

|---------------------------|-----------------|------|

| RN-28-1                   | 43.45           | °C/W |

| CP-32-32                  | 30.3            | °C/W |

<sup>1</sup> Test Condition 1: thermal impedance simulated with 4-layer standard JEDEC PCB.

## **ABSOLUTE MAXIMUM RATINGS**

# ELECTROSTATIC DISCHARGE (ESD) RATINGS

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

International electrotechnical commission (IEC) electromagnetic compatibility: Part 4-2 (IEC) per IEC 61000-4-2.

# ESD Ratings for ADN4622/ADN4624

#### Table 16. ADN4622/ADN4624, 28-Lead SOIC\_W\_FP

| ESD Model        | Withstand Threshold (V)   | Class   |

|------------------|---------------------------|---------|

| HBM <sup>1</sup> | ±4000                     | 3A      |

| IEC <sup>2</sup> | ±8000 (contact discharge) | Level 4 |

$^1\,$  All pins to respective GNDx, 1.5 k\Omega, 100 pF.

<sup>2</sup> LVDS pins to isolated GNDx across isolation barrier.

#### Table 17. ADN4622/ADN4624, 32-Lead LFCSP

| ESD Model        | Withstand Threshold (V)   | Class   |

|------------------|---------------------------|---------|

| HBM <sup>1</sup> | ±4000                     | 3A      |

| IEC <sup>2</sup> | ±2000 (contact discharge) | Level 1 |

<sup>1</sup> All pins to respective GNDx, 1.5 k $\Omega$ , 100 pF.

<sup>2</sup> LVDS pins to isolated GNDx across isolation barrier.

# ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

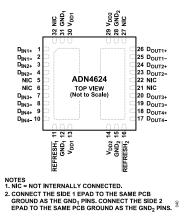

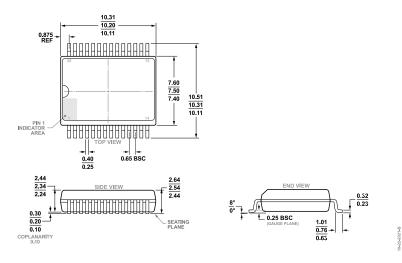

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 5. ADN4622 SOIC\_W\_FP Pin Configuration

| Table 18. ADN4622 SOIC_W_FP Pin Function Descriptions |

|-------------------------------------------------------|

|-------------------------------------------------------|

| Pin No. | Mnemonic             | Description                                                                                                                                                                                                                  |  |

|---------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 14   | V <sub>DD1</sub>     | 1.8 V Power Supply for Side 1. Connect both pins externally and bypass to the adjacent GND <sub>1</sub> pins with 0.1 µF capacitors.                                                                                         |  |

| 2, 13   | GND <sub>1</sub>     | Ground, Side 1.                                                                                                                                                                                                              |  |

| 3       | V <sub>IO1</sub>     | 3.3 V Input and Output Power Supply for Side 1. Bypass to the adjacent GND $_1$ pin with a 0.1 $\mu$ F capacitor.                                                                                                            |  |

| 4       | D <sub>IN1+</sub>    | Noninverted Differential Input 1.                                                                                                                                                                                            |  |

| 5       | D <sub>IN1-</sub>    | Inverted Differential Input 1.                                                                                                                                                                                               |  |

| 6       | D <sub>IN2+</sub>    | Noninverted Differential Input 2.                                                                                                                                                                                            |  |

| 7       | D <sub>IN2-</sub>    | Inverted Differential Input 2.                                                                                                                                                                                               |  |

| 8       | D <sub>OUT3-</sub>   | Inverted Differential Output 3.                                                                                                                                                                                              |  |

| 9       | D <sub>OUT3+</sub>   | Noninverted Differential Output 3.                                                                                                                                                                                           |  |

| 10      | D <sub>OUT4-</sub>   | Inverted Differential Output 4.                                                                                                                                                                                              |  |

| 11      | D <sub>OUT4+</sub>   | Noninverted Differential Output 4.                                                                                                                                                                                           |  |

| 12      | REFRESH <sub>1</sub> | Active-Low Enable for Side 1 Refresh Function. Short to GND <sub>1</sub> for normal operation with refresh enabled, or short to V <sub>DD1</sub> for lower power, lower jitter, and quieter operation with refresh disabled. |  |

| 15, 28  | V <sub>DD2</sub>     | 1.8 V Power Supply for Side 2. Connect both pins externally and bypass to the adjacent GND <sub>2</sub> pins with 0.1 µF capacitors.                                                                                         |  |

| 16, 27  | GND <sub>2</sub>     | Ground, Side 2.                                                                                                                                                                                                              |  |

| 17      | V <sub>IO2</sub>     | 3.3 V Input and Output Power Supply for Side 2. Bypass to the adjacent GND <sub>2</sub> pin with a 0.1 µF capacitor.                                                                                                         |  |

| 18      | D <sub>IN4+</sub>    | Noninverted Differential Input 4.                                                                                                                                                                                            |  |

| 19      | D <sub>IN4-</sub>    | Inverted Differential Input 4.                                                                                                                                                                                               |  |

| 20      | D <sub>IN3+</sub>    | Noninverted Differential Input 3.                                                                                                                                                                                            |  |

| 21      | D <sub>IN3-</sub>    | Inverted Differential Input 3.                                                                                                                                                                                               |  |

| 22      | D <sub>OUT2-</sub>   | Inverted Differential Output 2.                                                                                                                                                                                              |  |

| 23      | D <sub>OUT2+</sub>   | Noninverted Differential Output 2.                                                                                                                                                                                           |  |

| 24      | D <sub>OUT1-</sub>   | Inverted Differential Output 1.                                                                                                                                                                                              |  |

| 25      | D <sub>OUT1+</sub>   | Noninverted Differential Output 1.                                                                                                                                                                                           |  |

| 26      | REFRESH <sub>2</sub> | Active-Low Enable for Side 2 Refresh Function. Short to GND <sub>2</sub> for normal operation with refresh enabled, or short to V <sub>DD2</sub> for lower power, lower jitter, and quieter operation with refresh disabled. |  |

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

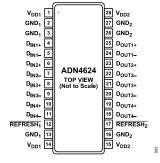

Figure 6. ADN4624 SOIC\_W\_FP Pin Configuration

| Pin No.    | Mnemonic             | Description                                                                                                                                                                                                                  |  |

|------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1, 14      | V <sub>DD1</sub>     | 1.8 V Power Supply for Side 1. Connect both pins externally and bypass to the adjacent GND <sub>1</sub> pins with 0.1 µF capacitors.                                                                                         |  |

| 2, 3, 13   | GND <sub>1</sub>     | Ground, Side 1.                                                                                                                                                                                                              |  |

| 4          | D <sub>IN1+</sub>    | Noninverted Differential Input 1.                                                                                                                                                                                            |  |

| 5          | D <sub>IN1-</sub>    | Inverted Differential Input 1.                                                                                                                                                                                               |  |

| 6          | D <sub>IN2+</sub>    | Noninverted Differential Input 2.                                                                                                                                                                                            |  |

| 7          | D <sub>IN2</sub> -   | Inverted Differential Input 2.                                                                                                                                                                                               |  |

| 8          | D <sub>IN3+</sub>    | Noninverted Differential Input 3.                                                                                                                                                                                            |  |

| 9          | D <sub>IN3-</sub>    | Inverted Differential Input 3.                                                                                                                                                                                               |  |

| 10         | D <sub>IN4+</sub>    | Noninverted Differential Input 4.                                                                                                                                                                                            |  |

| 11         | D <sub>IN4-</sub>    | Inverted Differential Input 4.                                                                                                                                                                                               |  |

| 12         | REFRESH <sub>1</sub> | Active-Low Enable for Side 1 Refresh Function. Short to GND <sub>1</sub> for normal operation with refresh enabled, or short to V <sub>DD1</sub> for lower power, lower jitter, and quieter operation with refresh disabled. |  |

| 15, 28     | V <sub>DD2</sub>     | 1.8 V Power Supply for Side 2. Connect both pins externally and bypass to the adjacent GND <sub>2</sub> pins with 0.1 µF capacitors.                                                                                         |  |

| 16, 26, 27 | GND <sub>2</sub>     | Ground, Side 2.                                                                                                                                                                                                              |  |

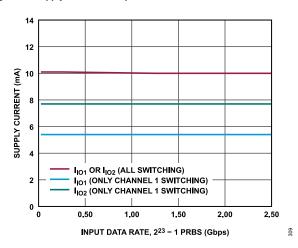

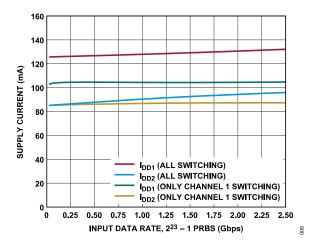

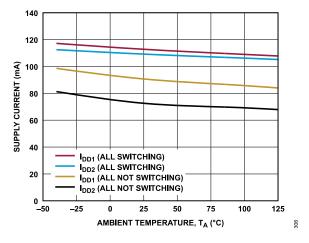

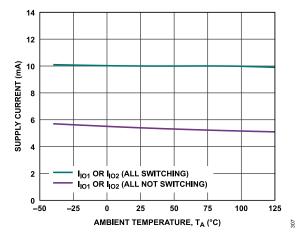

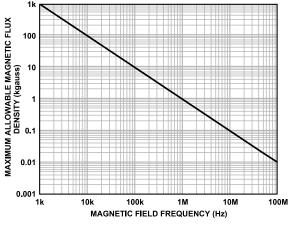

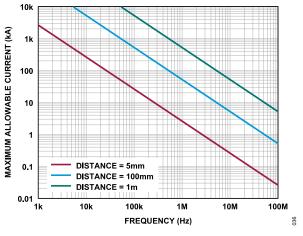

| 17         | REFRESH <sub>2</sub> | Active-Low Enable for Side 2 Refresh Function. Short to GND <sub>2</sub> for normal operation with refresh enabled, or short to V <sub>DD2</sub> for lower power, lower jitter, and quieter operation with refresh disabled. |  |