## 14.0 GHz to 14.5 GHz, SATCOM, Ku Band Upconverter

#### **FEATURES**

- ▶ IF to Ku band upconverter with integrated PLL

- ▶ RF output frequency range: 14.0 GHz to 14.5 GHz

- ▶ Internal LO frequency range: 8.7 GHz to 10.7 GHz

- Noise floor density: <−140 dBm/Hz</p>

- $\blacktriangleright$  Matched 50  $\Omega$  single-ended RF output and IF input

- On-chip power detector

- ▶ On-chip ADC

- ▶ Provides transmitter synthesizer lock detect

- ▶ Programmable at 20 MHz via 4-wire SPI interface

- ▶ Transmitter mute function

- ▶ 40-lead, 6 mm × 6 mm LFCSP package

#### **APPLICATIONS**

SATCOM user terminals

#### **GENERAL DESCRIPTION**

The ADMV4630 is a Ku band upconverter optimized for various satellite communication (SATCOM) user terminals that operate in the 14.0 GHz to 14.5 GHz frequency range.

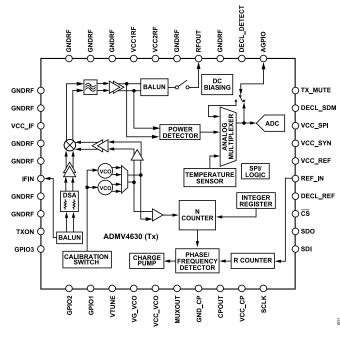

The ADMV4630 local oscillator (LO) signal is generated internally via the on-chip Integer N (INT) synthesizer. The internal synthesizer enables LO frequency coverage from 8.7 GHz to 10.7 GHz. The input intermediate frequency (IF) signals from 3 GHz to 5 GHz are upconverted to an RF of 14.0 GHz to 14.5 GHz. The chip includes filtering to attenuate both the LO feedthrough and unwanted lower sideband. The chip also includes a digital step attenuator at the IF input to provide up to 31 dB of gain control range with 1 dB steps to adjust for preceding cable losses. The transmitter output is automatically muted if the synthesizer becomes unlocked.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The digital serial peripheral interface (SPI) allows fast frequency and gain programming. In addition to the digital SPI control, an analog control pin (TX\_MUTE) quickly powers down all circuits and places the receiver in standby mode for power saving. Another analog general-purpose input/output (AGPIO) pin can be used either as an input to be read by the on-chip analog-to-digital converter (ADC), or as an analog output for proportional to absolute temperature (PTAT) voltages. There are also three digital GPIO pins that output logic levels to control external devices using the SPI.

The ADMV4630 upconverter comes in a compact, thermally enhanced, 6 mm  $\times$  6 mm, 40-lead lead frame chip scale package (LFCSP). The ADMV4630 operates over the  $-40^{\circ}$ C to  $+85^{\circ}$ C case temperature range.

## **TABLE OF CONTENTS**

| Features                                    | 1  | Loop Filter and Charge Pump Current     | 10    |

|---------------------------------------------|----|-----------------------------------------|-------|

| Applications                                |    | On-Chip MUXOUT Pin                      |       |

| Functional Block Diagram                    |    | Analog Mux Block, AGPIO Pin, and ADC    |       |

| General Description                         |    | GPIOx Pins                              |       |

| Specifications                              |    | Digital Lock Detect and MUTE_IF_UNLOCK  |       |

| Absolute Maximum Ratings                    |    | Bit                                     | 20    |

| Thermal Resistance                          |    | Signal Chain Bias, Mask, TX_MUTE Pin,   | . 20  |

| ESD Caution                                 |    | and TXON Pin                            | 20    |

| Pin Configuration and Function Descriptions |    | SPI Configuration                       |       |

| Typical Performance Characteristics         |    | VCO Autocalibration and Automatic Level | . ∠ ۱ |

| Minimum Attenuation Performance: DSA        | 0  | Control                                 | 21    |

| (Register 0x300) = 31                       | 8  | Double Buffered Registers               |       |

| Maximum Attenuation Performance: DSA        | 0  | Initialization Registers                |       |

| (Register 0x300) = 0                        | 14 | Register Summary                        |       |

| Spurious Performance                        |    | Register Details                        |       |

| Theory of Operation                         |    | SPI Configuration Register              |       |

| Reference Input Stage                       |    | Outline Dimensions                      |       |

| Reference Doubler, R Counter, and           | 10 | Ordering Guide                          |       |

| Reference Divide by 2                       | 19 | Evaluation Boards                       |       |

| INT Mode and N Counter                      |    | Evaluation Boardo                       | . 40  |

| Phase Frequency Detector (PFD) and          | 13 |                                         |       |

| Charge Pump (CP)                            | 10 |                                         |       |

| Onarge rump (or )                           | 13 |                                         |       |

|                                             |    |                                         |       |

| REVISION HISTORY                            |    |                                         |       |

| 2/2024—Rev. A to Rev. B                     |    |                                         |       |

| Changed Master to Controller (Throughout)   |    |                                         | 1     |

|                                             |    |                                         |       |

|                                             |    |                                         |       |

|                                             |    |                                         |       |

| 7/2022—Revision A: Initial Version          |    |                                         |       |

analog.com Rev. B | 2 of 40

## **SPECIFICATIONS**

$T_A$  = 25°C, IF = 4 GHz, VCC = VCC\_IF = VCC\_VCO = VCC\_CP = VCC\_REF = VCC\_SYN = VCC\_SPI = VCC2RF = VCC1RF = 3.3 V, digital signal attenuation (DSA) Register 0x300 = 31, clock reference input power = 3 dBm, upper sideband selected, unless otherwise noted. VCC refers to the voltage of all VCC\_xxx pins.

Table 1.

| Parameter                                          | Test Conditions/Comments  | Min   | Тур  | Max   | Unit                   |

|----------------------------------------------------|---------------------------|-------|------|-------|------------------------|

| RF OUTPUT FREQUENCY RANGE                          |                           | 14.0  |      | 14.5  | GHz                    |

| LO FREQUENCY RANGE                                 |                           | 8.7   |      | 10.7  | GHz                    |

| LO Lock Time                                       |                           |       |      | 370   | μs                     |

| LO REFERENCE FREQUENCY                             |                           |       | 25   |       | MHz                    |

| REFERENCE INPUT POWER                              |                           | 0     |      | 5     | dBm                    |

| LO PHASE NOISE PERFORMANCE                         |                           |       |      |       |                        |

| 1 kHz Offset from Carrier                          |                           |       | -85  |       | dBc/Hz                 |

| 10 kHz Offset from Carrier                         |                           |       | -90  |       | dBc/Hz                 |

| 100 kHz Offset from Carrier                        |                           |       | -95  |       | dBc/Hz                 |

| 1 MHz Offset from Carrier                          |                           |       | -125 |       | dBc/Hz                 |

| 10 MHz Offset from Carrier                         |                           |       | -135 |       | dBc/Hz                 |

| 100 MHz Offset from Carrier                        | Measured at the RF output |       | -138 |       | dBc/Hz                 |

| Integrated Single Sideband Phase Noise Performance | 1 kHz to 20 MHz           |       | -34  |       | dBc/Hz                 |

| IF INPUT FREQUENCY RANGE                           |                           | 3     |      | 5     | GHz                    |

| IF Channel Bandwidth                               |                           | ±62   |      |       | MHz                    |

| IF Input Power                                     |                           |       |      | 4     | dBm                    |

| F UPCONVERTER PERFORMANCE                          |                           |       |      |       |                        |

| Maximum Conversion Gain                            |                           | 16    | 19   |       | dB                     |

| Gain Control Range                                 |                           |       | 31   |       | dB                     |

| Gain Flatness                                      | Over 20 MHz bandwidth     | -0.15 |      | +0.15 | dB/20 MHz <sup>1</sup> |

| Output Noise Density                               |                           |       |      | -140  | dBm/Hz                 |

| Output Third-Order Intercept (IP3)                 | Minimum attenuation       | 19.5  | 22   |       | dBm                    |

| Output 1 dB Compression Point (P1dB)               | Minimum attenuation       |       | 11   |       | dBm                    |

| Sideband Rejection                                 | Noise floor limited       | 70    | 95   |       | dBc                    |

| LO to RF Feedthrough                               |                           |       | -40  | -30   | dBm                    |

| Transmitter Mute On/Off Ratio                      | Output switch only        | 25    |      |       | dB                     |

| Transmitter Mute On/Off Ratio                      | Switch plus power-down LO | 40    |      |       | dB                     |

| Adjacent Channel Power Ratio (ACPR)                |                           |       | -35  |       | dBc                    |

| Error Vector Magnitude (EVM)                       |                           |       | 2.0  |       | %                      |

| TRANSMITTER DETECTOR PERFORMANCE                   |                           |       |      |       |                        |

| Input Frequency                                    |                           | 14.0  |      | 14.5  | GHz                    |

| Input Power Range                                  | At RFOUT pin              | -2    |      | +13   | dBm                    |

| Detector Accuracy                                  | Not calibrated            |       | ±1   |       | dB                     |

| ADC PERFORMANCE                                    |                           |       |      |       |                        |

| ADC Bits                                           |                           |       | 8    |       | Bits                   |

| ADC Sampling Rate                                  |                           |       | 100  |       | kHz                    |

| POWER INTERFACE                                    |                           |       |      |       |                        |

| Power Supply (VCC_xxx) <sup>2</sup>                |                           | 3.135 | 3.3  | 3.465 | V                      |

| VCC_IF Supply Current                              |                           |       | 60   |       | mA                     |

| VCC_VCO Supply Current                             |                           |       | 80   |       | mA                     |

| VCC_CP Supply Current                              |                           |       | 15   |       | mA                     |

| VCC_REF Supply Current                             |                           |       | 2    |       | mA                     |

| VCC_SYN Supply Current                             |                           |       | 100  |       | mA                     |

| VCC_SPI Supply Current                             |                           |       | 3.5  |       | mA                     |

analog.com Rev. B | 3 of 40

## **SPECIFICATIONS**

Table 1. (Continued)

| Parameter               | Test Conditions/Comments | Min | Тур | Max | Unit |

|-------------------------|--------------------------|-----|-----|-----|------|

| VCC2RF Supply Current   |                          |     | 80  |     | mA   |

| VCC1RF Supply Current   |                          |     | 40  |     | mA   |

| VCC Total Current       |                          |     | 381 |     | mA   |

| Total Power Dissipation |                          |     |     | 1.7 | W    |

| Mute Time               |                          |     |     | 15  | μs   |

| Unmute Time             |                          |     |     | 15  | μs   |

$<sup>^{\</sup>rm 1}~$  dB/20 MHz is gain flatness over 20 MHz bandwidth.

analog.com Rev. B | 4 of 40

$<sup>^2 \ \ \</sup>mathsf{VCC\_xxx} = \mathsf{VCC\_IF} = \mathsf{VCC\_VCO} = \mathsf{VCC\_CP} = \mathsf{VCC\_REF} = \mathsf{VCC\_SYN} = \mathsf{VCC\_SPI} = \mathsf{VCC2RF} = \mathsf{VCC1RF} = 3.3 \ \mathsf{V}.$

#### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                                          | Rating          |

|--------------------------------------------------------------------|-----------------|

| Supply Voltage                                                     |                 |

| VCC_IF, VCC_VCO, VCC_REF, VCC_CP, VCC_SYN, VCC_SPI, VCC2RF, VCC1RF | 4.3 V           |

| IF Input Power                                                     | 5 dBm           |

| Reference Clock Input Power                                        | 12 dBm          |

| Junction Temperature                                               | 125°C           |

| Moisture Sensitivity Level (MSL) <sup>1</sup>                      | 3               |

| Peak Reflow Temperature                                            | 260°C           |

| Operating Case Temperature Range                                   | -40°C to +85°C  |

| Storage Temperature Range                                          | −55°C to +125°C |

| ESD Sensitivity                                                    |                 |

| Human Body Model (HBM)                                             | 1500 V          |

| Field Induced Charged Device Model (FICDM)                         | 250 V           |

Based on IPC/JEDEC J-STD-20 MSL classifications.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the junction to ambient (or die to ambient) thermal resistance measured in a one cubic foot sealed enclosure, and  $\theta_{JC}$  is the junction to case (or die to package) thermal resistance.

Table 3. Thermal Resistance

| Package Type         | $\theta_{JA}^{1}$ | θ <sub>JC</sub> <sup>1, 2</sup> | Unit |

|----------------------|-------------------|---------------------------------|------|

| CP-40-7 <sup>1</sup> | 30.7              | 1.1                             | °C/W |

- The thermal impedance simulated values are based on a JEDEC 2S2P test board with 6 mm × 6 mm thermal vias. Refer to JEDEC standard JESD51-2 for additional information.

- The cold plate of the θ<sub>JC</sub> bottom is attached to the bottom side of the PCB using a 100 μm thermal interface material (TIM) (3.56 W/mK).

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 5 of 40

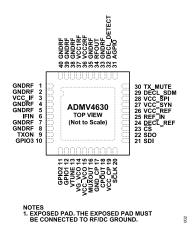

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

Table 4. Pin Function Descriptions

| Pin No.               | Mnemonic | Description                                                                                                                                                                      |

|-----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 5, 7, 8, 33, | GNDRF    | Grounds. Connect these pins to a low impedance ground plane.                                                                                                                     |

| 35, 38, 39, 40        |          |                                                                                                                                                                                  |

| 3                     | VCC_IF   | 3.3 V Power Supply Connections for IF Section. Decouple the VCC_IF pin with 10 pF and 1000 pF as close as possible to the pin.                                                   |

| 6                     | IFIN     | IF Inputs. This pin is internally dc grounded and must be ac-coupled.                                                                                                            |

| 9                     | TXON     | Power-Up Pin for Transmitter Chip. Pull the TXON pin to a logic high level in normal operation. Driving the TXON pin to a logic low level disables the chip.                     |

| 10                    | GPIO3    | General-Purpose Input/Output (GPIO). This pin provides additional digital control line and can be configured to be an input or output, high (3.3 V) or low logic level.          |

| 11                    | GPIO2    | GPIO. This pin provides an additional digital control line and can be configured to be an input or output, high (3.3 V) or low logic level.                                      |

| 12                    | GPIO1    | GPIO. This pin provides an additional digital control line and can be configured to be an input or output, high (3.3 V) or low logic level.                                      |

| 13                    | VTUNE    | Voltage Control Oscillator (VCO), Pin Tuning Voltage. This pin is driven by the output of the loop filter.                                                                       |

| 14                    | VG_VCO   | VCO Internal Node for DC Decoupling. Decouple the VG_VCO pin with 0.1 μF as close as possible to the pin.                                                                        |

| 15                    | VCC_VCO  | 3.3 V Power Supply Connections for VCO. Connect a low noise source power supply to the VCC_VCO pin and decouple this pin with 10 pF and 1000 pF as close as possible to the pin. |

| 16                    | MUXOUT   | Multiplexer Output. See the Register Details section.                                                                                                                            |

| 17                    | GND_CP   | Multiplexer Output Port.                                                                                                                                                         |

| 18                    | CPOUT    | Charge Pump Output Pin.                                                                                                                                                          |

| 19                    | VCC_CP   | 3.3 V Power Supply Connections for Charge Pump. Decouple the VCC_CP pin with 10 pF and 1000 pF as close as possible to the pin.                                                  |

| 20                    | SCLK     | Serial Clock. This pin is the clock input for the SPI interface.                                                                                                                 |

| 21                    | SDI      | Serial Data Input. See the SPI Configuration section.                                                                                                                            |

| 22                    | SDO      | Serial Data Output. See the SPI Configuration section.                                                                                                                           |

| 23                    | CS       | Chip Select Pin.                                                                                                                                                                 |

| 24                    | DECL_REF | Reference Decoupling Pin. Decouple this pin with 0.47 µF and 1000 pF as close as possible to the pin.                                                                            |

| 25                    | REF_IN   | Reference Frequency Input.                                                                                                                                                       |

| 26                    | VCC_REF  | 3.3 V Power Supply Connections for Reference. Decouple the VCC_REF pin with 100 pF and 1000 pF as close as possible to the pin.                                                  |

| 27                    | VCC_SYN  | 3.3 V Power Supply Connections for Synthesizer. Decouple the VCC_SYN pin with 100 pF and 1000 pF as close as possible to the pin.                                                |

| 28                    | VCC_SPI  | 3.3 V Power Supply Connections for SPI Control. Decouple the VCC_SPI pin with 100 pF and 1000 pF as close as possible to the pin.                                                |

| 29                    | DECL_SDM | Internal Low Dropout Regulator (LDO) Decoupling Pin. Decouple the DECL_SDM pin with 0.47 μF and 1000 pF as close as possible to the pin.                                         |

analog.com Rev. B | 6 of 40

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 4. Pin Function Descriptions (Continued)

| Pin No. | Mnemonic    | Description                                                                                                                                                                           |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30      | TX_MUTE     | Transmitter Output Switch Disable Pin. Drive the TX_MUTE pin to a logic low level in normal operation. Pulling the TX_MUTE pin to a logic high level disables the transmitter output. |

| 31      | AGPIO       | Bidirectional Analog GPIO. This pin can be configured to be the input or to be the output of the internal ADC. See the AGPIO Control Register section (Register 0x301).               |

| 32      | DECL_DETECT | Detector Decoupling Pin. Decouple this pin with 0.47 μF as close as possible to the pin.                                                                                              |

| 34      | RFOUT       | RF Output.                                                                                                                                                                            |

| 36      | VCC2RF      | 3.3 V Power Supply Connections for RF Section. Decouple the VCC2RF pin with 10 pF and 1000 pF as close as possible to the pin.                                                        |

| 37      | VCC1RF      | 3.3 V Power Supply Connections for RF Section. Decouple the VCC1RF pin with 10 pF and 1000 pF as close as possible to the pin.                                                        |

|         | EPAD        | Exposed Pad. The exposed pad must be connected to RF/dc ground.                                                                                                                       |

analog.com Rev. B | 7 of 40

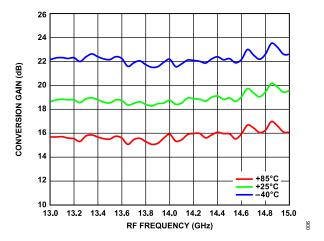

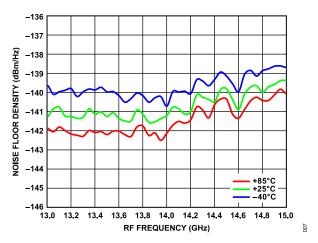

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

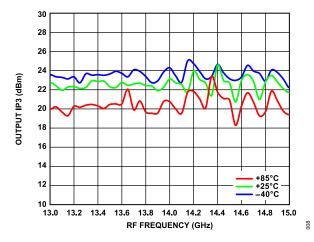

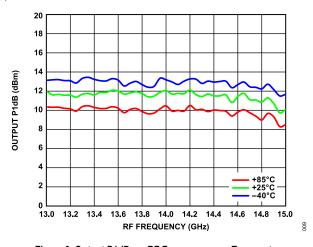

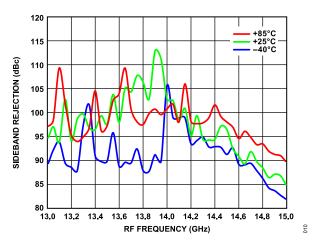

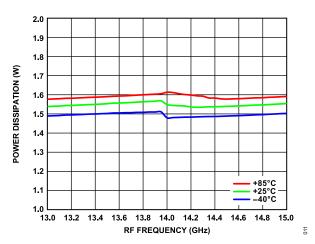

## MINIMUM ATTENUATION PERFORMANCE: DSA (REGISTER 0X300) = 31

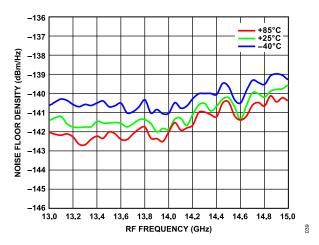

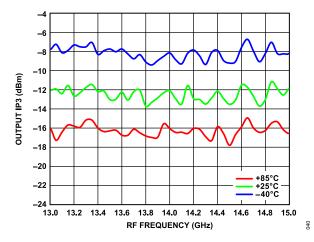

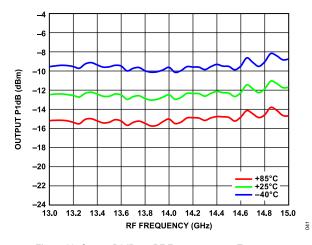

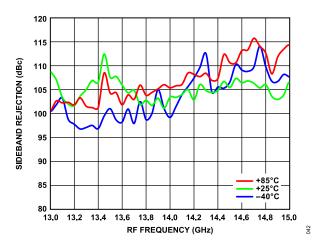

T<sub>A</sub> = 25°C, IF = 4 GHz, VCC = 3.3 V, clock reference input power = 3 dBm, upper sideband selected, unless otherwise noted.

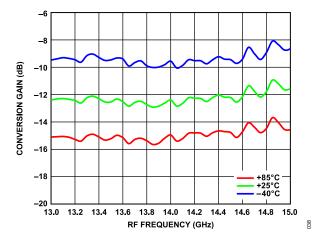

Figure 3. Conversion Gain vs. RF Frequency over Temperature

Figure 4. Noise Floor Density vs. RF Frequency over Temperature

Figure 5. Output IP3 vs. RF Frequency over Temperature

Figure 6. Output P1dB vs. RF Frequency over Temperature

Figure 7. Sideband Rejection vs. RF Frequency over Temperature

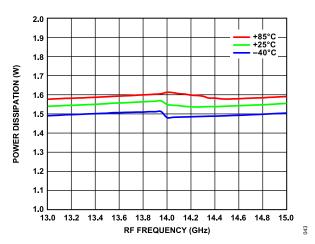

Figure 8. Power Dissipation vs. RF Frequency over Temperature

analog.com Rev. B | 8 of 40

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

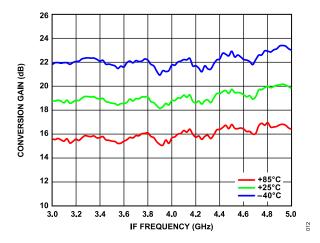

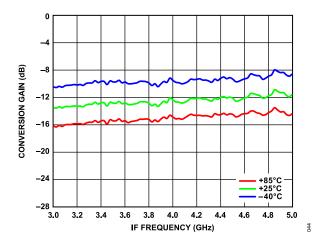

Figure 9. Conversion Gain vs. IF Frequency over Temperature

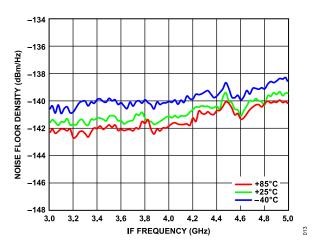

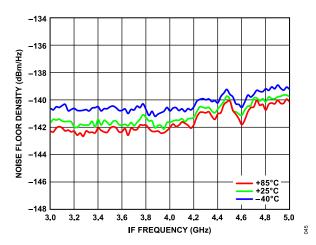

Figure 10. Noise Floor Density vs. IF Frequency over Temperature

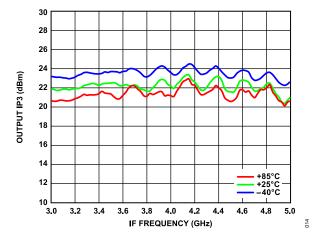

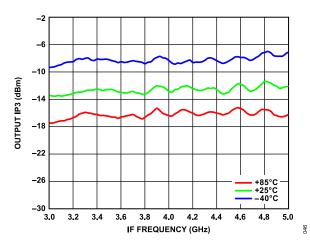

Figure 11. Output IP3 vs. IF Frequency over Temperature

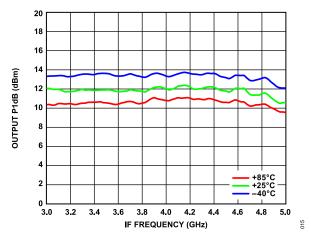

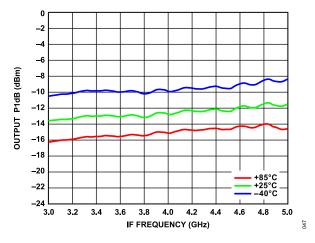

Figure 12. Output P1dB vs. IF Frequency over Temperature

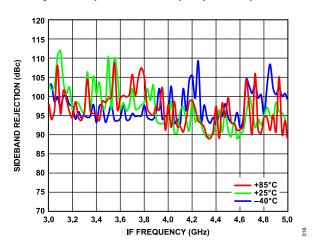

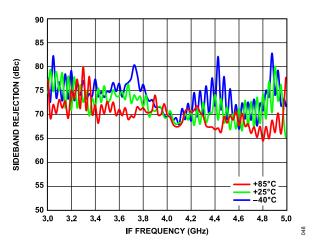

Figure 13. Sideband Rejection vs. IF Frequency over Temperature

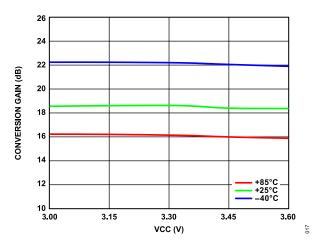

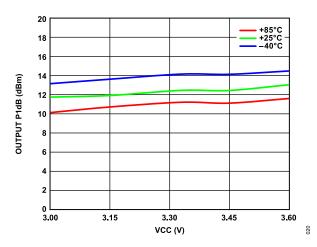

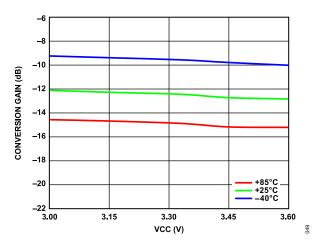

Figure 14. Conversion Gain vs. VCC over Temperature

analog.com Rev. B | 9 of 40

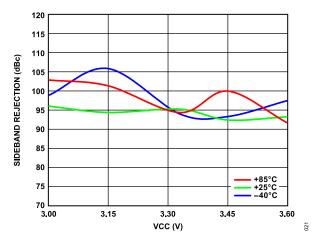

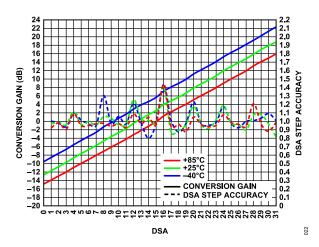

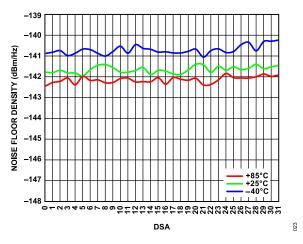

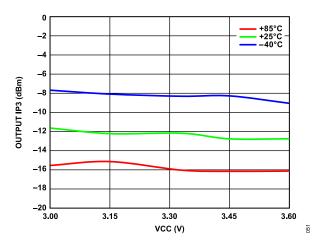

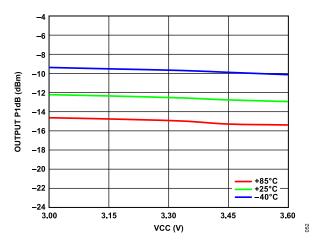

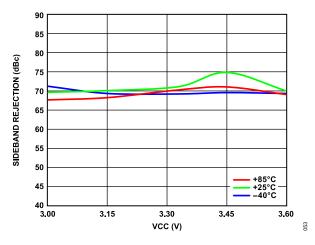

#### TYPICAL PERFORMANCE CHARACTERISTICS

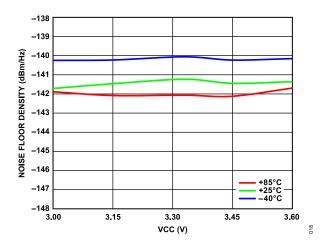

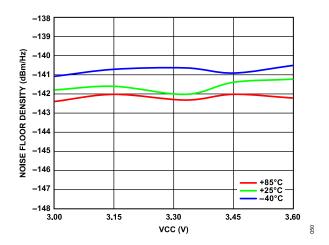

Figure 15. Noise Floor Density vs. VCC over Temperature

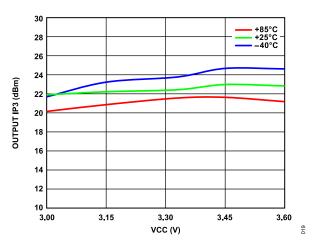

Figure 16. Output IP3 vs. VCC over Temperature

Figure 17. Output P1dB vs. VCC over Temperature

Figure 18. Sideband Rejection vs. VCC over Temperature

Figure 19. Conversion Gain and DSA Step Accuracy vs. DSA over Temperature

Figure 20. Noise Floor Density vs. DSA over Temperature

analog.com Rev. B | 10 of 40

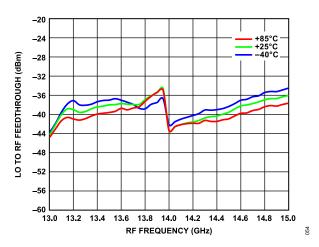

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

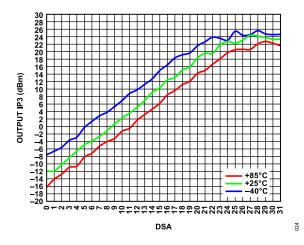

Figure 21. Output IP3 vs. DSA over Temperature

Figure 22. Output P1dB vs. DSA over Temperature

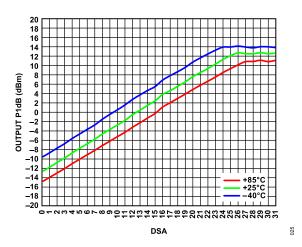

Figure 23. Sideband Rejection vs. DSA over Temperature

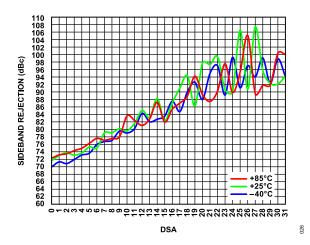

Figure 24. LO to RF Feedthrough vs. RF Frequency over Temperature

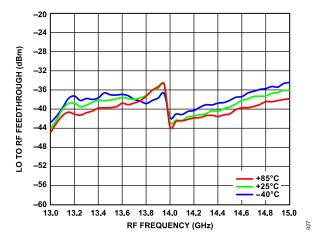

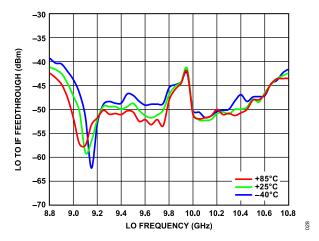

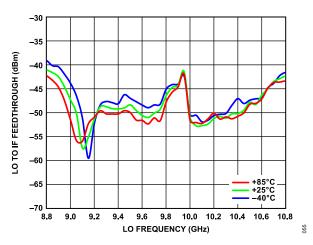

Figure 25. LO to IF Feedthrough vs. LO Frequency over Temperature

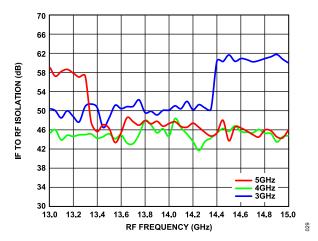

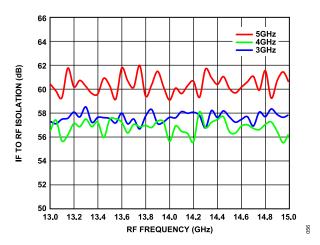

Figure 26. IF to RF Isolation vs. RF Frequency, IF = 3 GHz, 4 GHz, and 5 GHz

analog.com Rev. B | 11 of 40

#### TYPICAL PERFORMANCE CHARACTERISTICS

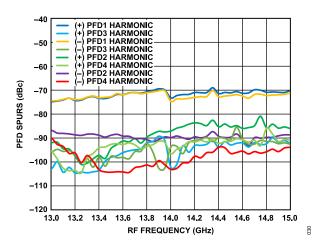

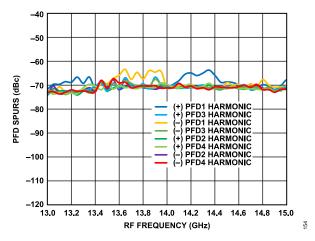

Figure 27. Phase Frequency Detector (PFD) Spurs vs. RF Frequency over Temperature

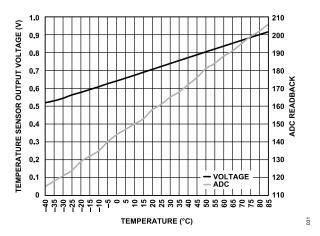

Figure 28. Temperature Sensor Output Voltage and ADC Readback vs.

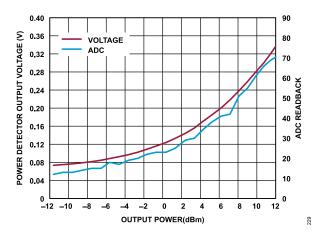

Temperature, LO Frequency = 10 GHz

Figure 29. Power Detector Output Voltage and ADC Readback vs. Output Power, LO Frequency = 10 GHz

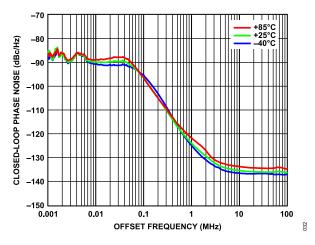

Figure 30. Closed-Loop Phase Noise vs. Offset Frequency over Temperature, LO = 10 GHz

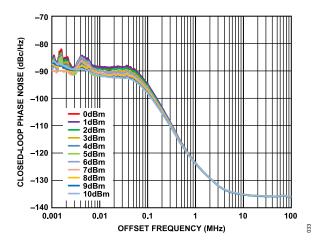

Figure 31. Closed-Loop Phase Noise vs. Offset Frequency over Reference Input Power

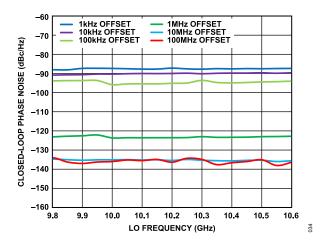

Figure 32. Closed-Loop Phase Noise vs. LO Frequency over Offset Frequency

analog.com Rev. B | 12 of 40

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

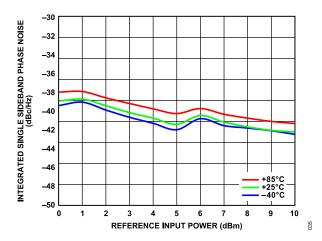

Figure 33. Integrated Single Sideband Phase Noise vs. Reference Input Power over Temperature, 1 kHz to 125 MHz

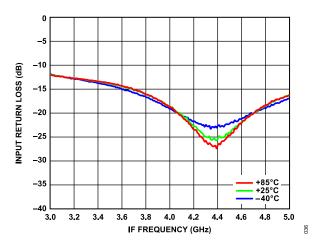

Figure 34. Input Return Loss vs. IF Frequency over Temperature

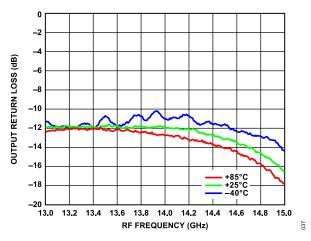

Figure 35. Output Return Loss vs. RF Frequency over Temperature

analog.com Rev. B | 13 of 40

#### TYPICAL PERFORMANCE CHARACTERISTICS

## MAXIMUM ATTENUATION PERFORMANCE: DSA (REGISTER 0X300) = 0

T<sub>A</sub> = 25°C, IF = 4 GHz, VCC = 3.3 V, clock reference input power = 3 dBm, and upper sideband selected, unless otherwise noted.

Figure 36. Conversion Gain vs. RF Frequency over Temperature

Figure 37. Noise Floor Density vs. RF Frequency over Temperature

Figure 38. Output IP3 vs. RF Frequency over Temperature

Figure 39. Output P1dB vs. RF Frequency over Temperature

Figure 40. Sideband Rejection vs. RF Frequency over Temperature

Figure 41. Power Dissipation vs. RF Frequency over Temperature

analog.com Rev. B | 14 of 40

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 42. Conversion Gain vs. IF Frequency over Temperature

Figure 43. Noise Floor Density vs. IF Frequency over Temperature

Figure 44. Output IP3 vs. IF Frequency over Temperature

Figure 45. Output P1dB vs. IF Frequency over Temperature

Figure 46. Sideband Rejection vs. IF Frequency over Temperature

Figure 47. Conversion Gain vs. VCC Frequency over Temperature

analog.com Rev. B | 15 of 40

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 48. Noise Floor Density vs. VCC over Temperature

Figure 49. Output IP3 vs. VCC over Temperature

Figure 50. Output P1dB vs. VCC over Temperature

Figure 51. Sideband Rejection vs. VCC over Temperature

Figure 52. LO to RF Feedthrough vs. RF Frequency over Temperature

Figure 53. LO to IF Feedthrough vs. LO Frequency over Temperature

analog.com Rev. B | 16 of 40

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 54. IF to RF Isolation vs. RF Frequency, IF = 3 GHz, 4 GHz, and 5 GHz

Figure 55. PFD Spurs vs. RF Frequency over Temperature, Measured from the RF Output Power Level

analog.com Rev. B | 17 of 40

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

#### **SPURIOUS PERFORMANCE**

$T_A$  = 25°C, IF = 4 GHz, VCC = 3.3 V, minimum attenuation (DSA = 31), clock reference input power = 3 dBm, and upper sideband is selected. Mixer spurious products are measured in dBc from the RF output power level. Spur values are (M × IF) + (N × LO).

# M × N Spurious Outputs, RF = 14 GHz, LO = 10 GHz

|          |   |      | N × LO |      |      |      |      |

|----------|---|------|--------|------|------|------|------|

|          |   | 0    | 1      | 2    | 3    | 4    | 5    |

|          | 0 | N/A  | 40     | 35   | ≥100 | ≥100 | ≥100 |

|          | 1 | 77   | 0      | 94   | ≥100 | ≥100 | ≥100 |

| M × IF   | 2 | ≥100 | 92     | 78   | ≥100 | ≥100 | ≥100 |

| IVI × IF | 3 | 54   | ≥100   | ≥100 | ≥100 | ≥100 | ≥100 |

|          | 4 | 56   | 75     | ≥100 | ≥100 | ≥100 | ≥100 |

|          | 5 | 34   | ≥100   | ≥100 | ≥100 | ≥100 | ≥100 |

## M × N Spurious Outputs, RF = 14.25 GHz, LO = 10.25 GHz

|          |   | N×LO |      |      |      |      |      |

|----------|---|------|------|------|------|------|------|

|          |   | 0    | 1    | 2    | 3    | 4    | 5    |

|          | 0 | N/A  | 40   | 35   | 98   | ≥100 | ≥100 |

|          | 1 | 77   | 0    | 95   | ≥100 | ≥100 | ≥100 |

| M × IF   | 2 | ≥100 | 96   | 81   | ≥100 | ≥100 | ≥100 |

| IVI ^ IF | 3 | 96   | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 |

|          | 4 | 92   | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 |

|          | 5 | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 |

## M × N Spurious Outputs, RF = 14.5 GHz, LO = 10.5 GHz

|          |   | N × LO |      |      |      |      |      |

|----------|---|--------|------|------|------|------|------|

|          |   | 0      | 1    | 2    | 3    | 4    | 5    |

|          | 0 | N/A    | 38   | 34   | ≥100 | ≥100 | ≥100 |

|          | 1 | 77     | 0    | ≥100 | ≥100 | ≥100 | ≥100 |

| M × IF   | 2 | ≥100   | 99   | 86   | ≥100 | ≥100 | ≥100 |

| IVI ^ IF | 3 | 96     | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 |

|          | 4 | 87     | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 |

|          | 5 | ≥100   | ≥100 | ≥100 | ≥100 | ≥100 | ≥100 |

analog.com Rev. B | 18 of 40

#### THEORY OF OPERATION

#### REFERENCE INPUT STAGE

The reference input stage is shown in Figure 56 and can be driven by an external singled-ended 25 MHz source. Ensure the external dc block is used at the reference input.

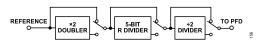

## REFERENCE DOUBLER, R COUNTER, AND REFERENCE DIVIDE BY 2

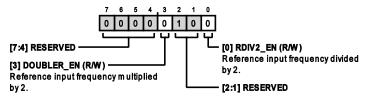

There is an internal reference multiply by 2 block (×2 doubler, see Figure 56) that generates higher phase frequency detector frequencies (f<sub>PFD</sub>). Use the DOUBLER\_EN bit (Register 0x20E, Bit 3) to enable the reference doubler.

There are two frequency dividers: a 5-bit R divider counter (1 to 32 allowed) and a divide by 2 block. These dividers divide the input reference frequency (f<sub>REF</sub>) down to produce a lower f<sub>PFD</sub>. Set the R counter by using the R DIV bit in Register 0x20C, Bits[4:0].

The reference divide by 2 block is enabled by using the RDIV2\_EN in Register 0x20E, Bit 0.

Figure 56. Reference Input Path Block Diagram

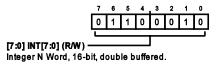

#### INT MODE AND N COUNTER

The ADMV4630 synthesizer operates in INT mode.

The N counter allows a division ratio in the phase-locked loop (PLL) feedback path from the VCO. The division ratio is determined by the INT bit value. The applicable registers for setting the INT bit values are Register 0x200 and Register 0x201.

The INT value, in conjunction with the reference path, can generate VCO frequencies spaced by the resolution of the f<sub>PED</sub>.

The  $f_{PFD}$  is calculated from the reference frequency ( $f_{REF}$ ) and the reference path configuration parameters with the following equation:

$$f_{PFD} = f_{REF} \times \frac{1+D}{R \times (1+T)} \tag{1}$$

where:

D is the reference doubler bit (0 or 1).

*R* is the reference divide ratio of the binary, 5-bit programmable counter (1 to 31).

T is the reference divide by 2 bit (0 or 1).

The VCO frequency (f<sub>VCO</sub>) is calculated with the following equation:

$$f_{VCO} = \frac{f_{LO}}{2} = f_{PFD} \times N \tag{2}$$

where:

$f_{LO}$  is the frequency of the LO driving the mixer. N is the desired value of INT, where INT is the 16-bit integer value (0 to 65,535).

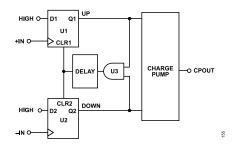

# PHASE FREQUENCY DETECTOR (PFD) AND CHARGE PUMP (CP)

The PFD takes inputs from the R counter and N counter to produce an output that is proportional to the phase and frequency differences between the two counters. This proportional information is output to a CP circuit that generates current to drive an external loop filter, which is then used to appropriately increase or decrease the VTUNE tuning voltage.

Figure 57 shows a simplified schematic of the PFD and CP. U1 and U2 are two D type flip flops and U3 is an AGND gate. Note that the PFD includes a fixed delay element, which is used to ensure that there is no dead zone in the PFD transfer function for consistent reference spur levels.

Figure 57. PFD and CP Simplified Schematic

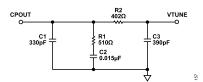

#### LOOP FILTER AND CHARGE PUMP CURRENT

Defining a loop filter for a PLL depends on several dynamics, such as the PFD frequency, the N counter value, the tuning sensitivity characteristics ( $k_{VCO}$ ) of the VCO, and the selected CP current. A lower  $f_{PFD}$  allows the PLL to operate in INT mode, which can eliminate integer boundary spurs at the expense of higher in band phase noise performance. Given the trade-offs, care must be taken with frequency planning and  $f_{PFD}$  selection to ensure the appropriate in band phase noise performance is met with acceptable spur levels for the end application.

The loop filter that is implemented in the EVAL-ADMV4630Z evaluation board is shown in Figure 58. The CP current ( $I_{CP}$ ) is set by Register 0x22E. The default register value is recommended.

For additional guidance with loop filter simulations on the ADMV4630, contact Analog Devices, Inc., for technical support.

Figure 58. Recommended Loop Filter Schematic

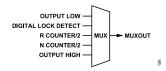

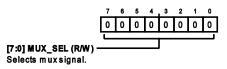

#### **ON-CHIP MUXOUT PIN**

The MUXOUT pin allows access to various internal signals and provides a digital lock detect function. A diagram of the MUXOUT

analog.com Rev. B | 19 of 40

#### THEORY OF OPERATION

pin output is shown in Figure 59. The state of the MUXOUT pin is determined from the MUX SEL value in Register 0x24E.

Figure 59. MUXOUT Pin Diagram

#### ANALOG MUX BLOCK, AGPIO PIN, AND ADC

The on-chip AGPIO pin can be used either as an external analog input or output of the device analog multiplexer (mux) signal. When used as an input, the AGPIO signal is transferred to the on-chip analog multiplexer. The analog mux selects between the temperature sensor, the power detector, and the AGPIO signal. There is an on-chip ADC sampling the signals from analog mux.

To enable the ADC to sample the analog mux signal, take the following steps:

- 1. Make sure the reference input is fed to the ADMV4630.

- 2. Set Register 0x301, Bits[2:0] to 0, 110, or 111 to select between the temperature sensor, the power detector, or the AGPIO signal as the analog mux output. If the AGPIO signal is selected to sample the ADC, set Register 0x301, Bit 3 to 1. Setting this bit sets AGPIO as the external signal input.

- **3.** Set Register 0x302, Bits[3:0] to 0x00 to disable the ADC log scale and reset ADC.

- Set Register 0x302 Bits[1:0] to 0x03 to enable and start ADC sampling.

- 5. Wait for 1 ms.

- 6. Set Register 0x302, Bit 1 to 0.

- 7. Read the ADC value from Register 0x304.

- **8.** Set Register 0x302, Bits[1:0] to 0x00 to turn off the ADC.

The default ADC input voltage range is 0 V to 1.1 V. If a higher input range is required, set Register 0x302, Bit 2 to 1 to halve the input voltage before sampling. The voltage range is then 0 V to 2.2 V.

Enable or disable the ADC output log scale by setting Register 0x302, Bit 3 to 1 or 0.

The AGPIO pin can also be used as an output to transfer the analog mux signal to the AGPIO pin. Take the following steps to set the AGPIO pin as the output:

- 1. Set Register 0x301, Bit 3 to 0 to set the AGPIO pin as the output.

- Set the Register 0x301, Bits[2:0] value to 0 or 110 to set either the temperature sensor or the power detector as the analog mux output.

- 3. Set Register 0x302, Bit 0 to 0 to turn off the ADC.

#### **GPIOX PINS**

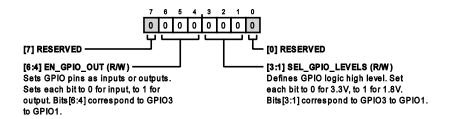

There are three GPIOx pins, where x is 1, 2, or 3, for input/output control. Use Register 0x307 to set the GPIO settings and see the Register Details section for more information.

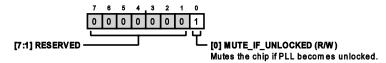

# DIGITAL LOCK DETECT AND MUTE\_IF\_UNLOCK BIT

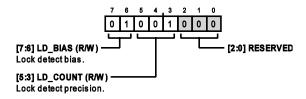

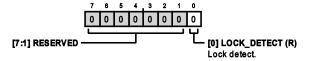

The digital lock detect function that is output on the MUXOUT pin has two adjustable settings in Register 0x214. The first setting, LD\_BIAS, adjusts an internal precision window and the second setting, LD\_COUNT, adjusts the consecutive cycle count to declare the PLL lock. It is recommended to keep the default register value for these adjustable settings. The lock detect status can also be obtained from Register 0x24D, Bit 0.

The MUTE\_IF\_UNLOCK bit (Register 0x103, Bit 0) provides the function to mute the output if the PLL is unlocked. Set this bit to 1 to enable the mute function.

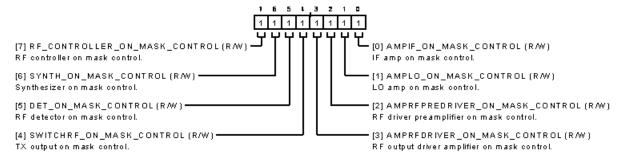

## SIGNAL CHAIN BIAS, MASK, TX\_MUTE PIN, AND TXON PIN

TXON and TX\_MUTE are two on-chip pins. These pins are signal masks commanding the chip to block or enable certain stages. These two pins can be pulled to high (3.3 V) or low (ground). Use Register 0x101, mute mask control, and Register 0x102, on mask control, to determine which stages in the signal path the two pins mask.

Register 0x100 (bias control), Register 0x101 (mute mask control), and Register 0x102 (on mask control) control the on and off status for each stage in the signal path.

Register 0x100 is a bias control register. Set each bit in this register to 1 or 0 to enable or disable the corresponding stage bias.

Register 0x101 is a mute mask control register. Set each bit in this register to 1 to allow the TX\_MUTE pin to mask the corresponding stage.

For example, when the LO amplifier mute mask control bit is on (Bit 1 in Register 0x101 set to 1) and the TX\_MUTE pin on the chip is pulled to high, the LO amplifier is blocked.

Table 5 is the truth table detailing how the TX\_MUTE pin and mute mask control register work together to block signal stages. Note that the MUTE\_IF\_UNLOCKED bit, (Register 0x103, Bit 0) has the same muting effect as the TX\_MUTE pin when enabled.

Register 0x102 is an on mask control register. Set each bit in this register to 1 to allow the TXON pin to mask the corresponding stage. Note that for the TXON pin to work, the corresponding stage bias control in Register 0x100 must be on and the TX\_MUTE pin and mute mask control must be disabled.

For example, when the LO amplifier on mask control bit is on by setting Register 0x102, Bit 1 to 1, and the on-chip TXON pin is pulled low, the LO amplifier is blocked.

analog.com Rev. B | 20 of 40

#### THEORY OF OPERATION

Table 6 is the truth table detailing how the TXON pin and on mask control register work together to block the signal stages.

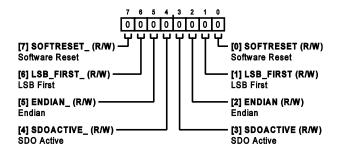

#### **SPI CONFIGURATION**

The ADMV4630 SPI configures the device for specific functions or operations via the 4-pin SPI port. This interface provides users with added flexibility and customization. The SPI consists of the following four control lines: SCLK, SDI, SDO, and  $\overline{\text{CS}}$ . The ADMV4630 protocol consists of a write or read bit, followed by 15 register address bits and 8 data bits. The address field and data field are organized LSB first and end with the MSB.

Set the MSB to 0 for a write operation and set the MSB to 1 for a read operation.

The write cycle sampling must be performed on the rising edge of the SCLK control line. The 24 bits of the serial write address and data are shifted in on the SDI control line. The ADMV4630 input logic level for the write cycle supports a 3.3 V interface.

For a read cycle, the read/write (R/W) bit and the 15 bits of address shift in on the rising edge of the SCLK pin on the SDI pin. Then, eight bits of serial read data shift out on the SDO pin LSB first on the falling edge of SCLK. The output logic level for a read cycle is 3.3 V. The output drivers of the SDO are enabled after the last rising edge of SCLK of the instruction cycle and remain active until the end of the read cycle. When the  $\overline{\text{CS}}$  pin is deasserted in a read operation, SDO returns to high impedance until the next read transaction. The  $\overline{\text{CS}}$  pin is active low and must be deasserted at the end of the write or read sequence.

An active low input on the  $\overline{CS}$  pin starts and gates a communication cycle. The  $\overline{CS}$  pin allows multiple devices, not just the ADMV4630, to be used on the same serial communications lines. The SDO pin goes to a high impedance state when the input on the  $\overline{CS}$  pin is high. During the communication cycle, the  $\overline{CS}$  pin must stay low.

The SPI communications protocol follows the Analog Devices SPI standard. For more information, see the ADI-SPI Serial Control Interface Standard (Rev 1.0) guide.

## VCO AUTOCALIBRATION AND AUTOMATIC LEVEL CONTROL

The multicore VCO uses an internal autocalibration and automatic level control (ALC) routine that optimizes the VCO settings for a user defined frequency and locks the PLL after the lower portion of the N counter integer value (Register 0x200) is programmed.

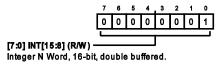

#### **DOUBLE BUFFERED REGISTERS**

Register 0x20C, Register 0x20E, and Register 0x201 are double buffered registers that take effect only after a write to the lower portion of the integer value (Register 0x200). Register 0x200 applies any changes to these double buffered registers and initiates the autocalibration routine.

The following steps describe the recommended programming sequence (users set the values) for double buffered registers:

- 1. Program Register 0x20C.

- 2. Program the RDIV2 EN bit (Register 0x20E, Bit 0).

- 3. Program the DOUBLER EN bit (Register 0x20E, Bit 3).

- 4. Program Register 0x201.

- 5. Program Register 0x200.

#### **INITIALIZATION REGISTERS**

Write the specified code to the following registers to initialize the device with maximum gain and LO at 10 GHz:

- 1. Register 0x000 = 0x99

- **2.** Register 0x000 = 0x18

- **3.** Register 0x103 = 0x00

- **4.** Register 0x22B = 0x0B

- **5.** Register 0x22F = 0x27

- **6.** Register 0x30A = 0x00

- **7.** Register 0x309 = 0x88

- **8.** Register 0x30D = 0x09

- **9.** Register 0x30E = 0x09

- **10.** Register 0x300 = 0x1F

analog.com Rev. B | 21 of 40

## **THEORY OF OPERATION**

Table 5. Signal Stage Status Truth Table Using the TX\_MUTE Pin and Mute Mask Control

| TX_MUTE Pin   <br>MUTE_IF_UNLOCKED <sup>1</sup> | Mute Mask Control<br>Register 0x101 <sup>1</sup> | TXON Pin <sup>1</sup> | On Mask Control Register 0x102 <sup>1</sup> | Bias Enable Control<br>Register 0x100 <sup>1</sup> | Result (1 is On, 0 is Off) <sup>1</sup> |

|-------------------------------------------------|--------------------------------------------------|-----------------------|---------------------------------------------|----------------------------------------------------|-----------------------------------------|

| 1                                               | 1                                                | 0 or 1                | 0 or 1                                      | 0 or 1                                             | 0                                       |

| 1                                               | 0                                                |                       | Controll                                    | ed by TXON pin                                     |                                         |

| 0                                               | 1                                                |                       | Controll                                    | ed by TXON pin                                     |                                         |

<sup>&</sup>lt;sup>1</sup> The 0 and 1 settings apply to all user specified bits in the listed register.

Table 6. Signal Stage Status Truth Table Using the TXON Pin and On Mask Control

| TX_MUTE Pin   <br>MUTE_IF_UNLOCKED Bit<br>(Register 0x103) <sup>1</sup> | Mute Mask Control<br>(Register 0x101) <sup>1</sup> | TXON Pin <sup>1</sup> | On Mask Control<br>(Register 0x102) <sup>1</sup> | Bias Enable Control<br>(Register 0x100) <sup>1</sup> | Result (1 is On, 0 is Off) <sup>1</sup> |

|-------------------------------------------------------------------------|----------------------------------------------------|-----------------------|--------------------------------------------------|------------------------------------------------------|-----------------------------------------|

| 0 or 1                                                                  | 0                                                  | 0 or 1                | 0                                                | 0                                                    | 0                                       |

| 0 or 1                                                                  | 0                                                  | 0 or 1                | 0                                                | 1                                                    | 1                                       |

| 0 or 1                                                                  | 0                                                  | 0                     | 1                                                | 0 or 1                                               | 0                                       |

| ) or 1                                                                  | 0                                                  | 1                     | 1                                                | 0                                                    | 0                                       |

| ) or 1                                                                  | 0                                                  | 1                     | 1                                                | 1                                                    | 1                                       |

| )                                                                       | 0 or 1                                             | 0 or 1                | 0                                                | 0                                                    | 0                                       |

| )                                                                       | 0 or 1                                             | 0 or 1                | 0                                                | 1                                                    | 1                                       |

| )                                                                       | 0 or 1                                             | 0                     | 1                                                | 0 or 1                                               | 0                                       |

| )                                                                       | 0 or 1                                             | 1                     | 1                                                | 0                                                    | 0                                       |

| )                                                                       | 0 or 1                                             | 1                     | 1                                                | 1                                                    | 1                                       |

<sup>&</sup>lt;sup>1</sup> The 0 and 1 settings apply to all user specified bits in the listed register.

analog.com Rev. B | 22 of 40

## **REGISTER SUMMARY**

Table 7. Register Summary

| Reg   | Name                                   | Bits  | Bit 7                                               | Bit 6                               | Bit 5                             | Bit 4                                  | Bit 3                                          | Bit 2                                         | Bit 1                               | Bit 0                               | Reset | RW  |

|-------|----------------------------------------|-------|-----------------------------------------------------|-------------------------------------|-----------------------------------|----------------------------------------|------------------------------------------------|-----------------------------------------------|-------------------------------------|-------------------------------------|-------|-----|

| 0x000 | SPI_<br>CONFIG_1                       | [7:0] | SOFT-<br>RESET_                                     | LSB_<br>FIRST_                      | ENDIAN_                           | SDO-<br>ACTIVE_                        | SDOACTIVE                                      | ENDIAN                                        | LSB_<br>FIRST                       | SOFT-<br>RESET                      | 0x00  | R/W |

| 0x004 | PRODUCT_<br>ID_L                       | [7:0] |                                                     |                                     |                                   | PRO                                    | DDUCT_ID_L                                     |                                               |                                     |                                     | 0x30  | R   |

| 0x005 | PRODUCT_<br>ID_H                       | [7:0] |                                                     |                                     |                                   | PRO                                    | DUCT_ID_H                                      |                                               |                                     |                                     |       | R   |

| 0x100 | BIAS_<br>CONTROL                       | [7:0] | RF_<br>CONTROLL<br>ER_<br>BIAS_<br>CONTROL          | SYNTH_<br>BIAS_<br>CONTROL          | DET_<br>BIAS_<br>CONTROL          | TXOUTPUT<br>_SWITCH                    | AMPRF-<br>DRIVER_<br>BIAS_<br>CONTROL          | AMPRFPRE-<br>DRIVER_<br>BIAS_<br>CONTROL      | AMPLO_<br>BIAS_<br>CONTROL          | AMPIF_<br>BIAS_<br>CONTROL          | 0xDF  | R/W |

| 0x101 | MUTE_<br>MASK_<br>CONTROL              | [7:0] | RF_<br>CONTROLL<br>ER_<br>MUTE_<br>MASK_<br>CONTROL | SYNTH_<br>MUTE_<br>MASK_<br>CONTROL | DET_<br>MUTE_<br>MASK_<br>CONTROL | SWITCHRF<br>_MUTE_<br>MASK_<br>CONTROL | AMPRF-<br>DRIVER_<br>MUTE_<br>MASK_<br>CONTROL | AMPRFPRE-<br>DRIVER_<br>MUTE_MASK_<br>CONTROL | AMPLO_<br>MUTE_<br>MASK_<br>CONTROL | AMPIF_<br>MUTE_<br>MASK_<br>CONTROL | 0xBF  | R/W |

| 0x102 | ON_MASK_<br>CONTROL                    | [7:0] | RF_<br>CONTROLL<br>ER_<br>ON_MASK_<br>CONTROL       | SYNTH_<br>ON_<br>MASK_<br>CONTROL   | DET_ON_<br>MASK_<br>CONTROL       | SWITCHRF<br>_ON_MASK<br>_CONTROL       | AMPRF-<br>DRIVER_<br>ON_MASK_<br>CONTROL       | AMPRFPRE-<br>DRIVER_<br>ON_MASK_<br>CONTROL   | AMPLO_<br>ON_MASK_<br>CONTROL       | AMPIF_<br>ON_<br>MASK_<br>CONTROL   | 0xFF  | R/W |

| 0x103 | MUTE_<br>UNLOCK                        | [7:0] |                                                     |                                     |                                   | RESERV                                 | ED                                             |                                               | MUTE_<br>  IF_<br>  UNLOCKED        |                                     | 0x01  | R/W |

| 0x200 | INT_L                                  | [7:0] |                                                     |                                     |                                   |                                        | INT[7:0]                                       |                                               |                                     |                                     | 0x90  | R/W |

| 0x201 | INT_H                                  | [7:0] |                                                     |                                     |                                   |                                        | INT[15:8]                                      |                                               |                                     |                                     | 0x01  | R/W |

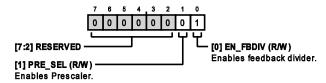

| 0x20B | SYNTH                                  | [7:0] |                                                     |                                     | RI                                | ESERVED                                |                                                |                                               | PRE_SEL                             | EN_FBDIV                            | 0x01  | R/W |

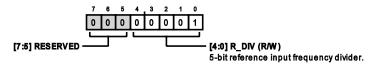

| 0x20C | R_DIV                                  | [7:0] |                                                     | RESERVED                            |                                   |                                        |                                                | R_DIV                                         |                                     |                                     | 0x01  | R/W |

| 0x20E | REFERENCE                              | [7:0] |                                                     | RESE                                | RVED                              |                                        | DOUBLER_<br>EN                                 | RESE                                          | RVED                                | RDIV2_EN                            | 0x04  | R/W |

| 0x214 | LOCK_<br>DETECT_<br>CONFIG             | [7:0] | LD_E                                                | BIAS                                |                                   | LD_COUN <sup>-</sup>                   | ſ                                              |                                               | RESERVED                            |                                     | 0x48  | R/W |

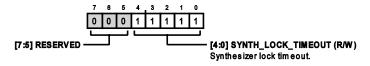

| 0x218 | SYNTH_<br>LOCK_<br>TIMEOUT             | [7:0] |                                                     | RESERVED                            |                                   |                                        | SY                                             | NTH_LOCK_TIME                                 | OUT                                 |                                     | 0x1F  | R/W |

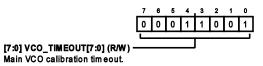

| 0x21C | VCO_<br>TIMEOUT_L                      | [7:0] |                                                     |                                     |                                   | VCO_                                   | TIMEOUT[7:0]                                   |                                               |                                     |                                     | 0x19  | R/W |

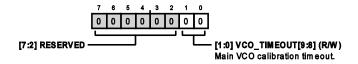

| 0x21D | VCO_<br>TIMEOUT_H                      | [7:0] |                                                     |                                     | RI                                | ESERVED                                |                                                |                                               | VCO_TIM                             | MEOUT[9:8]                          | 0x00  | R/W |

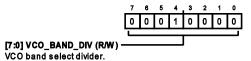

| 0x21E | VCO_<br>BAND_DIV                       | [7:0] |                                                     |                                     |                                   | VCC                                    | D_BAND_DIV                                     |                                               |                                     |                                     | 0x10  | R/W |

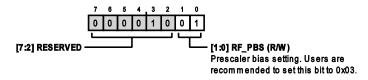

| 0x22B | MULTI_<br>FUNC_<br>SYNTH_<br>CTRL_022B | [7:0] |                                                     |                                     | RI                                | ESERVED                                |                                                |                                               | RF_                                 | _PBS                                | 0x09  | R/W |

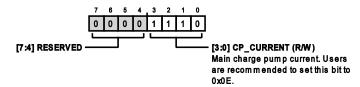

| 0x22E | CP_CURR                                | [7:0] |                                                     | RESE                                | RVED                              |                                        |                                                | CP_CUR                                        | RENT                                |                                     | 0x0E  | R/W |

| 0x22F | BICP                                   | [7:0] |                                                     |                                     |                                   |                                        | BICP                                           |                                               |                                     |                                     | 0x08  | R/W |

| 0x24D | LOCK_<br>DETECT                        | [7:0] |                                                     |                                     |                                   | RESERV                                 |                                                |                                               |                                     | LOCK_<br>DETECT                     | 0x00  | R   |

| 0x24E | MUXOUT                                 | [7:0] |                                                     |                                     |                                   | l                                      | MUX_SEL                                        |                                               |                                     |                                     | 0x00  | R/W |

analog.com Rev. B | 23 of 40

## **REGISTER SUMMARY**

Table 7. Register Summary (Continued)

| Reg   | Name                 | Bits  | Bit 7    | Bit 6      | Bit 5      | Bit 4 | Bit 3                 | Bit 2             | Bit 1         | Bit 0    | Reset | RW  |

|-------|----------------------|-------|----------|------------|------------|-------|-----------------------|-------------------|---------------|----------|-------|-----|

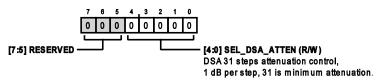

| 0x300 | DSA_<br>CONTROL      | [7:0] |          | RESERVED   |            |       |                       | SEL_DSA_ATTEN     |               |          | 0x00  | R/W |

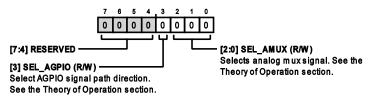

| 0x301 | AGPIO_<br>CONTROL    | [7:0] |          | RESE       | ERVED      |       | SEL_AGPIO             |                   | SEL_AMUX      |          | 0x00  | R/W |

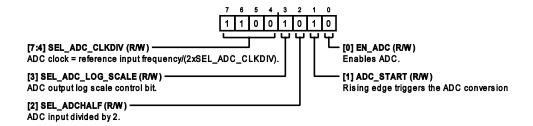

| 0x302 | ADC_<br>CONTROL      | [7:0] |          | SEL_AD0    | C_CLKDIV   |       | SEL_ADC_<br>LOG_SCALE | SEL_ADCHALF       | ADC_<br>START | EN_ADC   | 0xCA  | R/W |

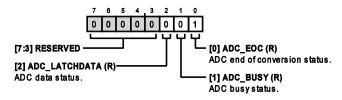

| 0x303 | ADC_<br>STATUS       | [7:0] |          |            | RESERVE    | )     | ·                     | ADC_<br>LATCHDATA | ADC_<br>BUSY  | ADC_EOC  | 0x01  | R   |

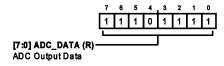

| 0x304 | ADC_DATA             | [7:0] |          |            |            |       | ADC_DATA              |                   |               |          | 0xEF  | R   |

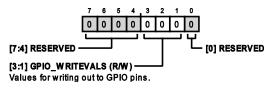

| 0x305 | GPIO_<br>WRITEVALS   | [7:0] |          | RESE       | ERVED      |       |                       | GPIO_WRITEVALS    | 3             | RESERVED | 0x00  | R/W |

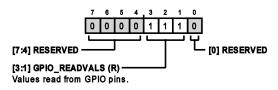

| 0x306 | GPIO_<br>READVALS    | [7:0] |          | RESE       | RVED       |       |                       | GPIO_READVALS     |               | RESERVED | 0x0E  | R   |

| 0x307 | GPIO_<br>CONTROL     | [7:0] | RESERVED |            | EN_GPIO_OL | JT    | S                     | SEL_GPIO_LEVEL    | S             | RESERVED | 0x00  | R/W |

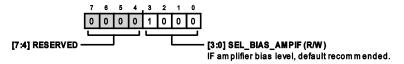

| 0x308 | RFBIAS_<br>CONTROL1  | [7:0] |          | RESE       | RVED       |       |                       | SEL_BIAS          | _AMPIF        |          | 0x08  | R/W |

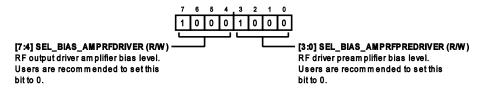

| 0x309 | RFBIAS_<br>CONTROL2  | [7:0] |          | SEL_BIAS_A | MPRFDRIVER | l     |                       | SEL_BIAS_AMPR     | RFPREDRIVER   |          | 0x88  | R/W |

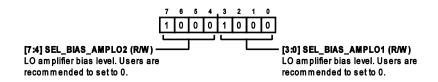

| 0x30A | RFBIAS_<br>CONTROL3  | [7:0] |          | SEL_BIAS   | S_AMPLO2   |       |                       | SEL_BIAS_         | AMPLO1        |          | 0x88  | R/W |

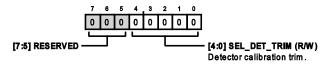

| 0x30C | DETECTOR_<br>CONTROL | [7:0] |          | RESERVED   |            |       | ,                     | SEL_DET_TRIM      |               |          | 0x00  | R/W |

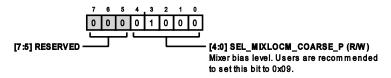

| 0x30D | MIXER_<br>CONTROL1   | [7:0] |          | RESERVED   |            |       | SEL_                  | MIXLOCM_COAR      | SE_P          |          | 0x08  | R/W |

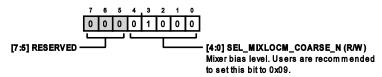

| 0x30E | MIXER_<br>CONTROL2   | [7:0] |          | RESERVED   |            |       | SEL_                  | MIXLOCM_COAR      | SE_N          |          | 0x08  | R/W |

analog.com Rev. B | 24 of 40

#### **REGISTER DETAILS**

#### **SPI CONFIGURATION REGISTER**

Address: 0x000, Reset: 0x00, Name: SPI\_CONFIG\_1

Table 8. Bit Descriptions for SPI\_CONFIG\_1

| Bits | Bit Name   | Description            | Reset | Access |

|------|------------|------------------------|-------|--------|

| 7    | SOFTRESET_ | Software Reset.        | 0x0   | R/W    |

|      |            | 1: reset asserted.     |       |        |

|      |            | 0: reset not asserted. |       |        |

| 6    | LSB_FIRST_ | LSB First.             | 0x0   | R/W    |

|      |            | 0: LSB first.          |       |        |

|      |            | 1: MSB first.          |       |        |

| 5    | ENDIAN_    | Endian.                | 0x0   | R/W    |

|      |            | 0: little endian.      |       |        |

|      |            | 1: big endian.         |       |        |

| 4    | SDOACTIVE_ | SDO Active.            | 0x0   | R/W    |

|      |            | 1: SDO active.         |       |        |

|      |            | 0: SDO inactive.       |       |        |

| 3    | SDOACTIVE  | SDO Active.            | 0x0   | R/W    |

|      |            | 0: SDO inactive.       |       |        |

|      |            | 1: SDO active.         |       |        |

| 2    | ENDIAN     | Endian.                | 0x0   | R/W    |

|      |            | 0: little endian.      |       |        |

|      |            | 1: big endian.         |       |        |

| 1    | LSB_FIRST  | LSB First.             | 0x0   | R/W    |

|      |            | 0: LSB first.          |       |        |

|      |            | 1: MSB first.          |       |        |

| 0    | SOFTRESET  | Software Reset.        | 0x0   | R/W    |

|      |            | 0: reset not asserted. |       |        |

|      |            | 1: reset asserted.     |       |        |

|      |            |                        |       |        |

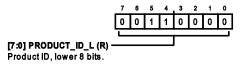

## **Product ID Register (Lower Eight Bits)**

Address: 0x004, Reset: 0x30, Name: PRODUCT\_ID\_L

analog.com Rev. B | 25 of 40

#### **REGISTER DETAILS**

#### Table 9. Bit Descriptions for PRODUCT ID L

| Bits  | Bit Name     | Description               | Reset | Access |

|-------|--------------|---------------------------|-------|--------|

| [7:0] | PRODUCT_ID_L | Product ID, lower 8 bits. | 0x30  | R      |

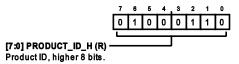

## **Product ID Register (Upper Eight Bits)**

Address: 0x005, Reset: 0x46, Name: PRODUCT\_ID\_H

Table 10. Bit Descriptions for PRODUCT ID H

| Bits  | Bit Name     | Description                | Reset | Access |

|-------|--------------|----------------------------|-------|--------|

| [7:0] | PRODUCT_ID_H | Product ID, higher 8 bits. | 0x46  | R      |

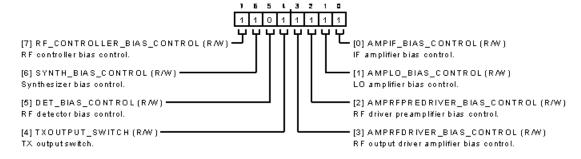

## **Bias Control Register**

Address: 0x100, Reset: 0xDF, Name: BIAS\_CONTROL

Table 11. Bit Descriptions for BIAS CONTROL

| 3its | Bit Name                    | Description                              | Reset | Access |

|------|-----------------------------|------------------------------------------|-------|--------|

| 7    | RF_CONTROLLER_BIAS_CONTROL  | RF controller bias control.              | 0x1   | R/W    |

|      |                             | 0: disables.                             |       |        |

|      |                             | 1: enables.                              |       |        |

|      | SYNTH_BIAS_CONTROL          | Synthesizer bias control.                | 0x1   | R/W    |

|      |                             | 0: disables.                             |       |        |

|      |                             | 1: enables.                              |       |        |

| 5    | DET_BIAS_CONTROL            | RF detector bias control.                | 0x0   | R/W    |

|      |                             | 0: disables.                             |       |        |

|      |                             | 1: enables.                              |       |        |

|      | TXOUTPUT_SWITCH             | TX output switch.                        | 0x1   | R/W    |

|      |                             | 0: disables.                             |       |        |

|      |                             | 1: enables.                              |       |        |

|      | AMPRFDRIVER_BIAS_CONTROL    | RF output driver amplifier bias control. | 0x1   | R/W    |

|      |                             | 0: disables.                             |       |        |

|      |                             | 1: enables.                              |       |        |

|      | AMPRFPREDRIVER_BIAS_CONTROL | RF driver preamplifier bias control.     | 0x1   | R/W    |

analog.com Rev. B | 26 of 40

#### **REGISTER DETAILS**

Table 11. Bit Descriptions for BIAS CONTROL (Continued)

| Bits | Bit Name           | Description                | Reset | Access |

|------|--------------------|----------------------------|-------|--------|

|      |                    | 0: disables.               |       |        |

|      |                    | 1: enables.                |       |        |

| 1    | AMPLO_BIAS_CONTROL | LO amplifier bias control. | 0x1   | R/W    |

|      |                    | 0: disables.               |       |        |

|      |                    | 1: enables.                |       |        |

|      | AMPIF_BIAS_CONTROL | IF amplifier bias control. | 0x1   | R/W    |

|      |                    | 0: disables.               |       |        |

|      |                    | 1: enables.                |       |        |

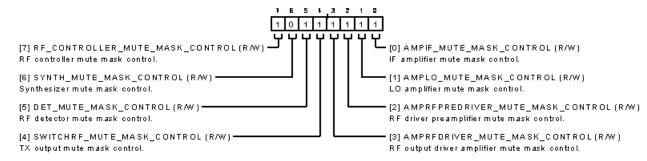

## **Mute Mask Control Register**

Address: 0x101, Reset: 0xBF, Name: MUTE\_MASK\_CONTROL

Table 12. Bit Descriptions for MUTE\_MASK\_CONTROL

| Bits | Bit Name                         | Description                                   | Reset | Access |

|------|----------------------------------|-----------------------------------------------|-------|--------|

| 7    | RF_CONTROLLER_MUTE_MASK_CONTROL  | RF controller mute mask control.              | 0x1   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

| 3    | SYNTH_MUTE_MASK_CONTROL          | Synthesizer mute mask control.                | 0x0   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

| 5    | DET_MUTE_MASK_CONTROL            | RF detector mute mask control.                | 0x1   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

|      | SWITCHRF_MUTE_MASK_CONTROL       | Tx output mute mask control.                  | 0x1   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

|      | AMPRFDRIVER_MUTE_MASK_CONTROL    | RF output driver amplifier mute mask control. | 0x1   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

|      | AMPRFPREDRIVER_MUTE_MASK_CONTROL | RF driver preamplifier mute mask control.     | 0x1   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

|      | AMPLO_MUTE_MASK_CONTROL          | LO amplifier mute mask control.               | 0x1   | R/W    |

|      |                                  | 0: disables mute mask.                        |       |        |

|      |                                  | 1: enables mute mask.                         |       |        |

|      | 1                                | · · · · · · · · · · · · · · · · · · ·         |       |        |

analog.com Rev. B | 27 of 40

#### **REGISTER DETAILS**

Table 12. Bit Descriptions for MUTE MASK CONTROL (Continued)

| Bits | Bit Name                | Description                     | Reset | Access |

|------|-------------------------|---------------------------------|-------|--------|

| 0    | AMPIF_MUTE_MASK_CONTROL | IF amplifier mute mask control. | 0x1   | R/W    |

|      |                         | 0: disables mute mask.          |       |        |

|      |                         | 1: enables mute mask.           |       |        |

## **On Mask Control Register**

Address: 0x102, Reset: 0xFF, Name: ON\_MASK\_CONTROL

Table 13. Bit Descriptions for ON\_MASK\_CONTROL

| Bits | Bit Name                       | Description                                 | Reset | Access |

|------|--------------------------------|---------------------------------------------|-------|--------|

| 7    | RF_CONTROLLER_ON_MASK_CONTROL  | RF controller on mask control.              | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 6    | SYNTH_ON_MASK_CONTROL          | Synthesizer on mask control.                | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 5    | DET_ON_MASK_CONTROL            | RF detector on mask control.                | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 4    | SWITCHRF_ON_MASK_CONTROL       | Tx output on mask control.                  | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 3    | AMPRFDRIVER_ON_MASK_CONTROL    | RF output driver amplifier on mask control. | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 2    | AMPRFPREDRIVER_ON_MASK_CONTROL | RF driver preamplifier on mask control      | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 1    | AMPLO_ON_MASK_CONTROL          | LO amp on mask control.                     | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

| 0    | AMPIF_ON_MASK_CONTROL          | IF amp on mask control.                     | 0x1   | R/W    |

|      |                                | 0: disables on mask.                        |       |        |

|      |                                | 1: enables on mask.                         |       |        |

analog.com Rev. B | 28 of 40

#### **REGISTER DETAILS**

### **Mute IF Unlock Register**

Address: 0x103, Reset: 0x01, Name: MUTE\_UNLOCK

Table 14. Bit Descriptions for MUTE\_UNLOCK

| Bits  | Bit Name         | Description                             | Reset | Access |

|-------|------------------|-----------------------------------------|-------|--------|

| [7:1] | RESERVED         | Reserved.                               | 0x0   | R      |

| 0     | MUTE_IF_UNLOCKED | Mutes the chip if PLL becomes unlocked. | 0x1   | R/W    |

|       |                  | 0: disables.                            |       |        |

|       |                  | 1: enables.                             |       |        |

### **Integer Register (Lower Eight Bits)**

Address: 0x200, Reset: 0x90, Name: INT\_L

Table 15. Bit Descriptions for INT\_L

| Bits  | Bit Name | Description                              | Reset | Access |

|-------|----------|------------------------------------------|-------|--------|

| [7:0] | INT[7:0] | Integer N Word, 16-bit, double buffered. | 0x90  | R/W    |

## **Integer Register (Upper Eight Bits)**

Address: 0x201, Reset: 0x01, Name: INT\_H

Table 16. Bit Descriptions for INT\_H

| Bits  | Bit Name  | Description                              | Reset | Access |

|-------|-----------|------------------------------------------|-------|--------|

| [7:0] | INT[15:8] | Integer N Word, 16-bit, double buffered. | 0x1   | R/W    |

## **Synthesizer Configuration Register**

Address: 0x20B, Reset: 0x01, Name: SYNTH

analog.com Rev. B | 29 of 40

#### **REGISTER DETAILS**

Table 17. Bit Descriptions for SYNTH

| Bits  | Bit Name | Description               | Reset | Access |

|-------|----------|---------------------------|-------|--------|

| [7:2] | RESERVED | Reserved.                 | 0x0   | R      |

| 1     | PRE_SEL  | Enables Prescaler.        | 0x0   | R/W    |

|       |          | 1: enables.               |       |        |

|       |          | 0: disables.              |       |        |

| 0     | EN_FBDIV | Enables feedback divider. | 0x1   | R/W    |

|       |          | 1: enables.               |       |        |

|       |          | 0: disables.              |       |        |

## **Reference Divider Register**

Address: 0x20C, Reset: 0x01, Name: R\_DIV

Table 18. Bit Descriptions for R\_DIV

| Bits  | Bit Name | Description                              | Reset | Access |

|-------|----------|------------------------------------------|-------|--------|

| [7:5] | RESERVED | Reserved.                                | 0x0   | R      |

| [4:0] | R_DIV    | 5-bit reference input frequency divider. | 0x1   | R/W    |

## **Reference Configuration Register**

Address: 0x20E, Reset: 0x04, Name: REFERENCE

Table 19. Bit Descriptions for REFERENCE

| Bits  | Bit Name   | Description                                | Reset | Access |

|-------|------------|--------------------------------------------|-------|--------|

| [7:4] | RESERVED   | Reserved.                                  | 0x0   | R      |

| 3     | DOUBLER_EN | Reference input frequency multiplied by 2. | 0x0   | R/W    |