# Commercial Space Product

## FEATURES

- ▶ 3.3 V supply voltage

- > 20 Mbps maximum data rate

- ▶ No damage or latch-up up to ±15 kV HBM

- Guaranteed fail-safe receiver operation over the entire commonmode range

- Current-limited drivers and thermal shutdown

- Power-up and power-down glitch free driver outputs

- ▶ Low operating current: 370 µA typical in receive mode

- ▶ Compatible with TIA/EIA-485-A specifications

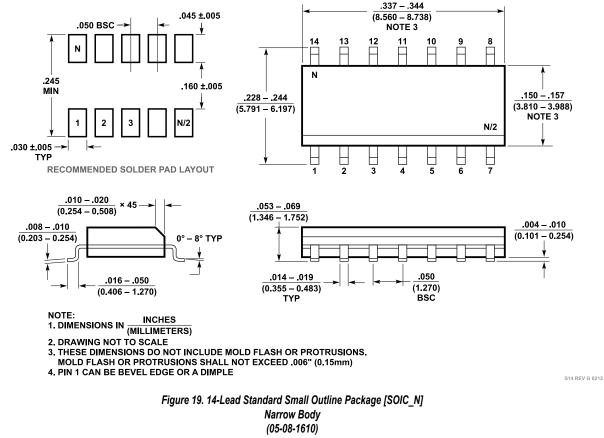

- ► Available in 14-lead SOIC N package

## **COMMERCIAL SPACE FEATURES**

- Supports aerospace applications

- ► Wafer diffusion lot traceability

- Radiation lot acceptance testing: TID

- Radiation benchmark

- Total Ionizing Dose (TID)

- Single Event Effects (SEE)

#### **APPLICATIONS**

- ▶ Low Earth orbit (LEO) space payloads

- Low power RS485/RS422 transceiver

- Level translator

- ▶ Backplane transceiver

#### **GENERAL DESCRIPTION**

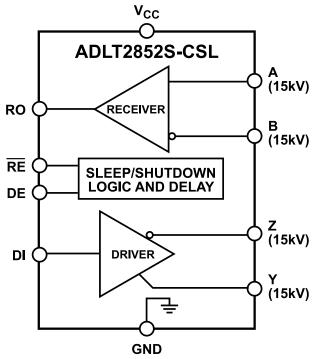

The ADLT2852S-CSL is a low power, 20 Mbps RS485/RS422 transceiver operating on a 3.3 V supply. The receiver has a fail-safe feature that guarantees a high output state under conditions of floating or shorted inputs.

The driver maintains a high output impedance over the entire common-mode range when disabled or when the supply is removed. Excessive power dissipation caused by bus contention or a fault is prevented by current limiting all outputs and by thermal shutdown. Enhanced electrostatic discharge (ESD) protection allows this device to withstand up to  $\pm 15$  kV human body model (HBM) on the transceiver interface pins without latch-up or damage.

The ADLT2852S-CSL is specified over the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range. Additional application and technical information can be found in the Commercial Space Products Program brochure and the LTC2852 data sheet.

# ADLT2852S-CSL

**Data Sheet**

## 3.3 V, 20 Mbps RS485/RS422 Transceiver

## FUNCTIONAL BLOCK DIAGRAM

50

Rev. A

DOCUMENT FEEDBACK

**TECHNICAL SUPPORT**

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                | . 1 |

|-----------------------------------------|-----|

| Commercial Space Features               | . 1 |

| Applications                            | . 1 |

| Functional Block Diagram                | .1  |

| General Description                     | .1  |

| Specifications                          | . 3 |

| Electrical Characteristics              | . 3 |

| Switching Characteristics               | . 4 |

| Radiation Test and Limit Specifications | .4  |

| Absolute Maximum Ratings                | .6  |

| Thermal Resistance                      |     |

|                                         |     |

| Radiation Features                          | 6  |

|---------------------------------------------|----|

| Outgas Testing                              | 6  |

| Electrostatic Discharge (ESD) Ratings       | 6  |

| ESD Caution                                 | 6  |

| Pin Configuration and Function Descriptions | 7  |

| Truth Table                                 | 7  |

| Typical Performance Characteristics         | 8  |

| Test Circuits                               | 10 |

| Outline Dimensions                          | 12 |

| Ordering Guide                              | 12 |

#### **REVISION HISTORY**

#### 12/2024-Rev. 0 to Rev. A

| Changes to Commercial Space Features Section                          | .1 |

|-----------------------------------------------------------------------|----|

| Added Radiation Features Section and Table 7; Renumbered Sequentially | 6  |

## 5/2022—Revision 0: Initial Version

## **SPECIFICATIONS**

## **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 3.3 V. All currents into the device pins are positive, and all currents out of the device pins are negative. All voltages are referenced to device ground, unless otherwise specified. Specifications represent performance at -55°C ≤ T<sub>A</sub> ≤ +125°C, unless otherwise specified.

#### Table 1. Electrical Characteristics

| Parameter                                                                                        | Symbol            | Test Conditions/Comments                                                                                   | Min  | Тур  | Мах             | Unit |

|--------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------|------|------|-----------------|------|

| DRIVER                                                                                           |                   |                                                                                                            |      |      |                 |      |

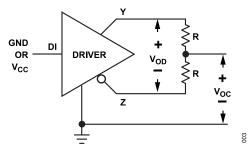

| Differential Driver Output Voltage                                                               | V <sub>OD</sub>   | Resistance (R) = ∞, V <sub>CC</sub> = 3 V (see Figure 12)                                                  |      |      | V <sub>CC</sub> | V    |

|                                                                                                  |                   | $R = 27 \Omega$ , $V_{CC} = 3 V$ (see Figure 12)                                                           | 1.5  |      | V <sub>CC</sub> | V    |

|                                                                                                  |                   | R = 50 Ω, V <sub>CC</sub> = 3.13 V (see Figure 12)                                                         | 2    |      | $V_{CC}$        | V    |

| Difference in Magnitude of Driver Differential Output<br>Voltage for Complementary Output States | $\Delta  V_{OD} $ | R = 27 $\Omega$ or 50 $\Omega$ (see Figure 12)                                                             |      |      | 0.2             | V    |

| Common Mode Output Voltage                                                                       | V <sub>OC</sub>   | R = 27 $\Omega$ or 50 $\Omega$ (see Figure 12)                                                             |      |      | 3               | V    |

| Difference in Magnitude of Driver Common Mode<br>Output Voltage for Complementary Output States  | $\Delta  V_{OC} $ | R = 27 $\Omega$ or 50 $\Omega$ (see Figure 12)                                                             |      |      | 0.2             | V    |

| Three-State (High Impedance) Output Current on Y and Z                                           | I <sub>OZD</sub>  | DE = 0 V, (Y or Z) = -7 V, 12 V                                                                            |      |      | ±50             | μA   |

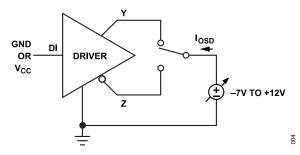

| Maximum Driver Short-Circuit Current                                                             | I <sub>OSD</sub>  | $-7~V \leq$ (Y or Z) $\leq$ +12 V (see Figure 13), applicable only at $T_A$ = 25°C                         |      | ±180 | ±250            | mA   |

|                                                                                                  |                   |                                                                                                            | -250 |      | +300            | mA   |

| RECEIVER                                                                                         |                   |                                                                                                            |      |      |                 |      |

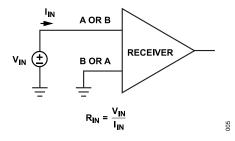

| Input Current (A, B)                                                                             | I <sub>IN</sub>   | DE = TE = 0 V, $V_{CC}$ = 0 V or 3.3 V, input voltage (V <sub>IN</sub> ) = 12 V (see Figure 14)            |      |      | 250             | μA   |

|                                                                                                  |                   | DE = TE = 0 V, $V_{CC}$ = 0 V or 3.3 V, $V_{IN}$ = -7 V, (see Figure 14)                                   | -145 |      |                 | μA   |

| Input Resistance                                                                                 | R <sub>IN</sub>   | $\overline{RE} = V_{CC}$ or 0 V, DE = TE = 0 V, $V_{IN} = -7$ V, $-3$ V, 3 V, 7 V, 12 V<br>(see Figure 14) | 48   | 125  |                 | kΩ   |

| Differential Input Threshold Voltage                                                             | V <sub>TH</sub>   | $-7 \text{ V} \le \text{B} \le +12 \text{ V}$                                                              |      |      | ±0.2            | V    |

| Input Hysteresis                                                                                 | ΔV <sub>TH</sub>  | B = 0 V, applicable only at $T_A = 25^{\circ}C$                                                            |      | 25   |                 | mV   |

| Output High Voltage                                                                              | V <sub>OH</sub>   | Receive output current (I(RO)) = –4 mA, A and B = 200 mV, V <sub>CC</sub> = 3 V                            | 2.4  |      |                 | V    |

| Output Low Voltage                                                                               | V <sub>OL</sub>   | $I(RO) = 4 \text{ mA}, \text{ A and B} = -200 \text{ mV}, \text{ V}_{CC} = 3 \text{ V}$                    |      |      | 0.4             | V    |

| Three-State (High Impedance) Output Current on RO                                                | I <sub>OZR</sub>  | $\overline{RE} = V_{CC}, 0 V \le RO \le V_{CC}$                                                            |      |      | ±1              | μA   |

| Short-Circuit Current                                                                            | I <sub>OSR</sub>  | $0 V \le RO \le V_{CC}$                                                                                    |      |      | ±85             | mA   |

| LOGIC                                                                                            |                   |                                                                                                            |      |      |                 |      |

| Input High Voltage                                                                               | VIH               | V <sub>CC</sub> = 3.6 V                                                                                    | 2    |      |                 | V    |

| Input Low Voltage                                                                                | VIL               | V <sub>CC</sub> = 3 V                                                                                      |      |      | 0.8             | V    |

| Input Current                                                                                    | I <sub>INL</sub>  |                                                                                                            |      | 0    | ±10             | μA   |

| SUPPLIES                                                                                         |                   |                                                                                                            |      |      |                 |      |

| Current in Shutdown Mode                                                                         | I <sub>CCS</sub>  | $DE = 0 V, \overline{RE} = V_{CC}$                                                                         |      | 0    | 15              | μA   |

| Current in Receive Mode                                                                          | I <sub>CCR</sub>  | $DE = 0 V, \overline{RE} = 0 V$                                                                            |      | 370  | 900             | μA   |

| Current in Transmit Mode                                                                         | I <sub>CCT</sub>  | No load, DE = $V_{CC}$ , $\overline{RE} = V_{CC}$                                                          |      | 450  | 1000            | μA   |

| Current with Both Driver and Receiver Enabled                                                    | ICCTR             | No load, DE = $V_{CC}$ , $\overline{RE}$ = 0 V                                                             |      | 450  | 1000            | μA   |

## **SPECIFICATIONS**

## SWITCHING CHARACTERISTICS

$V_{CC}$  = 3.3 V. All currents into the device pins are positive, and all currents out of the device pins are negative. All voltages are referenced to device ground, unless otherwise specified. Specifications represent performance at -55°C ≤ T<sub>A</sub> ≤ +125°C, unless otherwise specified.

#### Table 2. Switching Characteristics

| Parameter                                                          | Symbol                                                                    | Test Conditions/Comments                                                                                                                                                                                          | Min | Тур | Max  | Unit |

|--------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| DRIVER                                                             |                                                                           |                                                                                                                                                                                                                   |     |     |      |      |

| Maximum Data Rate <sup>1</sup>                                     | f <sub>MAX</sub>                                                          |                                                                                                                                                                                                                   | 20  |     |      | Mbps |

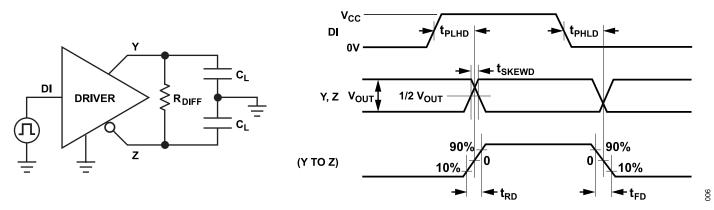

| Input to Output                                                    | t <sub>PLHD</sub> , t <sub>PHLD</sub>                                     | Differential resistance ( $R_{DIFF}$ ) = 54 $\Omega$ , load capacitance ( $C_L$ ) = 100 pF (see Figure 15)                                                                                                        |     | 10  | 50   | ns   |

| Input to Output Difference,  t <sub>PLHD</sub> – t <sub>PHLD</sub> | Δt <sub>PD</sub>                                                          | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                                                                                                       |     | 1   | 6    | ns   |

| Output Y to Output Z                                               | t <sub>skewD</sub>                                                        | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                                                                                                       |     | 1   | ±6   | ns   |

| Rise or Fall Time                                                  | t <sub>RD</sub> , t <sub>FD</sub>                                         | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                                                                                                       |     | 4   | 12.5 | ns   |

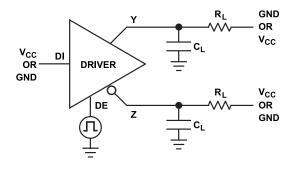

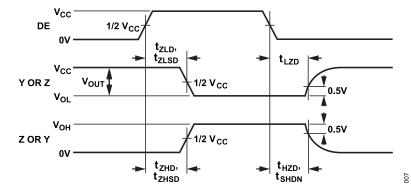

| Enable or Disable Time                                             | $t_{ZLD}, t_{ZHD}, t_{LZD}, t_{HZD}$                                      | Load resistance (R <sub>L</sub> ) = 500 $\Omega$ , C <sub>L</sub> = 50 pF, $\overline{RE}$ = 0 V (see Figure 16)                                                                                                  |     |     | 70   | ns   |

| Enable from Shutdown                                               | t <sub>ZHSD</sub> , t <sub>ZLSD</sub>                                     | $R_L$ = 500 Ω, $C_L$ = 50 pF, $\overline{RE}$ = V <sub>CC</sub> (see Figure 16)                                                                                                                                   |     |     | 8    | μs   |

| Time to Shutdown                                                   | t <sub>SHDN</sub>                                                         | $R_L = 500 \Omega$ , $C_L = 50 pF$ , (DE is low, $\overline{RE} = V_{CC}$ ) or (DE = 0 V, $\overline{RE}$ is high) (see Figure 16)                                                                                |     |     | 100  | ns   |

| RECEIVER                                                           |                                                                           |                                                                                                                                                                                                                   |     |     |      |      |

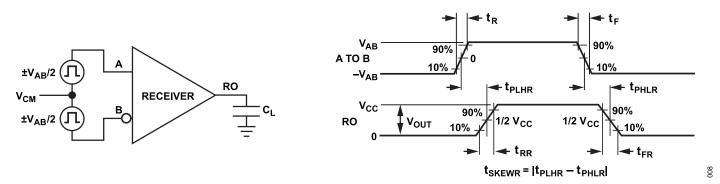

| Input to Output                                                    | t <sub>PLHR</sub> , t <sub>PHLR</sub>                                     | $C_L$ = 15 pF, common-mode voltage (V <sub>CM</sub> ) = 1.5 V, absolute value of A and B voltage ( V <sub>AB</sub>  ) = 1.5 V, rise time (t <sub>R</sub> ) and fall time (t <sub>F</sub> ) < 4 ns (see Figure 17) |     | 50  | 70   | ns   |

| Differential Receiver Skew,  t <sub>PLHR</sub> – t <sub>PHLR</sub> | t <sub>SKEWR</sub>                                                        | C <sub>L</sub> = 15 pF (see Figure 17)                                                                                                                                                                            |     | 1   | 6    | ns   |

| Output Rise or Fall Time                                           | t <sub>RR</sub> , t <sub>FR</sub>                                         | C <sub>L</sub> = 15 pF (see Figure 17)                                                                                                                                                                            |     | 3   | 12.5 | ns   |

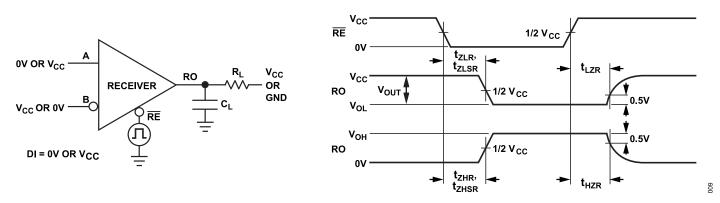

| Enable and Disable                                                 | t <sub>ZLR</sub> , t <sub>ZHR</sub> , t <sub>LZR</sub> , t <sub>HZR</sub> | $R_L$ = 1 k $\Omega$ , $C_L$ = 15 pF, DE = V <sub>CC</sub> (see Figure 18)                                                                                                                                        |     |     | 50   | ns   |

| Enable from Shutdown                                               | t <sub>ZHSR</sub> , t <sub>ZLSR</sub>                                     | $R_L = 1 k\Omega$ , $C_L = 15 pF$ , DE = 0 V (see Figure 18)                                                                                                                                                      |     |     | 8    | μs   |

<sup>1</sup> The maximum data rate is guaranteed by other measured parameters and is not tested directly.

## **RADIATION TEST AND LIMIT SPECIFICATIONS**

Total ionizing dose (TID) testing characterized to 30 krads (20 krads + 50% overstress) with biased annealing at 100°C for 168 hours.

#### Table 3. Electrical Characteristics

| Parameter                                                                                         | Symbol            | Test Conditions/Comments                                                                                    | Min  | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| DRIVER                                                                                            |                   |                                                                                                             |      |     |      |      |

| Difference in Magnitude of Driver Differential Output<br>Voltage for Complementary Output States  | Δ V <sub>OD</sub> | R = 27 $\Omega$ or 50 $\Omega$ (see Figure 12)                                                              |      |     | 0.2  | V    |

| Common-Mode Output Voltage                                                                        | V <sub>OC</sub>   | R = 27 Ω or 50 Ω (see Figure 12)                                                                            |      |     | 3    | V    |

| Difference in Magnitude of Driver Common-Mode Out-<br>put Voltage for Complementary Output States | Δ V <sub>OC</sub> | R = 27 $\Omega$ or 50 $\Omega$ (see Figure 12)                                                              |      |     | 0.2  | V    |

| Three-State (High Impedance) Output Current on Y and Z                                            | I <sub>OZD</sub>  | DE = 0 V, (Y or Z) = -7 V, 12 V                                                                             | -10  |     | +200 | μA   |

| Maximum Driver Short-Circuit Current                                                              | I <sub>OSD</sub>  | $-7 \text{ V} \le (\text{Y or Z}) \le +12 \text{ V}$ (see Figure 13)                                        | -260 |     | +300 | mA   |

| ECEIVER                                                                                           |                   |                                                                                                             |      |     |      |      |

| Input Current (A, B)                                                                              | I <sub>IN</sub>   |                                                                                                             |      |     |      |      |

|                                                                                                   |                   | DE = TE = 0 V, $V_{CC}$ = 0 V or 3.3 V, $V_{IN}$ = 12 V (see Figure 14)                                     |      |     | 135  | μA   |

|                                                                                                   |                   | DE = TE = 0 V, $V_{CC}$ = 0 V or 3.3 V, $V_{IN}$ = -7 V, (see Figure 14)                                    | -105 |     |      | μA   |

| Input Resistance                                                                                  | R <sub>IN</sub>   | RE = V <sub>CC</sub> or 0 V, DE = TE = 0 V, V <sub>IN</sub> = -7 V, -3 V, 3 V, 7 V, 12 V<br>(see Figure 14) | 94   |     |      | kΩ   |

| Differential Input Threshold Voltage                                                              | V <sub>TH</sub>   | $-7 \text{ V} \le \text{B} \le +12 \text{ V}$                                                               | -220 |     | +220 | mV   |

## **SPECIFICATIONS**

#### Table 3. Electrical Characteristics (Continued)

| Parameter                                         | Symbol            | Test Conditions/Comments                                 | Min | Тур | Max  | Unit |

|---------------------------------------------------|-------------------|----------------------------------------------------------|-----|-----|------|------|

| Input Hysteresis                                  | $\Delta V_{TH}$   | B = 0 V                                                  | 20  |     | 40   | mV   |

| Output High Voltage                               | V <sub>OH</sub>   | I(RO) = $-4$ mA, A and B = 200 mV, V <sub>CC</sub> = 3 V | 2.4 |     |      | V    |

| Output Low Voltage                                | V <sub>OL</sub>   | I(RO) = 4 mA, A and B = $-200$ mV, V <sub>CC</sub> = 3 V |     |     | 0.4  | V    |

| Three-State (High Impedance) Output Current on RO | I <sub>OZR</sub>  | $\overline{RE} = V_{CC}, 0 V \le RO \le V_{CC}$          | -1  |     | +1   | μA   |

| Short-Circuit Current                             | I <sub>OSR</sub>  | $0 V \leq RO \leq V_{CC}$                                | -85 |     | +85  | mA   |

| LOGIC                                             |                   |                                                          |     |     |      |      |

| Input High Voltage                                | VIH               | V <sub>CC</sub> = 3.6 V                                  | 2   |     |      | V    |

| Input Low Voltage                                 | V <sub>IL</sub>   | V <sub>CC</sub> = 3 V                                    |     |     | 0.8  | V    |

| Input Current                                     | I <sub>INL</sub>  |                                                          | -10 |     | +10  | μA   |

| SUPPLIES                                          |                   |                                                          |     |     |      |      |

| Current in Shutdown Mode                          | I <sub>CCS</sub>  | $DE = 0 V, \overline{RE} = V_{CC}$                       |     |     | 65   | μA   |

| Current in Receive Mode                           | I <sub>CCR</sub>  | DE = 0 V, RE = 0 V                                       |     |     | 850  | μA   |

| Current in Transmit Mode                          | I <sub>CCT</sub>  | No load, DE = $V_{CC}$ , $\overline{RE}$ = $V_{CC}$      |     |     | 1100 | μA   |

| Current with Both Driver and Receiver Enabled     | I <sub>CCTR</sub> | No load, DE = $V_{CC}$ , $\overline{RE}$ = 0 V           |     |     | 1200 | μA   |

| Parameter                                                          | Symbol                                                                    | Test Conditions/Comments                                                                                                           | Min | Тур | Мах | Unit |

|--------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| DRIVER                                                             |                                                                           |                                                                                                                                    |     |     |     |      |

| Input to Output                                                    | t <sub>PLHD</sub> , t <sub>PHLD</sub>                                     | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                        |     |     | 55  | ns   |

| Input to Output Difference,  t <sub>PLHD</sub> – t <sub>PHLD</sub> | Δt <sub>PD</sub>                                                          | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                        |     |     | 9   | ns   |

| Output Y to Output Z                                               | t <sub>SKEWD</sub>                                                        | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                        |     |     | 6   | ns   |

| Rise or Fall Time                                                  | t <sub>RD</sub> , t <sub>FD</sub>                                         | $R_{DIFF}$ = 54 $\Omega$ , $C_{L}$ = 100 pF (see Figure 15)                                                                        |     |     | 13  | ns   |

| Enable or Disable Time                                             | t <sub>ZLD</sub> , t <sub>ZHD</sub> , t <sub>LZD</sub> , t <sub>HZD</sub> | $R_L$ = 500 Ω, $C_L$ = 50 pF, $\overline{RE}$ = 0 V (see Figure 16)                                                                |     |     | 50  | ns   |

| Enable from Shutdown                                               | t <sub>ZHSD</sub> , t <sub>ZLSD</sub>                                     | $R_L$ = 500 Ω, $C_L$ = 50 pF, $\overline{RE}$ = V <sub>CC</sub> (see Figure 16)                                                    |     |     | 6   | μs   |

| Time to Shutdown                                                   | t <sub>SHDN</sub>                                                         | $R_L = 500 \Omega$ , $C_L = 50 pF$ , (DE is low, $\overline{RE} = V_{CC}$ ) or (DE = 0 V, $\overline{RE}$ is high) (see Figure 16) |     |     | 100 | ns   |

| RECEIVER                                                           |                                                                           |                                                                                                                                    |     |     |     |      |

| Receiver Input to Output                                           | t <sub>PLHR</sub> , t <sub>PHLR</sub>                                     | $C_L$ = 15 pF, $V_{CM}$ = 1.5 V, $ V_{AB} $ = 1.5 V, $t_R$ and $t_F$ < 4 ns (see Figure 17)                                        |     |     | 80  | ns   |

| Differential Receiver Skew,  t <sub>PLHR</sub> – t <sub>PHLR</sub> | t <sub>SKEWR</sub>                                                        | C <sub>L</sub> = 15 pF (see Figure 17)                                                                                             |     |     | 9   | ns   |

| Output Rise or Fall Time                                           | t <sub>RR</sub> , t <sub>FR</sub>                                         | C <sub>L</sub> = 15 pF (see Figure 17)                                                                                             |     |     | 9.5 | ns   |

| Enable and Disable                                                 | t <sub>ZLR</sub> , t <sub>ZHR</sub> , t <sub>LZR</sub> , t <sub>HZR</sub> | $R_L = 1 \text{ k}\Omega$ , $C_L = 15 \text{ pF}$ , DE = $V_{CC}$ (see Figure 18)                                                  |     |     | 50  | ns   |

| Enable from Shutdown                                               | t <sub>ZHSR</sub> , t <sub>ZLSR</sub>                                     | $R_L = 1 k\Omega$ , $C_L = 15 pF$ , DE = 0 V (see Figure 18)                                                                       |     |     | 6   | μs   |

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 5. Absolute Maximum Ratings

| Parameter                                | Rating                              |

|------------------------------------------|-------------------------------------|

| Supply Voltage (V <sub>CC</sub> )        | –0.3 V to +7 V                      |

| Logic Input Voltages (RE, DE, and DI)    | –0.3 V to +7 V                      |

| Interface Input and Output               |                                     |

| A, B, Y, and Z                           | (V <sub>CC</sub> – 15 V) to +15 V   |

| RO Voltage                               | -0.3 V to (V <sub>CC</sub> + 0.3 V) |

| Operating Temperature Range <sup>1</sup> | –55°C to +125°C                     |

| Storage Temperature Range                | –65°C to +150°C                     |

<sup>1</sup> This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Overtemperature protection activates at a junction temperature exceeding 150°C. Continuous operation above the specified maximum operating junction temperature may result in device degradation or failure.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JC}$  is the junction to case thermal resistance.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance.

#### Table 6. Thermal Resistance

| Package Type | θ <sub>JC</sub> | θ <sub>JA</sub> | Unit |

|--------------|-----------------|-----------------|------|

| 05-08-1610   | 37              | 88              | °C/W |

#### **RADIATION FEATURES**

#### Table 7. Radiation Features

| Specification                                                                                   | Value | Unit                    |

|-------------------------------------------------------------------------------------------------|-------|-------------------------|

| Maximum Total Dose Available (Dose Rate = 50<br>rad(Si)/sec to 300 rad(Si)/sec) <sup>1</sup>    | 20    | Krad (Si)               |

| No Single Event Latch-Up (SEL) Occurs at<br>Effective Linear Energy Transfer (LET) <sup>2</sup> | 57.5  | MeV-cm <sup>2</sup> /mg |

Guaranteed by device and process characterization. Email space@analog.com for data available up to 30 Krad (Si)

<sup>2</sup> Limits are characterized at the initial qualification and after any design or process changes that may affect the SEL characteristics but are not production lot tested, unless specified by the customer through the purchase order or contract. For more information on SEE test results, email space@analog.com for further data beyond the published report on ADLT2852S product page.

## OUTGAS TESTING

The criteria used for the acceptance and rejection of materials must be determined by the user and based upon specific component and system requirements. Historically, a total mass loss (TML) of 1.00% and collected volatile condensable material (CVCM) of 0.10% have been used as screening levels for rejection of spacecraft materials.

#### Table 8. Outgas Testing

| Specification (Tested per ASTM E595-15) | Value | Unit |

|-----------------------------------------|-------|------|

| TML                                     | 0.07  | %    |

| CVCM                                    | <0.01 | %    |

| Water Vapor Recovered                   | 0.03  | %    |

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

## ESD Ratings for ADLT2852S-CSL

#### Table 9. ADLT2852S-CSL, 14-Lead SOIC\_N

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±15,000                 | 3B    |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

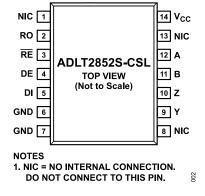

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

#### Table 10. Pin Function Descriptions

| Pin No.  | Mnemonic        | Description                                                                                                                                                                                                                                                          |

|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 8, 13 | NIC             | Not internal connection. Do not connect to this pin.                                                                                                                                                                                                                 |

| 2        | RO              | Receiver Output. If the receiver output is enabled ( $\overline{RE}$ low) and A > B by 200 mV, RO is high. If A < B by 200 mV, RO is low. If the receiver inputs are open, shorted, or terminated without a valid signal, RO is high.                                |

| 3        | RE              | Receiver Enable. A low input enables the receiver. A high input forces the receiver output into a high impedance state.                                                                                                                                              |

| 4        | DE              | Driver Enable. A high input on DE enables the driver. A low input forces the driver outputs into a high impedance state. If RE is high with DE low, the device enters a low power shutdown state.                                                                    |

| 5        | DI              | Driver Input. If the driver outputs are enabled (DE high), a low input on DI forces the driver positive output low and negative output high.<br>A high input on DI, with the driver outputs enabled, forces the driver positive output high and negative output low. |

| 6, 7     | GND             | Ground.                                                                                                                                                                                                                                                              |

| 9        | Y               | Noninverting Driver Output. High impedance when the driver is disabled or unpowered.                                                                                                                                                                                 |

| 10       | Z               | Inverting Driver Output. High impedance when the driver is disabled or unpowered.                                                                                                                                                                                    |

| 11       | В               | Inverting Receiver Input. Impedance is >96 k $\Omega$ when in receive mode or unpowered.                                                                                                                                                                             |

| 12       | A               | Noninverting Receiver Input. Impedance is >96 k $\Omega$ when in receive mode or unpowered.                                                                                                                                                                          |

| 14       | V <sub>CC</sub> | Positive Supply. 3 V $\leq$ V <sub>CC</sub> $\leq$ 3.6 V. Bypass with 0.1 µF ceramic capacitor.                                                                                                                                                                      |

#### **TRUTH TABLE**

#### Table 11. Truth Table

|    | Logic Inputs |            |                 |        |        |

|----|--------------|------------|-----------------|--------|--------|

| DE | RE           | Mode       | Α, Β            | Y, Z   | RO     |

| 0  | 0            | Receive    | R <sub>IN</sub> | Hi-Z   | Driven |

| 0  | 1            | Shutdown   | R <sub>IN</sub> | Hi-Z   | Hi-Z   |

| 1  | 0            | Transceive | R <sub>IN</sub> | Driven | Driven |

| 1  | 1            | Transmit   | R <sub>IN</sub> | Driven | Hi-Z   |

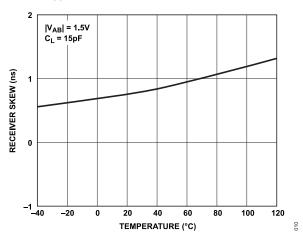

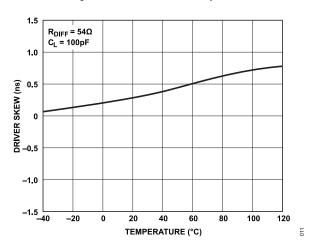

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A$  = 25°C.  $V_{CC}$  = 3.3 V, unless otherwise noted.

Figure 3. Receiver Skew vs. Temperature

Figure 4. Driver Skew vs. Temperature

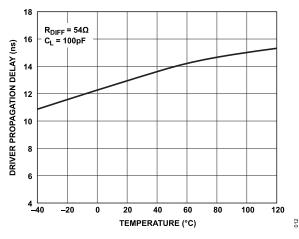

Figure 5. Driver Propagation Delay vs. Temperature

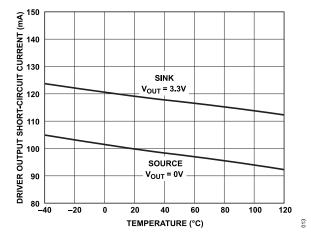

Figure 6. Driver Output Short-Circuit Current vs. Temperature (V<sub>OUT</sub> Is Output Voltage)

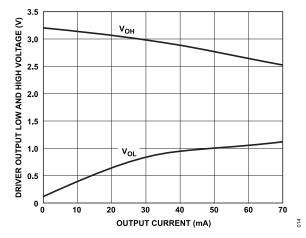

Figure 7. Driver Output Low and High Voltage vs. Output Current

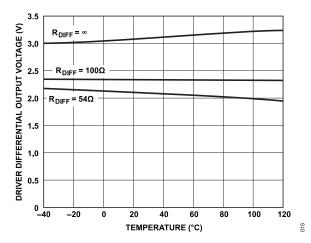

Figure 8. Driver Differential Output Voltage vs. Temperature

## **TYPICAL PERFORMANCE CHARACTERISTICS**

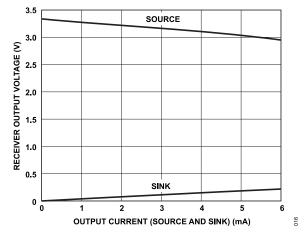

Figure 9. Receiver Output Voltage vs. Output Current (Source and Sink)

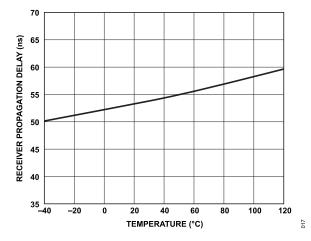

Figure 10. Receiver Propagation Delay vs. Temperature

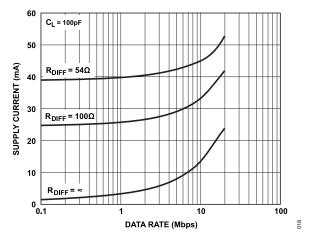

Figure 11. Supply Current vs. Data Rate

## **TEST CIRCUITS**

Figure 12. Driver DC Characteristics

Figure 13. Driver Output Short-Circuit Current

Figure 14. Receiver Input Current and Input Resistance

## **TEST CIRCUITS**

Figure 16. Driver Enable and Disable Timing Measurements

Figure 17. Receiver Propagation Delay Measurements

Figure 18. Receiver Enable and Disable Timing Measurements

## **OUTLINE DIMENSIONS**

Dimensions shown in inches and (millimeters)

Updated: May 06, 2022

#### **ORDERING GUIDE**

| Model           | Temperature Range | Package Description     | Packing Quantity | Package Option |

|-----------------|-------------------|-------------------------|------------------|----------------|

| ADLT2852MPS-CSL | -55°C to +125°C   | 14-Lead SOIC_N, 150 Mil | Tube, 55         | 05-08-1610     |

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

ADLT2852MPS-CSL