# ADATE320

# 1.25 GHz Dual Integrated DCL with PPMU, Level Setting DACs, and On-Chip Calibration Registers

### **FEATURES**

- 1.25 GHz, 2.5 Gbps data rate

- 3-level driver with high-Z and reflection clamps

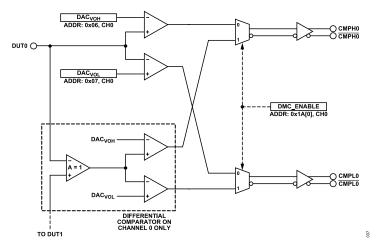

- Window and differential comparators

- ±25 mA active load

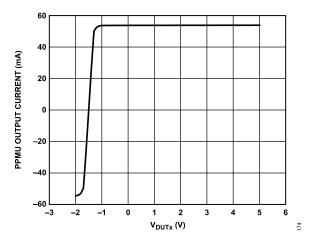

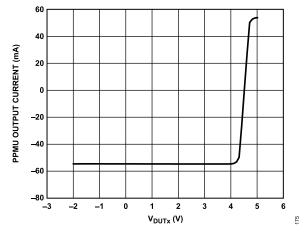

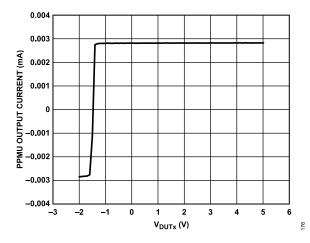

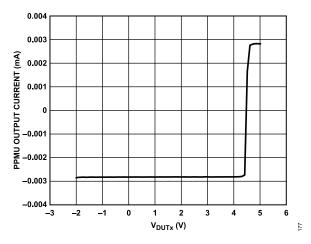

- ▶ Per pin parametric measurement unit (PMU) with a −1.5 V to +4.5 V range

- Low leakage mode (typically <5 nA)</p>

- Integrated 16-bit DACs with offset and gain correction

- ▶ 1.2 W power dissipation per channel (ADATE320)

- ▶ 1.3 W power dissipation per channel (ADATE320-1)

- Driver

- ▶ Voltage range: -1.5 V to +4.5 V

- Precision trimmed termination: 50.0 Ω

- ▶ Unterminated swing: 50 mV minimum to 6.0 V maximum

- ▶ 400 ps minimum pulse width, 1.0 V programmed swing

- ▶ 25 ps deterministic jitter

- Comparator

- Differential and single-ended window modes

- 100 ps equivalent input rise/fall time (ERT/EFT)

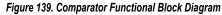

- ▶ 250 mV current mode logic (CML) outputs (ADATE320)

- ▶ 400 mV CML outputs (ADATE320-1)

- Load

- ▶ Per pin PMU (PPMU)

- ▶ Force voltage/compliance range: -1.5 V to +4.5 V

- ▶ 5 current ranges

- ▶ ±40 mA, ±1 mA, ±100 μA, ±10 μA, ±2 μA

- Dedicated go/no-go comparators

- ▶ DC levels

- ▶ Fully integrated and dedicated 16-bit DACs

- On-chip gain and offset calibration registers with automatic add/multiply function

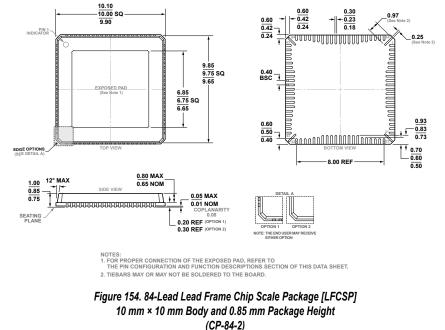

- 84-lead, 10 mm × 10 mm LFCSP (0.4 mm pitch)

### **APPLICATIONS**

- Automatic test equipment (ATE)

- Semiconductor/board test systems

- Instrumentation and characterization equipment

### **GENERAL DESCRIPTION**

The ADATE320 is a complete, single-chip ATE solution that performs the pin electronics functions of a driver, comparator, and active load (DCL), and a four quadrant per pin parametric measurement unit (PPMU). Dedicated 16-bit digital-to-analog converters (DACs) with on-chip calibration registers provide all the necessary dc levels for operation of the device.

The driver features three active modes: high, low, and terminate, as well as a high impedance inhibit state. The inhibit state, in conjunction with the integrated dynamic clamps, facilitates significant attenuation of transmission line reflections when the driver is not actively terminating the line. The open-circuit drive capability is -1.5 V to +4.5 V to accommodate a standard range of ATE and instrumentation applications.

The ADATE320 can be used as a dual, single-ended pin electronics channel or as a single differential channel. In addition to per channel high speed window comparators, the ADATE320 provides a programmable threshold differential comparator for differential ATE applications.

All dc levels for DCL and PPMU functions are generated by dedicated, on-chip, 16-bit DACs. To facilitate the programming of accurate levels, the ADATE320 includes an integrated calibration function to correct for the gain and offset errors of each functional block. Correction coefficients can be stored on chip, and any values written to the DACs adjust automatically using the appropriate correction factors.

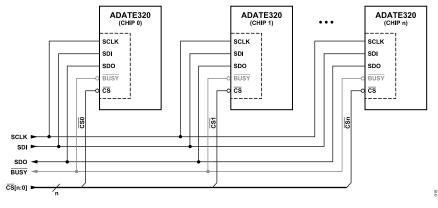

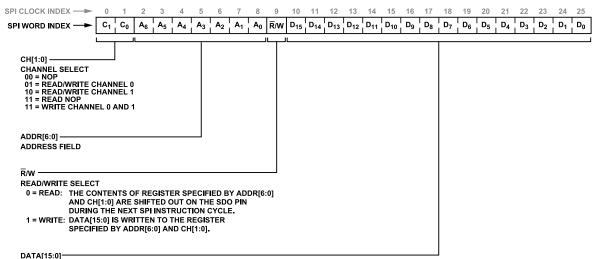

The ADATE320 uses a serial programmable interface (SPI) bus to program all functional blocks, DACs, and on-chip calibration constants. It also has an on-chip temperature sensor and overvoltage/undervoltage fault clamps that monitor and report the device temperature and any output pin or transient PPMU voltage faults that may occur during operation.

The ADATE320 is available in two options. The standard option has high speed comparator outputs with 250 mV output swing. The ADATE320-1 has 400 mV output swing. See the Ordering Guide for more information.

Rev. D

DOCUMENT FEEDBACK

TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### TABLE OF CONTENTS

| Features1                                  |

|--------------------------------------------|

| Applications1                              |

| General Description1                       |

| Functional Block Diagram3                  |

| Specifications                             |

| Electrical Specifications4                 |

| Driver Specifications5                     |

| Reflection Clamp Specifications7           |

| Normal Window Comparator (NWC)             |

| Specifications8                            |

| Differential Mode Comparator (DMC)         |

| Specifications10                           |

| Active Load Specifications11               |

| PPMU Specifications12                      |

| PPMU Go/No-Go Comparators                  |

| Specifications18                           |

| PPMU External Sense Pins Specifications 18 |

| VREF, VREFGND, and DUTGND                  |

| Reference Input Pins Specifications18      |

| Temperature Monitor Specifications         |

| Alarm Functions Specifications             |

| Serial Programmable Interface (SPI)        |

| Specifications19                           |

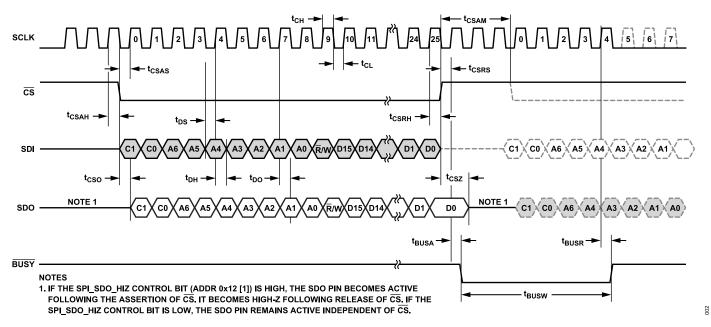

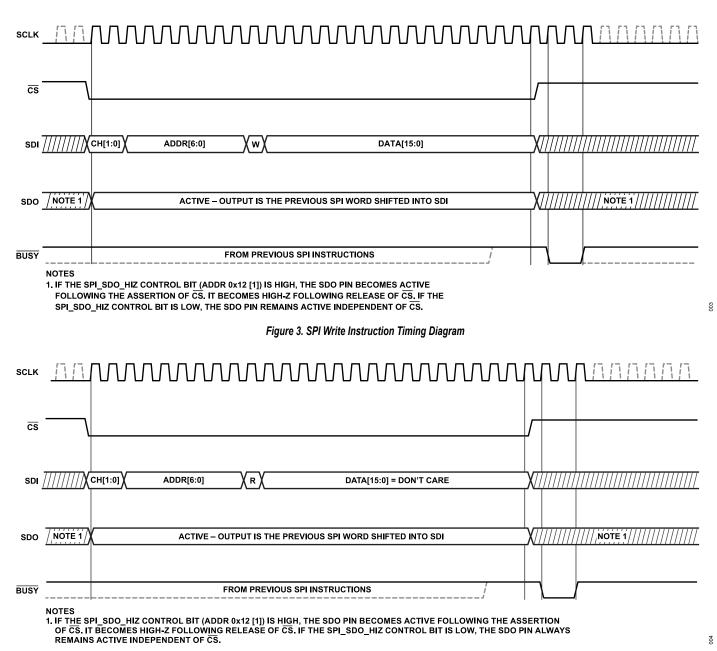

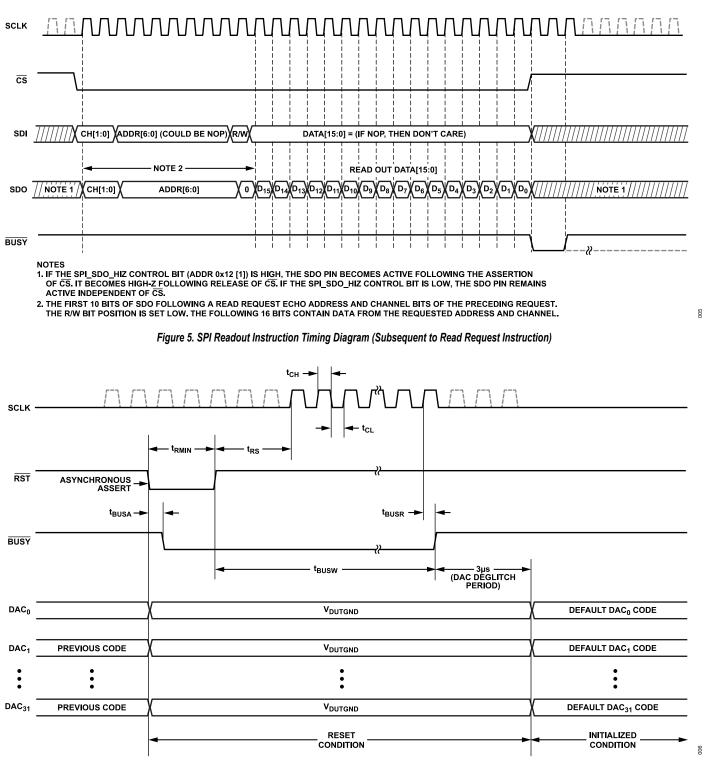

| SPI Timing Specifications20                |

| SPI Timing Diagrams21                      |

| Absolute Maximum Ratings                    | 25 |

|---------------------------------------------|----|

| Thermal Characteristics                     | 25 |

| Explanation of Test Levels                  | 25 |

| User Information and Truth Tables           |    |

| ESD Caution                                 | 27 |

| Pin Configuration and Function Descriptions | 28 |

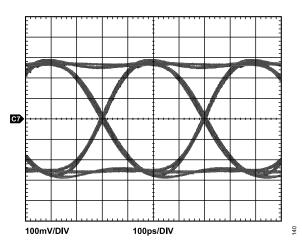

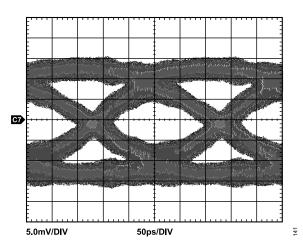

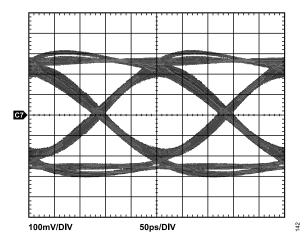

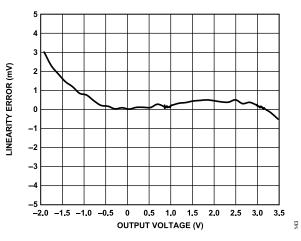

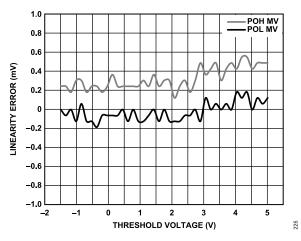

| Typical Performance Characteristics         | 30 |

| Theory of Operation                         | 50 |

| Serial Programmable Interface (SPI)         | 50 |

| Level Setting DACs                          | 52 |

| Alarm Functions                             | 58 |

| Applications Information                    | 61 |

| Power Supply, Grounding, and Typical        |    |

| Decoupling Strategy                         | 61 |

| Power Supply Sequencing                     |    |

| Detailed Functional Block Diagrams          | 64 |

| SPI Register Memory Map and Details         | 68 |

| Memory Map                                  |    |

| Register Details                            | 70 |

| Default Test Conditions                     |    |

| External Components                         |    |

| Outline Dimensions                          |    |

| Ordering Guide                              |    |

| Evaluation Boards                           | 78 |

### **REVISION HISTORY**

| 4/2024—Rev. C to Rev. D    |  |

|----------------------------|--|

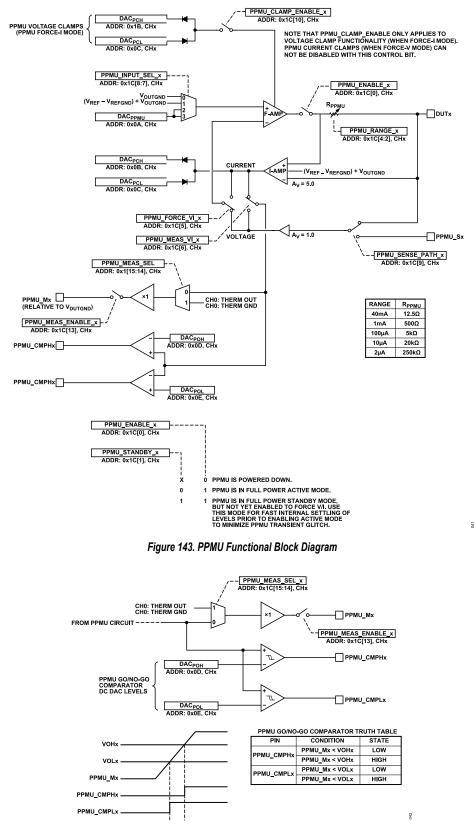

| Changes to Figure 143      |  |

| Updated Outline Dimensions |  |

| Added Evaluation Boards    |  |

|                            |  |

### 9/2022—Rev. B to Rev. C

| Deleted Figure 136; Renumbered Sequentially | 64 |

|---------------------------------------------|----|

| Changes to Figure 136                       |    |

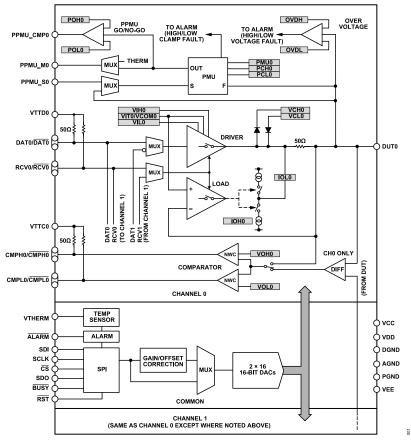

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

$V_{CC}$  = 8.0 V,  $V_{DD}$  = 1.8 V,  $V_{EE}$  = -5.0 V,  $V_{TTCx}$  =  $V_{TTDx}$  = 1.2 V,  $V_{REF}$  = 2.500 V,  $V_{REFGND}$  = 0.000 V. All default test conditions are as defined in Table 30. All specified values are at  $T_J$  = 60°C, where  $T_J$  corresponds to the typical internal temperature sensor reading (VTHERM pin), unless otherwise noted. Temperature coefficients are measured around  $T_J$  = 40°C, 60°C, 80°C, and 100°C. Typical values are based on the statistical mean of the design, simulation analyses, and/or limited bench evaluation data. Typical values are neither tested nor guaranteed. Test level codes are defined in the Explanation of Test Levels section.

# **ELECTRICAL SPECIFICATIONS**

### Table 1.

| Parameter                                                | Min   | Тур  | Max   | Unit | Test Level | Test Conditions/Comments                                                                                                                                              |

|----------------------------------------------------------|-------|------|-------|------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DUTx PIN CHARACTERISTICS                                 |       |      |       |      |            |                                                                                                                                                                       |

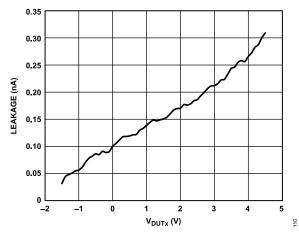

| Output Leakage Current                                   |       |      |       |      |            |                                                                                                                                                                       |

| DCL Disable                                              |       |      |       |      |            |                                                                                                                                                                       |

| PPMU Range E                                             | -10.0 | +5.0 | +10.0 | nA   | Р          | -1.5 V < V <sub>DUTx</sub> < +4.5 V, PPMU and DCL disabled, PPMU Range E, VCLx = -2.5 V, VCHx = +7.5 V                                                                |

| PPMU Range A to Range D                                  |       | 5.0  |       | nA   | CT         | -1.5 V < V <sub>DUTx</sub> < +4.5 V, PPMU and DCL disabled, PPMU Range A, Range B, Range C, and Range D, VCLx = -2.5 V, VCHx = +7.5 V                                 |

| Driver High-Z Mode                                       | -0.4  |      | +0.4  | μA   | Р          | -1.5 V < V <sub>DUTx</sub> < +4.5 V, PPMU disabled and DCL enabled, RCV active VCLx = -2.5 V, VCHx = +7.5 V                                                           |

| Capacitance                                              |       | 0.4  |       | pF   | S          | Drive VITx = 0.0 V                                                                                                                                                    |

| Voltage Range                                            | -1.5  |      | +4.5  | V    | D          |                                                                                                                                                                       |

| POWER SUPPLIES                                           |       |      |       |      |            | Power measured with the DUTx pin high-Z, 10 K to 0.0 V                                                                                                                |

| Positive DCL Supply, V <sub>CC</sub>                     | 7.6   | 8.0  | 8.4   | V    | D          | Defines dc power supply rejection (PSR) conditions                                                                                                                    |

| Negative DCL Supply, V <sub>EE</sub>                     | -5.25 | -5.0 | -4.75 | V    | D          | Defines dc PSR conditions                                                                                                                                             |

| Digital Supply, V <sub>DD</sub>                          | 1.7   | 1.8  | 1.9   | V    | D          |                                                                                                                                                                       |

| Comparator Termination, V <sub>TTCx</sub>                | 0.5   | 1.2  | 1.8   | V    | D          | VTTC0 is not electrically connected to VTTC1                                                                                                                          |

| Driver Termination, V <sub>TTDx</sub>                    | 0.0   | 1.2  | 1.8   | V    | D          | VTTD0 is not electrically connected to VTTD1                                                                                                                          |

| Positive DCL Supply Current, I <sub>CC</sub>             |       |      |       |      |            | Load and PPMU power-down                                                                                                                                              |

| ADATE320                                                 | 145   | 169  | 185   | mA   | Р          |                                                                                                                                                                       |

| ADATE320-1                                               | 145   | 169  | 185   | mA   | Р          |                                                                                                                                                                       |

| Negative DCL Supply Current, I <sub>EE</sub>             |       |      |       |      |            | Load and PPMU power-down                                                                                                                                              |

| ADATE320                                                 | 190   | 222  | 235   | mA   | P          |                                                                                                                                                                       |

| ADATE320-1                                               | 220   | 247  | 265   | mA   | Р          |                                                                                                                                                                       |

| Digital Core Supply Current, IDD                         | -125  | +10  | +125  | μA   | Р          | Quiescent (SPI is static)                                                                                                                                             |

| Comparator Termination Supply Current, V <sub>TTCx</sub> |       |      |       |      |            | $0.5 \text{ V} \le \text{V}_{\text{TTCx}} \le 1.8 \text{ V}$                                                                                                          |

| ADATE320                                                 |       | 41   |       | mA   | CT         |                                                                                                                                                                       |

| ADATE320-1                                               |       | 66   |       | mA   | CT         |                                                                                                                                                                       |

| Driver Termination Supply Current, V <sub>TTDx</sub>     |       | 0    |       | mA   | CT         | $0.0 \text{ V} \le \text{V}_{\text{TTDx}} \le 1.8 \text{ V}$ , (DATx + $\overline{\text{DATx}}$ )/2 = (RCVx + $\overline{\text{RCVx}}$ )/2 = $\text{V}_{\text{TTDx}}$ |

| Total Power Dissipation                                  |       |      |       |      |            | Load and PPMU power-down                                                                                                                                              |

| ADATE320                                                 | 2.10  | 2.52 | 2.75  | W    | Р          |                                                                                                                                                                       |

| ADATE320-1                                               | 2.25  | 2.66 | 2.90  | W    | Р          |                                                                                                                                                                       |

# DRIVER SPECIFICATIONS

VIH – VIL  $\ge$  100 mV to meet dc and ac performance specifications.

### Table 2.

| Parameter                                                            | Min  | Тур  | Max  | Unit   | Test Level     | Test Conditions/Comments                                                                                                                                                               |

|----------------------------------------------------------------------|------|------|------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                                    |      |      |      |        |                |                                                                                                                                                                                        |

| High Speed Differential Input<br>Characteristics                     |      |      |      |        |                |                                                                                                                                                                                        |

| High Speed Input Termination<br>Resistance: DATx/DATx, RCVx/<br>RCVx | 48   | 50   | 52   | Ω      | P              | Impedance between VTTDx and respective DATx and RCVx pins; force 4 mA into each pin, measure voltage from VTTDx; calculate resistance $(\Delta V/\Delta I)$                            |

| Input Voltage Range: DATx/<br>DATx, RCVx/RCVx                        | 0.0  |      | 1.8  | V      | P <sub>F</sub> |                                                                                                                                                                                        |

| Input Voltage Differential                                           | 0.2  | 0.4  | 1.0  | V      | P <sub>F</sub> | DATx - DATx ,  RCVx - RCVx                                                                                                                                                             |

| Output Characteristics                                               |      |      |      |        |                |                                                                                                                                                                                        |

| Output Range                                                         |      |      |      |        |                |                                                                                                                                                                                        |

| High, VIH                                                            | -1.4 |      | +4.5 | V      | D              |                                                                                                                                                                                        |

| Low, VIL                                                             | -1.5 |      | +4.4 | V      | D              |                                                                                                                                                                                        |

| Output Term Range, VIT                                               | -1.5 |      | +4.5 | V      | D              |                                                                                                                                                                                        |

| Functional Amplitude (VIH - VIL)                                     | 0.05 |      | 6.0  | V      | D              |                                                                                                                                                                                        |

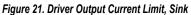

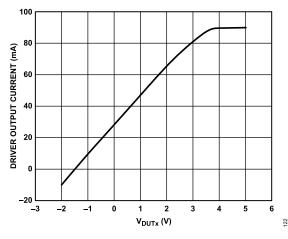

| DC Output Current Limit                                              |      |      |      |        |                |                                                                                                                                                                                        |

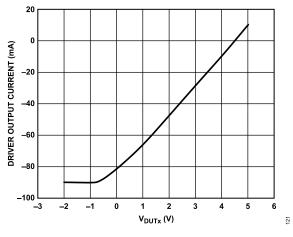

| Source                                                               | 75   |      | 120  | mA     | Р              | Drive high, VIH = 4.5 V, V <sub>DUTx</sub> = −2.0 V, measure current                                                                                                                   |

| Sink                                                                 | -120 |      | -75  | mA     | Р              | Drive low, VIL = $-1.5$ V, V <sub>DUTx</sub> = 5.0 V, measure current                                                                                                                  |

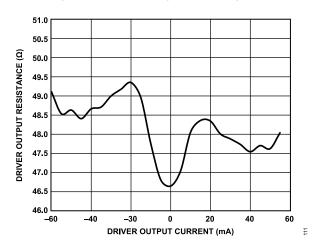

| Output Resistance, ±40 mA                                            | 46   | 48.5 | 52   | Ω      | Р              | $\Delta V_{\text{DUTx}}/\Delta I_{\text{DUTx}}$ ; source: VIHx = 3.0 V, I <sub>DUTx</sub> = 1 mA, 40 mA; sink: VIL =                                                                   |

|                                                                      |      |      |      |        |                | $0.0 \text{ V}, \text{ I}_{\text{DUTx}} = -1 \text{ mA}, -40 \text{ mA}$                                                                                                               |

| DC ACCURACY                                                          |      |      |      |        |                | VIH tests with VIL = $-2.5$ V, VIT = $-2.5$ V; VIL tests with VIH = $7.5$ V, VIT = $7.5$ V; VIT tests with VIL = $-2.5$ V, VIH = $7.5$ V, unless otherwise noted within this parameter |

| VIH, VIL, VIT                                                        |      |      |      |        |                |                                                                                                                                                                                        |

| Offset Error                                                         | -500 |      | +500 | mV     | P              | Measured at DAC Code 0x4000 (0.0 V), uncalibrated                                                                                                                                      |

| Offset Temperature Coefficient<br>(TC)                               |      | ±200 |      | µV/°C  | CT             |                                                                                                                                                                                        |

| Gain                                                                 | 1.0  |      | 1.1  | V/V    | P              | Gain derived from measurement at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V); based on an ideal DAC transfer function (see Table 24)                                           |

| Gain TC                                                              |      | ±50  |      | ppm/°C | CT             |                                                                                                                                                                                        |

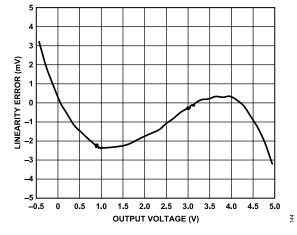

| Differential Nonlinearity (DNL)                                      |      | ±250 |      | μV     | CT             | After two-point gain/offset calibration; calibration points at 0x4000 (0.0 V) output; 0x8CCC (3.0 V); measured over full specified output range                                        |

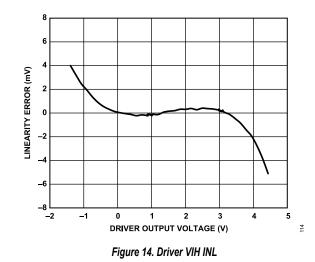

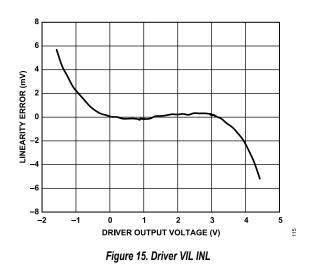

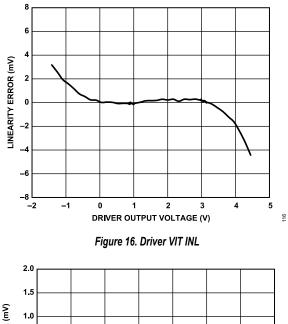

| Integral Nonlinearity (INL)<br>Focused Range                         | -5   |      | +5   | mV     | Р              | After two-point gain/offset calibration; calibration points at $0x4000$ (0.0 V) and $0x8CCC$ (3.0 V); measured over $-0.5$ V to $+3.5$ V output range                                  |

| INL Full Range                                                       | -20  |      | +20  | mV     | Ρ              | After two-point gain/offset calibration; calibration points at 0x4000 (0.0 V) and 0x8CCC (3.0 V); measured over full specified output range                                            |

| Resolution                                                           |      | 153  |      | μV     | D              |                                                                                                                                                                                        |

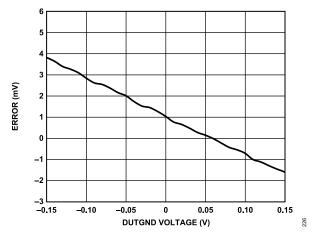

| DUTGND Voltage Accuracy                                              | -5   | ±1   | +5   | mV     | Ρ              | Over $\pm 0.1$ V range; measured over $-0.5$ V to $+3.5$ V focused driver output range                                                                                                 |

| DC Levels Interaction                                                |      |      |      |        |                | DC interaction on VIL, VIH, and VIT output levels while other driver DAC levels are varied                                                                                             |

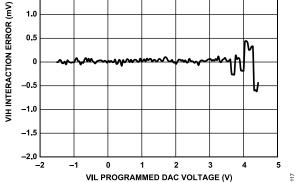

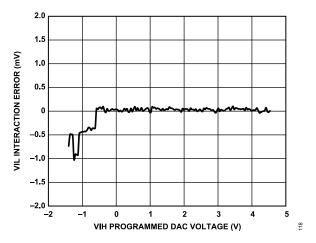

| VIH vs. VIL                                                          |      | ±1.0 |      | mV     | CT             | Monitor interaction on VIH = +4.5 V; sweep VIL = $-1.5$ V to +4.4 V, VIT = +1.0 V                                                                                                      |

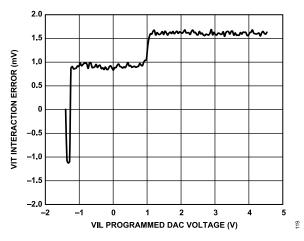

| VIH vs. VIT                                                          |      | ±1.0 |      | mV     | CT             | Monitor interaction on VIH = +4.5 V; sweep VIT = $-1.5$ V to +4.5 V, VIL = 0.0 V                                                                                                       |

| VIL vs. VIH                                                          |      | ±1.0 |      | mV     | CT             | Monitor interaction on VIL = $-1.5$ V; sweep VIH = $-1.4$ V to $+4.5$ V, VIT = $+1.0$ V                                                                                                |

# **ADATE320**

### **SPECIFICATIONS**

| Parameter                                                               | Min | Тур  | Мах | Unit  | Test Level     | Test Conditions/Comments                                                                                           |

|-------------------------------------------------------------------------|-----|------|-----|-------|----------------|--------------------------------------------------------------------------------------------------------------------|

| VIL vs. VIT                                                             |     | ±1.0 |     | mV    | CT             | Monitor interaction on VIL = $-1.5$ V; sweep VIT = $-1.5$ V to $+4.5$ V, VIH = $+2.0$ V                            |

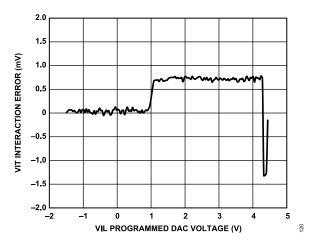

| VIT vs. VIH                                                             |     | ±2.0 |     | mV    | CT             | Monitor interaction on VIT = 1.0 V; sweep VIH = $-1.4$ V to $+4.5$ V, VIL = $-1.5$ V                               |

| VIT vs. VIL                                                             |     | ±2.0 |     | mV    | CT             | Monitor interaction on VIT = 1.0 V; sweep VIL = $-1.5$ V to +4.4 V, VIH = +4.5 V                                   |

| Overall Voltage Accuracy Focused<br>Range                               |     | ±5   |     | mV    | CT             | VIH – VIL $\ge$ 100 mV; sum of INL, dc interaction, DUTGND and TC errors over $\pm 5^{\circ}$ C, after calibration |

| VIH, VIL, VIT DC PSR                                                    |     | +15  |     | mV/V  | CT             | Measured at calibration points, see Table 1 for power supply ranges                                                |

| AC SPECIFICATIONS                                                       |     |      |     |       |                | All ac specifications performed after dc calibration                                                               |

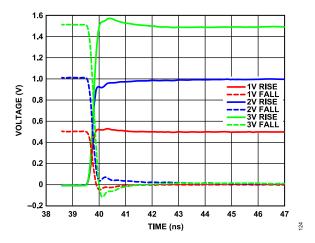

| Rise/Fall Times                                                         |     |      |     |       |                | Toggle DATx, VIL = 0.0 V, terminated                                                                               |

| 0.2 V Programmed Swing                                                  |     |      |     |       |                |                                                                                                                    |

| t <sub>RISE</sub>                                                       |     | 150  |     | ps    | CB             | 20% to 80%, VIH = 0.2 V                                                                                            |

| t <sub>FALL</sub>                                                       |     | 170  |     | ps    | C <sub>B</sub> | 20% to 80%, VIH = 0.2 V                                                                                            |

| 0.5 V Programmed Swing                                                  |     |      |     | 1     |                |                                                                                                                    |

| t <sub>RISE</sub>                                                       |     | 150  |     | ps    | CB             | 20% to 80%, VIH = 0.5 V                                                                                            |

| t <sub>FALL</sub>                                                       |     | 170  |     | ps    | CB             | 20% to 80%, VIH = 0.5 V                                                                                            |

| 1.0 V Programmed Swing                                                  |     |      |     |       |                |                                                                                                                    |

| t <sub>RISE</sub>                                                       |     | 150  |     | ps    | CB             | 20% to 80%, VIH = 1.0 V                                                                                            |

| t <sub>FALL</sub>                                                       |     | 170  |     | ps    | C <sub>B</sub> | 20% to 80%, VIH = 1.0 V                                                                                            |

| 2.0 V Programmed Swing                                                  |     |      |     |       |                |                                                                                                                    |

| t <sub>RISE</sub>                                                       | 120 | 160  | 230 | ps    | P              | 20% to 80%, VIH = 2.0 V                                                                                            |

| t <sub>FALL</sub>                                                       | 120 | 180  | 230 | ps    | Р              | 20% to 80%, VIH = 2.0 V                                                                                            |

| 4.0 V Programmed Swing                                                  |     |      |     |       |                |                                                                                                                    |

| t <sub>RISE</sub>                                                       |     | 320  |     | ps    | CB             | 10% to 90%, VIH = 4.0 V, unterminated                                                                              |

| t <sub>FALL</sub>                                                       |     | 320  |     | ps    | CB             | 10% to 90%, VIH = 4.0 V, unterminated                                                                              |

| $t_{\mbox{\scriptsize RISE}}$ to $t_{\mbox{\scriptsize FALL}}$ Mismatch |     | -20  |     | ps    | CB             | $t_{\text{RISE}}$ – $t_{\text{FALL}}$ (20% to 80%) within one channel, VIH = 2.0 V, VIL = 0.0 V, terminated        |

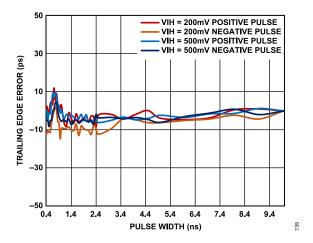

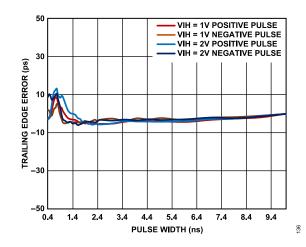

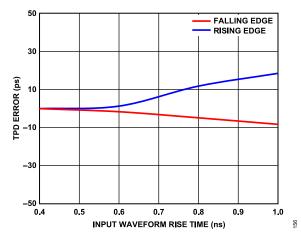

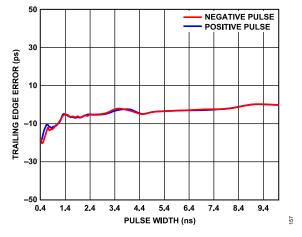

| Trailing Edge Timing Error                                              |     |      |     |       |                | Toggle DATx                                                                                                        |

| Programmed Swing                                                        |     |      |     |       |                | VIL = 0.0 V, terminated, 400 ps ≤ pulse width (PW) ≤ 10 ns                                                         |

| 0.2 V                                                                   |     | ±15  |     | ps    | CB             | VIH = 0.2 V                                                                                                        |

| 0.5 V                                                                   |     | ±15  |     | ps    | CB             | VIH = 0.5 V                                                                                                        |

| 1.0 V                                                                   |     | ±15  |     | ps    | CB             | VIH = 1.0 V                                                                                                        |

| 2.0 V                                                                   |     | ±15  |     | ps    | CB             | VIH = 2.0 V                                                                                                        |

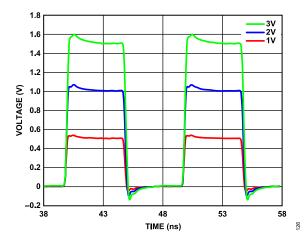

| Maximum Toggle Rate                                                     |     |      |     |       |                | Toggle DATx                                                                                                        |

| Programmed Swing                                                        |     |      |     |       |                | VIL = 0.0 V, terminated ≤10% amplitude loss                                                                        |

| 0.2 V                                                                   |     | 2.8  |     | Gbps  | CB             | VIH = 0.2 V                                                                                                        |

| 0.5 V                                                                   |     | 3.2  |     | Gbps  | CB             | VIH = 0.5 V                                                                                                        |

| 1.0 V                                                                   |     | 3.2  |     | Gbps  | CB             | VIH = 1.0 V                                                                                                        |

| 2.0 V                                                                   |     | 2.8  |     | Gbps  | C <sub>B</sub> | VIH = 2.0 V                                                                                                        |

| Dynamic Performance                                                     |     |      |     |       |                | Toggle DATx, drive VIL to/from VIH                                                                                 |

| Propagation Delay                                                       |     |      |     |       |                | VIH = 2.0 V, VIL = 0.0 V, terminated                                                                               |

| Time                                                                    |     | 750  |     | ps    | CB             |                                                                                                                    |

| TC                                                                      |     | 2    |     | ps/°C | CT             |                                                                                                                    |

| Delay Matching                                                          |     |      |     |       |                | VIH = 2.0 V, VIL = 0.0 V, terminated                                                                               |

| Edge to Edge                                                            |     | 10   |     | ps    | CB             | $t_{LH0} - t_{HL0}$ ; $t_{LH1} - t_{HL1}$                                                                          |

| Channel to Channel                                                      |     | 35   |     | ps    | C <sub>B</sub> | $t_{LH0} - t_{LH1}$ ; $t_{HL0} - t_{HL1}$                                                                          |

| Delay Change vs. Duty Cycle                                             |     | ±7   |     | ps    | C <sub>B</sub> | VIH = 2.0 V, VIL = 0.0 V, terminated, 1 MHz, 5% to 95%                                                             |

| Overshoot and Undershoot                                                |     | 50   |     | mV    | CB             | VIH = 2.0 V, VIL = 0.0 V, terminated, minimum driver CLC                                                           |

### Table 2. (Continued)

| Parameter                                     | Min | Тур | Max | Unit   | Test Level     | Test Conditions/Comments                                       |

|-----------------------------------------------|-----|-----|-----|--------|----------------|----------------------------------------------------------------|

| Settling Time (VIH to VIL)                    |     |     |     |        |                | Toggle DATx                                                    |

| To Within 3% of Final Value                   |     | 1   |     | ns     | CB             | VIH = 2.0 V, VIL = 0.0 V, from 50% crossing, terminated        |

| To Within 1% of Final Value                   |     | 10  |     | ns     | CB             | VIH = 2.0 V, VIL = 0.0 V, from 50% crossing, terminated        |

| Dynamic Performance                           |     |     |     |        |                |                                                                |

| Drive Active to/from VIT                      |     |     |     |        |                | Toggle RCVx, VIH = 2.0 V, VIT = 1.0 V, VIL = 0.0 V, terminated |

| Transition Time                               |     |     |     |        |                | 20% to 80%                                                     |

| Active to VIT                                 |     | 200 |     | ps     | CB             |                                                                |

| VIT to Active                                 |     | 170 |     | ps     | CB             |                                                                |

| Propagation Delay                             |     | 1.0 |     | ns     | CB             |                                                                |

| TC                                            |     | 2   |     | ps/°C  | CT             |                                                                |

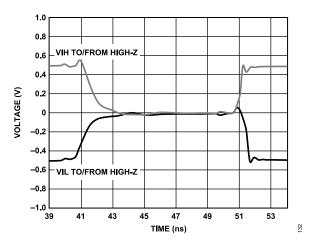

| Drive Active to/from Inhibit                  |     |     |     |        |                | Toggle RCVx, VIH = 1.0 V, VIL = −1.0 V, terminated             |

| Transition Time                               |     |     |     |        |                | 20% to 80%                                                     |

| Inhibit to Active                             |     | 250 |     | ps     | CB             |                                                                |

| Active to Inhibit                             |     | 850 |     | ps     | CB             |                                                                |

| Propagation Delay                             |     |     |     |        |                |                                                                |

| Inhibit to VIH                                |     | 2.1 |     | ns     | CB             |                                                                |

| Inhibit to VIL                                |     | 2.5 |     | ns     | CB             |                                                                |

| Matching Inhibit to VIL vs.<br>Inhibit to VIH |     | 0.4 |     | ns     | C <sub>B</sub> |                                                                |

| VIH to Inhibit                                |     | 2.5 |     | ns     | CB             |                                                                |

| VIL to Inhibit                                |     | 2.1 |     | ns     | CB             |                                                                |

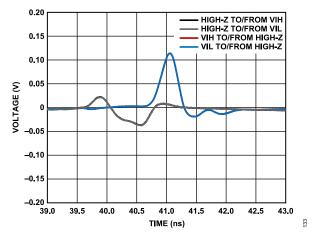

| Input/Output Spike                            |     | 125 |     | mV p-p | CB             | VIH = 0.0 V, VIL = 0.0 V, terminated, toggle RCVx              |

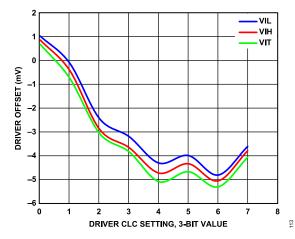

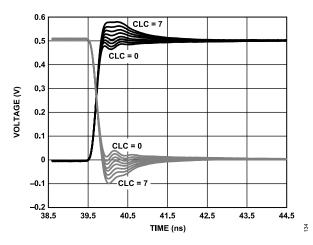

| Cable Loss Compensation (CLC)                 |     |     |     |        |                | VIH = 2.0 V, VIL = 0.0 V, terminated                           |

| Amplitude                                     |     | 20  |     | %      | CB             | Maximum CLC setting                                            |

| Resolution                                    |     | 3   |     | Bits   | D              |                                                                |

| Time Constant 1                               |     | 400 |     | ps     | S              | Maximum CLC setting                                            |

| Time Constant 2                               |     | 1.5 |     | ns     | S              | Maximum CLC setting                                            |

### **REFLECTION CLAMP SPECIFICATIONS**

Clamp accuracy specifications apply only when VCHx – VCLx > 0.8 V.

### Table 3.

| Parameter        | Min  | Тур   | Max  | Unit   | Test Level | Test Conditions/Comments                                                                                                                                                            |

|------------------|------|-------|------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCH              |      |       |      |        |            |                                                                                                                                                                                     |

| Functional Range | -0.5 |       | +5.0 | V      | D          |                                                                                                                                                                                     |

| Offset Error     | -300 |       | +300 | mV     | Р          | Driver high-Z, sinking 1 mA, measured at DAC Code 0x4000 (0.0 V), uncalibrated                                                                                                      |

| Offset TC        |      | ±0.25 |      | mV/°C  | CT         |                                                                                                                                                                                     |

| Gain             | 1.0  |       | 1.1  | V/V    | Ρ          | Driver high-Z, sinking 1 mA, gain derived from measurements at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V), based on an idea DAC transfer function (see Table 24)           |

| Gain TC          |      | ±25   |      | ppm/°C | CT         |                                                                                                                                                                                     |

| Resolution       |      | 153   |      | μV     | D          |                                                                                                                                                                                     |

| DNL              |      | ±250  |      | μV     | CT         | Driver high-Z, sinking 1 mA, after two-point gain/offset calibration; calibration points at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V), measured over the functional range |

| INL              | -20  |       | +20  | mV     | Ρ          | Driver high-Z, sinking 1 mA, after two-point gain/offset calibration; calibration points at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V), measured over the functional range |

### Table 3. (Continued)

| Parameter               | Min  | Тур   | Max  | Unit   | Test Level | Test Conditions/Comments                                                                                                                                                            |

|-------------------------|------|-------|------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCL                     |      |       |      |        |            |                                                                                                                                                                                     |

| Functional Range        | -2.0 |       | +3.5 | V      | D          |                                                                                                                                                                                     |

| Offset Error            | -300 |       | +300 | mV     | Р          | Driver high-Z, sourcing 1 mA, measured at DAC Code 0x4000 (0.0 V), uncalibrated                                                                                                     |

| Offset TC               |      | ±0.25 |      | mV/°C  | CT         |                                                                                                                                                                                     |

| Gain                    | 1.0  |       | 1.1  | V/V    | Ρ          | Drive high-Z, sourcing 1 mA, gain derived from measurements at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V), based on an idea DAC transfer function (see Table 24)           |

| Gain TC                 |      | ±25   |      | ppm/°C | CT         |                                                                                                                                                                                     |

| Resolution              |      | 153   |      | μV     | D          |                                                                                                                                                                                     |

| DNL                     |      | ±250  |      | μV     | CT         | Drive high-Z, sourcing 1 mA, after two-point gain/offset calibration; calibration points at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V), measured over the functional range |

| INL                     | -20  |       | +20  | mV     | Ρ          | Drive high-Z, sourcing 1 mA, after two-point gain/offset calibration; calibration points at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V), measured over the functional range |

| DC CLAMP CURRENT LIMIT  |      |       |      |        |            | Drive high-Z                                                                                                                                                                        |

| VCHx                    | -105 |       | -60  | mA     | Р          | VCHx = -1.0 V, VCLx = -2.0 V, V <sub>DUTx</sub> = 4.5 V                                                                                                                             |

| VCLx                    | +60  |       | +105 | mA     | P          | VCHx = 5.0 V, VCLx = 4.0 V, V <sub>DUTx</sub> = -1.5 V                                                                                                                              |

| DUTGND VOLTAGE ACCURACY | -10  | ±2    | +10  | mV     | P          | Over ±0.1 V range, measured at end points of VCHx and VCLx functional range                                                                                                         |

# NORMAL WINDOW COMPARATOR (NWC) SPECIFICATIONS

| Parameter                  | Min  | Тур   | Max  | Unit   | Test Level | Test Conditions/Comments                                                                                                                                                  |

|----------------------------|------|-------|------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC SPECIFICATIONS          |      |       |      |        |            |                                                                                                                                                                           |

| Input Voltage Range        | -1.5 |       | +4.5 | V      | D          |                                                                                                                                                                           |

| Differential Voltage Range | ±0.1 |       | ±6.0 | V      | D          |                                                                                                                                                                           |

| Input Offset Voltage       | -250 |       | +250 | mV     | Р          | Measured at DAC Code 0x4000 (0.0 V); uncalibrated                                                                                                                         |

| Input Offset Voltage TC    |      | ±150  |      | µV/°C  | CT         |                                                                                                                                                                           |

| Gain                       | 1.0  |       | 1.1  | V/V    | Ρ          | Gain derived from measurements at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V); based on an ideal DAC transfer function (see Table 24)                             |

| Gain TC                    |      | ±10   |      | ppm/°C | CT         |                                                                                                                                                                           |

| Threshold Resolution       |      | 153   |      | μV     | D          |                                                                                                                                                                           |

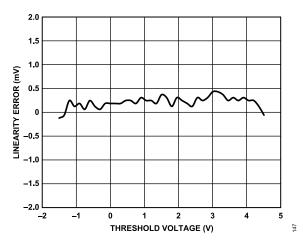

| Threshold DNL              |      | ±0.25 |      | mV     | CT         | Measured over -1.5 V to +4.5 V functional range after two-point gain/<br>offset calibration; calibration points at DAC Code 0x4000 (0.0 V) and<br>DAC Code 0x8CCC (3.0 V) |

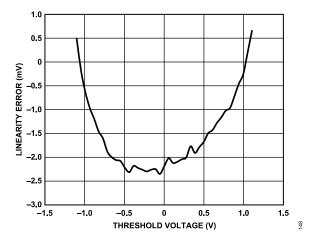

| Threshold INL              |      |       |      |        |            | After two-point gain/offset calibration; calibration points at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V)                                                        |

| Focused Range              | -5   |       | +5   | mV     | P          | Measured over -0.5 V to +3.5 V range                                                                                                                                      |

| Full Range                 | -7   |       | +7   | mV     | P          | Measured over -1.5 V to +4.5 V range                                                                                                                                      |

| DUTGND Voltage Accuracy    | -5   | ±1    | +5   | mV     | P          | Over ±0.1 V range; measured over –0.5 V to +3.5 V focused NWC input range                                                                                                 |

| Uncertainty Band           |      | 10    |      | mV     | CB         | $V_{DUTx}$ = 0.0 V, sweep comparator threshold to determine the uncertainty band                                                                                          |

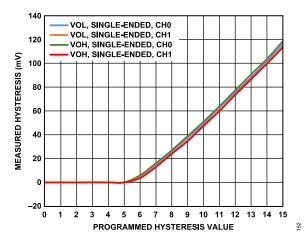

| Programmable Hysteresis    |      | 100   |      | mV     | CB         |                                                                                                                                                                           |

| Hysteresis Resolution      |      | 4     |      | Bits   | D          |                                                                                                                                                                           |

| DC PSR                     |      | ±5    |      | mV/V   | CT         | Measured at DAC Code 0x4000 (0.0 V) and DAC Code 0x8CCC (3.0 V) calibration points                                                                                        |

| Parameter                                                       | Min | Тур  | Мах | Unit  | Test Level     | Test Conditions/Comments                                                                                                                                                                                                               |

|-----------------------------------------------------------------|-----|------|-----|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Digital Output Characteristics                                  |     |      |     |       |                |                                                                                                                                                                                                                                        |

| Internal Pull-up Resistance to Comparator, VTTCx                | 46  | 50   | 54  | Ω     | Р              | Source 1 mA and 10 mA from the output pin in high state, measure $\Delta V$ to calculate resistance; R = $\Delta V/9$ mA; repeat for all output pins                                                                                   |

| Common-Mode Voltage                                             |     |      |     |       |                | Measured relative to $V_{TTCx}$ , with 100 $\Omega$ differential termination                                                                                                                                                           |

| ADATE320                                                        |     | -250 |     | mV    | CT             |                                                                                                                                                                                                                                        |

| ADATE320-1                                                      |     | -400 |     | mV    | CT             |                                                                                                                                                                                                                                        |

| Differential Mode Voltage                                       |     |      |     |       |                | Measured differentially                                                                                                                                                                                                                |

| 100 $\Omega$ Differential Termination                           |     |      |     |       |                |                                                                                                                                                                                                                                        |

| ADATE320                                                        |     | 250  |     | mV    | CT             |                                                                                                                                                                                                                                        |

| ADATE320-1                                                      |     | 400  |     | mV    | CT             |                                                                                                                                                                                                                                        |

| No External Termination                                         |     |      |     |       |                |                                                                                                                                                                                                                                        |

| ADATE320                                                        | 450 | 500  | 550 | mV    | Р              |                                                                                                                                                                                                                                        |

| ADATE320-1                                                      | 700 | 800  | 900 | mV    | P              |                                                                                                                                                                                                                                        |

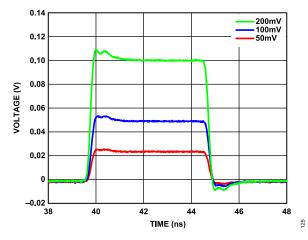

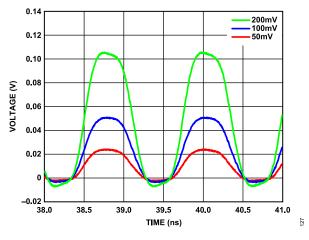

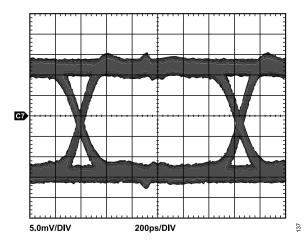

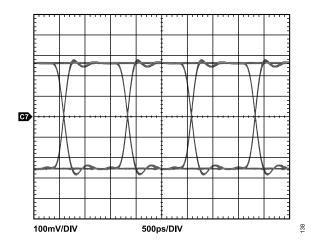

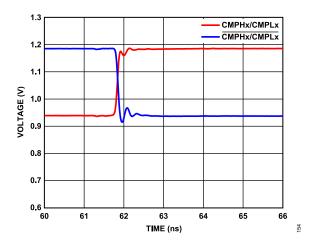

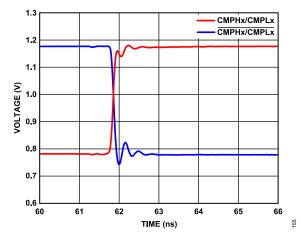

| AC SPECIFICATIONS                                               |     |      |     |       |                | Unless otherwise specified, all ac tests are performed after dc levels calibration; input transition time: 50 ps 20% to 80%; outputs terminated 50 $\Omega$ to 0.0 V; comparator CLC set to ¼ scale (010)                              |

| Rise/Fall Times, 20% to 80%                                     |     | 100  |     | ps    | CB             | Measured with 50 $\Omega$ to 0.0 V                                                                                                                                                                                                     |

| Propagation Delay                                               |     | 580  |     | ps    | C <sub>B</sub> | $V_{\text{DUTx}}$ = 0.0 V to 1.0 V swing, drive term mode, VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                   |

| Propagation Delay TC                                            |     | 1    |     | ps/°C | CT             | $V_{DUTx}$ = 0.0 V to 1.0 V swing, drive term mode, VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                          |

| Propagation Delay Matching High<br>Transition to Low Transition |     | 10   |     | ps    | CB             | $V_{DUTx}$ = 0.0 V to 1.0 V swing, drive term mode, VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                          |

| Propagation Delay Matching High to Low Comparator               |     | 10   |     | ps    | CB             | $V_{DUTx}$ = 0.0 V to 1.0 V swing, drive term mode, VIT = 0.0 V, comparator threshold = 0.5 V                                                                                                                                          |

| Propagation Delay Dispersion                                    |     |      |     |       |                | Drive term mode, VIT = 0.0 V                                                                                                                                                                                                           |

| Slew Rate: 400 ps vs. 1.0 ns<br>(20% to 80%)                    |     | 20   |     | ps    | CB             | $V_{DUTx}$ = 0.0 V to 0.5 V swing, comparator threshold = 0.25 V                                                                                                                                                                       |

| Overdrive: 250 mV vs. 1.0 V                                     |     | 25   |     | ps    | C <sub>B</sub> | For 250 mV: $V_{DUTx}$ : 0.0 V to 0.50 V swing; for 1.0 V: $V_{DUTx}$ : 0.0 V to 1.25 V swing, comparator threshold = 0.25 V                                                                                                           |

| 1.0 V Pulse Width: 0.4 ns, 0.5<br>ns, 1 ns, 5 ns, 10 ns         |     | 25   |     | ps    | CB             | $V_{DUTx}$ = 0.0 V to 1.0 V swing, 32 MHz, comparator threshold = 0.5 V                                                                                                                                                                |

| 0.5 V Pulse Width: 0.4 ns, 0.5<br>ns, 1 ns, 5 ns, 10 ns         |     | 25   |     | ps    | CB             | $V_{\text{DUTx}}$ = 0.0 V to 0.5 V swing, 32 MHz, comparator threshold = 0.25 V                                                                                                                                                        |

| Duty Cycle: 5% to 95%                                           |     | 10   |     | ps    | CB             | V <sub>DUTx</sub> = 0.0 V to 1.0 V swing, 32 MHz, comparator threshold = 0.5 V                                                                                                                                                         |

| Minimum Detectable Pulse Width                                  |     | 200  |     | ps    | CB             | V <sub>DUTx</sub> = 0.0 V to 1.0 V swing, 32 MHz, greater than 50% output differential amplitude                                                                                                                                       |

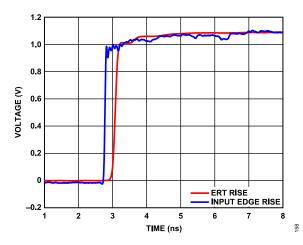

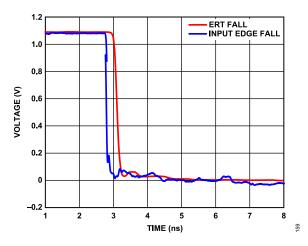

| Input Equivalent Rise/Fall Time,<br>1.0 V, Terminated           |     | 110  |     | ps    | CB             | $V_{DUTx}$ = 0.0 V to 1.0 V swing, drive term mode, VIT = 0.0 V, CLC = 010, measured from digitized plot, 20% to 80% transition time of digitized plot is root-sum square (RSS) of input equivalent rise/fall and 50 ps input stimulus |

| Input Equivalent Rise/Fall Time, 2.0 V, Unterminated            |     | 500  |     | ps    | C <sub>B</sub> | V <sub>DUTx</sub> = 0.0 V to 2.0 V swing, drive high-Z, measured from digitized plot, 20% to 80% transition time of digitized plot is root-sum square (RSS) of input equivalent rise/fall and 50 ps input stimulus                     |

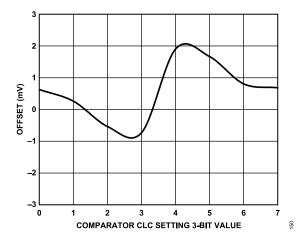

| Cable Loss Compensation (CLC)                                   |     |      |     |       |                | $V_{\text{DUTx}}$ = 0.0 V to 1.0 V swing, drive term mode, VIT = 0.0 V, maximum CLC setting                                                                                                                                            |

| CLC Amplitude                                                   |     | 20   |     | %     | CB             |                                                                                                                                                                                                                                        |

| CLC Resolution                                                  |     | 3    |     | Bits  | D              |                                                                                                                                                                                                                                        |

| CLC Time Constant 1                                             |     | 280  |     | ps    | S              |                                                                                                                                                                                                                                        |

| CLC Time Constant 2                                             |     | 4.8  |     | ns    | S              |                                                                                                                                                                                                                                        |

# DIFFERENTIAL MODE COMPARATOR (DMC) SPECIFICATIONS

| Parameter                                                       | Min   | Тур  | Мах  | Unit   | Test Level     | Test Conditions/Comments                                                                                                                                                                                |  |

|-----------------------------------------------------------------|-------|------|------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DC SPECIFICATIONS                                               |       | "14  | шах  |        |                | VOHx tests at VOLx = -1.5 V, VOLx tests at VOHx = 1.5 V                                                                                                                                                 |  |

|                                                                 | 4.5   |      |      | N      |                | VORX lesis at VOLX – $-1.5$ V, VOLX lesis at VORX – $1.5$ V                                                                                                                                             |  |

| Input Voltage Range                                             | -1.5  |      | +4.5 | V      | D              |                                                                                                                                                                                                         |  |

| Functional Differential Range                                   | ±0.05 |      | ±1.1 | V      | D              |                                                                                                                                                                                                         |  |

| Maximum Differential Input                                      |       |      | ±6.0 | V      | D              |                                                                                                                                                                                                         |  |

| Input Offset Voltage                                            | -250  |      | +250 | mV     | P              | Offset interpolated from measurements at DAC Code 0x2666 (-1.0 V) and DAC Code 0x5999 (1.0 V), with $V_{CM}$ = 0.0 V                                                                                    |  |

| Input Offset Voltage TC                                         |       | ±150 |      | μV/°C  | CT             |                                                                                                                                                                                                         |  |

| Gain                                                            | 1.0   |      | 1.1  | V/V    | Ρ              | Gain derived from measurements at DAC Code 0x2666 (-1.0 V) and DAC Code 0x5999 (1.0 V); based on an ideal DAC transfer function (see Table 24)                                                          |  |

| Gain TC                                                         |       | ±40  |      | ppm/°C | CT             |                                                                                                                                                                                                         |  |

| VOHx, VOLx Resolution                                           |       | 153  |      | μV     | D              |                                                                                                                                                                                                         |  |

| VOHx, VOLx DNL                                                  |       | ±250 |      | μV     | CT             | After two-point gain/offset calibration; $V_{CM}$ = 0.0 V; calibration points at DAC Code 0x2666 (-1.0 V) and DAC Code 0x5999 (1.0 V)                                                                   |  |

| VOHx, VOLx INL                                                  | -8    |      | +8   | mV     | Ρ              | After two-point gain/offset calibration; $V_{CM}$ = 0.0 V; calibration points<br>DAC Code 0x2666 (-1.0 V) and DAC Code 0x5999 (1.0 V), measured<br>over VOHx/VOLx range of -1.1 V to +1.1 V             |  |

| Uncertainty Band                                                |       | 11   |      | mV     | CB             | V <sub>DUTx</sub> = 0.0 V, sweep comparator threshold to determine the uncertainty band                                                                                                                 |  |

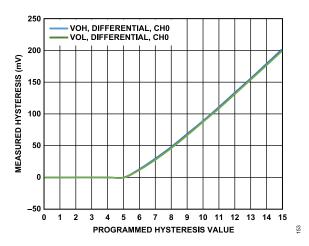

| Programmable Hysteresis                                         |       | 200  |      | mV     | CB             |                                                                                                                                                                                                         |  |

| Hysteresis Resolution                                           |       | 4    |      | Bits   | D              |                                                                                                                                                                                                         |  |

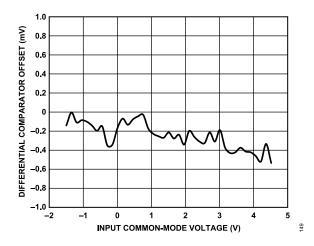

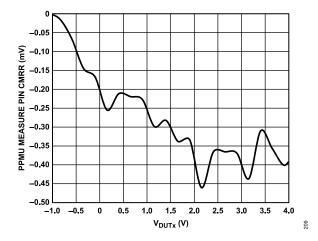

| Common-Mode Rejection Ratio<br>(CMRR)                           | -1.0  |      | +1.0 | mV/V   | Ρ              | $\Delta Offset$ measured at V_CM = –1.5 V and +4.5 V, V_DM = 0.0 V                                                                                                                                      |  |

| DC PSR                                                          |       | ±5   |      | mV/V   | CT             | $\Delta Offset$ measured at V <sub>CM</sub> = 0.0 V, V <sub>DM</sub> = calibration points DAC Code 0x2666 (–1.0 V) and DAC Code 0x5999 (1.0 V)                                                          |  |

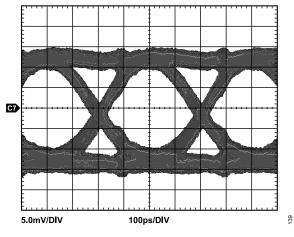

| AC SPECIFICATIONS                                               |       |      |      |        |                | All ac tests are performed after dc levels calibration; input transition time = 50 ps 20% to 80%; outputs terminated 50 $\Omega$ to VTTCx, comparator CLC set to ¼ scale (010)                          |  |

| Propagation Delay                                               |       | 580  |      | ps     | CB             | $V_{DUT0}$ = 0.0 V, $V_{DUT1}$ = -0.5 V to +0.5 V swing, drive termination mode, VIT = 0.0 V, comparator threshold = 0.0 V, repeat with VDUTx inputs reversed                                           |  |

| Propagation Delay TC                                            |       | 2    |      | ps/°C  | CT             | $V_{DUT0}$ = 0.0 V, $V_{DUT1}$ = -0.5 V to +0.5 V swing, drive termination mode, VIT = 0.0 V, comparator threshold = 0.0 V, repeat with VDUTx inputs reversed                                           |  |

| Propagation Delay Matching High<br>Transition to Low Transition |       | 15   |      | ps     | C <sub>B</sub> | $V_{DUT0} = 0.0 \text{ V}, V_{DUT1} = -0.5 \text{ V}$ to +0.5 V swing, drive termination mode,<br>VIT = 0.0 V, comparator threshold = 0.0 V, repeat with VDUTx inputs<br>reversed                       |  |

| Propagation Delay Matching High to<br>Low Comparator            |       | 15   |      | ps     | C <sub>B</sub> | $V_{DUT0} = 0.0 \text{ V}, V_{DUT1} = -0.5 \text{ V}$ to +0.5 V swing, drive termination mode,<br>VIT = 0.0 V, comparator threshold = 0.0 V, repeat with VDUTx inputs<br>reversed                       |  |

| Propagation Delay Dispersion                                    |       |      |      |        |                | V <sub>DUT0</sub> = 0.0 V, VIT = 0.0 V, drive termination mode, repeat with VDUTx inputs reversed                                                                                                       |  |

| Slew Rate: 400 ps vs. 1 ns (20% to 80%)                         |       | 30   |      | ps     | C <sub>B</sub> | $V_{\text{DUT1}} = -0.5 \text{ V}$ to +0.5 V swing, comparator threshold = 0.0 V                                                                                                                        |  |

| Overdrive: 250 mV vs. 750 mV                                    |       | 25   |      | ps     | C <sub>B</sub> | For 250 mV: $V_{DUT1}$ = 0.0 V to 0.5 V swing; for 750 mV: $V_{DUT1}$ = 0.0 V t<br>1.0 V swing, comparator threshold = -0.25 V, repeat with VDUTx input<br>reversed with comparator threshold = +0.25 V |  |

| 1.0 V Pulse Width: 0.7 ns, 1.0 ns,<br>5.0 ns, 10 ns             |       | 25   |      | ps     | C <sub>B</sub> | $V_{DUT1} = -0.5 \text{ V to } +0.5 \text{ V swing}$ , 32 MHz, comparator threshold = 0.0 V                                                                                                             |  |

### Table 5. (Continued)

| Parameter                                        | Min | Тур | Max | Unit | Test Level     | Test Conditions/Comments                                                                                                                                                                                                           |

|--------------------------------------------------|-----|-----|-----|------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.5 V Pulse Width: 0.6 ns, 1.0 ns, 5.0 ns, 10 ns |     | 25  |     | ps   | C <sub>B</sub> | $V_{\text{DUT1}}$ = –0.25 V to +0.25 V swing, 32 MHz, comparator threshold = 0.0 V                                                                                                                                                 |

| Duty Cycle: 5% to 95%                            |     | 5   |     | ps   | CB             | $V_{DUT1}$ = -0.5 V to +0.5 V swing, 32 MHz, comparator threshold = 0.0 V                                                                                                                                                          |

| Minimum Detectable Pulse Width                   |     | 200 |     | ps   | C <sub>B</sub> | $V_{DUT0} = 0.0 \text{ V}, V_{DUT1} = -0.5 \text{ V}$ to +0.5 V swing, 32 MHz, drive term<br>mode, VIT = 0.0 V, comparator threshold = 0.0 V, greater than 50%<br>output differential amplitude, repeat with VDUTx inputs reversed |

| Input Equivalent Rise/Fall Time                  |     | 110 |     | ps   | C <sub>B</sub> | $V_{DUT0} = 0.0 \text{ V}, V_{DUT1} = -0.5 \text{ V}$ to +0.5 V swing, drive term mode, VIT = 0.0 V, comparator threshold = 0.0 V, CLC = 1/4 scale, measured from digitized plot, t = $\sqrt{(t_{CMP}^2 - t_{IN}^2)}$              |

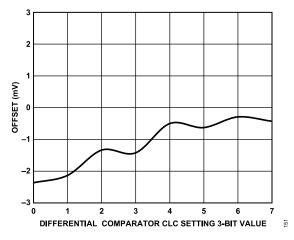

| Cable Loss Compensation (CLC)                    |     |     |     |      |                | $V_{DUT0} = 0.0 \text{ V}, V_{DUT1} = -0.8 \text{ V}$ to +0.8 V swing, drive term mode, VIT = 0.0 V, comparator threshold = 0.0 V, comparator CLC set to maximum CLC setting, repeat with VDUTx inputs reversed                    |

| CLC Amplitude                                    |     | 20  |     | %    | CB             |                                                                                                                                                                                                                                    |

| CLC Resolution                                   |     | 3   |     | Bits | D              |                                                                                                                                                                                                                                    |

| CLC Time Constant 1                              |     | 280 |     | ps   | S              |                                                                                                                                                                                                                                    |

| CLC Time Constant 2                              |     | 4.8 |     | ns   | S              |                                                                                                                                                                                                                                    |

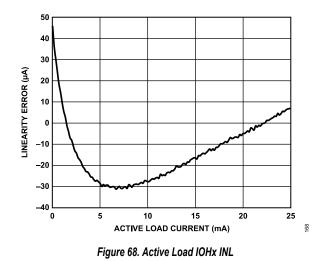

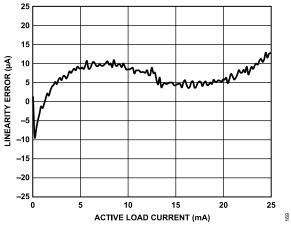

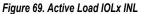

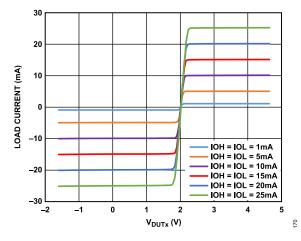

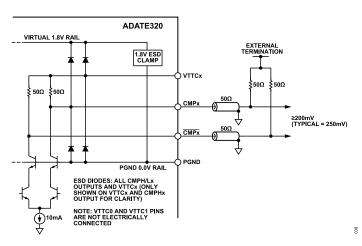

### ACTIVE LOAD SPECIFICATIONS

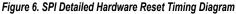

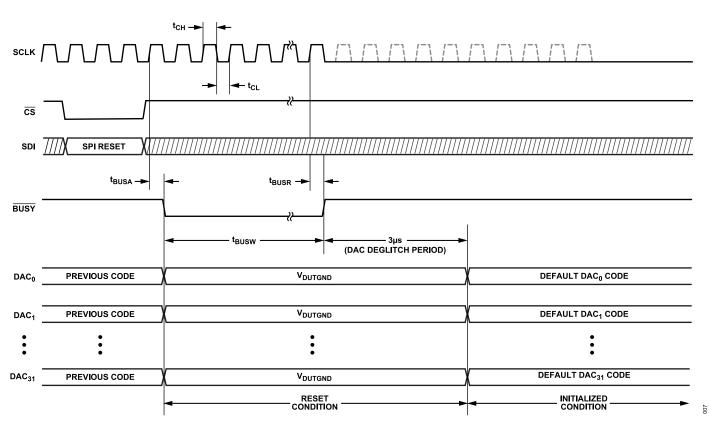

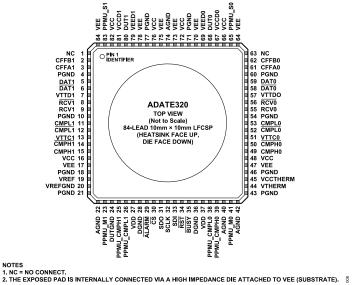

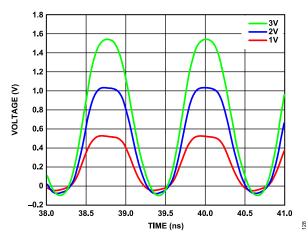

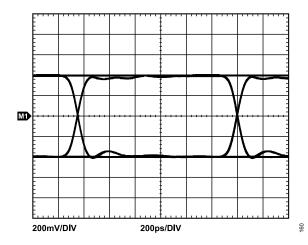

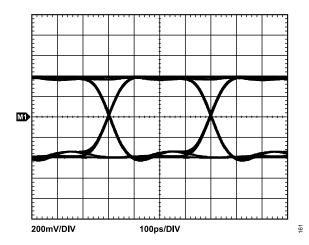

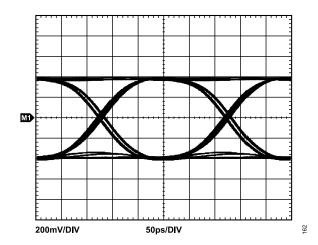

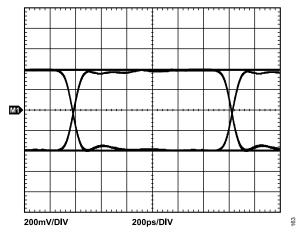

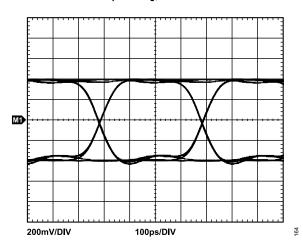

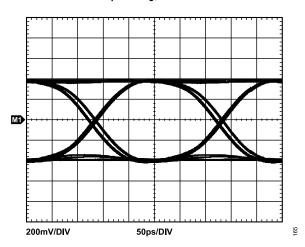

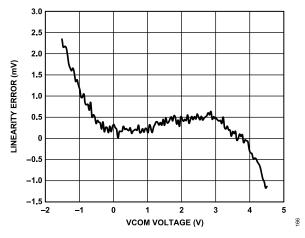

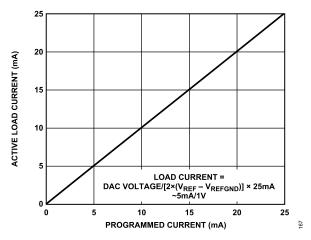

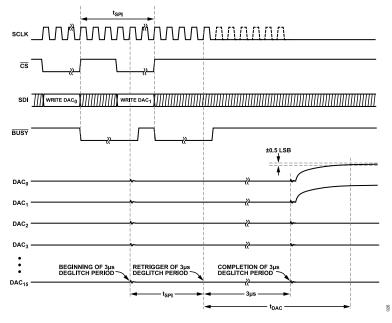

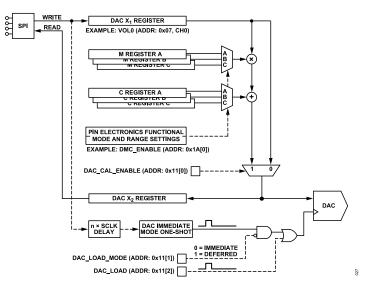

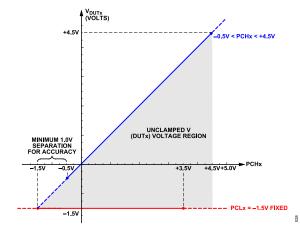

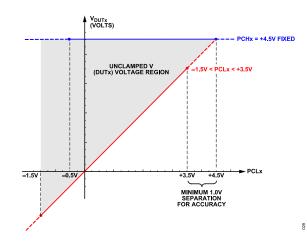

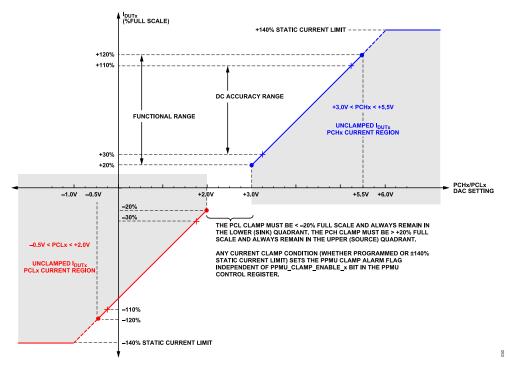

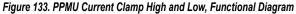

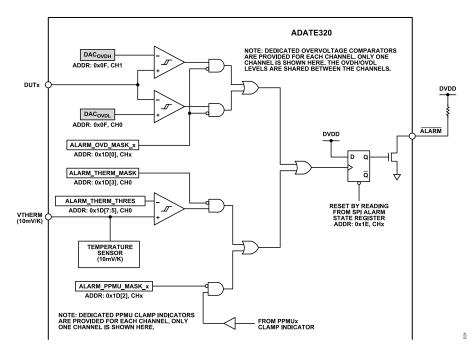

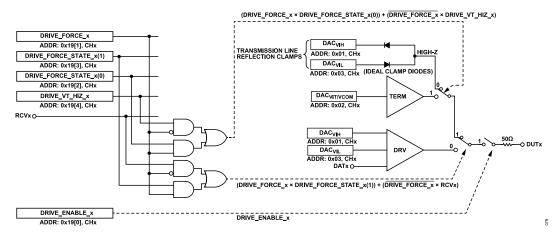

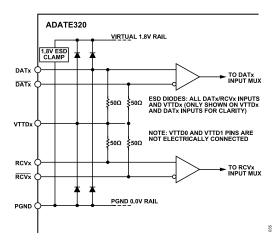

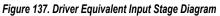

| Parameter                                        | Min  | Тур  | Max  | Unit       | Test Level | Test Conditions/Comments                                                                                                                                                                     |