# Programmable Transimpedance, Current to Bits Receiver µModule

Data Sheet ADA4355

### **FEATURES**

High performance, current input, data acquisition μModule that includes a TIA, analog filter, ADC driver, and ADC 3 selectable  $T_z$  settings:  $2 \, k\Omega$ ,  $20 \, k\Omega$ , and  $200 \, k\Omega$  Internal 1.8 V LDO for the ADC

All passive components including supply decoupling

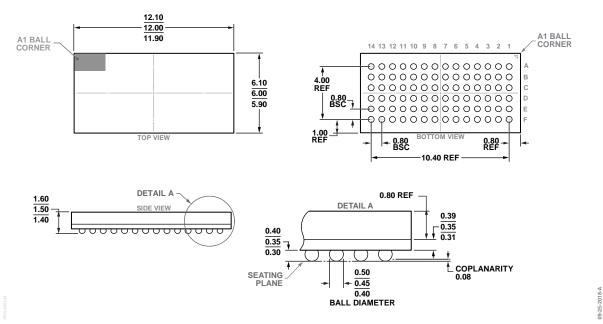

Small form factor: 12.00 mm  $\times$  6.00 mm CSP\_BGA

Operation from a single 3.3 V supply

Full-scale input current to 800  $\mu$ A (T<sub>z</sub> = 2 k $\Omega$ )

Fast input overload recovery

High analog input current to 40 mA

Analog filter for noise reduction and antialias filtering

Selectable 1.0 MHz and 100 MHz LPF bandwidth

Low input referred current noise: 16 pA rms

$T_z$  = 200 k $\Omega$ , 65,536 averages, 1 MHz analog filter

Supports input pulse widths down to 10 ns

14-bit ADC with sample rate up to 125 MSPS

Serial LVDS data output SPI control interface

Quiescent power: 546 mW, LDO enabled

Temperature range: -40°C to +85°C

### **APPLICATIONS**

Current to voltage conversion Chemical analyzers Mass spectroscopy Time of Flight Fiber optic sensing OTDR

**Optical amplifiers**

Reconfigurable optical add and drop multiplexers (ROADM)

### **GENERAL DESCRIPTION**

The ADA4355 is a complete, high performance, current input  $\mu$ Module\*. For space savings, the ADA4355 includes all the required active and passive components to realize a complete current to bits data acquisition solution, supporting a small form factor, optical modules as well as multichannel systems.

The high speed transimpedance amplifier (TIA) of the device supports 10 ns pulse widths, allowing high spatial resolution for Time of Flight (ToF) measurements. Additionally, the ADA4355 includes three TIA gain ( $T_Z$ ) settings to maximize dynamic range. An internal, selectable, analog low-pass filter (LPF) can limit the device bandwidth with a corner frequency of 100 MHz to minimize broadband noise while also serving as an antialiasing filter for the 125 MSPS ADC. For lower bandwidth signals, or wider signal pulses (for example, 20  $\mu s$  or wider), the filter can be set to a corner frequency of 1.0 MHz to provide additional noise reduction.

The 14-bit ADC converts the amplified voltage signal at a rate of up to 125 MSPS and outputs the digitized signals through two serial, low voltage differential signaling (LVDS) data lanes, operating at rates of up to 1 Gbps per lane. The data clock output (DCO) operates at frequencies of up to 500 MHz and supports double data rate (DDR) operation.

The ADA4355 exhibits fast overdrive recovery from a large input current signal and is available in a  $12.00 \text{ mm} \times 6.00 \text{ mm}$  CSP\_BGA package with a  $-40^{\circ}$ C to  $+85^{\circ}$ C operating temperature range.

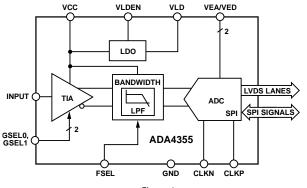

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

## **TABLE OF CONTENTS**

| Features1                                     |

|-----------------------------------------------|

| Applications 1                                |

| General Description1                          |

| Functional Block Diagram1                     |

| Revision History2                             |

| Specifications3                               |

| Performance Specifications                    |

| Power Specifications                          |

| CLK, SPI, and Control Specifications          |

| ADC SPI Timing Specifications6                |

| ADC LVDS Output Specifications                |

| Absolute Maximum Ratings                      |

| Thermal Resistance13                          |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions14 |

| Typical Performance Characteristics           |

| Equivalent Circuits                           |

| Theory of Operation26                         |

| Applications Information                      |

| Power and Power Control          | 27 |

|----------------------------------|----|

| Clocks                           | 27 |

| Clock Stability Considerations   | 29 |

| Controls                         | 29 |

| Digital Output and Timing        | 29 |

| OTDR Performance                 | 33 |

| PCB Design Tips                  | 36 |

| SPI                              | 37 |

| Configuration Using the SPI      | 37 |

| ADC SPI Start-Up Sequence        | 37 |

| Hardware Interface               | 37 |

| SPI Accessible Features          | 37 |

| Memory Map                       | 38 |

| Overview                         | 38 |

| Memory Map Register Table        | 39 |

| Memory Map Register Descriptions | 42 |

| Outline Dimensions               | 45 |

| Ordering Guide                   | 45 |

### **REVISION HISTORY**

10/2020—Revision A: Initial Version

## **SPECIFICATIONS**

### **PERFORMANCE SPECIFICATIONS**

$T_A = 25$ °C, VCC = 3.3 V, LDO enabled (see the power connection scheme shown in Figure 3), FSEL = 0, and the source capacitance ( $C_S$ ) = 0.5 pF, unless otherwise noted.

Table 1

| Parameter                                   | Test Conditions/Comments                                | Min  | Тур             | Max  | Unit   |

|---------------------------------------------|---------------------------------------------------------|------|-----------------|------|--------|

| INPUT                                       |                                                         |      |                 |      |        |

| Input Referred Current Noise, IN            | $T_Z = 2 k\Omega$                                       |      | 159             |      | nA rms |

|                                             | $T_Z = 20 \text{ k}\Omega$                              |      | 32              |      | nA rms |

|                                             | $T_Z = 200 \text{ k}\Omega$ , FSEL = 1                  |      | 4               |      | nA rms |

|                                             | $T_Z = 2 \text{ k}\Omega$ , 65,536 averages             |      | 621             |      | pA rms |

|                                             | $T_Z = 20 \text{ k}\Omega$ , 65,536 averages            |      | 125             |      | pA rms |

|                                             | $T_Z = 200 \text{ k}\Omega$ , 65,536 averages, FSEL = 1 |      | 16              |      | pA rms |

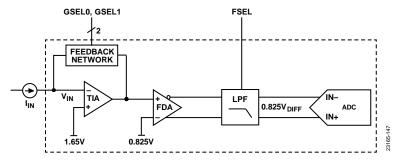

| Input Voltage, V <sub>IN</sub>              | See Figure 2                                            |      | 1.65            |      | V      |

| Input Bias Current, IB                      |                                                         |      | ±1              |      | nA     |

| Linear Input Current Range, I <sub>IN</sub> | $T_Z = 2 k\Omega$                                       |      | -80 to +800     |      | μΑ     |

|                                             | $T_Z = 20 \text{ k}\Omega$                              |      | -8.0 to +80     |      | μΑ     |

|                                             | $T_Z = 200 \text{ k}\Omega$                             |      | -0.8 to +8.0    |      | μΑ     |

| T <sub>z</sub> Gain Accuracy                | All gains                                               |      | ±1              | ±5   | %      |

| Input Capacitance                           |                                                         |      | 2.0             |      | pF     |

| ADC Input Bias Voltage                      | All gains, see Figure 2, $I_{IN} = 0 \mu A$             |      | 825             |      | mV     |

| AC PERFORMANCE                              |                                                         |      |                 |      |        |

| Input Referred Supply Sensitivity           | All gains                                               |      | 0.5             |      | nA/mV  |

| TIA Bandwidth                               | $T_Z = 2 k\Omega$                                       |      | 43              |      | MHz    |

|                                             | $T_Z = 20 \text{ k}\Omega$                              |      | 18              |      | MHz    |

|                                             | $T_Z = 200 \text{ k}\Omega$                             |      | 1.6             |      | MHz    |

| LPF Bandwidth                               | FSEL = 0                                                |      | 100             |      | MHz    |

|                                             | FSEL = 1                                                |      | 1.0             |      | MHz    |

| ADC PERFORMANCE                             |                                                         |      |                 |      |        |

| ADC Internal Reference Voltage (VREF)       |                                                         | 0.98 | 1               | 1.02 | V      |

| Resolution                                  |                                                         | 14   |                 |      | Bits   |

| Sampling Rate                               |                                                         | 20   |                 | 125  | MSPS   |

| No Missing Codes                            |                                                         |      | Guaranteed      |      |        |

| DIGITAL OUTPUTS, ANSI-644                   |                                                         |      |                 |      |        |

| Logic Compliance                            |                                                         |      | LVDS            |      |        |

| Differential Output Voltage, VoD            |                                                         | 290  | 345             | 400  | mV     |

| Output Offset Voltage, Vos                  |                                                         | 1.15 | 1.25            | 1.35 | V      |

| Output Coding (Default)                     |                                                         |      | Twos complement |      |        |

| OPERATION TEMPERATURE RANGE                 |                                                         | -40  |                 | +85  | °C     |

Figure 2. Internal Bias Voltages (FDA Is a Fully Differential Amplifier.)

### **POWER SPECIFICATIONS**

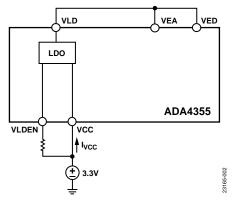

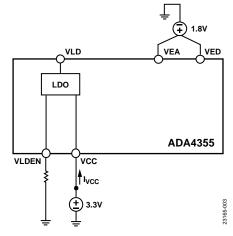

$T_A = 25$ °C and VCC = 3.3 V, unless otherwise noted. VEA and VED are the internal ADC 1.8 V supply rails, and VLD is the 1.8 V on-board LDO output.

Table 2.

| Parameter                         | Symbol           | Test Conditions/Comments   | Min | Тур           | Max | Unit |

|-----------------------------------|------------------|----------------------------|-----|---------------|-----|------|

| POWER SUPPLIES                    | VCC              |                            | 3.1 | 3.3           | 3.6 | V    |

| VCC Current                       | I <sub>VCC</sub> | See Figure 3, LDO enabled  |     | 165           |     | mA   |

|                                   |                  | See Figure 4, LDO disabled |     | 72            |     | mA   |

| <b>ADC Digital Circuit Supply</b> | VED              | See Figure 4, LDO disabled |     | $1.8 \pm 5\%$ |     | V    |

| VED Current                       | I <sub>VED</sub> |                            |     | 47            |     | mA   |

| ADC Analog Circuit Supply         | VEA              | See Figure 4, LDO disabled |     | $1.8 \pm 5\%$ |     | V    |

| VEA Current                       | I <sub>VEA</sub> |                            |     | 47            |     | mA   |

| On-Chip LDO Output                | VLD              | See Figure 3, LDO enabled  |     | 1.8           |     | V    |

| Quiescent Power                   | P <sub>Q</sub>   | See Figure 3, LDO enabled  |     | 546           |     | mW   |

|                                   |                  | See Figure 4, LDO disabled |     | 406           |     | mW   |

|                                   |                  | ADC power-down mode        |     | 238           |     | mW   |

|                                   |                  | ADC standby mode           |     | 322           |     | mW   |

Figure 3. On-Chip LDO Enabled

Figure 4. On-Chip LDO Disabled

### **CLK, SPI, AND CONTROL SPECIFICATIONS**

$T_A = 25^{\circ}\text{C}$ , VCC = 3.3 V, and LDO enabled (see the power scheme shown in Figure 3), unless otherwise noted.

Table 3.

| Parameter                                                       | <b>Test Conditions/Comments</b>                 | Min       | Тур              | Max       | Unit  |

|-----------------------------------------------------------------|-------------------------------------------------|-----------|------------------|-----------|-------|

| CLOCK INPUTS (CLKP AND CLKN)                                    |                                                 |           |                  |           |       |

| External Clock Frequency                                        |                                                 | 10        |                  | 1000      | MHz   |

| Conversion Rate                                                 |                                                 | 10        |                  | 125       | MSPS  |

| Logic Compliance                                                |                                                 |           | CMOS/LVDS/LVPECL |           |       |

| Differential Input Voltage                                      | For LVDS and LVPECL                             | 0.2       |                  | 3.6       | V p-p |

| Input Voltage Range                                             |                                                 | GND - 0.2 |                  | VEA + 0.2 | V     |

| Input Common-Mode Voltage                                       |                                                 |           | 0.9              |           | V     |

| Input Resistance (Differential)                                 |                                                 |           | 15               |           | kΩ    |

| Input Capacitance, C <sub>IN</sub>                              |                                                 |           | 4                |           | рF    |

| SERIAL PORT INTERFACE (SPI) CLOCK                               |                                                 |           |                  |           |       |

| SCLK Frequency                                                  |                                                 |           |                  | 25        | MHz   |

| SPI INPUTS (SCLK, CS, AND SDIO)                                 |                                                 |           |                  |           |       |

| Input High Voltage, V <sub>INH</sub>                            |                                                 | 1.2       |                  | VEA + 0.2 | V     |

| Input Low Voltage, V <sub>INL</sub>                             |                                                 | 0         |                  | 0.8       | V     |

| SCLK                                                            |                                                 |           |                  |           |       |

| Input Resistance, R <sub>IN</sub>                               |                                                 |           | 30               |           | kΩ    |

| C <sub>IN</sub>                                                 |                                                 |           | 2                |           | рF    |

| CS                                                              |                                                 |           |                  |           |       |

| R <sub>IN</sub>                                                 |                                                 |           | 26               |           | kΩ    |

| C <sub>IN</sub>                                                 |                                                 |           | 2                |           | рF    |

| SDIO                                                            |                                                 |           |                  |           |       |

| R <sub>IN</sub>                                                 |                                                 |           | 26               |           | kΩ    |

| C <sub>IN</sub>                                                 |                                                 |           | 5                |           | рF    |

| SPI OUTPUT (SDIO)                                               |                                                 |           |                  |           |       |

| Logic 1 Output Voltage                                          | High output current ( $I_{OH}$ ) = 800 $\mu$ A  |           | 1.79             |           | V     |

| Logic 0 Output Voltage                                          | Low output current ( $I_{OL}$ ) = 50 $\mu$ A    |           |                  | 0.05      | V     |

| OTHER CONTROL INPUTS (GSEL0, GSEL1, FSEL, AND VLDEN)            |                                                 |           |                  |           |       |

| V <sub>INH</sub>                                                |                                                 | 2         |                  | VCC       | ٧     |

| $V_{INL}$                                                       |                                                 | 0         |                  | 0.4       | ٧     |

| Input Low or High Current, I <sub>INL</sub> or I <sub>INH</sub> | Input voltage $(V_{IN}) = V_{INL}$ or $V_{INH}$ |           | 40               |           | nA    |

| CIN                                                             |                                                 |           | 2                |           | рF    |

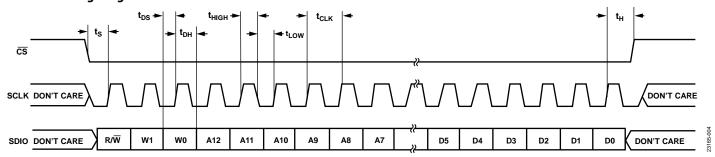

### **ADC SPI TIMING SPECIFICATIONS**

Table 4.

| Parameter                         | Description                                                                                   |    | Тур | Max | Unit |

|-----------------------------------|-----------------------------------------------------------------------------------------------|----|-----|-----|------|

| SPI TIMING REQUIREMENTS           | See Figure 5, unless otherwise noted                                                          |    |     |     |      |

| t <sub>DS</sub>                   | Setup time between the data and the rising edge of SCLK                                       | 2  |     |     | ns   |

| t <sub>DH</sub>                   | Hold time between the data and the rising edge of SCLK                                        | 2  |     |     | ns   |

| t <sub>CLK</sub>                  | Period of the SCLK                                                                            | 40 |     |     | ns   |

| <b>t</b> s                        | Setup time between CS and SCLK                                                                |    |     |     | ns   |

| t <sub>H</sub>                    | Hold time between CS and SCLK                                                                 |    |     |     | ns   |

| thigh                             | SCLK pulse width high                                                                         |    |     |     | ns   |

| t <sub>LOW</sub>                  | SCLK pulse width low                                                                          |    |     |     | ns   |

| t <sub>EN_SDIO</sub> <sup>1</sup> | Time required for SDIO to switch from an input to an output relative to the SCLK falling edge |    |     |     | ns   |

| t <sub>DIS_SDIO</sub> 1           | Time required for SDIO to switch from an output to an input relative to the SCLK rising edge  | 10 |     |     | ns   |

$<sup>^{\</sup>scriptscriptstyle 1}$  This parameter is not shown in Figure 5.

### **ADC SPI Timing Diagram**

Figure 5. Serial Port Interface Timing Diagram

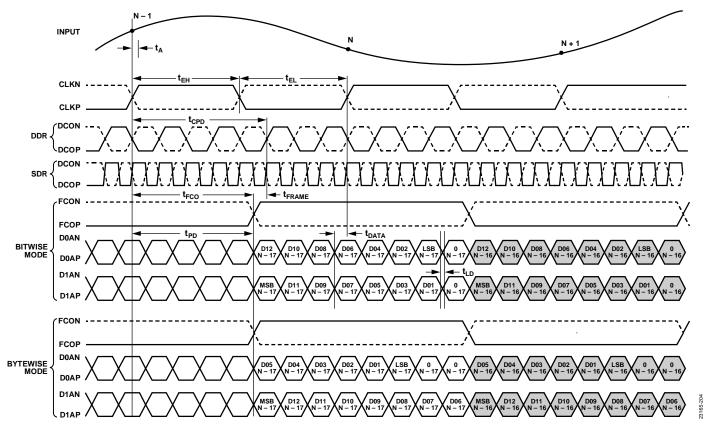

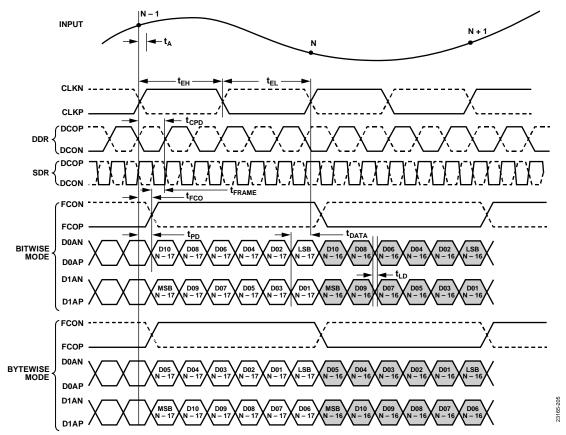

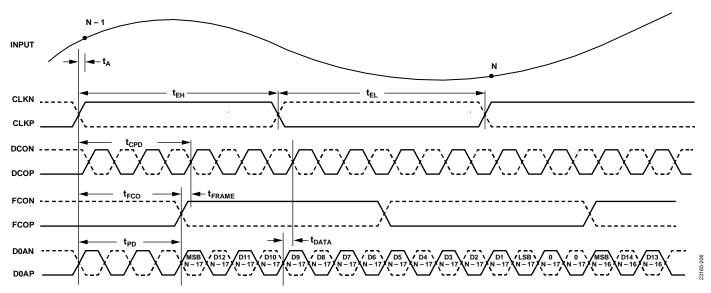

### **ADC LVDS OUTPUT SPECIFICATIONS**

Table 5.

| Parameter <sup>1, 2</sup>                                          | Temperature | Min                             | Тур                         | Max                     | Unit         |

|--------------------------------------------------------------------|-------------|---------------------------------|-----------------------------|-------------------------|--------------|

| CLOCK <sup>3</sup>                                                 |             |                                 |                             |                         |              |

| Input Rate                                                         | Full        | 10                              |                             | 1000                    | MHz          |

| Conversion Rate <sup>4</sup>                                       | Full        | 10                              |                             | 125                     | MSPS         |

| Pulse Width                                                        |             |                                 |                             |                         |              |

| High (t <sub>EH</sub> )                                            | Full        |                                 | 6.25 to 4.00                |                         | ns           |

| Low (t <sub>EL</sub> )                                             | Full        |                                 | 6.25 to 4.00                |                         | ns           |

| OUTPUT PARAMETERS <sup>3</sup>                                     |             |                                 |                             |                         |              |

| Propagation Delay, tPD                                             | Full        | 1.5                             | 2.3                         | 3.1                     | ns           |

| Rise Time, t <sub>R</sub> (20% to 80%) <sup>5</sup>                | Full        |                                 | 300                         |                         | ps           |

| Fall Time, t <sub>F</sub> (20% to 80%) <sup>5</sup>                | Full        |                                 | 300                         |                         | ps           |

| Frame Clock Output (FCO) Propagation Delay,                        | Full        | 1.5                             | 2.3                         | 3.1                     | ns           |

| <b>t</b> <sub>FCO</sub>                                            |             |                                 |                             |                         |              |

| DCO Propagation Delay, t <sub>CPD</sub> <sup>6</sup>               | Full        |                                 | $t_{FCO} + (t_{SAMPLE}/16)$ |                         | ns           |

| DCO to Data Delay, t <sub>DATA</sub> 6                             | Full        | $(t_{SAMPLE}/16) - 300$         | t <sub>SAMPLE</sub> /16     | $(t_{SAMPLE}/16) + 300$ | ps           |

| DCO to FCO Delay, t <sub>FRAME</sub> 6                             | Full        | (t <sub>SAMPLE</sub> /16) - 300 | t <sub>SAMPLE</sub> /16     | $(t_{SAMPLE}/16) + 300$ | ps           |

| Lane Delay, t <sub>LD</sub>                                        | Full        |                                 | 90                          |                         | ps           |

| Data to Data Skew, t <sub>DATA-MAX</sub> — t <sub>DATA-MIN</sub> 5 | Full        |                                 | ±50                         | ±200                    | ps           |

| Wake-Up Time (Standby)                                             | 25°C        |                                 | 250                         |                         | ns           |

| Wake-Up Time (Power-Down)                                          | 25°C        |                                 | 375                         |                         | μs           |

| Pipeline Latency                                                   | Full        |                                 | 16                          |                         | Clock cycles |

| APERTURE                                                           |             |                                 |                             |                         |              |

| Aperture Delay, t <sub>A</sub>                                     | 25°C        |                                 | 1                           |                         | ns           |

| Aperture Uncertainty (Jitter, t <sub>J</sub> ) <sup>5</sup>        | 25°C        |                                 | 174                         |                         | fs rms       |

| Out-of-Range Recovery Time                                         | 25°C        |                                 | 1                           |                         | Clock cycles |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for definitions and for details on how these tests were completed. <sup>2</sup> These parameters were measured on standard FR4 materials.

<sup>&</sup>lt;sup>3</sup> The clock can be adjusted via the SPI.

<sup>&</sup>lt;sup>4</sup> The conversion rate is the clock rate after the divider. Valid for 2-lane operation.

<sup>&</sup>lt;sup>5</sup> This parameter is not shown in Figure 6 through Figure 11.

$<sup>^6</sup>$   $t_{SAMPLE}/16$  is based on the number of bits in two LVDS data lanes.  $t_{SAMPLE} = 1/f$ .

#

Figure 6. 16-Bit DDR/Single Data Rate (SDR), Two-Lane, 1× Frame Mode (Default)

Figure 7. 12-Bit DDR/SDR, Two-Lane,  $1 \times$  Frame Mode

Figure 8. 16-Bit DDR/SDR, Two-Lane, 2× Frame Mode

Figure 9. 12-Bit DDR/SDR, Two-Lane, 2× Frame Mode

Figure 10. Wordwise DDR, One-Lane,  $1\times$  Frame, 16-Bit Output Mode

Figure 11. Wordwise DDR, One-Lane,  $1 \times$  Frame, 12-Bit Output Mode

### **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Table 0.                            |                                  |  |  |  |

|-------------------------------------|----------------------------------|--|--|--|

| Parameter                           | Rating                           |  |  |  |

| Electrical                          |                                  |  |  |  |

| VCC to GND                          | –0.3 V to +4.0 V                 |  |  |  |

| VEA, VED to GND                     | –0.3 V to +2.0 V                 |  |  |  |

| VLD to GND                          | −0.3 V to VCC                    |  |  |  |

| CLKP, CLKN, SPI <sup>1</sup> to GND | –0.3 V to +2.0 V                 |  |  |  |

| INPUT to GND                        | −0.2 V to VCC + 0.2 V            |  |  |  |

| Analog Input Current                | 40 mA                            |  |  |  |

| Control <sup>2</sup> to GND         | -0.3 V to VCC $+$ 0.3 V or 1 mA, |  |  |  |

|                                     | whichever occurs first           |  |  |  |

| Digital Output <sup>3</sup> to GND  | −0.3 V to +2.0 V                 |  |  |  |

| <b>Environmental Temperature</b>    |                                  |  |  |  |

| Storage Range (Ambient)             | −65°C to +125°C                  |  |  |  |

| Maximum Junction                    | 125°C                            |  |  |  |

| Electrostatic Discharge (ESD)       |                                  |  |  |  |

| Human Body Model                    |                                  |  |  |  |

| INPUT (Ball E1) and DNC             | 500 V                            |  |  |  |

| (Ball F1) Balls                     |                                  |  |  |  |

| All Other Balls                     | 3000 V                           |  |  |  |

| Field Induced Charge                | 1250 V                           |  |  |  |

| Device Model (FICDM)                |                                  |  |  |  |

| Assemble (Soldering, 10 sec)        | 300°C                            |  |  |  |

<sup>&</sup>lt;sup>1</sup> Includes SCLK, SDIO, and CS.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

Thermal resistance values specified in Table 7 are calculated based on standard JEDEC specifications.

Table 7. Thermal Resistance

| Package Type | θја  | <b>Ө</b> ЈС ТОР | $\Psi_{JT}$ | Unit |

|--------------|------|-----------------|-------------|------|

| BC-84-4      | 52.6 | 22.0            | 17.7        | °C/W |

Only use  $\theta_{JA}$  and  $\theta_{JC\ TOP}$  to compare thermal performance of the package of the device with other semiconductor packages when all test conditions listed are similar. One common mistake is to use  $\theta_{JA}$  and  $\theta_{JC}$  to estimate the junction temperature in the system environment. Instead, using  $\Psi_{JT}$  is a more appropriate way to estimate the worst case junction temperature of the device in the system environment. First, take an accurate thermal measurement of the top center of the device (on the mold compound in this case) while the device operates in the system environment. This measurement is known in the following equation as  $T_{TOP}$ .

Then, use this equation to solve for the worst case  $T_J$  in that given environment as follows:

$$T_I = \Psi_{IT} \times P + T_{TOP}$$

where:

$\Psi_{JT}$  is the junction to top thermal characterization number as specified in the data sheet.

*P* refers to the total power dissipation in the chip (W).

$T_{TOP}$  refers to the package top temperature (°C) and is measured at the top center of the package in that given environment.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Includes FSEL, GSEL1, GSEL0, and VLDEN.

<sup>&</sup>lt;sup>3</sup> Includes DOAP, DOAN, D1AP, D1AN, DCOP, DCON, FCOP, and FCON.

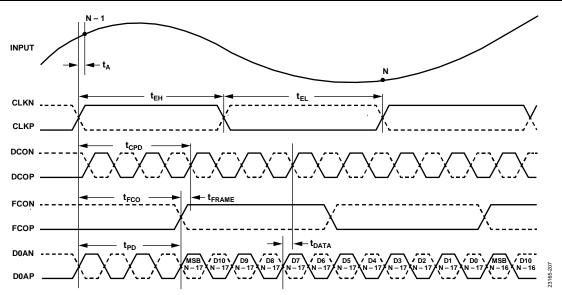

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

ADA4355 TOP VIEW (BALL SIDE DOWN)

NOTES

1. DO NOT CONNECT. THESE BALLS ARE RESERVED.

Figure 12. Ball Configuration

**Table 8. Ball Configuration and Function Descriptions**

| Ball No.                                                                                           | Mnemonic     | Type <sup>1</sup> | Description                                                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------|--------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1, A8, A12, B1 to B6, B9, B10, B12, C1, C2, C6 to C12, D1, D6, D10 to D12, E2, E3, E6, E7, E9, F9 | GND          | Р                 | Ground.                                                                                                                                                                                                 |  |

| A3, C3 to C5, D3 to D5, F3 to F6, F8                                                               | VCC          | Р                 | 3.3 V Power Supply.                                                                                                                                                                                     |  |

| E10                                                                                                | VEA          | Р                 | 1.8 V Analog Power Supply to ADC.                                                                                                                                                                       |  |

| E12                                                                                                | VED          | Р                 | 1.8 V Digital Power Supply to ADC.                                                                                                                                                                      |  |

| F12                                                                                                | VLD          | РО                | 1.8 V LDO Output. Connect VLD to VEA and VED to power the ADC from the internal LDO or leave VLD floating if the ADC is powered from the external source. Do not connect VLD to the external circuitry. |  |

| F7                                                                                                 | VLDEN        | DI                | VLD Output Enable. Set VLDEN = 1 to enable the VLD output.                                                                                                                                              |  |

| A6                                                                                                 | FSEL         | DI                | LPF Bandwidth Select. FSEL selects the 100 MHz (FSEL = 0) or 1.0 MHz (FSEL = 1) LPF bandwidth.                                                                                                          |  |

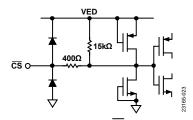

| A10                                                                                                | CS           | DI                | Chip Select. Set $\overline{CS} = 0$ to enable SPI mode. $\overline{CS}$ has an internal 15 k $\Omega$ pull-up resistor.                                                                                |  |

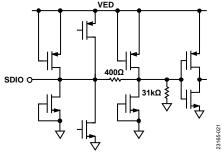

| B11                                                                                                | SDIO         | DIO               | Serial Data Input/Output. In SPI mode, SDIO is a bidirectional SPI data input/output with a 31 $\rm k\Omega$ internal pull-down resistor.                                                               |  |

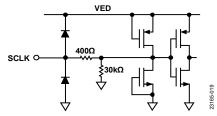

| A11                                                                                                | SCLK         | DI                | SPI Clock Input in SPI Mode. SCLK has a 30 kΩ internal pull-down resistor.                                                                                                                              |  |

| D13, D14                                                                                           | DCON, DCOP   | DO                | Data Clock Outputs, Differential.                                                                                                                                                                       |  |

| C13, C14                                                                                           | FCON, FCOP   | DO                | Frame Clock Outputs, Differential.                                                                                                                                                                      |  |

| B13, B14                                                                                           | D1AN, D1AP   | DO                | Lane 1 Digital Outputs, Differential.                                                                                                                                                                   |  |

| A13, A14                                                                                           | D0AN, D0AP   | DO                | Lane 0 Digital Outputs, Differential.                                                                                                                                                                   |  |

| F11, E11                                                                                           | CLKP, CLKN   | DI                | ADC Sampling Clock Inputs, Differential.                                                                                                                                                                |  |

| A4, A5                                                                                             | GSEL0, GSEL1 | DI                | TIA Gain Selection. See Table 9 for the truth table.                                                                                                                                                    |  |

| E1                                                                                                 | INPUT        | Al                | Analog Input. Connect INPUT to a reversed biased photodiode anode.                                                                                                                                      |  |

| A2, A7, A9, B7, B8, D2, D7 to D9, E4, E5,<br>E8, E13, E14, F1, F2, F10, F13, F14                   | DNC          | N/A               | Do Not Connect. These balls are reserved.                                                                                                                                                               |  |

<sup>&</sup>lt;sup>1</sup> P means power, PO means power output, DI means data input, DIO means data input/output, DO means data output, AI means analog input, and N/A means not applicable.

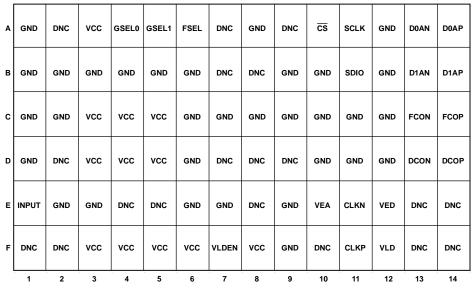

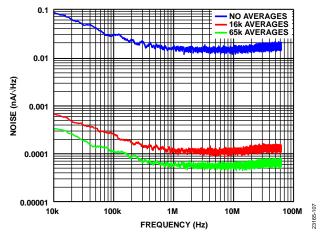

### TYPICAL PERFORMANCE CHARACTERISTICS

T<sub>A</sub> = 25°C, VCC = 3.3 V, no averaging, and LDO enabled (see the power scheme shown in Figure 3), unless otherwise noted.

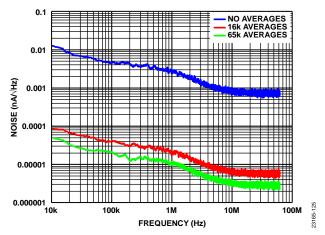

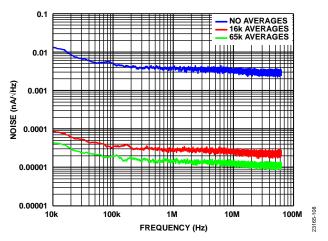

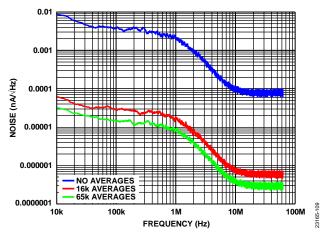

Figure 13. Noise Spectral Density,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

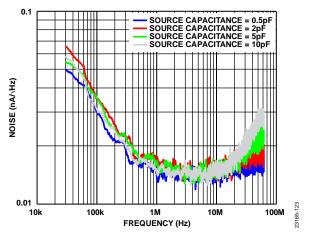

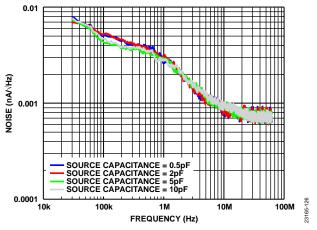

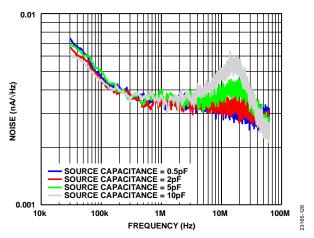

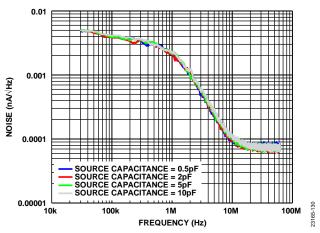

Figure 14. Noise Spectral Density for Various Source Capacitances,  $T_z$  = 2 k $\Omega$ , LPF = 100 MHz

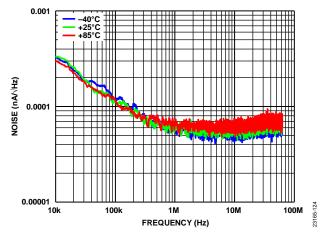

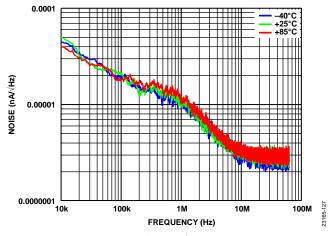

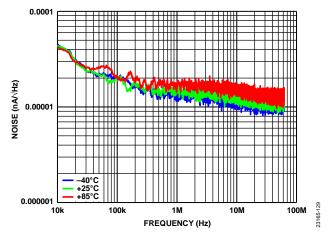

Figure 15. Noise Spectral Density for Various Temperatures,  $T_z$  = 2  $k\Omega$ , LPF = 100 MHz

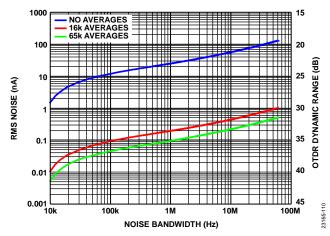

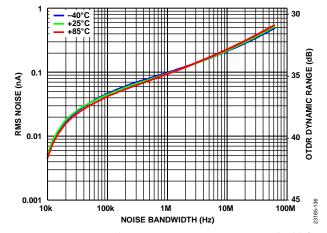

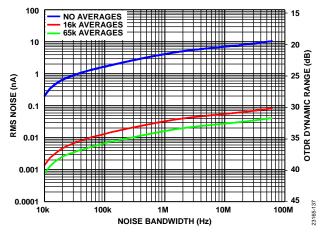

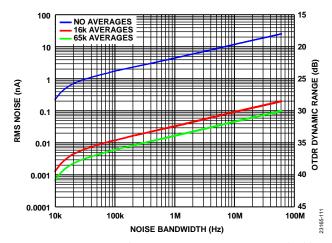

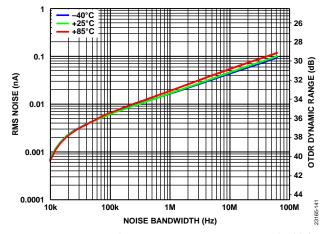

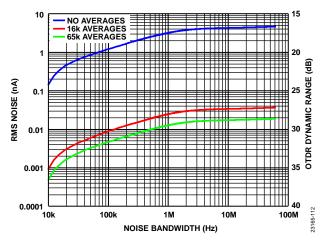

Figure 16. RMS Noise and Optical Time Domain Reflectometry (OTDR) Dynamic Range vs. Noise Bandwidth,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

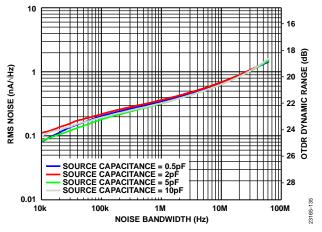

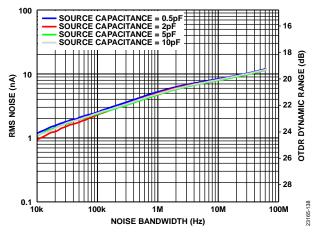

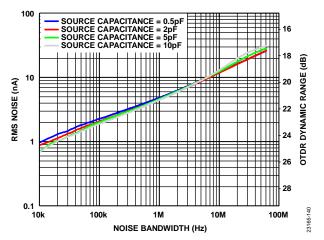

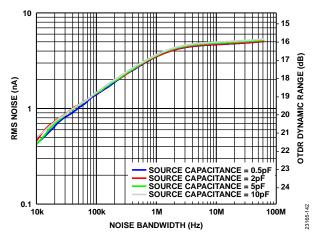

Figure 17. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Source Capacitances,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

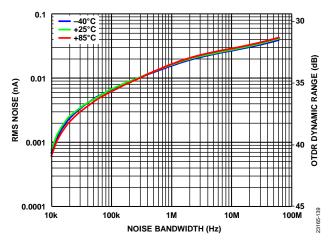

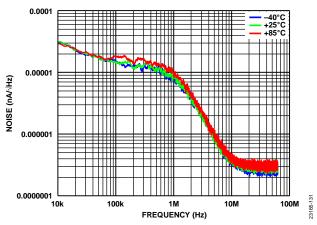

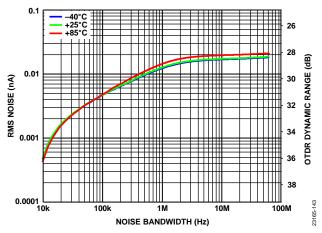

Figure 18. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Temperatures,  $T_z = 2 k\Omega$ , LPF = 100 MHz

Figure 19. Noise Spectral Density,  $T_Z = 20 \text{ k}\Omega$ , LPF = 1 MHz

Figure 20. Noise Spectral Density for Various Source Capacitances,  $T_Z = 20 \, k\Omega$ , LPF = 1 MHz

Figure 21. Noise Spectral Density for Various Temperatures,  $T_Z = 20 \text{ k}\Omega$ , LPF = 1 MHz

Figure 22. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth,  $T_Z = 20 \ k\Omega$ , LPF = 1 MHz

Figure 23. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Source Capacitances,  $T_Z = 20 \, k\Omega$ , LPF = 1 MHz

Figure 24. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Temperatures,  $T_Z = 20 \, k\Omega$ , LPF = 1 MHz

Figure 25. Noise Spectral Density,  $T_Z = 20 \text{ k}\Omega$ , LPF = 100 MHz

Figure 26. Noise Spectral Density for Various Source Capacitances,  $T_Z$  = 20 k $\Omega$ , LPF = 100 MHz

Figure 27. Noise Spectral Density for Various Temperatures,  $T_Z$  = 20 k $\Omega$ , LPF = 100 MHz

Figure 28. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth,  $T_Z$  = 20 k $\Omega$ , LPF = 100 MHz

Figure 29. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Source Capacitances,  $T_Z = 20 \text{ k}\Omega$ , LPF = 100 MHz

Figure 30. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Temperatures,  $T_z$  = 20 k $\Omega$ , LPF = 100 MHz

Figure 31. Noise Spectral Density,  $T_Z = 200 k\Omega$ , LPF = 1 MHz

Figure 32. Noise Spectral Density for Various Source Capacitances,  $T_Z = 200 \, k\Omega$ , LPF = 1 MHz

Figure 33. Noise Spectral Density for Various Temperatures,  $T_Z = 200 \, k\Omega$ , LPF = 1 MHz

Figure 34. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth,  $T_Z$  = 200 k $\Omega$ , LPF = 1 MHz

Figure 35. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Source Capacitances,  $T_Z = 200 \, k\Omega$ , LPF = 1 MHz

Figure 36. RMS Noise and OTDR Dynamic Range vs. Noise Bandwidth for Various Temperatures,  $T_Z = 200 \, k\Omega$ , LPF = 1 MHz

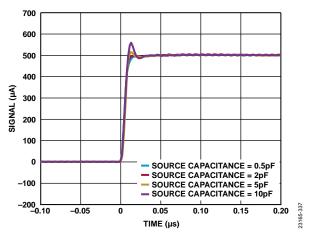

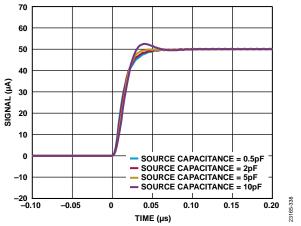

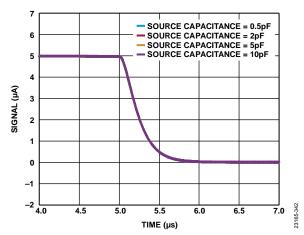

Figure 37. Pulse Response Rising Edge for Various Source Capacitances,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

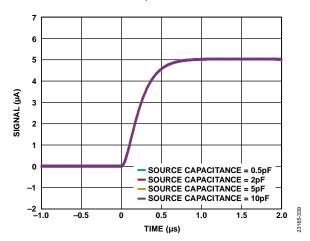

Figure 38. Pulse Response Rising Edge for Various Source Capacitances,  $T_Z = 20 \, k\Omega$ , LPF = 100 MHz

Figure 39. Pulse Response Rising Edge for Various Source Capacitances,  $T_Z = 200 \, k\Omega$ , LPF = 1 MHz

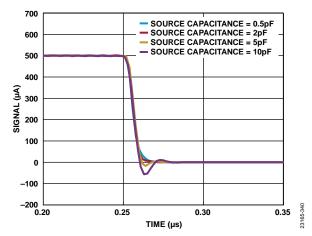

Figure 40. Pulse Response Falling Edge for Various Source Capacitances,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

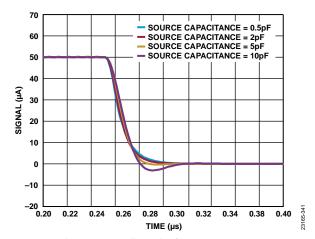

Figure 41. Pulse Response Falling Edge for Various Source Capacitances,  $T_Z = 20 \text{ k}\Omega$ , LPF = 100 MHz

Figure 42. Pulse Response Falling Edge for Various Source Capacitances,  $T_Z$  = 200 k $\Omega$ , LPF = 1 MHz

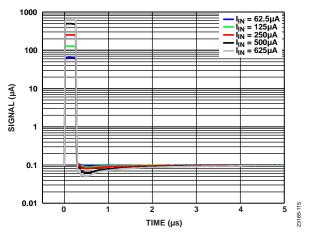

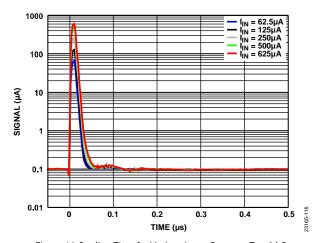

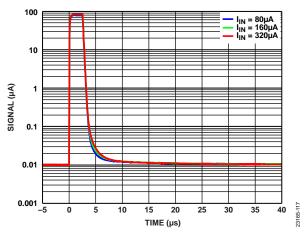

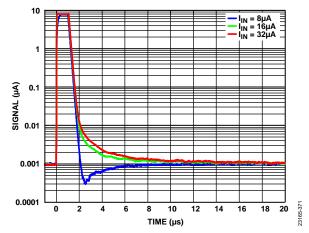

Figure 43. Settling Time for Various Input Currents,  $T_Z = 2 k\Omega$ , 250 ns Pulse Width, LPF = 100 MHz

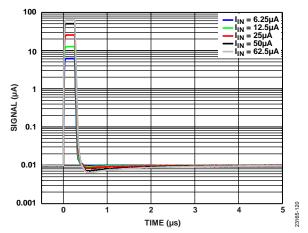

Figure 44. Settling Time for Various Input Currents,  $T_Z = 20 \text{ k}\Omega$ , 2.5  $\mu$ s Pulse Width, LPF = 1 MHz

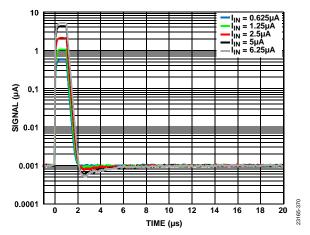

Figure 45. Settling Time for Various Input Currents,  $T_Z$  = 200 k $\Omega$ , 5  $\mu$ s Pulse Width, LPF = 1 MHz

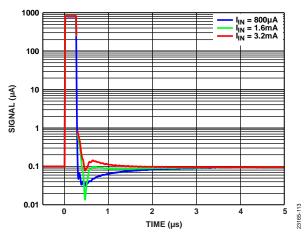

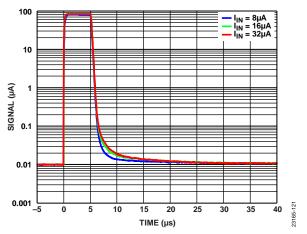

Figure 46. Settling Time for Various Input Currents,  $T_Z = 2 k\Omega$ , 10 ns Pulse Width, LPF = 100 MHz

Figure 47. Settling Time for Various Input Currents,  $T_Z = 20 \text{ k}\Omega$ , 250 ns Pulse Width, LPF = 100 MHz

Figure 48. Settling Time for Various Input Currents,  $T_z$  = 200 k $\Omega$ , 1  $\mu$ s Pulse Width, LPF = 100 MHz

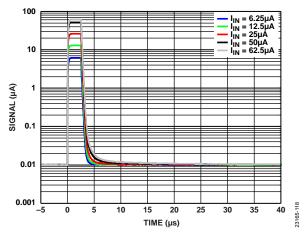

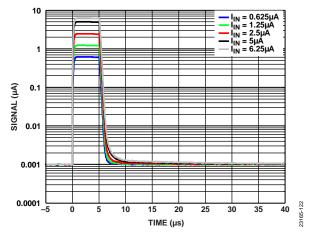

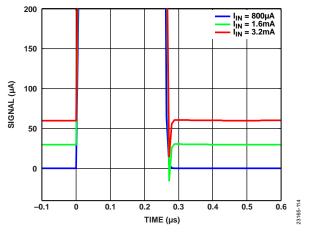

Figure 49. Overload Recovery,  $T_z = 2 k\Omega$ , 250 ns Pulse Width, LPF = 100 MHz

Figure 50. Overload Recovery,  $T_z = 20 \text{ k}\Omega$ , 2.5  $\mu$ s Pulse Width, LPF = 1 MHz

Figure 51. Overload Recovery,  $T_z = 200 \text{ k}\Omega$ , 5  $\mu$ s Pulse Width, LPF = 1 MHz

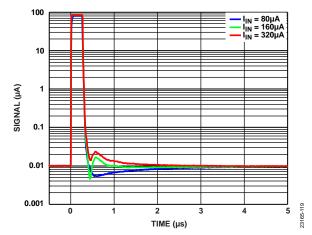

Figure 52. Overload Recovery (Zoomed In),  $T_Z = 2 k\Omega$ , 250 ns Pulse Width, LPF = 100 MHz (Traces Offset Vertically for Readability)

Figure 53. Overload Recovery,  $T_Z = 20 \text{ k}\Omega$ , 250 ns Pulse Width, LPF = 100 MHz

Figure 54. Overload Recovery,  $T_z = 200 \text{ k}\Omega$ , 1  $\mu$ s Pulse Width, LPF = 100 MHz

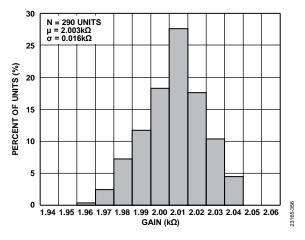

Figure 55. TIA Gain Distribution,  $T_z = 2 k\Omega$

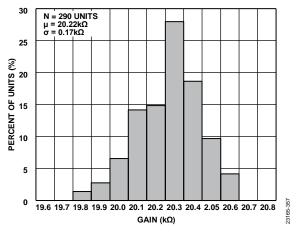

Figure 56. TIA Gain Distribution,  $T_Z = 20 \text{ k}\Omega$

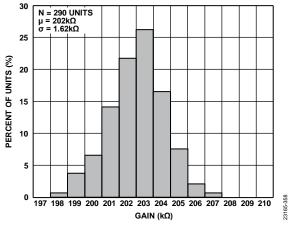

Figure 57. TIA Gain Distribution,  $T_Z = 200 \text{ k}\Omega$

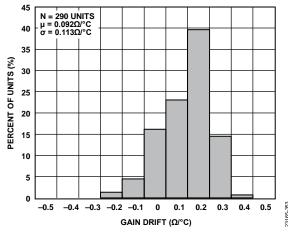

Figure 58. TIA Gain Drift Distribution,  $T_Z = 2 k\Omega$

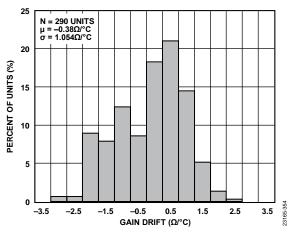

Figure 59. TIA Gain Drift Distribution,  $T_Z = 20 \text{ k}\Omega$

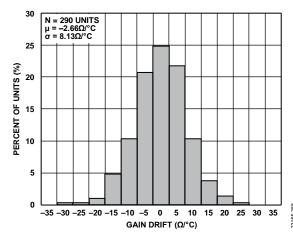

Figure 60. TIA Gain Drift Distribution,  $T_z = 200 \text{ k}\Omega$

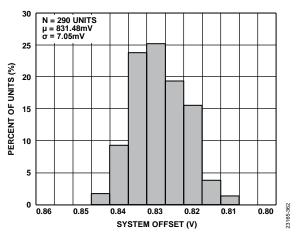

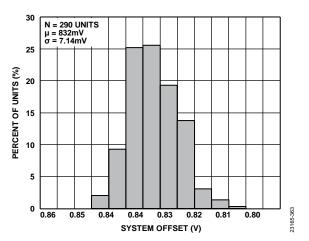

Figure 61. System Offset Distribution,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

Figure 62. System Offset Distribution,  $T_Z = 20 k\Omega$ , LPF = 100 MHz

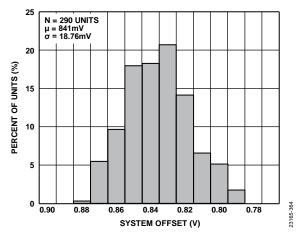

Figure 63. System Offset Distribution,  $T_Z = 200 \text{ k}\Omega$ , LPF = 1 MHz

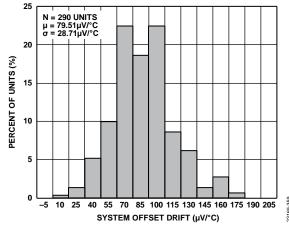

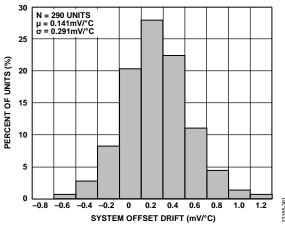

Figure 64. System Offset Drift Distribution,  $T_Z = 2 k\Omega$ , LPF = 100 MHz

Figure 65. System Offset Drift Distribution,  $T_Z = 20 \text{ k}\Omega$ , LPF = 100 MHz

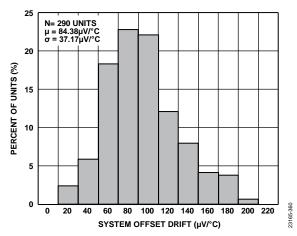

Figure 66. System Offset Drift Distribution,  $T_Z = 200 \text{ k}\Omega$ , LPF = 1 MHz

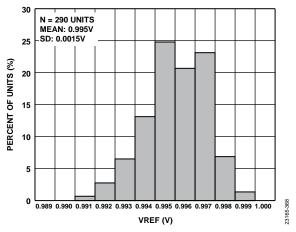

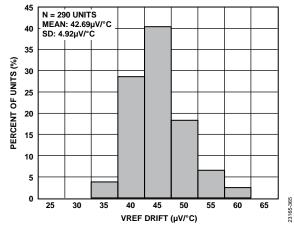

Figure 67. ADC Internal Reference Voltage (VREF) Distribution

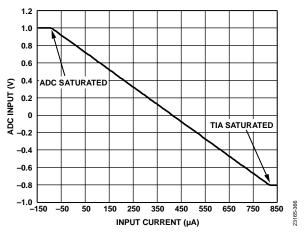

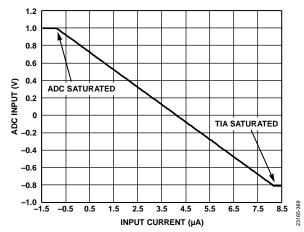

Figure 68. ADC Input Voltage vs. Input Current,  $T_Z = 2 k\Omega$

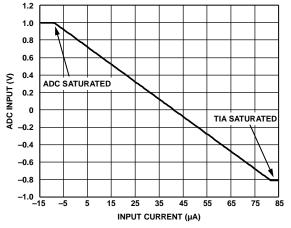

Figure 69. ADC Input Voltage vs. Input Current,  $T_Z = 20 \text{ k}\Omega$

Figure 70. ADC Internal VREF Drift Distribution

Figure 71. ADC Input Voltage vs. Input Current,  $T_Z = 200 \text{ k}\Omega$

# **EQUIVALENT CIRCUITS**

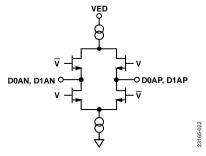

Figure 72. Equivalent Digital Output Circuit

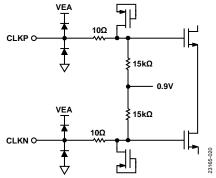

Figure 73. Equivalent Clock Input Circuit

Figure 74. Equivalent SDIO Input Circuit

Figure 75. Equivalent SCLK Input Circuit

Figure 76. Equivalent  $\overline{CS}$  Input Circuit

### THEORY OF OPERATION

The ADA4355 integrates a field effect transistor (FET), input TIA with three switchable gains (2 k $\Omega$ , 20 k $\Omega$ , and 200 k $\Omega$ ). The gain switches are designed to minimize error sources that result in slow settling time and slow overload recovery. The internal overload current protection allows the input current to exceed the full-scale current while still providing fast overload recovery. Additionally, the overload current protection enables analog input current levels up to 40 mA to be sustained with no damage to the TIA. The positive node of the TIA is biased to 1.65 V as shown in Figure 2.

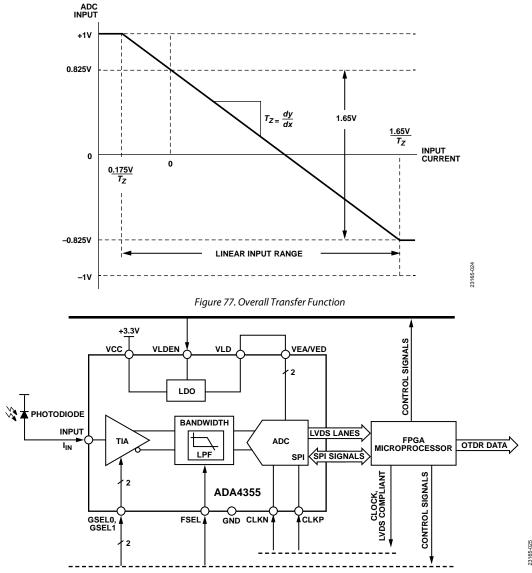

Figure 77 shows the overall system transfer function. Because the photodetector provides current in only one direction (sink or source), the overall transfer function has 0.825 V offset to maximize the input range of the ADC. When the input current is 0  $\mu A$ , the ADC differential input is 0.825 V. As the input current increases, the TIA output decreases toward GND. When the input current reaches 1.65 V/Tz, the TIA output is at GND, limiting the ADC differential input voltage to -0.825 V. The positive full-scale input current is 1.65 V/Tz, and there is room to measure negative input current down to -0.175 V/Tz.

Figure 78. Typical Application Block Diagram with a Single  $V_{CC}$  Supply, FPGA Control, and Data Process

## APPLICATIONS INFORMATION

### **POWER AND POWER CONTROL**

The  $12 \text{ mm} \times 6 \text{ mm}$  CSP\_BGA has multiple balls designated to support the ADA4355 power requirements, with 12 balls assigned to VCC, and one ball each to VEA, VED, and VLD.

Connect VCC to a clean 3.3 V supply to provide power to the ADA4355 analog core and on-chip LDO. It is important to connect all VCC balls to the 3.3 V supply. VLD is the on-chip 1.8 V LDO output, and VEA and VED are the ADC supply balls.

To power the ADC via the on-chip LDO, connect VLD to VEA and VED, and pull VLDEN high (see Figure 3).

If external 1.8 V supplies are desired, disable the on-chip LDO by pulling VLDEN low and connect VEA and VED to an external 1.8 V supply (see Figure 4).

#### Ground

The ADA4355 has multiple balls assigned as GND. There is no connection between the GND balls inside the package. Therefore, connect all GND balls to a low impedance GND plane on the PCB.

#### **CLOCKS**

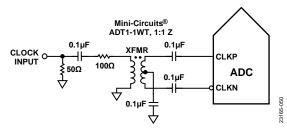

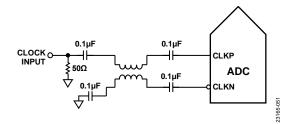

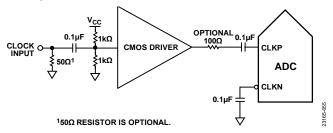

For optimum performance, drive the ADC sample clock inputs, CLKP and CLKN, with a differential signal. The clock signal is typically ac-coupled into the CLKP and CLKN balls via a transformer or capacitors. These balls are biased internally (see Figure 73) and require no external bias.

### **Clock Input Options**

The ADA4355 has a flexible clock input structure. The clock input can be a CMOS, LVDS, low voltage, positive emitter coupled logic (LVPECL), or sine wave signal. Regardless of the type of signal used, clock source jitter is an important consideration, as described in the Jitter Considerations section.

Figure 79 and Figure 80 show two preferred methods for clocking the ADA4355 (at clock rates up to 1 GHz prior to the internal clock divider). A low jitter clock source is converted from a single-ended signal to a differential signal using either an RF transformer or an RF balun.

Figure 79. Transformer-Coupled Differential Clock (Up to 200 MHz)

Figure 80. Balun-Coupled Differential Clock (up to 1 GHz)

The RF balun configuration is recommended for clock frequencies between 125 MHz and 1 GHz, and the RF transformer configuration is recommended for clock frequencies from 10 MHz to 200 MHz.

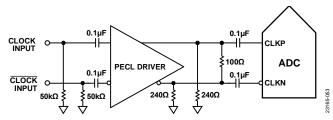

If a low jitter clock source is not available, another option is to ac couple a differential PECL signal to the sample clock input balls, as shown in Figure 81. The AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516-0/AD9516-1/AD9516-2/AD9516-3/AD9516-4/AD9516-5/AD9517-0/AD9517-1/AD9517-2/AD9517-3/AD9517-4 PECL drivers offer excellent jitter performance.

Figure 81. Differential PECL Sample Clock (up to 1 GHz)

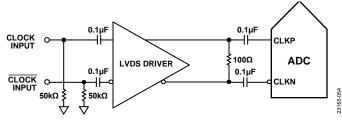

A third option is to ac couple a differential LVDS signal to the sample clock input balls, as shown in Figure 82. The AD9510/AD9511/AD9512/AD9513/AD9514/AD9515/AD9516-0/AD9516-1/AD9516-2/AD9516-3/AD9516-4/AD9516-5/AD9517-0/AD9517-1/AD9517-2/AD9517-3/AD9517-4 LVDS drivers offer excellent jitter performance.

Figure 82. Differential LVDS Sample Clock (up to 1 GHz)

In some applications, it may be acceptable to drive the sample clock inputs with a single-ended 1.8 V CMOS signal. In such applications, drive the CLKP ball directly from a CMOS gate, and bypass the CLKN ball to ground with a 0.1  $\mu$ F capacitor (see Figure 83).

Figure 83. Single-Ended 1.8 V CMOS Input Clock (up to 200 MHz)

### **Input Clock Divider**

The ADA4355 contains an input clock divider that can divide the input clock by integer values from 1 to 8. The power-on default, clock divider ratio is always 1. If a different clock divide ratio is required, change SPI Register 0x0B. To achieve a given sample rate, multiply the frequency of the externally applied clock by the divide value. The increased rate of the external clock normally results in lower clock jitter, which is beneficial for intermediate frequency (IF) undersampling applications.

### **Clock Duty Cycle**

The ADC uses both clock edges to generate a variety of internal timing signals and, as a result, can be sensitive to the clock duty cycle. Commonly, a  $\pm 5\%$  tolerance is required on the clock duty cycle to maintain dynamic performance characteristics.

The ADA4355 offers a duty cycle stabilizer (DCS) that retimes the nonsampling (falling) edge, providing an internal clock signal with a nominal 50% duty cycle. The DCS allows the user to provide a wide range of clock input duty cycles without affecting the performance of the ADA4355. Noise and distortion performance are nearly unchanged for a wide range of duty cycles with the DCS on. To bypass DCS, the user can change SPI Register 0x09.

Jitter in the rising edge of the clock is still a concern and is not easily reduced by the internal stabilization circuit. The duty cycle control loop does not function for clock rates <20 MHz, nominally. The loop has a time constant associated with it that must be considered in applications where the clock rate can change dynamically. A wait time of 5  $\mu$ s is required after a dynamic clock frequency increase or decrease before the DCS loop relocks to the input signal.

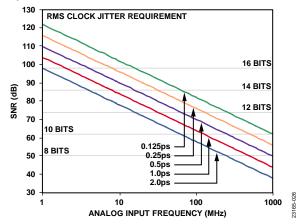

#### **Jitter Considerations**

High speed, high resolution ADCs are sensitive to the quality of the clock input. The following equation shows how signal-to-noise ratio (SNR) degrades at a given input frequency ( $f_A$ ) due only to aperture jitter ( $t_1$ ):

$$SNR \ Degradation = 20 \log_{10} \left( \frac{1}{2\pi \times f_A \times t_J} \right)$$

In this equation, the rms aperture jitter represents the rms of all jitter sources, including the clock input, analog input signal, and ADC aperture jitter specifications. IF undersampling applications are particularly sensitive to jitter. The effect of jitter alone on SNR, with no other noise contributors, is shown in Figure 84.

Figure 84. Ideal SNR vs. Analog Input Frequency and Jitter

Treat the clock input as an analog signal when aperture jitter can affect the dynamic range of the ADA4355. Separate clock driver power supplies from the ADC output driver supplies to avoid modulating the clock signal with digital noise. Low jitter, crystal oscillators are the best clock sources. If the clock is generated from another type of source (by gating, dividing, or other methods), it is recommended to retime the clock by the original clock as the last step.

See the AN-501 Application Note and the AN-756 Application Note for more information about jitter performance as it relates to the internal ADC of the ADA4355.

### **CLOCK STABILITY CONSIDERATIONS**

Immediately after power-on, the ADA4355 enters an initialization phase during which an internal state machine sets up the biases and the registers for proper operation. During the initialization process, the ADA4355 needs a stable clock. If the clock source to the ADC is not present or not stable during ADC power-up, it disrupts the state machine and causes the ADC to start up in an unknown state. To correct this, invoke a digital reset via Register 0x08 after the clock source is stable. Clock instability during normal operation may also necessitate a digital reset to restore proper operation.

The pseudo code sequence for a digital reset is as follows:

- 1. Write Register 0x08 = 0x03 for a digital reset.

- 2. Write Register 0x08 = 0x00 for normal operation.

#### **CONTROLS**

The ADA4355 uses four balls to control various functions of the analog front end. Use the GSEL1 and GSEL0 balls to select  $T_Z$  (see Table 9), use the VLDEN ball to enable or disable the on-chip LDO, and use FSEL to select the filter bandwidth for the internal LPF. These control balls must be driven as these balls have no internal pull-up or pull-down resistors.

### **Transimpedance Gain and Performance Controls**

Each  $T_Z$  determines its relevant saturation current ( $I_{SAT}$ ) and input referred rms current noise ( $I_N$ ). The GSEL0 and GSEL1 balls work together as shown in Table 9.

Table 9. Truth Table for GSEL1 and GEL0

| GSEL1 (Ball A5) | GSEL0 (Ball A4) | Transimpedance (Tz)         |

|-----------------|-----------------|-----------------------------|

| 0               | 1               | $T_Z = 2 k\Omega$           |

| 1               | 0               | $T_Z = 20 \text{ k}\Omega$  |

| 0               | 0               | $T_Z = 200 \text{ k}\Omega$ |

| 1               | 1               | Reserved                    |

#### **LDO Enable Controls**

The on-chip 1.8 V LDO is controlled via the VLDEN ball. The control signal vs. LDO output are shown in Table 10.

Table 10. LDO Control Signal Truth Table

| VLDEN (Ball F7) | VLD (Ball F12) |

|-----------------|----------------|

| 0               | No output      |

| 1               | 1.8 V          |

#### LPF Bandwidth Selection

The ADA4355 uses an internal analog LPF to optimize settling time and noise performance. The LPF is controlled via the FSEL ball as shown in Table 11. Input signal pulse width should be considered when choosing the LPF bandwidth.

Table 11. LPF Truth Table

| FSEL (Ball A6) | LPF Bandwidth (MHz) |

|----------------|---------------------|

| 0              | 100                 |

| 1              | 1                   |

#### **DIGITAL OUTPUT AND TIMING**

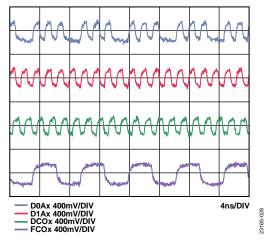

The ADA4355 supports high speed, digital serial outputs. These serial differential outputs are LVDS-compatible data and clock lanes. These output lanes include the D0AP, D0AN, D1AP, D1AN, DCOP, DCON, FCOP, and FCON balls.

At power-on default, the ADA4355 differential outputs conform to the ANSI-644 LVDS standard. Each of the LVDS output driver currents sets a nominal 3.5 mA. A 100  $\Omega$  differential termination resistor placed at the LVDS receiver inputs results in a nominal 350 mV swing (or 700 mV p-p differential) at the receiver.

The ADA4355 differential outputs also support a low power, reduced signal range option (similar to the IEEE 1596.3 standard) via the SPI programming. When operating in reduced range mode, the LVDS output driver current reduces to 2 mA. This reduction results in a 200 mV swing (or 400 mV p-p differential) across a 100  $\Omega$  termination at the receiver.

The LVDS outputs facilitate interfacing with LVDS receivers in custom application specific ICs (ASICs) and FPGAs for improved switching performance in noisy environments. To reduce the environmental noise impact, the PCB trace design recommends single point-to-point net topologies with a 100  $\Omega$  termination resistor placed as close as possible to the receiver. Timing errors may result if there is no far end receiver termination, or if there is poor differential trace routing. To avoid such timing errors, minimize trace lengths and keep the differential output traces close together and at equal lengths.

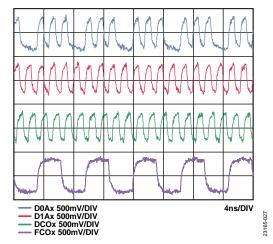

Figure 85 shows an example of the FCO and data stream with proper trace length and position. In Figure 85 and Figure 86, D0 is the differential signal, D0AP – D0AN, and D1 is the differential signal, D1AP – D1AN.

Figure 85. LVDS Output Timing Example in ANSI-644 Mode (Default)

Figure 86 shows the LVDS output timing example in reduced range mode.

Figure 86. LVDS Output Timing Example in Reduced Range Mode

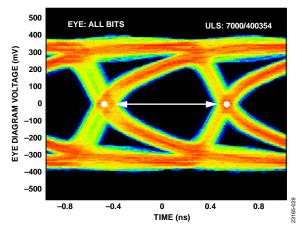

Figure 87 shows an example of the LVDS output data eye using the ANSI-644 standard (default) with trace lengths of less than 24 inches on standard FR-4 material.

Figure 87. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths of Less Than 24 Inches (Approximate 6 Inch Trace Length Result Shown) on Standard FR-4 Material, External 100  $\Omega$  Far End Termination Only

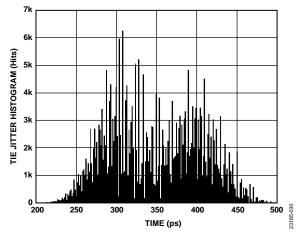

Figure 88 shows a time interval error (TIE) jitter histogram with trace lengths of less than 24 inches on standard FR-4 material.

Figure 88. TIE Jitter Histogram for Trace Lengths Less Than 24 Inches (Approximate 6 Inch Trace Length Result Shown) on Standard FR-4 Material

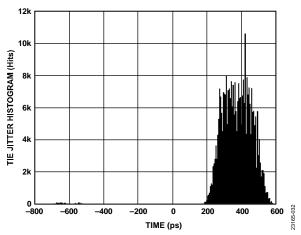

The TIE jitter histogram reflects the decrease of the data eye opening because the edge deviates from the ideal position. It is the responsibility of the user to determine if the waveforms meet the timing budget of the design.

The format of the output data is two complement by default. An example of the output coding format can be found in Table 12. To change the output data format to offset binary, see the Memory Map section.

Immediately after power-on, the ADA4355 output serial stream sets as double data rate (DDR), two-lane, byte wise, MSB first,  $1 \times$  frame, and 16-bit mode. In this default setting, the ADA4355 data rate for each serial stream is equal to (16 bits  $\times$  the sample clock rate)/2 lanes, with a maximum of 1 Gbps per lane ((16 bits  $\times$  125 MSPS)/2 lanes = 1 Gbps per lane).

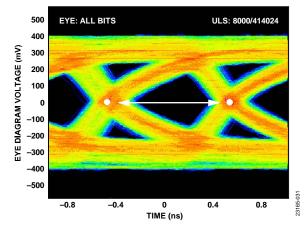

Figure 89 shows an example of the LVDS output data eye using the ANSI-644 standard (default) with trace lengths greater than 24 inches on standard FR-4 material.

Figure 89. Data Eye for LVDS Outputs in ANSI-644 Mode with Trace Lengths Greater Than 24 Inches (Approximate 36 Inch Trace Length Result Shown) on Standard FR-4 Material, External 100 Ω Far End Termination Only

Figure 90 shows a TIE jitter histogram with trace lengths greater than 24 inches on standard FR-4 material.

Figure 90. TIE Jitter Histogram for Trace Lengths Greater Than 24 Inches (Approximate 36 Inch Trace Length Result Shown) on Standard FR-4 Material

Two output clocks assist in capturing data from the ADA4355. The DCO clocks the output data and is equal to  $4\times$  the sample clock (CLK) rate for the default mode of operation. Data is clocked out of the ADA4355 and must be captured on the rising and falling edges of the DCO that supports DDR capturing. The FCO signals the start of a new output byte and is equal to the sample clock rate in  $1\times$  frame mode. See Figure 6 for more information.

When the SPI is used, the DCO phase can be adjusted in approximately 60° increments relative to one data cycle (30° relative to one DCO cycle). This adjustment allows the user to refine system time margins, if required. The example DCOP and DCON timing, as shown in Figure 6, is 180° relative to one data cycle (90° relative to one DCO cycle).

In power-on default mode, as shown in Figure 6, the MSB is first in the data output serial stream. This configuration can be inverted by programming the SPI so that the LSB is first in the data output serial stream.

### **Digital Output Coding**

There are 12 digital output test pattern options available that can be initiated through the SPI. This feature is useful when validating receiver capture and timing. Refer to Table 13 for the output bit sequencing options available. Some test patterns have two serial sequential words and can be alternated in various ways depending on the test pattern chosen.

Note that some patterns do not adhere to the data format select option. In addition, custom, user defined test patterns can be assigned in the following register addresses: Register 0x19, Register 0x1A, Register 0x1B, and Register 0x1C.

**Table 12. Digital Output Coding**

| Input (V) <sup>1</sup> | Condition       | Offset Binary Output Mode | Twos Complement Mode |

|------------------------|-----------------|---------------------------|----------------------|

| VIN+ – VIN–            | <-1 V - 0.5 LSB | 0000 0000 0000 0000       | 1000 0000 0000 0000  |

| VIN+-VIN-              | -1 V            | 0000 0000 0000 0000       | 1000 0000 0000 0000  |

| VIN+-VIN-              | οV              | 1000 0000 0000 0000       | 0000 0000 0000 0000  |

| VIN+-VIN-              | +1 V – 1.0 LSB  | 1111 1111 1111 1100       | 0111 1111 1111 1100  |

| VIN+ - VIN-            | >+1 V - 0.5 LSB | 1111 1111 1111 1100       | 0111 1111 1111 1100  |

<sup>&</sup>lt;sup>1</sup> VIN+ and VIN- are the positive and negative input voltages.

**Table 13. Flexible Output Test Modes**

| Output Test<br>Mode Bit<br>Sequence | Pattern Name      | Digital Output Word 1                                   | Digital Output Word 2                                   | Subject to<br>Data Format<br>Select | Notes                    |

|-------------------------------------|-------------------|---------------------------------------------------------|---------------------------------------------------------|-------------------------------------|--------------------------|

| 0000                                | Off (default)     | Not applicable (N/A)                                    | Not applicable                                          | Not applicable                      | Not<br>applicable        |

| 0001                                | Midscale short    | 1000 0000 0000 (12-bit)<br>1000 0000 0000 0000 (16-bit) | Not applicable                                          | Yes                                 | Offset binary code shown |

| 0010                                | +Full-scale short | 1111 1111 1111 (12-bit)<br>1111 1111 1111 1100 (16-bit) | Not applicable                                          | Yes                                 | Offset binary code shown |

| 0011                                | –Full-scale short | 0000 0000 0000 (12-bit)<br>0000 0000 0000 0000 (16-bit) | Not applicable                                          | Yes                                 | Offset binary code shown |

| 0100                                | Checkerboard      | 1010 1010 1010 (12-bit)<br>1010 1010 1010 1000 (16-bit) | 0101 0101 0101 (12-bit)<br>0101 0101 0101 0100 (16-bit) | No                                  | Not<br>applicable        |

| Output Test<br>Mode Bit<br>Sequence | Pattern Name                   | Digital Output Word 1                                   | Digital Output Word 2                                   | Subject to<br>Data Format<br>Select | Notes                                                      |

|-------------------------------------|--------------------------------|---------------------------------------------------------|---------------------------------------------------------|-------------------------------------|------------------------------------------------------------|

| 0101                                | PN sequence long <sup>1</sup>  | Not applicable                                          | Not applicable                                          | Yes                                 | PN23<br>ITU 0.150<br>X <sup>23</sup> + X <sup>18</sup> + 1 |

| 0110                                | PN sequence short <sup>1</sup> | Not applicable                                          | Not applicable                                          | Yes                                 | PN9<br>ITU 0.150<br>X <sup>9</sup> + X <sup>5</sup> + 1    |

| 0111                                | One-/zero-word toggle          | 1111 1111 1111 (12-bit)<br>111 1111 1111 1100 (16-bit)  | 0000 0000 0000 (12-bit)<br>0000 0000 0000 0000 (16-bit) | No                                  | Not<br>applicable                                          |

| 1000                                | User input                     | Register 0x19 and Register 0x1A                         | Register 0x1B and Register 0x1C                         | No                                  | Not<br>applicable                                          |

| 1001                                | 1-/0-bit toggle                | 1010 1010 1010 (12-bit)<br>1010 1010 1010 1000 (16-bit) | Not applicable                                          | No                                  | Not<br>applicable                                          |

| 1010                                | 1× sync                        | 0000 0011 1111 (12-bit)<br>0000 0001 1111 1100 (16-bit) | Not applicable                                          | No                                  | Not<br>applicable                                          |

| 1011                                | One bit high                   | 1000 0000 0000 (12-bit)<br>1000 0000 0000 0000 (16-bit) | Not applicable                                          | No                                  | Pattern<br>associated<br>with the<br>external ball         |

| 1100                                | Mixed frequency                | 1010 0011 0011 (12-bit)<br>1010 0001 1001 1100 (16-bit) | Not applicable                                          | No                                  | Not<br>applicable                                          |

<sup>&</sup>lt;sup>1</sup> All test mode options except pseudorandom number (PN) sequence short and PN sequence long can support 12-bit to 16-bit word lengths to verify data capture to the receiver.

### **OTDR PERFORMANCE**

The adjustable transimpedance gain and LPF bandwidth of the ADA4355 enable the device to deliver excellent performance over a wide range of OTDR applications. The combination of a 200 k $\Omega$  transimpedance gain and a 1 MHz LPF cutoff frequency enables the ADA4355 to reach the low noise levels needed to achieve the dynamic range required for long haul OTDR applications. Conversely, the combination of a 2 k $\Omega$  gain and a 100 MHz LPF cutoff frequency provides the higher bandwidth needed for the narrow pulse widths that are required for the closely spaced event detection necessary for data center applications.

In addition, an extension in dynamic range can be realized by combining multiple gain measurements into a single result. This technique is discussed in the Dynamic Range Extension section.

### **High Dynamic Range**

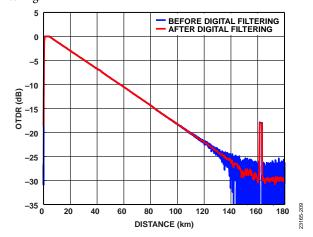

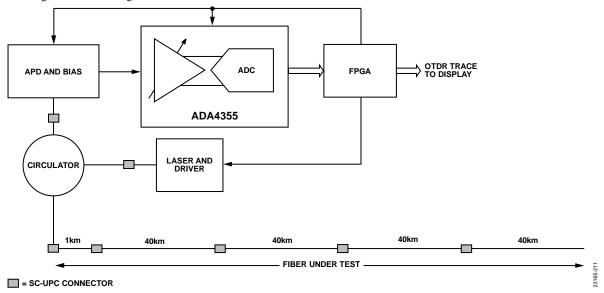

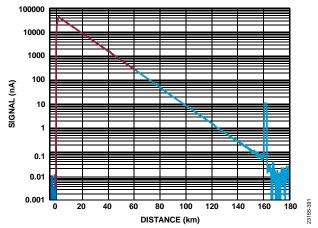

Figure 92 shows the OTDR test setup used to measure 160 km of optical fiber. The transimpedance gain was set to 200 k $\Omega$ , and the LPF was set to 1 MHz. The laser pulse width was 20  $\mu$ s with a peak pulsed power of 15 dBm and an avalanche photodiode (APD) current gain of 3. The measurement time was limited to 3 minutes, allowing for 65,000 averages, which lowered the noise

level to approximately 14 pA rms. Using the SNR = 1 calculation, the OTDR dynamic range achieved is 28 dB. Additional digital filtering can be used to further lower the noise for improved dynamic range. Applying a simple moving average filter with a window size of 1000 samples improves the dynamic range to 31 dB. Figure 91 shows a comparison of the OTDR results for before digital filtering and after digital filtering.

Figure 91. OTDR Measurement on 160 km Optical Fiber

Figure 92. OTDR Test Set-Up

### **Dynamic Range Extension**

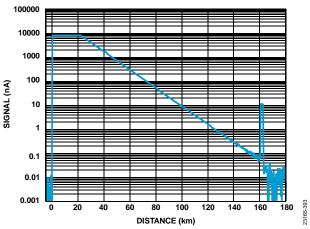

One of the primary benefits of selectable gains on the ADA4355 is the ability to extend the dynamic range of the OTDR measurement. A length of optical fiber approximately 160 km long, with 0.2 dB/km of attenuation, was once again tested. The ADA4355 transimpedance gain was maintained at 200 k $\Omega$ , as was the laser launch power and pulse width at 15 dBm and 20  $\mu$ s, respectively. Averaging was held to 3 minutes, or 65,000 averages, and a moving average filter was used. For this case, the APD bias voltage was increased, thereby raising the APD current gain to approximately 30×.

The measurement result is shown in Figure 93 and reveals that the system becomes saturated at an 8  $\mu A$  input current. Because of this saturation, the first 20 km of fiber cannot be analyzed.

Note that the y-axis of Figure 93 is expressed in terms of current so that the  $8~\mu A$  saturation current can easily be seen.

Figure 93.OTDR Measurement with 200 k $\Omega$  Gain

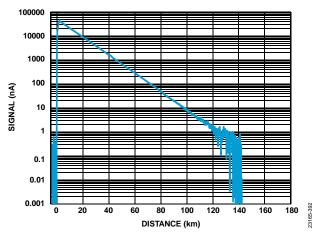

Switching the ADA4355 gain from 200 k $\Omega$  to 20 k $\Omega$  allows a maximum signal level that is  $10\times$  larger than when using 200 k $\Omega$ , which means the saturation current is now 80  $\mu A$  and that much of the region below 20 km can now be analyzed.

Figure 94 shows the results from a single frame taken with 20  $k\Omega$  gain and using all the same settings as the 200  $k\Omega$  measurement. The single frame measurement takes 2 ms to complete only and only the first 20 km are of interest.

Figure 94. OTDR Measurement with 20 k $\Omega$  Gain

Combining the measurements from Figure 93 and Figure 94 yield the results shown in Figure 95. The portion >20 km comes from Figure 93, and the portion  $\leq$ 20 km comes from Figure 94. The combined dynamic range is 34.5 dB, which is an extension of almost 4 dB at a time cost of only 2 ms.

Figure 95. OTDR Combined Measurement, 200 k $\Omega$  Gain and 20 k $\Omega$  Gain

If additional dynamic range is required, the process can be repeated by using 2 k $\Omega$  gain, which raises the saturation current to 800  $\mu$ A, and then stitching all three individual results together.

### **High Spatial Resolution**

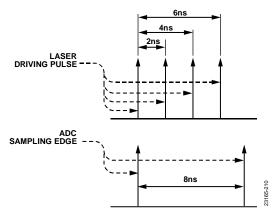

The ADA4355 has a maximum sampling rate of 125 MSPS, which translates to an 8 ns sampling period and a best case theoretical spatial resolution of approximately 0.8 m. This resolution is marginally acceptable for pulse widths of approximately 10 ns or greater. Although, with only one sample per pulse, closely spaced events can be difficult to detect. However, while using a fixed sampling rate, spatial resolution can be increased by using a phase shift to advance or delay the laser pulse and/or the rising and falling edge of the sampling clock.

Figure 96 shows the sampling period of the ADA4355 and the placement of the laser driving pulses. In this example, four phase shifts were applied (0 ns, 2 ns, 4 ns, and 6 ns). This phase shifting effectively improves the spatial resolution from approximately 0.8 m to 0.2 m, thereby enabling the use of shorter pulse widths and positive detection of more closely spaced events.

Figure 96. Phase Shifting the Laser Pulses

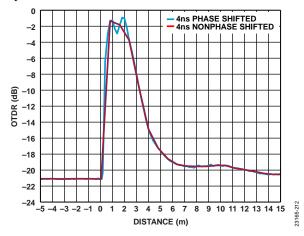

Figure 97 clearly shows the benefit of phase shifting for the detection of closely spaced events. A 4 ns pulse was used to detect two events 1 m apart. Figure 97 shows two distinct events are detected in the phase shifted case, while the two events blend together and appear as a single event in the nonphase shifted case.

Figure 97. Comparison of Closely Spaced Event Detection with and Without Phase Shifting, 4 ns Pulse Width, 1 m Event Separation

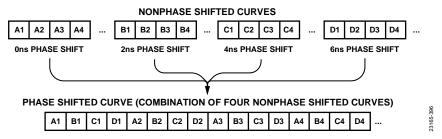

Figure 98 illustrates the method used to build the phase shifted curve from Figure 97. The nonphase shifted measurement was repeated four times, but each time it was shifted an additional 2 ns to the right. The phase shifted curve from Figure 97 was then assembled by taking the points from the four individual measurements and combining these points as shown in Figure 98. The end result takes four times longer to complete. However, the end result has four times as many data points (2 ns apart), resulting in much improved horizontal resolutions.

Figure 98. Method Used to Assemble Phase Shifted Curve From Figure 97

### **PCB DESIGN TIPS**

### **Signal Integrity Recommendations**

Place the photodiode signal source as close as possible to the ADA4355 input to minimize trace length and associated parasitic capacitance. Clear away all ground layers directly underneath the input trace to reduce parasitics even further. Additionally, match all LVDS line (DCON, DCOP, FCON, FCOP, D0AN, D0AP, D1AN, and D1AP) lengths to eliminate potential timing issues.

### **Thermal Design Recommendations**

The ADA4355 uses multiple VCC and GND balls to facilitate the internal power and grounding requirements. All of these balls must be connected for proper electrical connectivity within the module. Additionally, the PCB connection of the multiple VCC and GND balls is an integral part of the thermal design. All of the ADA4355 VCC and GND balls must be connected to a PCB copper plane with the lowest thermal resistance possible. To achieve the best thermal performance, these planes must have as many thermal vias as practical to provide the lowest possible thermally resistive path for heat dissipation to flow through the bottom of the PCB. Solder fill or plug these vias.

### **Surface-Mount Design**

Table 14 is provided as an aid to PCB design to accommodate CSP\_BGA style surface-mount packages. For industry-standard design recommendations, refer to IPC-7351, *Generic Requirements for Surface Mount Design and Land Pattern Standard*.

Table 14. CSP\_BGA Data for Use with Surface-Mount Design

| Package                   | Ball Attach Type    | Solder Mask Opening | Ball Pad Size    |  |

|---------------------------|---------------------|---------------------|------------------|--|

| 84-Ball CSP_BGA (BC-84-4) | Solder mask defined | 0.35 mm diameter    | 0.40 mm diameter |  |

### SPI

The ADA4355 SPI allows users to configure the internal ADC for specific functions or operations through a structured register space. Registers are accessible via the SPI port. Register contents can be modified by writing to the port. Bytes that can be further divided into fields constitute register memory, which is documented in the Memory Map section. Information specified in this data sheet takes precedence over the AN-877 Application Note, *Interfacing to High Speed ADCs via SPI*, which provides general information.

### **CONFIGURATION USING THE SPI**

The ADA4355 uses a 3-wire SPI configuration, SCLK, SDIO, and CS. See Table 15 for the functionality for each ball.

**Table 15. Serial Port Interface Balls**

| Mnemonic | Function                                                                                             |

|----------|------------------------------------------------------------------------------------------------------|

| SCLK     | Serial clock when CS is low. The serial shift clock                                                  |

|          | input, which synchronizes serial interface reads and writes.                                         |

| SDIO     | Serial data input/output when $\overline{CS}$ is low. Serves as                                      |

|          | an input or output, depending on the instruction sent and the relative position in the timing frame. |

| CS       | Chip select. An active low control that enables the SPI mode read and write cycles.                  |

The falling edge of CS, in conjunction with the rising edge of SCLK, determines the start of the framing. An example of the serial timing is shown in Figure 5. See Table 4 for definitions of the timing parameters.

In an ADA4355 application,  $\overline{\text{CS}}$  must be held low at power-up to enable SPI mode, and then kept low, which is called streaming.  $\overline{\text{CS}}$  can stall high between bytes to allow additional external timing.

During the instruction phase of an SPI operation, a 16-bit instruction is transmitted. Data follows the instruction phase, and the length of this data is determined by the W0 and W1 bits (see Figure 5).

In addition to word length, the instruction phase determines whether the serial frame is a read or write operation, allowing the serial port to both program the chip and to read the contents of the on-chip memory. The first bit of the first byte in a multibyte serial data transfer frame indicates whether a read command or a write command is issued. If the instruction is a readback operation, performing a readback causes the SDIO ball to change direction from an input to an output at the appropriate point in the serial frame.

All data is composed of 8-bit words. Data can be sent in MSB first mode or in LSB first mode. MSB first mode is the default on power-up and can be changed via the SPI port configuration register. For more information about this and other features,

see the AN-877 Application Note, *Interfacing to High Speed ADCs via SPI*.

### **ADC SPI START-UP SEQUENCE**