# 14-Bit, 500 MSPS LVDS, Dual Analog-to-Digital Converter

## **FEATURES**

- ▶ Parallel LVDS (DDR) outputs

- ▶ 1.1 W total power per channel at 500 MSPS (default settings)

- SFDR = 85 dBFS at 170 MHz f<sub>IN</sub> (500 MSPS)

- ▶ SNR = 68.6 dBFS at 170 MHz f<sub>IN</sub> (500 MSPS)

- ▶ ENOB = 10.9 bits at 170 MHz f<sub>IN</sub>

- ▶ DNL = ±0.5 LSB

- ▶ INL = ±2.5 LSB

- ▶ Noise density = -153 dBFS/Hz at 500 MSPS

- ▶ 1.25 V, 2.50 V, and 3.3 V supply operation

- No missing codes

- ▶ Internal analog-to-digital converter (ADC) voltage reference

- ▶ Flexible input range and termination impedance

- 1.46 V p-p to 2.06 V p-p (2.06 V p-p nominal)

- 400 Ω, 200 Ω, 100 Ω, and 50 Ω differential

- SYNC± input allows multichip synchronization

- ▶ DDR LVDS (ANSI-644 levels) outputs

- > 2 GHz usable analog input full power bandwidth

- >96 dB channel isolation/crosstalk

- Amplitude detect bits for efficient AGC implementation

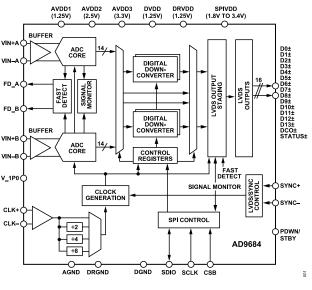

## FUNCTIONAL BLOCK DIAGRAM

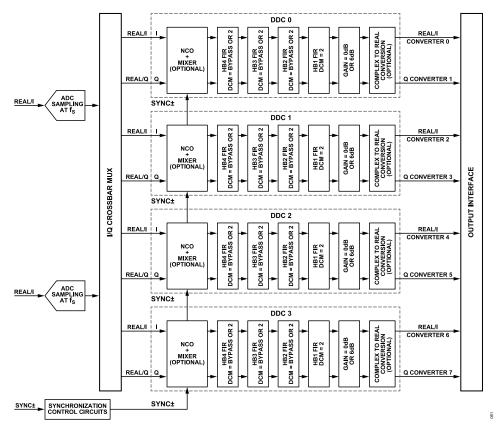

- ► Two integrated wideband digital processors per channel

- ▶ 12-bit numerically controlled oscillator (NCO)

- ▶ 3 cascaded half-band filters

- Differential clock inputs

- Serial port control

- ▶ Integer clock divide by 2, 4, or 8

- Small signal dither

## APPLICATIONS

- Communications

- Diversity multiband, multimode digital receivers

3G/4G, TD-SCDMA, W-CDMA, MC-GSM, LTE

- General-purpose software radios

- Ultrawideband satellite receiver

- Instrumentation (spectrum analyzers, network analyzers, integrated RF test solutions)

- Radar

- Digital oscilloscopes

- ▶ High speed data acquisition systems

- DOCSIS CMTS upstream receiver paths

- HFC digital reverse path receivers

Figure 1.

Rev. A

DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                                    | 1    |

|---------------------------------------------|------|

| Applications                                | 1    |

| Functional Block Diagram                    | 1    |

| General Description                         | 3    |

| Product Highlights                          | 3    |

| Specifications                              | 4    |

| DC Specifications                           |      |

| AC Specifications                           |      |

| Digital Specifications                      |      |

| Switching Specifications                    | 7    |

| Timing Specifications                       |      |

| Absolute Maximum Ratings                    |      |

| Thermal Characteristics                     | . 14 |

| ESD Caution                                 | .14  |

| Pin Configuration and Function Descriptions | . 15 |

| Typical Performance Characteristics         | . 17 |

| Equivalent Circuits                         |      |

| Theory of Operation                         | .22  |

| ADC Architecture                            | .22  |

| Analog Input Considerations                 | . 22 |

| Voltage Reference                           | .25  |

| Clock Input Considerations                  | . 25 |

| Power-Down/Standby Mode                     | .27  |

| Temperature Diode                           | .27  |

| ADC Overrange and Fast Detect               | .28  |

| ADC Overrange                               |      |

| Fast Threshold Detection (FD_A and FD_B)    | . 28 |

| Signal Monitor                              |      |

| Digital Downconverters (DDCs)               |      |

| DDC I/Q Input Selection                     |      |

| DDC I/Q Output Selection                    | . 30 |

|                                             |      |

| DDC General Description               | 30 |

|---------------------------------------|----|

| Frequency Translation                 |    |

| General Description                   |    |

| DDC NCO Plus Mixer Loss and SFDR      | 37 |

| Numerically Controlled Oscillator     | 37 |

| FIR Filters                           |    |

| General Description                   |    |

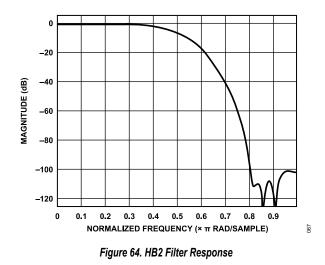

| Half-Band Filters                     |    |

| DDC Gain Stage                        |    |

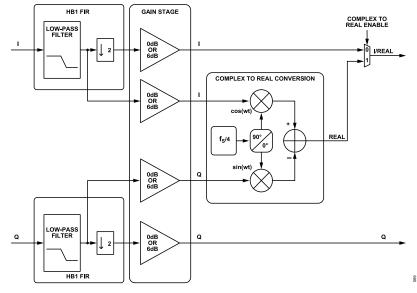

| DDC Complex to Real Conversion Block  |    |

| DDC Example Configurations            |    |

| Digital Outputs                       |    |

| Digital Outputs                       |    |

| ADC Overrange                         |    |

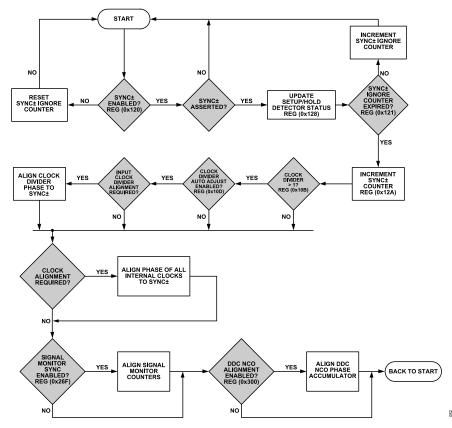

| Multichip Synchronization             | 46 |

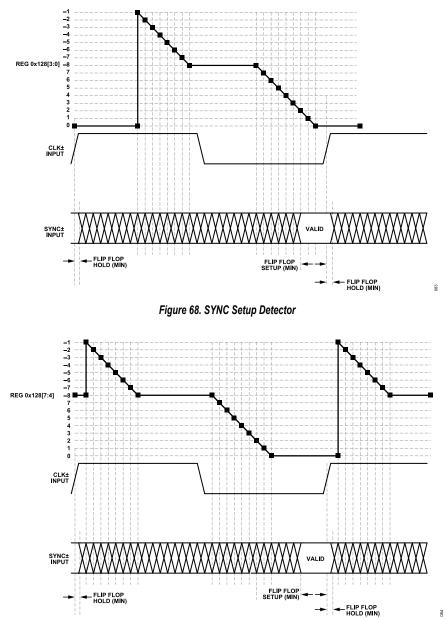

| SYNC± Setup and Hold Window Monitor   | 47 |

| Test Modes                            | 49 |

| ADC Test Modes                        |    |

| Serial Port Interface (SPI)           | 50 |

| Configuration Using the SPI           | 50 |

| Hardware Interface                    | 50 |

| SPI Accessible Features               | 50 |

| Memory Map                            |    |

| Reading the Memory Map Register Table | 51 |

| Memory Map Register Table             | 52 |

| Applications Information              |    |

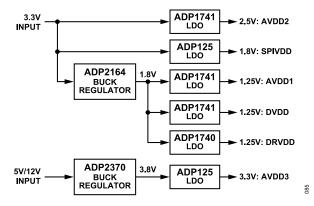

| Power Supply Recommendations          | 62 |

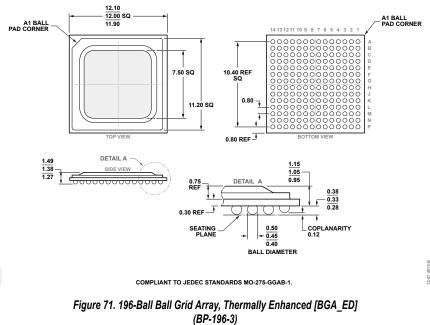

| Outline Dimensions                    | 63 |

| Ordering Guide                        | 63 |

| Evaluation Boards                     |    |

|                                       |    |

## **REVISION HISTORY**

| 6/2023—Rev. 0 to Rev. A    |   |

|----------------------------|---|

| Change to Note 2, Table 4  | 7 |

| Change to Figure 5 Caption | 9 |

| Change to Figure 7 Caption |   |

| Moved Table 9              |   |

| Added Dither Section       |   |

| Changes to Table 16        |   |

| Changes to Table 26        |   |

| Changes to Table 29        |   |

| Changes to Ordering Guide  |   |

|                            |   |

## 4/2015—Revision 0: Initial Version

## **GENERAL DESCRIPTION**

The AD9684 is a dual, 14-bit, 500 MSPS ADC. The device has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This product is designed for sampling wide bandwidth analog signals. The AD9684 is optimized for wide input bandwidth, a high sampling rate, excellent linearity, and low power in a small package.

The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth buffered inputs, supporting a variety of user selectable input ranges. An integrated voltage reference eases design considerations. Each ADC data output is internally connected to an optional decimate by 2 block.

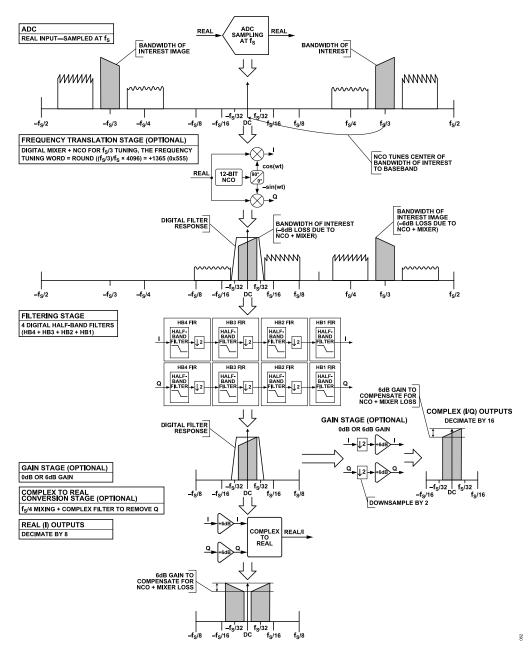

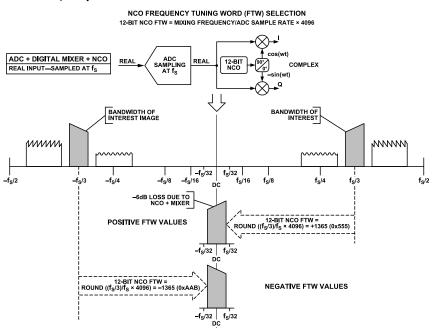

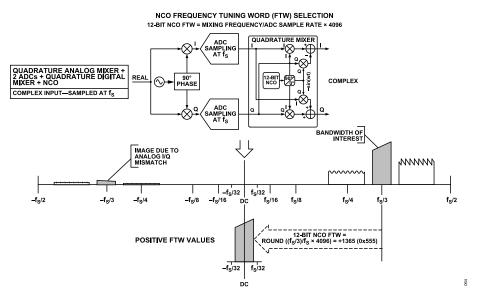

The analog input and clock signals are differential inputs. Each ADC data output is internally connected to two digital downconverters (DDCs). Each DDC consists of four cascaded signal processing stages: a 12-bit frequency translator (NCO), and three half-band decimation filters supporting a divide by factor of two, four, and eight.

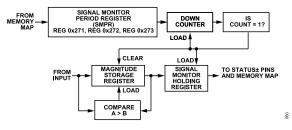

The AD9684 has several functions that simplify the automatic gain control (AGC) function in a communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect output bits of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly reduce the system gain to avoid an overrange condition at the ADC input. In addition to the fast detect outputs, the AD9684 also offers signal monitoring capability. The signal monitoring block provides additional information about the signal that the ADC digitized.

The dual ADC output data is routed directly to the one external, 14-bit LVDS output port, supporting double data rate (DDR) formatting. An external data clock and status bit are offered for data capture flexibility.

The LVDS outputs have several configurations, depending on the acceptable rate of the receiving logic device and the sampling rate of the ADC. Multiple device synchronization is supported through the SYNC± input pins.

The AD9684 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using a 1.8 V to 3.4 V capable 3-wire serial port interface (SPI).

The AD9684 is available in a Pb-free, 196-ball ball grid array (BGA) and is specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C industrial temperature range. This product is protected by a U.S. patent.

## **PRODUCT HIGHLIGHTS**

- 1. Wide full power bandwidth supports intermediate frequency (IF) sampling of signals up to 2 GHz.

- 2. Buffered inputs with programmable input termination ease filter design and implementation.

- **3.** Four integrated wideband decimation filters and NCO blocks supporting multiband receivers.

- 4. Flexible SPI controls various product features and functions to meet specific system requirements.

- 5. Programmable fast overrange detection and signal monitoring.

- 6. SYNC± input allows synchronization of multiple devices.

- 7. 12 mm × 12 mm, 196-ball BGA ED.

## DC SPECIFICATIONS

AVDD1 = 1.25 V, AVDD2 = 2.5 V, AVDD3 = 3.3 V, DVDD = 1.25 V, DRVDD = 1.25 V, SPIVDD = 1.8 V, specified maximum sampling rate (500 MSPS), 1.7 V p-p full-scale differential input, 1.0 V internal reference,  $A_{IN}$  = -1.0 dBFS, default SPI settings,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                       | Temperature | Min  | Тур       | Max  | Unit    |

|-------------------------------------------------|-------------|------|-----------|------|---------|

| RESOLUTION                                      | Full        | 14   |           |      | Bits    |

| ACCURACY                                        |             |      |           |      |         |

| No Missing Codes                                | Full        |      | Guarantee | ed   |         |

| Offset Error                                    | Full        | -0.3 | 0         | +0.3 | % FSR   |

| Offset Matching                                 | Full        |      | 0         | +0.3 | % FSR   |

| Gain Error                                      | Full        | -6.5 | 0         | +6.5 | % FSR   |

| Gain Matching                                   | Full        |      | 0         | +5.0 | % FSR   |

| Differential Nonlinearity (DNL)                 | Full        | -0.6 | ±0.5      | +0.7 | LSB     |

| Integral Nonlinearity (INL)                     | Full        | -4.5 | ±2.5      | +5.0 | LSB     |

| TEMPERATURE DRIFT                               |             |      |           |      |         |

| Offset Error                                    | 25°C        |      | ±3        |      | ppm/°C  |

| Gain Error                                      | 25°C        |      | -39       |      | ppm/°C  |

| INTERNAL VOLTAGE REFERENCE                      | Full        |      | 1.0       |      | V       |

| INPUT-REFERRED NOISE                            |             |      |           |      |         |

| V <sub>REF</sub> = 1.0 V                        | 25°C        |      | 2.63      |      | LSB rms |

| ANALOG INPUTS                                   |             |      |           |      |         |

| Differential Input Voltage Range (Programmable) | Full        | 1.46 | 2.06      | 2.06 | V p-p   |

| Common-Mode Voltage (V <sub>CM</sub> )          | 25°C        |      | 2.05      |      | V       |

| Differential Input Capacitance <sup>1</sup>     | 25°C        |      | 1.5       |      | pF      |

| Analog Input Full Power Bandwidth               | 25°C        |      | 2         |      | GHz     |

| POWER SUPPLY                                    |             |      |           |      |         |

| AVDD1                                           | Full        | 1.22 | 1.25      | 1.28 | V       |

| AVDD2                                           | Full        | 2.44 | 2.50      | 2.56 | V       |

| AVDD3                                           | Full        | 3.2  | 3.3       | 3.4  | V       |

| DVDD                                            | Full        | 1.22 | 1.25      | 1.28 | V       |

| DRVDD                                           | Full        | 1.22 | 1.25      | 1.28 | V       |

| SPIVDD                                          | Full        | 1.22 | 1.8       | 3.4  | V       |

| I <sub>AVDD1</sub>                              | Full        |      | 448       | 503  | mA      |

| I <sub>AVDD2</sub>                              | Full        |      | 396       | 455  | mA      |

| I <sub>AVDD3</sub>                              | Full        |      | 103       | 124  | mA      |

| I <sub>DVDD</sub>                               | Full        |      | 108       | 127  | mA      |

| I <sub>DRVDD</sub>                              | Full        |      | 106       | 119  | mA      |

| I <sub>SPIVDD</sub>                             | Full        |      | 2         | 6    | mA      |

| POWER CONSUMPTION                               |             |      |           |      |         |

| Total Power Dissipation <sup>2</sup>            | Full        |      | 2.2       |      | W       |

| Power-Down Dissipation                          | Full        |      | 710       |      | mW      |

| Standby                                         | Full        |      | 1.0       |      | W       |

<sup>1</sup> Differential capacitance is measured between the VIN+x and VIN-x pins (x = A or B).

<sup>2</sup> Parallel interleaved LVDS mode. The power dissipation on DRVDD changes with the output data mode used.

## **AC SPECIFICATIONS**

AVDD1 = 1.25 V, AVDD2 = 2.5 V, AVDD3 = 3.3 V, DVDD = 1.25 V, DRVDD = 1.25 V, SPIVDD = 1.8 V, specified maximum sampling rate (500 MSPS), 1.7 V p-p full-scale differential input, 1.0 V internal reference,  $A_{IN} = -1.0$  dBFS, default SPI settings,  $T_A = 25^{\circ}$ C, unless otherwise noted.

|                                                                 | _           |      |      |     |         |

|-----------------------------------------------------------------|-------------|------|------|-----|---------|

| Parameter <sup>1</sup>                                          | Temperature | Min  | Тур  | Max | Unit    |

| ANALOG INPUT FULL SCALE                                         | Full        |      | 2.06 |     | V р-р   |

| NOISE DENSITY <sup>2</sup>                                      | Full        |      | -153 |     | dBFS/Hz |

| SIGNAL-TO-NOISE RATIO (SNR) <sup>3</sup>                        |             |      |      |     |         |

| f <sub>IN</sub> = 10 MHz                                        | 25°C        |      | 69.2 |     | dBFS    |

| f <sub>IN</sub> = 170 MHz                                       | Full        | 67.5 | 68.6 |     | dBFS    |

| f <sub>IN</sub> = 340 MHz                                       | 25°C        |      | 68.4 |     | dBFS    |

| f <sub>IN</sub> = 450 MHz                                       | 25°C        |      | 68.0 |     | dBFS    |

| f <sub>IN</sub> = 765 MHz                                       | 25°C        |      | 64.4 |     | dBFS    |

| f <sub>IN</sub> = 985 MHz                                       | 25°C        |      | 63.8 |     | dBFS    |

| f <sub>IN</sub> = 1950 MHz                                      | 25°C        |      | 60.5 |     | dBFS    |

| SIGNAL-TO-NOISE RATIO AND DISTORTION RATIO (SINAD) <sup>3</sup> |             |      |      |     |         |

| f <sub>IN</sub> = 10 MHz                                        | 25°C        |      | 68.7 |     | dBFS    |

| f <sub>IN</sub> = 170 MHz                                       | Full        | 67   | 68.5 |     | dBFS    |

| f <sub>IN</sub> = 340 MHz                                       | 25°C        |      | 67.6 |     | dBFS    |

| f <sub>IN</sub> = 450 MHz                                       | 25°C        |      | 67.2 |     | dBFS    |

| f <sub>IN</sub> = 765 MHz                                       | 25°C        |      | 63.8 |     | dBFS    |

| f <sub>IN</sub> = 985 MHz                                       | 25°C        |      | 62.5 |     | dBFS    |

| f <sub>IN</sub> = 1950 MHz                                      | 25°C        |      | 58.3 |     | dBFS    |

| EFFECTIVE NUMBER OF BITS (ENOB)                                 |             |      |      |     |         |

| f <sub>IN</sub> = 10 MHz                                        | 25°C        |      | 11.1 |     | Bits    |

| f <sub>IN</sub> = 170 MHz                                       | Full        | 10.8 | 10.9 |     | Bits    |

| f <sub>IN</sub> = 340 MHz                                       | 25°C        |      | 10.8 |     | Bits    |

| f <sub>IN</sub> = 450 MHz                                       | 25°C        |      | 10.8 |     | Bits    |

| f <sub>IN</sub> = 765 MHz                                       | 25°C        |      | 10.3 |     | Bits    |

| f <sub>IN</sub> = 985 MHz                                       | 25°C        |      | 10.1 |     | Bits    |

| f <sub>IN</sub> = 1950 MHz                                      | 25°C        |      | 9.5  |     | Bits    |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR) <sup>3</sup>                 |             | _    |      |     |         |

| $f_{\rm IN} = 10 \text{ MHz}$                                   | 25°C        |      | 83   |     | dBFS    |

| f <sub>IN</sub> = 170 MHz                                       | Full        | 76   | 85   |     | dBFS    |

| f <sub>IN</sub> = 340 MHz                                       | 25°C        | 10   | 82   |     | dBFS    |

| f <sub>IN</sub> = 450 MHz                                       | 25°C        |      | 86   |     | dBFS    |

| f <sub>IN</sub> = 765 MHz                                       | 25°C        |      | 81   |     | dBFS    |

| f <sub>IN</sub> = 985 MHz                                       | 25°C        |      | 76   |     | dBFS    |

| f <sub>IN</sub> = 1950 MHz                                      | 25°C        |      | 69   |     | dBFS    |

| WORST HARMONIC, SECOND OR THIRD <sup>3</sup>                    |             |      |      |     |         |

| f <sub>IN</sub> = 10 MHz                                        | 25°C        |      | -83  |     | dBFS    |

| f <sub>IN</sub> = 170 MHz                                       | Full        |      | -85  | -76 | dBFS    |

| $f_{\rm IN} = 340 \text{ MHz}$                                  | 25°C        |      | -82  | 10  | dBFS    |

| $f_{\rm IN} = 450 \text{ MHz}$                                  | 25°C        |      | -86  |     | dBFS    |

| f <sub>IN</sub> = 765 MHz                                       | 25°C        |      | -81  |     | dBFS    |

| f <sub>IN</sub> = 985 MHz                                       | 25°C        |      | -76  |     | dBFS    |

| f <sub>IN</sub> = 1950 MHz                                      | 25°C        |      | -69  |     | dBFS    |

| WORST OTHER, EXCLUDING SECOND OR THIRD HARMONIC <sup>3</sup>    | 20 0        |      | 09   |     |         |

| f <sub>IN</sub> = 10 MHz                                        | 25°C        |      | -93  |     | dBFS    |

Table 2. (Continued)

| Parameter <sup>1</sup>                                                                     | Temperature | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------|-------------|-----|-----|-----|------|

| f <sub>IN</sub> = 170 MHz                                                                  | Full        |     | -92 | -76 | dBFS |

| f <sub>IN</sub> = 340 MHz                                                                  | 25°C        |     | -90 |     | dBFS |

| f <sub>IN</sub> = 450 MHz                                                                  | 25°C        |     | -92 |     | dBFS |

| f <sub>IN</sub> = 765 MHz                                                                  | 25°C        |     | -89 |     | dBFS |

| f <sub>IN</sub> = 985 MHz                                                                  | 25°C        |     | -89 |     | dBFS |

| f <sub>IN</sub> = 1950 MHz                                                                 | 25°C        |     | -85 |     | dBFS |

| TWO-TONE INTERMODULATION DISTORTION (IMD), A <sub>IN1</sub> AND A <sub>IN2</sub> = -7 dBFS |             |     |     |     |      |

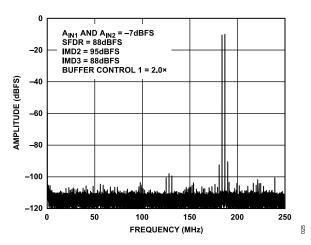

| f <sub>IN1</sub> = 185 MHz, f <sub>IN2</sub> = 188 MHz                                     | 25°C        |     | -88 |     | dBFS |

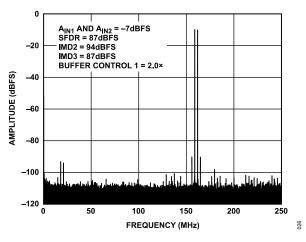

| f <sub>IN1</sub> = 338 MHz, f <sub>IN2</sub> = 341 MHz                                     | 25°C        |     | -87 |     | dBFS |

| CROSSTALK <sup>4</sup>                                                                     | 25°C        |     | 96  |     | dB   |

| FULL POWER BANDWIDTH                                                                       | 25°C        |     | 2   |     | GHz  |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for definitions and for details on how these tests were completed.

<sup>2</sup> Noise density is measured at a low analog input frequency (30 MHz).

<sup>3</sup> See #unique\_18/unique\_18\_Connect\_42\_T9 for the recommended settings for full-scale voltage and buffer current control.

<sup>4</sup> Crosstalk is measured at 170 MHz with a -1.0 dBFS analog input on one channel and no input on the adjacent channel.

## DIGITAL SPECIFICATIONS

AVDD1 = 1.25 V, AVDD2 = 2.5 V, AVDD3 = 3.3 V, DVDD = 1.25 V, DRVDD = 1.25 V, SPIVDD = 1.8 V, specified maximum sampling rate (500 MSPS), 1.7 V p-p full-scale differential input, 1.0 V internal reference,  $A_{IN} = -1.0$  dBFS, default SPI settings,  $T_A = 25^{\circ}$ C, unless otherwise noted.

| Parameter                                  | Temperature | Min | Тур          | Max  | Unit   |

|--------------------------------------------|-------------|-----|--------------|------|--------|

| CLOCK INPUTS (CLK+, CLK-)                  |             |     |              |      |        |

| Logic Compliance                           | Full        |     | LVDS/LVPEC   | ;L   |        |

| Differential Input Voltage                 | Full        | 600 | 1200         | 1800 | mV p-p |

| Input Common-Mode Voltage                  | Full        |     | 0.85         |      | V      |

| Input Resistance (Differential)            | Full        |     | 35           |      | kΩ     |

| Input Capacitance                          | Full        |     |              | 2.5  | pF     |

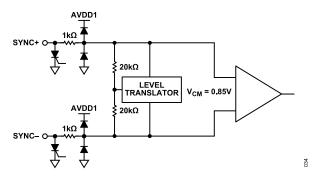

| SYNC INPUTS (SYNC+, SYNC-)                 |             |     |              |      |        |

| Logic Compliance                           | Full        |     | LVDS/LVPEC   | L    |        |

| Differential Input Voltage                 | Full        | 400 | 1200         | 1800 | mV p-p |

| Input Common-Mode Voltage                  | Full        | 0.6 | 0.85         | 2.0  | V      |

| Input Resistance (Differential)            | Full        |     | 35           |      | kΩ     |

| Input Capacitance (Differential)           | Full        |     |              | 2.5  | pF     |

| LOGIC INPUTS (SDIO, SCLK, CSB, PDWN/STBY)  |             |     |              |      |        |

| Logic Compliance                           | Full        |     | CMOS         |      |        |

| Logic 1 Voltage                            | Full        |     | 0.8 × SPIVDD |      | V      |

| Logic 0 Voltage                            | Full        | 0   | 0.2 × SPIVDD |      | V      |

| Input Resistance                           | Full        |     | 30           |      | kΩ     |

| LOGIC OUTPUT (SDIO)                        |             |     |              |      |        |

| Logic Compliance                           | Full        |     | CMOS         |      |        |

| Logic 1 Voltage (I <sub>OH</sub> = 800 µA) | Full        |     | 0.8 × SPIVDD |      | V      |

| Logic 0 Voltage (I <sub>OL</sub> = 50 μA)  | Full        |     | 0.2 × SPIVDD |      | V      |

| LOGIC OUTPUTS (FD_A, FD_B)                 |             |     |              |      |        |

| Logic Compliance                           | Full        |     | CMOS         |      |        |

| Logic 1 Voltage                            | Full        | 0.8 | SPIVDD       |      | V      |

| Logic 0 Voltage                            | Full        | 0   | 0            |      | V      |

## Table 3. (Continued)

| Parameter                                                   | Temperature | Min  | Тур  | Мах  | Unit   |

|-------------------------------------------------------------|-------------|------|------|------|--------|

| Input Resistance                                            | Full        |      | 30   |      | kΩ     |

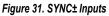

| DIGITAL OUTPUTS (Dx±, <sup>1</sup> DCO±, STATUS±)           |             |      |      |      |        |

| Logic Compliance                                            | Full        |      | LVDS |      |        |

| Differential Output Voltage                                 | Full        | 230  |      | 430  | mV p-p |

| Output Common-Mode Voltage (V <sub>CM</sub> )               |             |      |      |      |        |

| AC-Coupled                                                  | 25°C        | 0    |      | 1.8  | V      |

| Short-Circuit Current (I <sub>DSHORT</sub> )                | 25°C        | -100 |      | +100 | mA     |

| Differential Return Loss (RL <sub>DIFF</sub> ) <sup>2</sup> | 25°C        | 8    |      |      | dB     |

| Common-Mode Return Loss (RL <sub>CM</sub> ) <sup>2</sup>    | 25°C        | 6    |      |      | dB     |

| Differential Termination Impedance                          | Full        | 80   | 100  | 120  | Ω      |

<sup>1</sup> Where x = 0 to 13.

<sup>2</sup> Differential and common-mode return loss is measured from 100 MHz to 0.75 MHz × baud rate.

## SWITCHING SPECIFICATIONS

AVDD1 = 1.25 V, AVDD2 = 2.5 V, AVDD3 = 3.3 V, DVDD = 1.25 V, DRVDD = 1.25 V, SPIVDD = 1.8 V, specified maximum sampling rate, 1.7 V p-p full-scale differential input, 1.0 V internal reference,  $A_{IN}$  = -1.0 dBFS, default SPI settings,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                                     | Temperature | Min  | Тур   | Max  | Unit         |

|---------------------------------------------------------------|-------------|------|-------|------|--------------|

| CLOCK                                                         |             |      |       |      |              |

| Clock Rate (at CLK+/CLK- Pins)                                | Full        | 0.25 |       | 4    | GHz          |

| Maximum Sample Rate <sup>1</sup>                              | Full        | 500  |       |      | MSPS         |

| Minimum Sample Rate <sup>2</sup>                              | Full        | 250  |       |      | MSPS         |

| Clock Pulse Width                                             |             |      |       |      |              |

| High                                                          | Full        | 1000 |       |      | ps           |

| Low                                                           | Full        | 1000 |       |      | ps           |

| LVDS DATA OUTPUT PARAMETERS                                   |             |      |       |      |              |

| Data Propagation Delay (t <sub>PD</sub> ) <sup>3</sup>        | Full        |      | 2.225 |      | ns           |

| DCO± Propagation Delay (t <sub>DCO</sub> ) <sup>3</sup>       | Full        |      | 2.2   |      | ns           |

| DCO± to Data Skew                                             |             |      |       |      |              |

| Rising Edge Data (t <sub>SKEWR</sub> ) <sup>3</sup>           | Full        | -150 | -25   | +100 | ps           |

| Falling Edge Data (t <sub>SKEWF</sub> ) <sup>3</sup>          | Full        | 850  | 1.025 | 1100 | ps           |

| STATUS± Propagation Delay (t <sub>STATUS</sub> ) <sup>4</sup> | Full        |      | 2.2   |      | ns           |

| DCO± to STATUS± Skew (t <sub>FRAME</sub> ) <sup>4</sup>       | Full        | -150 | -25   | +100 | ps           |

| Data Propagation Delay (t <sub>PD</sub> ) <sup>3</sup>        | Full        |      | 2.225 |      | ns           |

| DCO± Propagation Delay (t <sub>DCO</sub> ) <sup>3</sup>       | Full        |      | 2.2   |      | ns           |

| LATENCY <sup>5</sup>                                          |             |      |       |      |              |

| Pipeline Latency                                              | Full        |      | 35    |      | Clock cycles |

| Fast Detect Latency                                           | Full        |      |       | 28   | Clock cycles |

| HB1 Filter Latency <sup>3</sup>                               | Full        |      | 50    |      | Clock cycles |

| HB1 + HB2 Filter Latency <sup>3</sup>                         | Full        |      | 101   |      | Clock cycles |

| HB1 + HB2 + HB3 Filter Latency <sup>3</sup>                   | Full        |      | 217   |      | Clock cycles |

| HB1 + HB2 + HB3 + HB4 Filter Latency <sup>3</sup>             | Full        |      | 433   |      | Clock cycles |

| Fast Detect Latency                                           | Full        |      | 28    |      | Clock cycles |

| Wake-Up Time <sup>6</sup>                                     |             |      |       |      |              |

| Standby                                                       | 25°C        |      | 1     |      | ms           |

| Power-Down                                                    | 25°C        |      |       | 4    | ms           |

Table 4. (Continued)

| Parameter                                      | Temperature | Min | Тур | Max | Unit         |

|------------------------------------------------|-------------|-----|-----|-----|--------------|

| APERTURE                                       |             |     |     |     |              |

| Aperture Delay (t <sub>A</sub> )               | Full        |     | 530 |     | ps           |

| Aperture Uncertainty (Jitter, t <sub>j</sub> ) | Full        |     | 55  |     | fs rms       |

| Out of Range Recovery Time                     | Full        |     | 1   |     | Clock Cycles |

<sup>1</sup> The maximum sample rate is the clock rate after the divider.

<sup>2</sup> The minimum sample rate operates at 250 MSPS.

<sup>3</sup> This specification is valid for parallel interleaved, channel multiplexed, and byte mode output modes.

<sup>4</sup> This specification is valid for byte mode output mode only.

<sup>5</sup> No DDCs used.

<sup>6</sup> Wake-up time is defined as the time required to return to normal operation from power-down mode or standby mode.

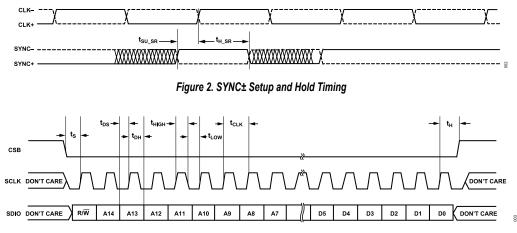

## TIMING SPECIFICATIONS

Table 5.

| Parameter                         | Description                                                                                                                   | Min | Тур | Мах | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| CLK± to SYNC± TIMING REQUIREMENTS | See Figure 2                                                                                                                  |     |     |     |      |

| t <sub>SU_SR</sub>                | Device clock to SYNC± setup time                                                                                              |     | 117 |     | ps   |

| -<br>t <sub>H_SR</sub>            | Device clock to SYNC± hold time                                                                                               |     | -96 |     | ps   |

| SPI TIMING REQUIREMENTS           | See Figure 3                                                                                                                  |     |     |     |      |

| t <sub>DS</sub>                   | Setup time between the data and the rising edge of SCLK                                                                       | 2   |     |     | ns   |

| t <sub>DH</sub>                   | Hold time between the data and the rising edge of SCLK                                                                        | 2   |     |     | ns   |

| t <sub>CLK</sub>                  | Period of the SCLK                                                                                                            | 40  |     |     | ns   |

| t <sub>S</sub>                    | Setup time between CSB and SCLK                                                                                               | 2   |     |     | ns   |

| t <sub>H</sub>                    | Hold time between CSB and SCLK                                                                                                | 2   |     |     | ns   |

| tніgн                             | Minimum period that SCLK must be in a logic high state                                                                        | 10  |     |     | ns   |

| t <sub>LOW</sub>                  | Minimum period that SCLK must be in a logic low state                                                                         | 10  |     |     | ns   |

| t <sub>EN_SDIO</sub>              | Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge (not shown in Figure 3) | 10  |     |     | ns   |

| t <sub>DIS_SDIO</sub>             | Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge (not shown in Figure 3)  | 10  |     |     | ns   |

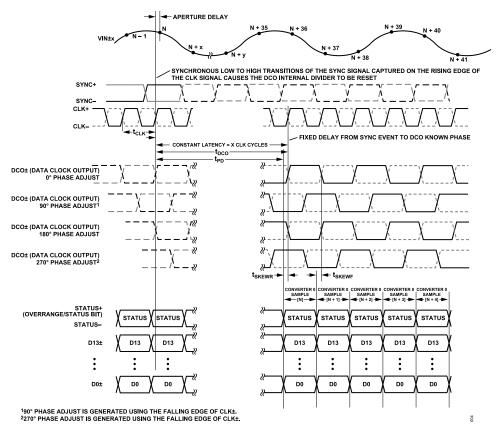

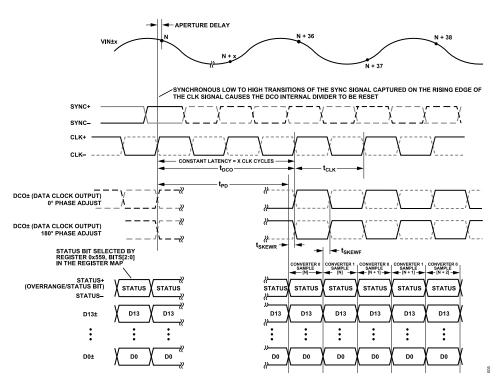

## **Timing Diagrams**

Figure 3. Serial Port Interface Timing Diagram

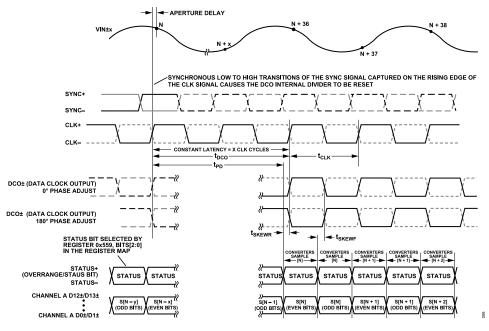

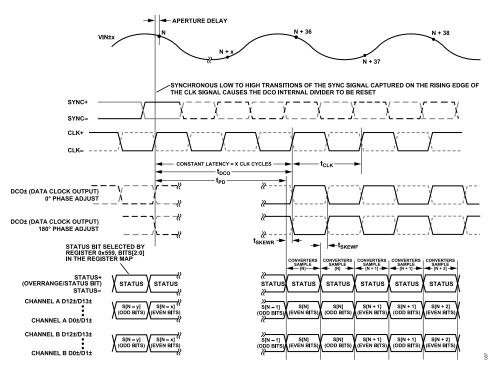

Figure 4. Parallel Interleaved Mode—One Converter, ≤14-Bit Data

Figure 5. Parallel Interleaved Mode—Two Converters, <14-Bit Data, Output Sample Rate < 500 MSPS

Figure 6. Channel Multiplexed (Even/Odd) Mode—One Converter, ≤14-Bit Data

Figure 7. Channel Multiplexed (Even/Odd) Mode—Two Converters, ≤14-Bit Data, Output Sample Rate < 500 MSPS

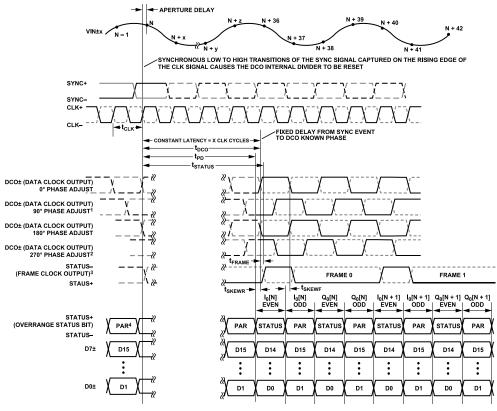

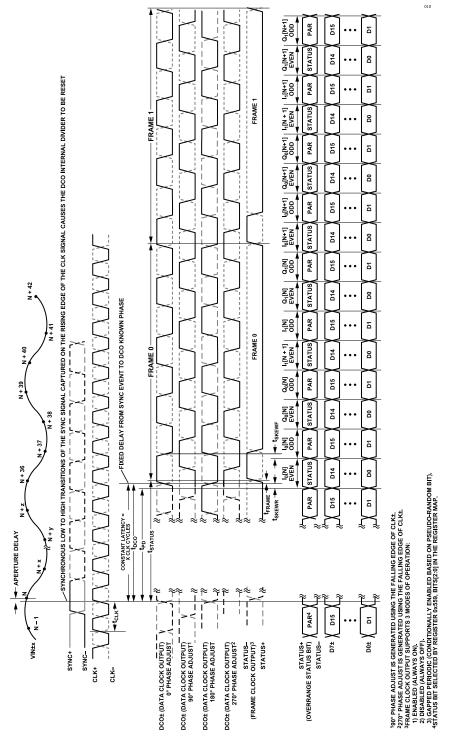

190° PHASE ADJUST IS GENERATED USING THE FALLING EDGE OF CLK±. 2270° PHASE ADJUST IS GENERATED USING THE FALLING EDGE OF CLK±. <sup>3</sup>FRAME CLOCK OUTPUT SUPPORTS 3 MODES OF OPERATION: 1) ENABLED (ALWAYS ON). 2) DISABLED (ALWAYS OFF). 3) GAPPED PERIODIC (CONDITIONALLY ENABLED BASED ON PSEUDO-RANDOM BIT). <sup>4</sup>STATUS BIT SELECTED BY REGISTER 0x559, BITS[2:0] IN THE REGISTER MAP.

908

Figure 8. LVDS Byte Mode—Two Virtual Converters, One DDC, I/Q Data Decimate by 4

Figure 9. LVDS Byte Mode—Four Virtual Converters, Two DDCs, ≤16-Bit Data, I/Q Data Decimate by 8

110

Figure 10. LVDS Byte Mode—Eight Virtual Converters, Four DDCs, ≤16-Bit Data, I/Q Data Decimate by 16

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                                        | Rating                   |

|--------------------------------------------------|--------------------------|

| Electrical                                       |                          |

| AVDD1 to AGND                                    | 1.32 V                   |

| AVDD2 to AGND                                    | 2.75 V                   |

| AVDD3 to AGND                                    | 3.63 V                   |

| DVDD to DGND                                     | 1.32 V                   |

| DRVDD to DRGND                                   | 1.32 V                   |

| SPIVDD to AGND                                   | 3.63 V                   |

| AGND to DRGND                                    | -0.3 V to +0.3 V         |

| VIN±x to AGND                                    | 3.2 V                    |

| SCLK, SDIO, CSB to AGND                          | -0.3 V to SPIVDD + 0.3 V |

| VIN±x Maximum Swing                              | 4.3 V p-p                |

| PDWN/STBY to AGND                                | -0.3 V to SPIVDD + 0.3 V |

| Environmental                                    |                          |

| Operating Temperature Range (T <sub>CASE</sub> ) | -40°C to +85°C           |

| Maximum Junction Temperature                     | 125°C                    |

| Storage Temperature Range (Ambient)              | -65°C to +150°C          |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL CHARACTERISTICS

Typical  $\theta_{JA}$ ,  $\theta_{JB}$ , and  $\theta_{JC}$  are specified vs. the number of printed circuit board (PCB) layers in different airflow velocities (in m/sec). Airflow increases heat dissipation effectively reducing  $\theta_{JA}$  and  $\theta_{JB}$ . The use of appropriate thermal management techniques is recommended to ensure that the maximum junction temperature does not exceed the limits shown in Table 7.

#### Table 7. Simulated Thermal Data

| РСВ Туре   | Airflow<br>Velocity<br>(m/sec) | θ <sub>JA</sub>      | θ <sub>JB</sub>     | θ <sub>JC_TOP</sub> | θ <sub>JC_BOT</sub> | Unit |

|------------|--------------------------------|----------------------|---------------------|---------------------|---------------------|------|

| JEDEC      | 0.0                            | 17.8 <sup>1, 2</sup> | 6.3 <sup>1, 3</sup> | 4.7 <sup>1, 4</sup> | 1.2 <sup>1, 4</sup> | °C/W |

| 2s2p Board | 1.0                            | 15.6 <sup>1, 2</sup> | 5.9 <sup>1, 3</sup> | N/A <sup>5</sup>    | N/A <sup>5</sup>    | °C/W |

|            | 2.5                            | 15.0 <sup>1, 2</sup> | 5.7 <sup>1, 3</sup> | N/A <sup>5</sup>    | N/A <sup>5</sup>    | °C/W |

| 10-Layer   | 0.0                            | 13.8                 | 4.6                 | 4.7                 | 1.2                 | °C/W |

| PCB        | 1.0                            | 12.7                 | 4.6                 | N/A <sup>5</sup>    | N/A <sup>5</sup>    | °C/W |

|            | 2.5                            | 12.0                 | 4.6                 | N/A <sup>5</sup>    | N/A <sup>5</sup>    | °C/W |

<sup>1</sup> Per JEDEC 51-7, plus JEDEC 51-5 2s2p test board.

<sup>2</sup> Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

<sup>3</sup> Per JEDEC JESD51-8 (still air).

<sup>4</sup> Per MIL-STD 883, Method 1012.1.

<sup>5</sup> N/A means not applicable.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

012

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

| _ | 1     | 2    | 3    | 4     | 5      | 6     | 7     | 8     | 9     | 10    | 11     | 12    | 13        | 14      | _ |

|---|-------|------|------|-------|--------|-------|-------|-------|-------|-------|--------|-------|-----------|---------|---|

| A | AGND  | AGND | AGND | AVDD2 | AVDD1  | AGND  | CLK+  | CLK-  | AGND  | AVDD1 | AVDD2  | AGND  | AGND      | AGND    | A |

| в | AVDD3 | AGND | AGND | AVDD2 | AVDD1  | AGND  | AGND  | AGND  | AGND  | AVDD1 | AVDD2  | AGND  | AGND      | AVDD3   | в |

| с | AVDD3 | AGND | AGND | AVDD2 | AVDD1  | AGND  | SYNC+ | SYNC- | AGND  | AVDD1 | AVDD2  | AGND  | AGND      | AVDD3   | c |

| D | AGND  | AGND | AGND | AVDD2 | AVDD1  | AGND  | AVDD1 | AGND  | AGND  | AVDD1 | AVDD2  | AGND  | AGND      | AGND    | D |

| E | VIN-B | AGND | AGND | AVDD2 | AVDD1  | AGND  | AGND  | AGND  | AGND  | AVDD1 | AVDD2  | AGND  | AGND      | VIN-A   | E |

| F | VIN+B | AGND | AGND | AVDD2 | AGND   | AGND  | AGND  | AGND  | AGND  | AGND  | AVDD2  | AGND  | AGND      | VIN+A   | F |

| G | AGND  | AGND | AGND | AGND  | AGND   | AGND  | AGND  | AGND  | AGND  | AGND  | AVDD2  | AGND  | AGND      | AGND    | G |

| н | AGND  | AGND | AGND | CSB   | AGND   | AGND  | AGND  | AGND  | AGND  | V_1P0 | AGND   | AGND  | AGND      | AGND    | н |

| J | FD_B  | AGND | AGND | SCLK  | SPIVDD | AGND  | AGND  | AGND  | AGND  | AVDD2 | SPIVDD | AGND  | PDWN/STBY | FD_A    | J |

| к | DGND  | DGND | AGND | SDIO  | AGND   | AGND  | AGND  | AGND  | AGND  | AGND  | AGND   | AGND  | DCO-      | DCO+    | к |

| L | DVDD  | DVDD | DGND | DGND  | AGND   | AGND  | AGND  | AGND  | AGND  | AGND  | AGND   | AGND  | STATUS-   | STATUS+ | L |

| м | D1+   | D1-  | DVDD | DVDD  | DRVDD  | DRVDD | DRVDD | DRGND | DRGND | DRGND | DRGND  | DRGND | D13-      | D13+    | м |

| N | D2-   | D3   | D4   | D5    | D6     | D0    | DRVDD | DRGND | D7-   | D8    | D9-    | D10-  | D11-      | D12-    | N |

| Р | D2+   | D3+  | D4+  | D5+   | D6+    | D0+   | DRVDD | DRGND | D7+   | D8+   | D9+    | D10+  | D11+      | D12+    | Р |

|   | 1     | 2    | 3    | 4     | 5      | 6     | 7     | 8     | 9     | 10    | 11     | 12    | 13        | 14      |   |

Figure 11. Pin Configuration (Top View)

#### Table 8. Pin Function Descriptions

| Pin No.                                                                                                                                                                                                                                                                                                                         | Mnemonic     | Туре      | Description                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supplies                                                                                                                                                                                                                                                                                                                  |              |           |                                                                                                                                                                                                                                                                                  |

| A5, A10, B5, B10, C5, C10, D5, D7, D10,<br>E5, E10                                                                                                                                                                                                                                                                              | AVDD1        | Supply    | Analog Power Supply (1.25 V Nominal).                                                                                                                                                                                                                                            |

| A4, A11, B4, B11, C4, C11, D4, D11, E4,<br>E11, F4, F11, G11, J10                                                                                                                                                                                                                                                               | AVDD2        | Supply    | Analog Power Supply (2.50 V Nominal).                                                                                                                                                                                                                                            |

| B1, B14, C1, C14                                                                                                                                                                                                                                                                                                                | AVDD3        | Supply    | Analog Power Supply (3.3 V Nominal)                                                                                                                                                                                                                                              |

| L1, L2, M3, M4                                                                                                                                                                                                                                                                                                                  | DVDD         | Supply    | Digital Power Supply (1.25 V Nominal).                                                                                                                                                                                                                                           |

| M5, M6, M7, N7, P7                                                                                                                                                                                                                                                                                                              | DRVDD        | Supply    | Digital Driver Power Supply (1.25 V Nominal).                                                                                                                                                                                                                                    |

| J5, J11                                                                                                                                                                                                                                                                                                                         | SPIVDD       | Supply    | Digital Power Supply for SPI (1.8 V to 3.4 V).                                                                                                                                                                                                                                   |

| K1, K2, L3, L4                                                                                                                                                                                                                                                                                                                  | DGND         | Ground    | Ground Reference for DVDD.                                                                                                                                                                                                                                                       |

| M8 to M12, N8, P8                                                                                                                                                                                                                                                                                                               | DRGND        | Ground    | Ground Reference for DRVDD.                                                                                                                                                                                                                                                      |

| A1, A2, A3, A6, A9, A12, A13, A14, B2, B3,<br>B6, B7, B8, B9, B12, B13, C2, C3, C6, C9,<br>C12, C13, D1, D2, D3, D6, D8, D9, D12,<br>D13, D14, E2, E3, E6 to E9, E12, E13, F2,<br>F3, F5 to F10, F12, F13, G1 to G10, G12,<br>G13, G14, H1, H2, H3, H5 to H9, H11 to<br>H14, J2, J3, J6 to J9, J12, K3, K5 to K12,<br>L5 to L12 | AGND         | Ground    | Ground Reference for AVDD.                                                                                                                                                                                                                                                       |

| Analog                                                                                                                                                                                                                                                                                                                          |              |           |                                                                                                                                                                                                                                                                                  |

| E14, F14                                                                                                                                                                                                                                                                                                                        | VIN-A, VIN+A | Input     | ADC A Analog Input Complement/True.                                                                                                                                                                                                                                              |

| E1, F1                                                                                                                                                                                                                                                                                                                          | VIN-B, VIN+B | Input     | ADC B Analog Input Complement/True.                                                                                                                                                                                                                                              |

| H10                                                                                                                                                                                                                                                                                                                             | V_1P0        | Input/DNC | 1.0 V Reference Voltage Input/Do Not Connect. This pin is configurable through the SPI as a no connect or as an input. Do not connect this pin if using the internal reference. This pin requires a 1.0 V reference voltage input if using an external voltage reference source. |

| A7, A8                                                                                                                                                                                                                                                                                                                          | CLK+, CLK-   | Input     | Clock Input True/Complement.                                                                                                                                                                                                                                                     |

| CMOS Outputs                                                                                                                                                                                                                                                                                                                    |              |           |                                                                                                                                                                                                                                                                                  |

| J14, J1                                                                                                                                                                                                                                                                                                                         | FD_A, FD_B   | Output    | Fast Detect Outputs for Channel A and Channel B.                                                                                                                                                                                                                                 |

| Digital Inputs                                                                                                                                                                                                                                                                                                                  |              |           |                                                                                                                                                                                                                                                                                  |

| C7, C8                                                                                                                                                                                                                                                                                                                          | SYNC+, SYNC- | Input     | Active High LVDS SYNC Input—True/Complement.                                                                                                                                                                                                                                     |

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 8. Pin Function Descriptions (Continued)

| Pin No.      | Mnemonic         | Туре         | Description                                     |  |

|--------------|------------------|--------------|-------------------------------------------------|--|

| Data Outputs |                  |              |                                                 |  |

| N6, P6       | D0-, D0+         | Output       | LVDS Lane 0 Output Data—Complement/True.        |  |

| M1, M2       | D1+, D1-         | Output       | LVDS Lane 1 Output Data—True/Complement.        |  |

| N1, P1       | D2-, D2+         | Output       | LVDS Lane 2 Output Data—Complement/True.        |  |

| N2, P2       | D3-, D3+         | Output       | LVDS Lane 3 Output Data—Complement/True.        |  |

| N3, P3       | D4-, D4+         | Output       | LVDS Lane 4 Output Data—Complement/True.        |  |

| N4, P4       | D5–, D5+         | Output       | LVDS Lane 5 Output Data—Complement/True.        |  |

| N5, P5       | D6-, D6+         | Output       | LVDS Lane 6 Output Data—Complement/True.        |  |

| N9, P9       | D7-, D7+         | Output       | LVDS Lane 7 Output Data—Complement/True.        |  |

| N10, P10     | D8-, D8+         | Output       | LVDS Lane 8 Output Data—Complement/True.        |  |

| N11, P11     | D9-, D9+         | Output       | LVDS Lane 9 Output Data—Complement/True.        |  |

| N12, P12     | D10-, D10+       | Output       | LVDS Lane 10 Output Data—Complement/True.       |  |

| N13, P13     | D11-, D11+       | Output       | LVDS Lane 11 Output Data—Complement/True.       |  |

| N14, P14     | D12-, D12+       | Output       | LVDS Lane 12 Output Data—Complement/True.       |  |

| M13, M14     | D13-, D13+       | Output       | LVDS Lane 13 Output Data—Complement/True.       |  |

| L13, L14     | STATUS-, STATUS+ | Output       | LVDS Status Output Data—Complement/True.        |  |

| K13, K14     | DCO-, DCO+       | Output       | LVDS Digital Clock Output Data—Complement/True. |  |

| SPI Controls |                  |              |                                                 |  |

| K4           | SDIO             | Input/output | SPI Serial Data Input/Output.                   |  |

| J4           | SCLK             | Input        |                                                 |  |

| H4           | CSB              | Input        |                                                 |  |

| J13          | PDWN/STBY        | Input        |                                                 |  |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

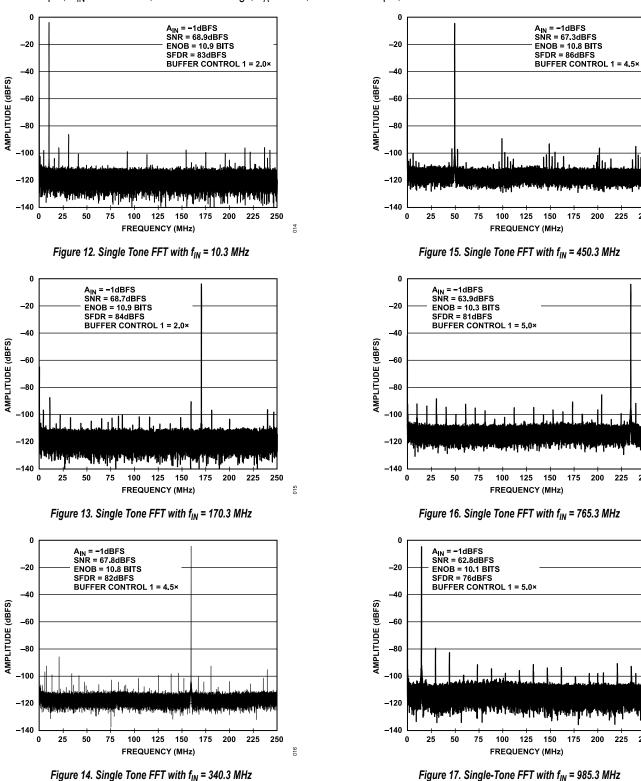

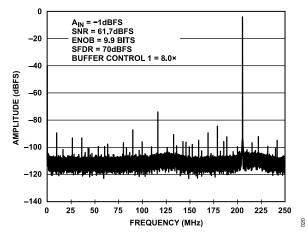

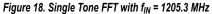

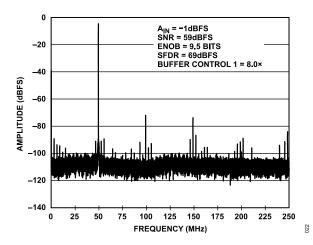

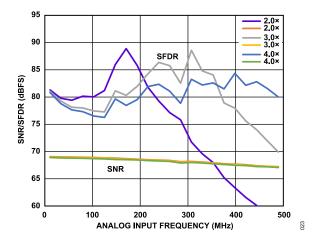

AVDD1 = 1.2 V, AVDD2 = 2.5 V, AVDD3 = 3.3 V, DVDD = 1.2 V, DRVDD = 1.2 V, SPIVDD = 1.8 V, sampling rate = 500 MHz, 1.6 V p-p full-scale differential input, A<sub>IN</sub> = -1.0 dBFS, default SPI settings, T<sub>A</sub> = 25°C, 256k FFT sample, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

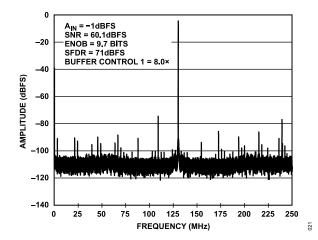

Figure 21. SNR/SFDR vs. Analog Input Frequency (f<sub>IN</sub>); f<sub>IN</sub> < 500 MHz; Buffer Control 1 Setting = 2.0×, 3.0×, and 4.0×

Figure 22. Two-Tone FFT with  $f_{IN1}$  = 184 MHz and  $f_{IN2}$  = 187 MHz

Figure 23. Two-Tone FFT; f<sub>IN1</sub> = 338 MHz, f<sub>IN2</sub> = 341 MHz

## **TYPICAL PERFORMANCE CHARACTERISTICS**

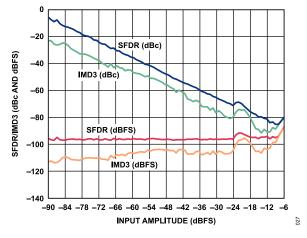

Figure 24. Two-Tone SFDR/IMD3 vs. Input Amplitude ( $A_{IN}$ ) with  $f_{IN1}$  = 184 MHz and  $f_{IN2}$  = 187 MHz

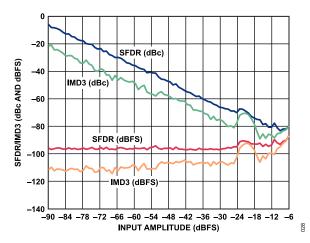

Figure 25. Two-Tone SFDR/IMD3 vs. Input Amplitude ( $A_{IN}$ ) with  $f_{IN1}$  = 338 MHz and  $f_{IN2}$  = 341 MHz

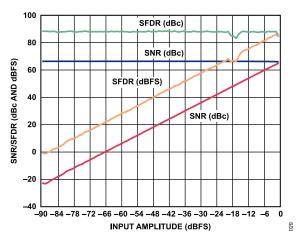

Figure 26. SNR/SFDR vs. Input Amplitude, f<sub>IN</sub> = 170.3 MHz

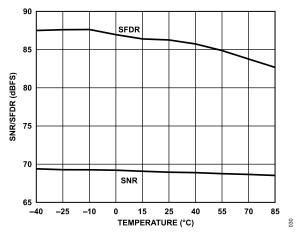

Figure 27. SNR/SFDR vs. Temperature, f<sub>IN</sub> = 170.3 MHz

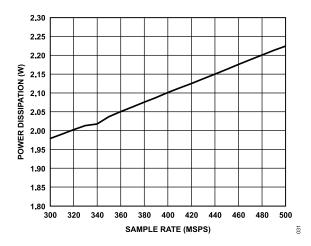

Figure 28. Power Dissipation vs. Sample Rate (f<sub>S</sub>) (Default SPI)

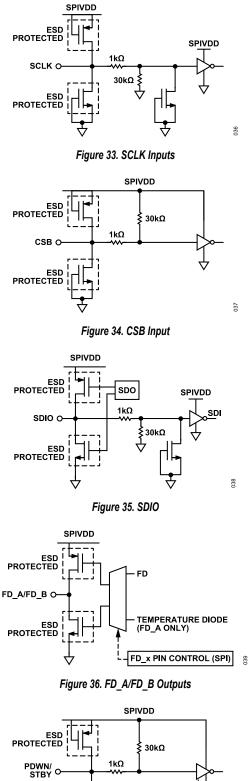

# **EQUIVALENT CIRCUITS**

Figure 32. LVDS Digital Outputs, STATUS±, DCO±

035

Figure 37. PDWN/STBY Input

ESD PROTECTED

040

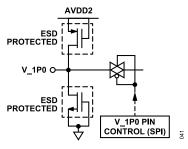

# **EQUIVALENT CIRCUITS**

Figure 38. V\_1P0 Input/Output

The AD9684 has two analog input channels and 14 LVDS output lane pairs. The ADC is designed to sample wide bandwidth analog signals of up to 2 GHz. The AD9684 is optimized for wide input bandwidth, a high sampling rate, excellent linearity, and low power in a small package.

The dual ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs that support a variety of user selectable input ranges. An integrated voltage reference eases design considerations.

The AD9684 has several functions that simplify the AGC function in a communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect output bits of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly reduce the system gain to avoid an overrange condition at the ADC input.

The LVDS outputs can be configured depending on the decimation ratio. Multiple device synchronization is supported through the SYNC± input pins.

## ADC ARCHITECTURE

The architecture of the AD9684 consists of an input buffered pipelined ADC. The input buffer provides a termination impedance to the analog input signal. This termination impedance can be changed using the SPI to meet the termination needs of the driver/ amplifier. The default termination value is set to 400  $\Omega$ . The input buffer is optimized for high linearity, low noise, and low power.

The input buffer provides a linear high input impedance (for ease of drive) and reduces kickback from the ADC. The buffer is optimized for high linearity, low noise, and low power. The quantized outputs from each stage are combined into a final 14-bit result in the digital correction logic. The pipelined architecture permits the first stage to operate with a new input sample, whereas the remaining stages operate with the preceding samples. Sampling occurs on the rising edge of the clock.

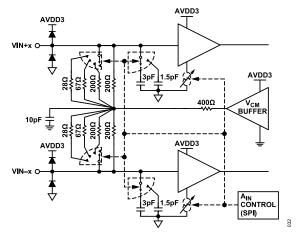

## ANALOG INPUT CONSIDERATIONS

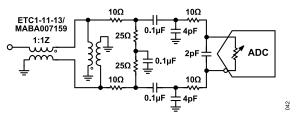

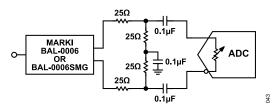

The analog input to the AD9684 is a differential buffer. The internal common-mode voltage of the buffer is 2.05 V. The clock signal alternately switches the input circuit between sample mode and hold mode. When the input circuit is switched into sample mode, the signal source must be capable of charging the sample capacitors and settling within one-half of a clock cycle. A small resistor, in series with each input, helps reduce the peak transient current injected from the output stage of the driving source. In addition, low Q inductors or ferrite beads can be placed on each leg of the input to reduce high differential capacitance at the analog inputs and, thus, achieve the maximum bandwidth of the ADC. Such use of low Q inductors or ferrite beads is required when driving the converter front end at high IF frequencies. Place either a differential capacitor

or two single-ended capacitors on the inputs to provide a matching passive network. This ultimately creates a low-pass filter at the input, which limits unwanted broadband noise. For more information, see the AN-742 Application Note, the AN-827 Application Note, and the *Analog Dialogue* article "Transformer-Coupled Front-End for Wideband A/D Converters" (Volume 39, April 2005). In general, the precise values depend on the application.

For best dynamic performance, the source impedances driving VIN+x and VIN-x must be matched such that common-mode settling errors are symmetrical. These errors are reduced by the common-mode rejection of the ADC. An internal reference buffer creates a differential reference that defines the span of the ADC core.

Maximum SNR performance is achieved by setting the ADC to the largest span in a differential configuration. In the case of the AD9684, the available span is 2.06 V p-p differential.

## **Differential Input Configurations**

There are several ways to drive the AD9684, either actively or passively. However, optimum performance is achieved by driving the analog input differentially.

For applications in which SNR and SFDR are key parameters, differential transformer coupling is the recommended input configuration because the noise performance of most amplifiers is not adequate to achieve the true performance of the AD9684.

For low to midrange frequencies, a double balun or double transformer network is recommended for optimum performance of the AD9684 (see Figure 39). For higher frequencies in the second and third Nyquist zones, it is better to remove some of the front-end passive components to ensure wideband operation (see Figure 40).

Figure 39. Differential Transformer-Coupled Configuration for First and Second Nyquist Frequencies

Figure 40. Differential Transformer-Coupled Configuration for Second and Third Nyquist Frequencies

#### **Input Common Mode**

The analog inputs of the AD9684 are internally biased to the common mode as shown in Figure 41. The common-mode buffer has a limited range in that the performance suffers greatly if the common-mode voltage drops by more than 100 mV. Therefore, in dc-coupled applications, set the common-mode voltage to 2.05 V  $\pm$  100 mV to ensure proper ADC operation.

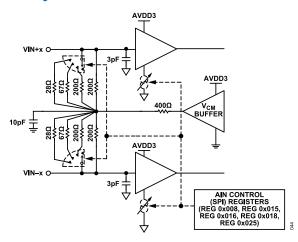

## Analog Input Controls and SFDR Optimization

The AD9684 offers flexible controls for the analog inputs, such as input termination and buffer current. All of the available controls are shown in Figure 41.

Figure 41. Analog Input Controls

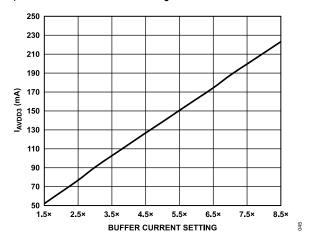

Using Register 0x018, the buffer currents on each channel can be scaled to optimize the SFDR over various input frequencies and bandwidths of interest. As the input buffer currents are set, the amount of current required by the AVDD3 supply changes. For a complete list of buffer current settings, see Table 29.

Figure 42. AVDD3 Power (I<sub>AVDD3</sub>) vs. Buffer Current Control Setting in Register 0x018

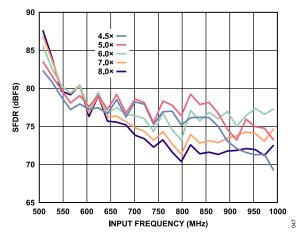

Figure 43. Buffer Current Sweeps (SFDR vs. Input Frequency and I<sub>BUFF</sub>), 10 MHz <  $f_{\rm IN}$  < 500 MHz

Figure 44. Buffer Current Sweeps (SFDR vs. Input Frequency and  $I_{BUFF}$ ), 500 MHz <  $f_{\rm IN}$  < 1000 MHz

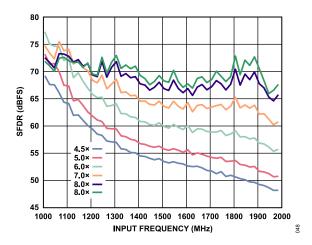

Figure 45. Buffer Current Sweeps (SFDR vs. Input Frequency and I<sub>BUFF</sub>), 1 GHz < f<sub>IN</sub> < 2 GHz, Front-End Network Shown in Figure 40

Figure 43, Figure 44, and Figure 45 show how the SFDR can be optimized using the buffer current setting in Register 0x018

for different Nyquist zones. At frequencies greater than 1 GHz, it is better to run the ADC at input amplitudes less than -1 dBFS (-3 dBFS, for example). This greatly improves the linearity of the converted signal without sacrificing SNR performance.

#### Table 9. SFDR Optimization for Input Frequencies

Table 9 shows the recommended buffer current and full-scale voltage settings for the different analog input frequency ranges.

|                    | zation for input i requencies |                        |                          |                                                 |

|--------------------|-------------------------------|------------------------|--------------------------|-------------------------------------------------|

|                    | Buffer Control 1              | Input Full-Scale Range | Input Full-Scale Control |                                                 |

| Frequency          | (Register 0x018)              | (Register 0x025)       | (Register 0x030)         | Input Termination (Register 0x016) <sup>1</sup> |

| DC to 250 MHz      | 0x20 (2.0×)                   | 0x0C (2.06 V p-p)      | 0x04                     | 0x0C/0x1C/0x6C                                  |

| 250 MHz to 500 MHz | 0x70 (4.5×)                   | 0x0C (2.06 V p-p)      | 0x04                     | 0x0C/0x1C/0x6C                                  |

| 500 MHz to 1 GHz   | 0x80 (5.0×)                   | 0x08 (1.46 V p-p)      | 0x18                     | 0x0C/0x1C/0x6C                                  |

| 1 GHz to 2 GHz     | 0xF0 (8.5×)                   | 0x08 (1.46 V p-p)      | 0x18                     | 0x0C/0x1C/0x6C                                  |

<sup>1</sup> The input termination can be changed to accommodate the application with little or no impact to ac performance.

# Absolute Maximum Input Swing

The absolute maximum input swing allowed at the inputs of the AD9684 is 4.3 V p-p differential. Signals operating near or at this level can cause permanent damage to the ADC.

## Dither

The AD9684 has internal on-chip dither circuitry that improves the ADC linearity and SFDR, particularly at smaller signal levels. A known but random amount of white noise is injected into the input of the AD9684. This dither improves the small signal linearity within the ADC transfer function and is precisely subtracted out digitally. The dither is turned on by default and does not reduce the ADC input dynamic range. The data sheet specifications and limits are obtained with the dither turned on.

The dither is turned on by default. It is not recommended to turn it off.

## VOLTAGE REFERENCE

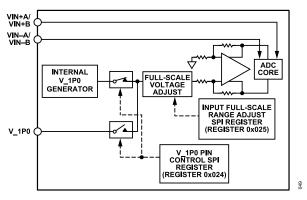

A stable and accurate 1.0 V voltage reference is built into the AD9684. This internal 1.0 V reference sets the full-scale input range of the ADC. For more information on adjusting the input swing, see Table 29. Figure 46 shows the block diagram of the internal 1.0 V reference controls.

Figure 46. Internal Reference Configuration and Controls

Register 0x024 enables the user either to use this internal 1.0 V reference, or to provide an external 1.0 V reference. When using an external voltage reference, provide a 1.0 V reference. The full-scale adjustment is made using the SPI, irrespective of the reference voltage. For more information on adjusting the full-scale level of the AD9684, see the Memory Map Register Table section.

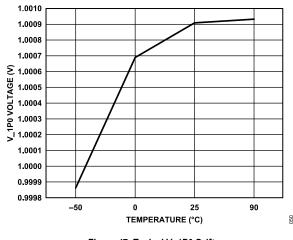

The use of an external reference may be necessary, in some applications, to enhance the gain accuracy of the ADC or improve thermal drift characteristics. Figure 47 shows the typical drift characteristics of the internal 1.0 V reference.

Figure 47. Typical V\_1P0 Drift

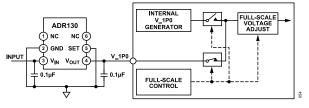

The external reference must be a stable 1.0 V reference. The ADR130 is a good option for providing the 1.0 V reference. Figure 48 shows how the ADR130 can be used to provide the external 1.0 V reference to the AD9684. The grayed out areas show unused blocks within the AD9684 while using the ADR130 to provide the external reference.

Figure 48. External Reference Using the ADR130

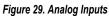

## **CLOCK INPUT CONSIDERATIONS**

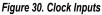

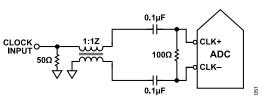

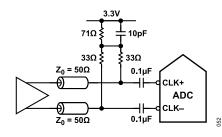

For optimum performance, drive the AD9684 sample clock inputs (CLK+ and CLK-) with a differential signal. This signal is typically ac-coupled to the CLK+ and CLK- pins via a transformer or clock drivers. These pins are biased internally and require no additional biasing.

Figure 49 shows a preferred method for clocking the AD9684. The low jitter clock source is converted from a single-ended signal to a differential signal using an RF transformer.

Figure 49. Transformer Coupled Differential Clock

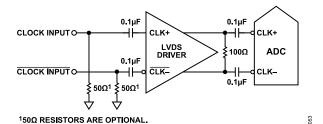

Another option is to ac couple a differential CML or LVDS signal to the sample clock input pins, as shown in Figure 50 and Figure 51.

Figure 50. Differential CML Sample Clock

Figure 51. Differential LVDS Sample Clock

## **Clock Duty Cycle Considerations**

Typical high speed ADCs use both clock edges to generate a variety of internal timing signals. As a result, these ADCs may be sensitive to the clock duty cycle. Commonly, a 5% tolerance is required on the clock duty cycle to maintain dynamic performance characteristics. In applications where the clock duty cycle cannot be guaranteed to be 50%, a higher multiple frequency clock can be supplied to the device. The AD9684 can be clocked at 2 GHz with the internal clock divider set to 2. The output of the divider offers a 50% duty cycle, high slew rate (fast edge) clock signal to the internal ADC. See the Memory Map section for more details on using this feature.

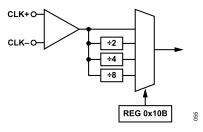

## **Input Clock Divider**

The AD9684 contains an input clock divider with the ability to divide the Nyquist input clock by 1, 2, 4, and 8. The divider ratios can be selected using Register 0x10B. This is shown in Figure 52.

The maximum frequency at the CLK± inputs is 4 GHz. This is the limit of the divider. In applications where the clock input is a multiple of the sample clock, the appropriate divider ratio must be programmed into the clock divider before applying the clock signal. This ensures that the current transients during device startup are controlled.

Figure 52. Clock Divider Circuit

The AD9684 clock divider can be synchronized using the external SYNC± input. A valid SYNC± input causes the clock divider to reset to a programmable state. This feature is enabled by setting Bit 7 of Register 0x10D. This synchronization feature allows multiple devices to have their clock dividers aligned to guarantee simultaneous input sampling.

## Input Clock Divider 1/2 Period Delay Adjustment

The input clock divider inside the AD9684 provides phase delay in increments of  $\frac{1}{2}$  the input clock cycle. Program Register 0x10C to enable this delay independently for each channel.

## **Clock Fine Delay Adjustment**

To adjust the AD9684 sampling edge instant, write to Register 0x117 and Register 0x118. Setting Bit 0 of Register 0x117 enables the fine delay feature, and Register 0x118, Bits[7:0] set the value of the delay. This value can be programmed individually for each channel. The clock delay can be adjusted from -151.7 ps to +150 ps in  $\sim$ 1.7 ps increments. The clock delay adjust takes effect immediately when it is enabled via SPI writes. Enabling the clock fine delay adjustment in Register 0x117 causes a datapath reset.

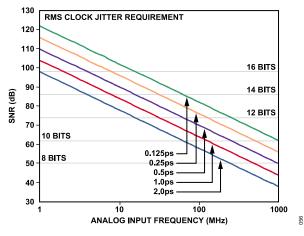

## **Clock Jitter Considerations**

High speed, high resolution ADCs are sensitive to the quality of the clock input. The degradation in SNR at a given input frequency  $(f_A)$  due only to aperture jitter  $(t_J)$  can be calculated by

$$SNR = 20 \times \log 10 (2 \times \pi \times f_A \times t_J)$$

(1)

In this equation, the rms aperture jitter represents the root mean square of all jitter sources, including the clock input, analog input signal, and ADC aperture jitter specifications. IF undersampling applications are particularly sensitive to jitter (see Figure 53).

Figure 53. Ideal SNR vs. Analog Input Frequency and Jitter

Treat the clock input as an analog signal when aperture jitter may affect the dynamic range of the AD9684. Separate the power supplies for the clock drivers from the ADC output driver supplies to avoid modulating the clock signal with digital noise. If the clock is generated from another type of source (by gating, dividing, or other methods), retime the clock by the original clock at the last step. For more in-depth information about jitter performance as it relates to ADCs, see the AN-501 Application Note and the AN-756 Application Note.

Figure 54 shows the estimated SNR of the AD9684 across the input frequency for different clock induced jitter values. Estimate the SNR using the following equation:

$$SNR(dBFS) = 10\log\left(10\left(\frac{-SNR_{ADC}}{10}\right) + 10\left(\frac{-SNR_{JITTER}}{10}\right)\right)$$

(2)

Figure 54. Estimated SNR Degradation for the AD9684 vs. Input Frequency and Clock Jitter

## POWER-DOWN/STANDBY MODE

The AD9684 has a PDWN/STBY pin that configures the device in power-down or standby mode. The default operation is the power-down function. The PDWN/STBY pin is a logic high pin. The

analog.com

power-down option can also be set via Register 0x03F and Register 0x040.

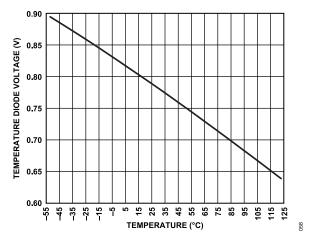

## **TEMPERATURE DIODE**

The AD9684 contains a diode-based temperature sensor for measuring the temperature of the die. This diode can output a voltage and serve as a coarse temperature sensor to monitor the internal die temperature.

The temperature diode voltage can be output to the FD\_A pin using the SPI. Use Register 0x028, Bit 0 to enable or disable the diode. Register 0x028 is a local register. Channel A must be selected in the device index register (Register 0x008) to enable the temperature diode readout. Configure the FD\_A pin to output the diode voltage by programming Register 0x040, Bits[2:0]. See Table 29 for more information.

The voltage response of the temperature diode (with SPIVDD = 1.8 V) is shown in Figure 55.

Figure 55. Diode Voltage vs. Temperature

## ADC OVERRANGE AND FAST DETECT

In receiver applications, it is desirable to have a mechanism to reliably determine when the converter is about to be clipped. The standard overrange pin outputs information on the state of the analog input. It is also helpful to have a programmable threshold below full scale that allows time to reduce the gain before the clip actually occurs. In addition, because input signals can have significant slew rates, the latency of this function is of major concern. Highly pipe-lined converters can have significant latency. The AD9684 contains fast detect circuitry for individual channels to monitor the threshold and assert the FD\_A and FD\_B pins.

## ADC OVERRANGE

The ADC overrange indicator is asserted when an overrange is detected on the input of the ADC. The overrange indicator can be output on the STATUS $\pm$  pins (when CSB > 0). The latency of this overrange indicator matches the sample latency.

The AD9684 also records any overrange condition in any of the four virtual converters. The overrange status of each virtual converter is registered as a sticky bit in Register 0x563. The contents of Register 0x563 can be cleared using Register 0x562, by toggling the bits corresponding to the virtual converter to set and reset the position.

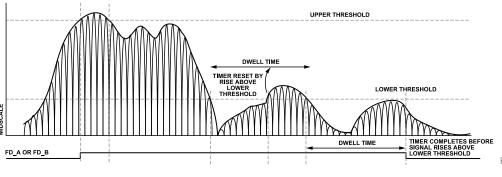

# FAST THRESHOLD DETECTION (FD\_A AND FD\_B)

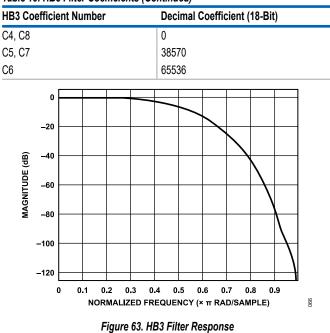

The fast detect (FD) bit (enabled via the control bits in Register 0x559) is immediately set whenever the absolute value of the input signal exceeds the programmable upper threshold level. The FD bit is cleared only when the absolute value of the input signal drops below the lower threshold level for greater than the programmable dwell time. This feature provides hysteresis and prevents the FD bit from excessively toggling. The operation of the upper threshold and lower threshold registers, along with the dwell time registers, is shown in Figure 56.