# AD4682/AD4683

### Pseudo Differential Input, 1 MSPS/500 kSPS, Dual, Simultaneous Sampling, 16-Bit, SAR ADCs

### **FEATURES**

- Dual 16-bit ADC family

- ► Dual simultaneous sampling

- Pseudo differential analog inputs

- ► Throughput conversion rate

- ▶ 1 MSPS for the AD4682

- ▶ 500 kSPS for the AD4683

- ► SNR (typical)

- ▶ 87.5 dB, V<sub>REF</sub> = 3.3 V external

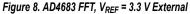

- ▶ 93.4 dB with RES = 1 and OSR = ×8

- On-chip oversampling function

- Alert function

- Resolution boost function

- ▶ INL error (maximum): 2.5 LSBs

- ▶ 2.5 V internal reference

- ▶ High speed serial interface

- ► -40°C to +125°C operation

- ▶ 3 mm × 3 mm, 16-lead LFCSP

### **APPLICATIONS**

- Motor control position feedback

- Motor control current sense

- Sonar

- Power quality

- Data acquisition systems

- Erbium doped fiber amplifier (EDFA) applications

- ▶ Inphase (I) and quadrature (Q) demodulation

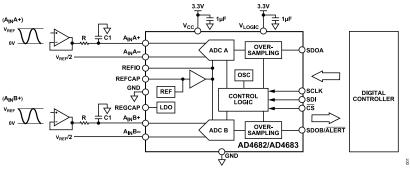

### FUNCTIONAL BLOCK DIAGRAM

### **GENERAL DESCRIPTION**

The AD4682 and the AD4683 are a 16-bit, pin-compatible family of dual, simultaneous sampling, high speed, low power, successive approximation register (SAR), analog-to-digital converters (ADCs) that operate from a 3.0 V to 3.6 V power supply and feature throughput rates up to 1 MSPS for the AD4682 and 500 kSPS for the AD4683. The analog input type is pseudo differential and is sampled and converted on the falling edge of  $\overline{CS}$ .

Integrated on-chip oversampling blocks improve dynamic range and reduce noise at lower bandwidths. A buffered internal 2.5 V reference is included. Alternatively, an external reference up to 3.3 V can be used.

The conversion process and data acquisition use standard control inputs that allow simple interfacing to microprocessors or digital signal processors (DSPs). The devices are compatible with 1.8 V, 2.5 V, and 3.3 V interfaces, using a separate logic supply.

### **COMPANION PARTS**

- ▶ ADC Drivers: ADA4896-2, ADA4940-2, ADA4807-2, LTC6227

- ▶ Voltage References: ADR4533 (3.3 V), ADR4525 (2.5 V)

- Low Dropout Regulators: ADP166, ADP7104, ADP7182

- Additional companion products on the AD4682 and AD4683 product pages

#### Table 1. Related Devices in the Family

| Input Type          | 16-Bit | 14-Bit | 12-Bit |

|---------------------|--------|--------|--------|

| Differential        | AD7380 | AD7381 |        |

| Pseudo Differential | AD7383 | AD7384 |        |

| Single-Ended        | AD7386 | AD7387 | AD7388 |

Figure 1.

Rev. A

DOCUMENT FEEDBACK

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

### TABLE OF CONTENTS

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Companion Parts                             | 1  |

| Functional Block Diagram                    | 1  |

| Specifications                              | 3  |

| Timing Specifications                       | 5  |

| Absolute Maximum Ratings                    | 7  |

| Thermal Resistance                          | 7  |

| Electrostatic Discharge (ESD) Ratings       | 7  |

| ESD Caution                                 | 7  |

| Pin Configuration and Function Descriptions | 8  |

| Typical Performance Characteristics         | 9  |

| Terminology                                 | 13 |

| Theory of Operation                         | 14 |

| Circuit Information                         | 14 |

| Converter Operation                         | 14 |

| Analog Input Structure                      | 14 |

| ADC Transfer Function                       | 15 |

| Applications Information                    | 16 |

| Power Supply                                | 16 |

| Modes of Operation                          | 18 |

| Oversampling                                | 18 |

|    | Resolution Boost                | . 18 |

|----|---------------------------------|------|

|    | Alert                           | . 19 |

|    | Power Modes                     | 19   |

|    | Internal and External Reference | .20  |

| ,  | Software Reset                  | .20  |

|    | Diagnostic Self Test            |      |

|    | terface                         |      |

|    | Reading Conversion Results      |      |

|    | Low Latency Readback            |      |

|    | Reading From Device Registers   |      |

|    | Writing to Device Registers     |      |

|    | CRC                             |      |

|    | egisters                        |      |

|    | Addressing Registers            | .26  |

|    | CONFIGURATION1 Register         |      |

|    | CONFIGURATION2 Register         |      |

|    | ALERT Register                  |      |

|    | ALERT LOW THRESHOLD Register    |      |

|    | ALERT HIGH THRESHOLD Register   |      |

| Oı | utline Dimensions               | 31   |

|    | Ordering Guide                  |      |

|    | Evaluation Boards               |      |

|    |                                 |      |

### **REVISION HISTORY**

### 6/2023—Rev. 0 to Rev. A

| Changes to Specifications Section                |  |

|--------------------------------------------------|--|

| Change to t <sub>SCLKED</sub> Parameter, Table 3 |  |

| Changes to Figure 4 and Figure 5                 |  |

| Changes to Power Supply Section                  |  |

| Changes to Power-Up Section                      |  |

| Changes to Figure 35                             |  |

### 10/2020—Revision 0: Initial Version

$V_{CC}$  = 3.0 V to 3.6 V,  $V_{LOGIC}$  = 1.65 V to 3.6 V, reference voltage ( $V_{REF}$ ) = 2.5 V internal, sampling frequency ( $f_{SAMPLE}$ ) = 1 MSPS (AD4682) or 500 kSPS (AD4683),  $T_A$  = -40°C to +125°C, and no oversampling enabled, unless otherwise noted. FS is full scale. R = 100  $\Omega$  (series with SDOA pin and SDOB pin).

#### Table 2. Specifications

| Parameter                              | Test Conditions/Comments                          | Min                  | Тур                         | Мах                    | Unit     |

|----------------------------------------|---------------------------------------------------|----------------------|-----------------------------|------------------------|----------|

| RESOLUTION                             |                                                   | 16                   |                             |                        | Bits     |

| THROUGHPUT CONVERSION RATE             |                                                   |                      |                             |                        |          |

| AD4682                                 |                                                   |                      |                             | 1                      | MSPS     |

| AD4683                                 |                                                   |                      |                             | 500                    | kSPS     |

| DC ACCURACY                            |                                                   |                      |                             |                        |          |

| No Missing Codes                       |                                                   | 16                   |                             |                        | Bits     |

| Differential Nonlinearity (DNL) Error  |                                                   | -1.0                 | ±0.5                        | +1.0                   | LSB      |

| Integral Nonlinearity (INL) Error      |                                                   | -2.5                 | ±1                          | +2.5                   | LSB      |

| Gain Error                             | -40°C to +125°C                                   | -0.06                | ±0.02                       | +0.06                  | % FS     |

| Gain Error Temperature Drift           |                                                   | -3                   | ±1                          | +3                     | ppm/°C   |

| Gain Error Match                       |                                                   |                      | 0.025                       | +0.07                  | % FS     |

| Offset Error                           |                                                   | -0.5                 | ±0.05                       | +0.5                   | mV       |

| Offset Temperature Drift               |                                                   | -5                   | ±1                          | +5                     | µV/°C    |

| Offset Error Match                     | -40°C to +125°C                                   |                      | 0.05                        | +0.5                   | mV       |

| AC ACCURACY                            | Input frequency (f <sub>IN</sub> ) = 1 kHz        |                      |                             |                        | -        |

| Dynamic Range                          | $V_{\text{REF}} = 3.3 \text{ V} \text{ external}$ |                      | 88                          |                        | dB       |

| , 3                                    |                                                   |                      | 86                          |                        | dB       |

| Oversampled Dynamic Range              | Oversampling ratio (OSR) = ×4                     |                      | 91.8                        |                        | dB       |

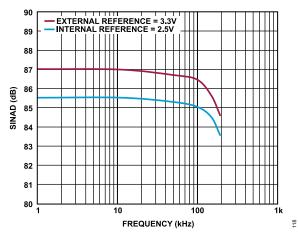

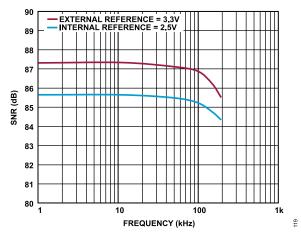

| Signal-to-Noise Ratio (SNR)            | $V_{\text{REF}} = 3.3 \text{ V}$ external         | 85                   | 87.5                        |                        | dB       |

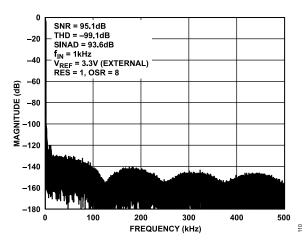

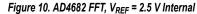

|                                        |                                                   | 84                   | 86                          |                        | dB       |

|                                        | OS_MODE = 1, OSR = ×8, RES = 1                    |                      | 93.4                        |                        | dB       |

|                                        | $f_{IN} = 100 \text{ kHz}$                        |                      | 85.3                        |                        | dB       |

| Spurious-Free Dynamic Range (SFDR)     |                                                   |                      | 101                         |                        | dB       |

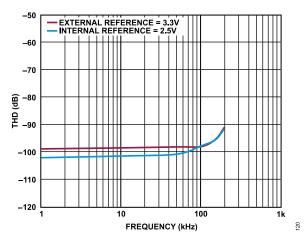

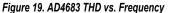

| Total Harmonic Distortion (THD)        |                                                   |                      | -100                        |                        | dB       |

|                                        | f <sub>IN</sub> = 100 kHz                         |                      | -97                         |                        | dB       |

| Signal-to-Noise-and-Distortion (SINAD) | $V_{REF} = 3.3 V$ external                        | 84.5                 | 87                          |                        | dB       |

|                                        | VREF = 0.0 V External                             | 83.5                 | 85.5                        |                        | dB       |

| Channel to Channel Isolation           |                                                   | 00.0                 | -110                        |                        | dB       |

|                                        |                                                   |                      | 110                         |                        |          |

| Voltage Range                          | $(A_{IN}x+)$ to $(A_{IN}x-)$                      | -V <sub>REF</sub> /2 |                             | +V <sub>REF</sub> /2   | V        |

| Absolute Input Voltage Range           |                                                   | -0.1                 |                             | V <sub>REF</sub> + 0.1 | V        |

| Common-Mode Input Range                | A <sub>IN</sub> x-                                | 0.1                  | V <sub>REF</sub> /2 ± 0.075 | VREF 1 0.1             | V        |

| Common-Mode Rejection Ratio (CMRR)     | f <sub>IN</sub> = 500 kHz                         |                      | -70                         |                        | dB       |

| DC Leakage Current                     | IN - 500 KI IZ                                    |                      | 0.1                         | 1                      |          |

| Input Capacitance                      | When in track mode                                |                      | 18                          | I                      | μA<br>pF |

|                                        | When in hold mode                                 |                      | 5                           |                        | pF<br>pF |

| SAMPLING DYNAMICS                      |                                                   |                      | 5                           |                        | рг       |

|                                        |                                                   |                      | 0                           |                        |          |

| Input Bandwidth                        | At -0.1 dB                                        |                      | 6                           |                        | MHz      |

| Anastura Dalau                         | At −3 dB                                          |                      | 25                          |                        | MHz      |

| Aperture Delay                         |                                                   |                      | 2                           | 400                    | ns       |

| Aperture Delay Match                   |                                                   |                      | 26                          | 100                    | ps       |

| Aperture Jitter                        |                                                   |                      | 20                          |                        | ps       |

| REFERENCE INPUT AND OUTPUT             |                                                   |                      |                             |                        |          |

| V <sub>REF</sub> Input                 |                                                   |                      |                             |                        |          |

| Voltage Range                          | External reference                                | 2.49                 |                             | 3.4                    | V        |

### Table 2. Specifications (Continued)

| Parameter                                         | Test Conditions/Comments                   | Min                      | Тур             | Max                      | Unit   |

|---------------------------------------------------|--------------------------------------------|--------------------------|-----------------|--------------------------|--------|

| Current                                           | External reference                         |                          |                 |                          |        |

| AD4682                                            | 1 MSPS                                     |                          | 0.26            | 0.29                     | mA     |

| AD4683                                            | 500 kSPS                                   |                          | 0.23            | 0.26                     | mA     |

| V <sub>REF</sub> Output Voltage                   | -40°C to +125°C                            | 2.495                    | 2.5             | 2.505                    | V      |

| V <sub>REF</sub> Temperature Coefficient          |                                            |                          | 5               | 10                       | ppm/°C |

| V <sub>REF</sub> Noise                            |                                            |                          | 7               |                          | µV rms |

| DIGITAL INPUTS (SCLK, SDI, AND CS)                |                                            |                          |                 |                          |        |

| Logic Levels                                      |                                            |                          |                 |                          |        |

| Input Voltage                                     |                                            |                          |                 |                          |        |

| Low (V <sub>IL</sub> )                            |                                            |                          |                 | 0.2 × V <sub>LOGIC</sub> | V      |

| High (V <sub>IH</sub> )                           |                                            | 0.8 × V <sub>LOGIC</sub> |                 | 20010                    | V      |

| Input Current                                     |                                            |                          |                 |                          |        |

| Low (I <sub>IL</sub> )                            |                                            | -1                       |                 | +1                       | μA     |

| High (I <sub>IH</sub> )                           |                                            | -1                       |                 | +1                       | μΑ     |

| DIGITAL OUTPUTS (SDOA AND SDOB/ALERT)             |                                            |                          |                 |                          |        |

| Output Coding                                     |                                            |                          | Twos complement |                          | Bits   |

| Output Voltage                                    |                                            |                          |                 |                          |        |

| Low (V <sub>OL</sub> )                            | Sink current (I <sub>SINK</sub> ) = 300 µA |                          |                 | 0.4                      | V      |

| High (V <sub>OH</sub> )                           | Source current ( $I_{SOURCE}$ ) = -300 µA  | V <sub>LOGIC</sub> - 0.3 |                 |                          | V      |

| Floating State                                    | (-SOURCE)                                  |                          |                 |                          |        |

| Leakage Current                                   |                                            |                          |                 | ±1                       | μA     |

| Output Capacitance                                |                                            |                          | 10              |                          | pF     |

| POWER SUPPLIES                                    |                                            |                          |                 |                          | P'     |

| V <sub>CC</sub>                                   |                                            |                          |                 |                          |        |

| VCC                                               |                                            | 3.0                      | 3.3             | 3.6                      | V      |

|                                                   | External reference = 3.3 V                 | 3.2                      | 3.3             | 3.6                      | V      |

| V <sub>LOGIC</sub>                                |                                            | 1.65                     | 5.5             | 3.6                      | V      |

| V <sub>CC</sub> Current (I <sub>VCC</sub> )       |                                            | 1.05                     |                 | 5.0                      | V      |

| Normal Mode (Operational)                         | AD4682, 1 MSPS                             |                          | 7.28            | 8.4                      | mA     |

|                                                   | AD4683, 500 kSPS                           |                          | 4.76            | 5.6                      | mA     |

| Normal Mode (Static)                              | AD4003, 500 KSFS                           |                          | 4.70<br>2.3     | 2.8                      | mA     |

| Shutdown Mode                                     |                                            |                          |                 |                          |        |

|                                                   |                                            |                          | 101             | 200                      | μA     |

| V <sub>LOGIC</sub> Current (I <sub>VLOGIC</sub> ) | SDOA and SDOB at 0x1FFF                    |                          | 004             | 050                      |        |

| Normal Mode (Operational)                         | AD4682, 1 MSPS                             |                          | 884             | 950                      | μA     |

|                                                   | AD4683, 500 kSPS                           |                          | 438             | 470                      | μA     |

| Normal Mode (Static)                              |                                            |                          | 10              | 200                      | nA     |

| Shutdown Mode                                     |                                            |                          | 10              | 200                      | nA     |

| Power Dissipation                                 |                                            |                          | 00              | 407                      |        |

| Total Power (P <sub>TOTAL</sub> ) (Operational)   |                                            |                          | 83              | 107                      | mW     |

| V <sub>CC</sub> Power (P <sub>VCC</sub> )         |                                            |                          |                 | 00 C                     |        |

| Normal Mode (Operational)                         | AD4682, 1 MSPS                             |                          | 26.2            | 30.3                     | mW     |

|                                                   | AD4683, 500 kSPS                           |                          | 17.2            | 20.2                     | mW     |

| Normal Mode (Static)                              |                                            |                          | 8               | 11                       | mW     |

| Shutdown Mode                                     |                                            |                          | 365             | 720                      | μW     |

| V <sub>LOGIC</sub> Power (P <sub>VLOGIC</sub> )   | SDOA and SDOB at 0x1FFF                    |                          |                 |                          |        |

| Normal Mode (Operational)                         | AD4682, 1 MSPS                             |                          | 3.2             | 3.5                      | mW     |

|                                                   | AD4683, 500 kSPS                           |                          | 1.6             | 1.7                      | mW     |

| Normal Mode (Static)                              |                                            |                          | 36              | 720                      | nW     |

#### Table 2. Specifications (Continued)

| Parameter     | Test Conditions/Comments | Min | Тур | Max | Unit |

|---------------|--------------------------|-----|-----|-----|------|

| Shutdown Mode |                          |     | 36  | 720 | nW   |

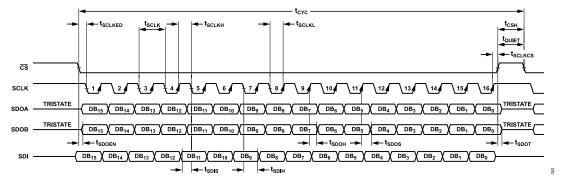

### TIMING SPECIFICATIONS

$V_{CC}$  = 3.0 V to 3.6 V,  $V_{LOGIC}$  = 1.65 V to 3.6 V,  $V_{REF}$  = 2.5 V internal, and  $T_A$  = -40°C to +125°C, unless otherwise noted. See Figure 2 to Figure 5, Figure 37, Figure 38, and Figure 39 for the timing diagrams. Multifunction pin names may be referenced by their relevant function only.

| Parameter             | Min  | Тур | Max | Unit | Description                                                    |

|-----------------------|------|-----|-----|------|----------------------------------------------------------------|

| t <sub>CYC</sub>      |      |     |     |      | Time between conversions                                       |

|                       | 1    |     |     | μs   | AD4682                                                         |

|                       | 2    |     |     | μs   | AD4683                                                         |

| t <sub>SCLKED</sub>   | 0.8  |     |     | ns   | CS falling edge to first SCLK falling edge                     |

| t <sub>SCLK</sub>     | 25   |     |     | ns   | SCLK period                                                    |

| t <sub>SCLKH</sub>    | 10   |     |     | ns   | SCLK high time                                                 |

| t <sub>SCLKL</sub>    | 10   |     |     | ns   | SCLK low time                                                  |

| t <sub>CSH</sub>      | 10   |     |     | ns   | CS pulse width                                                 |

| t <sub>QUIET</sub>    |      |     |     |      | Interface quiet time prior to conversion                       |

|                       | 500  |     |     | ns   | AD4682                                                         |

|                       | 1500 |     |     | ns   | AD4683                                                         |

| t <sub>SDOEN</sub>    |      |     |     |      | CS low to SDOA and SDOB/ALERT enabled                          |

|                       |      |     | 6   | ns   | $V_{LOGIC} \ge 2.25 V$                                         |

|                       |      |     | 8   | ns   | $1.65 \text{ V} \le \text{V}_{\text{LOGIC}} \le 2.3 \text{ V}$ |

| t <sub>SDOH</sub>     | 3    |     |     | ns   | SCLK rising edge to SDOA and SDOB/ALERT hold time              |

| t <sub>SDOS</sub>     |      |     |     |      | SCLK rising edge to SDOA and SDOB/ALERT setup time             |

|                       |      |     | 6   | ns   | $V_{LOGIC} \ge 2.25 V$                                         |

|                       |      |     | 8   | ns   | $1.65 \text{ V} \le \text{V}_{\text{LOGIC}} < 2.3 \text{ V}$   |

| t <sub>SDOT</sub>     |      |     | 8   | ns   | CS rising edge to SDOA and SDOB/ALERT high impedance           |

| t <sub>SDIS</sub>     | 1    |     |     | ns   | SDI setup time prior to SCLK falling edge                      |

| t <sub>SDIH</sub>     | 1    |     |     | ns   | SDI hold time after SCLK falling edge                          |

| t <sub>SCLKCS</sub>   | 0    |     |     | ns   | SCLK rising edge to CS rising edge                             |

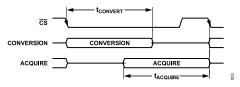

| t <sub>CONVERT</sub>  |      |     | 190 | ns   | Conversion time                                                |

| t <sub>ACQUIRE</sub>  |      |     |     | ns   | Acquire time                                                   |

|                       | 810  |     |     | ns   | AD4682                                                         |

|                       | 1810 |     |     | ns   | AD4683                                                         |

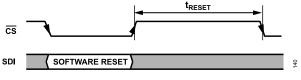

| t <sub>RESET</sub>    |      |     |     |      | Valid time to start conversion after software reset            |

|                       |      | 250 |     | ns   | Valid time to start conversion after soft reset                |

|                       |      | 800 |     | ns   | Valid time to start conversion after hard reset                |

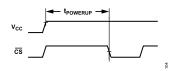

| t <sub>POWERUP</sub>  |      |     |     |      | Supply active to conversion                                    |

|                       |      |     | 5   | ms   | First conversion allowed                                       |

|                       |      |     | 11  | ms   | Settled to within 1% with internal reference                   |

|                       |      |     | 5   | ms   | Settled to within 1% with external reference                   |

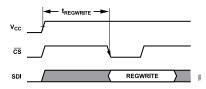

| t <sub>REGWRITE</sub> |      |     | 5   | ms   | Supply active to register read write access allowed            |

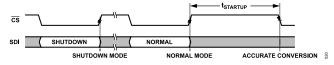

| tSTARTUP              |      |     |     |      | Exiting shutdown mode to conversion                            |

| -                     |      |     | 11  | ms   | Settled to within 1% with internal reference                   |

|                       |      |     | 10  | μs   | Settled to within 1% with external reference                   |

| t <sub>ALERTS</sub>   |      |     | 220 | ns   | Time from $\overline{CS}$ to $\overline{ALERT}$ indication     |

| tALERTC               |      |     | 12  | ns   | Time from $\overline{CS}$ to $\overline{ALERT}$ clear          |

#### Table 3. Timing Specifications

### **Timing Diagrams**

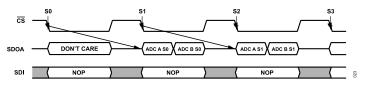

Figure 2. Serial Interface Timing Diagram

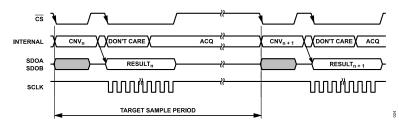

Figure 3. Internal Conversion Acquire Timing

Figure 4. Power-Up Time to Conversion

Figure 5. Power-Up Time to Register Read Write Access

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Parameter                                   | Rating                                                                    |

|---------------------------------------------|---------------------------------------------------------------------------|

| V <sub>CC</sub> to GND                      | -0.3 V to +4 V                                                            |

| V <sub>LOGIC</sub> to GND                   | -0.3 V to +4 V                                                            |

| Input Voltage                               |                                                                           |

| Analog to GND                               | -0.3 V to V_{REF} + 0.3 V, V_{CC} + 0.3 V, or +4 V (whichever is smaller) |

| Digital to GND                              | -0.3 V to V <sub>LOGIC</sub> + 0.3 V, or +4 V (whichever is smaller)      |

| Digital Output Voltage to GND               | -0.3 V to V <sub>LOGIC</sub> + 0.3 V, or +4 V (whichever is smaller)      |

| REFIO Input to GND                          | -0.3 V to V <sub>CC</sub> + 0.3 V                                         |

| Input Current to Any Pin Except<br>Supplies | ±10 mA                                                                    |

| Temperature                                 |                                                                           |

| Operating Range                             | -40°C to +125°C                                                           |

| Storage Range                               | -65°C to +150°C                                                           |

| Junction                                    | 150°C                                                                     |

| Pb-Free Soldering Reflow                    | 260°C                                                                     |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection, junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### Table 5. Thermal Resistance

| Package Type          | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|-----------------------|-----------------|-----------------|------|

| CP-16-45 <sup>1</sup> | 55.4            | 12.7            | °C/W |

<sup>1</sup> Test Condition 1: thermal impedance simulated values are based on JEDEC 2S2P thermal test board four thermal vias. See JEDEC JESDS-51.

### **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Field induced charge device model (FICDM) per ANSI/ESDA/ JE-DEC JS-002.

### ESD Ratings for AD4682 and AD4683

#### Table 6. AD4682 and AD4683, 16-Lead LFCSP

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | ±4000                   | 3A    |

| FICDM     | ±1250                   | C3    |

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

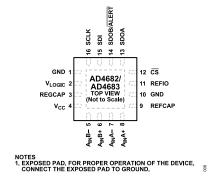

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Figure 6. Pin Configuration

#### Table 7. Pin Function Descriptions

| Pin No. | Mnemonic                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 10   | GND                                    | Ground Reference Points. The GND pins are the ground reference points for all circuitry on the device.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2       | V <sub>LOGIC</sub>                     | Logic Interface Supply Voltage, 1.65 V to 3.6 V. Decouple V <sub>LOGIC</sub> to GND with a 1 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3       | REGCAP                                 | Decoupling Capacitor Pin for Voltage Output from the Internal Regulator. Decouple REGCAP to GND with a 1 µF capacitor. The voltage at REGCAP is 1.9 V typical.                                                                                                                                                                                                                                                                                                                                                                 |

| 4       | V <sub>CC</sub>                        | Power Supply Input Voltage, 3.0 V to 3.6 V. Decouple V <sub>CC</sub> to GND using a 1 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5, 6    | A <sub>IN</sub> B−, A <sub>IN</sub> B+ | Analog Inputs of ADC B. The $A_{IN}B$ - and $A_{IN}B$ + analog inputs form a pseudo differential pair. $A_{IN}B$ - is typically connected to $V_{REF}/2$ , and the $A_{IN}B$ + voltage range is from 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                                                        |

| 7, 8    | A <sub>IN</sub> A-, A <sub>IN</sub> A+ | Analog Inputs of ADC A. The $A_{IN}A$ - and $A_{IN}A$ + analog inputs form a pseudo differential pair. $A_{IN}A$ - is typically connected to $V_{REF}/2$ , and the $A_{IN}A$ + voltage range is from 0 V to $V_{REF}$ .                                                                                                                                                                                                                                                                                                        |

| 9       | REFCAP                                 | Decoupling Capacitor Pin for Band Gap Reference. Decouple REFCAP to GND with a 0.1 µF capacitor. The voltage at REFCAP is 2.5 V typical.                                                                                                                                                                                                                                                                                                                                                                                       |

| 11      | REFIO                                  | Reference Input and Output. The on-chip reference of 2.5 V is available as an output on REFIO for external use if the device is configured accordingly. Alternatively, an external reference of 2.5 V to 3.3 V can be input to REFIO. Set the REFSEL bit in the CONFIGURATION1 register to 1 when using the external reference, and apply the REFSEL bit after $V_{CC}$ and $V_{LOGIC}$ . Decoupling is required on REFIO for both the internal and external reference options. Apply a 1 $\mu$ F capacitor from REFIO to GND. |

| 12      | CS                                     | Chip Select Input. Active low, logic input. CS provides the dual function of initiating conversions on the AD4682 and the AD4683 and framing the serial data transfer.                                                                                                                                                                                                                                                                                                                                                         |

| 13      | SDOA                                   | Serial Data Output A. SDOA functions as a serial data output pin to access the ADC A or ADC B conversion results or data from any of the on-chip registers.                                                                                                                                                                                                                                                                                                                                                                    |

| 14      | SDOB/ALERT                             | Serial Data Output B/Alert Indication Output. The SDOB/ALERT pin can operate as a serial data output pin or an alert indication output.                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                                        | SDOB functions as a serial data output pin to access the ADC B conversion results.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|         |                                        | ALERT operates as an alert pin going low to indicate that a conversion result exceeded a configured threshold. When using ALERT, set the SDO bit in the CONFIGURATION2 register to 1, and set the ALERT_EN bit to 1 in the CONFIGURATION1 register.                                                                                                                                                                                                                                                                            |

| 15      | SDI                                    | Serial Data Input. SDI provides the data written to the on-chip control registers.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16      | SCLK                                   | Serial Clock Input. SCLK is for data transfers to and from the ADC.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | EPAD                                   | Exposed Pad. For proper operation of the device, connect the exposed pad to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

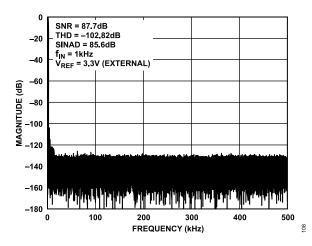

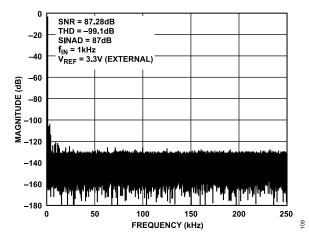

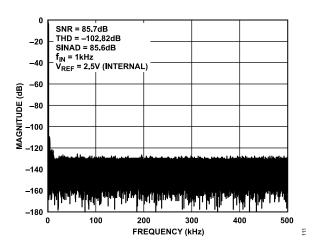

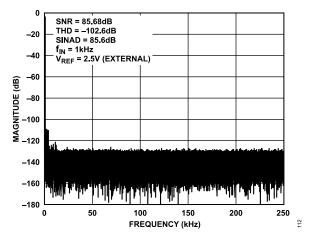

Figure 9. AD4682 FFT, Rolling Average Oversampling

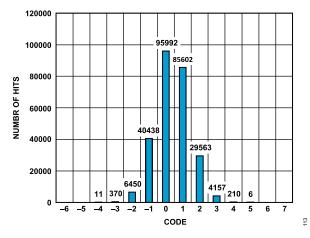

Figure 12. DC Histogram at Code Center

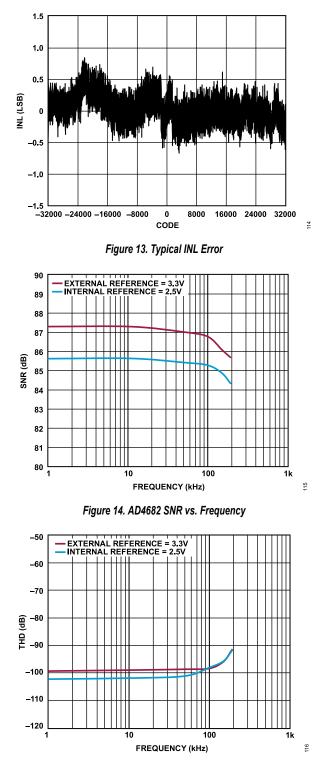

Figure 15. AD4682 THD vs. Frequency

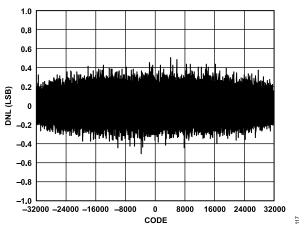

Figure 16. Typical DNL Error

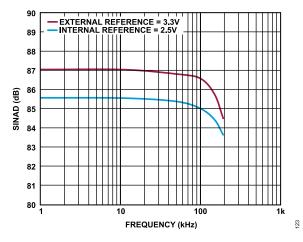

Figure 17. AD4682 SINAD vs. Frequency

Figure 18. AD4683 SNR vs. Frequency

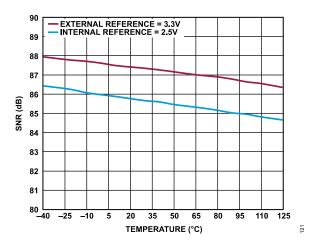

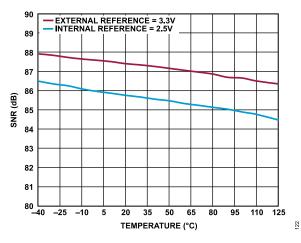

Figure 20. AD4682SNR vs. Temperature

Figure 21. AD4683 SNR vs. Temperature

Figure 22. AD4683 SINAD vs. Frequency

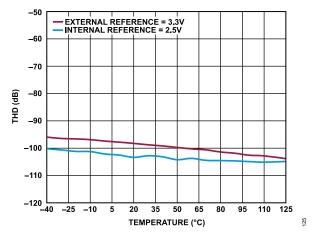

Figure 23. AD4682 THD vs. Temperature

Figure 24. AD4683 THD vs. Temperature

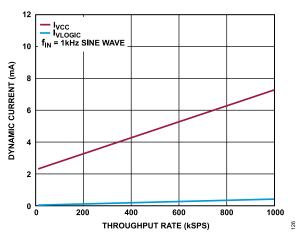

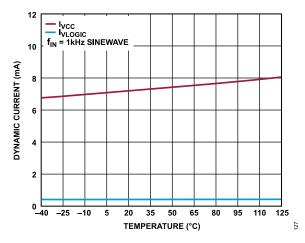

Figure 26. Dynamic Current vs. Temperature

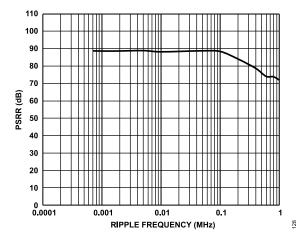

Figure 27. Power Supply Rejection Ratio (PSRR) vs. Ripple Frequency

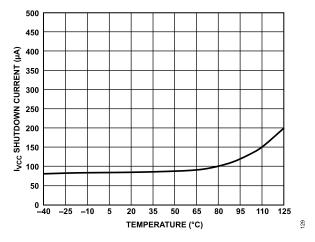

Figure 28. Ivcc Shutdown Current vs. Temperature

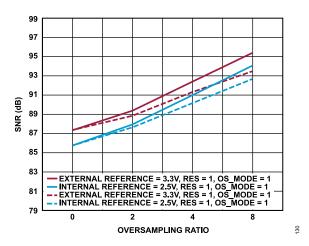

Figure 29. AD4682 SNR vs. Oversampling Ratio, Rolling Average Oversampling

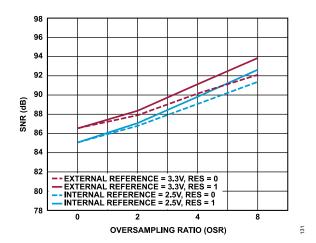

Figure 30. AD4683 SNR vs. Oversampling Ratio, Rolling Average Oversampling

### TERMINOLOGY

### **Differential Nonlinearity (DNL)**

In an ideal ADC, code transitions are 1 LSB apart. DNL is the maximum deviation from this ideal value. DNL is often specified in terms of resolution for which no missing codes are guaranteed.

### Integral Nonlinearity (INL)

INL is the deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line.

### **Gain Error**

The first transition (from 100 ... 000 to 100 ... 001) occurs at a level  $\frac{1}{2}$  LSB above nominal negative full scale. The last transition (from 011 ... 110 to 011 ... 111) occurs for an analog voltage  $\frac{1}{2}$  LSB below the nominal full scale. The gain error is the deviation of the difference between the actual level of the last transition and the actual level of the first transition from the difference between the ideal levels.

### **Gain Error Temperature Drift**

Gain error temperature drift is the gain error change due to a temperature change of 1°C.

### Gain Error Match

Gain error matching is the difference in negative full-scale error between the input channels and the difference in positive full-scale error between the input channels.

### **Offset Error**

Offset error is the difference between the ideal midscale voltage, 0 V, and the actual voltage producing the midscale output code, 0 LSB.

### **Offset Temperature Drift**

Offset temperature drift is the zero error change due to a temperature change of 1°C.

### Offset Error Match

Offset error match is the difference in zero error between the input channels.

### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist

frequency, excluding harmonics and dc. The value for SNR is expressed in dB.

### Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in dB, between the rms amplitude of the input signal and the peak spurious signal.

### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first five harmonic components to the rms value of a full-scale input signal and is expressed in dB.

### Signal-to-Noise-and-Distortion (SINAD)

SINAD is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components that are less than the Nyquist frequency, including harmonics but excluding dc. The value for SINAD is expressed in dB.

### Common-Mode Rejection Ratio (CMRR)

CMRR is the ratio of the power in the ADC output at the frequency, f, to the power of a 200 mV p-p sine wave applied to the commonmode voltage of  $A_{IN}x$ + and  $A_{IN}x$ - of frequency, f. The value for CMRR is expressed in dB.

$$CMRR = 10\log(P_{ADC \ IN}/P_{ADC \ OUT}) \tag{1}$$

where:

$P_{ADC_{IN}}$  is the common-mode power at the frequency, f, applied to the  $A_{IN}x$ + and  $A_{IN}x$ - inputs.

PADC OUT is the power at the frequency, f, in the ADC output.

### **Aperture Delay**

Aperture delay is the measure of the acquisition performance and is the time between the falling edge of the  $\overline{CS}$  input and when the input signal is held for a conversion.

### Aperture Delay Match

Aperture delay match is the difference of the aperture delay between ADC A and ADC B.

### **Aperture Jitter**

Aperture jitter is the variation in aperture delay.

### THEORY OF OPERATION

### **CIRCUIT INFORMATION**

The AD4682 and the AD4683 are high speed, dual, simultaneous sampling, pseudo differential, 16-bit, SAR ADCs. The AD4682 and the AD4683 operate from a 3.0 V to 3.6 V power supply and feature throughput rates of 1 MSPS and 500 kSPS, respectively.

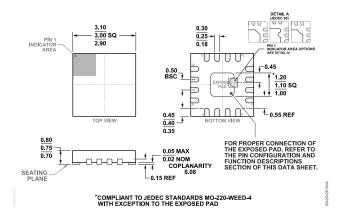

The AD4682 and the AD4682 contain two SAR ADCs and a serial peripheral interface (SPI) with two separate data output pins. The devices are housed in a 16-lead LFCSP, offering the user considerable space-saving advantages over alternative solutions.

Data is accessed from the devices via the SPI. The SPI can operate with one or two serial outputs. The AD4682 and the AD4682 have an on-chip 2.5 V internal reference, V<sub>REF</sub>. If an external reference is required, disable the internal reference, supply a reference value that ranges from 2.5 V to 3.3 V, and set the REFSEL bit in the CONFIGURATION1 register to 1. If the internal reference is used elsewhere in the system, buffer the reference output. The pseudo differential analog input range for the AD4682 and the AD4683 is the common-mode voltage (V<sub>CM</sub>) ± V<sub>REF</sub>/2.

The AD4682 and the AD4683 feature an on-chip oversampling block to improve performance. Rolling average oversampling mode and power-down options that allow power saving between conversions are also available. Configuration of the devices is implemented via the standard SPI (see the Interface section).

### **CONVERTER OPERATION**

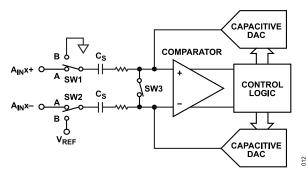

The AD4682 and the AD4683 have two SAR ADCs, each based around two capacitive digital-to-analog converters (DACs). Figure 31 and Figure 32 show the simplified schematics of one of these ADCs in acquisition and conversion phases, respectively. The ADC comprises the control logic, an SAR, and two capacitive DACs. In Figure 31 (the acquisition phase), SW3 is closed, SW1 and SW2 are in Position A, the comparator is held in a balanced condition, and the sampling capacitor ( $C_S$ ) arrays can acquire the pseudo differential signal on the input.

Figure 31. ADC Acquisition Phase

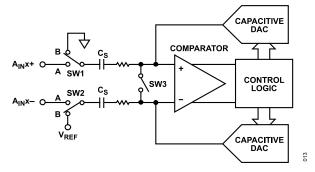

When the ADC starts a conversion (see Figure 32), SW3 opens and SW1 and SW2 move to Position B, causing the comparator to become unbalanced. Both inputs are disconnected when the conversion begins. The control logic and charge redistribution DACs are used to add and subtract fixed amounts of charge from the sampling capacitor arrays to bring the comparator back into a balanced condition. When the comparator is rebalanced, the conversion completes. The control logic generates the ADC output code. The output impedances of the sources driving the A<sub>IN</sub>x+ and A<sub>IN</sub>x- pins must be matched. Otherwise, the two inputs have different settling times, which results in errors.

Figure 32. ADC Conversion Phase

### ANALOG INPUT STRUCTURE

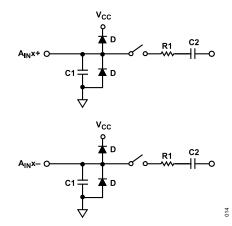

Figure 33 shows the equivalent analog input circuit of the AD4682 and the AD4683. The four diodes (D) provide ESD protection for the analog inputs. Ensure that the analog input signals do not exceed the supply rails by more than 300 mV. Exceeding the limit causes these diodes to become forward-biased and start conducting into the substrate. These diodes can conduct up to 10 mA without causing irreversible damage to the devices.

The C1 capacitors in Figure 33 are typically 3 pF and can primarily be attributed to pin capacitance. The R1 resistors are lumped components made up of the on resistance of the switches. The value of these resistors is typically about 200  $\Omega$ . The C2 capacitors are sampling capacitors of the ADC with a capacitance of 15 pF typically.

Figure 33. Equivalent Analog Input Circuit, Conversion Phase—Switches Open, Track Phase—Switches Closed

### THEORY OF OPERATION

### ADC TRANSFER FUNCTION

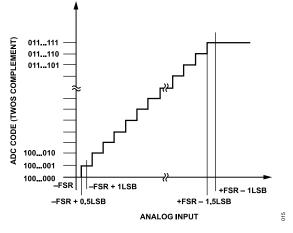

The AD4682 and the AD4683 can use a typical 2.5 V to 3.3 V V<sub>REF</sub>. The AD4682 and the AD4683 convert the differential voltage of the analog inputs (A<sub>IN</sub>A+, A<sub>IN</sub>A–, A<sub>IN</sub>B+, and A<sub>IN</sub>B–) into a digital output.

The conversion result is MSB first, twos complement. The LSB size is  $V_{REF}/2^N$ , where N is the ADC resolution. The ADC resolution is determined by the resolution of the device chosen, and if resolution boost mode is enabled. Table 8 outlines the LSB size expressed in  $\mu V$  for different resolutions and reference voltage options.

The ideal transfer characteristics for the AD4682 and the AD4683 are shown in Figure 34.

Figure 34. ADC Ideal Transfer Function (FSR = Full-Scale Range)

| Table 8 | . LSB Size |

|---------|------------|

|---------|------------|

| Resolution (Bits) | 2.5 V Reference (µV) | 3.3 V Reference (µV) |

|-------------------|----------------------|----------------------|

| 16                | 38.1                 | 50.3                 |

| 18                | 9.5                  | 12.6                 |

### **APPLICATIONS INFORMATION**

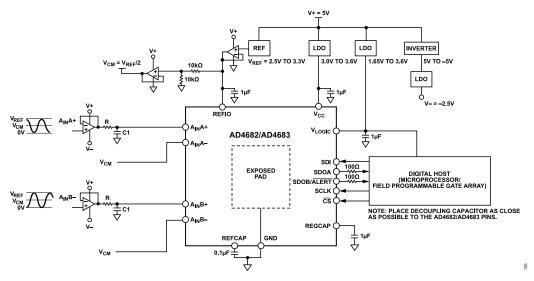

Figure 35 shows an example of the typical connection diagram for the AD4682 and the AD4683. Decouple the  $V_{CC}$ ,  $V_{LOGIC}$ , REGCAP, and REFIO pins with suitable decoupling capacitors as shown in Figure 35.

The exposed pad is a ground reference point for circuitry on the devices and must be connected to the PCB ground.

Place a differential RC filter on the analog inputs to ensure optimal performance is achieved.

The performance of the AD4682 and the AD4683 devices can be impacted by noise on the digital interface. This impact is dependent on the on-board layout and design. Keep a minimal distance between the digital line to the digital interface, or place a 100  $\Omega$  resistor in series and close to the SDOA pin and the SDOB/ALERT pin to reduce noise from the digital interface coupling of the AD4682 and the AD4683.

The two pseudo differential ADC channels of the AD4682 and the AD4683 can accept an input voltage range from 0 V to  $V_{REF}$  on  $A_{IN}A+$  and  $A_{IN}B+$ , and a  $V_{REF}/2$  voltage on  $A_{IN}A-$  and  $A_{IN}B-$ . The  $A_{IN}A+$ ,  $A_{IN}B+$ ,  $A_{IN}A-$ , and  $A_{IN}B-$  analog input pins can be driven with an amplifier. Table 9 lists the recommended driver amplifiers that best fit and add value to the application. The AD4682 and the AD4683 have a buffered internal 2.5 V reference that is accessed via the REFIO pin. The buffered internal 2.5 V reference must use an external buffer, like the ADA4807-2, when connecting the reference to the external circuitry. The AD4682 and the AD4683 have an option to use an ultralow noise, high accuracy voltage reference as an external voltage source ranging from 2.5 V to 3.3 V, such as the ADR4533 and ADR4525.

### **POWER SUPPLY**

The typical application circuit in Figure 35 can be powered by a single 5 V voltage source (V+) that supplies the entire signal chain. The 5 V supply can come from a low noise, CMOS low dropout (LDO) regulator (ADP7105). The driver amplifier supply is supplied by the +5 V (V+) and -2.5 V negative supply rail (V-), which is derived from the inverter (ADM660). The inverter converts the +5 V to -5 V and supplies the voltage to the ADP7182 low noise voltage regulator to output the -2.5 V.

The two independent supplies of the AD4682 and the AD4683, V<sub>CC</sub> and V<sub>LOGIC</sub>, that supply the analog circuitry and digital interface, respectively, can be supplied by a low quiescent current LDO regulator, such as the ADP166. The ADP166 is a suitable supply with a fixed output voltage range from 1.2 V to 3.3 V for typical V<sub>CC</sub> and V<sub>LOGIC</sub> levels. Decouple both the V<sub>CC</sub> supply and the V<sub>LOGIC</sub> supply separately with a 1  $\mu$ F capacitor that is placed close to the AD4682/AD4683 and connected using short and wide traces to provide low impedance paths and reduce the glitches in the power supply lines. Additionally, an internal LDO regulator supplies the AD4682 and the AD4683. The on-chip regulator provides a 1.9 V supply for internal use on the device only. Decouple the REGCAP pin with a 1  $\mu$ F capacitor to GND with short and wide traces and place the capacitor close to the AD4682/AD4683 REGCAP and GND pins.

### Power-Up

The AD4682 and the AD4683 are not easily damaged by power supply sequencing.  $V_{CC}$  and  $V_{LOGIC}$  can be applied in any sequence. Apply an external reference after  $V_{CC}$  and  $V_{LOGIC}$  are applied.

The AD4682/AD4683 require a  $t_{POWERUP}$  time from applying V<sub>CC</sub> and V<sub>LOGIC</sub> until the ADC conversion results are stable. Figure 4 shows the recommended power-up timing and condition with  $\overline{CS}$  held high. It is recommended and a good practice to perform a software reset after power-up. See the Software Reset section for details.

| Companion Parts    | Part Name | Description                                                                   | Typical Application                                |

|--------------------|-----------|-------------------------------------------------------------------------------|----------------------------------------------------|

| ADC Driver         | ADA4896-2 | 1 nV/√Hz, rail-to-rail output amplifier                                       | Precision, low noise, high frequency               |

|                    | ADA4940-2 | Ultra low power, full differential, low distortion                            | Precision, low density, low power                  |

|                    | ADA4807-2 | 1 mA, rail-to-rail output amplifier                                           | Precision, low power, high frequency               |

|                    | LTC6227   | 1 nV/√Hz, 420 MHz gain bandwidth product (GBW), rail-to-rail output amplifier | Precision, low noise, high frequency               |

| External Reference | ADR4525   | Ultralow noise, high accuracy 2.5 V voltage reference                         | 2.5 V reference voltage                            |

|                    | ADR4533   | Ultralow noise, high accuracy 3.3 V voltage reference                         | 3.3 V reference voltage                            |

| LDO                | ADP166    | Very low quiescent, 150 mA, LDO regulator                                     | 3.0 V to 3.6 V supply for $V_{CC}$ and $V_{LOGIC}$ |

#### Table 9. Signal Chain Components

### **APPLICATIONS INFORMATION**

Figure 35. Typical Application Circuit

### **MODES OF OPERATION**

The AD4682 and the AD4683 have several on-chip configuration registers for controlling the operational mode of the device.

Multifunction pin names may be referenced by their relevant function only.

### OVERSAMPLING

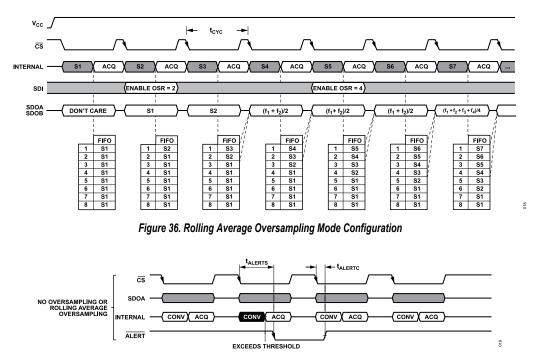

Oversampling is a common method used in analog electronics to improve the accuracy of the ADC result. Multiple samples of the analog input are captured and averaged to reduce the noise component from the quantization noise and the thermal noise (kTC) of the ADC. The AD4682 and the AD4683 offer an oversampling function on chip, rolling average oversampling.

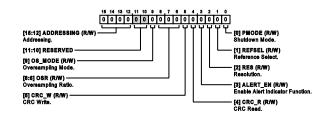

The rolling average oversampling functionality is enabled by writing a 1 on the OS\_MODE bit, Bit 9, and a valid nonzero value on the OSR bits, Bits[8:6], in the CONFIGURATION1 register. Oversampling is disabled by writing a 0 on the OS\_MODE bit, Bit 9, and a zero value on the OSR bits, Bits[8:6], of the CONFIGURATION1 register.

### **Rolling Average Oversampling**

Rolling average oversampling mode can be used in applications where higher output data rates are required and where higher SNR or dynamic range is required. Rolling average oversampling involves taking a number of samples, adding the samples together, and dividing the result by the number of samples taken. This result is then output from the AD4682 or the AD4683. The sample data is not cleared after the process completes. The rolling average oversampling mode uses a first in, first out (FIFO) buffer of the most recent samples in the averaging calculation, allowing the ADC throughput rate and output data rate to stay the same.

Rolling average oversampling mode is enabled by setting the OS\_MODE bit to Logic 1 and having a valid nonzero value in

#### Table 10. AD4682 Rolling Average Oversampling Performance Overview

the OSR bits. The oversampling ratio of the digital filter is controlled using the oversampling bits, OSR (see Table 10). The output result is decimated to 16-bit resolution for the AD4682 and the AD4683. If additional resolution is required, configure the resolution boost bit in the CONFIGURATION1 register. See the Resolution Boost section for further details.

In rolling average oversampling mode, all ADC conversions are controlled and initiated by the falling edge of  $\overline{CS}$ . After a conversion is complete, the result is loaded into the FIFO. The FIFO length is 8, regardless of the oversampling ratio set. The FIFO is filled on the first conversion after a power-on reset, the first conversion after a software controlled hard or soft reset, or the first conversion after the REFSEL bit is toggled. A new conversion result is shifted into the FIFO on completion of every ADC conversion, regardless of the status of the OSR bits and the OS\_MODE bit. This conversion allows a seamless transition from no oversampling to rolling average oversampling or different rolling average oversampling ratios without waiting for the FIFO to fill.

The number of samples, n, defined by the OSR bits are taken from the FIFO, added together, and the result is divided by n. The time between  $\overline{CS}$  falling edges is the cycle time, which can be controlled by the user, depending on the required data output rate.

### **RESOLUTION BOOST**

The default conversion result output data size for the AD4682 and the AD4683 is 16 bits. When the on-chip oversampling function is enabled, the performance of the ADC can exceed the 16-bit level. To accommodate the performance boost achievable, it is possible to enable an additional two bits of resolution. If the RES bit in the CONFIGURATION1 register is set to Logic 1, and the AD4682 and the AD4683 are in a valid oversampling mode, the conversion result size for the AD4682 and the AD4683 is 18 bits. In this mode, 18 SCLKs are required to propagate the data.

|                |                           |                  | SNR (c    | IB Typical)      |         |                                 |

|----------------|---------------------------|------------------|-----------|------------------|---------|---------------------------------|

|                |                           | V <sub>REF</sub> | = = 2.5 V | V <sub>REI</sub> | = 3.3 V |                                 |

| OSR, Bits[8:6] | <b>Oversampling Ratio</b> | RES = 0          | RES = 1   | RES = 0          | RES = 1 | Output Data Rate (kSPS Maximum) |

| 000            | Disabled                  | 85.7             | 85.7      | 87.3             | 87.3    | 1000                            |

| 001            | 2                         | 87.6             | 87.9      | 88.8             | 89.3    | 1000                            |

| 010            | 4                         | 90.1             | 90.9      | 91.3             | 92.4    | 1000                            |

| 011            | 8                         | 92.6             | 94.0      | 93.4             | 95.4    | 1000                            |

### **MODES OF OPERATION**

Figure 37. Alert Operation

### ALERT

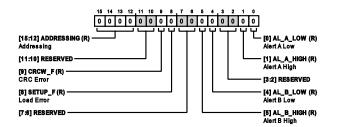

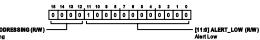

The alert functionality is an out of range indicator and can be used as an early indicator of an out of bounds conversion result. An alert event triggers when the conversion result value register exceeds the alert high limit value in the ALERT\_HIGH\_ THRESHOLD register or falls below the alert low limit value in the ALERT\_LOW\_THRESHOLD register. The ALERT\_HIGH\_ THRESHOLD register and ALERT\_LOW\_THRESHOLD register are common to all ADCs. When setting the threshold limits, the alert high threshold must always be greater than the alert low threshold. Detailed alert information is accessible in the ALERT register.

The ALERT register contains two status bits per ADC, one corresponding to the high limit, and the other to the low limit. A logical OR of alert signals for all ADCs creates a common alert value. This value can be configured to drive out on the ALERT function of the SDOB/ALERT pin. The SDOB/ALERT pin is configured as ALERT by configuring the following bits in the CONFIGURATION1 and CONFIGURATION2 registers:

- ▶ Set the SDO bit to 1.

- ▶ Set the ALERT\_EN bit to 1.

- Set a valid value to the ALERT\_HIGH\_THRESHOLD register and the ALERT\_LOW\_THRESHOLD register.

The alert indication function is available in rolling average oversampling and nonoversampling modes.

The ALERT function of the SDOB/ALERT pin is updated at the end of the conversion. The alert indication status bits in the ALERT register are updated as well and must be read before the end of

the next conversion. The  $\overline{\text{ALERT}}$  function of the SDOB/ $\overline{\text{ALERT}}$  pin is cleared with a falling edge of  $\overline{\text{CS}}$ . Issuing a software reset also clears the alert status in the  $\overline{\text{ALERT}}$  register.

### **POWER MODES**

The AD4682 and the AD4683 have two power modes, normal and shutdown. These modes of operation provide flexible power management options, allowing optimization of the power dissipation and throughput rate ratio for different application requirements.

Program the PMODE bit in the CONFIGURATION1 register to configure the power modes in the AD4682 and the AD4683. Set the PMODE bit to Logic 0 for normal mode and Logic 1 for shutdown mode.

### Normal Mode

Keep the AD4682 and the AD4683 in normal mode to achieve the fastest throughput rate. All blocks within the AD4682 and the AD4683 remain fully powered at all times, and an ADC conversion can be initiated by a falling edge of  $\overline{CS}$ , when required. When the AD4682 and the AD4683 are not converting, the devices are in static mode and power consumption is automatically reduced. Additional current is required to perform a conversion. Therefore, power consumption on the AD4682 and the AD4683 scales with throughput.

### **MODES OF OPERATION**

### Shutdown Mode

When slower throughput rates and lower power consumption are required, use shutdown mode by either powering down the ADC between each conversion, or by performing a series of conversions at a high throughput rate and then powering down the ADC for a relatively long duration between these burst conversions. When the AD4682 and the AD4683 are in shutdown mode, all analog circuitry powers down, including the internal reference, if enabled. The SPI remains active during shutdown mode to allow the AD4682 and the AD4683 to exit shutdown mode.

To enter shutdown mode, write to the PMODE bit in the CONFIGU-RATION1 register. The AD4682 and the AD4683 shut down, and current consumption reduces.

To exit shutdown mode and return to normal mode, set the PMODE bit in the CONFIGURATION1 register to Logic 0. All register configuration settings remain unchanged entering or exiting shutdown mode. After exiting shutdown mode, allow sufficient time for the circuitry to turn on before starting a conversion. If the internal reference is enabled, allow the reference to settle for accurate conversions to happen.

### INTERNAL AND EXTERNAL REFERENCE

The AD4682 and the AD4683 have a buffered 2.5 V internal reference primarily used as a reference voltage for device operation. When using the buffered internal 2.5 V reference externally via the REFIO pin, the reference must use an external buffer before connecting to the external circuitry. Alternatively, if a more accurate reference or higher dynamic range is required, an external reference can be supplied. An externally supplied reference voltage can range from 2.5 V to 3.3 V.

Reference selection, internal or external, is configured by the RE-FSEL bit in the CONFIGURATION1 register. If the REFSEL bit is set to 0, the internal reference buffer is enabled. If the REFSEL bit

Figure 39. Shutdown Mode Operation

is set to 1, the internal reference buffer is disabled. If an external reference is preferred, set the REFSEL bit to 1 and supply an external reference to the REFIO pin.

### SOFTWARE RESET

The AD4682 and the AD4683 have two reset modes, a soft reset and a hard reset. To initiate a reset, write to the reset bits, Bits[7:0], in the CONFIGURATION2 register.

A soft reset maintains the contents of the configurable registers but refreshes the interface and the ADC blocks. Any internal state machines are reinitialized, and the oversampling block and FIFO are flushed. The ALERT register is then cleared. The reference and LDO regulator remain powered.

A hard reset, in addition to the blocks reset by a soft reset, resets all user registers to default status, resets the reference buffer, and resets the internal oscillator block.

Figure 38. Software Reset Operation

### DIAGNOSTIC SELF TEST

The AD4682 and the AD4683 run a diagnostic self test after a power-on reset (POR) or after a software hard reset to ensure the proper configuration is loaded into the device.

The result of the self test is displayed in the SETUP\_F bit in the ALERT register. If the SETUP\_F bit is set to Logic 1, the diagnostic self test fails. If the self test fails, perform a software hard reset to reset the AD4682 and the AD4683 registers to the default status.

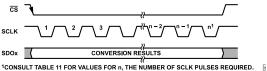

The interface to the AD4682 and the AD4683 is via an SPI. The interface consists of the  $\overline{CS}$ , SCLK, SDOA, SDOB/ALERT, and SDI pins. Multifunction pin names may be referenced by their relevant function only.

The  $\overline{CS}$  signal frames a serial data transfer and initiates an ADC conversion process. The falling edge of  $\overline{CS}$  puts the track-and-hold into hold mode, at which point the analog input is sampled, and the bus is taken out of three-state.

The SCLK signal synchronizes data in and out of the devices via the SDOA, SDOB, and SDI signals. A minimum of 16 SCLKs are required for a write to or read from a register. The minimum number of SCLKs for a conversion read is dependent on the resolution of the devices and the configuration settings (see Table 11).

The ADC conversion operation is driven internally by an on-board oscillator and is independent of the SCLK signal.

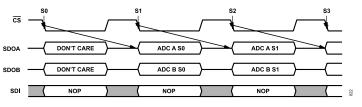

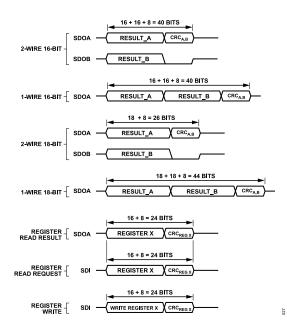

The AD4682 and the AD4683 have two serial output signals, SDOA and SDOB. To achieve the highest throughput of the devices, use both SDOA and SDOB, 2-wire mode, to read conversion results. If a reduced throughput is required or oversampling is used, it is possible to use 1-wire mode, SDOA signal only, for reading conversion results. Programming the SDO bit in the CONFIGURATION2 register configures 2-wire mode or 1-wire mode.

Configuring a cyclic redundancy check (CRC) operation for SPI reads or SPI writes alters the operation of the interface. Consult the relevant CRC Read, CRC Write, and CRC Polynomial sections to ensure proper operation.

### **READING CONVERSION RESULTS**

The  $\overline{CS}$  signal initiates the conversion process. A high to low transition on the  $\overline{CS}$  signal initiates a simultaneous conversion of both ADCs, ADC A and ADC B. The AD4682 and the AD4683 have a one-cycle readback latency. Therefore, the conversion results are

available on the next SPI access. Take the  $\overline{CS}$  signal low, and the conversion result clocks out on the serial output pins. The next conversion also initiates at this point.

The conversion result shifts out of the device as a 16-bit result for the AD4682 and the AD4683. The MSB of the conversion result shifts out on the  $\overline{CS}$  falling edge. The remaining data shifts out of the device under the control of the SCLK input. The data shifts out on the rising edge of the SCLK, and the data bits are valid on both the falling edge and the rising edge. After the final SCLK falling edge, take  $\overline{CS}$  high again to return the SDOA and SDOB/ALERT pins to a high impedance state.

The number of SCLK cycles to propagate the conversion results on the SDOA and SDOB/ALERT pins is dependent on the serial mode of operation configured and if resolution boost mode is enabled (see Figure 40 and Table 11 for details). If CRC reading is enabled, this reading requires additional SCLK pulses to propagate the CRC information (see the CRC section for more details).

As the  $\overline{\text{CS}}$  signal initiates a conversion and frames the data, any data access must be completed within a single frame.

| Table 11. Number of SCLK Cycles, n, Required for Reading Conversion |

|---------------------------------------------------------------------|

| Results                                                             |

| Interface     | Resolution Boost |          |             |

|---------------|------------------|----------|-------------|

| Configuration | Mode             | CRC Read | SCLK Cycles |

| 2-Wire        | Disabled         | Disabled | 16          |

|               |                  | Enabled  | 24          |

|               | Enabled          | Disabled | 18          |

|               |                  | Enabled  | 26          |

| 1-Wire        | Disabled         | Disabled | 32          |

|               |                  | Enabled  | 40          |

|               | Enabled          | Disabled | 36          |

|               |                  | Enabled  | 44          |

TABLE 11 FOR VALUES FOR n, THE NUMBER OF SCLK PULSES REQUIRE

Figure 40. Reading Conversion Results

### Serial 2-Wire Mode

Configure 2-wire mode by setting the SDO bit in the CONFIGURA-TION1 register to 0. In 2-wire mode, the conversion result for ADC A is output on the SDOA pin, and the conversion result for ADC B is output on the SDOB/ALERT pin (see Figure 41).

### Serial 1-Wire Mode

In applications where slower throughput rates are allowed, the SPI can be configured to operate in 1-wire mode. In 1-wire mode, the conversion results from ADC A and ADC B are output on the serial output, SDOA. Additional SCLK cycles are required to propagate all

of the data. The ADC A data is output first, followed by the ADC B conversion results (see Figure 42).

### LOW LATENCY READBACK

The interface on the AD4682 and the AD4683 has a one cycle latency, as shown in Figure 43. For applications that operate at lower throughput rates, the latency of reading the conversion result can be reduced. When the conversion time elapses, a second  $\overline{CS}$  pulse after the initial  $\overline{CS}$  pulse that initiates the conversion can readback the conversion result. This operation is shown in Figure 43.

Figure 41. Reading Conversion Results: 2-Wire Mode

Figure 42. Reading Conversion Results: 1-Wire Mode

Figure 43. Low Throughput Low Latency

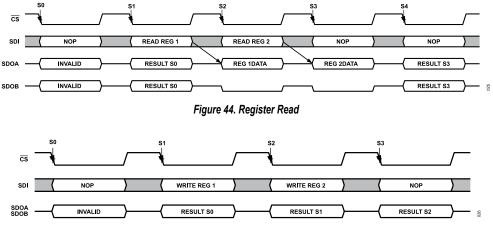

### **READING FROM DEVICE REGISTERS**

All of the registers in the AD4682 and the AD4683 can be read over the SPI. To perform a register read, issue a register read command followed by an additional SPI command that can be either a valid command or a no operation (NOP) command. The format for a read command is shown in Table 14. Set Bit D15 to 0 to select a read command. Bits[D14:D12] contain the register address, and the subsequent 12 bits, Bits[D11:D0], are ignored.

### WRITING TO DEVICE REGISTERS

All of the read and write registers in the AD4682 and the AD4683 can be written to over the SPI. The length of an SPI write access is determined by the CRC write function. An SPI access is 16 bits if CRC write is disabled and 24 bits when CRC write is enabled. The format for a write command is shown in Table 14. Set Bit D15 to 1 to select a write command. Bits[D14:D12] contain the register address, and the subsequent 12 bits, Bits[D11:D0], contain the data to be written to the selected register.

Figure 45. Register Write

### CRC

The AD4682 and the AD4683 have CRC checksum modes that can improve interface robustness by detecting errors in data transmissions. The CRC feature is independently selectable for SPI reads and SPI writes. For example, the CRC function for SPI writes can be enabled to prevent unexpected changes to the device configuration but disabled on SPI reads, therefore maintaining a higher throughput rate. The CRC feature is controlled by the programming of the CRC\_W bit and CRC\_R bits in the CONFIGURATION1 register.

### CRC Read