# 24-Bit, 2 MSPS/500 kSPS, Dual Channel SAR ADCs

#### **FEATURES**

- ▶ High performance

- ► Throughput: 2 MSPS (AD4630-24) or 500 kSPS (AD4632-24) per channel maximum

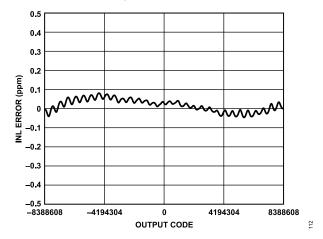

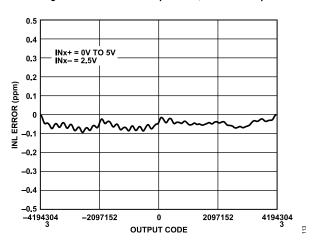

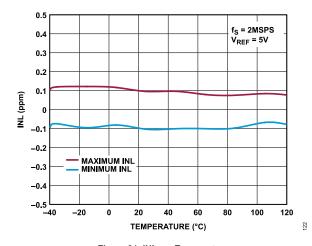

- ▶ INL: ±0.9 ppm maximum from -40°C to +125°C

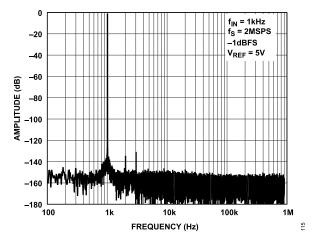

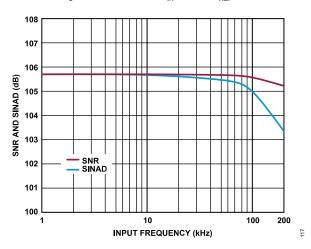

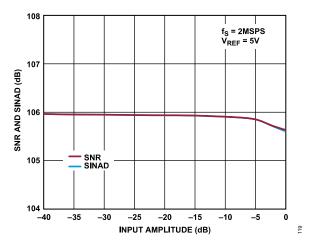

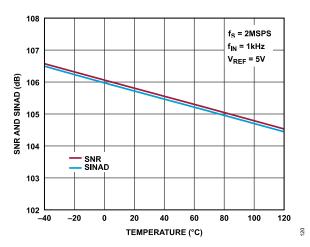

- ▶ SNR: 105.7 dB typical

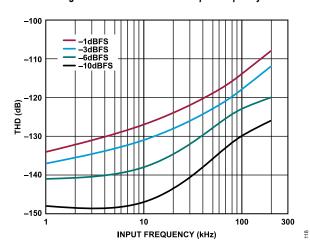

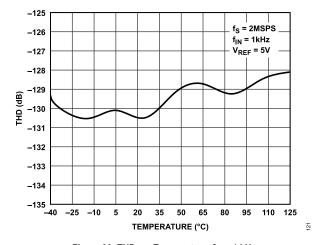

- ► THD: -127 dB typical

- ▶ NSD: -166 dBFS/Hz typical

- ▶ Low power

- ▶ 15 mW per channel at 2 MSPS

- ▶ 5 mW per channel at 500 kSPS

- ▶ 1.5 mW per channel at 10 kSPS

- ▶ Easy Drive features reduce system complexity

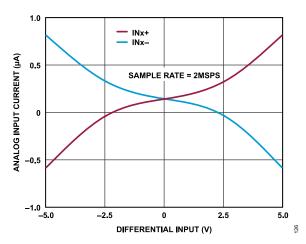

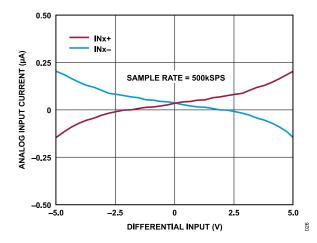

- ▶ Low 0.6 µA input current for dc inputs at 2 MSPS

- Wide input common-mode range: −(1/128) × V<sub>REF</sub> to +(129/128) × V<sub>REF</sub>

- ▶ Flexible external reference voltage range: 4.096 V to 5 V

- Accurate integrated reference buffer with 2 μF bypass capacitor

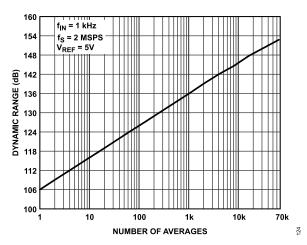

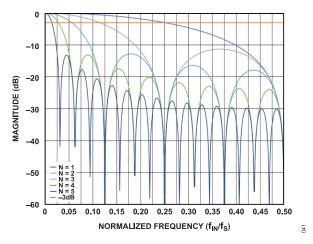

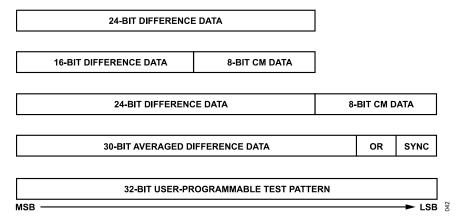

- ▶ Programmable block averaging filter with up to 2<sup>16</sup> decimation

- Extended sample resolution to 30 bits

- Overrange and synchronization bits

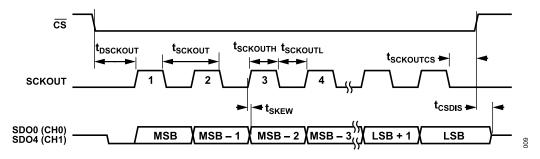

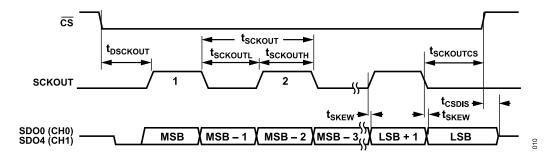

- ► Flexi-SPI digital interface

- ▶ 1, 2, or 4 SDO lanes per channel allows slower SCK

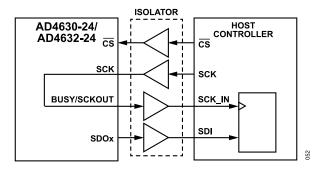

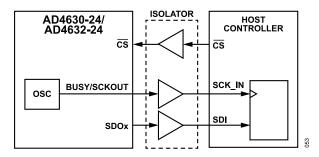

- ▶ Echo clock mode simplifies use of digital isolator

- ► Compatible with 1.2 V to 1.8 V logic

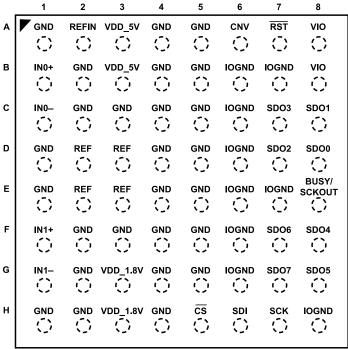

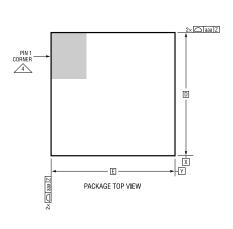

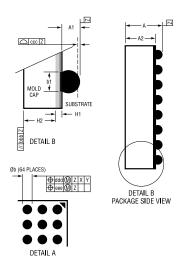

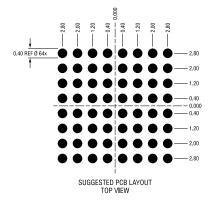

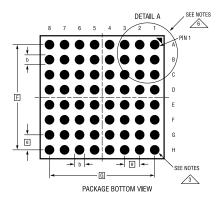

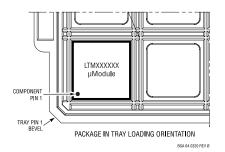

- ▶ 7 mm × 7 mm 64-Ball CSP\_BGA package with internal supply and reference capacitors to help reduce system footprint

# **APPLICATIONS**

- Automatic test equipment

- Digital control loops

- Medical instrumentation

- Seismology

- ▶ Semiconductor manufacturing

- Scientific instrumentation

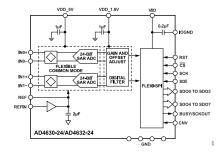

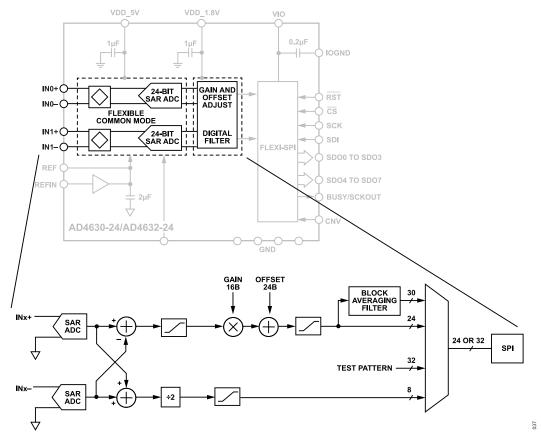

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

#### **GENERAL DESCRIPTION**

The AD4630-24/AD4632-24 are two-channel, simultaneous sampling, Easy Drive<sup>™</sup>, 2 MSPS or 500 kSPS successive approximation register (SAR) analog-to-digital converters (ADCs). With a guaranteed maximum ±0.9 ppm INL and no missing codes at 24 bits, the AD4630-24/AD4632-24 achieve unparalleled precision from −40°C to +125°C. Figure 1 shows the functional architecture of the AD4630-24/AD4632-24.

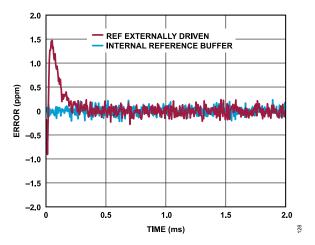

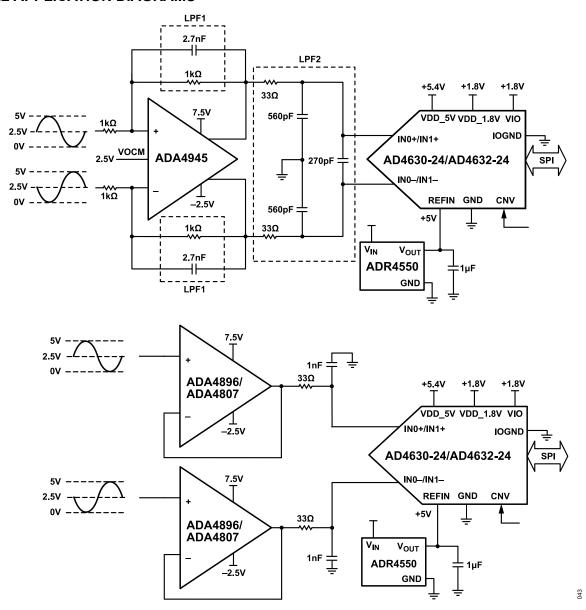

A low drift, internal precision reference buffer eases voltage reference sharing with other system circuitry. The AD4630-24/ AD4632-24 offer a typical dynamic range of 106 dB when using a 5 V reference. The low noise floor enables signal chains requiring less gain and lower power. A block averaging filter with programmable decimation ratio can increase dynamic range up to 153 dB. The wide differential input and common-mode ranges allow inputs to use the full voltage reference ( $\pm V_{REF}$ ) range without saturating, simplifying signal conditioning requirements and system calibration. The improved settling of the Easy Drive analog inputs broadens the selection of analog front-end components compatible with the AD4630-24/AD4632-24. Both single-ended and differential signals are supported.

The versatile Flexi-SPI serial peripheral interface (SPI) eases host processor and ADC integration. A wide data clocking window, multiple SDO lanes, and optional dual data rate (DDR) data clocking can reduce the serial clock to 10 MHz while operating at a sample rate of 2 MSPS or 500 kSPS. Echo clock mode and ADC host clock mode relax the timing requirements and simplify the use of digital isolators.

The 64-ball chip scale package ball grid array (CSP\_BGA) of the AD4630-24/AD4632-24 integrates all critical power supply and reference bypass capacitors, reducing the footprint and system component count, and lessening sensitivity to board layout.

# **TABLE OF CONTENTS**

| Features                                                                               | 1         | Layout Guidelines                  | 42 |

|----------------------------------------------------------------------------------------|-----------|------------------------------------|----|

| Applications                                                                           | 1         | Registers                          | 43 |

| Functional Block Diagram                                                               | 1         | Register Details                   |    |

| General Description                                                                    | 1         | Interface Configuration A Register | 44 |

| Specifications                                                                         |           | Interface Configuration B Register | 44 |

| Timing Specifications                                                                  | 6         | Device Configuration Register      |    |

| Absolute Maximum Ratings                                                               | 12        | Chip Type Register                 | 45 |

| Thermal Resistance                                                                     | 12        | Product ID Low Register            | 45 |

| Electrostatic Discharge (ESD) Ratings                                                  | 12        | Product ID High Register           | 46 |

| ESD Caution                                                                            |           | Chip Grade Register                | 46 |

| Pin Configuration and Function Descriptions                                            | 13        | Scratchpad Register                |    |

| Typical Performance Characteristics                                                    |           | SPI Revision Register              |    |

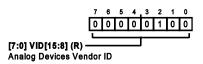

| Terminology                                                                            |           | Vendor ID Low Register             |    |

| Theory of Operation                                                                    | 21        | Vendor ID High Register            | 47 |

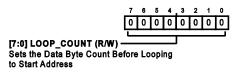

| Overview                                                                               |           | Stream Mode Register               |    |

| Converter Operation                                                                    |           | Interface Configuration C Register | 48 |

| Transfer Function                                                                      |           | Interface Status A Register        |    |

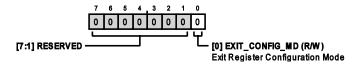

| Analog Features                                                                        |           | Exit Configuration Mode Register   |    |

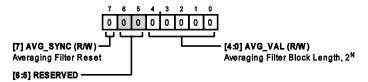

| Digital Sample Processing Features                                                     |           | Averaging Mode Register            |    |

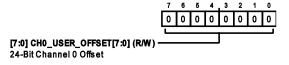

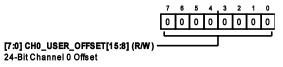

| Applications Information                                                               |           | Channel 0 Offset Registers         |    |

| Typical Application Diagrams                                                           |           | Channel 1 Offset Registers         |    |

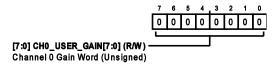

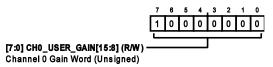

| Analog Front-End Design                                                                |           | Channel 0 Gain Registers           |    |

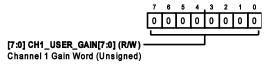

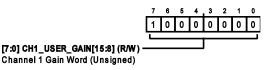

| Multiplexed Applications                                                               |           | Channel 1 Gain Registers           |    |

| Reference Circuitry Design                                                             |           | Modes Register                     | 52 |

| Device Reset                                                                           |           | Internal Oscillator Register       |    |

| Power Supplies                                                                         |           | Output Driver Register             |    |

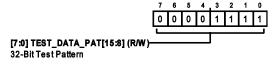

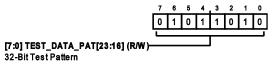

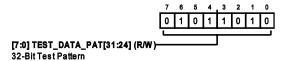

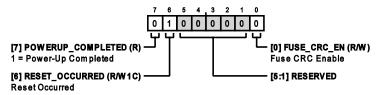

| Serial Interface                                                                       |           | Test Pattern Registers             |    |

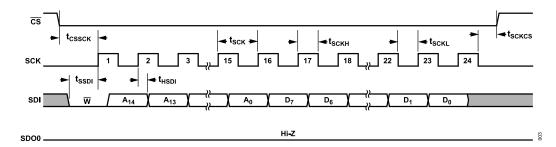

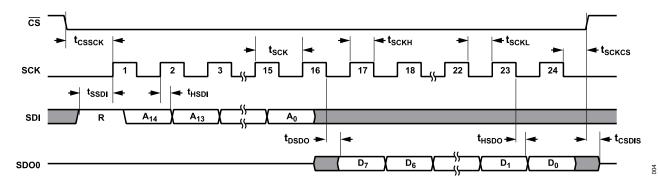

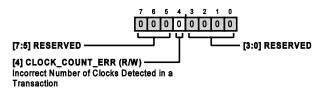

| SPI Signals                                                                            | 29        | Digital Diagnostics Register       |    |

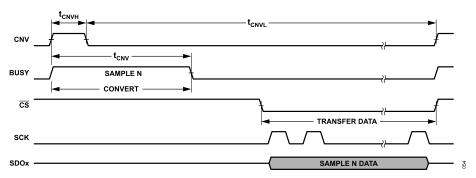

| Sample Conversion Timing and Data                                                      |           | Digital Errors Register            |    |

| Transfer                                                                               |           | Outline Dimensions                 |    |

| Clocking Modes                                                                         |           | Ordering Guide                     |    |

| Data Clocking Requirements and Timing                                                  | 36        | Evaluation Boards                  | 55 |

| REVISION HISTORY                                                                       |           |                                    |    |

| 5/2023—Rev. A to Rev. B                                                                | \ Cootion |                                    | 00 |

| Deleted Power Supply Rejection Ratio (PSRR)                                            | •         |                                    |    |

| Changes to Analog Features Section                                                     |           |                                    |    |

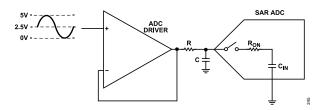

| Changes to Figure 44  Added Easy Drive Features Section                                |           |                                    |    |

| Added Precharge Buffer Section                                                         |           |                                    |    |

| Change to Long Acquisition Phase Section                                               |           |                                    |    |

| · · · · · · · · · · · · · · · · · · ·                                                  |           |                                    |    |

| Changes to Driver Amplifier Choice Section<br>Added Figure 45; Renumbered Sequentially |           |                                    |    |

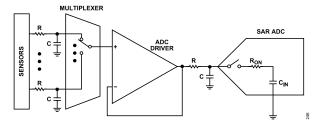

| Added Multiplexed Applications Section and Fi                                          |           |                                    |    |

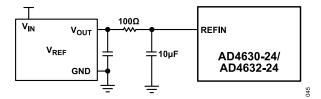

| Changes to Power Supplies Section                                                      | •         |                                    |    |

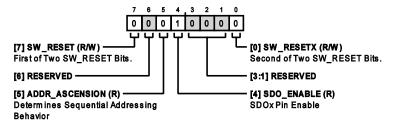

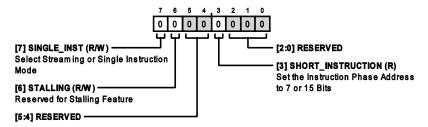

| Changes to Power Supplies Section  Changes to Register Access Mode Section             |           |                                    |    |

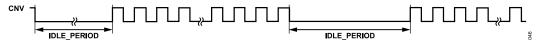

| Added Figure 52, Figure 53, and Figure 54                                              |           |                                    |    |

| Changes to Sample Conversion Timing and Da                                             |           |                                    |    |

| Shanges to Sample Conversion filling and De                                            | ata mans  | ioi ocouoii                        |    |

# **TABLE OF CONTENTS**

| Added Figure 57                                                                                 | 32 |

|-------------------------------------------------------------------------------------------------|----|

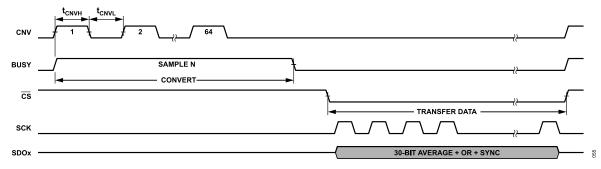

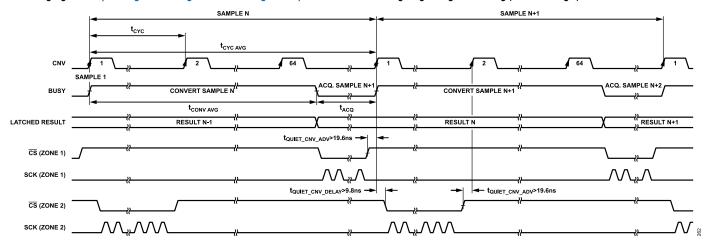

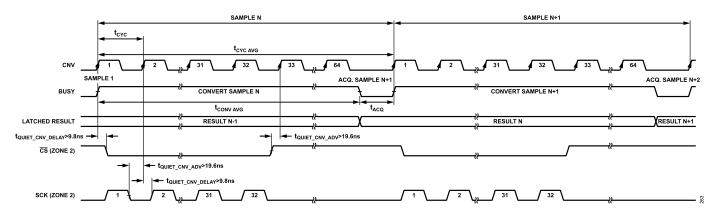

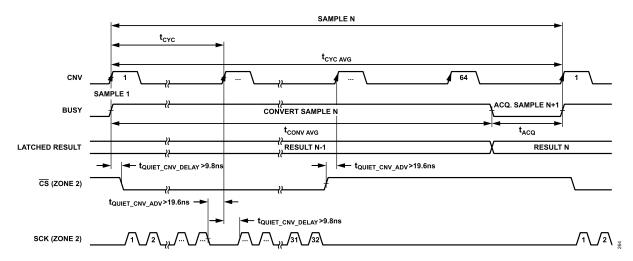

| Changes to Basic and Averaging Conversion Cycles Section                                        | 36 |

| Added Figure 63, Figure 64, and Figure 65                                                       |    |

|                                                                                                 |    |

| 7/2022—Rev. 0 to Rev. A                                                                         |    |

| Added AD4632-24                                                                                 |    |

| Changes to Features Section and General Description Section                                     | 1  |

| Changes to Table 1                                                                              | 4  |

| Changes to Table 2                                                                              | 6  |

| Changes to Table 7 Title, Figure 9 Title, and Figure 10 Title                                   | 10 |

| Change to Figure 25 Title                                                                       | 17 |

| Added Figure 26; Renumbered Sequentially                                                        | 17 |

| Change to Figure 30 Title and Figure 35 Title                                                   |    |

| Added Figure 31                                                                                 |    |

| Added Figure 36                                                                                 | 19 |

| Changes to Overview Section                                                                     | 21 |

| Changes to Converter Operation Section                                                          | 21 |

| Changes to Serial Interface Section, SPI Signals Section, and Table 13                          |    |

| Change to Sample Conversion Timing and Data Transfer Section                                    |    |

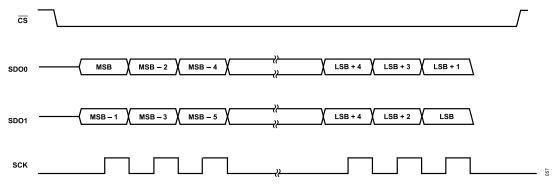

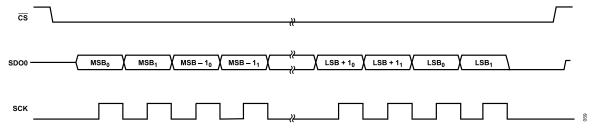

| Changes to Host Clock Mode Section, Figure 54 Title, Dual Data Rate Section, 1-Lane Output Data |    |

| Clocking Mode Section, and 2-Lane Output Data Clocking Mode Section                             | 34 |

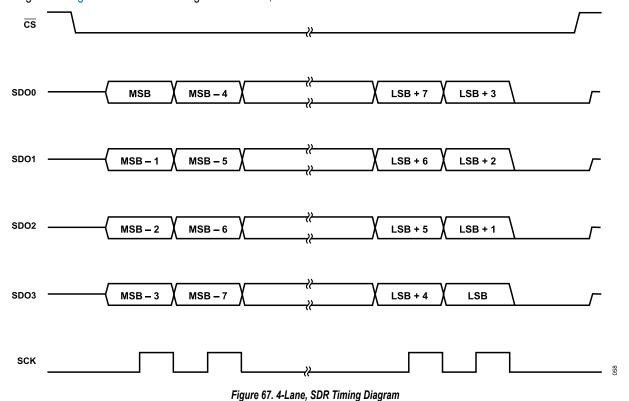

| Changes to 4-Lane Output Data Clocking Mode Section, Interleaved Lane Output Data Clocking Mode |    |

| Section, and Table 14.                                                                          |    |

| Change to Basic and Averaging Conversion Cycles Section                                         |    |

| Changes to Host Clock Mode Timing Section Title, 1-Lane, Host Clock Mode, SDR Section, and 1-   |    |

| Lane, Host Clock Mode, DDR Section                                                              | 41 |

| Change to Table 43                                                                              |    |

| Changes to Figure 60 and Figure 60 Title                                                        |    |

| Changes to Ordering Guide                                                                       |    |

| -·····aaaaa                                                                                     |    |

# 11/2021—Revision 0: Initial Version

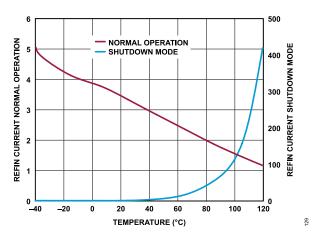

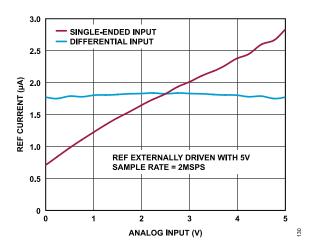

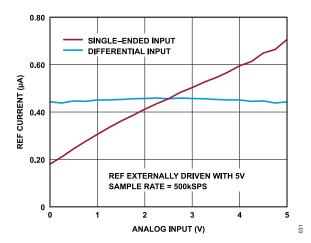

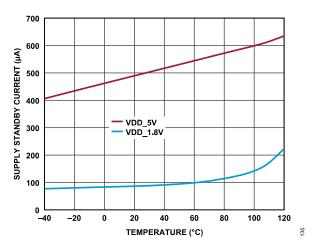

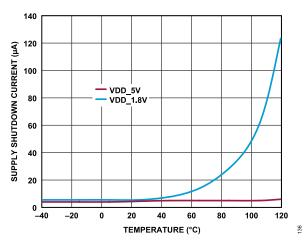

$VDD\_5V = 5.4 \text{ V}, VDD\_1.8V = 1.8 \text{ V}, VIO = 1.8 \text{ V}, REFIN = 5 \text{ V}, input common mode} = 2.5 \text{ V}, sampling frequency (f_S) = 2 \text{ MSPS} and 500 \text{ kSPS} for the AD4630-24/AD4632-24, and all specifications } T_{MIN} \text{ to } T_{MAX}, unless otherwise noted. Typical values are at } T_A = 25^{\circ}C.$

Table 1. Specifications

| Parameter                                    | Test Conditions/Comments                                              | Min                         | Тур           | Max                           | Unit        |

|----------------------------------------------|-----------------------------------------------------------------------|-----------------------------|---------------|-------------------------------|-------------|

| RESOLUTION                                   |                                                                       | 24                          |               |                               | Bits        |

| ANALOG INPUT                                 |                                                                       |                             |               |                               |             |

| Voltage Range                                | INx+ voltage (V <sub>INx+</sub> ) - INx- voltage (V <sub>INx-</sub> ) | -(65/64) × V <sub>REF</sub> |               | $+(65/64) \times V_{REF}$     | V           |

| Absolute Input Voltage                       | V <sub>INx+</sub> , V <sub>INx-</sub> to GND                          | -(1/128) × V <sub>REF</sub> |               | +(129/128) × V <sub>REF</sub> | V           |

| Common-Mode Input Range                      | $(V_{INX+} + V_{INX-})/2$                                             | -(1/128) × V <sub>REF</sub> |               | +(129/128) × V <sub>REF</sub> | V           |

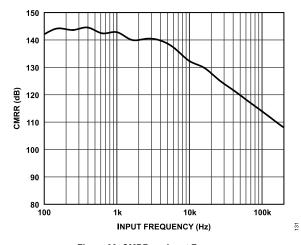

| Common-Mode Rejection Ratio (CMRR)           | Input frequency (f <sub>IN</sub> ) = 10 kHz                           |                             | 132           |                               | dB          |

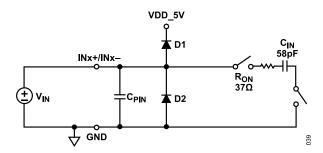

| Analog Input Current                         | Acquisition phase, T <sub>A</sub> = 25°C                              |                             | 0.4           |                               | nA          |

|                                              | Converting any dc input at 2 MSPS                                     |                             | 0.6           |                               | μA          |

| Analog Input Capacitance (C <sub>IN</sub> )  | Acquisition phase                                                     |                             | 60            |                               | pF          |

|                                              | Outside acquisition phase (pin capacitance (C <sub>PIN</sub> ))       |                             | 2             |                               | pF          |

| THROUGHPUT                                   |                                                                       |                             |               |                               |             |

| Complete Cycle                               |                                                                       |                             |               |                               |             |

| AD4630-24                                    |                                                                       | 500                         |               |                               | ns          |

| AD4632-24                                    |                                                                       | 2000                        |               |                               | ns          |

| Conversion Time                              |                                                                       | 264                         | 282           | 300                           | ns          |

| Acquisition Phase <sup>1</sup>               |                                                                       |                             |               |                               |             |

| AD4630-24                                    |                                                                       | 244                         | 260           | 275                           | ns          |

| AD4632-24                                    |                                                                       | 1744                        | 1760          | 1775                          | ns          |

| Throughput Rate                              |                                                                       |                             |               |                               |             |

| AD4630-24                                    |                                                                       | 0                           |               | 2                             | MSPS        |

| AD4632-24                                    |                                                                       | 0                           |               | 500                           | kSPS        |

| DC ACCURACY                                  |                                                                       |                             |               |                               |             |

| No Missing Codes                             |                                                                       | 24                          |               |                               | Bits        |

| Integral Nonlinearity (INL) Error            |                                                                       | -0.9                        | ±0.1          | +0.9                          | ppm         |

| Differential Nonlinearity (DNL) Error        |                                                                       |                             | ±0.5          |                               | LSB         |

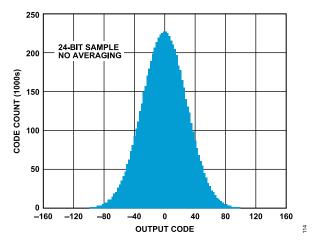

| Transition Noise                             |                                                                       |                             |               |                               | LSB         |

|                                              |                                                                       |                             | 29.7          |                               | rms         |

| Zero Error                                   |                                                                       | -90                         | 0             | +90                           | μV          |

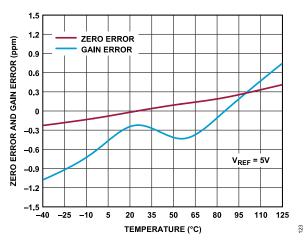

| Zero Error Drift                             |                                                                       |                             | ±0.007        |                               | ppm/°       |

| Gain Error                                   | Buffer disabled, REF = 5 V                                            | -0.004                      | ±0.0002       | +0.004                        | %FS         |

|                                              | Buffer enabled, REFIN = 5 V                                           | -0.008                      | ±0.0006       | +0.008                        | %FS         |

| Gain Error Temperature Drift                 | Buffer disabled, REF = 5 V                                            |                             | ±0.025        |                               | ppm/°       |

|                                              | Buffer enabled, REFIN = 5 V                                           |                             | ±0.07         |                               | ppm/°       |

| Power Supply Sensitivity                     | $VDD_5V = 5.4 V \pm 0.1 V$                                            |                             | ±0.1          |                               | ppm         |

|                                              | VDD_1.8V = 1.8 V ± 5%                                                 |                             | ±0.2          |                               | ppm         |

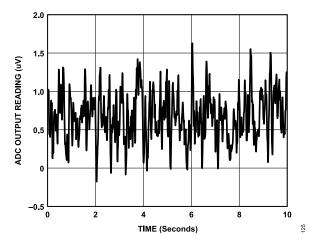

| Low Frequency Noise <sup>2</sup>             | Bandwidth = 0.1 Hz to 10 Hz                                           |                             | 1.8           |                               | μV p-p      |

| AC ACCURACY                                  |                                                                       |                             |               |                               |             |

| Dynamic Range                                |                                                                       |                             | 106           |                               | dB          |

| Noise Spectral Density (NSD)                 |                                                                       |                             | -166          |                               | dBFS/       |

| Total RMS Noise                              |                                                                       |                             | 17.7          |                               | Z           |

|                                              | f = 1 kHz =0.5 dBES                                                   | 103.3                       | 17.7<br>105.7 |                               | μV rm<br>dB |

| Signal to Noise Ratio (SNR)                  | f <sub>IN</sub> = 1 kHz, -0.5 dBFS                                    | 103.3                       | 105.7         |                               | dВ          |

| Spurious-Free Dynamic Range (SFDR)           | f <sub>IN</sub> = 1 kHz, -0.5 dBFS                                    |                             |               | _115                          |             |

| Total Harmonic Distortion (THD)              | f <sub>IN</sub> = 1 kHz, -0.5 dBFS                                    | 102.2                       | -127          | -115                          | dB          |

| Signal-to-Noise-and-Distortion (SINAD) Ratio | f <sub>IN</sub> = 1 kHz, -0.5 dBFS                                    | 103.3                       | 105.7         |                               | dB          |

| Oversampled Dynamic Range                    | Averaging = 2                                                         |                             | 109           |                               | dB          |

analog.com Rev. B | 4 of 55

Table 1. Specifications (Continued)

| Parameter                                             | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min                                                       | Тур     | Max          | Unit   |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------|--------------|--------|

|                                                       | Averaging = 256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | 130     |              | dB     |

|                                                       | Averaging = 65536                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                           | 152.7   |              | dB     |

| SNR                                                   | $VDD_{5V} = 5.0 \text{ V}, f_{IN} = 1 \text{ kHz}, -0.5 \text{ dBFS}, REFIN = 4.096 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                           | 104     |              | dB     |

| SFDR                                                  | VDD_5V = 5.0 V, f <sub>IN</sub> = 1 kHz, -0.5 dBFS, REFIN = 4.096 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           | 130     |              | dB     |

| THD                                                   | VDD_5V = 5.0 V, f <sub>IN</sub> = 1 kHz, -0.5 dBFS, REFIN = 4.096 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           | -130    |              | dB     |

| SINAD                                                 | VDD_5V = 5.0 V, f <sub>IN</sub> = 1 kHz, -0.5 dBFS, REFIN = 4.096 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                           | 104     |              | dB     |

| SNR                                                   | $f_{IN} = 100 \text{ kHz}, -0.5 \text{ dBFS}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                           | 105.6   |              | dB     |

| THD                                                   | f <sub>IN</sub> = 100 kHz, -0.5 dBFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | -113    |              | dB     |

| SINAD                                                 | f <sub>IN</sub> = 100 kHz, -0.5 dBFS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 104.9   |              | dB     |

| -3 dB Input Bandwidth                                 | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                           | 74      |              | MHz    |

| Aperture Delay                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | 0.7     |              | ns     |

| Aperture Jitter                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | 1.4     |              | ps rms |

| CHANNEL-TO-CHANNEL CROSSTALK                          | f <sub>IN</sub> = 1 kHz, 1.3 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                           | -135    |              | dB     |

| INTERNAL REFERENCE BUFFER                             | External reference drives REFIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                           | 100     |              | ub ub  |

| REFIN Voltage Range                                   | 5.3 V ≤ VDD 5V ≤ 5.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.95                                                      | 5       | 5.05         | V      |

| NET IIV Voltage Natige                                | 4.8 V ≤ VDD_5V ≤ 5.25 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4.33                                                      | 4.5     | 5.05         | V      |

|                                                       | 4.6 V ≤ VDD_5V ≤ 5.25 V<br>4.75 V ≤ VDD_5V ≤ 5.25 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.046                                                     | 4.096   | 4.146        | V      |

| REFIN Bias Current                                    | 4.73 V 3 VDD_3V 3 3.23 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -50                                                       | 5       | 4.140<br>+50 | '.     |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -30                                                       | 3<br>40 | +30          | nA     |

| REFIN Input Capacitance Reference Buffer Offset Error | DEEIN - 5 V T - 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 400                                                       |         | .400         | pF     |

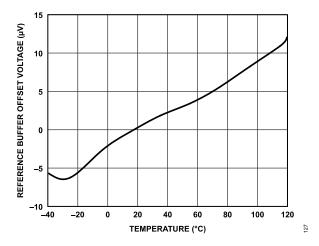

| Reference Buller Offset Error                         | REFIN = 5 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -100                                                      | ±25     | +100         | μV     |

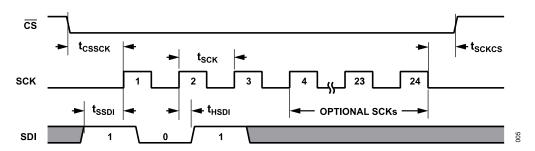

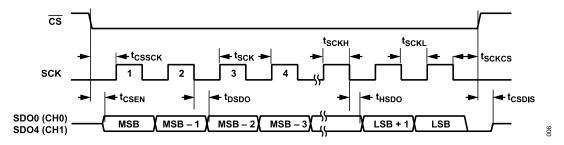

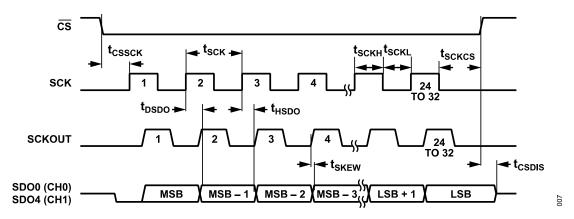

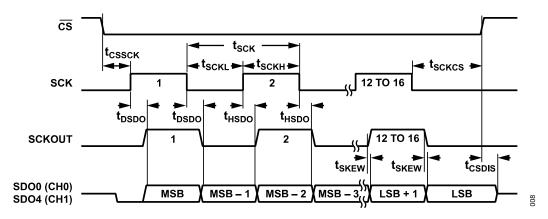

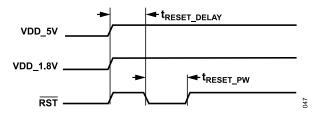

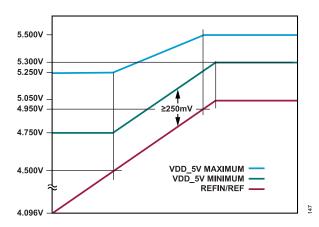

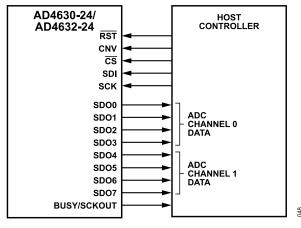

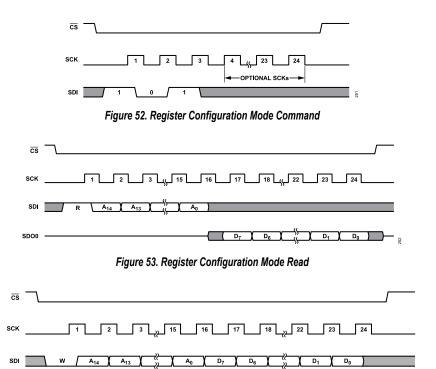

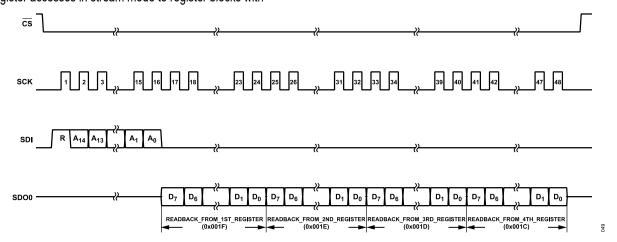

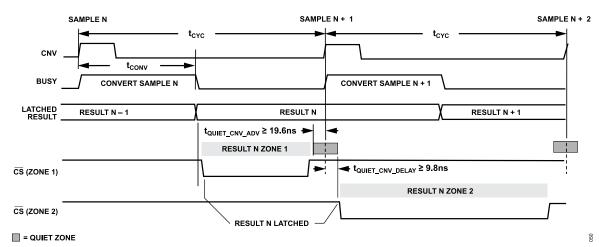

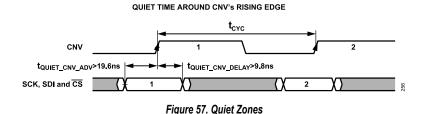

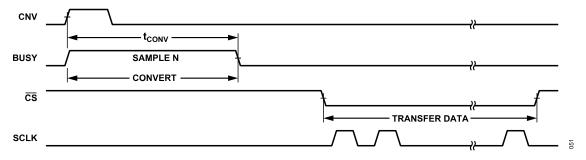

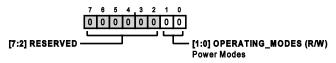

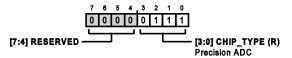

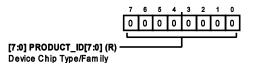

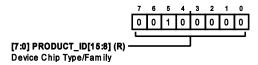

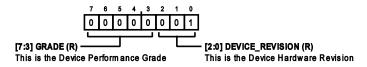

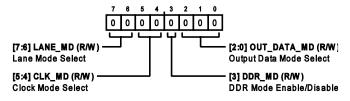

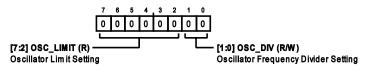

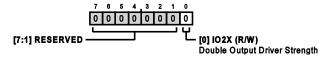

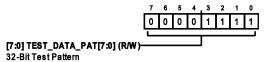

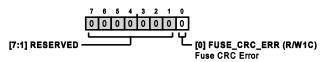

|                                                       | REFIN = 4.5 V, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 400                                                       | ±25     | . 100        | μV     |