# TMC457 – DATA SHEET

S-profile motion controller with PID feedback control and high-resolution microstepping sequencer for stepper motors and piezo motors

### 1 Features

The TMC457 is a single axis micro-stepping motion controller offering a jerk-free S-shaped motion profile and tailored to work with TMC246/TMC249 stepper motor drivers, stepping piezo motors, or any Step/Direction driver. Add an encoder for precise positioning using the internal PID regulator or to increase reliability by fault detection. The high-resolution microstep sequencer directly controls stepper motors and piezo motors.

For designs using ADITrinamic TMC26x, TMC2xxx or later motor drivers, please consider the TMC4361A S-Ramp motion controller, offering an adapted feature set.

### **Highlights**

- S-shaped and linear ramps

- On-the-fly alteration of all parameters

- 12 bit, 8192 entry microstep look-up table

- Incremental encoder interface with scaling

- Fast and stable easyPID<sup>™</sup> PID controller

- 32 bit registers from mHz to MHz / from nanometer to meter

- SPI interface to microcontroller

- Reference switch & virtual stop switches

- Step / direction output

- Position pulse output

- Scalable step / direction input

- Direct interface TMC246/TMC249 family stepper motor drivers w.StallGuard™

- ChopSync™ built in for best motor velocity range with TMC24x drivers

Analog high resolution motor driver control via external dual 12 bit DAC

### **Types of Motors**

- Two phase stepper motors

- PiezoMotors (direct sequencer support for PiezoMotor's PiezoLEGS® motor)

- Any type of motor via STEP/DIR interface

### **Applications**

- Medical and laboratory equipment with high-speed motion e.g., for liquid handling

- High end placement and positioning systems / High reliability drives

- Sub-micrometer positioning (piezo motors)

- Active stabilization with incremental encoder and fast PID regulator

ORDER CODES

| Order code | Description                                                         | Size                    |

|------------|---------------------------------------------------------------------|-------------------------|

| TMC457-B   | Stepper and Piezo Motor Controller IC, SPI, Step/Dir, FBGA144, Tray | 13 x 13 mm <sup>2</sup> |

### Life support policy

TRINAMIC Motion Control GmbH & Co. KG does not authorize or warrant any of its products for use in life support systems, without the specific written consent of TRINAMIC Motion Control GmbH & Co. KG.

Life support systems are equipment intended to support or sustain life, and whose failure to perform, when properly used in accordance with instructions provided, can be reasonably expected to result in personal injury or death.

### © TRINAMIC Motion Control GmbH & Co. KG 2008

Information given in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed for the consequences of its use nor for any infringement of patents or other rights of third parties which may result from its use.

Specification is subject to change without notice.

# 2 Contents

| 1  | FEATURES                                                                         | 1        |

|----|----------------------------------------------------------------------------------|----------|

| 2  | CONTENTS                                                                         | 3        |

|    | 2.1 Figures                                                                      | 2        |

|    | 2.2 Tables                                                                       | 4        |

| 3  | GENERAL DESCRIPTION                                                              | 5        |

| 4  | TMC457 BLOCK DIAGRAM AND INTERFACES                                              | 5        |

|    | 4.1 Microcontroller Interface (SPI <sup>TM</sup> )                               |          |

|    | 4.2 Step Direction Inputs                                                        | 6        |

|    | 4.3 DAC (LTC2602) Interface                                                      |          |

|    | 4.3.1 Piezo Motor Driver                                                         |          |

|    | 4.4.1 Stepper Motor Driver (high resolution micro stepping)                      |          |

|    | 4.4.2 Stepper Motor Driver (low resolution micro stepping)                       | 7        |

| 5  |                                                                                  |          |

| •  | 5.1 Ramp Generator                                                               |          |

|    | 5.2 ABN Incremental Encoder Interface                                            |          |

|    | 5.2.1 Setting the encoder to match the motor resolution:                         |          |

|    | 5.3 Vector control                                                               | 9        |

|    | 5.3.1 Initialization of vector control mode                                      | 1(       |

|    | 5.5 Step Direction Output Interface                                              |          |

|    | 5.6 Step Direction Input Interface for multi axis interpolation                  |          |

|    | 5.7 Reference Switch and Stop Switch Interface                                   | 11       |

|    | 5.8 Micro Step Sequencer                                                         |          |

|    | 5.8.1 ChopSync™ CHOPCLK                                                          |          |

|    | 5.10 Interrupt Controller                                                        |          |

|    | 5.11 Sine Wave Look-up Table (SIN-LUT) Access and Parameterization               | 13       |

|    | 5.11.1 Calculation of the Sine Wave Look-Up-Table to drive a Piezo Motor         |          |

|    | 5.11.2 Calculation of the Sine Wave Look-Up-Table to drive a Stepper Motor       |          |

| 6  | REGISTER MAPPING                                                                 | 14       |

|    | 6.1 SPI Datagram Structure                                                       |          |

|    | 6.1.1 Selection of Write / Read (WRITE_notREAD)                                  |          |

|    | 6.1.2 Data Alignment                                                             |          |

|    | 6.2.1 Nomenclature of Read / Write / Clear on Read / Clear on Write of Registers | 12<br>15 |

|    | 6.2.2 Time Scaling by Clock Frequency                                            | 15       |

|    | 6.2.3 Real World Units vs. Units of the TMC457                                   | 26       |

| 7  | EXAMPLES                                                                         | 27       |

|    | 7.1 How to Get a Motor Running                                                   | 27       |

|    | 7.2 Set Incremental Encoder Interface Parameters                                 | 27       |

| 8  | NOTATION OF NUMBER SYSTEMS                                                       | 28       |

| _  | DININING DAGGERS AND SUSCEPTIONS DATA OF THE THROUST                             | •        |

| 9  | PINNING, PACKAGE, AND ELECTRICAL DATA OF THE TMC457                              |          |

|    | 9.1 Pinning of TMC457                                                            |          |

|    | 9.1.1 Pull-Up / Pull-Down Resistances                                            |          |

|    | 9.2 Package Outlines and Dimensions.                                             |          |

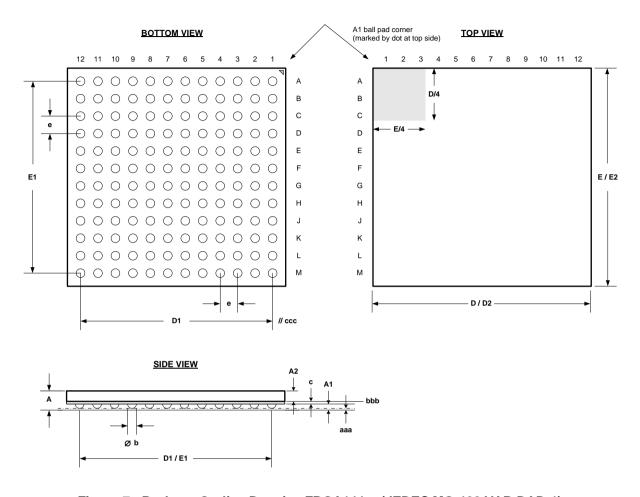

|    | 9.2.1 Fine Pitch BGA Package with 144 Balls (FBGA144) of TMC457-BC               |          |

| 1( | MICRO CONTROLLER INTERFACE (SPI)                                                 | 34       |

| 11                                                       | CHARACTERISTICS                                          | 35                   |

|----------------------------------------------------------|----------------------------------------------------------|----------------------|

| 12                                                       | LITERATURE                                               | 36                   |

| 13                                                       | REVISION HISTORY                                         | 36                   |

| 2.1                                                      | Figures                                                  |                      |

| Figure<br>Figure<br>Figure<br>Figure<br>Figure<br>Figure | e 1 : Functional Block Diagram of the TMC457             |                      |

| 2.2                                                      | Tables                                                   |                      |

| Table<br>Table<br>Table<br>Table<br>Table                | 1 : PWM frequency calculation for ChopSync <sup>TM</sup> | 32<br>33<br>34<br>35 |

|                                                          | 7 - Power Dissipation                                    |                      |

### 3 **General Description**

The TMC457 has been designed with Trinamic's background of more than 10 years of dedicated motion control ICs for stepper motors, like the former 6 axis controller TMC406, the low cost 3 axis controller TMC428 with its compatible successor TMC429, and the high-end controller TMC453 with its compatible successor TMC454. While there lie 10 years of development and experience between the TMC453 and the TMC457, the basic features look similar, but a lot of ideas, application know-how and customer feedback have been evaluated, sorted, and flown into the design. The intention in creating the TMC457 was to provide a motion controller that provides superior performance, which can hardly be achieved by software in a processor system, while providing a very easy-to-use interface to the programmer, which looks like the peripherals found in a microcontroller. The electronic gear shift / pre-scaling found in our other motion controllers was eliminated by extending position and velocity registers to 32 bits. This direct control makes it easy to use the full range and precision of parameter setting. The easyPID™ closed loop PID regulator eases the achievement of control loop stability by providing a programmable hysteresis. Some features found in the TMC453 and TMC428 have been streamlined, to make them easier to use and some options have been removed, like the programmable sequencer for many different motor types, bearing in mind the most common applications.

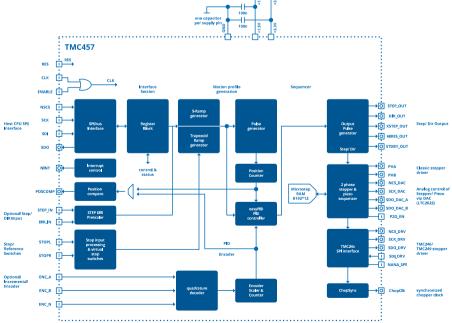

Figure 1: Functional Block Diagram of the TMC457

## 4 TMC457 Block Diagram and Interfaces

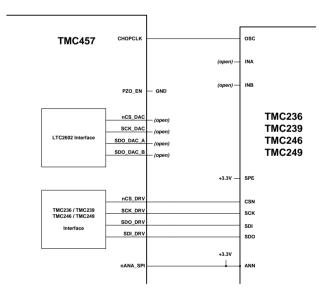

Figure 1 shows the block diagram of the TMC457 motion controller. The TMC457 is equipped with a SPI interface for communication with the microcontroller. It uses a fixed data length of 40 bit – 8 bit

address and 32 data. The TMC457 has a driver SPI to directly control the TRINAMIC stepper motor drivers TMC236, TMC239, TMC246, and TMC249. It supports processing of StallGuard information to emulate a reference switch, when using TMC246 or TMC249. The TMC457 has step direction input and step direction outputs as well to allow the control of step direction power stages (like the TMC332) or for external monitoring of motion by step pulse counting. For high precision micro stepping the TMC457 is equipped with a DAC interface for LTC2602. This allows control of the TMC236 family with extended microstep resolution or control of external power drivers with the classical analog control. An incremental encoder interface is added for processing incremental encoders with digital quadrature signal outputs (ABN). The position available from the quadrature signal decoder is directly available as an input for the PID position regulator. The PID regulator is for position stabilization also during motion. The PID regulator runs at an update rate of 100kHz and thus provides fastest response times.

### 4.1 Microcontroller Interface (SPI™)

The SPI for communication with the microcontroller to set motion control parameters (velocity, acceleration, bow, ...) of the TMC457 and to send motion command for positioning (set target position) and continuous motion applications (set velocity).

### 4.2 Step Direction Inputs

In addition to the SPI for micro controller communication with the TMC457, the motion can be controlled externally via the step direction inputs STEP\_IN and DIR\_IN.

### 4.3 DAC (LTC2602) Interface

The DAC interface directly controls LTC2602 from Linear Technologies to generate analog output signals (two channels for micro stepping of bipolar two-phase stepper motors) and four channels as required for PiezoLEGS motors from the company Piezo-Motors.

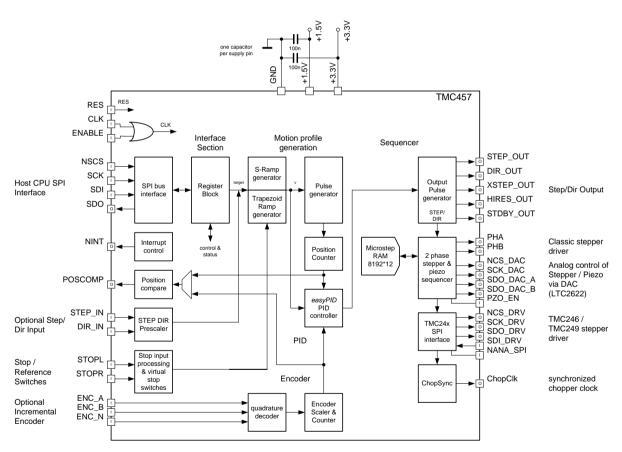

#### 4.3.1 Piezo Motor Driver

The power four required power stages of the driver for the piezoelectric motor (PiezoLEGS) must be able to drive a 100nF capacitance at 3kHz with an amplitude of 48V each. A power stage with these capabilities is realized for the TMC457 evaluation board.

Figure 2: TMC457 with Piezo Motor Interface

#### 4.4 Stepper Motor Driver Interface (TMC236, TMC239, TMC246, TMC249)

The direct TRINAMIC driver interface of the TMC457 allows the TRINAMIC drivers to be controlled by the TMC457.

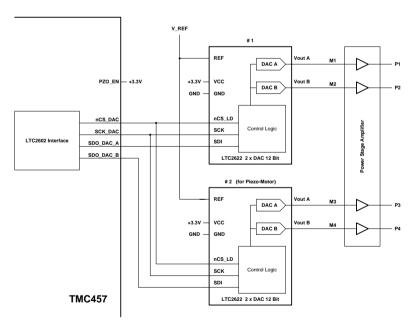

#### 4.4.1 Stepper Motor Driver (high resolution micro stepping)

For high resolution micro stepping the TMC457 has an interface for dual SPI DAC LTC2602.

Figure 3: High Resolution Micro Stepping Configuration

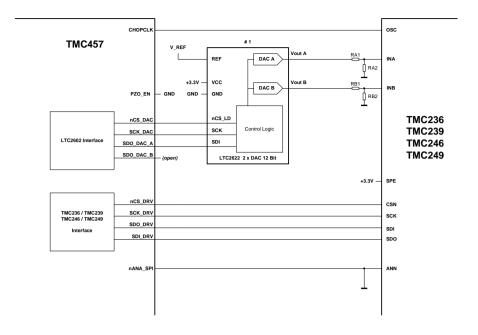

### 4.4.2 Stepper Motor Driver (low resolution micro stepping)

For low resolution micro stepping, a TRINAMIC driver can be connected directly via SPI without an additional DAC. With this, one can drive with 16 times micro stepping.

Figure 4: Stepper Motor Driver Configuration (SPI)

### 5 Functional Blocks and Registers

### 5.1 Ramp Generator

The ramp generator is the heart of the motion controller. It runs either ramp with linear velocity profile or ramp with s-shape velocity profile. The selection is done by the bow parameter. Setting bow to 0 selects linear velocity profile. Linear ramps perform the quickest motion, by using the maximum available acceleration at all times. But, since the acceleration becomes switched on and off abruptly, system resonances can occur. They appear like an additional load on the motor, thus reducing the available useful portion of motor torque. Further, system resonances need some time to fade away, and this can costs valuable system time, if a complete stand still is required, before other actions can start. With the S-shaped ramp, resonances can be reduced. However, it is advised to choose the bow parameter as high as possible, in order to optimize positioning time.

The ramp generator provides different modes of operation:

- 1. A simple target-positioning based on trapezoidal ramps. This mode uses a straight-forward algorithm to move the motor, and thus the resulting travel time is easily predictable and can be calculated based on start velocity, acceleration and target velocity. To enable this mode, set bow index=0.

- 2. For fully featured S-shaped ramps, select the *bow\_index* to smoothen the transition between the acceleration segments.

- 3. Hold mode is a simple mode, where the velocity is directly controlled by a register (*v\_target*). The motion controller does not limit acceleration.

- 4. Velocity mode provides an intermediate mode of operation, where the motion controller approaches the target velocity based on the acceleration settings.

It should be noted that the choice of the microstep resolution directly influences the complete ramp generator parameter settings, because a higher microstep resolution means a higher end velocity setting, and thus a higher acceleration and a higher bow parameter to yield the same results. This way, the settings are scaled in a huge range, e.g., when changing between fullstep and highest resolution microstep.

#### Attention:

At all times, all parameters may be changed, but it should be noted, that unexpected results may occur, when changing the bow parameter to a lower value during an acceleration phase, or when changing the acceleration or deceleration parameter to a lower value. In these cases, the maximum positioning velocity, respectively the target position could be exceeded, in case the new values do not allow decelerating quickly enough. Even an overrun of the register value could occur and lead to unexpected results. Under normal circumstances, the bow parameter will be fixed in an application.

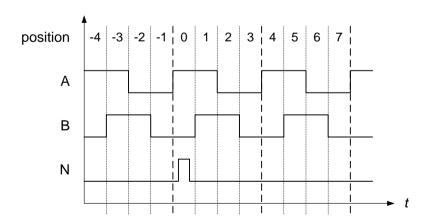

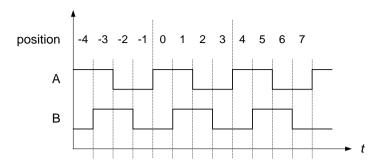

Figure 5: Outline of ABN Signals of an Incremental Encoder

#### 5.2 ABN Incremental Encoder Interface

The TMC457 is equipped with an incremental encoder interface for ABN encoders that gives positions via digital incremental quadrature signals (usually named A and B) and a clear signal (usually named N for null of Z for zero). The N signal can be used to clear a position. It might be necessary to disable the clearing of the encoder position after the first N signal event because the encoder gives this signal once for each revolution and for most applications a motor turns more than one revolution.

The encoder constant named *enc\_const* is added or subtracted on each position change of the quadrature signals AB of the incremental encoder. The encoder constant *enc\_const* represents an unsigned fixed-point number (16.16) to facilitate the generic adaption between motors and encoders. In decimal mode, the lower 16 bit represent a number between 0 and 9999. This is especially important for piezo motors (PiezoLEGS) because they do not have a fixed step length. These motors achieve their very high positioning precision in the range of nanometers via closed loop control together with a position encoder. For stepper motors equipped with incremental encoders the fixed number representation allows very comfortable parameterization. Additionally, gear can easily be taken into account.

The encoder counter named  $x\_enc$  holds the current determined encoder position. Different modes concerning handling of the signals A, B, and N take active low and active high signals of usual incremental encoders into account. For details, please refer to the register mapping section 6 Register Mapping, page 14 ff.

The register *enc\_status* holds the status concerning event of the ABN signals. The register *enc\_latch* stores the actual encoder position on an N signal event. The register *x\_latch* stores the position while a reference switch event occurs.

A register named *enc\_warn\_dist* (encoder warning distance) is used to generate an interrupt via the TMC457 interrupt controller if the distance between encoder position and actual position is larger than *enc\_warn\_dist*. The calculated error *pid\_e* is available from the PID controller unit. Therefore, the PID controller needs to be enabled.

#### 5.2.1 Setting the encoder to match the motor resolution:

Encoder example settings for motor parameters: 2048  $\mu$ steps, 200FS  $\rightarrow$  409600 / U Factor = FS\* $\mu$ S / encoder resolution

| Encoder example settings for a 200 fullstep motor with 2048 microsteps |                         |                                  |  |  |  |  |  |

|------------------------------------------------------------------------|-------------------------|----------------------------------|--|--|--|--|--|

| Encoder resolution                                                     | required encoder factor | comment                          |  |  |  |  |  |

| 200                                                                    | 2048                    |                                  |  |  |  |  |  |

| 360                                                                    | 1137,7778               | No exact match possible!         |  |  |  |  |  |

|                                                                        | = 74565404,4444 / 2^16  |                                  |  |  |  |  |  |

|                                                                        | = 11377777,7778 / 10000 |                                  |  |  |  |  |  |

| 500                                                                    | 819,2                   |                                  |  |  |  |  |  |

|                                                                        | = 53687091,2 / 2^16     |                                  |  |  |  |  |  |

|                                                                        | = 8192000 / 10000       | exact match with decimal setting |  |  |  |  |  |

| 1000                                                                   | 409,6                   | exact match with decimal setting |  |  |  |  |  |

| 1024                                                                   | 400                     |                                  |  |  |  |  |  |

| 3600                                                                   | 113,7778                | No exact match possible!         |  |  |  |  |  |

| 4000                                                                   | 102,4                   | exact match with decimal setting |  |  |  |  |  |

| 4096                                                                   | 100                     |                                  |  |  |  |  |  |

| 8192                                                                   | 50                      |                                  |  |  |  |  |  |

| 16384                                                                  | 25                      |                                  |  |  |  |  |  |

| 32768                                                                  | 12.5                    |                                  |  |  |  |  |  |

### 5.3 Vector control

The vector control unit allows a load angle based motor control. This makes the motor behave like a servo motor, i.e. it can be overloaded or stopped, and will later on catch up again, using the PID regulator. Therefore, be careful to also activate the PID regulator!

Vector control is only possible using binary encoder resolutions, because no decimal setting is available. Low resolution decimal encoders still give a match.

| Vector control example settings for a 200 fullstep motor |                                |               |  |  |  |

|----------------------------------------------------------|--------------------------------|---------------|--|--|--|

| Encoder resolution                                       | required vector encoder factor | venc_us_const |  |  |  |

| 512                                                      | 25                             | 1600          |  |  |  |

| 1024                                                     | 12.5                           | 800           |  |  |  |

| 2048                                                     | 6.25                           | 400           |  |  |  |

| 4096                                                     | 3.125 = 3 1/8                  | 200           |  |  |  |

| 8192                                                     | 1.5625 = 1 9/16                | 100           |  |  |  |

| 16384                                                    | 0.78125 = 25/32                | 50            |  |  |  |

| 32768                                                    | 0.390625 = 25/64               | 25            |  |  |  |

A 400 fullstep motor needs the double setting

Different load angle limits above 90° allow for field weakening operation, which gives a faster motor operation.

#### 5.3.1 Initialization of vector control mode

A precise initialization of the vector control mode is critical for best functionality. Also, the encoder needs to have an absolute precision, which is at least ½ fullstep of the motor.

For a newly assembled drive, an initial initialization is necessary. This initialization requires that the motor does not see any mechanical load during initialization. Later on, the vector control can be initialized with a stored offset from the initial initialization, using absolute position information, for example based on the encoder N channel.

For initial initialization, the following procedure can be followed:

The actual encoder position <code>venc\_us\_pos</code> needs to be initialized for vector control. The position must match selected <code>microstep\_adr</code> bits, when the motor is unloaded in its exact position. This for example can be accomplished, by switching the motor to a high standby torque after power on. Directly after a power on, all <code>microstep\_adr</code> bits are zero. Now, the motor will be in the exact zero position, as long as it sees no mechanical load. Therefore, now the <code>venc\_us\_pos</code> can be initialized with zero, in order to match the encoder angle to the electrical angle of the motor.

When the absolute position of the encoder is known, the vector control register *venc\_us\_pos* can be initialized based on this information. Therefore, the encoder needs to be read out, or the N channel needs to be found, and afterwards the stored offset can be added to the absolute position and be written to *venc\_us\_pos*. Be sure to do this in a high priority procedure, because the encoder should not advance a step in the meantime. If this cannot be guaranteed, a check and iteration should be done.

### 5.4 PID Controller - easyPID™

The PID (Proportional Integral Differential) controller calculates a velocity v based on a position difference error pid\_e = enc\_x - x\_actual where enc\_x is the actual position-the real mechanical position-determined by the incremental encoder interface and x\_actual is the actual position of the micro step sequencer—the position the TMC457 assumes to be the actual one. With this, the TMC457 moves with this (signed) velocity v until the actual position- measured by the incremental encoder —match. The velocity v to minimize the error e is calculated by

$$v = P \cdot e(t) + \int_{0}^{t} I \cdot e(t) \cdot dt + D \cdot \frac{d}{dt} e(t).$$

The motor moves with this velocity  $v = pid_v_actual$  until the error e(t) vanishes resp. falls below a programmed limit – the hysteresis  $pid_tolerance$ . Primary, the PID regulator is parameterized by its basic parameter P, I, D represented by registers  $pid_p$ ,  $pid_i$ ,  $pid_d$ . Setting  $pid_d = 0$  makes a P regulator, additionally setting  $pid_i = 0$  makes a P regulator. For micro controller interaction, the

parameter pid\_dv\_cpu is added to the pid\_v\_actual. The readable register pid\_dv\_clip holds the actual value of clipping done by the PID controller of the TMC457.

Due to constraints of practical real word application, the integer part of the PID regulator can be clipped to a limit named pid\_iclip. Without this, the integral part of the PID regulator pid\_isum increases with each time step by pid\_i\*pid\_e as long as the motor does not follow. The actual error can be read out from register pid\_e. The integration over time of the error e is done with a fixed clock frequency of fPID\_INTEGRAL[Hz] = fCLK[Hz] / 128. The time scaling for the deviation with respect to time of the error is controlled by the register named pid\_clk\_div.

A stabilization of the target position by programmable hysteresis is integrated to avoid oscillations of regulation when the actual position is close to the real mechanical position. The PID controller of the TMC457 is fast – programmable up to approximate 100kHz update rate at fCLK = 16 MHz of the TMC457 – so that it can be used during motion to stabilize the motion. The parameterization of the PID controller of the TMC457 occurs in a direct way. Due to this, it is named easyPID<sup>TM</sup>. Nevertheless, the parameterization of a PID controller might need a detailed knowledge of the application and the dynamic of the mechanics that is controlled by the PID controller. Additionally, a special control register allows software interaction for additional feedback control algorithms that can be implemented within the micro controller used to parameterize the TMC457.

### 5.5 Step Direction Output Interface

The TMC457 is equipped with step direction outputs (STEP, OUT). In Addition, it is equipped with a so-called X\_STEP output. A pulse on this output represents a number of (micro) steps. It is configured by the register named pulse\_xstep\_div. The TMC457 is able to generate step pulses with up to its clock frequency fCLK[Hz]. Because a step frequency in the range of the clock frequency of the TMC457 might be too high for usual step direction drivers, an additional step output named X\_STEP (extended step) is available. The X\_STEP represents a number of steps to be done at a lower frequency. The threshold that selects between step pulses and extended step pulses is programmable. This can be parameterized to give full steps on the XSTEP output of the TMC457.

### 5.6 Step Direction Input Interface for multi axis interpolation

The TMC457 is equipped with step direction inputs (STEP\_IN, DIR\_IN). This allows using the TMC457 with an external ramp generator. A number of TMC457 can be synchronized by interconnecting the step direction inputs and outputs via a switch matrix. One TMC457 is used as master and its step and direction output is fed to the other TMC457. They can be programmed to follow the master pulses scaled by the 15-bit factor sd\_scale (and sign). This way, multi-axis interpolation can be realized. The slave motion thus always is equal or slower than the master. When programming the master axis, the maximum allowed acceleration and velocity values of the slave axis have to be considered.

The step input is sampled once per system clock. Thus, the maximum input frequency is equal to the half system clock frequency. Please remark, that this also limits the master velocity during interpolated moves.

#### 5.7 Reference Switch and Stop Switch Interface

The TMC457 is equipped with reference switch that can be programmed for automatic actions. For details, please refer to the register mapping section 6 Register Mapping, page 14 ff. The reference switch inputs are available to store a position on a reference switch event. Additionally, these inputs can be enabled to force a stop.

### 5.8 Micro Step Sequencer

The micro step sequencer can be programmed for different micro step resolutions. The sequencer controls the mixed decay feature of TRINAMIC stepper motor drivers. Current scaling is also done under control of the sequencer. When using TMC246 or TMC249 the StallGuard™ threshold is under control of the sequencer. A readable register holds the TRINAMIC stepper motor driver status bits and diagnosis bits.

#### 5.8.1 ChopSync™ CHOPCLK

To use the ChopSync<sup>™</sup> feature together with a TRINAMIC stepper motor driver the output CHOPCLK of the TMC457 has to be connected to the PWM oscillator input OSC of the TRINAMIC stepper

motor driver (TMC236, TMC239, TMC246, or TMC249) – without a capacitor at the OSC input. The recommended chopper frequency fOSC for the TRINAMIC stepper motor driver is 36kHz. The chopper frequency should not be below 25kHz and must be lower than 50kHz. The chopper frequency is programmed via the register chop\_clk\_div.

<u>Warning:</u> A chopper clock signal with a too high frequency might damage the stepper motor driver due to dynamic power dissipation overload.

| fCLK[Hz]   | fOSC[Hz] | chop_c     | clk_div  |

|------------|----------|------------|----------|

| 16 000 000 | 36.000   | 0x1BC      | (=444)   |

| 16.000.000 | 25.000   | 0x280      | (=640)   |

| 8 000 000  | 36.000   | 0x0DE      | (=222)   |

| 8.000.000  | 25.000   | 0x140      | (=320)   |

| fCLK[Hz]   | fOSC[Hz] | fCLK[Hz] / | fOSC[Hz] |

Table 1 : PWM frequency calculation for ChopSync™

### 5.9 Type and Version Register / Version specific notes and known bugs

The type of the controller and its version can be read out from a register. For the TMC457 version 1.02 one gets 0x00457102 reading the type and version register. This allows hardware detection. Reading the version allows handling of different version by a single software version.

| Version | Bug                                                      | Description and workaround                                                                                                                                                      |

|---------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.02    | AMAX lower limit with linear ramps                       | When using linear ramps, setting AMAX to a value lower than 128 results in a strange positioning behavior, when AMAX and DMAX differ.                                           |

|         |                                                          | This is due to an internal rounding which results in AMAX being used for deceleration rather than DMAX or vice versa.                                                           |

|         |                                                          | This bug will be corrected in future versions.                                                                                                                                  |

|         |                                                          | Workaround:                                                                                                                                                                     |

|         |                                                          | Use AMAX values above 128, when AMAX and DMAX are required to be different. AMAX values below 128 are typically only required, when working with low microstepping resolutions. |

|         |                                                          | Alternative: Use S-shaped ramps.                                                                                                                                                |

| -1.03   | Stop switches do not become disabled at                  | When the motor becomes stopped by a stop switch, a movement into the opposite direction is not possible without disabling the stop switch.                                      |

|         | move in opposite direction while actual velocity is zero | The reason is that the stop switches are active in any direction when velocity is zero.                                                                                         |

|         |                                                          | This bug will be corrected in future versions.                                                                                                                                  |

|         |                                                          | Workaround:                                                                                                                                                                     |

|         |                                                          | Disable stop switch when moving into opposite direction.                                                                                                                        |

| 1.04    | -                                                        | Actual Version                                                                                                                                                                  |

#### **5.10 Interrupt Controller**

The interrupt controller is programmable for different conditions. If an interrupt condition occurs the open drain output nINT is pulled to low (activated) if the interrupt mask for the corresponding interrupt condition is enabled.

### 5.11 Sine Wave Look-up Table (SIN-LUT) Access and Parameterization

The TMC457 is equipped with an internal RAM (8192 addresses x 12-bit data) to hold a sine wave look-up table for micro stepping. This look-up table must be initialized first after power up of the TMC457. Depending on the type of motor, a dedicated sine wave table has to be written into the internal RAM of the TMC457. For both, 8192 values of 12-bit integer have to be calculated. The sine LUT RAM is accesses via two register addresses, one for read and one for write.

**Important Hint:** When reading data from RAM, the read data are valid with the next read access. So, the read data are pipelined with a delay of one SPI datagram.

#### 5.11.1 Calculation of the Sine Wave Look-Up-Table to drive a Piezo Motor

$$y(x) = 4096 + 4095 * \sin(2\pi * x/8192 - 2*\pi/8)$$

with  $x = 0, 1, 2, 3, ..., 8189, 8190, 8191.$

### 5.11.2 Calculation of the Sine Wave Look-Up-Table to drive a Stepper Motor

$$y(x) = abs(4095 * sin(2\pi * x/8192))$$

with  $x = 0, 1, 2, 3, ..., 8189, 8190, 8191.$

With offset, to adjust current zero crossing, the formula becomes

$$v(x) = offset + abs((4095 - offset) * sin(2\pi * x/8192))$$

with  $x = 0, 1, 2, 3, ..., 8189, 8190, 8191.$

The offset has a theoretical range of 0 to 4094. For a practical application, the offset will lie between 0 and 100. When using current scaling, the offset also becomes scaled down – this may be needed to be taken into account!

### 6 Register Mapping

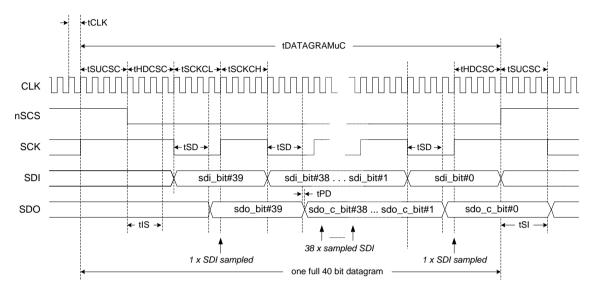

### 6.1 SPI Datagram Structure

The TMC457 uses 40 Bit SPI™ (Serial Peripheral Interface, SPI is Trademark of Motorola) datagrams for communication with a microcontroller. Microcontrollers which are equipped with hardware SPI are typically able to communicate with integer multiples of 8 bit.

Each datagram sent to the TMC457 is composed of an address byte followed by four data bytes. This allows direct 32 bit data word communication with the register set of the TMC457. Each register is accessed via 32 data bits even if it uses less than 32 data bits.

For simplification, each register is specified by a one-byte address, where the reading address is given with the most significant bit = '0'. For a write access, the most significant bit of the address byte is '1'. Most registers are write-only registers, some can be read additionally, and there are also some read only registers.

### 6.1.1 Selection of Write / Read (WRITE\_notREAD)

The read and write selection is controlled by the MSB of the address byte (bit 39 of the SPI datagram). This bit is '0' for read access and '1' for write access. So, the bit named W is a WRITE\_notREAD control bit. The active high write bit is the MSB of the address byte. So, 0x80 has to be added to the address for a write access.

Example: For a read access to the register (x\_actual) with the address 0x01, the address byte has to be set to 0x01. For a write access to the register (x\_actual) with the address 0x01, the address byte has to be set to 0x80 + 0x01 = 0x81. For read access, the data bit might have any value ('-'). So, one can set them to '0'.

READ x\_actual datagram ⇔ 0x01000000000; WRITE x\_actual := 0x89ABCDEF; datagram ⇔ 0x8189ABCDEF;

| TMC457 SPI Datagram Structure      |            |            |                                      |                 |  |  |

|------------------------------------|------------|------------|--------------------------------------|-----------------|--|--|

| MSB (transmited firs               | t)         | 40 bit     |                                      |                 |  |  |

| 39                                 |            |            |                                      | 0               |  |  |

| 8 bit ADDRESS                      |            | 32 bit     | DATA                                 |                 |  |  |

| 39 32                              |            | 31 0       |                                      |                 |  |  |

| RW + 7 bit<br>ADDRESS              | 8 bit DATA | 8 bit DATA | 8 bit DATA                           | 8 bit DATA      |  |  |

| 39 / 38 32                         | 31 24      | 23 16 15 8 |                                      | 7 0             |  |  |

| w 3832                             | 3128 2724  | 2320 1916  | 1512 118                             | 74 30           |  |  |

| 3 3 3 3 3 3 3 3<br>9 8 7 6 5 4 3 2 |            |            | 1 1 1 1 1 1 1 9 8<br>5 4 3 2 1 0 9 8 | 7 6 5 4 3 2 1 0 |  |  |

### 6.1.2 Data Alignment

All data are right aligned. Some registers represent unsigned (positive) values, some represent integer values (signed) as two's complement numbers, single bits or groups of bits are represented as single bits respectively as integer groups.

### 6.2 Register Block Structure – Register Mapping

All parameterizations take place by register writes. The access to the registers is via SPI. The ramp generator register set enfolds basic motion control parameters, a ramp generator register set, an incremental encoder register set, a PID controller register set – named easyPID<sup>TM</sup>, a step direction output configuration register set, a reference switch configuration register set, a micro step sequencer configuration register, a type & version register, an interrupt configuration register, and a sine wave lookup table (LUT) RAM port register.

### 6.2.1 Nomenclature of Read / Write / Clear on Read / Clear on Write of Registers

Units are written in are given in brackets, e.g. [micro steps]. Read only registers are designated by R. Read only registers with automatic clear (C) on read are designated by R+C. Registers that are cleared on write are designated by W+C. Write only registers are designated by W.

#### 6.2.2 Time Scaling by Clock Frequency

Time is scaled by the the clock frequency of the TMC457. This scales velocity, acceleration, and bow. So, velocity is given in unit [micro steps per time] and not as [micro steps per second], acceleration is given in unit [micro steps per time^2] and not unit [micro steps per second^2]. Formulas for the conversion into units based on time in seconds is given in section 0, page 26.

| Ramp | Ramp Generator Register Set – Basic Motion Control Parameters |      |                 |                                                                                                                                                                                                                                                                |                                                               |  |  |

|------|---------------------------------------------------------------|------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| R/W  | Addr                                                          | Bits | Register        | Description                                                                                                                                                                                                                                                    | Range [Unit]                                                  |  |  |

| RW   | 0x00                                                          | 90   | mode            | bit 1,0: ramp_mode  00 = positioning mode  01 = reserved  10 = velocity mode  11 = hold mode  bit 2: step_dir_enable  bit 4: shaft  bit 8: PID_on  bit 9: PID_base v_actual                                                                                    | default = %000000010                                          |  |  |

| RW   | 0x01                                                          | 310  | x_actual        | Actual position                                                                                                                                                                                                                                                | ± [µsteps]                                                    |  |  |

| R    | 0x02                                                          | 310  | v_actual        | Actual velocity                                                                                                                                                                                                                                                | ± [µsteps / t]                                                |  |  |

| W    | 0x03                                                          | 300  | v_max           | Maximum velocity for positioning mode                                                                                                                                                                                                                          | 0 to \$7FFF0000<br>for any a_max<br>[µsteps / t]              |  |  |

| W    | 0x04                                                          | 310  | v_target        | Target velocity The sign determines the direction in velocity mode and hold mode.                                                                                                                                                                              | ± \$7FFF0000<br>for any a_max<br>[µsteps / t]                 |  |  |

| W    | 0x05                                                          | 230  | a_max           | Acceleration, unsigned fixed point 16.8 representation                                                                                                                                                                                                         | 0 to \$FFFFFD<br>[µsteps / t^2]                               |  |  |

| W    | 0x06                                                          | 230  | d_max           | Deceleration parameter, unsigned Fixed point 16.8 representation The effective deceleration with s-ramp enabled is 15/16 of <i>d_max</i> .                                                                                                                     | 0 to \$FFFFD<br>[µsteps / t^2]                                |  |  |

| W    | 0x07                                                          | 230  | d_stop          | Deceleration for stop event, for security reason it is with bow = 0                                                                                                                                                                                            | [µsteps / t^2]                                                |  |  |

| W    | 0x08                                                          | 40   | bow_max         | S-Ramp configuration 0=linear ramp (trapezoid) bow_index = 1, 2, 3,, 18 ⇔ bow_value = 1, 2, 4,, 262144                                                                                                                                                         | bow_value<br>[µsteps / t^3]                                   |  |  |

| W    | 0x09                                                          | 310  | x_target        | Target position for automatic ramp in unit microsteps                                                                                                                                                                                                          | ± [µsteps]                                                    |  |  |

| W    | 0x0A                                                          | 310  | x_compare       | POSCOMP output function: The position <i>x_compare</i> is compared either with <i>x_actual</i> or with the encoder position <i>enc_x</i> . (Selection bit: <i>enc_clr_mode</i> .12.) POSCOMP becomes 0 : for x_actual ≤ x_compare 1 : for x_actual > x_compare | ± [µsteps]                                                    |  |  |

| R    | 0x0B                                                          | 40   | status          | bit 0: target_pos_reached bit 1: target_v_reached bit 2: v_is_zero bit 3: - (reserved) bit 4: enc warn dist                                                                                                                                                    |                                                               |  |  |

| R    | 0x0C                                                          | 310  | a_actual        | Actual acceleration value Important note: a_max resp. d_max can be exceeded by up to 1/1024 of the bow_value if 1/1024*bow_value is not an integer divider of a_max resp. d_max                                                                                | 0,, ± a_max<br>resp. d_max<br>resp. d_stop;<br>[µsteps / t^2] |  |  |

| W    | 0x0D                                                          | 150  | sd_scale        | Step Direction input control: bit 140: sd_scaler bit 15: sd_scale_sign                                                                                                                                                                                         | dir & c<br>(c⇔accumulatio<br>n constant-1)                    |  |  |

|      | 0x0E                                                          | -    | -               | reserved                                                                                                                                                                                                                                                       |                                                               |  |  |

| W    | 0X0F                                                          | 230  | a_max_<br>d_max | Sets a_max and d_max to the same value with a single write access to register a_max_d_max                                                                                                                                                                      | [µsteps / t^2]                                                |  |  |

| 0x00: | 0x00: mode - Ramp Generator Register |           |           |                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-------|--------------------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/W   | Bit                                  | Function  | Valu<br>e | Description                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| RW    | 1,0                                  | ramp_     | 00        | positioning mode                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|       |                                      | mode      | 01        | reserved                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|       |                                      |           | 10        | velocity mode (default mode on RESET)                                                                                                                                                                                                                                                                                                                 |  |  |  |

|       |                                      |           | 11        | hold mode (sets v_actual equal to v_target)                                                                                                                                                                                                                                                                                                           |  |  |  |

| RW    | 2                                    | step_dir_ | 0         | step direction inputs are ignored                                                                                                                                                                                                                                                                                                                     |  |  |  |

|       |                                      | enable    | 1         | The step and direction inputs (STEP_IN, DIR_IN) become scaled by <i>sd_scale</i> . In this mode, <i>x_target</i> becomes directly controlled by the scaled step inputs. In order to allow the motor to directly follow the control signals, set to positioning mode and set a high acceleration value <i>a_max_d_max</i> with <i>bow</i> set to zero. |  |  |  |

| RW    | 4                                    | shaft     | 0         | Normal direction of the output pulse generator                                                                                                                                                                                                                                                                                                        |  |  |  |

|       |                                      |           | 1         | Inverts the direction of the output pulse generator                                                                                                                                                                                                                                                                                                   |  |  |  |

| RW    | 8                                    | PID_on    | 0         | PID controller is completely off, all values are frozen. The output pulse generator is fed by <i>v_actual</i> directly.                                                                                                                                                                                                                               |  |  |  |

|       |                                      |           | 1         | PID controller is on. This mode also allows access to the PID error pid_e, which is required for a number of other functions. For normal operation, also set PID_base flag to v_actual base.                                                                                                                                                          |  |  |  |

| RW    | 9                                    | PID_base  | 0         | The pulse generator output is controlled by the PID calculation result only. The motor will not move, if PID result is zero.                                                                                                                                                                                                                          |  |  |  |

|       |                                      |           | 1         | PID output base is <i>v_actual</i> . The PID result is added to the velocity output generated by the ramp generator and becomes clipped to 2^31-1.                                                                                                                                                                                                    |  |  |  |

| 0x08: | 0x08: bow_max - Ramp Generator Register |           |           |                                                                                                                      |  |  |  |

|-------|-----------------------------------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/W   | Bit                                     | Function  | Valu<br>e | Description                                                                                                          |  |  |  |

| W     | 40                                      | bow_index | 0         | The ramp generator uses trapezoid ramps. This corresponds to an infinite bow value.                                  |  |  |  |

|       |                                         |           | 1         | Bow for s-shaped ramps in logarithmic representation. A high bow                                                     |  |  |  |

|       |                                         |           | to        | value leads to a shorter bow phase. The bow_value is added with                                                      |  |  |  |

|       |                                         |           | 18        | 1/1024 fclk[Hz] to acceleration a_actual up to the value set by a_max for acceleration resp. d_max for deceleration. |  |  |  |

|       |                                         |           |           | bow_value = 2^(bow_index-1)                                                                                          |  |  |  |

|       |                                         |           |           | bow_index = 1, 2, 3,, 18 ⇔                                                                                           |  |  |  |

|       |                                         |           |           | bow_value = 1, 2, 4,, 262144                                                                                         |  |  |  |

|       |                                         |           |           | Attention on bow setting:                                                                                            |  |  |  |

|       |                                         |           |           | The resulting bow_value must not exceed A_MAX or D_MAX                                                               |  |  |  |

|       |                                         |           |           | setting. Otherwise oscillations may result.                                                                          |  |  |  |

| 0x0b: | 0x0b: status - Ramp Generator Register |                          |           |                                                                                                                                                                           |  |  |

|-------|----------------------------------------|--------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R/W   | Bit                                    | Function                 | Valu<br>e | Description                                                                                                                                                               |  |  |

| R     | 0                                      | target_pos<br>_reached   | 1         | Signals that the motor has stopped at the target position ( <i>x_actual=x_target</i> ), or at a position determined by <i>PositionLimit_L</i> or <i>PositionLimit_R</i> . |  |  |

|       | 1                                      | target_v_<br>reached     | 1         | Signals that <i>v_actual</i> has reached <i>v_target</i> , respectively <i>v_max</i> during an automatic ramp.                                                            |  |  |

|       | 2                                      | v_is_zero                | 1         | Signals that the motor has stopped.                                                                                                                                       |  |  |

|       | 3                                      | -                        | -         | Unused (reserved)                                                                                                                                                         |  |  |

|       | 4                                      | enc_warn_<br>dist_status | 1         | Signals that the deviation between encoder position and actual ramp position exceeds the warning threshold <i>enc_warn_dist</i> .                                         |  |  |

| 0x0D: | 0x0D: sd_scale - Ramp Generator Register |             |           |                                                                       |  |  |

|-------|------------------------------------------|-------------|-----------|-----------------------------------------------------------------------|--|--|

| R/W   | Bit                                      | Function    | Valu<br>e | Description                                                           |  |  |

| W     | 140                                      | sd_scaler   | Х         | Each step input pulse counts up resp. down x_target by (x+1) / (2^15) |  |  |

|       | 15                                       | sd_scale_ 0 |           | Count up, when direction input is positive                            |  |  |

|       |                                          | sign        | 1         | Count down, when direction input is positive                          |  |  |

| Encod | Encoder Register Set |      |                   |                                                                                                                                                                                                                                                                                      |                                                                                                                    |  |  |  |

|-------|----------------------|------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| R/W   | Addr                 | Bits | Register          | Description                                                                                                                                                                                                                                                                          | Range [Unit]                                                                                                       |  |  |  |

| W     | 0x10                 | 310  | enc_const         | Accumulation constant, 16 bit integer part, 16 bit fractional part enc_x accumulates +/- enc_const / (2^16* enc_x) (binary) or +/- enc_const / (10^4* enc_x) (decimal) To switch between decimal and binary setting, see enc_mode bit 13. Use the sign, to match rotation direction! | binary:<br>± [µsteps/2^16]<br>±(032767.0<br>65535)<br>decimal:<br>±(032767.0<br>9999)<br>default = 1.0<br>(=65536) |  |  |  |

| RW    | 0x11                 | 310  | enc_x             | Actual encoder position                                                                                                                                                                                                                                                              | ± [µsteps]                                                                                                         |  |  |  |

| W     | 0x12                 | 120  | enc_mode          | bit 0 : pol_A bit 1 : pol_B bit 2 : pol_N bit 3 : ignore_AB bit 4 : clr_cont bit 5 : clr_once bit 6 : pos_edge bit 7 : neg_edge bit 8 : clr_enc_x bit 12 : x_comp_sel_enc bit 13 : enc_sel_decimal                                                                                   |                                                                                                                    |  |  |  |

| R+C   | 0x13                 | 0    | enc_status        | bit 0 : <i>N_event</i> Encoder N event detected; status bit is cleared on read: Read (R) + clear (C)                                                                                                                                                                                 |                                                                                                                    |  |  |  |

| R     | 0x14                 | 310  | enc_latch         | Encoder position enc_x latched on N event                                                                                                                                                                                                                                            | [µsteps]                                                                                                           |  |  |  |

| R     | 0x15                 | 310  | x_act_latch       | Motor position <i>x_actual</i> latched on reference switch event or virtual stop switch event                                                                                                                                                                                        | [µsteps]                                                                                                           |  |  |  |

| W     | 0x16                 | 190  | enc_warn_<br>dist | Warning threshold for motor to encoder deviation ( <i>x_actual - enc_x</i> ). This function uses <i>pid_e</i> . An interrupt can be triggered when the threshold is exceeded. abs( <i>pid_e</i> ) > <i>enc_warn_dist</i>                                                             | [µsteps]                                                                                                           |  |  |  |

| 0x12: | 0x12: enc_mode - Encoder Register |           |           |                                                                         |  |  |

|-------|-----------------------------------|-----------|-----------|-------------------------------------------------------------------------|--|--|

| R/W   | Bit                               | Function  | Valu<br>e | Description                                                             |  |  |

|       | 0                                 | pol_A     | Х         | A polarity when N is active                                             |  |  |

|       | 1                                 | pol_B     | Х         | B polarity when N is active                                             |  |  |

|       | 2                                 | pol_N     | Х         | defines polarity of N                                                   |  |  |

|       | 3                                 | ignore_AB | Х         | Ignore A and B polarity                                                 |  |  |

|       | 4                                 | clr_cont  | 1         | continuous clear while N is active (clear once per revolution)          |  |  |

|       | 5                                 | clr_once  | 1         | N event enable, clear on next N event                                   |  |  |

|       | 6                                 | pos_edge  | 1         | N positive edge trigger (when N becomes active)                         |  |  |

|       |                                   |           |           | Disables N level control                                                |  |  |

|       | 7                                 | neg_edge  | 1         | N negative edge trigger (when N becomes inactive)                       |  |  |

|       |                                   |           |           | Disables N level control                                                |  |  |

|       | 8                                 | clr_enc_x | 0         | Upon N event, the <i>enc_x</i> becomes latched to <i>enc_latch</i> only |  |  |

|       |                                   |           | 1         | Additionally clear encoder counter enc_x at N-event                     |  |  |

|       | 9                                 | -         |           | - (reserved)                                                            |  |  |

|       | 10                                | -         |           | - (reserved)                                                            |  |  |

|       | 11                                | -         |           | - (reserved)                                                            |  |  |

|       | 12                                | x_comp_   | 0         | Source for POSCOMP: x_compare is compared to x_actual                   |  |  |

|       |                                   | sel_enc   | 1         | x_compare is compared to enc_x                                          |  |  |

|       | 13                                | enc_sel_  | 0         | Encoder divisor binary: Counts in n/65536                               |  |  |

|       |                                   | decimal   | 1         | Encoder divisor decimal: Counts in n/10000                              |  |  |

| Vecto | Vector Control Register Set |           |                   |                                                                                                                                                                                                                                                                                                                |                                    |  |  |  |

|-------|-----------------------------|-----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|

| R/W   | Addr                        | Bits      | Register          | Description                                                                                                                                                                                                                                                                                                    | Range [Unit]                       |  |  |  |

| W     | 0x17                        | 110       | venc_us_<br>const | Accumulation constant, 6 integer part, 6 bit fractional part  venc_us_const = 64*(motor full steps per rotation) / encoder resolution 0.0: vector control off Use the sign, to match rotation direction!                                                                                                       | ± [µsteps/64]<br>default = 0 (off) |  |  |  |

| RW    | 0x18                        | 70        | venc_us_<br>pos   | Actual encoder position (use for initialization of function – position must match selected <i>microstep_adr</i> bits)                                                                                                                                                                                          | [256 / electrical period]          |  |  |  |

| W     | 0x19                        | 98,<br>10 | venc_us_<br>sel   | bit 0,1: venc_microstep_resolution  00 = 2048 microsteps  01 = 1024 microsteps  10 = 256 microsteps  11 = 64 microsteps selects bits from microstep_adr (0x33) to match one electrical period  bit 8, 9: venc_phi_load_sel  00 = 90°  01 = 101,25°  10 = 112,5°  11 = 121,75° selects maximum motor load angle |                                    |  |  |  |

| 0x19: | 0x19: venc_us_sel - Vector Control Register |                       |           |                                                                                                                 |  |

|-------|---------------------------------------------|-----------------------|-----------|-----------------------------------------------------------------------------------------------------------------|--|

| R/W   | Bit                                         | Function              | Valu<br>e | Description                                                                                                     |  |

| W     | 1, 0                                        | venc_us_<br>sel       | 00        | 2048 microsteps: <i>microstep_adr</i> bits 12 downto 5 are used to determine angle within one electrical period |  |

|       |                                             |                       | 01        | 1024 microsteps: <i>microstep_adr</i> bits 11 downto 4 are used to determine angle within one electrical period |  |

|       |                                             |                       | 10        | 256 microsteps: <i>microstep_adr</i> bits 9 downto 2 are used to determine angle within one electrical period   |  |

|       |                                             |                       | 11        | 64 microsteps: <i>microstep_adr</i> bits 7 downto 0 are used to determine angle within one electrical period    |  |

|       | 9, 8                                        | venc_phi_<br>load_sel | 00        | vector encoder function load angle limit to<br>+/- 90° (64/256 of an electrical period) (max. torque)           |  |

|       |                                             |                       | 01        | +/- 101.25° (72/256 of an electrical period)                                                                    |  |

|       |                                             |                       | 10        | +/- 112,5° (80/256 of an electrical period)                                                                     |  |

|       |                                             |                       | 11        | +/- 123,75° (88/256 of an electrical period) (max. velocity)                                                    |  |

| PID R    | egister S | et - easyl       | PID™             |                                                                                                                                                                                                          |                                             |

|----------|-----------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| R/W      | Addr      | Bits             | Register         | Description                                                                                                                                                                                              | Range                                       |

| W        | 0x20      | 230              | pid_p            | P parameter (unsigned) update frequency f <sub>CLk</sub> /128; Result: pid_e*pid_p/256 (becomes clipped to +/-2^31)                                                                                      | (0: disable)                                |

| W        | 0x21      | 230              | pid_i            | I parameter (unsigned) Result: (pid_isum/256)*pid_i/256 (becomes clipped to +/-2^31)                                                                                                                     | (0: disable)                                |

| W        | 0x22      | 230              | pid_d            | D parameter (unsigned),  pid_e is sampled with a frequency of  (fclk[Hz]/128/pid_d_clkdiv).  Result: (pid_e_last-pid_e_now) * pid_d  (The delta-error (pid_e_last-pid_e_now)  becomes clipped to +/-127) | (0: disable)                                |

| W        | 0x23      | 140              | pid_iclip        | Clipping parameter for pid_isum Clipping of (pid_isum*2^16*pid_iclip)                                                                                                                                    | 0\$7F80                                     |

| R<br>W+C | 0x24      | 310              | pid_isum         | PID integrator sum (signed) Updated with f <sub>CLK</sub> [Hz]/128 Cleared to zero upon write access                                                                                                     | ±                                           |

| W        | 0x25      | 70               | pid_d_<br>clkdiv | Clock divider for D part calculation D-part is calculated with a frequency of: fclk / (pid_d_clkdiv*128) (Attention: pid_d_clkdiv=0 results in 256)                                                      | 1255, 0<br>= 1256                           |