# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **General Description**

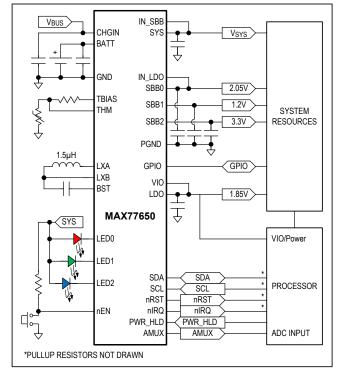

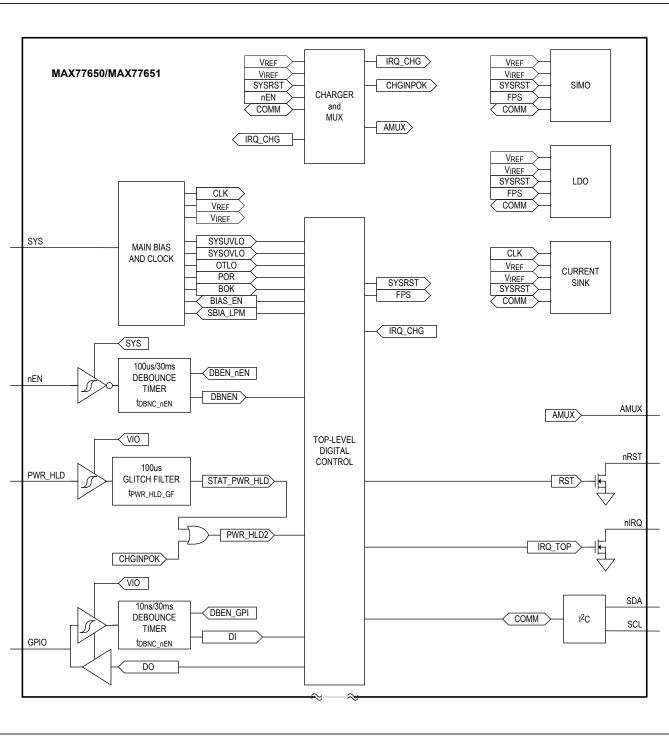

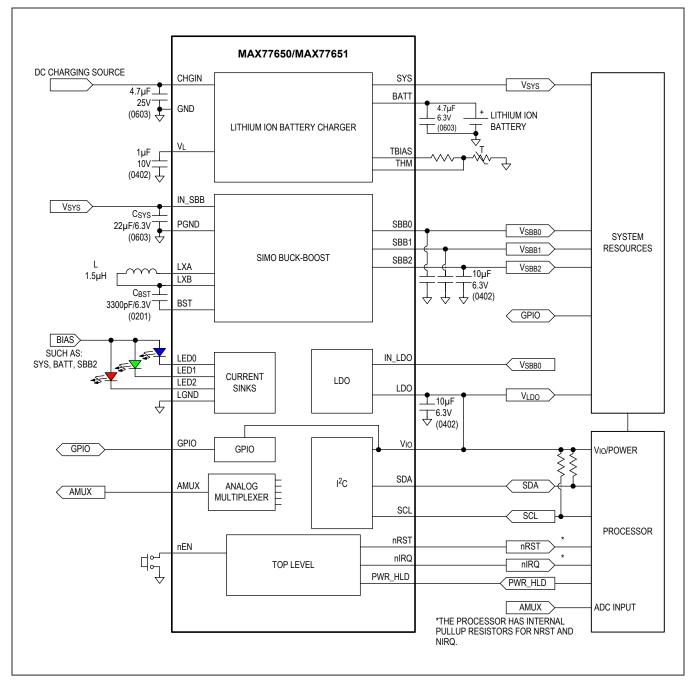

The MAX77650/MAX77651 provide highly-integrated battery charging and power supply solutions for low-power wearable applications where size and efficiency are critical. Both devices feature a SIMO buck-boost regulator that provides three independently programmable power rails from a single inductor to minimize total solution size. A 150mA LDO provides ripple rejection for audio and other noise-sensitive applications. A highly configurable linear charger supports a wide range of Li+ battery capacities and includes battery temperature monitoring for additional safety (JEITA).

The devices include other features such as current sinks for driving LED indicators and an analog multiplexer that switches several internal voltage and current signals to an external node for monitoring with an external ADC. A bidirectional I<sup>2</sup>C interface allows for configuring and checking the status of the devices. An internal on/off controller provides a controlled startup sequence for the regulators and provides supervisory functionality when the devices are on. Numerous factory programmable options allow the device to be tailored for many applications, enabling faster time to market.

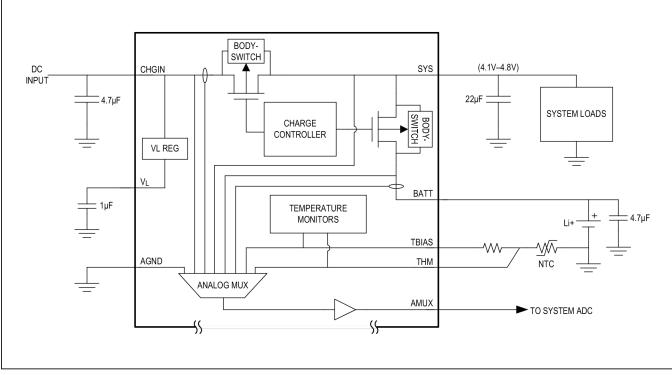

### **Simplified Application Circuit**

### **Benefits and Features**

- Highly Integrated

- Smart Power Selector™ Li+/Li-Poly Charger

- 3 Output, Single-Inductor Multiple-Output (SIMO) Buck-Boost Regulator

- 150mA LDO

- 3-Channel Current Sink Driver

- Analog MUX Output for Power Monitoring

- Low Power

- 0.3µA Shutdown Current

- 5.6µA Operating Current (3 SIMO Channels + LDO)

- Charger Optimized for Small Battery Size

- Programmable Fast-Charge Current from 7.5mA to 300mA

- Programmable Battery Regulation Voltage from 3.6V to 4.6V

- Programmable Termination Current from 0.375mA to 45mA

- JEITA Battery Temperature Monitors Adjust Charge Current and Battery Regulation Voltage for Safe Charging

- Flexible and Configurable

- I<sup>2</sup>C Compatible Interface and GPIO

- Factory OTP Options Available

- Small Size

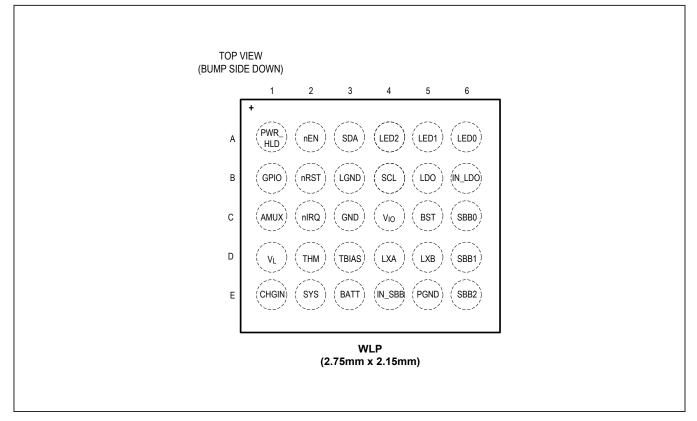

- 2.75mm x 2.15mm x 0.7mm WLP Package

- 30-Bump, 0.4mm-Pitch WLP, 6x5 Array

- Small Total Solution Size (19.2mm<sup>2</sup>)

### **Applications**

- Bluetooth Headphones/Hearables

- Fitness, Health, and Activity Monitors

- Portable Devices

- Internet of Things (IoT)

### Ordering Information appears at end of data sheet.

Smart Power Selector is a trademark of Maxim Integrated Products, Inc.

### Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Benefits and Features** ...... Applications ..... Simplified System Diagram . . 1 Absolute Maximum Ratings ..... Package Information . 7 Electrical Characteristics—Global Resources..... 10 Electrical Characteristics—Smart Power Selector Charger ..... 12 Electrical Characteristics—Analog Multiplexer and Power Monitor AFEs. Electrical Characteristics—SIMO Buck-Boost. 17 Electrical Characteristics—LDO 19 Electrical Characteristics—Current Sinks ..... 21 Electrical Characteristics—I<sup>2</sup>C Serial Interface..... 22 Typical Operating Characteristics 25 Pin Configuration ..... 34 Pin Description ..... 34 Detailed Description..... 36 Support Materials . . Top-Level Interconnect Simplified Diagram ..... 36 Global Resources..... 38 SYS Undervoltage Lockout Comparator ..... 38 SYS Overvoltage Lockout Comparator ..... 38 nEN Enable Input ..... 38 39 On/Off Controller. 42 Smart Power Selector Charger 50

### **TABLE OF CONTENTS**

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

| TABLE OF CONTENTS (CONTINUED)              |    |

|--------------------------------------------|----|

| Features                                   | 50 |

| Charger Symbol Reference Guide             | 51 |

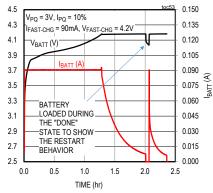

| Smart Power Selector                       | 52 |

| Input Current Limiter                      | 52 |

| Minimum Input Voltage Regulation           | 52 |

| Minimum System Voltage Regulation          | 52 |

| Die Temperature Regulation                 | 52 |

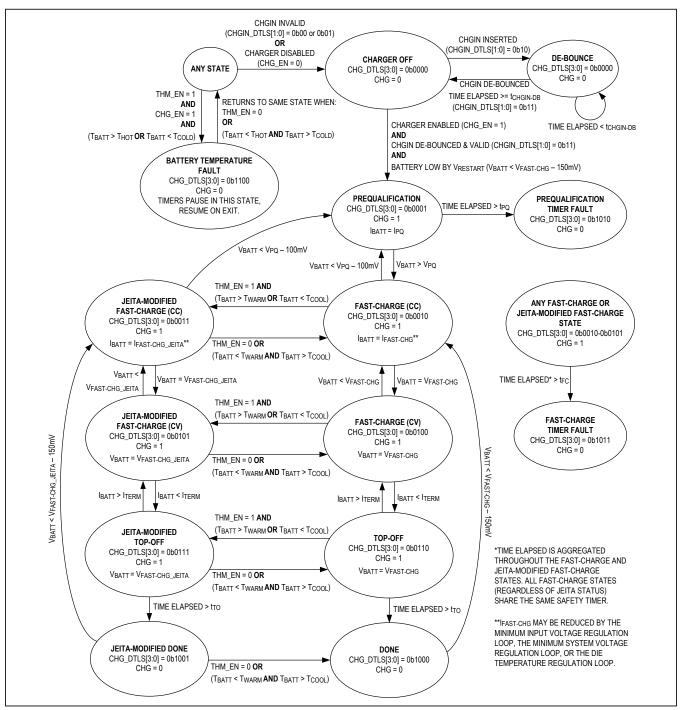

| Charger State Machine                      | 53 |

| Charger Off State                          | 54 |

| Prequalification State                     | 54 |

| Fast-Charge States                         | 54 |

| Top-Off State                              | 54 |

| Done State                                 | 54 |

| Prequalification Timer Fault State         | 54 |

| Fast-Charge Timer Fault State              | 55 |

| Battery Temperature Fault State            | 55 |

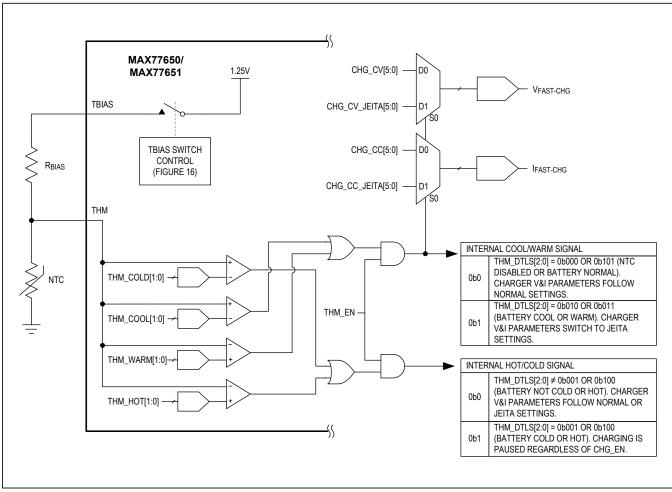

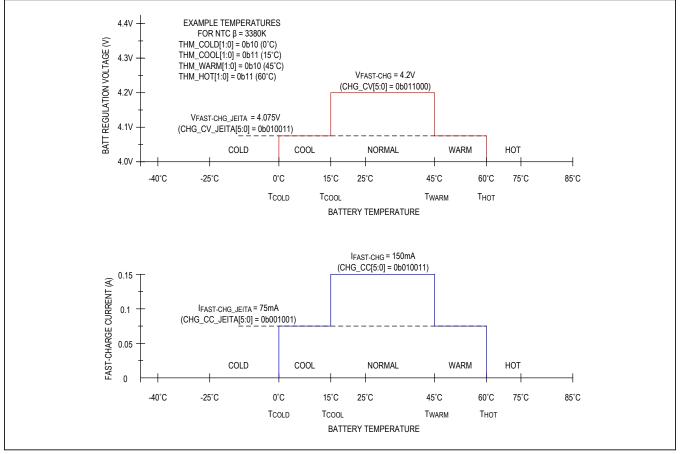

| JEITA-Modified States                      | 55 |

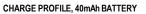

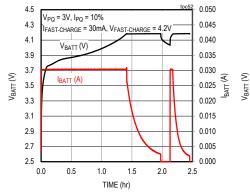

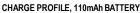

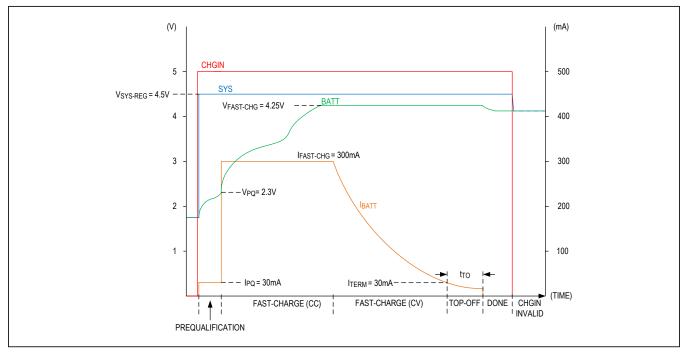

| Typical Charge Profile                     | 55 |

| Charger Applications Information           | 56 |

| Configuring a Valid System Voltage         | 56 |

| CHGIN/SYS/BATT Capacitor Selection.        | 56 |

| Adjustable Thermistor Temperature Monitors |    |

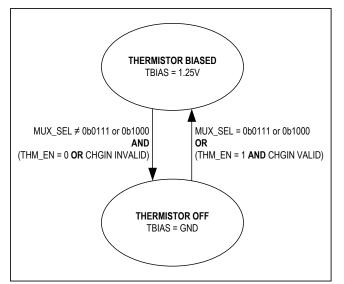

| Thermistor Bias                            | 59 |

| Configurable Temperature Thresholds        | 59 |

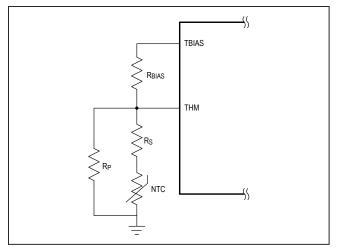

| Thermistor Applications Information        | 60 |

| Using Different Thermistor $\beta$         |    |

| NTC Thermistor Selection                   |    |

| Analog Multiplexer & Power Monitor AFEs    |    |

| Measuring Battery Current                  |    |

| Method for Measuring Discharging Current   |    |

| Method for Measuring Charging Current      | 62 |

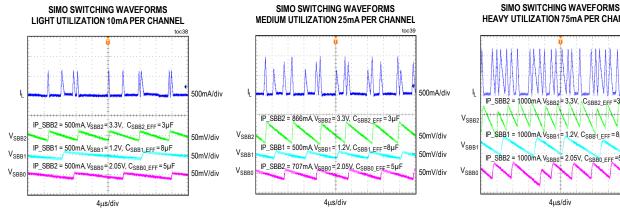

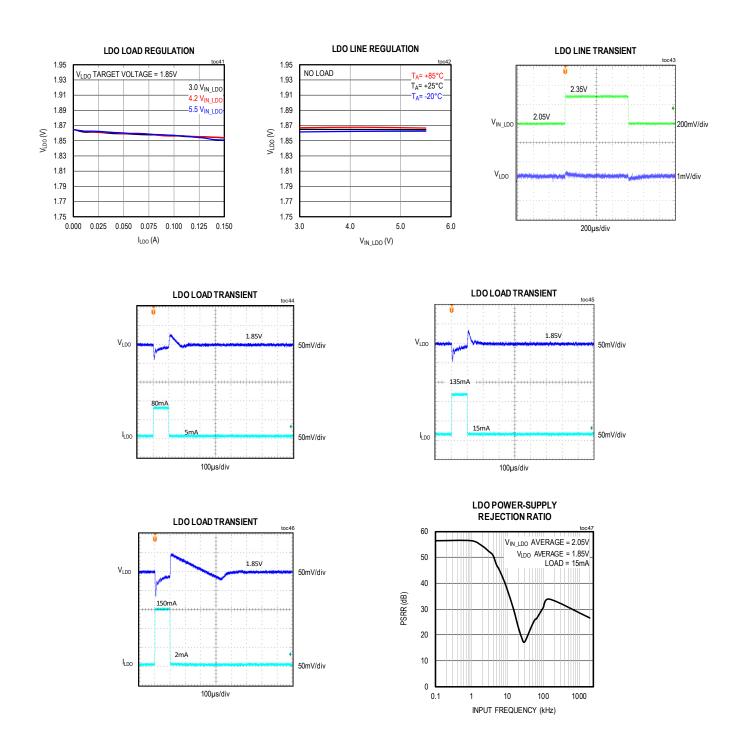

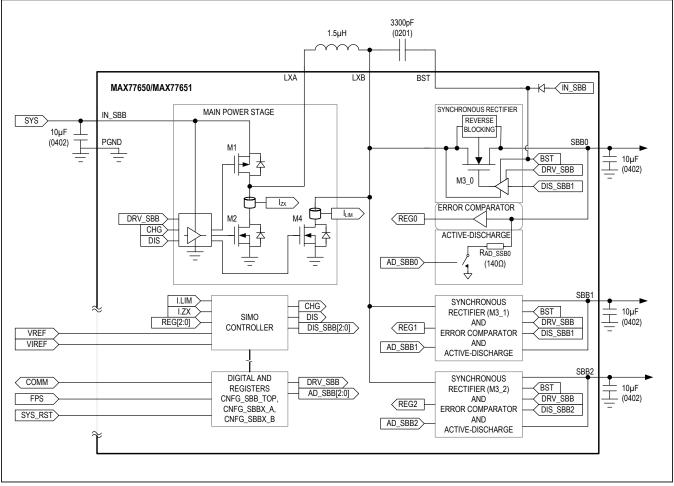

| SIMO Buck-Boost.                           |    |

| SIMO Benefits and Features                 |    |

| SIMO Control Scheme                        |    |

| SIMO Soft-Start                            | 64 |

| SIMO Registers.                            |    |

| SIMO Active Discharge Resistance           |    |

| SIMO Applications Information              |    |

| SIMO Available Output Current              | 65 |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

| TABLE OF CONTENTS (CONTINUED)                  |

|------------------------------------------------|

| Inductor Selection                             |

| Input Capacitor Selection                      |

| Boost Capacitor Selection                      |

| Output Capacitor Selection                     |

| SIMO Switching Frequency                       |

| Unused Outputs                                 |

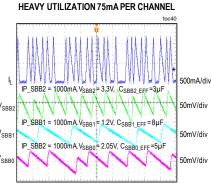

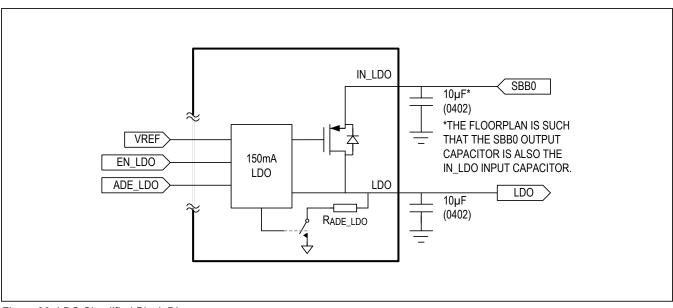

| LDO                                            |

| Features                                       |

| LDO Simplified Block Diagram                   |

| LDO Active Discharge Resistor                  |

| LDO Soft-Start                                 |

| LDO Applications Information                   |

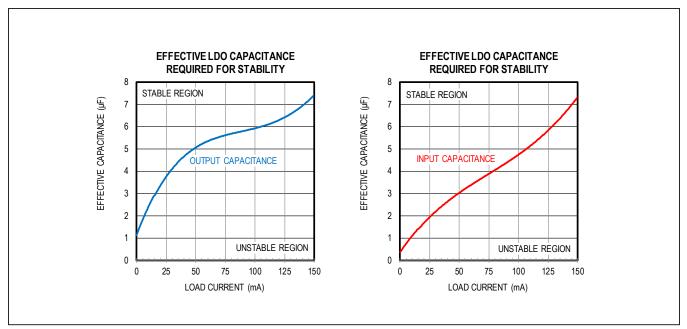

| Input and Output Capacitor Selection           |

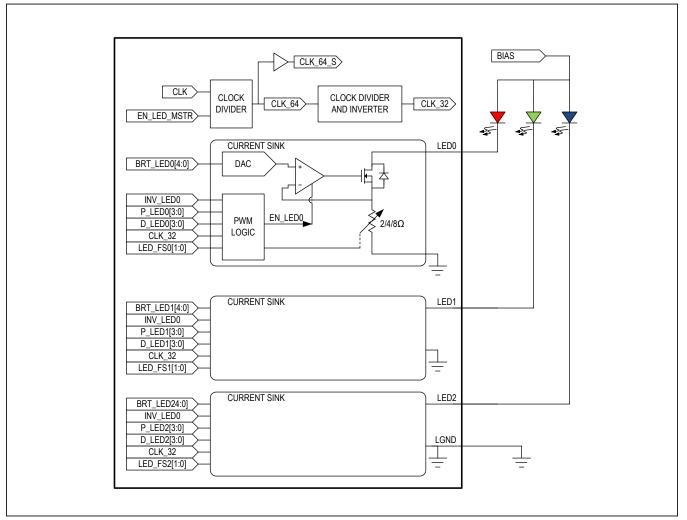

| Current Sinks                                  |

| Current Sink Applications Information          |

| LED Assignment                                 |

| Unused Current Sink Ports                      |

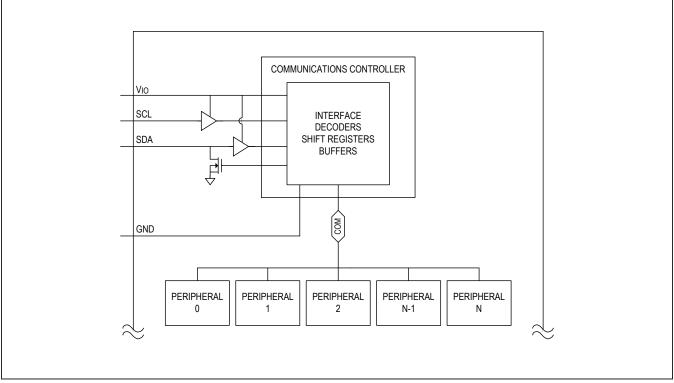

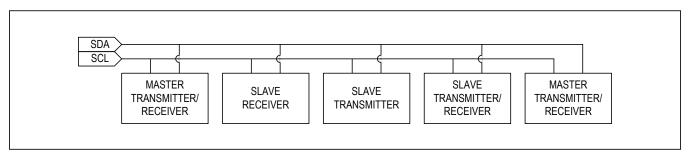

| I <sup>2</sup> C Serial Interface              |

| I <sup>2</sup> C System Configuration          |

| I <sup>2</sup> C Interface Power               |

| I <sup>2</sup> C Data Transfer                 |

| I <sup>2</sup> C Start and Stop Conditions     |

| I <sup>2</sup> C Acknowledge Bit               |

| I <sup>2</sup> C Slave Address                 |

| I <sup>2</sup> C Clock Stretching              |

| I <sup>2</sup> C General Call Address          |

| I <sup>2</sup> C Device ID                     |

| I <sup>2</sup> C Communication Speed           |

| I <sup>2</sup> C Communication Protocols       |

| Writing to a Single Register                   |

| Writing Multiple Bytes to Sequential Registers |

| Reading from a Single Register                 |

| Reading from Sequential Registers              |

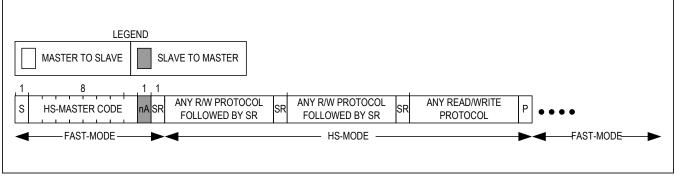

| Engaging HS-mode for operation up to 3.4MHz78  |

| Typical Application Circuit                    |

| Ordering Information                           |

| Revision History                               |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

| Figure 1. Top-Level Interconnect Simplified Diagram                        | 37 |

|----------------------------------------------------------------------------|----|

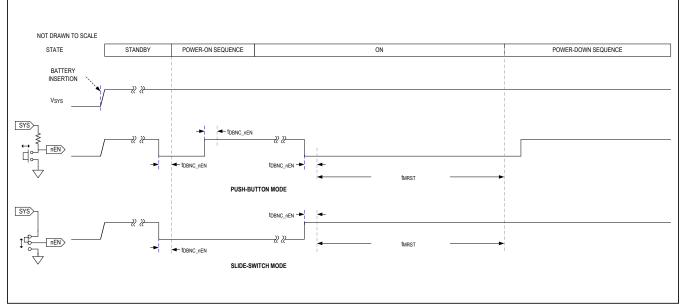

| Figure 2. nEN Usage Timing Diagram                                         | 39 |

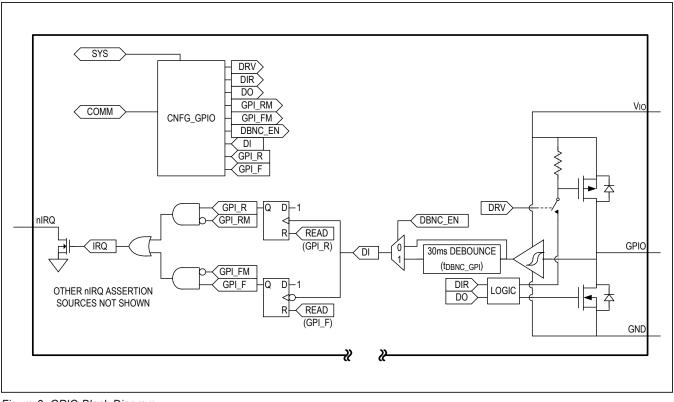

| Figure 3. GPIO Block Diagram                                               | 41 |

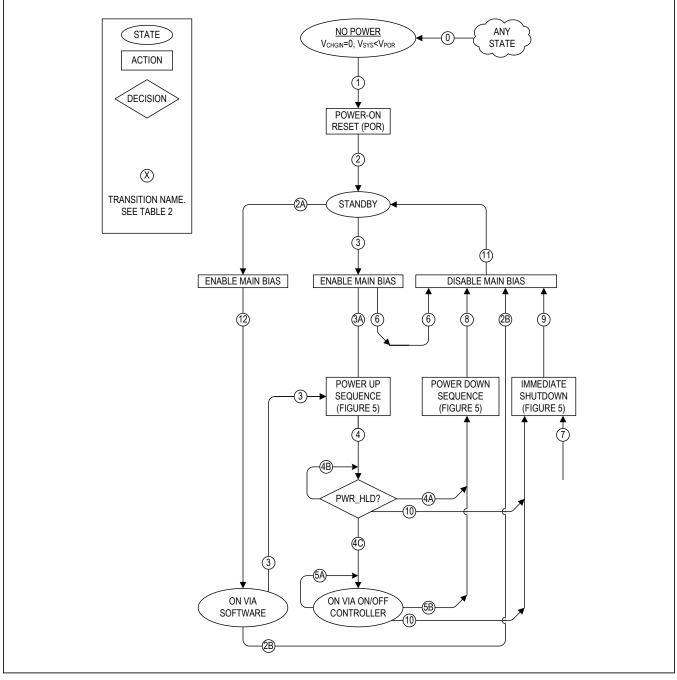

| Figure 4. Top-Level On/Off Controller                                      | 43 |

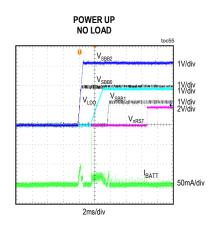

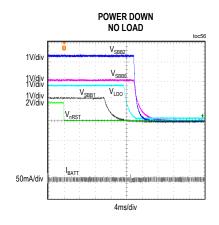

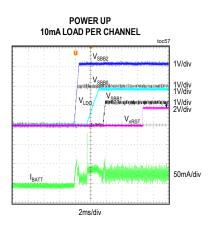

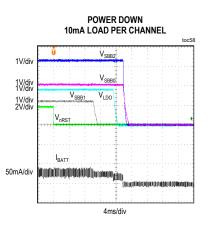

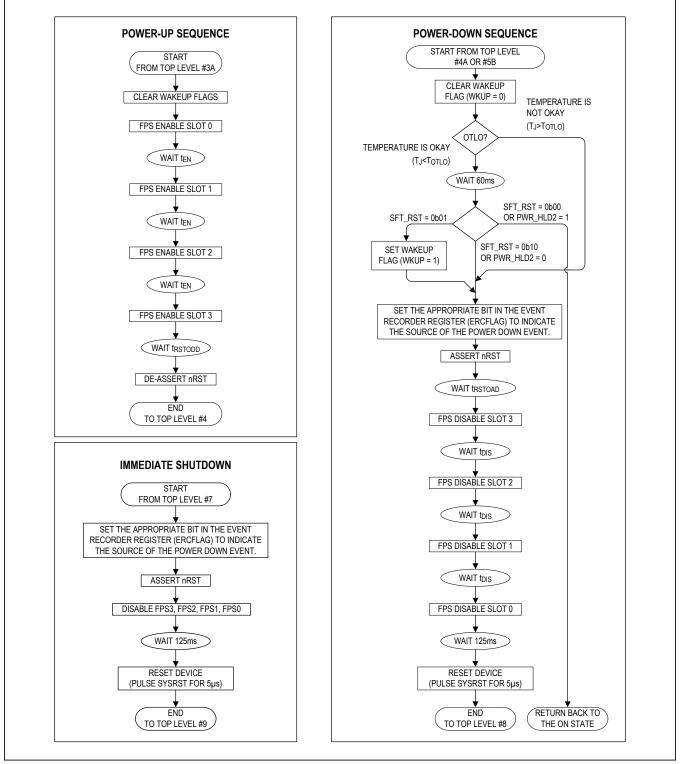

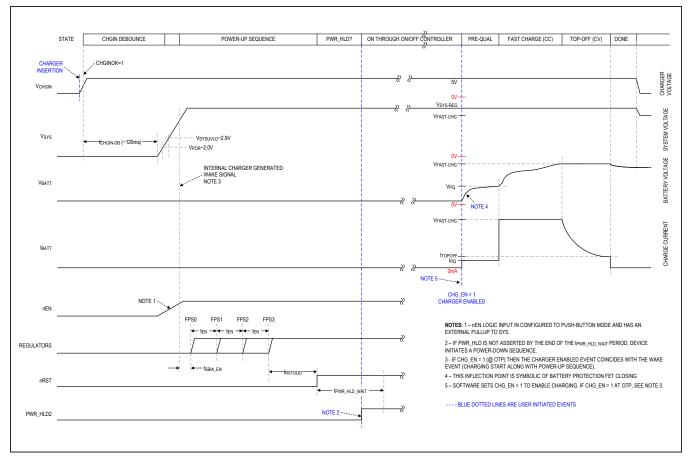

| Figure 5. Power-Up/Power-Down Sequence                                     | 45 |

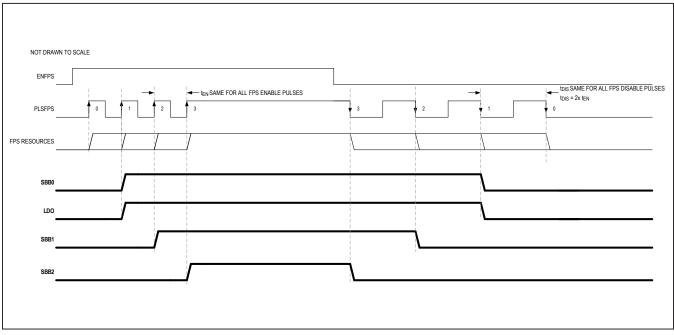

| Figure 6. Flexible Power Sequencer Basic Timing Diagram                    | 46 |

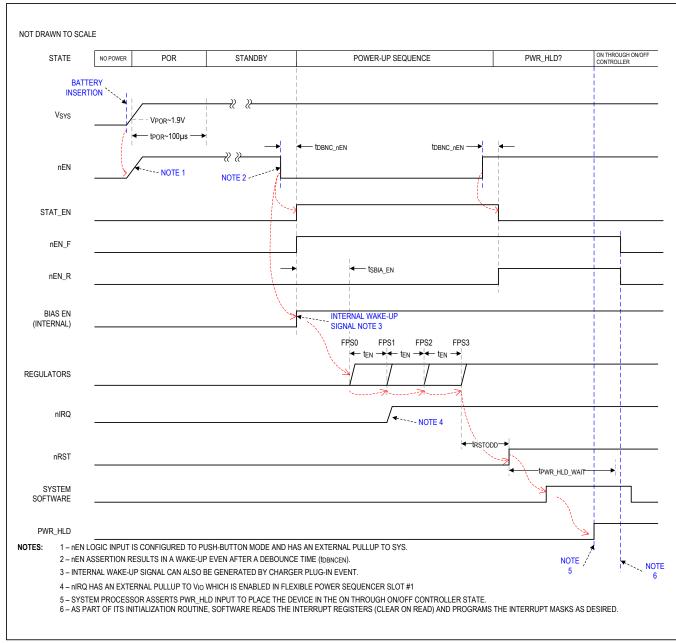

| Figure 7. Startup Timing Diagram Due to nEN                                | 47 |

| Figure 8. Startup Timing Diagram Due to Charge Source Insertion            | 48 |

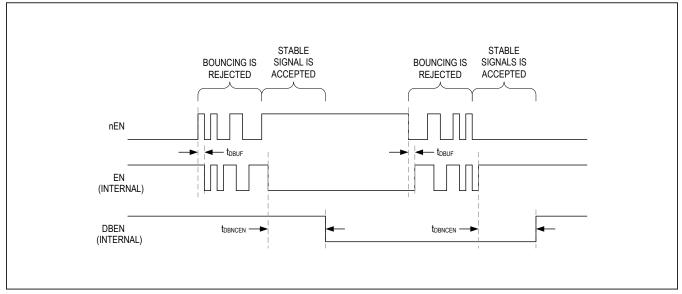

| Figure 9. Debounced Inputs.                                                | 49 |

| Figure 10. Linear Charger Simplified Block Diagram                         | 50 |

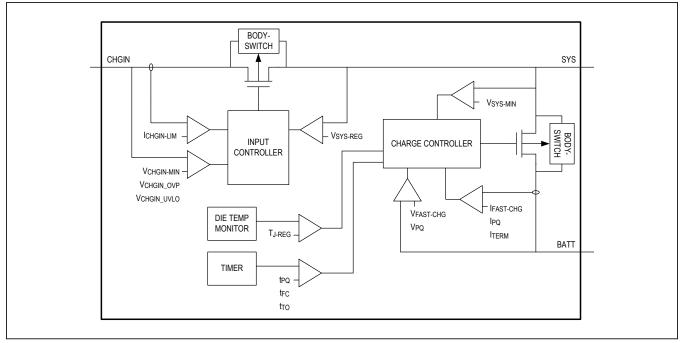

| Figure 11. Charger Simplified Control Loops                                | 51 |

| Figure 12. Charger State Diagram                                           | 53 |

| Figure 13. Example Battery Charge Profile                                  | 55 |

| Figure 14. Thermistor Logic Functional Diagram                             | 57 |

| Figure 15. Safe-Charging Profile Example                                   | 58 |

| Figure 16. Thermistor Bias State Diagram                                   | 59 |

| Figure 17. Thermistor Circuit with Adjusting Series and Parallel Resistors | 60 |

| Figure 18. SIMO Detailed Block Diagram                                     | 63 |

| Figure 19. LDO Capacitance for Stability                                   | 69 |

| Figure 20. LDO Simplified Block Diagram                                    | 69 |

| Figure 21. Current Sink Block Diagram                                      | 70 |

| Figure 22. I <sup>2</sup> C Simplified Block Diagram                       | 71 |

| Figure 23. I <sup>2</sup> C System Configuration                           | 72 |

| Figure 24. I <sup>2</sup> C Start and Stop Conditions                      | 72 |

| Figure 25. Acknowledge Bit                                                 | 73 |

| Figure 26. Slave Address Example                                           | 73 |

| Figure 27. Writing to a Single Register with the Write Byte Protocol.      | 75 |

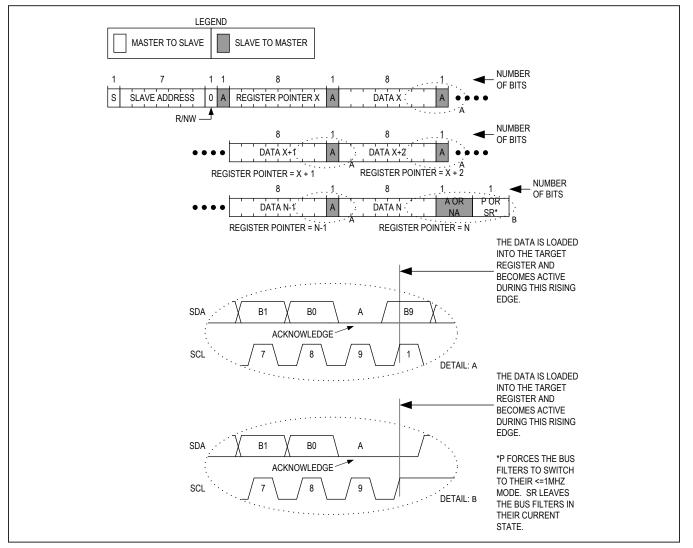

| Figure 28. Writing to Sequential registers X to N                          | 76 |

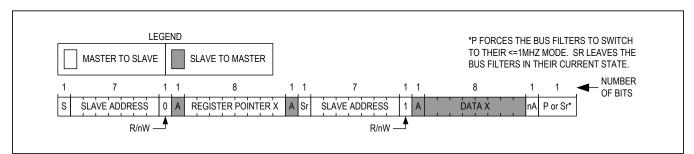

| Figure 29. Reading from a Single Register with the Read Byte Protocol      | 77 |

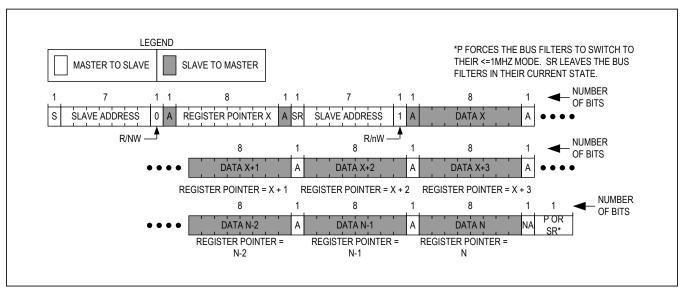

| Figure 30. Reading Continuously from Sequential Registers X to N           | 77 |

| Figure 31. Engaging HS Mode                                                | 78 |

### LIST OF FIGURES

### Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

# Table 1. Regulator Summary 36 Table 2. On/Off Controller Transition/State 44 Table 3. Charger Quick Symbol Reference Guide. 51 Table 4. Trip Temperatures vs. Trip Voltages for Different NTC β. 59 Table 5. Example RS and Rp Correcting Values for NTC β Above 3380K 60 Table 6. NTC Thermistors 60 Table 7. AMUX Signal Transfer Functions 61 Table 8. Battery Current Direction Decode 62 Table 9. SIMO Available Output Current for Common Applications 65 Table 10. Example Inductors 65 Table 11. I<sup>2</sup>C Slave Address Options 74

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Absolute Maximum Ratings**

| nEN, PWR_HLD, nIRQ, nRST to GND0.3V to V <sub>SYS</sub> + 0.3V | IN_SBB to PGND0.3V to +6.0V                                  |

|----------------------------------------------------------------|--------------------------------------------------------------|

| SCL, SDA, GPIO to GND0.3V to V <sub>IO</sub> + 0.3V            | LXA Continuous Current (Note 3)1.2A <sub>RMS</sub>           |

| CHGIN to GND0.3V to +30.0V                                     | LXB Continuous Current (Note 4)1.2A <sub>RMS</sub>           |

| SYS, BATT to GND0.3V to +6.0V                                  | SBB0, SBB1, SBB2 to PGND (Note 2)0.3V to +6.0V               |

| SYS to IN_SBB0.3V to +0.3V                                     | BST to IN_SBB0.3V to +6.0V                                   |

| V <sub>L</sub> to GND0.3V to +6.0V                             | BST to LXB0.3V to +6.0V                                      |

| AMUX, THM, TBIAS to GND0.3V to +6.0V                           | SBB0, SBB1, SBB2 Short-Circuit DurationContinuous            |

| nIRQ, nRST, SDA, AMUX, GPIO Continous Current±20mA             | PGND to GND0.3V to +0.3V                                     |

| CHGIN Continuous Current1.2A <sub>RMS</sub>                    | LGND to GND0.3V to +0.3V                                     |

| SYS Continuous Current1.2A <sub>RMS</sub>                      | Operating Temperature Range40°C to +85°C                     |

| BATT Continuous Current (Note 1)1.2A <sub>RMS</sub>            | Junction Temperature+150°C                                   |

| LDO to GND (Note 2)0.3V to V <sub>IN LDO</sub> + 0.3V          | Storage Temperature Range65°C to +150°C                      |

| IN_LDO, V <sub>IO</sub> to GND0.3V to the lower of             | Soldering Temperature (reflow)+260°C                         |

| (V <sub>SYS</sub> + 0.3V) and +6.0V                            | Continuous Power Dissipation (Multilayer Board)              |

| LED0, LED1, LED2 to LGND0.3V to +6.0V                          | (T <sub>A</sub> = +70°C, derate 20.4mW/°C above +70°C)1632mW |

**Note 1:** Do not repeatedly hot-plug a source to the BATT terminal at a rate greater than 10Hz. Hot plugging low-impedance sources results in an ~8A momentary (~2µs) current spike.

- Note 2: When the active discharge resistor is engaged, limit its power dissipation to an average of 10mW.

- Note 3: LXA has internal clamping diodes to PGND and IN\_SBB. It is normal for these diodes to briefly conduct during switching events. Avoid steady-state conduction of these diodes.

- **Note 4:** Do not externally bias LXB. LXB has an internal low-side clamping diode to PGND, and an internal high-side clamping diode that dynamically shifts to the selected SIMO output. It is normal for these internal clamping diodes to briefly conduct during switching events. When the SIMO regulator is disabled, the LXB to PGND absolute maximum voltage is -0.3V to V<sub>SBB0</sub> + 0.3V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

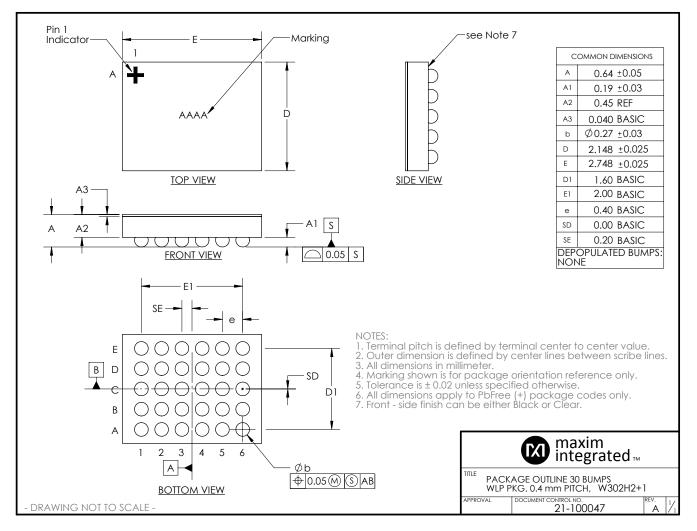

### **Package Information**

| PACKAGE CHARACTERISTICS                | VALUES                         |

|----------------------------------------|--------------------------------|

| Package Code                           | W302H2+1                       |

| Outline Number                         | <u>21-100047</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 49°C/W (2s2p board)            |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

# Package Information (continued)

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Top Level**

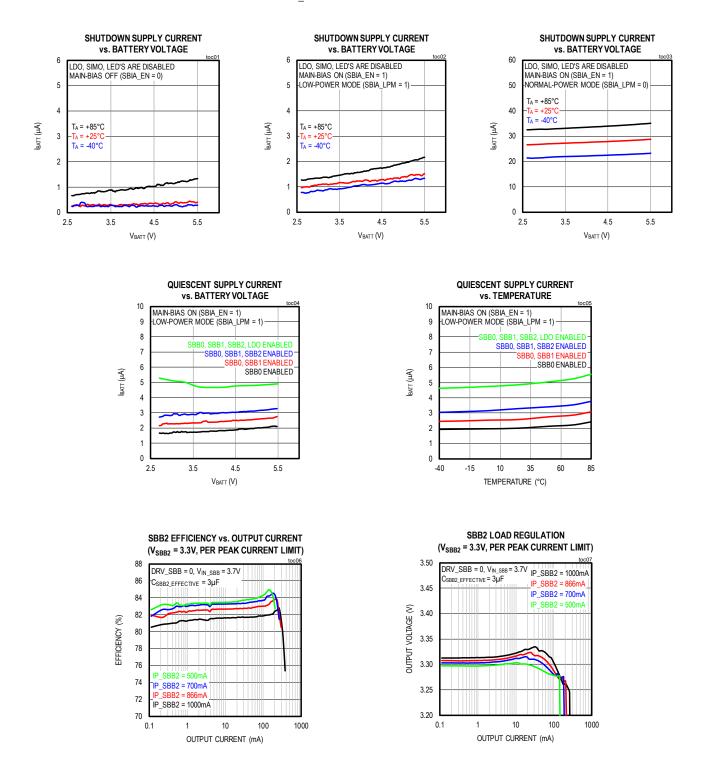

$(V_{CHGIN} = 0V, V_{SYS} = V_{BATT} = V_{IN\_SBB} = V_{IN\_LDO} = 3.7V, V_{IO} = 1.8V$ , limits are 100% production tested at  $T_A = +25^{\circ}C$ , limits over the operating temperature range ( $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                                                                     | SYMBOL                                            | COND                                                                      | ITIONS                                                                 | MIN | ТҮР | MAX | UNITS |

|-----------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----|-------|

| Operating Voltage<br>Range                                                                    | V <sub>SYS</sub>                                  |                                                                           |                                                                        | 2.7 |     | 5.5 | V     |

| Shutdown Supply<br>Current                                                                    |                                                   | Current measured                                                          | Main bias is off<br>(SBIA_EN = 0). This<br>is the standby state        |     | 0.3 | 1   |       |

|                                                                                               | I <sub>SHDN</sub>                                 | SHDN IN_LDO, all Io<br>resources are off (S<br>(LDO, SBB0, SBB1, S        | Main bias is on in<br>low-power mode<br>(SBIA_EN = 1,<br>SBIA_LPM = 1) |     | 1   |     | μΑ    |

|                                                                                               | SBB2, LED0, LED1,<br>LED2), T <sub>A</sub> = 25°C | Main bias is on in<br>normal-power mode<br>(SBIA_EN = 1,<br>SBIA_LPM = 0) |                                                                        | 28  |     |     |       |

| Quiescent Supply<br>Current IQ IQ IQ SBB0, SBB1, and<br>SBB2 are enabled<br>with no load. LED | IN_LDO. LDO,                                      | Main bias is in<br>low-power mode<br>(SBIA_LPM = 1)                       |                                                                        | 5.6 | 13  |     |       |

|                                                                                               | IQ                                                | SBB2 are enabled<br>with no load. LED0,<br>LED1, and LED2                 | Main bias is in<br>normal-power mode<br>(SBIA_LPM = 0)                 |     | 40  | 60  | - μΑ  |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Global Resources**

(V<sub>SYS</sub> = 3.7V, limits are 100% production tested at  $T_A$  = +25°C, limits over the operating temperature range ( $T_A$  = -40°C to +85°C) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                               | SYMBOL               | CONDI                                       | TIONS                  | MIN  | TYP    | MAX  | UNITS |

|-----------------------------------------|----------------------|---------------------------------------------|------------------------|------|--------|------|-------|

| POWER-ON RESET (PO                      | R)                   |                                             |                        |      |        |      |       |

| POR Threshold                           | V <sub>POR</sub>     | V <sub>SYS</sub> falling                    |                        | 1.6  | 1.9    | 2.1  | V     |

| POR Threshold<br>Hysteresis             |                      |                                             |                        |      | 100    |      | mV    |

| UNDERVOLTAGE LOCK                       | OUT (UVLO)           |                                             |                        | ·    |        |      |       |

| UVLO Threshold                          |                      | V <sub>SYS</sub> falling, UVLO_F            | [3:0] = 0xA            | 2.5  | 2.6    | 2.7  | V     |

| OVEO THreshold                          | V <sub>SYSUVLO</sub> | V <sub>SYS</sub> falling, UVLO_F            | [3:0] = 0xF            | 2.75 | 2.85   | 2.95 | - V   |

| UVLO Threshold<br>Hysteresis            | VSYSUVLO_HYS         | UVLO_H[3:0] = 0x5                           |                        |      | 300    |      | mV    |

| OVERVOLTAGE LOCKO                       | OUT (OVLO)           |                                             |                        | ·    |        |      |       |

| OVLO Threshold                          | VSYSOVLO             | V <sub>SYS</sub> rising                     |                        | 5.70 | 5.85   | 6.00 | V     |

| THERMAL MONITORS                        |                      |                                             |                        |      |        |      |       |

| Overtemperature<br>Lockout Threshold    | T <sub>OTLO</sub>    | T <sub>J</sub> rising                       |                        |      | 165    |      | °C    |

| Thermal Alarm<br>Temperature 1          | T <sub>JAL1</sub>    | T <sub>J</sub> rising                       |                        |      | 80     |      | °C    |

| Thermal Alarm<br>Temperature 2          | T <sub>JAL2</sub>    | T <sub>J</sub> rising                       | T <sub>J</sub> rising  |      | 100    |      | °C    |

| Thermal Alarm<br>Temperature Hysteresis |                      |                                             |                        |      | 15     |      | °C    |

| ENABLE INPUT (nEN)                      |                      | ·                                           |                        |      |        |      |       |

| nEN Input Leakage                       |                      | V <sub>SYS</sub> = 5.5V, V <sub>nEN</sub> = | T <sub>A</sub> = +25°C | -1   | ±0.001 | +1   | - μΑ  |

| Current                                 | InEN_LKG 0V, and 5.5 | 0V, and 5.5V                                | T <sub>A</sub> = +85°C |      | ±0.01  |      |       |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Global Resources (continued)**

(V<sub>SYS</sub> = 3.7V, limits are 100% production tested at  $T_A$  = +25°C, limits over the operating temperature range ( $T_A$  = -40°C to +85°C) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                      | SYMBOL                                                                                                               | COND                                                                                             | ITIONS                 | MIN                       | TYP                       | MAX                       | UNITS |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------|---------------------------|---------------------------|---------------------------|-------|

| nEN Input Falling<br>Threshold | V <sub>TH_nEN_F</sub>                                                                                                | nEN falling                                                                                      |                        | V <sub>SYS</sub><br>- 1.4 | V <sub>SYS</sub><br>- 1.0 |                           | V     |

| nEN Input Rising<br>Threshold  | V <sub>TH_nEN_F</sub>                                                                                                | nEN falling                                                                                      |                        |                           | V <sub>SYS</sub><br>- 0.9 | V <sub>SYS</sub><br>- 0.6 | V     |

| Dehaumaa Tima                  | 1                                                                                                                    | DBEN_nEN = 0                                                                                     |                        |                           | 100                       |                           | μs    |

| Debounce Time                  | <sup>t</sup> DBNC_nEN                                                                                                | DBEN_nEN = 1                                                                                     |                        |                           | 30                        |                           | ms    |

| Manual Data A Tina             | 1                                                                                                                    | MRT_OTP = 0                                                                                      |                        | 14                        | 16                        | 20                        |       |

| Manual Reset Time              | <sup>t</sup> MRST                                                                                                    | MRT_OTP = 1                                                                                      |                        | 7                         | 8                         | 10.5                      | S     |

| POWER HOLD INPUT (P            | WR_HLD)                                                                                                              |                                                                                                  |                        |                           |                           |                           |       |

| PWR_HLD Input                  | IPWR_HLD_LKG                                                                                                         | V <sub>SYS</sub> = V <sub>IO</sub> = 5.5V,<br>V <sub>PWR HLD</sub> = 0V,                         | T <sub>A</sub> = +25°C | -1                        | ±0.001                    | +1                        | -μA   |

| Leakage Current                |                                                                                                                      | and 5.5V                                                                                         | T <sub>A</sub> = +85°C |                           | ±0.01                     |                           | μ, τ  |

| PWR_HLD Input<br>Voltage Low   | VIL                                                                                                                  | V <sub>IO</sub> = 1.8V                                                                           |                        |                           |                           | 0.3 x<br>V <sub>IO</sub>  | V     |

| PWR_HLD Input<br>Voltage High  | V <sub>IH</sub>                                                                                                      | V <sub>IO</sub> = 1.8V                                                                           |                        | 0.7 x<br>V <sub>IO</sub>  |                           |                           | V     |

| PWR_HLD Input<br>Hysteresis    | V <sub>HYS</sub>                                                                                                     | V <sub>IO</sub> = 1.8V                                                                           |                        |                           | 50                        |                           | mV    |

| PWR_HLD Glitch Filter          | <sup>t</sup> PWR_HLD_GF                                                                                              | Both rising and falling edges are filtered                                                       |                        |                           | 100                       |                           | μs    |

| PWR_HLD Wait Time              | <sup>t</sup> PWR_HLD_WAIT                                                                                            | Maximum time for PWR_HLD input to assert<br>after nRST deasserts during the power-up<br>sequence |                        | 3.5                       | 4.0                       | 5.0                       | S     |

| OPEN-DRAIN INTERRU             | PT OUTPUT (nIRQ                                                                                                      | !)                                                                                               |                        |                           |                           |                           | ·     |

| Output Voltage Low             | V <sub>OL</sub>                                                                                                      | I <sub>SINK</sub> = 2mA                                                                          |                        |                           |                           | 0.4                       | V     |

| Output Falling Edge<br>Time    | <sup>t</sup> f_nIRQ                                                                                                  | C <sub>IRQ</sub> = 25pF                                                                          |                        |                           | 2                         |                           | ns    |

|                                |                                                                                                                      | $V_{SYS} = V_{IO} = 5.5V$ ,<br>nIRQ set to be high                                               | T <sub>A</sub> = +25°C | -1                        | ±0.001                    | +1                        |       |

| Leakage Current                | I <sub>nIRQ_LKG</sub>                                                                                                | impedance (i.e., no<br>interrupts), VnIRQ =<br>0V and 5.5V                                       | T <sub>A</sub> = +85°C |                           | ±0.01                     |                           | μA    |

| OPEN-DRAIN RESET OU            | JTPUT (nRST)                                                                                                         | ·                                                                                                |                        |                           |                           |                           |       |

| Output Voltage Low             | V <sub>OL</sub>                                                                                                      | I <sub>SINK</sub> = 2mA                                                                          |                        |                           |                           | 0.4                       | V     |

| Output Falling Edge<br>Time    | <sup>t</sup> f_nRST                                                                                                  | C <sub>RST</sub> = 25pF                                                                          |                        |                           | 2                         |                           | ns    |

| nRST Deassert Delay<br>Time    | <sup>t</sup> RSTODD                                                                                                  | See <u>Figure 5</u> and <u>Figure 7</u> for more information                                     |                        |                           | 5.12                      |                           | ms    |

| nRST Assert Delay Time         | t <sub>RSTOAD</sub>                                                                                                  | See Figure 5 for more                                                                            | information            |                           | 10.24                     |                           | ms    |

|                                | $V_{SYS} = V_{IO} = 5.5V,$ nRST set to be high<br>impedance (i.e., not<br>reset), V <sub>nRST</sub> = 0V<br>and 5.5V | nRST set to be high                                                                              | T <sub>A</sub> = +25°C | -1                        | ±0.001                    | +1                        |       |

|                                |                                                                                                                      | T <sub>A</sub> = +85°C                                                                           |                        | ±0.01                     |                           | μA                        |       |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Global Resources (continued)**

(V<sub>SYS</sub> = 3.7V, limits are 100% production tested at  $T_A$  = +25°C, limits over the operating temperature range ( $T_A$  = -40°C to +85°C) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                   | SYMBOL                | CONDITIONS                |                          | MIN                      | ТҮР    | MAX                      | UNITS |

|-----------------------------|-----------------------|---------------------------|--------------------------|--------------------------|--------|--------------------------|-------|

| GENERAL-PURPOSE IN          | PUT/OUTPUT (G         | PIO)                      |                          |                          |        |                          |       |

| Input Voltage Low           | V <sub>IL</sub>       | V <sub>IO</sub> = 1.8V    |                          |                          |        | 0.3 x<br>V <sub>IO</sub> | V     |

| Input Voltage High          | V <sub>IH</sub>       | V <sub>IO</sub> = 1.8V    | V <sub>IO</sub> = 1.8V   |                          |        |                          | V     |

|                             |                       | $V_{CDIO} = 0V$ and       | T <sub>A</sub> = +25°C   | -1                       | ±0.001 | +1                       |       |

| Input Leakage Current       | IGPI_LKG              |                           | T <sub>A</sub> = +85°C   |                          | ±0.01  |                          | μA    |

| Output Voltage Low          | V <sub>OL</sub>       | I <sub>SINK</sub> = 2mA   |                          |                          |        | 0.4                      | V     |

| Output Voltage High         | V <sub>OH</sub>       | I <sub>SOURCE</sub> = 1mA |                          | 0.8 x<br>V <sub>IO</sub> |        |                          | V     |

| Input Debounce Time         | <sup>t</sup> DBNC_GPI | DBEN_GPI = 1              |                          |                          | 30     |                          | ms    |

| Output Falling Edge<br>Time | t <sub>f_</sub> GPIO  | C <sub>GPIO</sub> = 25pF  |                          |                          | 3      |                          | ns    |

| Output Rising Edge<br>Time  | <sup>t</sup> r_GPIO   | C <sub>GPIO</sub> = 25pF  | C <sub>GPIO</sub> = 25pF |                          | 3      |                          | ns    |

| FLEXIBLE POWER SEQU         | JENCER                | ·                         |                          | ·                        |        |                          |       |

| Power-Up Event Periods      | t <sub>EN</sub>       | See Figure 6              |                          |                          | 1.28   |                          | ms    |

| Power-Down Event<br>Periods | t <sub>DIS</sub>      | See Figure 6              |                          |                          | 2.56   |                          | ms    |

### **Electrical Characteristics—Smart Power Selector Charger**

| PARAMETER                                | SYMBOL                 | CONDITIONS                                                                     | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|------------------------|--------------------------------------------------------------------------------|------|------|------|-------|

| DC INPUT                                 |                        |                                                                                |      |      |      |       |

| CHGIN Valid Voltage<br>Range             | V <sub>CHGIN</sub>     | Initial CHGIN voltage before enabling<br>charging                              | 4.10 |      | 7.25 | V     |

| CHGIN Standoff Voltage<br>Range          | V <sub>STANDOFF</sub>  | DC rising                                                                      |      | 28   |      | V     |

| CHGIN Overvoltage<br>Threshold           | V <sub>CHGIN_OVP</sub> | DC rising                                                                      | 7.25 | 7.50 | 7.75 | V     |

| CHGIN Overvoltage<br>Hysteresis          |                        |                                                                                |      | 100  |      | mV    |

| CHGIN Undervoltage<br>Lockout            | VCHGIN_UVLO            | DC rising                                                                      | 3.9  | 4.0  | 4.1  | V     |

| CHGIN Undervoltage<br>Lockout Hysteresis |                        |                                                                                |      | 500  |      | mV    |

| Input Current Limit<br>Range             | I <sub>CHGIN-LIM</sub> | V <sub>SYS</sub> = V <sub>SYS-REG</sub> - 100mV, programmable<br>in 95mA steps | 95   |      | 475  | mA    |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Smart Power Selector Charger (continued)**

| PARAMETER                                      | SYMBOL                                                    | CONDITIONS                                                                                                                                                | MIN  | TYP  | MAX  | UNITS   |

|------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|

| Input Current Limit<br>Accuracy                |                                                           | I <sub>CHGIN-LIM</sub> = 95mA, V <sub>SYS</sub> = V <sub>SYS-REG</sub> -<br>100mV                                                                         | 90   | 95   | 100  | mA      |

| Minimum Input Voltage<br>Regulation Range      | V <sub>CHGIN-MIN</sub>                                    | V <sub>CHGIN</sub> falling due to loading conditions<br>and/or high-impedance charge source,<br>programmable in 100mV increments with<br>VCHGIN_MIN[2:0]. | 4.0  |      | 4.7  | V       |

| Minimum Input Voltage<br>Regulation Accuracy   |                                                           | V <sub>CHGIN-MIN</sub> = 4.5V (VCHGIN_MIN[2:0] = 0b101), I <sub>CHGIN</sub> reduced by 10%                                                                | 4.32 | 4.50 | 4.68 | V       |

| Charger Input<br>Debounce Timer                | <sup>t</sup> CHGIN-DB                                     | V <sub>CHGIN</sub> = 5V, time before CHGIN is allowed to deliver current to SYS or BATT                                                                   | 100  | 120  | 140  | ms      |

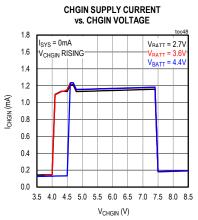

| SUPPLY AND QUIESCEN                            | NT CURRENTS                                               |                                                                                                                                                           |      |      |      |         |

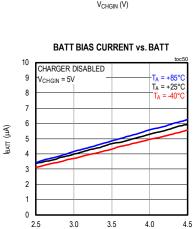

| BATT Bias Current                              | IBATT-BIAS                                                | V <sub>CHGIN</sub> = 5V, charger is not in USB<br>suspend (USBS = 0), charging is finished<br>(CHG_DTLS indicate done), I <sub>SYS</sub> = 0mA            |      | 5    |      | μΑ      |

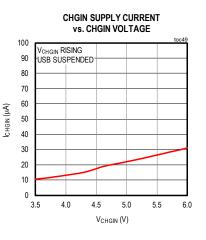

| CHGIN Supply Current                           | ICHGIN                                                    | V <sub>CHGIN</sub> = 5V, charger is not in USB<br>suspend (USBS = 0), Charging is finished<br>(CHG_DTLS indicate done), I <sub>SYS</sub> = 0mA            |      | 1.0  | 1.8  | mA      |

|                                                | $V_{CHGIN}$ = 0V to 1V, $V_{BATT}$ = 3.3V, $I_{SYS}$ = 0A |                                                                                                                                                           |      | 50   | μA   |         |

| CHGIN Suspend Supply<br>Current                | ICHGIN                                                    | V <sub>CHGIN</sub> = 5V, charger in USB suspend<br>(USBS = 1)                                                                                             |      |      | 50   | μA      |

| PREQUALIFICATIONS                              |                                                           |                                                                                                                                                           |      |      |      |         |

| Charge Current<br>Soft-Start Slew Time         |                                                           | Zero to full scale                                                                                                                                        |      | 1    |      | ms      |

| Input Current<br>Soft-Start Slew Time          |                                                           | Zero to full scale                                                                                                                                        |      | 1    |      | ms      |

| Prequalification Voltage<br>Threshold Range    | V <sub>PQ</sub>                                           | Charger is in prequalification mode when $V_{BATT} < V_{PQ}$ , this threshold has 100mV of hysteresis, programmable in 100mV steps with CHG_PQ[2:0]       | 2.3  |      | 3.0  | V       |

| Prequalification Voltage<br>Threshold Accuracy |                                                           | V <sub>PQ</sub> = 3.0V                                                                                                                                    | -3   |      | +3   | %       |

| Prequalification Mode                          | <b>I-</b> -                                               | $V_{BATT}$ = 2.5V, $V_{PQ}$ = 3.0V, expressed as a percentage of I <sub>FAST-CHG</sub> , I_PQ = 0                                                         |      | 10   |      | %       |

| Charge Current                                 | I <sub>PQ</sub>                                           | $V_{BATT}$ = 2.5V, $V_{PQ}$ = 3.0V, expressed as a percentage of I <sub>FAST-CHG</sub> , I_PQ = 1                                                         |      | 20   |      | 70      |

| Prequalification Safety<br>Timer               | t <sub>PQ</sub>                                           | V <sub>BATT</sub> < V <sub>PQ</sub> = 3.0V                                                                                                                | 27   | 30   | 33   | minutes |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Smart Power Selector Charger (continued)**

| PARAMETER                                           | SYMBOL                | CONDITIONS                                                                                                                                                                            | MIN  | TYP   | MAX  | UNITS |  |

|-----------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|--|

| FAST CHARGE                                         |                       |                                                                                                                                                                                       |      |       |      |       |  |

| Fast-Charge Voltage<br>Range                        | VFAST-CHG             | I <sub>BATT</sub> = 0mA, programmable in 25mV<br>steps with CHG_CV[5:0]                                                                                                               | 3.6  |       | 4.6  | V     |  |

| Fast-Charge Voltage                                 |                       | $I_{BATT}$ = 0mA, $V_{FAST-CHG}$ = 4.3V, $V_{SYS}$ = 4.5V, $T_A$ = +25°C                                                                                                              | -0.5 | ±0.15 | +0.5 | %     |  |

| Accuracy                                            |                       | $I_{BATT}$ = 0mA, $V_{FAST-CHG}$ = 3.6V to 4.6V,<br>$V_{SYS}$ = 4.8V                                                                                                                  |      |       | 1.0  | 70    |  |

| Fast-Charge Current<br>Range                        | I <sub>FAST-CHG</sub> | Programmable in 7.5mA steps with CHG_<br>CC[5:0]                                                                                                                                      | 7.5  |       | 300  | mA    |  |

| Fast-Charge Current                                 |                       | I <sub>FAST-CHG</sub> = 15mA, T <sub>A</sub> = 25°C, V <sub>BATT</sub> =<br>V <sub>FAST-CHG</sub> - 300mV                                                                             | -1.5 |       | +1.5 | 0/    |  |

| Accuracy                                            |                       | I <sub>FAST-CHG</sub> = 300mA, T <sub>A</sub> = 25°C, V <sub>BATT</sub> =<br>V <sub>FAST-CHG</sub> - 300mV                                                                            | -1.5 |       | +1.5 | - %   |  |

| Fast-Charge Current<br>Accuracy over<br>Temperature |                       | Across all current settings, V <sub>BATT</sub> = V <sub>FAST-</sub><br><sub>CHG</sub> - 300mV                                                                                         | -10  |       | +10  | %     |  |

| Fast-Charge Safety<br>Timer Range                   | t <sub>FC</sub>       | Programmable in 2 hour increments or<br>disabled with T_FAST_CHG[1:0], from<br>prequal done to timer fault                                                                            | 3    |       | 7    | hours |  |

| Fast-Charge Safety<br>Timer Accuracy                |                       | t <sub>FC</sub> = 3 hours                                                                                                                                                             | -10  |       | +10  | %     |  |

| Fast-Charge Safety<br>Timer Suspend<br>Threshold    |                       | Fast-charge CC mode, loading conditions<br>and/or a weak charging source caused<br>charge current to drop below this threshold,<br>expressed as a percentage of I <sub>FAST-CHG</sub> |      | 20    |      | %     |  |

| Junction Temperature<br>Regulation Setting<br>Range | T <sub>J-REG</sub>    | Programmable in 10°C steps with TJ_REG[2:0]                                                                                                                                           | 60   |       | 100  | °C    |  |

| Junction Temperature<br>Regulation Loop Gain        | G <sub>TJ-REG</sub>   | Rate at which $I_{FAST-CHG}/I_{PQ}$ is reduced to maintain $T_{J-REG}$ , expressed a percentage of $I_{FAST-CHG}/I_{PQ}$ per degree centigrade rise                                   |      | -5.4  |      | %/°C  |  |

| TERMINATION AND TOP                                 | POFF                  |                                                                                                                                                                                       |      |       |      |       |  |

|                                                     |                       | I_TERM = 0b00 (expressed as a percentage<br>of I <sub>FAST-CHG</sub> )                                                                                                                |      | 5     |      |       |  |

| End-of-Charge                                       | <br>                  | I_TERM = 0b01 (expressed as a percentage<br>of I <sub>FAST-CHG</sub> )                                                                                                                |      | 7.5   |      | 0/    |  |

| Termination Current                                 | ITERM                 | I_TERM = 0b10 (expressed as a percentage<br>of I <sub>FAST-CHG</sub> )                                                                                                                |      | 10    |      | - %   |  |

|                                                     |                       | I_TERM = 0b11 (expressed as a percentage<br>of I <sub>FAST-CHG</sub> )                                                                                                                |      | 15    |      |       |  |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Smart Power Selector Charger (continued)**

| PARAMETER                                             | SYMBOL               | CONDITIONS                                                                                                                                                                                                                                                                                                      | MIN   | TYP                          | MAX   | UNITS   |

|-------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|-------|---------|

| End-of-Charge Termina-                                |                      | I <sub>FAST-CHG</sub> = 15mA, I <sub>TERM</sub> = 1.5mA (10% of I <sub>FAST-CHG</sub> ), T <sub>A</sub> = +25°C                                                                                                                                                                                                 | 1.35  | 1.5                          | 1.65  | mA      |

| tion Current Accuracy                                 |                      | I <sub>FAST-CHG</sub> = 300mA, I <sub>TERM</sub> = 30mA (10% of I <sub>FAST-CHG</sub> ), T <sub>A</sub> = +25°C                                                                                                                                                                                                 | 27    | 30                           | 33    |         |

| Top-Off Timer Range                                   | t <sub>TO</sub>      | I <sub>BATT</sub> < I <sub>TERM</sub> , programmable in 5 minute<br>steps with T_TOPOFF[2:0]                                                                                                                                                                                                                    | 0     |                              | 35    | minutes |

| Top-Off Timer Accuracy                                |                      | t <sub>TO</sub> = 10 minutes                                                                                                                                                                                                                                                                                    | -10   |                              | +10   | %       |

| Charge Restart Thresh-<br>old                         | V <sub>RESTART</sub> | CHG = 0 (charging done), charging re-<br>sumes when V <sub>BATT</sub> < V <sub>FAST-CHG</sub> - V <sub>RE-</sub><br>START                                                                                                                                                                                       | 65    | 150                          |       | mV      |

| DEVICE ON-RESISTANC                                   | E AND LEAKAG         | E                                                                                                                                                                                                                                                                                                               |       |                              |       |         |

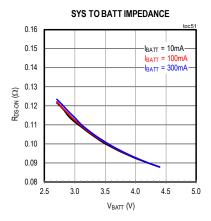

| BATT to SYS<br>On-Resistance                          |                      | V <sub>BATT</sub> = 3.7V, I <sub>BATT</sub> = 300mA, V <sub>CHGIN</sub> = 0V, battery is discharging to SYS                                                                                                                                                                                                     |       | 100                          |       | mΩ      |

| Charger FET Leakage                                   |                      | $V_{SYS}$ = 4.5V, $V_{BATT}$ = 0V, $T_A$ = 25°C, charger disabled                                                                                                                                                                                                                                               |       | 0.1                          | 1.0   | - μΑ    |

| Current                                               |                      | $V_{SYS}$ = 4.5V, $V_{BATT}$ = 0V, $T_A$ = 85°C, charger disabled                                                                                                                                                                                                                                               |       | 1                            |       |         |

| CHGIN to SYS<br>On-Resistance                         |                      | V <sub>CHGIN</sub> = 4.65V                                                                                                                                                                                                                                                                                      |       | 600                          |       | mΩ      |

| Input FET Leakage                                     |                      | $V_{CHGIN}$ = 0V, $V_{SYS}$ = 4.2V, $T_A$ = +25°C,<br>body-switched diode reverse biased                                                                                                                                                                                                                        |       | 0.1                          | 1.0   |         |

| Current                                               |                      | $V_{CHGIN}$ = 0V, $V_{SYS}$ = 4.2V, $T_A$ = +85°C,<br>body-switched diode is reverse biased                                                                                                                                                                                                                     |       | 1                            |       | μA      |

| SYSTEM NODE                                           |                      |                                                                                                                                                                                                                                                                                                                 |       |                              |       |         |

| System Voltage<br>Regulation Range                    | V <sub>SYS-REG</sub> | Programmable in 25mV steps with VSYS_<br>REG[4:0]                                                                                                                                                                                                                                                               | 4.1   |                              | 4.8   | V       |

| System Voltage                                        |                      | $V_{SYS-REG}$ = 4.5V, $I_{SYS}$ = 1mA, $T_A$ = +25°C                                                                                                                                                                                                                                                            | 4.41  | 4.50                         | 4.59  |         |

| System Voltage<br>Regulation Accuracy                 | V <sub>SYS</sub>     | $V_{SYS-REG}$ = 4.5V, $I_{SYS}$ = 1mA, $T_A$ = -40°C to +85°C                                                                                                                                                                                                                                                   | 4.365 | 4.500                        | 4.635 | V       |

| Minimum System<br>Voltage Regulation<br>Loop Setpoint | V <sub>SYS-MIN</sub> | V <sub>CHGIN</sub> = 5V, V <sub>SYS-REG</sub> = 4.5V, V <sub>SYS</sub> <<br>V <sub>SYS-REG</sub> due to I <sub>CHGIN</sub> = I <sub>CHGIN-LIM</sub> (in-<br>put in current-limit), battery charging, I <sub>BATT</sub><br>reduced to 50% of I <sub>FAST-CHG</sub> (minimum<br>system voltage regulation active) | 4.34  | 4.4                          | 4.45  | V       |

| Supplement Mode Sys-<br>tem Voltage Regulation        |                      | I <sub>SYS</sub> = 150mA                                                                                                                                                                                                                                                                                        |       | V <sub>BATT</sub><br>- 0.15V |       | V       |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Adjustable Thermistor Temperature Monitors**

(V<sub>CHGIN</sub> = 5.0V, V<sub>SYS</sub> = 4.5V, V<sub>BATT</sub> = 4.2V, limits are 100% production tested at  $T_A$  = +25°C, limits over the operating temperature range ( $T_A$  = -40°C to +85°C) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                                    | SYMBOL                         | CONDITIONS                                                                                                           | MIN   | TYP  | MAX   | UNITS |

|----------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| JEITA TEMPERATURE                            | IONITORS                       |                                                                                                                      | ·     |      |       |       |

| TBIAS Voltage                                | V <sub>TBIAS</sub>             | THM_EN = 1, V <sub>CHGIN</sub> = 5V                                                                                  |       | 1.25 |       | V     |

| JEITA Cold Threshold<br>Range                | V <sub>COLD</sub>              | Voltage rising threshold, programmable with THM_COLD[1:0] in 5°C increments when using an NTC $\beta$ = 3380K        | 0.867 |      | 1.024 | V     |

| JEITA Cool Threshold<br>Range                | V <sub>COOL</sub>              | Voltage rising threshold, programmable<br>with THM_COOL[1:0] in 5°C increments<br>when using an NTC $\beta$ = 3380K  | 0.747 |      | 0.923 | V     |

| JEITA Warm Threshold<br>Range                | Vwarm                          | Voltage falling threshold, programmable<br>with THM_WARM[1:0] in 5°C increments<br>when using an NTC $\beta$ = 3380K | 0.367 |      | 0.511 | V     |

| JEITA Hot Threshold<br>Range                 | V <sub>HOT</sub>               | Voltage falling threshold, programmable<br>with THM_HOT[1:0] in 5°C increments<br>when using an NTC β = 3380K        | 0.291 |      | 0.411 | V     |

| Temperature Threshold<br>Accuracy            |                                | Voltage threshold accuracy expressed as temperature for an NTC $\beta$ = 3380K                                       |       | ±3   |       | °C    |

| Temperature Threshold<br>Hysteresis          |                                | Temperature hysteresis set on each volt-<br>age threshold for an NTC $\beta$ = 3380K                                 |       | 3    |       | °C    |

| JEITA Modified Fast-<br>Charge Voltage Range | V <sub>FAST-CHG</sub><br>JEITA | I <sub>BATT</sub> = 0mA, programmable in 25mV<br>steps, battery is either cool or warm                               | 3.6   |      | 4.6   | V     |

| JEITA Modified Fast-<br>Charge Current Range | IFAST-CHG_JEI-<br>TA           | Programmable in 7.5mA steps, battery is either cool or warm                                                          | 7.5   |      | 300   | mA    |

### **Electrical Characteristics—Analog Multiplexer and Power Monitor AFEs**

| PARAMETER                              | SYMBOL                 | CONDITIONS                                                                         | MIN | TYP   | MAX | UNITS |

|----------------------------------------|------------------------|------------------------------------------------------------------------------------|-----|-------|-----|-------|

| ANALOG MULTIPLEXER                     | R AND POWER M          | ONITOR AFES                                                                        |     |       |     |       |

| Full-Scale Voltage                     | V <sub>FS</sub>        |                                                                                    |     | 1.25  |     | V     |

| SYS Voltage Monitor<br>Gain            | G <sub>VSYS</sub>      | $V_{FS}$ corresponds to maximum $V_{SYS\text{-}REG}$ setting                       |     | 0.26  |     | V/V   |

| CHGIN POWER                            |                        |                                                                                    |     |       |     |       |

| CHGIN Current Monitor<br>Gain          | G <sub>ICHGIN</sub>    | V <sub>FS</sub> corresponds to maximum I <sub>CHGIN-LIM</sub> setting              |     | 2.632 |     | V/A   |

| CHGIN Voltage Monitor<br>Gain          | G <sub>VCHGIN</sub>    | V <sub>FS</sub> corresponds to V <sub>CHGIN_OVP</sub>                              |     | 0.167 |     | V/V   |

| BATT MONITOR                           |                        |                                                                                    |     |       |     |       |

| Battery Charge Current<br>Monitor Gain | G <sub>IBATT-CHG</sub> | V <sub>FS</sub> corresponds to 100% of I <sub>FAST-CHG</sub> setting (CHG_CC[5:0]) |     | 12.5  |     | mV/%  |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—Analog Multiplexer and Power Monitor AFEs (continued)**

| PARAMETER                                                | SYMBOL              | COND                                                              | ITIONS                                                | MIN  | ТҮР   | MAX   | UNITS |

|----------------------------------------------------------|---------------------|-------------------------------------------------------------------|-------------------------------------------------------|------|-------|-------|-------|

| Charge Current Monitor                                   |                     | I <sub>FAST-CHG</sub> = 15mA, T<br>V <sub>FAST-CHG</sub> - 300mV  | <sup>T</sup> <sub>A</sub> = 25°C, V <sub>BATT</sub> = | -3.5 |       | +3.5  | %     |

| Accuracy                                                 |                     | I <sub>FAST-CHG</sub> = 300mA,<br>V <sub>FAST-CHG</sub> - 300mV   | T <sub>A</sub> = +25°C, V <sub>BATT</sub> =           | -3.5 |       | +3.5  | 70    |

| Charge Current Monitor<br>Accuracy over<br>Temperature   |                     | Across all current sett<br><sub>CHG</sub> - 300mV                 | tings, V <sub>BATT</sub> = V <sub>FAST-</sub>         | -10  |       | +10   | %     |

| Battery Discharge<br>Monitor Full-Scale<br>Current Range | IDISCHG-SCALE       | Programmable with IN SCALE[3:0]                                   | 8.2                                                   |      | 300   | mA    |       |

| Battery Discharge<br>Current Monitor<br>Accuracy         |                     | 15mA to 300mA battery discharge current,<br>IDISCHG-SCALE = 300mA |                                                       | -15  |       | +15   | %     |

| Battery Discharge<br>Current Monitor Offset              |                     | I <sub>BATT</sub> = 0mA                                           | I <sub>BATT</sub> = 0mA                               |      |       | +0.65 | mA    |

| Battery Voltage Monitor<br>Gain                          | G <sub>VBATT</sub>  | V <sub>FS</sub> corresponds to m<br>setting                       | naximum V <sub>FAST-CHG</sub>                         |      | 0.272 |       | V/V   |

| ANALOG MULTIPLEXER                                       | R                   |                                                                   |                                                       |      |       |       |       |

| Channel Switching Time                                   |                     |                                                                   |                                                       |      | 0.3   |       | μs    |

|                                                          |                     | V <sub>AMUX</sub> = 0V, AMUX                                      | T <sub>A</sub> = +25°C                                |      | 1     | 500   | nA    |

| Off Leakage Current                                      |                     | is high impedance                                                 | T <sub>A</sub> = +85°C                                |      | 1     |       | μA    |

| THM AND TBIAS                                            |                     |                                                                   |                                                       |      |       |       |       |

| THM Voltage Monitor<br>Gain                              | G <sub>VTHM</sub>   |                                                                   |                                                       |      | 1     |       | V/V   |

| TBIAS Voltage Monitor<br>Gain                            | G <sub>VTBIAS</sub> |                                                                   |                                                       |      | 1     |       | V/V   |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

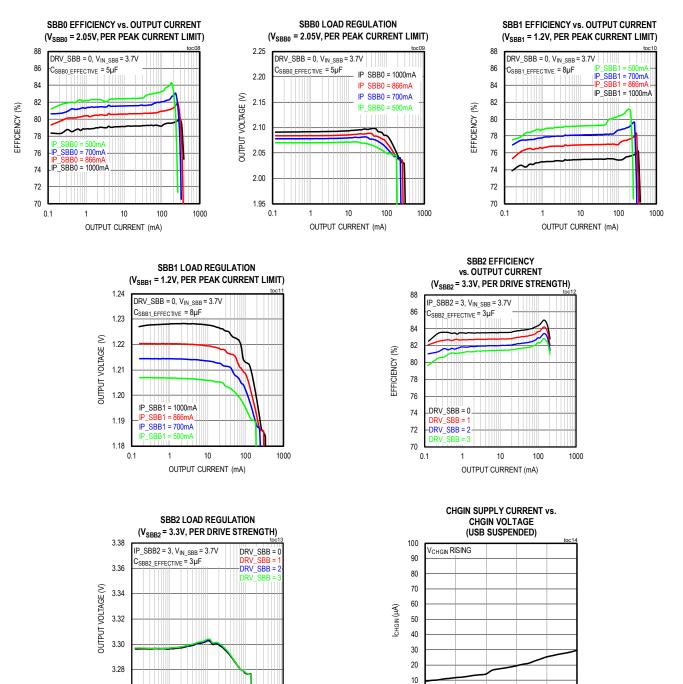

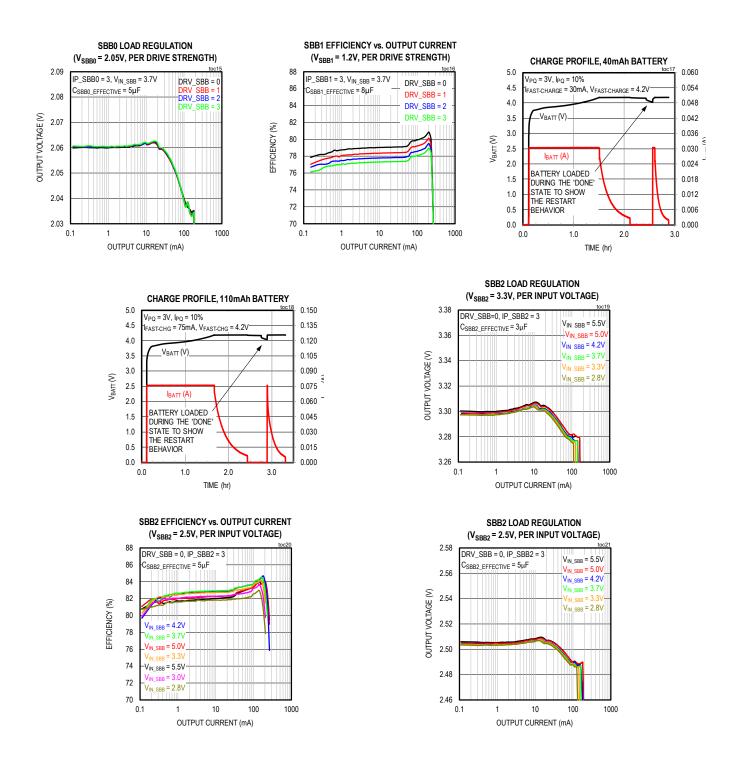

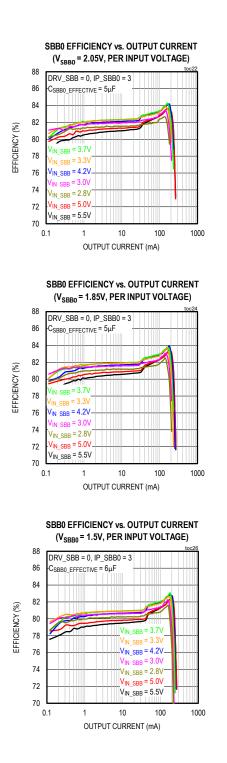

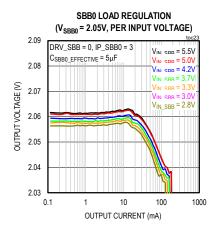

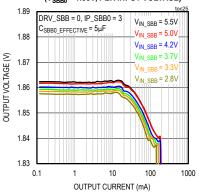

### **Electrical Characteristics—SIMO Buck-Boost**

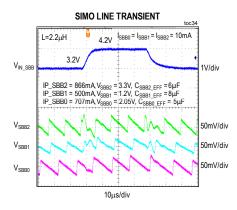

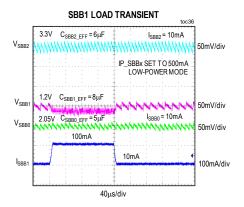

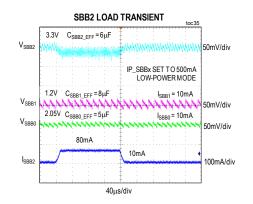

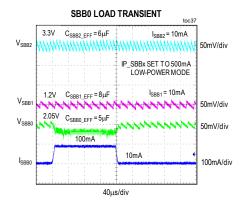

$(V_{SYS} = 3.7V, V_{IN\_SBB} = 3.7V, C_{SBBx} = 10\mu$ F, L = 1.5µH, limits are 100% production tested at T<sub>A</sub> = +25°C, limits over the operating temperature range (T<sub>A</sub> = -40°C to +85°C) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                 | SYMBOL                                                         | CONDI                                                                       | TIONS                  | MIN  | TYP    | MAX  | UNITS |  |

|---------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------|------|--------|------|-------|--|

| OUTPUT VOLTAGE RAN        | IGE (SBB0)                                                     |                                                                             |                        |      |        |      |       |  |

| Minimum Output<br>Voltage |                                                                |                                                                             |                        |      | 0.8    |      | V     |  |

| Maximum Output<br>Voltage |                                                                |                                                                             |                        |      | 2.375  |      | V     |  |

| Output DAC Bits           |                                                                |                                                                             |                        |      | 6      |      | bits  |  |

| Output DAC LSB Size       |                                                                |                                                                             |                        |      | 25     |      | mV    |  |

| OUTPUT VOLTAGE RAN        | IGE (SBB1)                                                     |                                                                             |                        |      |        |      |       |  |

| Minimum Output            |                                                                | MAX77650                                                                    |                        |      | 0.8    |      | V     |  |

| Voltage                   |                                                                | MAX77651                                                                    |                        |      | 2.4    |      |       |  |

| Maximum Output            |                                                                | MAX77650                                                                    |                        |      | 1.5875 |      | - v   |  |

| Voltage                   |                                                                | MAX77651                                                                    |                        |      | 5.25   |      | V     |  |

| Output DAC Bits           |                                                                |                                                                             |                        |      | 6      |      | bits  |  |

| Output DAC LSB Size       |                                                                | MAX77650                                                                    |                        |      | 12.5   |      | mV    |  |

| Output DAC LOB Size       |                                                                | MAX77651                                                                    |                        |      | 50     |      | IIIV  |  |

| OUTPUT VOLTAGE RAN        | IGE (SBB2)                                                     |                                                                             |                        |      |        |      |       |  |

| Minimum Output            |                                                                | MAX77650                                                                    |                        |      | 0.8    |      | - V   |  |

| Voltage                   |                                                                | MAX77651                                                                    |                        |      | 2.4    | 2.4  |       |  |

| Maximum Output            |                                                                | MAX77650                                                                    |                        |      | 3.95   |      | - v   |  |

| Voltage                   |                                                                | MAX77651                                                                    |                        |      | 5.25   |      | - V   |  |

| Output DAC Bits           |                                                                |                                                                             |                        |      | 6      |      | bits  |  |

| Output DAC LSB Size       |                                                                |                                                                             |                        |      | 50     |      | mV    |  |

| OUTPUT VOLTAGE ACC        | URACY                                                          |                                                                             |                        |      |        |      |       |  |

| Output Voltage            |                                                                | V <sub>SBBx</sub> falling,<br>threshold where LXA<br>switches high. Speci-  | T <sub>A</sub> = +25°C | -2.5 |        | +2.5 |       |  |

| Accuracy                  | fied as a percentage<br>of target output volt-<br>age (Note 3) | T <sub>A</sub> = -40°C to<br>+85°C                                          | -4.0                   |      | +4.0   | %    |       |  |

| TIMING CHARACTERIS        | TICS                                                           |                                                                             |                        |      |        |      |       |  |

| Enable Delay              |                                                                | Delay time from the SI<br>enable signal to when<br>order to service that or | it begins to switch in |      | 60     |      | μs    |  |

| Soft-Start Slew Rate      | dV/dt <sub>SS</sub>                                            |                                                                             |                        | 3.3  | 5.0    | 6.6  | mV/µs |  |

# Ultra-Low Power PMIC with 3-Output SIMO and Power Path Charger for Small Li+

### **Electrical Characteristics—SIMO Buck-Boost (continued)**

$(V_{SYS} = 3.7V, V_{IN\_SBB} = 3.7V, C_{SBBx} = 10\mu$ F, L = 1.5µH, limits are 100% production tested at T<sub>A</sub> = +25°C, limits over the operating temperature range (T<sub>A</sub> = -40°C to +85°C) are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                     | SYMBOL               | CONDI                                                                              | TIONS                  | MIN   | ТҮР         | MAX   | UNITS |

|-------------------------------|----------------------|------------------------------------------------------------------------------------|------------------------|-------|-------------|-------|-------|

| POWER STAGE CHARA             |                      |                                                                                    |                        |       |             |       |       |

| LXA Leakage Current           |                      | SBB0, SBB1, SBB2<br>are disabled,                                                  | T <sub>A</sub> = +25°C | -1.0  | ±0.1        | +1.0  |       |

| LAA Leakage Current           |                      | V <sub>IN_SBB</sub> = 5.5V,<br>V <sub>LXA</sub> = 0V, or 5.5V                      | T <sub>A</sub> = +85°C |       | ±1.0        |       | μA    |

|                               |                      | SBB0, SBB1, SBB2<br>are disabled, V <sub>IN</sub>                                  | T <sub>A</sub> = +25°C | -1.0  | ±0.1        | +1.0  |       |

| LXB Leakage Current           | 0V or 5.<br>= 5.5V   | SBB = 5.5V, V <sub>LXA</sub> =<br>0V or 5.5V, all V <sub>SBBx</sub><br>= 5.5V      | T <sub>A</sub> = +85°C |       | ±1.0        |       | μA    |

|                               |                      | $V_{IN\_SBB} = 5.5V,$                                                              | T <sub>A</sub> = +25°C |       | +0.01       | +1.0  |       |

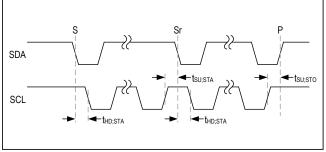

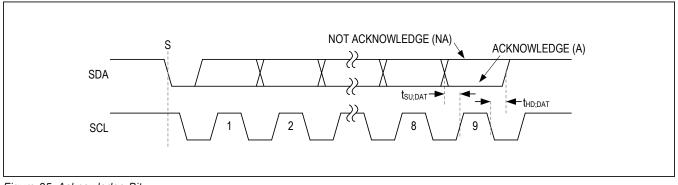

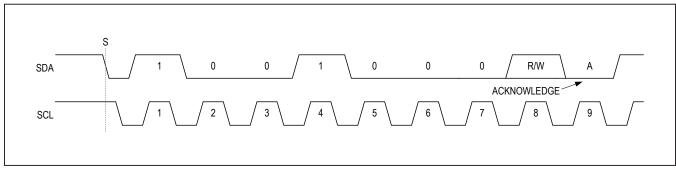

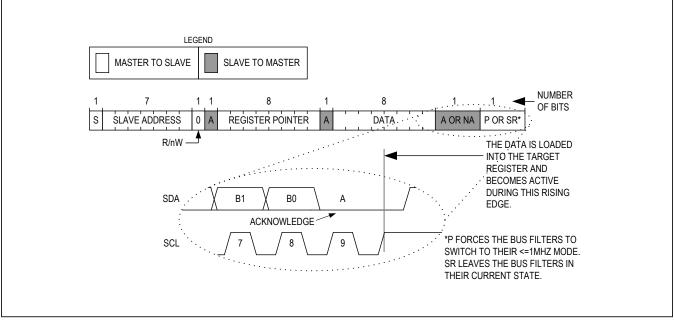

| BST Leakage Current           |                      | V <sub>LXB</sub> = 5.5V,<br>V <sub>BST</sub> = 11V                                 | T <sub>A</sub> = +85°C |       | +0.1        |       | μΑ    |