MAX5982A/MAX5982B/

MAX5982C

Click here to ask an associate for production status of specific part numbers.

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

#### **General Description**

The MAX5982A/MAX5982B/MAX5982C provide a complete interface for a powered device (PD) to comply with the IEEE® 802.3af/at standard in a power-over-Ethernet (PoE) system. The MAX5982A/MAX5982B/MAX5982C provide the PD with a detection signature, classification signature, and an integrated isolation power switch with inrush current control. During the inrush period, the MAX5982A/MAX5982B/MAX5982C limit the current to less than 182mA before switching to the higher current limit (1700mA to 2100mA) when the isolation power MOSFET is fully enhanced. The devices feature an input UVLO with wide hysteresis and long deglitch time to compensate for twisted-pair cable resistive drop and to assure glitch-free transition during power-on/-off conditions. The MAX5982A/MAX5982B/MAX5982C can withstand up to 100V at the input.

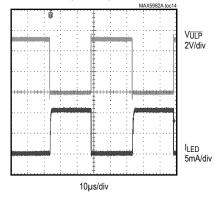

The MAX5982A/MAX5982B/MAX5982C support a 2-Event classification method as specified in the IEEE 802.3at standard and provide a signal to indicate when probed by a Type 2 power sourcing equipment (PSE). The devices detect the presence of a wall adapter power source connection and allow a smooth switchover from the PoE power source to the wall power adapter.

The MAX5982A/MAX5982B/MAX5982C also provide a power-good (PG) signal, two-step current limit and foldback, overtemperature protection, and di/dt limit. A sleep mode feature in the MAX5982A/MAX5982B provides low power consumption while supporting Maintain Power Signature (MPS). An ultra-low-power sleep mode feature in the MAX5982A/MAX5982B further reduces power consumption while still supporting MPS. The MAX5982A/MAX5982B also feature an LED driver that is automatically activated during sleep mode.

The MAX5982A/MAX5982B/MAX5982C are available in a 16-pin, 5mm x 5mm, TQFN power package. These devices are rated over the -40°C to +85°C and -40°C to +125°C extended temperature ranges.

### Features

- Sleep Mode and Ultra-Low-Power Sleep (MAX5982A/MAX5982B)

- IEEE 802.3af/at Compliant

- 2-Event Classification or an External Wall Adapter Indicator Output

- Simplified Wall Adapter Interface

- PoE Classification 0-5

- 100V Input Absolute Maximum Rating

- Inrush Current Limit of 182mA Maximum

- Current Limit During Normal Operation Between 1700mA and 2100mA

- Current Limit and Foldback

- Legacy UVLO at 36V

- LED Driver with Programmable LED Current (MAX5982A/MAX5982B)

- Overtemperature Protection

- Thermally Enhanced, 5mm x 5mm, 16-Pin TQFN

### **Applications**

- IEEE 802.3af/at Powered Devices

- IP Phones, Wireless Access Nodes, IP Security Cameras

- WiMAX<sup>™</sup> Base Stations

Ordering Information appears at end of data sheet.

WiMAX is a trademark of WiMAX Forum. IEEE is a registered service mark of the Institute of Electrical and Electronics Engineers, Inc.

19-5960; Rev 4; 11/21

© 2021 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2021 Analog Devices, Inc. All rights reserved.

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to V <sub>SS</sub>                       |               |

|----------------------------------------------------------|---------------|

| DET, RTN, WAD, PG, ZEC to V <sub>SS</sub>                | 0.3V to +100V |

| CLS, SL, WK, ULP, LED to V <sub>SS</sub>                 | 0.3V to +6V   |

| Maximum Current on CLS (100ms maximum)                   |               |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) (N | ote 1)        |

| TQFN (derate 28.6mW/°C above +70°C)                      |               |

| Multilayer Board                                         | 2285.7mW      |

| Operating Temperature Range       | 40°C to +125°C |

|-----------------------------------|----------------|

| Maximum Junction Temperature      | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

| Soldering Temperature (reflow)    | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: Maximum power dissipation is obtained using JEDEC JESD51-5 and JESD51-7 specifications.

### Package Thermal Characteristics (Note 2)

TQFN

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

### **Electrical Characteristics**

$(V_{IN} = (V_{DD} - V_{SS}) = 48V, R_{DET} = 24.9k\Omega, R_{CLS} = 615\Omega$ , and  $R_{\overline{SL}} = 60.4k\Omega$ . RTN, WAD, PG,  $\overline{2EC}$ ,  $\overline{WK}$ , and  $\overline{ULP}$  unconnected, all voltages are referenced to  $V_{SS}$ , unless otherwise noted.  $T_A = T_J = -40^{\circ}C$  to  $+85^{\circ}C$  (MAX5982AETE/BETE/CETE),  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$  (MAX5982AATE/BATE/CATE), unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 3)

| PARAMETER                                  | SYMBOL                                   | CC                                                                               | ONDITIONS                                | MIN   | TYP   | MAX   | UNITS |  |

|--------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------|-------|-------|-------|-------|--|

| DETECTION MODE                             |                                          | •                                                                                |                                          |       |       |       |       |  |

| Input Offset Current                       | IOFFSET                                  | V <sub>IN</sub> = 1.4V to 10                                                     | V <sub>IN</sub> = 1.4V to 10.1V (Note 4) |       |       | 10    | μA    |  |

| Effective Differential Input<br>Resistance | dR                                       | $V_{IN} = 1.4V \text{ up to}$<br>$V_{DD} = RTN = W_{DD}$                         | 23.95                                    | 25.00 | 25.50 | kΩ    |       |  |

| CLASSIFICATION MODE                        |                                          |                                                                                  |                                          |       |       |       |       |  |

| Classification Disable Threshold           | V <sub>TH,CLS</sub>                      | V <sub>IN</sub> rising (Note                                                     | 6)                                       | 22.0  | 22.8  | 23.6  | V     |  |

| Classification Stability Time              |                                          |                                                                                  |                                          |       | 0.2   |       | ms    |  |

|                                            | I <sub>CLASS</sub>                       | $V_{IN}$ = 12.5V to<br>20.5V, $V_{DD}$ =<br>RTN = WAD =<br>PG = $\overline{2EC}$ | Class 0, R <sub>CLS</sub> = 615Ω         | 0     |       | 3.96  | - mA  |  |

|                                            |                                          |                                                                                  | Class 1, R <sub>CLS</sub> = 117Ω         | 9.12  |       | 11.88 |       |  |

| Classification Current                     |                                          |                                                                                  | Class 2, R <sub>CLS</sub> = 66.5Ω        | 17.2  |       | 19.8  |       |  |

| Classification Current                     |                                          |                                                                                  | Class 3, R <sub>CLS</sub> = 43.7Ω        | 26.3  |       | 29.7  |       |  |

|                                            |                                          |                                                                                  | Class 4, R <sub>CLS</sub> = 30.9Ω        | 36.4  |       | 43.6  |       |  |

|                                            |                                          |                                                                                  | Class 5, R <sub>CLS</sub> = 21.3Ω        | 52.7  |       | 63.3  |       |  |

| TYPE 2 (802.3at) CLASSIFICAT               | ION MODE                                 |                                                                                  |                                          |       |       |       |       |  |

| Mark Event Threshold                       | V <sub>THM</sub>                         | V <sub>IN</sub> falling                                                          |                                          | 10.1  | 10.7  | 11.6  | V     |  |

| Hysteresis on Mark Event<br>Threshold      |                                          |                                                                                  |                                          |       | 0.82  |       | V     |  |

| Mark Event Current                         | I <sub>MARK</sub>                        | $V_{IN}$ falling to enter mark event, 5.2V $\leq$ $V_{IN} \leq$ 10.1V            |                                          | 0.25  |       | 0.85  | mA    |  |

| Depat Event Threehold                      | N/                                       | V folling                                                                        | -40°C to +125°C                          | 2.7   | 3.8   | 5.2   |       |  |

| Reset Event Threshold                      | V <sub>THR</sub> V <sub>IN</sub> falling | v <sub>IN</sub> tailing                                                          | -40°C to +85°C                           | 2.8   | 3.8   | 5.2   | - V   |  |

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Electrical Characteristics (continued)**

$(V_{IN} = (V_{DD} - V_{SS}) = 48V, R_{DET} = 24.9k\Omega, R_{CLS} = 615\Omega$ , and  $R_{\overline{SL}} = 60.4k\Omega$ . RTN, WAD, PG,  $\overline{2EC}$ ,  $\overline{WK}$ , and  $\overline{ULP}$  unconnected, all voltages are referenced to  $V_{SS}$ , unless otherwise noted.  $T_A = T_J = -40^{\circ}C$  to  $+85^{\circ}C$  (MAX5982AETE/BETE/CETE),  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$  (MAX5982AATE/BATE/CATE), unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 3)

| PARAMETER                                | SYMBOL                 | CC                                                             | ONDIT              | IONS                           | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|------------------------|----------------------------------------------------------------|--------------------|--------------------------------|------|------|------|-------|

| POWER MODE                               |                        |                                                                |                    |                                |      |      |      |       |

| VIN Supply Voltage Range                 |                        |                                                                |                    |                                |      |      | 60   | V     |

| VIN Supply Current                       | lq                     | Current through                                                | intern             | al MOSFET = 0                  |      | 0.25 | 0.55 | mA    |

| V <sub>IN</sub> Turn-On Voltage          | V <sub>ON</sub>        | V <sub>IN</sub> rising                                         |                    |                                | 34.3 | 35.4 | 36.6 | V     |

| VIN Turn-Off Voltage                     | V <sub>OFF</sub>       | V <sub>IN</sub> falling                                        |                    |                                | 30   |      |      | V     |

| VIN Turn-On/-Off Hysteresis              | V <sub>HYST_UVLO</sub> | (Note 7)                                                       |                    |                                | 4.2  |      |      | V     |

| V <sub>IN</sub> Deglitch Time            | tOFF_DLY               | V <sub>IN</sub> falling from 4                                 | 40V to             | 20V (Note 8)                   | 30   | 120  |      | μs    |

| Inrush to Operating Mode Delay           | tDELAY                 | t <sub>DELAY</sub> = minimu<br>width after enteri              |                    |                                | 90   | 96   | 102  | ms    |

|                                          |                        |                                                                | T <sub>J</sub> =   | +25°C                          |      | 0.1  | 0.2  |       |

| Isolation Power MOSFET                   | R <sub>ON_ISO</sub>    | I <sub>RTN</sub> = 950mA                                       | T <sub>J</sub> =   | : +85°C                        |      | 0.15 | 0.25 | Ω     |

| On-Resistance                            |                        |                                                                |                    | : +125°C                       |      | 0.2  |      |       |

| RTN Leakage Current                      | IRTN LKG               | V <sub>RTN</sub> = 12.5V to 30V                                |                    |                                |      | 10   | μA   |       |

| CURRENT LIMIT                            |                        |                                                                |                    |                                |      |      |      |       |

| Inrush Current Limit                     | IINRUSH                | During initial turr                                            | n-on p             | eriod, V <sub>RTN</sub> = 1.5V | 90   | 135  | 182  | mA    |

| Current Limit During Normal              |                        | After inrush                                                   | -                  | 40°C to +85°C                  | 1700 | 1900 | 2100 |       |

| Current Limit During Normal<br>Operation | ILIM                   | completed,<br>V <sub>RTN</sub> = 1V (Note 9) -40°C to +125°C   |                    | 1650                           | 1900 | 2150 | mA   |       |

| Current Limit in Foldback<br>Condition   | I <sub>LIM-FLDBK</sub> | Both during inrush and after inrush completed $V_{RTN}$ = 7.5V |                    |                                | 53   |      | mA   |       |

| Foldback Threshold                       |                        | V <sub>RTN</sub> (Note 10)                                     |                    |                                | 6.5  | 7.0  | 7.5  | V     |

| LOGIC                                    |                        |                                                                |                    |                                |      |      |      |       |

| WAD Detection Threshold                  | V <sub>WAD-REF</sub>   | V <sub>WAD</sub> rising, V <sub>IN</sub><br>(referenced to R   |                    | V to 48V                       | 8    | 9    | 10   | V     |

| WAD Detection Threshold<br>Hysteresis    |                        | V <sub>WAD</sub> falling, V <sub>R</sub><br>unconnected        | RTN = (            | OV, V <sub>SS</sub>            |      | 0.35 |      | V     |

| WAD Input Current                        | I <sub>WAD-LKG</sub>   | V <sub>WAD</sub> = 10V (ref                                    | ferenc             | ed to RTN)                     |      |      | 3.5  | μA    |

| 2EC Sink Current                         |                        | V <sub>2EC</sub> = 3.5V (ref<br>V <sub>SS</sub> disconnecte    |                    | ed to RTN),                    | 1    | 1.5  | 2.25 | mA    |

| 2EC Off-Leakage Current                  |                        | V <sub>2EC</sub> = 48V                                         |                    |                                |      |      | 1    | μA    |

| PG Sink Current                          |                        | V <sub>RTN</sub> = 1.5V, V <sub>P</sub><br>period              | o <sub>G</sub> = 0 | .8V, during inrush             | 125  | 230  | 375  | μA    |

| PG Off-Leakage Current                   |                        | $V_{PG} = 60V$                                                 |                    |                                |      | 1    | μA   |       |

| SLEEP MODE (MAX5982A/MA                  | ,<br>X5982B)           |                                                                |                    |                                |      |      |      |       |

| WK and ULP Logic Threshold               | V <sub>TH</sub>        | $V_{\overline{WK}}$ falling and $V_{\overline{WK}}$            | VULP               | rising and falling             | 1.5  |      | 3    | V     |

| SL Logic Threshold                       | 1                      | Falling                                                        |                    | 0.75                           | 0.8  | 0.85 | V    |       |

| SL Current                               |                        | R <sub>SI</sub> = 0Ω                                           |                    |                                |      | 140  |      | μA    |

|                                          |                        | R <sub>SL</sub> = 60.4kΩ, V                                    |                    | 3.5V                           | 10   | 10.5 | 11.5 |       |

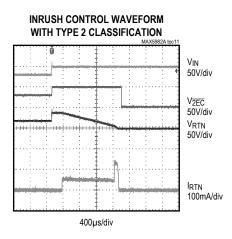

| LED Current Amplitude                    | ILED                   | R <sub>SL</sub> = 30.2kΩ, V                                    |                    |                                | 19.5 | 20.9 | 22.5 | mA    |

|                                          |                        | R <sub>SL</sub> = 30.2kΩ, V                                    |                    |                                | 19   |      |      |       |

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Electrical Characteristics (continued)**

$(V_{IN} = (V_{DD} - V_{SS}) = 48V, R_{DET} = 24.9k\Omega, R_{CLS} = 615\Omega$ , and  $R_{\overline{SL}} = 60.4k\Omega$ . RTN, WAD, PG,  $\overline{2EC}$ ,  $\overline{WK}$ , and  $\overline{ULP}$  unconnected, all voltages are referenced to  $V_{SS}$ , unless otherwise noted.  $T_A = T_J = -40^{\circ}C$  to  $+85^{\circ}C$  (MAX5982AETE/BETE/CETE),  $T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$  (MAX5982AATE/BATE/CATE), unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 3)

| PARAMETER                         | SYMBOL            | COND                                                                                                                                      | DITIONS                                    | MIN | TYP  | MAX  | UNITS |

|-----------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----|------|------|-------|

| LED Current Programmable<br>Range |                   |                                                                                                                                           |                                            | 10  |      | 20   | mA    |

| LED Current with Grounded SL      |                   | $V_{\overline{SL}} = 0V$                                                                                                                  | $V_{\overline{SL}} = 0V$                   |     | 24.5 | 28.5 | mA    |

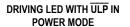

| LED Current Frequency             | f <sub>ILED</sub> | Normal and ultra-low                                                                                                                      | w-power sleep modes                        |     | 250  |      | Hz    |

| LED Current Duty Cycle            | D <sub>ILED</sub> | Normal and ultra-low                                                                                                                      | w-power sleep modes                        |     | 25   |      | %     |

| V <sub>DD</sub> Current Amplitude | I <sub>VDD</sub>  | Normal sleep mode                                                                                                                         | Normal sleep mode, V <sub>LED</sub> = 3.5V |     | 11   | 12.2 | mA    |

| Internal Current Duty Cycle       | D <sub>IVDD</sub> | Normal and ultra-low-power sleep modes                                                                                                    |                                            |     | 75   |      | %     |

|                                   | t <sub>MPS</sub>  | Ultra-low-power sleep mode                                                                                                                | -40°C to +85°C                             | 80  | 84   | 88   |       |

| Internal Current Enable Time      |                   |                                                                                                                                           | -40°C to +125°C                            | 80  | 84   | 90   | - ms  |

| Internal Current Dischle Time     |                   | Ultra-low-power -                                                                                                                         | -40°C to +125°C                            | 217 | 228  | 240  |       |

| Internal Current Disable Time     | t <sub>MPDO</sub> | sleep mode                                                                                                                                | -40°C to +85°C                             | 220 | 228  | 236  | ms    |

| SL Delay Time                     | t <sub>SL</sub>   | Time $V_{\overline{SL}}$ must remain below the $\overline{SL}$<br>logic threshold to enter sleep and ultra-<br>low-power modes (MAX5982A) |                                            | 5.4 | 6.0  | 6.6  | s     |

| THERMAL SHUTDOWN                  |                   |                                                                                                                                           |                                            |     |      |      |       |

| Thermal-Shutdown Threshold        | T <sub>SD</sub>   | T <sub>J</sub> rising                                                                                                                     |                                            |     | +150 |      | °C    |

| Thermal-Shutdown Hysteresis       |                   | T <sub>J</sub> falling                                                                                                                    |                                            |     | 30   |      | °C    |

**Note 3:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over temperature are guaranteed by design.

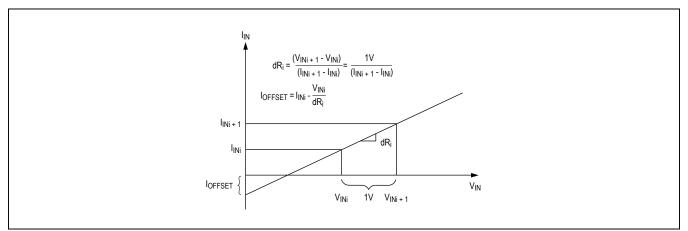

Note 4: The input offset current is illustrated in Figure 1.

Note 5: Effective differential input resistance is defined as the differential resistance between V<sub>DD</sub> and V<sub>SS</sub>. See Figure 1.

Note 6: Classification current is turned off whenever the device is in power mode.

**Note 7:** UVLO hysteresis is guaranteed by design, not production tested.

**Note 8:** A 20V glitch on input voltage, which takes V<sub>DD</sub> below V<sub>ON</sub> shorter than or equal to t<sub>OFF\_DLY</sub> does not cause the MAX5982A/MAX5982B/MAX5982C to exit power-on mode.

Note 9: Maximum current limit during normal operation is guaranteed by design; not production tested.

**Note 10:** In power mode, current-limit foldback is used to reduce the power dissipation in the isolation MOSFET during an overload condition across V<sub>DD</sub> and RTN.

Figure 1. Effective Differential Input Resistance/Offset Current

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

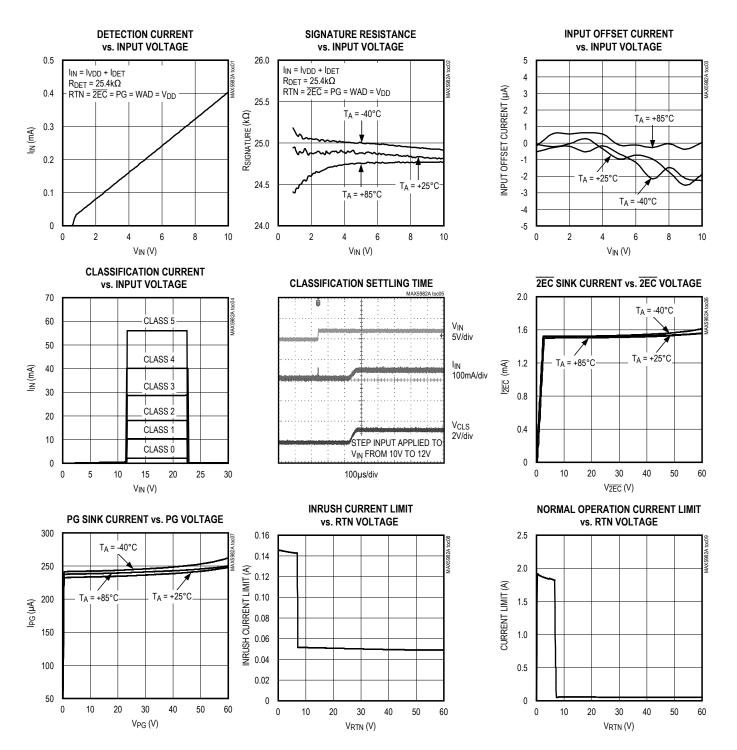

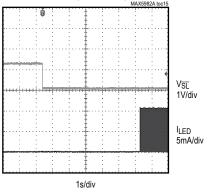

### **Typical Operating Characteristics**

$(V_{IN} = (V_{DD} - V_{SS}) = 54V, R_{DET} = 24.9k\omega, R_{CLS} = 615\omega$ , and  $R_{\overline{SL}} = 60.4k\omega$ . RTN, WAD, PG,  $\overline{2EC}$ ,  $\overline{WK}$ , and  $\overline{ULP}$  unconnected; all voltages are referenced to  $V_{SS}$ .)

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

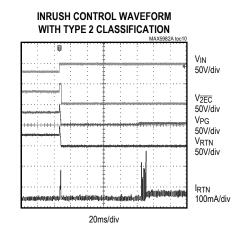

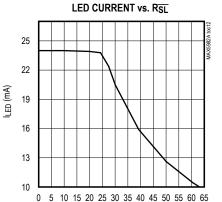

### **Typical Operating Characteristics (continued)**

$(V_{IN} = (V_{DD} - V_{SS}) = 54V, R_{DET} = 24.9k\omega, R_{CLS} = 615\omega$ , and  $R_{\overline{SL}} = 60.4k\omega$ . RTN, WAD, PG,  $\overline{2EC}$ ,  $\overline{WK}$ , and  $\overline{ULP}$  unconnected; all voltages are referenced to  $V_{SS}$ .)

$R_{\overline{SL}}(k\Omega)$

LED CURRENT vs. LED VOLTAGE

#### SLEEP/ULTRA-LOW-POWER MODE DELAY (MAX5982A)

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

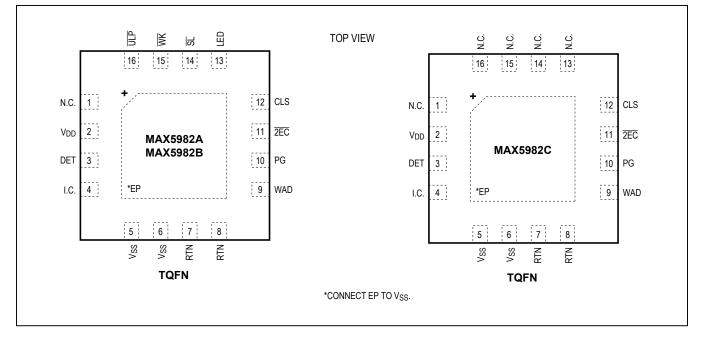

### **Pin Configurations**

### **Pin Description**

| Р                     | IN       |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX5982A/<br>MAX5982B | MAX5982C | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1                     | 1, 13–16 | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2                     | 2        | V <sub>DD</sub> | Positive Supply Input. Connect a 68nF (min) bypass capacitor between $V_{\mbox{DD}}$ and $V_{\mbox{SS}}.$                                                                                                                                                                                                                                                                                                                                         |

| 3                     | 3        | DET             | Detection Resistor Input. Connect a signature resistor ( $R_{DET}$ = 24.9k $\Omega$ ) from DET to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                               |

| 4                     | 4        | I.C.            | Internally Connected. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5, 6                  | 5, 6     | V <sub>SS</sub> | Negative Supply Input. $V_{SS}$ connects to the source of the integrated isolation n-channel power MOSFET.                                                                                                                                                                                                                                                                                                                                        |

| 7, 8                  | 7, 8     | RTN             | Drain of Isolation MOSFET. RTN connects to the drain of the integrated isolation n-channel power MOSFET. Connect RTN to the downstream DC-DC converter ground as shown in the <i>Typical Application Circuit</i> .                                                                                                                                                                                                                                |

| 9                     | 9        | WAD             | Wall Power Adapter Detector Input. Wall adapter detection is enabled the moment $V_{DD}$ - $V_{SS}$ crosses the mark event threshold. Detection occurs when the voltage from WAD to RTN is greater than 9V. When a wall power adapter is present, the isolation n-channel power MOSFET turns off and $\overline{2EC}$ current sink turns on. Connect WAD directly to RTN when the wall power adapter or other auxiliary power source is not used. |

| 10                    | 10       | PG              | Open-Drain, Power-Good Indicator Output. PG sinks 230µA to disable the downstream DC-DC converter while turning on the hot-swap MOSFET switch. PG current sink is disabled during detection, classification, and in the steady-state power mode. The PG current sink is turned on to disable the downstream DC-DC converter when the device is in sleep mode.                                                                                     |

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Pin Description (continued)**

| PIN                   |          |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX5982A/<br>MAX5982B | MAX5982C | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11                    | 11       | 2EC  | 2-Event Classification Detect or Wall Adapter Detect Output. A 1.5mA current sink is enabled at $\overline{2EC}$ when a Type 2 PSE or a wall adapter is detected. When powered by a Type 2 PSE, the $\overline{2EC}$ current sink is enabled after the isolation MOSFET is fully on until V <sub>IN</sub> drops below the UVLO threshold. $\overline{2EC}$ is latched when powered by a Type 2 PSE until V <sub>IN</sub> drops below the reset threshold. $\overline{2EC}$ also asserts when a wall adapter supply, typically greater than 9V, is applied between WAD and RTN. $\overline{2EC}$ is not latched if asserted by WAD. The $\overline{2EC}$ current sink is turned off when the device is in sleep mode. |

| 12                    | 12       | CLS  | Classification Resistor Input. Connect a resistor ( $R_{CLS}$ ) from CLS to $V_{SS}$ to set the desired classification current. See the classification current specifications in the <i>Electrical Characteristics</i> table to find the resistor value for a particular PD classification.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13                    | _        | LED  | LED Driver Output. During sleep mode, LED sources a periodic current ( $I_{LED}$ ) at 250Hz with 25% duty cycle. The amplitude of $I_{LED}$ is set by $R_{\overline{SL}}$ according to the formula $I_{LED}$ (in A) = 645.75/( $R_{\overline{SL}}$ + 1200).                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14                    |          | SL   | Sleep Mode Enable Input. In the MAX5982B, a falling edge on $\overline{SL}$ brings the device into sleep mode ( $V_{\overline{SL}}$ must drop below 0.75V). In the MAX5982A, $V_{\overline{SL}}$ must remain below the threshold (0.75V) for a period of at least 6s after falling edge to bring the device into sleep mode. An external resistor ( $R_{\overline{SL}}$ ) connected between SL and $V_{SS}$ sets the LED current ( $I_{LED}$ ).                                                                                                                                                                                                                                                                      |

| 15                    |          | WK   | Wake Mode Enable Input. $\overline{WK}$ has an internal 2.5k $\Omega$ pullup resistor to the internal 5V bias rail. A falling edge on $\overline{WK}$ brings the device out of sleep mode and into the normal operating mode (wake mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 16                    |          | ULP  | Ultra-Low-Power Sleep Enable Input (in Sleep Mode). $\overline{\text{ULP}}$ has an internal 50k $\Omega$ pullup resistor to the internal 5V bias rail. A falling edge on $\overline{\text{SL}}$ in the MAX5982B (and a 6s period below the $\overline{\text{SL}}$ threshold in the MAX5982A) while $\overline{\text{ULP}}$ is asserted low enables ultra-low-power sleep mode. When ultra-low-power sleep mode is enabled, the power consumption of the device is reduced even lower than normal sleep mode to comply with ultra-low-power sleep power requirements while still supporting MPS.                                                                                                                      |

|                       | _        | EP   | Exposed Pad. Do not use EP as an electrical connection to V <sub>SS</sub> . EP is internally connected to V <sub>SS</sub> through a resistive path and must be connected to V <sub>SS</sub> externally. To optimize power dissipation, solder the exposed pad to a large copper power plane.                                                                                                                                                                                                                                                                                                                                                                                                                         |

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

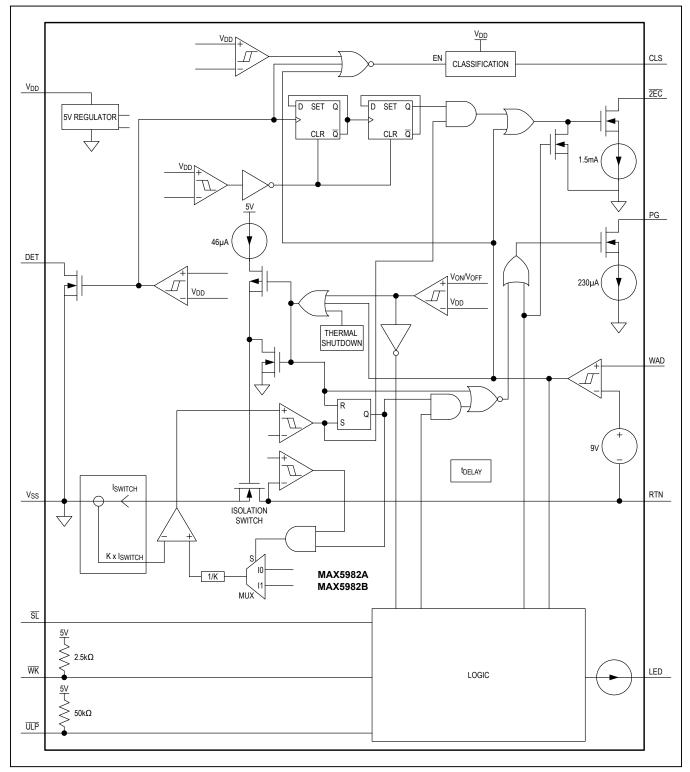

### MAX5982A/MAX5982B Simplified Block Diagram

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

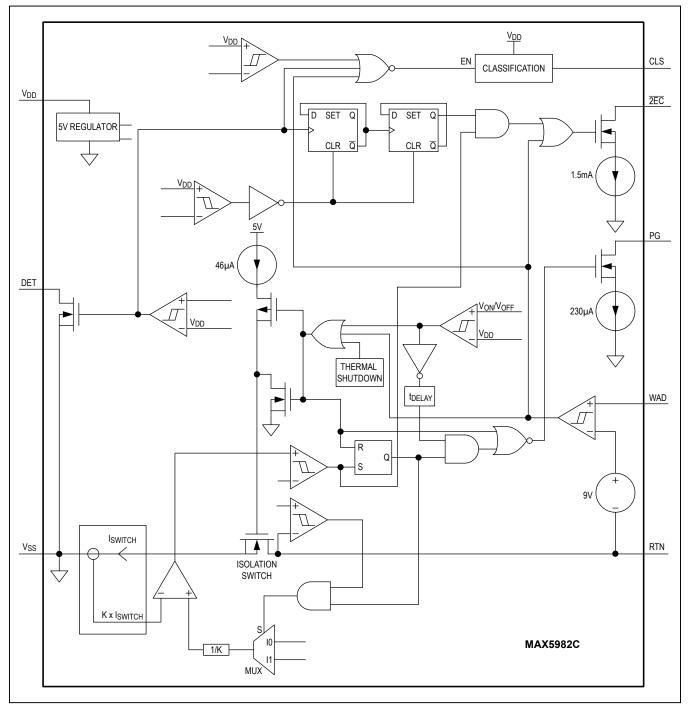

### MAX5982C Simplified Block Diagram

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

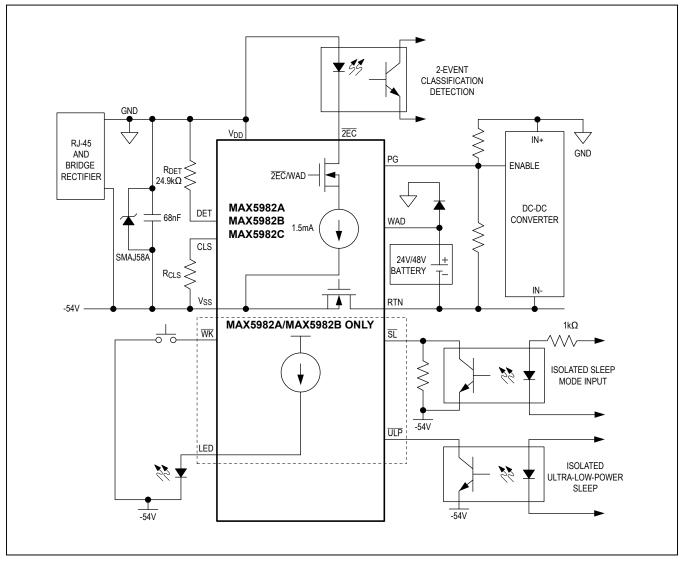

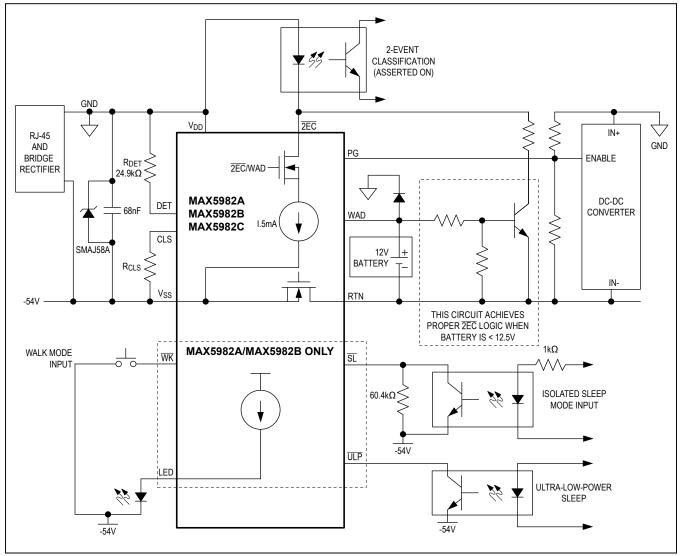

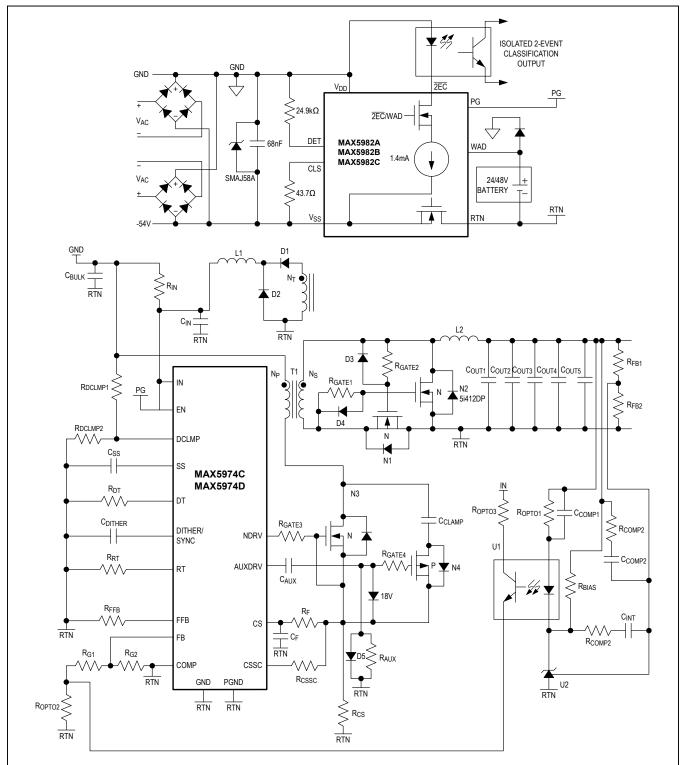

### **Typical Operating Circuit**

### **Detailed Description**

#### **Operating Modes**

Depending on the input voltage ( $V_{IN} = V_{DD} - V_{SS}$ ), the MAX5982A/MAX5982B/MAX5982C operate in four different modes: PD detection, PD classification, mark event, and PD power. The devices enter PD detection mode when the input voltage is between 1.4V and 10.1V. The device enters PD classification mode when the input voltage is between 12.6V and 20V. The devices enter PD power mode once the input voltage exceeds V<sub>ON</sub>.

#### Detection Mode $(1.4V \le V_{IN} \le 10.1V)$

In detection mode, the power source equipment (PSE) applies two voltages on V<sub>IN</sub> in the 1.4V to 10.1V range (1V step minimum) and then records the current measurements at the two points. The PSE then computes  $\Delta V/\Delta I$  to ensure the presence of the 24.9k $\Omega$  signature resistor. Connect the signature resistor (R<sub>DET</sub>) from V<sub>DD</sub> to DET for proper signature detection. The MAX5982A/MAX5982B/MAX5982C pull DET low in detection mode. DET goes high impedance when the input voltage exceeds 12.5V. In detection mode, most of the MAX5982A/MAX5982B/MAX5982C internal circuitry is off and the offset current is less than 10µA.

If the voltage applied to the PD is reversed, install protection diodes at the input terminal to prevent internal damage to the MAX5982A/MAX5982B/MAX5982C (see the *Typical Application Circuit*). Since the PSE uses a slope technique ( $\Delta V/\Delta I$ ) to calculate the signature resistance, the DC offset due to the protection diodes is subtracted and does not affect the detection process.

### Classification Mode (12.6V $\leq$ V<sub>IN</sub> $\leq$ 20V)

In the classification mode, the PSE classifies the PD based on the power consumption required by the PD. This allows

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

the PSE to efficiently manage power distribution. Class 0–5 is defined as shown in Table 1. (The IEEE 802.3af/at standard defines only Class 0–4 and Class 5 for any special requirement.) An external resistor (R<sub>CLS</sub>) connected from CLS to V<sub>SS</sub> sets the classification current.

The PSE determines the class of a PD by applying a voltage at the PD input and measuring the current sourced out of the PSE. When the PSE applies a voltage between 12.6V and 20V, the MAX5982A/MAX5982B/MAX5982C exhibit a current characteristic with a value shown in Table 1. The PSE uses the classification current information to classify the power requirement of the PD. The classification current includes the current drawn by R<sub>CLS</sub> and the supply current of the MAX5982A/MAX5982B/MAX5982B/MAX5982C so the total current drawn by the PD is within the IEEE 802.3af/at standard figures. The classification current is turned off whenever the device is in power mode.

#### 2-Event Classification and Detection

During 2-Event classification, a Type 2 PSE probes PD for classification twice. In the first classification event, the PSE presents an input voltage between 12.6V and 20.5V and the MAX5982A/MAX5982B/MAX5982C present the programmed load  $I_{CLASS}$ . The PSE then drops the probing voltage below the mark event threshold of 10.1V and the MAX5982A/MAX5982B/MAX5982C present the mark current ( $I_{MARK}$ ). This sequence is repeated one more time.

When the MAX5982A/MAX5982B/MAX5982C are powered by a Type 2 PSE, the 2-Event identification output  $\overline{2EC}$  asserts low after the internal isolation n-channel MOSFET is fully turned on.  $\overline{2EC}$  current sink is turned off when V<sub>DD</sub> goes below the UVLO threshold (V<sub>OFF</sub>) and turns on when V<sub>DD</sub> goes above the UVLO threshold (V<sub>ON</sub>), unless V<sub>DD</sub> goes below V<sub>THR</sub> to reset the latched output of the Type 2 PSE detection flag.

| CLASS | MAXIMUM<br>POWER USED<br>BY PD | R <sub>CLS</sub><br>(Ω) | V <sub>IN</sub> *<br>(V) | CLASS CURRENT SEEN AT V <sub>IN</sub><br>(mA)<br>MIN MAX |    | CLASSIFICAT | 2.3at PD<br>ON CURRENT<br>NION (mA) |

|-------|--------------------------------|-------------------------|--------------------------|----------------------------------------------------------|----|-------------|-------------------------------------|

|       | (W)                            |                         |                          |                                                          |    | MIN         | MAX                                 |

| 0     | 0.44 to 12.95                  | 615                     | 12.6 to 20               | 0                                                        | 4  | 0           | 5                                   |

| 1     | 0.44 to 3.94                   | 117                     | 12.6 to 20               | 9                                                        | 12 | 8           | 13                                  |

| 2     | 3.84 to 6.49                   | 66.5                    | 12.6 to 20               | 17                                                       | 20 | 16          | 21                                  |

| 3     | 6.49 to 12.95                  | 43.7                    | 12.6 to 20               | 26                                                       | 30 | 25          | 31                                  |

| 4     | 12.95 to 25.5                  | 30.9                    | 12.6 to 20               | 36                                                       | 44 | 35          | 45                                  |

| 5     | > 25.5w                        | 21.3                    | 12.6 to 20               | 54                                                       | 64 | 51          | 68                                  |

### **Table 1. Setting Classification Current**

$*V_{IN}$  is measured across the MAX5982A/MAX5982B/MAX5982C input  $V_{DD}$  to  $V_{SS}$ .

Alternatively, the  $\overline{2\text{EC}}$  output also serves as a wall adapter detection output when the MAX5982A/MAX5982B/MAX5982C are powered by an external wall power adapter. See the *Wall Power Adapter Detection and Operation* section for more information.

#### Power Mode (Wake Mode)

The MAX5982A/MAX5982B/MAX5982C enter power mode when V<sub>IN</sub> rises above the undervoltage-lockout threshold (V<sub>ON</sub>). When V<sub>IN</sub> rises above V<sub>ON</sub>, the MAX5982A/MAX5982B/MAX5982C turn on the internal n-channel isolation MOSFET to connect V<sub>SS</sub> to RTN with inrush current limit internally set to 53mA when V<sub>RTN</sub> - V<sub>SS</sub> > 7V and 135mA when V<sub>RTN</sub> - V<sub>SS</sub> < 7V. The isolation MOSFET is fully turned on when the voltage at RTN is near V<sub>SS</sub> and the inrush current is reduced below the inrush limit. Once the isolation MOSFET is fully turned on, the MAX5982A/MAX5982B/MAX5982B/MAX5982C change the current limit to 1900mA (typ). The open-drain power-good output (PG) remains low for a minimum of t<sub>DELAY</sub> until the power MOSFET fully turns on to keep the downstream DC-DC converter disabled during inrush.

#### **Undervoltage Lockout**

The MAX5982A/MAX5982B/MAX5982C operate up to a 60V supply voltage with a turn-on UVLO threshold (V<sub>ON</sub>) at 35.4V and a turn-off UVLO threshold (V<sub>OFF</sub>) at 31V. When the input voltage is above V<sub>ON</sub>, the MAX5982A/MAX5982B/MAX5982C enter power mode and the internal MOSFET is turned on. When the input voltage goes below V<sub>OFF</sub> for more than t<sub>OFF DLY</sub>, the MOSFET turns off.

### Sleep and Ultra-Low-Power Sleep Modes (MAX5982A/MAX5982B)

The MAX5982A/MAX5982B feature a sleep mode, which pulls PG low while keeping the internal n-channel isolation MOSFET turned on. The PG output is used to disable downstream DC-DC converters reducing the power consumption of the overall PD system in sleep mode. In sleep mode, the LED driver output (LED) sources periodic current pulses. The LED current ( $I_{LED}$ ) is set by an external resistor ( $R_{\overline{SL}}$ ); see the Applications Information section for more information. To enable sleep mode, apply a falling edge to  $\overline{SL}$  (MAX5982B) or hold  $\overline{SL}$  low for a minimum of 6 seconds after a falling edge.

An ultra-low-power sleep mode allows the MAX5982A/ MAX5982B to further reduce power consumption while maintaining the power signature of the standard. The ultra-low-power sleep enable input ULP is internally held high with a 50k $\Omega$  pullup resistor to the internal 5V bias of the MAX5982A/MAX5982B. To enable ultra-low-power sleep sleep mode, set ULP to logic-low and apply a falling

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

edge to  $\overline{SL}$  (MAX5982B) or hold  $\overline{SL}$  low for a minimum of 6s (MAX5982A). Apply a falling edge on the wake-mode enable input ( $\overline{WK}$ ) to disable sleep or ultra-low-power sleep mode and resume normal operation.

#### LED Driver (MAX5982A/MAX5982B)

The MAX5982A/MAX5982B drive an LED connected from the output LED to V<sub>SS</sub>. During sleep mode/ultra-low-power sleep mode, the LED is driven by current pulses with the amplitude set by the resistor connected from  $\overline{SL}$  to V<sub>SS</sub>. The LED driver current amplitude is programmable from 10mA to 20mA using R<sub>SL</sub> according to the following formula:

$I_{LED} = \frac{645.75}{R_{SL} + 1200} \text{ (in amperes)}$

#### **Power-Good Output**

An open-drain output (PG) is used to allow disabling downstream DC-DC converter until the n-channel isolation MOSFET is fully turned on. PG is pulled low to  $V_{SS}$  for a period of  $t_{DELAY}$  and until the internal isolation MOSFET is fully turned on. The PG is also pulled low during sleep mode and coming out of thermal shutdown.

#### **Thermal-Shutdown Protection**

The MAX5982A/MAX5982B/MAX5982C include thermal protection from excessive heating. If the junction temperature exceeds the thermal-shutdown threshold of +150°C, the MAX5982A/MAX5982B/MAX5982C turn off the internal power MOSFET, LED driver, and  $\overline{2\text{EC}}$  current sink. When the junction temperature falls below +120°C, the devices enter inrush mode and then return to power mode. Inrush mode ensures the downstream DC-DC converter is turned off as the internal power MOSFET is turned on.

### Wall Power Adapter Detection and Operation

For applications where an auxiliary power source such as a wall power adapter is used to power the PD, the MAX5982A/MAX5982B/MAX5982C feature wall power adapter detection. The MAX5982A/MAX5982B/MAX5982C give highest priority to the WAD and smoothly switch the power supply to WAD when it is detected. Once the input voltage ( $V_{DD} - V_{SS}$ ) exceeds the mark event threshold, the MAX5982A/MAX5982B/MAX5982B/MAX5982C enable wall adapter detection. The wall power adapter is connected from WAD to RTN. The MAX5982A/MAX5982B/MAX5982B/MAX5982C detect the wall power adapter when the voltage from WAD to RTN is greater than 9V. When a wall power adapter is detected, the internal n-channel isolation MOSFET turns off,  $\overline{2EC}$  current sink turns on, and classification current is disabled if V<sub>IN</sub> is in the classification range.

### **Applications Information**

### **Operation with 12V Adapter**

#### Layout Procedure

Careful PCB layout is critical to achieve high efficiency and low EMI. Follow these layout guidelines for optimum performance:

1) Place the input capacitor, classification resistor, and transient voltage suppressor as close as possible to the MAX5982A/MAX5982B/MAX5982C.

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

- Use large SMT component pads for power dissipating devices such as the MAX5982A/MAX5982B/ MAX5982C and the external diodes.

- 3) Use short and wide traces for high-power paths.

- 4) Place enough vias in the pad for the EP of the MAX5982A/MAX5982B/MAX5982C so that heat generated inside can be effectively dissipated by the PCB copper. The recommended spacing for the vias is 1mm to 1.2mm pitch. The thermal vias should be plated (1oz copper) and have a small barrel diameter (0.3mm to 0.33mm).

Figure 2. Typical Configuration When Using a 12V Wall Power Adapter

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Typical Application Circuit**

### IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE | SLEEP/ULTRA-LOW-<br>POWER MODE | 6s FILTER DELAY ON SL |

|--------------|-----------------|-------------|--------------------------------|-----------------------|

| MAX5982AETE+ | -40°C to +85°C  | 16 TQFN-EP* | Yes                            | Yes                   |

| MAX5982BETE+ | -40°C to +85°C  | 16 TQFN-EP* | Yes                            | No                    |

| MAX5982CETE+ | -40°C to +85°C  | 16 TQFN-EP* | No                             | —                     |

| MAX5982AATE+ | -40°C to +125°C | 16 TQFN-EP* | Yes                            | Yes                   |

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

### **Chip Information**

PROCESS: BICMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE    | PACKAGE | OUTLINE        | LAND           |

|------------|---------|----------------|----------------|

| TYPE       | CODE    | NO.            | PATTERN NO.    |

| 16 TQFN-EP | T1655+4 | <u>21-0140</u> | <u>90-0121</u> |

## IEEE 802.3af/at-Compliant, Powered Device Interface Controllers with Integrated 70W High-Power MOSFET

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                       | PAGES<br>CHANGED |

|--------------------|------------------|-------------------------------------------------------------------|------------------|

| 0                  | 6/11             | Initial release                                                   | —                |

| 1                  | 3/19             | Updated Electrical Characteristics and Ordering Information table | 1–4, 16          |

| 2                  | 6/19             | Updated Electrical Characteristics and Ordering Information table | 1–4, 16          |

| 3                  | 7/19             | Updated Electrical Characteristics and Ordering Information table | 1–4, 16          |

| 4                  | 11/21            | Updated Ordering Information table                                | 16               |

www.analog.com

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implicationor otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX5982AETE+ MAX5982AETE+T MAX5982BETE+ MAX5982BETE+T MAX5982CETE+ MAX5982CETE+T MAX5982AATE+ MAX5982AATE+T