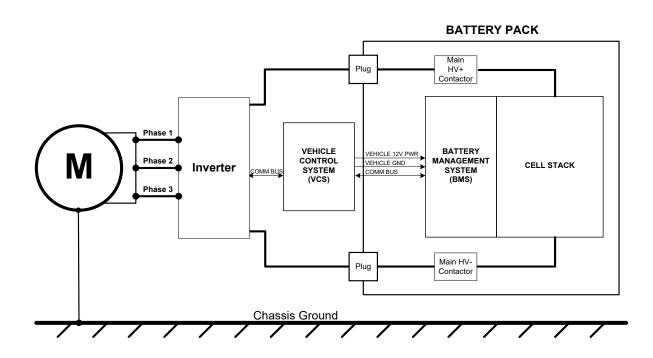

## 12-Channel High-Voltage Data Acquisition System

# General Description

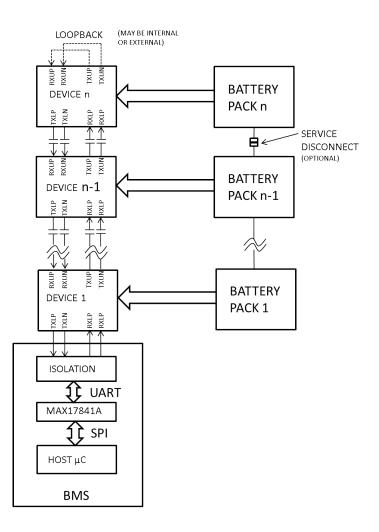

The MAX17823B is a data acquisition system for the management of high-voltage battery modules. The system features a 12-bit SAR ADC that can measure 12 cell voltages and two temperatures in 161  $\mu$ s. There are 12 internal switches for cell-balancing and extensive built-in diagnostics. Up to 32 devices can be daisy-chained together to manage 384 cells and monitor 64 temperatures.

Cell voltages (0V to 5V) are measured differentially over a 65V common-mode range. Cell measurements have a typical accuracy of 2mV (3.6V cell, 25°C). If oversampling is enabled, up to 128 measurements per channel can be averaged internally with 14-bit resolution. The system can shut itself down in the event of a thermal overload by measuring its own die temperature.

The system uses Maxim's battery-management UART protocol for robust communications and when used in conjunction with the MAX17880 12-channel battery monitor, it is ideal for automotive batterymanagement systems that require a high safety integrity level.

## **Applications**

- High-Voltage Battery Stacks

- Electric Vehicles (EVs)

- Hybrid Electric Vehicles (HEVs)

- Electric Bikes

- Battery-Backup Systems (UPS)

- Super-Cap Systems

- Battery-Powered Tools

## **Benefits and Features**

AEC-Q100 Grade 2 Temperature Range

- 40°C to 105°C

EVALUATION KIT AVAILABLE

- Operating Voltage from 9V to 65V

- Ultra-Low Power Operation

- Standby Mode: 2mA

- Shutdown Mode: 2µA

- 12 Cell-Voltage Measurement Channels

- 2mV Accuracy (3.6V, +25°C)

- 5mV Accuracy (0°C to +45°C)

- 10mV Accuracy (-40°C to +105°C)

- 12 Cell-Balancing Switches

- Up to 150mA per switch

- Emergency Discharge Mode

- Two Temperature Measurement Channels

- Die Temperature Measurement

- Automatic Thermal Protection

- 29 Voltage Threshold Alerts

- 12 Over-Voltage Faults

- 12 Under-Voltage Faults

- Two Over-Temperature Faults

- Two Under-Temperature Faults

- One Cell Mismatch Alert (highest cell versus lowest cell)

- Four GPIOs

- Built-in Diagnostics to Support ASIL D and FMEA Requirements

- Battery-Management UART Protocol

- Daisy-Chain up to 32 Devices

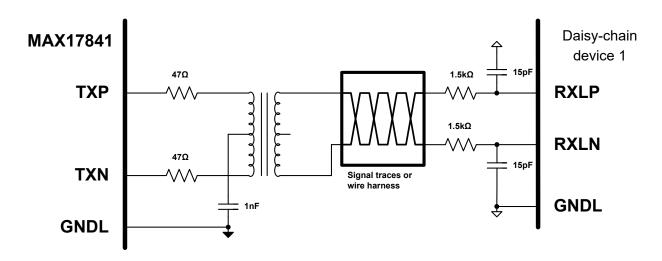

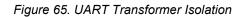

- Communication Port Isolation

- Up to 2Mbps Baud Rate (auto-detect)

- 1.5µs Propagation Delay per Device

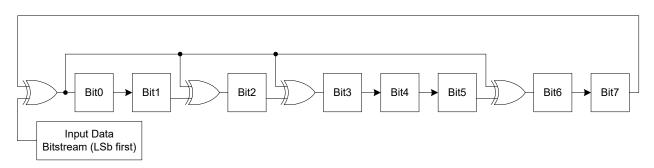

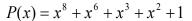

- Packet-Error Checking (PEC)

- Factory-Trimmed Oscillators

No External Crystals Required

- 10mm x 10mm Package (64-pin LQFP)

Ordering Information appears at end of data sheet.

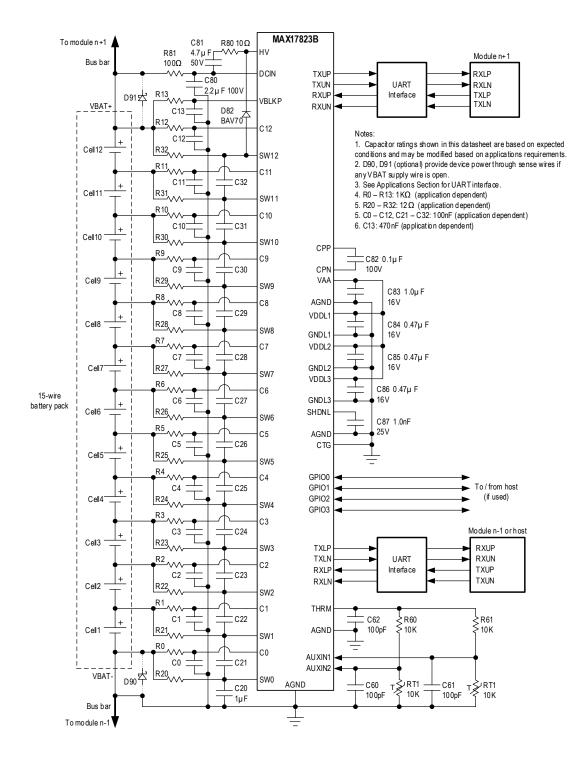

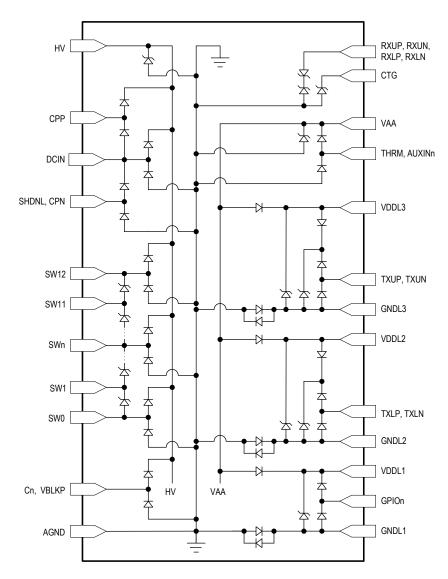

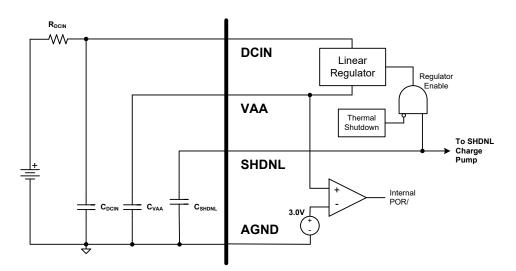

## **Simplified Operating Circuit**

## 12-Channel High-Voltage Data Acquisition System

## **Absolute Maximum Ratings**

| HV to AGND                                                | 0.3 to +80V                               |

|-----------------------------------------------------------|-------------------------------------------|

| DCIN, SWn, VBLKP, Cn to AGND                              | 0.3V to min (V <sub>HV</sub> + 0.3V, 72V) |

| Cn to Cn-1                                                | -72V to +72V                              |

| SWn to SWn-1                                              |                                           |

| VAA to AGND                                               | -0.3v to +4V                              |

| VDDL1 to GNDL1                                            | -0.3V to +4V                              |

| VDDL2 to GNDL2                                            | -0.3V to +6V                              |

| VDDL3 to GNDL3                                            | -0.3V to +6V                              |

| VAA to VDDL1, VDDL2, VDDL3                                | -0.3V to + 0.3V                           |

| AGND to GNDL1, GNDL2, GNDL3                               | -0.3V to + 0.3V                           |

| AUXIN1, AUXIN2, THRM to AGND                              |                                           |

| SHDNL to AGND                                             | -0.3 to V <sub>DCIN</sub> + 0.3V          |

| CTG to AGND                                               | -0.3V to +6V                              |

| RXLP, RXLN, RXUP, RXUN to AGND                            | 30V to +30V                               |

| TXLP, TXLN to GNDL2                                       | -0.3V to +6V                              |

| TXUP, TXUN to GNDL3                                       | -0.3V to +6V                              |

| CPP to AGND                                               |                                           |

| CPN to AGND                                               | -0.3V to V <sub>DCIN</sub> + 0.3V         |

| GPIO0, GPIO1, GPIO2, GPIO3 to GNDL1                       | -0.3V to V <sub>DDL1</sub> + 0.3V         |

| Maximum Continuous Current into Any Pin (see Note 1)      |                                           |

| Maximum Continuous Current into SWn Pin (see Note 2)      |                                           |

| Maximum Average Power for ESD Diodes (see Note 3)         |                                           |

| Package Continuous Power (see Note 4)                     |                                           |

| Operating Temperature Range                               |                                           |

| Junction-to-Ambient Thermal Resistance (θ <sub>IA</sub> ) |                                           |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )    |                                           |

| Storage Temperature Range                                 |                                           |

| Junction Temperature (continuous)                         |                                           |

| Soldering Lead Temperature (10s maximum)                  |                                           |

|                                                           |                                           |

Note 1: Balancing switches disabled.

**Note 2:** One balancing switch enabled, 60s maximum.

**Note 3:** Average power for time period τ where τ is the time constant (in μs) of the transient diode current during hot-plug event. For, example, if τ is 330μs, the maximum average power is 0.793W. Peak current must never exceed 2A. Actual average power during hot-plug must be calculated from the diode current waveform for the application circuit and compared to the maximum rating.

**Note 4:** Multi-layer board. For  $T_A > 70^{\circ}C$  derate 25mW/°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## 12-Channel High-Voltage Data Acquisition System

## **Electrical Characteristics**

$(V_{DCIN} = +48V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40^{\circ}C$  and  $T_{MAX} = +105^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ . Operation is with the recommended application circuit. See Note 5.)

| PARAMETER                                                    | SYMBOL                | CONDITIONS                                                                                                                                                       | MIN     | TYP        | MAX               | UNITS |

|--------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|-------------------|-------|

| POWER REQUIREMENTS                                           |                       |                                                                                                                                                                  |         |            |                   |       |

| Supply Voltage                                               | V <sub>DCIN</sub>     |                                                                                                                                                                  | 9       |            | 65                | V     |

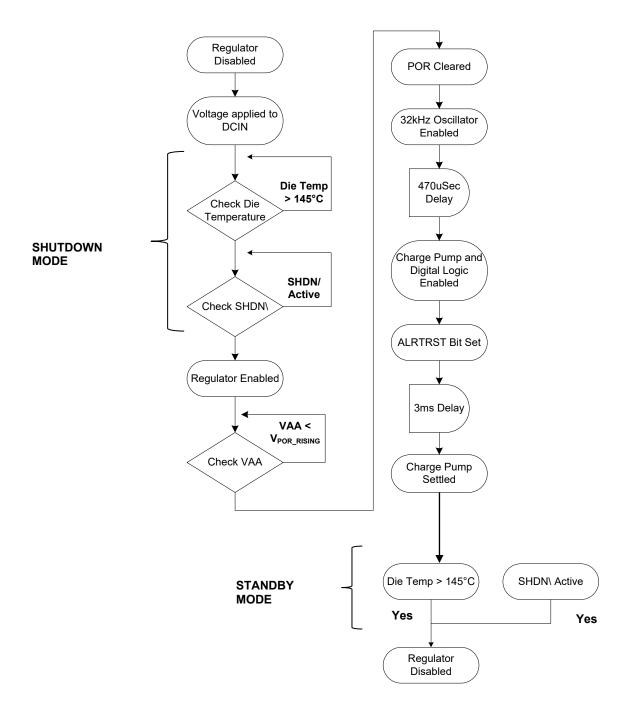

| DCIN Current,<br>Shutdown Mode                               | IDCSHDN               | V <sub>SHDNL</sub> = 0V                                                                                                                                          |         | 0.1        | 2                 | μA    |

| DCIN Current,<br>Standby Mode (Note 16)                      | IDCSTBY               | V <sub>SHDNL</sub> > 1.8V, UART in idle mode, not<br>in acquisition mode, BALSWEN,<br>CTSTEN = 0000h                                                             | 1.4     | 2.0        | 2.6               | mA    |

| DCIN Current,<br>Acquisition Mode (Note 16)                  | IDCMEAS               | MEASUREEN = 0FFFh,<br>acquisition mode                                                                                                                           | 3.5     | 5.4        | 8.5               | mA    |

| Incremental DCIN Current,<br>Communication Mode<br>(Note 16) | Ідссомм               | Baud rate = 2Mb/s (0% idle time<br>preambles mode), 200pF load on<br>TXUP, 200pF on TXUN, TXL not<br>active, not in acquisition mode,<br>BALSWEN, CTSTEN = 0000h |         | 1.5        | 3                 | mA    |

| HV Current,<br>Acquisition Mode                              | I <sub>HVMEAS</sub>   | Acquisition mode, MEASUREEN =<br>0FFFh, V <sub>HV</sub> = V <sub>DCIN</sub> + 5.5V                                                                               | 0.9     | 1.1        | 1.3               | mA    |

| Incremental HV Current,<br>Cell-Balancing Mode               | I <sub>HVBAL</sub>    | V <sub>HV</sub> = V <sub>DCIN</sub> + 5.5V, n balancing<br>switches enabled                                                                                      | (n+1)x5 | (n+1)x13.5 | (n+1)x26          | μA    |

| CELL VOLTAGE INPUTS (C                                       | n, VBLKP)             |                                                                                                                                                                  |         |            |                   |       |

| Differential Input Range                                     | N/                    | Unipolar mode                                                                                                                                                    | 0.2     |            | 4.8               | V     |

| (Note 11)                                                    | V <sub>CELLn</sub>    | Bipolar mode                                                                                                                                                     | -2.3    |            | +2.3              | V     |

| Common-Mode Input Range                                      | V <sub>CnCM</sub>     | Not connected to SWn inputs                                                                                                                                      | 0       |            | 65                | V     |

| Input Leakage Current                                        | $I_{LKG\_Cn}$         | Not in acquisition mode, $V_{Cn} = 65V$                                                                                                                          | -200    | ±10        | +200              | nA    |

| VBLKP Input Resistance                                       | R <sub>VBLKP</sub>    | $V_{BLKP} = V_{DCIN} = 57.6V$                                                                                                                                    | 4.5     | 10         | 20                | MΩ    |

| HVMUX Switch Resistance                                      | R <sub>HVMUX</sub>    | CTSTDAC[3:0] = Fh                                                                                                                                                | 1.7     | 3.3        | 5                 | kΩ    |

| <b>CELL-BALANCING INPUTS</b>                                 | (SWn)                 |                                                                                                                                                                  |         |            |                   |       |

| Leakage Current                                              | $I_{LKG_SW}$          | $V_{SW0} = 0V$ , $V_{SWn} = 5V$ , $V_{SWn-1} = 0V$                                                                                                               | -1      |            | +1                | μA    |

| Resistance, SWn to SWn-1                                     | R <sub>sw</sub>       | BALSWEN[n-1] = 1, I <sub>SWn</sub> = 100mA                                                                                                                       | 0.5     | 2          | 5                 | Ω     |

| Maximum Allowed Balancing<br>Current (Note 15)               | I <sub>BAL_MAX</sub>  | T <sub>j</sub> = 105°C, 25% average duty-cycle<br>per switch                                                                                                     |         | 256        |                   | mA    |

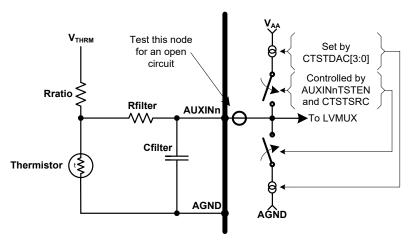

| AUXILIARY INPUTS (AUXIN                                      | 1, AUXIN2)            |                                                                                                                                                                  |         |            |                   |       |

| Input Voltage Range                                          | V <sub>AUXIN</sub>    |                                                                                                                                                                  | 0       |            | $V_{\text{THRM}}$ | V     |

| Input Leakage Current                                        | I <sub>LKG_AUX</sub>  | Not in acquisition mode,<br>V <sub>AUXINn</sub> = 1.65V                                                                                                          | -400    | 10         | +400              | nA    |

| THRM OUTPUT                                                  |                       |                                                                                                                                                                  |         |            |                   |       |

| Switch Resistance,<br>VAA to THRM                            | R <sub>THRM</sub>     |                                                                                                                                                                  |         | 25         | 70                | Ω     |

| Leakage Current                                              | I <sub>LKG_THRM</sub> | V <sub>THRM</sub> = 3.3V                                                                                                                                         | -1      |            | 1                 | μA    |

## 12-Channel High-Voltage Data Acquisition System

| PARAMETER                                               | SYMBOL                        | CONDITIONS                                                                                 | MIN  | TYP  | MAX                                                 | UNITS                                                 |

|---------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------|------|------|-----------------------------------------------------|-------------------------------------------------------|

| MEASUREMENT ACCURAC                                     | Υ                             |                                                                                            |      |      |                                                     |                                                       |

|                                                         |                               | Unipolar mode, V <sub>CELLn</sub> = 3.6V                                                   |      | +2   |                                                     | mV<br>mV                                              |

|                                                         |                               | Bipolar mode, V <sub>CELLn</sub> = 1.1V                                                    |      | ΞZ   |                                                     |                                                       |

| Total Measurement Error,<br>HVMUX Inputs                |                               | Unipolar mode<br>$0.2V \le V_{CELLn} \le 4.3V$ ,<br>$0^{\circ}C \le T_{A} \le 45^{\circ}C$ | -5   | ±3.6 | +5                                                  | m\/                                                   |

| (Note 12)                                               | V CELLNERR                    | Unipolar mode,<br>0.2V ≤ V <sub>CELLn</sub> ≤ 4.8V                                         |      |      |                                                     | mV<br>mVRMS<br>mV<br>mV<br>MV<br>MV<br>%<br>C<br>LSbs |

|                                                         |                               | Bipolar mode,<br>-2.3V ≤ V <sub>CELLn</sub> ≤ 2.3V,<br>SWn inputs not connected            | -10  |      | +5<br>+10<br>+10<br>+10<br>+180<br>+3<br>+0.3<br>+5 |                                                       |

|                                                         |                               | Unipolar mode, V <sub>CELL</sub> = 3.6V                                                    |      | ±2   |                                                     |                                                       |

| Total Measurement Error.                                |                               | Bipolar mode, V <sub>CELLn</sub> = 1.1V                                                    |      | ΞZ   |                                                     | mV                                                    |

| ALTMUX Inputs<br>(Note 12)                              | $V_{\text{SWnERR}}$           | Unipolar mode,<br>0.2V ≤ V <sub>CELLn</sub> ≤ 4.8V                                         | -10  | +1(  | +10                                                 |                                                       |

|                                                         |                               | Bipolar mode, 0V ≤ V <sub>CELLn</sub> ≤ 2.3V                                               |      |      |                                                     |                                                       |

| Channel Noise (Note 7)                                  | V <sub>CELLNOISE</sub>        | No oversampling                                                                            |      | 1.1  |                                                     | mVRMS                                                 |

| Total Measurement Error,<br>V <sub>BLKP</sub> Input     | VBLKPERR                      | $9V \le V_{BLKP} \le 57.6V$ , $V_{DCIN} = 57.6V$ ,<br>Average of 64 acquisitions           | -180 |      | +180                                                | mV                                                    |

| Offset Error, AUXIN Inputs                              | V <sub>OS_AUX</sub>           |                                                                                            | -3   |      | +3                                                  | mV                                                    |

| Gain Error, AUXIN Inputs                                | A <sub>V_AUX</sub>            |                                                                                            | -0.3 |      | +0.3                                                | %                                                     |

| Total Measurement Error,<br>Die Temperature<br>(Note 7) | $T_{DIE\_ERR}$                | T <sub>j</sub> = -40°C to 105°C,<br>no oversampling                                        | -5   | ±3   | +5                                                  | °C                                                    |

| Differential Non-Linearity<br>(any conversion)          | DNL                           |                                                                                            |      | ±1.0 |                                                     | LSbs                                                  |

| ADC Resolution                                          |                               |                                                                                            | 12   |      |                                                     | bits                                                  |

| Level-shifting Amplifier Offset<br>(Note 14)            | $V_{\text{OS}\_\text{LSAMP}}$ | DIAGSEL[2:0] = 011b                                                                        | -200 | -10  | +200                                                | mV                                                    |

## 12-Channel High-Voltage Data Acquisition System

| PARAMETER                                            | SYMBOL                 | CONDITIONS                                                         | MIN                   | TYP    | MAX   | UNITS |

|------------------------------------------------------|------------------------|--------------------------------------------------------------------|-----------------------|--------|-------|-------|

| SHDNL INPUT AND CHARGE                               | PUMP                   |                                                                    | •                     |        |       |       |

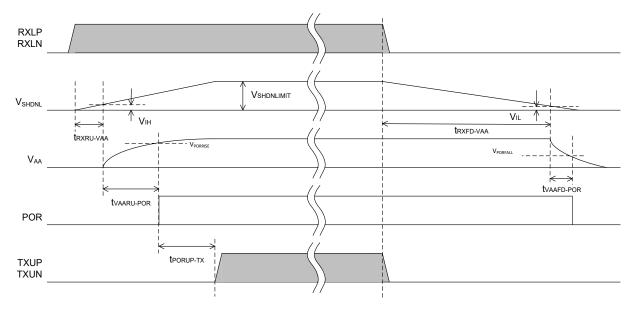

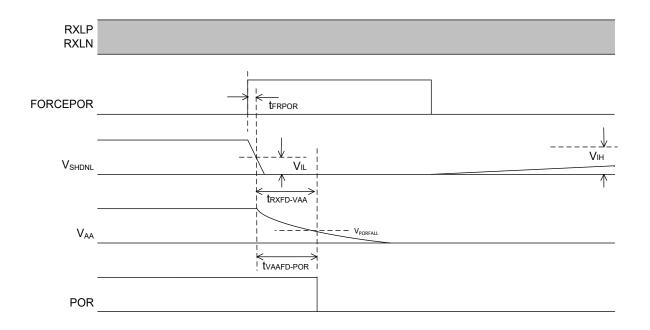

| Input Low Voltage                                    | VIL_SHDNL              |                                                                    |                       |        | 0.6   | V     |

| Input High Voltage                                   | VIH_SHDNL              |                                                                    | 1.8                   |        |       | V     |

|                                                      |                        | V <sub>DCIN</sub> ≥ 12V                                            | 8                     | 9.5    | 12    | V     |

| Regulated Voltage                                    | VSHDNLIMIT             | V <sub>DCIN</sub> = 9V                                             |                       | 6.7    |       | V     |

| Pull-down Resistance                                 | R <sub>FORCEPOR</sub>  | FORCEPOR = 1                                                       | 2.5                   | 4.7    | 8     | kΩ    |

| nnut Lookago Current                                 |                        | V <sub>SHDNL</sub> = 3.3V                                          |                       |        | 1     | μA    |

| nput Leakage Current                                 | I <sub>LKG_SHDNL</sub> | V <sub>SHDNL</sub> = 65V                                           |                       | 40     | 75    | μA    |

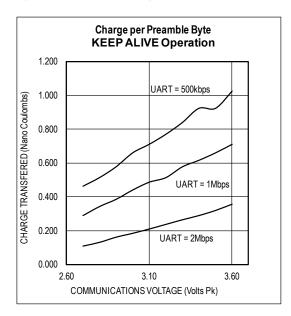

| Charge Pump Current<br>(Note 10)                     | I <sub>SHDNL</sub>     | V <sub>SHDNL</sub> < V <sub>SHDNLIMIT</sub> , baud rate<br>= 2Mbps | 15                    | 117    | 350   | μA    |

| GENERAL-PURPOSE I/O (GP                              | lOn)                   |                                                                    |                       |        |       |       |

| Input Low Voltage                                    | $V_{IL\_GPIO}$         |                                                                    |                       |        | 0.8   | V     |

| nput High Voltage                                    | V <sub>IH_GPIO</sub>   |                                                                    | 2.4                   |        |       | V     |

| Pull-down Resistance                                 | R <sub>GPIO</sub>      | GPIO[15:12] = 0h (input)                                           | 0.5                   | 2      | 7.5   | MΩ    |

| Output Low Voltage                                   | V <sub>OL_GPIO</sub>   | I <sub>SINK</sub> = 3mA                                            |                       |        | 0.4   | V     |

| Output High Voltage                                  | V <sub>OH_GPIO</sub>   | I <sub>SOURCE</sub> = 3mA                                          | V <sub>DDL1</sub> - ( | ).4    |       | V     |

| REGULATOR                                            |                        |                                                                    |                       |        |       |       |

| Output Voltage                                       | V <sub>AA</sub>        | $0 \le I_{AA} \le 10 \text{mA}$                                    | 3.2                   | 3.3    | 3.4   | V     |

| Short-Circuit Current                                | I <sub>AASC</sub>      | VAA shorted to AGND                                                | 10                    | 20     | 70    | mA    |

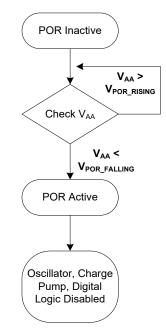

| POR Threshold                                        | VPORFALL               | V <sub>AA</sub> falling                                            | 2.85                  | 2.95   | 3.02  | V     |

| -OK IIIIesilolu                                      | V <sub>PORRISE</sub>   | V <sub>AA</sub> rising                                             |                       | 3.0    | 3.1   | V     |

| POR Hysteresis                                       | V <sub>PORHYS</sub>    |                                                                    |                       | 40     |       | mV    |

| Thermal Shutdown<br>Temperature (Note 7)             | T <sub>SHDN</sub>      | Temperature rising                                                 |                       | 145    |       | °C    |

| Гhermal Shutdown<br>Hysteresis (Note 7)              | T <sub>HYS</sub>       |                                                                    |                       | 15     |       | °C    |

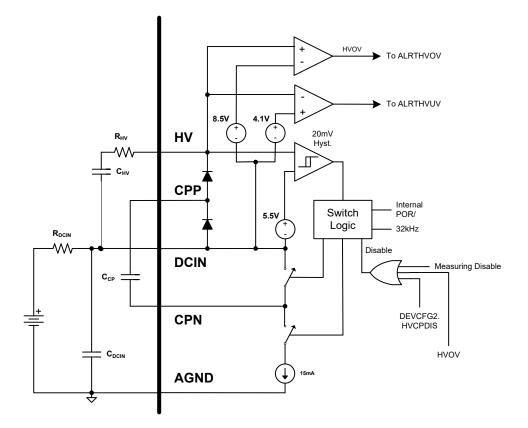

| HV CHARGE PUMP                                       | 1                      |                                                                    |                       |        |       |       |

| Output Voltage (V <sub>HV</sub> -V <sub>DCIN</sub> ) | V <sub>HV-DCIN</sub>   | $9V \le V_{DCIN} \le 12V, I_{LOAD} = 1.5mA$                        | 5                     | 5.5    | 6     | V     |

|                                                      | - HV-DOIN              | $12V \le V_{DCIN} \le 65V,$<br>$I_{LOAD} = 3mA$                    | 5                     | 5.5    | 6     | •     |

| Charge Pump Efficiency<br>Note 18)                   |                        | V <sub>DCIN</sub> = 57.6V                                          |                       | 38     |       | %     |

| HV Headroom (V <sub>HV</sub> -V <sub>C12</sub> )     | V <sub>HVHDRM</sub>    | ALRTHVHDRM = 0                                                     | 4.7                   |        |       | V     |

| OSCILLATORS                                          |                        |                                                                    |                       |        |       |       |

| 32kHz Oscillator Frequency                           | f <sub>osc_з2к</sub>   |                                                                    | 32.11                 | 32.768 | 33.42 | kHz   |

| 16MHz Oscillator Frequency                           | f <sub>OSC_16M</sub>   |                                                                    | 15.68                 | 16     | 16.32 | MHz   |

| PARAMETER                                                                | SYMBOL                 | CONDITIONS                                                                                                               | MIN  | TYP   | MAX                                                                                                        | UNITS  |

|--------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-------|------------------------------------------------------------------------------------------------------------|--------|

| DIAGNOSTIC TEST SOURCES                                                  | 5                      |                                                                                                                          |      |       |                                                                                                            |        |

|                                                                          |                        | CTSTDAC[3:0] = Fh,<br>$V_{Cn} < V_{AA} - 1.4V, V_{AA} = 3.3V$                                                            | 80   | 100   | 120                                                                                                        |        |

| Cell Test Source Current                                                 | <br>                   | CTSTDAC[3:0] = 6h,<br>V <sub>Cn</sub> < V <sub>AA</sub> - 1.4V, V <sub>AA</sub> = 3.3V                                   | 36   | 45    | 54                                                                                                         | μA     |

|                                                                          | ITSTCn                 | $\begin{array}{l} \text{CTSTDAC[3:0] = 6h,} \\ \text{V}_{\text{Cn}} > \text{V}_{\text{AGND}} + 1.4\text{V} \end{array}$  | -54  | -45   | 120<br>54<br>-36<br>-80<br>60<br>27<br>120<br>54<br>-36<br>-80<br>1.254<br>-36<br>-80<br>-80<br>-80<br>-80 | μΛ     |

|                                                                          |                        | $\begin{array}{l} \text{CTSTDAC[3:0] = Fh,} \\ \text{V}_{\text{Cn}} > \text{V}_{\text{AGND}} + 1.4 \text{V} \end{array}$ | -120 | -100  | -80                                                                                                        |        |

| HVMUX Test Source Current                                                |                        | CTSTDAC[3:0] = Fh,<br>V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V, V <sub>HV</sub> = 53.5V                                  | 40   | 50    | 60                                                                                                         |        |

|                                                                          | I <sub>TSTMUX</sub>    | CTSTDAC[3:0] = 6h, $V_{Cn} < V_{HV}$ - 1.4V, $V_{HV}$ = 53.5V                                                            | 18   | 22.5  | 27                                                                                                         | μA     |

| AUXIN Test Source Current                                                |                        | CTSTDAC[3:0] = Fh,<br>$V_{AUXINn} < V_{AA} - 1.4V$ ,<br>$V_{AA} = 3.3V$                                                  | 80   | 100   | 120                                                                                                        |        |

|                                                                          | I <sub>tstauxin</sub>  | CTSTDAC[3:0] = 6h,<br>$V_{AUXINn} < V_{AA} - 1.4V,$<br>$V_{AA} = 3.3V$                                                   | 36   | 45    | 54                                                                                                         | μA     |

|                                                                          | 1017107411             | $\begin{array}{l} CTSTDAC[3:0] = 6h \\ V_{AUXINn} > V_{AGND} + 1.4V \end{array}$                                         | -54  | -45   |                                                                                                            |        |

|                                                                          |                        | $\begin{array}{l} CTSTDAC[3:0] = Fh, \\ V_{AUXINn} > V_{AGND} + 1.4V \end{array}$                                        | -120 | -100  |                                                                                                            |        |

| DIAGNOSTIC REFERENCES                                                    |                        |                                                                                                                          |      |       |                                                                                                            |        |

| ALTREF Voltage (Note 14)                                                 | VALTREF                | DIAGSEL[2:0] = 001b                                                                                                      | 1.23 | 1.242 | 1.254                                                                                                      | V      |

| ALTREF Temperature<br>Coefficient (ΔV <sub>ALTREF</sub> /ΔT)<br>(Note 7) | A <sub>ALTREF</sub>    |                                                                                                                          |      | ±25   |                                                                                                            | ppm/°C |

| PTAT Output Voltage (Note 7)                                             | V <sub>PTAT</sub>      | T <sub>J</sub> = 120°C                                                                                                   |      | 1.2   |                                                                                                            | V      |

| PTAT Temperature Coefficient $(\Delta V_{PTAT}/\Delta T)$ (Note 7)       | A <sub>V_PTAT</sub>    |                                                                                                                          |      | 3.07  |                                                                                                            | mV/°C  |

| PTAT Temperature Offset<br>(Note 7)                                      | T <sub>OS_PTAT</sub>   |                                                                                                                          |      | 0     |                                                                                                            | °C     |

| ALERTS                                                                   | ·                      | -                                                                                                                        |      |       |                                                                                                            |        |

| ALRTVDDLn Threshold                                                      | $V_{VDDL_OC}$          | VAA = 3.3V                                                                                                               | 3    | 3.15  | 3.25                                                                                                       | V      |

| ALRTGNDLn Threshold                                                      | $V_{\text{GNDL}_{OC}}$ | AGND = 0V                                                                                                                | 0.05 | 0.15  | 0.3                                                                                                        | V      |

| ALRTHVUV Threshold                                                       | V <sub>HVUV</sub>      | V <sub>HV</sub> - V <sub>DCIN</sub> falling                                                                              | 3.8  | 4.1   | 4.25                                                                                                       | V      |

| ALRTHVOV Threshold                                                       | V <sub>HVOV</sub>      | V <sub>HV</sub> - V <sub>DCIN</sub> rising                                                                               | 7    | 8.5   | 10                                                                                                         | V      |

| ALRTTEMP Threshold (Note 7)                                              | T <sub>ALRTTEMP</sub>  |                                                                                                                          | 115  | 120   | 125                                                                                                        | °C     |

| ALRTTEMP Hysteresis (Note 7)                                             | TALRTTEMPHYS           |                                                                                                                          |      | 2     |                                                                                                            | °C     |

#### 12-Channel High-Voltage Data Acquisition System

| PARAMETER                                                                                                            | SYMBOL                  | CONDITIONS                 | MIN                      | TYP                  | MAX                      | UNITS                  |

|----------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|--------------------------|----------------------|--------------------------|------------------------|

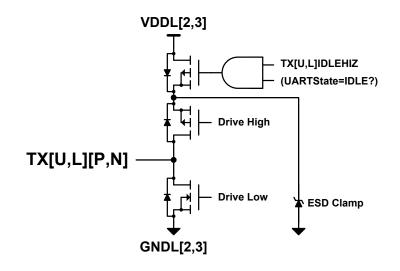

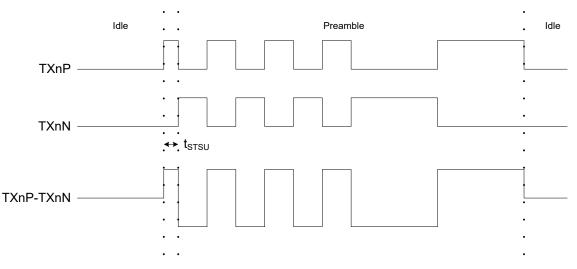

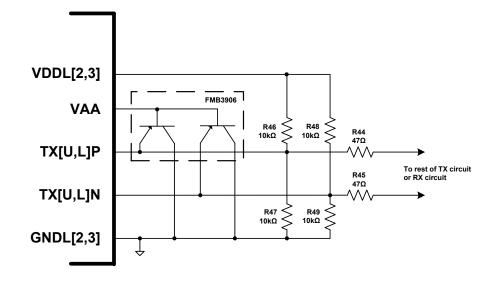

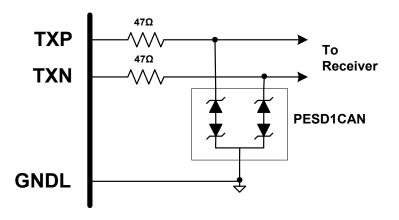

| UART OUTPUTS (TXLP, TXLN, TXUF                                                                                       | P, TXUN)                |                            |                          |                      |                          |                        |

| Output Low Voltage                                                                                                   | V <sub>OL</sub>         | I <sub>SINK</sub> = 20mA   |                          |                      | 0.4                      | V                      |

| Output High Voltage (TXLP, TXLN)                                                                                     | V <sub>OH</sub>         | I <sub>SOURCE</sub> = 20mA | V <sub>DDL2</sub> - 0.4  |                      |                          | V                      |

| Output High Voltage (TXUP, TXUN)                                                                                     | V <sub>OH</sub>         | I <sub>SOURCE</sub> = 20mA | V <sub>DDL3</sub> - 0.4  |                      |                          | V                      |

| Leakage Current                                                                                                      | I <sub>LKG TX</sub>     | V <sub>TX</sub> = 1.5V     | -1                       |                      | 1                        | μA                     |

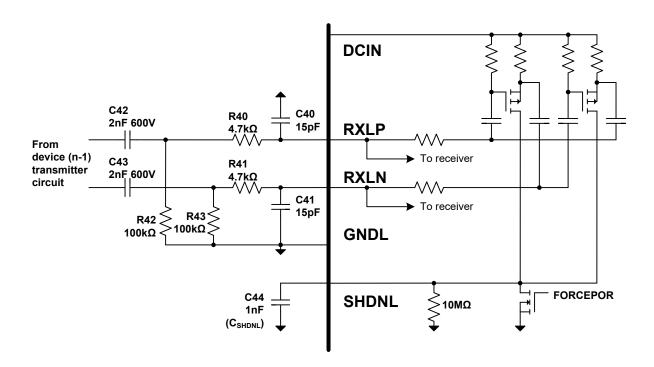

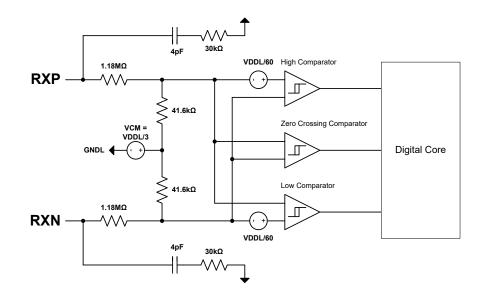

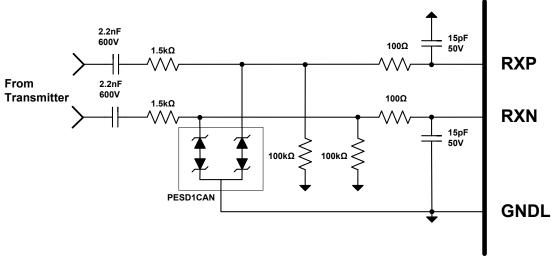

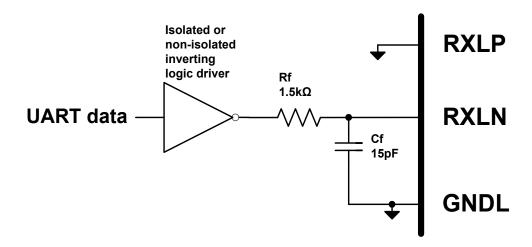

| UART INPUTS (RXLP, RXLN, RXUP,                                                                                       | RXUN)                   |                            |                          |                      |                          |                        |

| Input Voltage Range                                                                                                  | V <sub>RX</sub>         |                            | -25                      |                      | 25                       | V                      |

| Receiver High Comparator Threshold<br>(Notes 9, 13)                                                                  | V <sub>CH</sub>         |                            | V <sub>DDL</sub> /2-0.4  | $V_{DDL}/2$          | V <sub>DDL</sub> /2+0.4  | V                      |

| Receiver Zero-Crossing Comparator<br>Threshold (Note 9)                                                              | V <sub>ZC</sub>         |                            | -0.4                     | 0                    | 0.4                      | V                      |

| Receiver Low Comparator Threshold (Notes 9, 13)                                                                      | V <sub>CL</sub>         |                            | -V <sub>DDL</sub> /2-0.4 | -V <sub>DDL</sub> /2 | -V <sub>DDL</sub> /2+0.4 | V                      |

| Receiver Comparator Hysteresis<br>(Note 9)                                                                           | V <sub>HYS_RX</sub>     |                            |                          | 75                   |                          | mV                     |

| Receiver Common-mode Voltage Bias<br>(Notes 9, 13)                                                                   | V <sub>CM</sub>         |                            |                          | $V_{DDL}/3$          |                          | V                      |

| Leakage Current                                                                                                      | I <sub>LKG RX</sub>     | V <sub>RX</sub> = 1.5V     |                          | ±1.0                 |                          | μA                     |

| Input Capacitance (RXLP, RXLN)                                                                                       | C <sub>RXL</sub>        |                            |                          | 4                    |                          | pF                     |

| Input Capacitance (RXUP, RXUN)                                                                                       | C <sub>RXU</sub>        |                            |                          | 2                    |                          | pF                     |

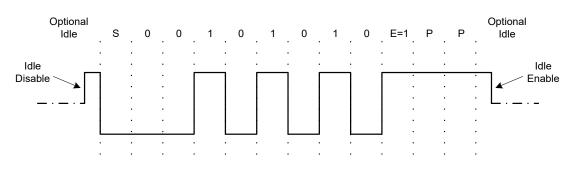

| UART TIMING                                                                                                          |                         |                            |                          |                      |                          |                        |

|                                                                                                                      |                         | Baud rate = 2Mb/s          |                          | 8                    |                          |                        |

| Bit Period (Note 17)                                                                                                 | t <sub>BIT</sub>        | Baud rate = 1Mb/s          |                          | 16                   |                          | 1/f <sub>OSC_16M</sub> |

|                                                                                                                      |                         | Baud rate = 0.5Mb/s        |                          | 32                   |                          |                        |

| RX Idle to START Setup Time<br>(Notes 6, 7)                                                                          | t <sub>RXSTSU</sub>     |                            | 0                        |                      | 1                        | t <sub>BIT</sub>       |

| STOP Hold Time to Idle (Notes 6, 7)                                                                                  | t <sub>SPHD</sub>       |                            |                          |                      | 0.5                      | t <sub>BIT</sub>       |

| RX Minimum Idle Time (STOP bit to<br>START bit) (Note 6, 7)                                                          | t <sub>RXIDLESPST</sub> |                            | 1                        |                      |                          | t <sub>BIT</sub>       |

| RX Fall Time (Notes 7, 8)                                                                                            | t <sub>FALL</sub>       |                            |                          |                      | 0.5                      | t <sub>BIT</sub>       |

| RX Rise Time (Notes 7, 8)                                                                                            | t <sub>RISE</sub>       |                            |                          |                      | 0.5                      | t <sub>BIT</sub>       |

| Propagation Delay (RX Port to TX port)                                                                               | t <sub>PROP</sub>       |                            |                          | 2.5                  | 3                        | t <sub>BIT</sub>       |

| Start-Up Time from SHNDL high and<br>V <sub>AA</sub> = 0V to RXUP/RXUN valid<br>Note 5: Unless otherwise noted limit | t <sub>STARTUP</sub>    |                            |                          | 1                    |                          | ms                     |

**Note 5:** Unless otherwise noted, limits are 100% production-tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

**Note 6:** Maximum limited by application circuit.

**Note 7:** Guaranteed by design and not production-tested.

**Note 8:** Fall time measured 90% to 10%, rise time measured 10% to 90%.

**Note 9:** Differential signal ( $V_{RXP} - V_{RXN}$ ) where  $V_{RXP}$  and  $V_{RXN}$  do not exceed a common-mode voltage range of ±25V.

Note 10:  $I_{SHDNL}$  measured with  $V_{SHDNL} = 0.3V$ , STOP characters, zero idle time,  $V_{RX PEAK} = 3.3V$

- Note 11: V<sub>CELLn</sub> = V<sub>Cn</sub> V<sub>Cn-1</sub>, Range over which measurement settling time and accuracy is guaranteed.

- Note 12: V<sub>CELLn</sub> = V<sub>Cn</sub> V<sub>Cn-1</sub>, V<sub>CELLn</sub> = V<sub>CELLn-1</sub>, and V<sub>DCIN</sub> = 12 x | V<sub>CELLn</sub> | (9V minimum). No oversampling enabled (OVSAMPL[2:0] = 0). Average of 64 acquisitions.

**Note 13:**  $V_{DDL} = V_{DDL2}$  for lower port and  $V_{DDL} = V_{DDL3}$  for upper port.

Note 14: As measured during specified diagnostic mode.

**Note 15:** Not production tested. See Cell-Balancing section for details on the maximum allowed balancing current. Duty-cycle is calculated for a 10-year device lifetime.

**Note 16:** Acquisition mode (ADC conversions) is entered when the SCAN bit is set and ends when SCANDONE is set. With the typical acquisition duty-cycle very low, the average current I<sub>DCIN</sub> is much less than I<sub>DCMEAS</sub>. Total supply current during communication I<sub>DCIN</sub> = I<sub>DCCOMM</sub> + I<sub>DCSTBY</sub>.

**Note 17:** In daisy-chain applications, the bit time of the second stop bit may be less than specified to account for clock rate variation and sampling error between devices.

**Note 18:** Charge pump efficiency =  $\Delta I_{LOAD} / \Delta I_{SUPPLY}$ , where  $I_{LOAD}$  is applied from HV to AGND,  $\Delta I_{LOAD}$  = 5mA, and  $\Delta ISUPPLY = I_{DCIN}$  (for  $I_{LOAD}$  = 5mA) -  $I_{DCIN}$  (for  $I_{LOAD}$  = 0).

## **Typical Operating Characteristics**

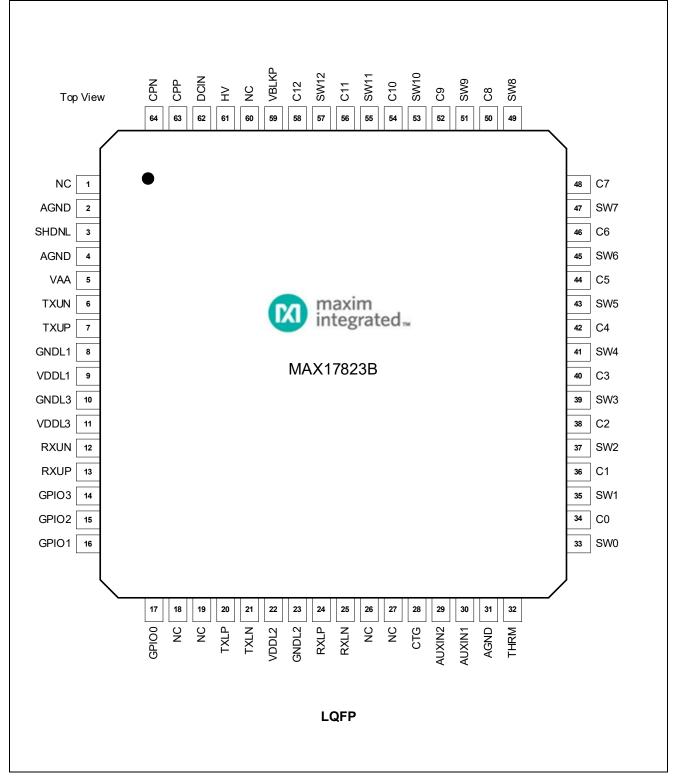

## **Pin Configuration**

## Pin Description www.maximintegrated.com

## 12-Channel High-Voltage Data Acquisition System

| PIN | NAME   | FUNCTION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | NC     | NC       | Not connected. Connect to ground or leave floating.                                                                                                                                                                                                                                                                                                    |

| 2   | AGND   | Ground   | Analog ground. Connect to negative terminal of cell 1 and ground plane.                                                                                                                                                                                                                                                                                |

| 3   | SHDNL  | Input    | Shutdown active low input. Drive >1.8V to enable operation and drive <0.6V to reset device<br>and place in shutdown mode. +72V tolerant. If not driven externally, this input may be<br>controlled solely via UART communication and software control. Bypass with a 1nF<br>capacitor to AGND. For single–ended UART, SHDNL must be driven externally. |

| 4   | AGND   | Ground   | Analog ground. Connect to negative terminal of cell 1 and ground plane.                                                                                                                                                                                                                                                                                |

| 5   | VAA    | Power    | 3.3V regulator output used to supply VDDL1, VDDL2, and VDDL3. Bypass with a $1\mu F$ capacitor to ground.                                                                                                                                                                                                                                              |

| 6   | TXUN   | Output   | Negative output for upper port transmitter. Driven between VDDL3 and GNDL3.                                                                                                                                                                                                                                                                            |

| 7   | TXUP   | Output   | Positive output for upper port transmitter. Driven between VDDL3 and GNDL3.                                                                                                                                                                                                                                                                            |

| 8   | GNDL1  | Ground   | Digital ground. Connect to ground plane.                                                                                                                                                                                                                                                                                                               |

| 9   | VDDL1  | Power    | 3.3V digital supply. Connect externally to VAA and bypass with $0.47\mu F$ capacitor to GNDL1.                                                                                                                                                                                                                                                         |

| 10  | GNDL3  | Ground   | Ground for upper port transmitter. Connect to ground plane.                                                                                                                                                                                                                                                                                            |

| 11  | VDDL3  | Power    | $3.3V$ supply for upper port transmitter. Connect externally to VAA and bypass with $0.47\mu F$ capacitor to GNDL3.                                                                                                                                                                                                                                    |

| 12  | RXUN   | Input    | Negative input for upper port receiver. Tolerates ±30V.                                                                                                                                                                                                                                                                                                |

| 13  | RXUP   | Input    | Positive input for upper port receiver. Tolerates $\pm 30V$ . Connect to ground for single-ended operation.                                                                                                                                                                                                                                            |

| 14  | GPIO3  | I/O      | General-Purpose I/O 3. Driven between VDDL1 and GNDL1. $2M\Omega$ internal pull-down.                                                                                                                                                                                                                                                                  |

| 15  | GPIO2  | I/O      | General-Purpose I/O 2. Driven between VDDL1 and GNDL1. $2M\Omega$ internal pull-down.                                                                                                                                                                                                                                                                  |

| 16  | GPIO1  | I/O      | General-Purpose I/O 1. Driven between VDDL1 and GNDL1. $2M\Omega$ internal pull-down.                                                                                                                                                                                                                                                                  |

| 17  | GPIO0  | I/O      | General-Purpose I/O 0. Driven between VDDL1 and GNDL1. $2M\Omega$ internal pull-down.                                                                                                                                                                                                                                                                  |

| 18  | NC     | NC       | Not connected. Connect to ground or leave floating.                                                                                                                                                                                                                                                                                                    |

| 19  | NC     | NC       | Not connected. Connect to ground or leave floating.                                                                                                                                                                                                                                                                                                    |

| 20  | TXLP   | Output   | Positive output for lower port transmitter. Driven between VDDL2 and GNDL2.                                                                                                                                                                                                                                                                            |

| 21  | TXLN   | Output   | Negative output for lower port transmitter. Driven between VDDL2 and GNDL2.                                                                                                                                                                                                                                                                            |

| 22  | VDDL2  | Power    | $3.3V$ supply for lower port transmitter. Connect externally to VAA and bypass with $0.47\mu F$ capacitor to GNDL2.                                                                                                                                                                                                                                    |

| 23  | GNDL2  | Ground   | Ground for lower port transmitter. Connect to ground plane.                                                                                                                                                                                                                                                                                            |

| 24  | RXLP   | Input    | Positive input for lower port receiver. Tolerates ±30V. Connect to ground for single-ended operation.                                                                                                                                                                                                                                                  |

| 25  | RXLN   | Input    | Negative input for lower port receiver. Tolerates ±30V.                                                                                                                                                                                                                                                                                                |

| 26  | NC     | NC       | Not connected. Connect to ground or leave floating.                                                                                                                                                                                                                                                                                                    |

| 27  | NC     | NC       | Not connected. Connect to ground or leave floating.                                                                                                                                                                                                                                                                                                    |

| 28  | CTG    | Input    | Reserved for factory use. Connect to ground.                                                                                                                                                                                                                                                                                                           |

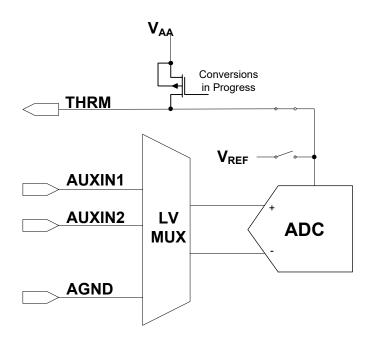

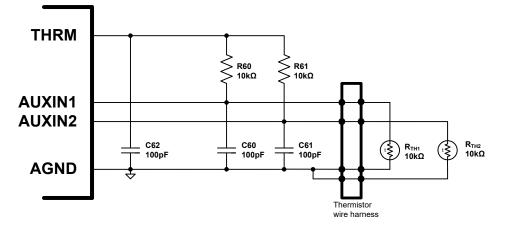

| 29  | AUXIN2 | Input    | Auxiliary voltage input 2 to measure external temperature. Connect to a voltage divider consisting of a $10K\Omega$ pull-up to THRM and $10K\Omega$ NTC thermistor to ground. If not used, connect to the pull-up only.                                                                                                                                |

| 30  | AUXIN1 | Input    | Auxiliary voltage input 1 to measure external temperature. Connect to a voltage divider consisting of a 10K $\Omega$ pull-up to THRM and a 10K $\Omega$ NTC thermistor to ground. If not used, connect to the pull-up only.                                                                                                                            |

| 31  | AGND   | Ground   | Analog ground. Connect to negative terminal of cell 1 and ground plane.                                                                                                                                                                                                                                                                                |

## 12-Channel High-Voltage Data Acquisition System

| PIN | NAME  | FUNCTION | DESCRIPTION                                                                                                                                                                                                             |

|-----|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32  | THRM  | Power    | 3.3V switched output used to supply the voltage dividers for the auxiliary inputs. The output is enabled only during measurements or as configured by THRMMODE[1:0]. This output can source up to 2mA.                  |

| 33  | SW0   | Input    | Balance input for Cell 1 negative.                                                                                                                                                                                      |

| 34  | C0    | Input    | Voltage input for Cell 1 negative. Connect to AGND.                                                                                                                                                                     |

| 35  | SW1   | Input    | Balance input for Cell 1 positive (Cell 2 negative).                                                                                                                                                                    |

| 36  | C1    | Input    | Voltage input for Cell 1 positive (Cell 2 negative).                                                                                                                                                                    |

| 37  | SW2   | Input    | Balance input for Cell 2 positive (Cell 3 negative).                                                                                                                                                                    |

| 38  | C2    | Input    | Voltage input for Cell 2 positive (Cell 3 negative).                                                                                                                                                                    |

| 39  | SW3   | Input    | Balance input for Cell 3 positive (Cell 4 negative).                                                                                                                                                                    |

| 40  | C3    | Input    | Voltage input for Cell 3 positive (Cell 4 negative).                                                                                                                                                                    |

| 41  | SW4   | Input    | Balance input for Cell 4 positive (Cell 5 negative).                                                                                                                                                                    |

| 42  | C4    | Input    | Voltage input for Cell 4 positive (Cell 5 negative).                                                                                                                                                                    |

| 43  | SW5   | Input    | Balance input for Cell 5 positive (Cell 6 negative).                                                                                                                                                                    |

| 44  | C5    | Input    | Voltage input for Cell 5 positive (Cell 6 negative).                                                                                                                                                                    |

| 45  | SW6   | Input    | Balance input for Cell 6 positive (Cell 7 negative).                                                                                                                                                                    |

| 46  | C6    | Input    | Voltage input for Cell 6 positive (Cell 7 negative).                                                                                                                                                                    |

| 47  | SW7   | Input    | Balance input for Cell 7 positive (Cell 8 negative).                                                                                                                                                                    |

| 48  | C7    | Input    | Voltage input for Cell 7 positive (Cell 8 negative).                                                                                                                                                                    |

| 49  | SW8   | Input    | Balance input for Cell 8 positive (Cell 9 negative).                                                                                                                                                                    |

| 50  | C8    | Input    | Voltage input for Cell 8 positive (Cell 9 negative).                                                                                                                                                                    |

| 51  | SW9   | Input    | Balance input for Cell 9 positive (Cell 10 negative).                                                                                                                                                                   |

| 52  | C9    | Input    | Voltage input for Cell 9 positive (Cell 10 negative).                                                                                                                                                                   |

| 53  | SW10  | Input    | Balance input for Cell 10 positive (Cell 11 negative).                                                                                                                                                                  |

| 54  | C10   | Input    | Voltage input for Cell 10 positive (Cell 11 negative).                                                                                                                                                                  |

| 55  | SW11  | Input    | Balance input for Cell 11 positive (Cell 12 negative).                                                                                                                                                                  |

| 56  | C11   | Input    | Voltage input for Cell 11 positive (Cell 12 negative).                                                                                                                                                                  |

| 57  | SW12  | Input    | Balance input for Cell 12 positive.                                                                                                                                                                                     |

| 58  | C12   | Input    | Voltage input for Cell 12 positive.                                                                                                                                                                                     |

| 59  | VBLKP | Input    | Block voltage positive input. Internal $10M\Omega$ pull-down during measurement.                                                                                                                                        |

| 60  | NC    | NC       | Not connected. Connect to ground or leave floating.                                                                                                                                                                     |

| 61  | HV    | Power    | Decoupling capacitor connection for the HV charge pump. $V_{HV} = V_{DCIN} + 5.5V$ (typical).<br>Bypass with a 50V, 4.7µF capacitor to DCIN.                                                                            |

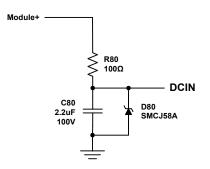

| 62  | DCIN  | Power    | DC supply for the low-voltage regulator, HV charge pump, and SHDNL charge pump. Connect to a voltage source between 9V and 65V via a 100 $\Omega$ series resistor. Bypass with a 100V, 2.2 $\mu$ F capacitor to ground. |

| 63  | CPP   | Power    | Positive capacitor connection for the HV charge pump. Connect a 100V, $0.1\mu$ F capacitor from CPP to CPN.                                                                                                             |

| 64  | CPN   | Power    | Negative capacitor connection for the HV charge pump.                                                                                                                                                                   |

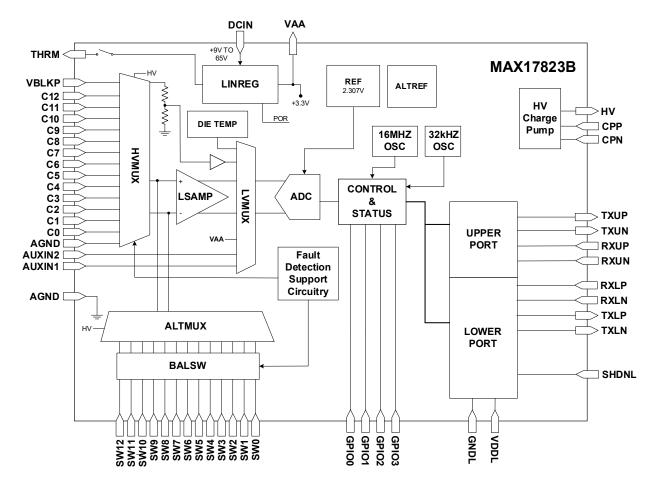

## **Detailed Description**

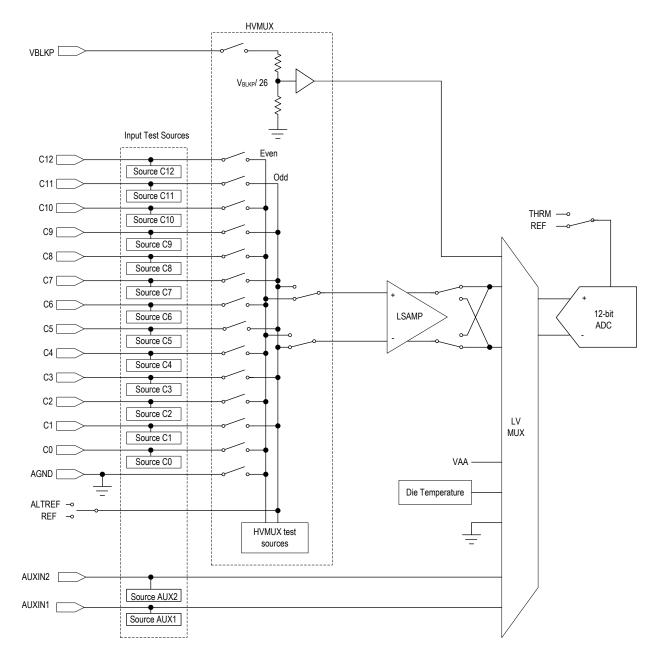

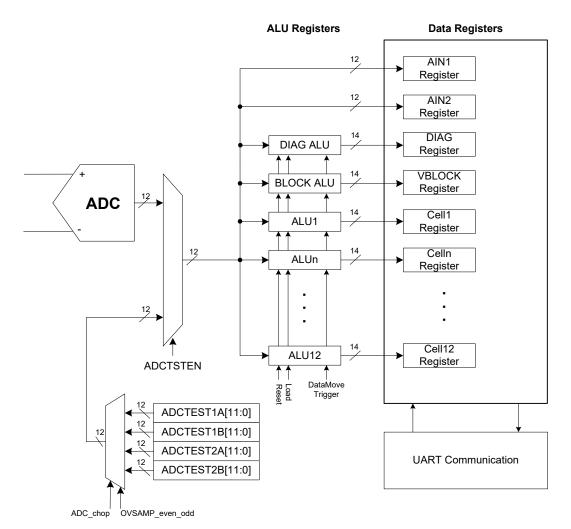

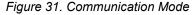

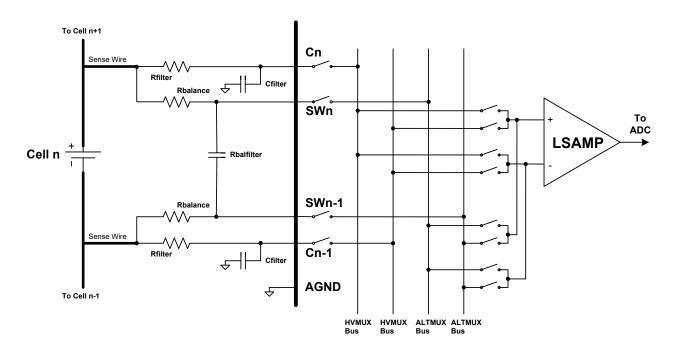

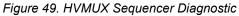

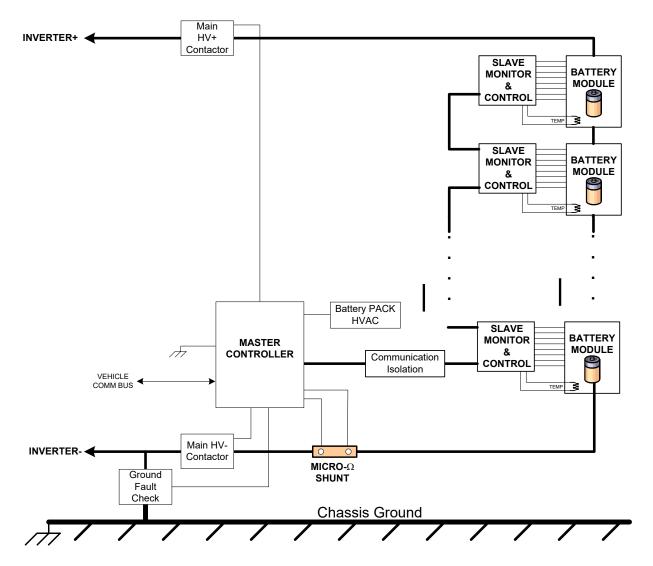

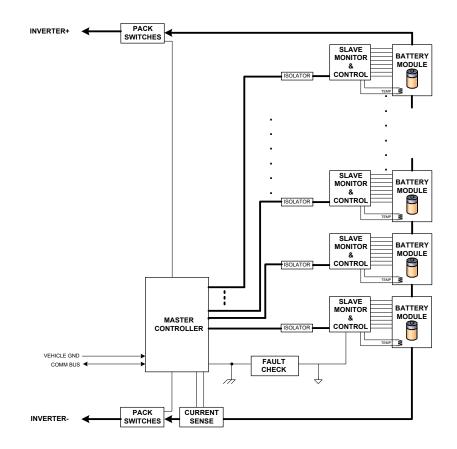

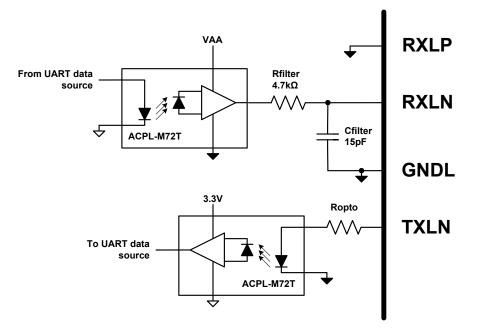

The data acquisition system consists of the major blocks shown in Figure 1 and described in Table 1.

## Table 1. System Blocks

| Block              | Description                                                                                                                                                     |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC                | Analog-to-Digital Converter. Uses a 12-bit successive-approximation register (SAR) with a reference voltage of 2.307V and supplied by $V_{AA}$ .                |

| HVMUX              | 12-channel high-voltage (65V) differential multiplexer for Cn inputs.                                                                                           |

| HV CHARGE PUMP     | High-voltage charge-pump supply ( $V_{DCIN}$ + 5.5V) for the HVMUX, ALTMUX, BALSW, and LSAMP circuits which must switch high-voltage signals. Supplied by DCIN. |

| LSAMP              | Level-shifting amplifier with a gain of 6/13. The result is that a 5V differential signal is attenuated to 2.307V, which is the reference voltage for the ADC.  |

| LVMUX              | Multiplexes various low-voltage signals including the level-shifted signals and temperature signals to the ADC for subsequent A-to-D conversion.                |

| ALTMUX             | 12-channel, high-voltage differential multiplexer for SWn inputs.                                                                                               |

| BALSW              | Cell-balancing switches.                                                                                                                                        |

| LINREG             | 3.3V (V <sub>AA</sub> ) linear regulator used to power the ADC and digital logic. Supplied by DCIN (9V to 65V).                                                 |

| REF                | 2.307V precision reference voltage for ADC and LINREG. Temperature-compensated.                                                                                 |

| ALTREF             | 1.242V precision reference voltage used for diagnostics.                                                                                                        |

| 16MHZ OSC          | 16MHz oscillator with 2% accuracy for clocking state-machines and UART timing.                                                                                  |

| 32KHZ OSC          | 32,768Hz oscillator for driving charge pumps and timers.                                                                                                        |

| LOWER PORT         | Differential UART for communication with host or down-stack devices. Auto-detects baud rates of 0.5Mbps, 1Mbps, or 2Mbps.                                       |

| UPPER PORT         | Differential UART for communication with up-stack devices.                                                                                                      |

| CONTROL AND STATUS | ALUs, control logic, and data registers                                                                                                                         |

| DIE TEMP           | A Proportional-to-Absolute-Temperature (PTAT) voltage source used to measure the die temperature.                                                               |

Figure 1. Functional Block Diagram

Notes:

All diodes are rated for ESD clamping conditions. They are not intended to accurately clamp DC voltage.

All diodes have a parasitic diode from AGND to their cathode that is omitted for clarity. These parasitic diodes have their anode at AGND.

Figure 2. ESD Diodes

12-Channel High-Voltage Data Acquisition System

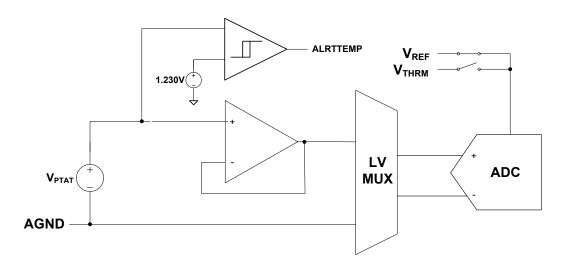

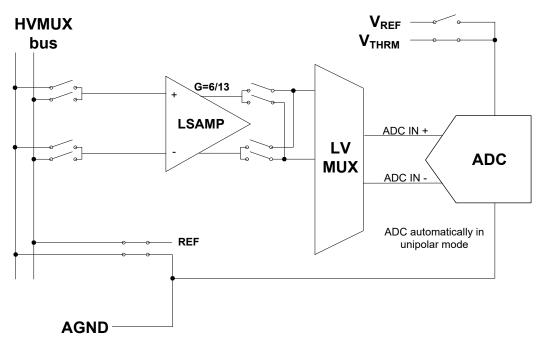

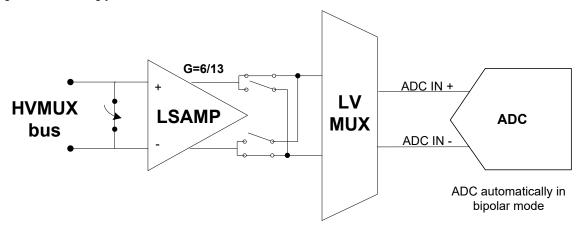

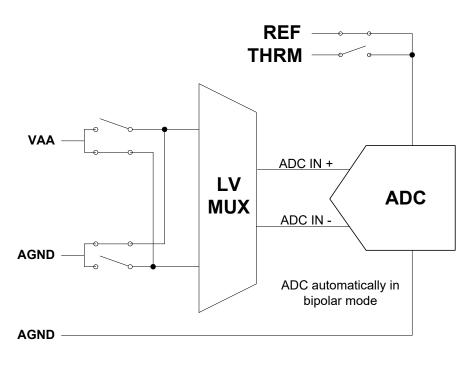

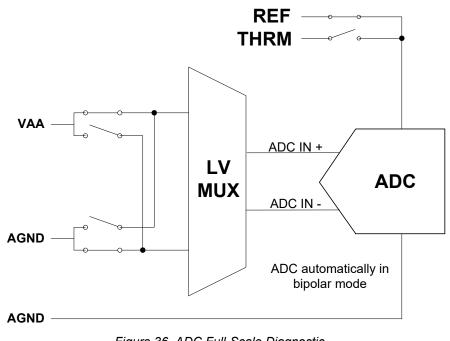

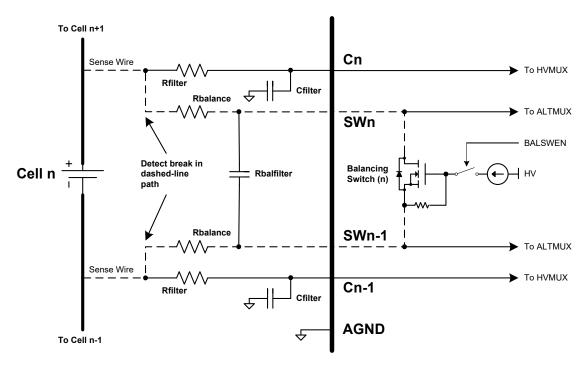

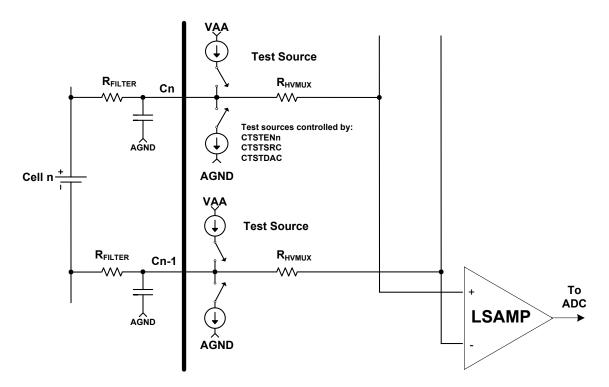

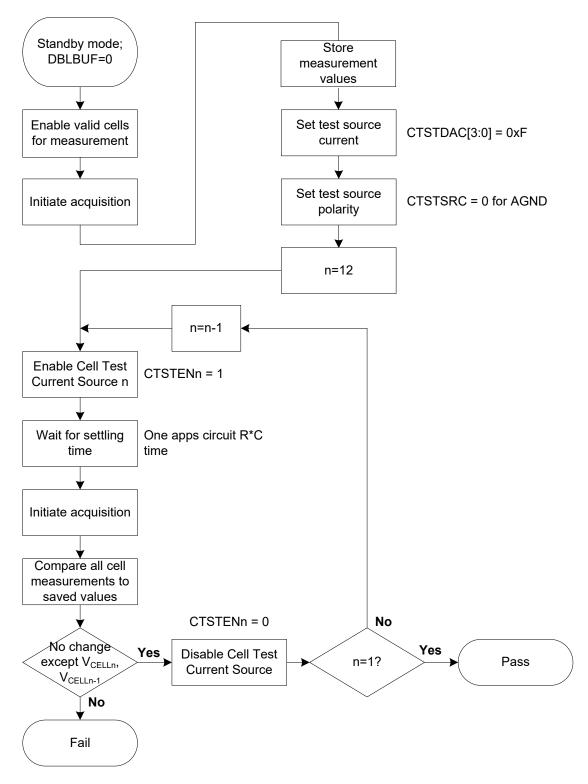

Figure 3. Analog Front-End

#### **Data Conventions**

Representation of data follows the conventions shown in Table 2. All registers are 16-bit words.

## Table 2. Numeric Conventions

| Description          | Convention        | Example                 |

|----------------------|-------------------|-------------------------|

| Binary number        | 0b prefix         | 0b01100001 = 61h        |

| Hexadecimal address  | 0x prefix         | 0x61                    |

| Hexadecimal data     | h suffix          | 61h                     |

| Register bit         | Register name [x] | STATUS[15] = 1          |

| Register field       | Field name [x:y]  | DA[4:0] = 0b01100 = 0Ch |

| Concatenated numbers | {xxxx, yyyy}      | {DA[4:0], 0b001} = 61h  |

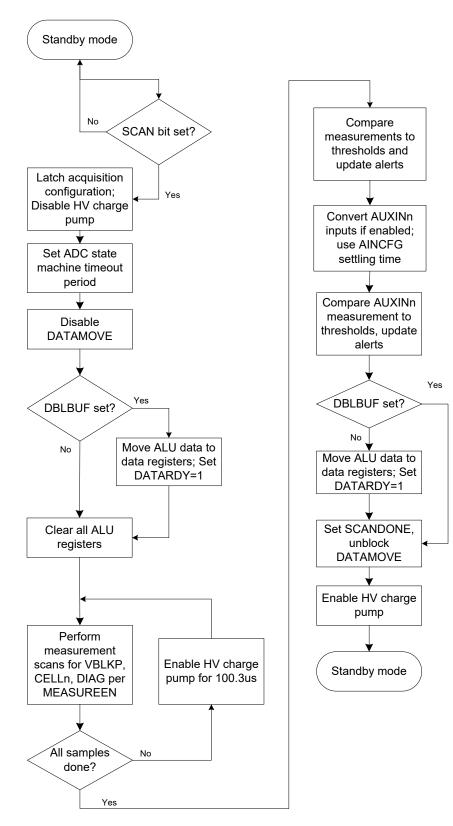

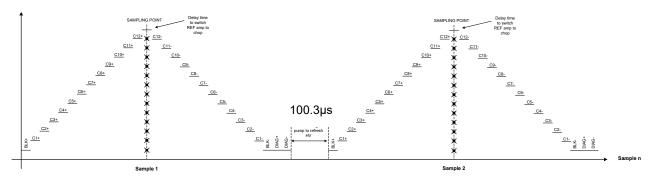

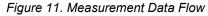

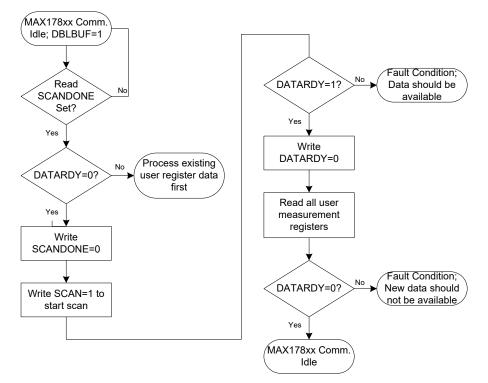

#### **Data Acquisition**

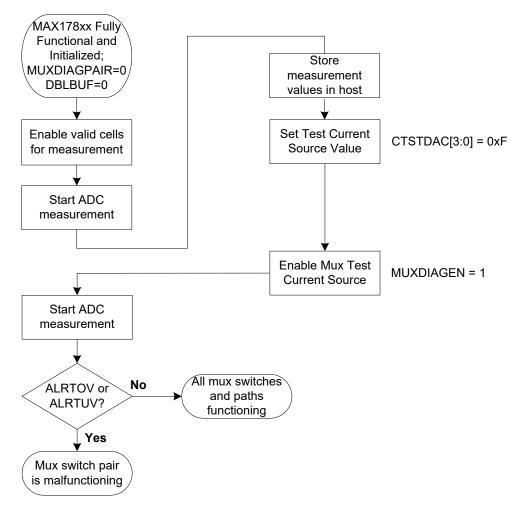

A data acquisition is composed of the distinct processes defined in Table 3 and controlled by various configuration registers described in this section. Configuration changes should be made prior to the acquisition in which the changes are to be effected.

| Process                         | Description                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conversion                      | The ADC samples a single input channel, converts it into a 12-bit binary value, and stores it in an ALU register.                                                                                                                                                                                                                             |

| Scan                            | The ADC sequentially performs conversions on all enabled cell input channels.                                                                                                                                                                                                                                                                 |

| Measurement cycle or Sample     | The ADC performs two scans for the purpose of minimizing error. The conversions (two for each input channel) are averaged together to form a single 14-bit binary value called a measurement. <b>Note:</b> The auxiliary inputs are only scanned once to create the auxiliary measurements.                                                   |

| Acquisition or Acquisition mode | If oversampling is enabled, the ADC takes sequential measurements and averages them together to form one 14-bit binary value for each input channel sampled. If there is no oversampling, the acquisition is essentially a single measurement cycle. <b>Note:</b> The auxiliary inputs are never oversampled and are stored as 12-bit values. |

## **Table 3. Data Acquisition Processes**

#### **Precision Internal Voltage References**

The measurement system uses two precision, temperature-compensated voltage references. The references are completely internal to the device and do not require any external components. The primary voltage reference, or REF, is used to derive the linear regulator output voltage and to supply the ADC reference. An alternate, independent reference, ALTREF, may be used to verify the primary reference voltage as described in the Diagnostics section.

#### Measurement Calibration

The acquisition system is calibrated at the factory and cannot be changed afterwards. The calibration parameters are stored in a ROM consisting of 12 read-only registers, CAL0 – CAL10 and CAL15. ROMCRC[8:0] is an 8-bit CRC value based on the calibration ROM and is stored in ID2[15:8] at the factory. ROMCRC[8:0] may be used to check the integrity of the calibration as described in the Diagnostics section.

## 12-Channel High-Voltage Data Acquisition System

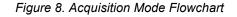

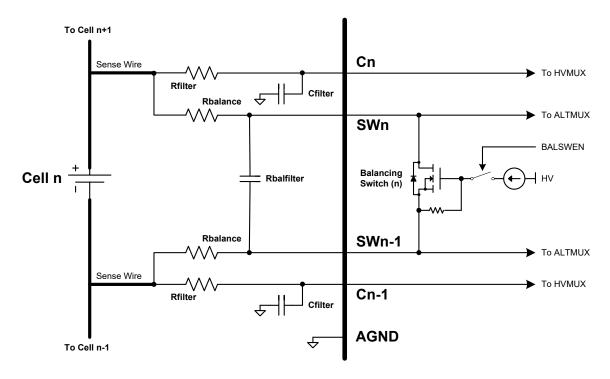

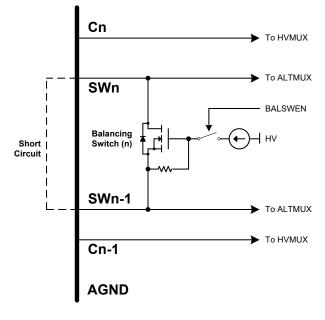

#### **Cell Inputs**

Up to 12 voltage measurements can be sampled differentially from the 13 cell inputs. The differential signal  $V_{CELLn}$  is defined as  $V_{Cn}$  -  $V_{Cn-1}$  for n = 1 to 12.

The cells to be measured are selected by MEASUREEN[11:0]. During the scan, each selected signal is multiplexed into the level-shifting amplifier (LSAMP) as shown in Figure 3. Since the common-mode range of the input signals is 0V to 65V, the signal must be level-shifted to the common-mode range of the amplifier. The amplifier has a gain of 6/13 so that a 5V differential signal will be attenuated to 2.307V which is the ADC reference voltage.