# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **General Description**

The MAX14760/MAX14762/MAX14764 analog switches are capable of passing bipolar signals that are beyond their supply rails. These devices operate from a single +3.0V to +5.5V supply, and support signals in the -25V to +25V range.

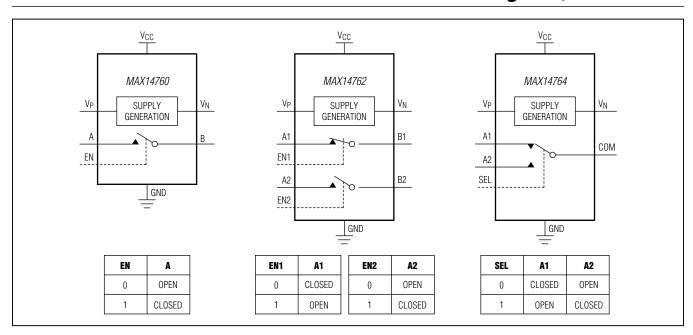

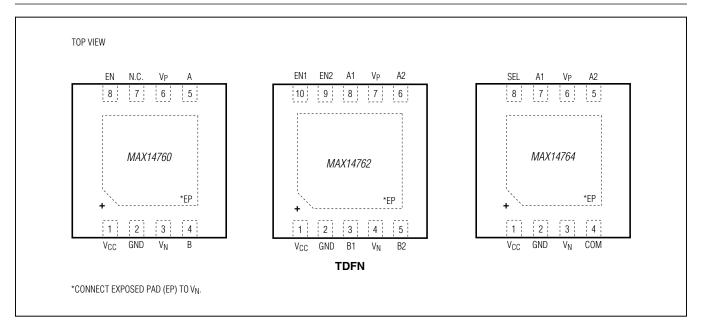

The MAX14760 is a single-pole/single-throw (SPST) analog switch, while the MAX14762 is a dual-SPST analog switch. The MAX14764 is a single-pole/double-throw (SPDT) analog switch.

The MAX14760/MAX14762/MAX14764 feature  $20\Omega$  (max) on-resistance with a  $\pm 10$ nA (max) on-leakage current for MAX14760/MAX14762.

The MAX14760/MAX14764 are available in 8-pin (3mm x 3mm) TDFN packages. The MAX14762 is available in a 10-pin (3mm x 3mm) TDFN package. These devices are specified over the -40°C to +85°C extended operating temperature range.

<u>Ordering Information/Selector Guide</u> appears at end of data sheet.

For related parts and recommended products to use with this part, refer to www.maxim-ic.com/MAX14760.related.

#### **Benefits and Features**

- ♦ Simplify Power-Supply Requirements

- ♦ 3.0V to 5.5V Supply Range

- **♦ High Performance**

- $\diamondsuit$  20 $\Omega$  (max) On-Resistance

- $\diamond$  Low On-Resistance Flatness, 58m $\Omega$  (typ)

- **♦ Thermal Shutdown Protection**

- → -40°C to +85°C Operating Temperature Range

- ♦ High Bandwidth:115MHz (typ)

- ♦ Save Space on Board

- ♦ Small 8-Pin and 10-Pin TDFN Packages

#### **Applications**

Industrial Measurement Systems

Instrumentation Systems

Opto-Relay Replacement

Medical Systems

ATE Systems

Audio Signal Routing and Switching

### Functional Diagrams/Truth Tables

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND, unless otherwise noted.) $V_{CC} - 0.3V \text{ to } +6V \\ EN, EN1, EN2, SEL - 0.3V \text{ to } +(V_{CC}+0.3V) \\ A, A1, A2, B, B1, B2, COM - (V_N - 0.3V) \text{ to Lesser of } \\ (V_P + 0.3V) \text{ or } (V_N + 52V) \\ \\$ | Continuous Power Dissipation (T <sub>A</sub> = +70°C)<br>8-Pin TDFN Package (derate 24.4mW/°C<br>above +70°C)                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                             | Operating Temperature Range -40°C to +85°C Storage Temperature Range -65°C to +160°C Lead Temperature (soldering, 10s) +300°C Soldering Temperature (reflow) +260°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

| 8 TDFN                                                          | 10 TDFN                                                         |

|-----------------------------------------------------------------|-----------------------------------------------------------------|

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )41°C/W | Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )41°C/W |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )8°C/W      | Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )9°C/W      |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0V \text{ to } 5.5V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 5V$ , and  $T_A = +25^{\circ}\text{C}$ .) (Note 2)

| PARAMETER                            | SYMBOL                                                  | CONDITIONS                                                  |                                       | MIN | TYP | MAX | UNITS |

|--------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|---------------------------------------|-----|-----|-----|-------|

| DC CHARACTERISTICS                   |                                                         |                                                             |                                       |     |     |     |       |

| Power Supply Range                   | V <sub>CC</sub>                                         |                                                             |                                       | 3.0 |     | 5.5 | V     |

| Continuous Current Through<br>Switch | I <sub>A</sub>                                          |                                                             |                                       | -25 |     | +25 | mA    |

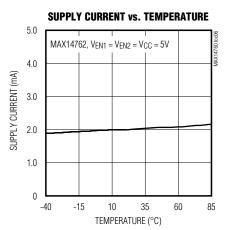

|                                      |                                                         | V <sub>CC</sub> ≤ 4.7V                                      | V <sub>EN</sub> _= V <sub>CC</sub>    |     | 4.1 | 10  | - mA  |

| Cupply Current                       | 1                                                       | VCC ≥ 4.7 V                                                 | V <sub>EN</sub> _= V <sub>CC</sub> /2 |     | 4.1 | 10  |       |

| Supply Current                       | Icc                                                     | V <sub>CC</sub> > 4.7V                                      | V <sub>EN</sub> _= V <sub>CC</sub>    |     | 2.5 | 6   |       |

|                                      |                                                         |                                                             | V <sub>EN</sub> _= V <sub>CC</sub> /2 |     | 2.5 | 6   |       |

| Analog Signal Range                  | V <sub>COM</sub> ,<br>V <sub>A_</sub> , V <sub>B_</sub> | Switch open or closed                                       |                                       | -25 |     | +25 | V     |

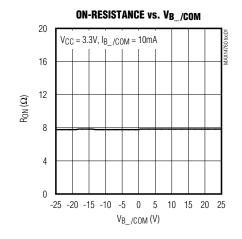

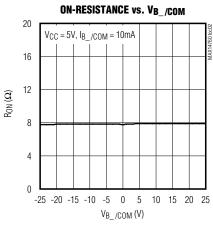

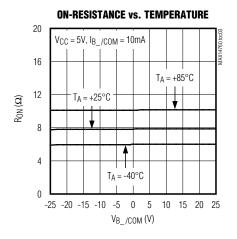

| On-Resistance                        | R <sub>ON</sub>                                         | $I_{COM}$ or $I_{B} = \pm 25$ mA, $V_{A} = \pm 25$ V        |                                       |     | 8   | 20  | Ω     |

| On-Resistance Flatness               | ΔR <sub>ON</sub>                                        | $-25V < V_{A} < +25V$ , $I_{COM}$ or $I_{B} = \pm 25$ mA    |                                       |     | 58  |     | mΩ    |

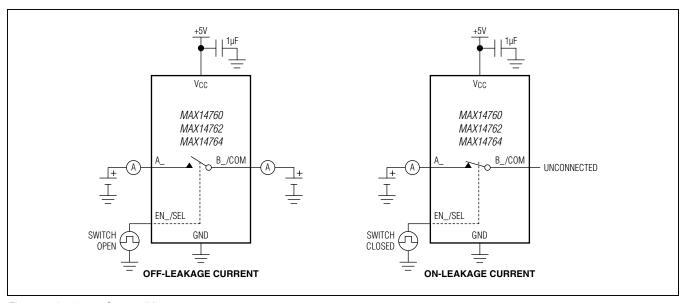

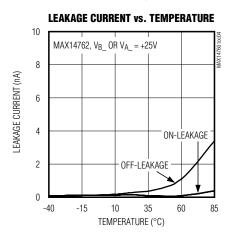

| A, A1, A2 Off-Leakage Current        | I <sub>A_(OFF)</sub>                                    | $V_{A_{-}}$ = +25V, $V_{COM}$ or $V_{B_{-}}$ = 0V, Figure 1 |                                       | -30 |     | +30 | nA    |

| COM, B, B1, B2 Off-Leakage           | I <sub>COM(OFF)</sub> ,                                 | V <sub>COM</sub> or V <sub>B</sub> _ = 15<br>(MAX14764)     | 5V, V <sub>A</sub> _ = 0V, Figure 1   | -10 |     | +10 | - A   |

| Current                              | I <sub>B_</sub> (OFF)                                   | V <sub>B</sub> _ = 15V, V <sub>A</sub> _ = MAX14762)        | 0V, Figure 1 (MAX14760/               | -10 |     | +10 | nA nA |

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 3.0 \text{V to } 5.5 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = 5 \text{V}, \text{ and } T_A = +25 ^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                       | SYMBOL            | CONDITIONS                                                                         | MIN | TYP   | MAX | UNITS |  |

|---------------------------------|-------------------|------------------------------------------------------------------------------------|-----|-------|-----|-------|--|

| On Lackage Courset              |                   | $V_{A_{-}}$ = ±25V, B/COM is unconnected,<br>Figure 1 (MAX14760/MAX14762)          | -10 |       | +10 | Λ     |  |

| On-Leakage Current              | ION               | V <sub>A</sub> _ = ±25V, B/COM is unconnected,<br>Figure 1 (MAX14764)              | -30 |       | +30 | - nA  |  |

| DIGITAL LOGIC                   |                   |                                                                                    |     |       |     |       |  |

|                                 |                   | $V_{CC} = 3.0V$                                                                    |     |       | 0.7 |       |  |

| Input Voltage Logic Low         | \/                | V <sub>CC</sub> = 3.6V                                                             |     |       | 0.7 | V     |  |

| Input-Voltage Logic-Low         | V <sub>IL</sub>   | V <sub>CC</sub> = 4.5V                                                             |     |       | 0.8 | ] v   |  |

|                                 |                   | V <sub>CC</sub> = 5.5V                                                             |     |       | 0.8 |       |  |

|                                 |                   | V <sub>CC</sub> = 3.0V                                                             | 1.7 |       |     |       |  |

| Innut Valtage Lagie Lligh       |                   | V <sub>CC</sub> = 3.6V                                                             | 1.9 |       |     |       |  |

| Input-Voltage Logic-High        | V <sub>IH</sub>   | V <sub>CC</sub> = 4.5V                                                             | 2.0 |       |     | ]     |  |

|                                 |                   | V <sub>CC</sub> = 5.5V                                                             | 2.1 |       |     |       |  |

| Input Current                   | ΙL                |                                                                                    | -1  |       | +1  | μΑ    |  |

| AC CHARACTERISTICS              |                   |                                                                                    |     |       |     |       |  |

| Power-On Time                   | tpwron            | C <sub>VP</sub> = C <sub>VN</sub> = 100nF (Note 3)                                 |     | 50    |     | ms    |  |

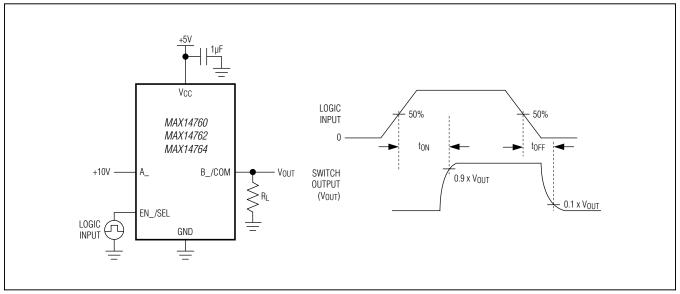

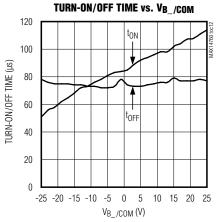

| Enable Turn-On Time             | t <sub>ON</sub>   | $V_{A_{-}} = \pm 10V$ , $R_{L} = 10k\Omega$ , Figure 2 (MAX14760/MAX14762)         |     | 100   | 200 | μs    |  |

|                                 |                   | $V_{A_{-}} = \pm 10V$ , $R_{L} = 10k\Omega$ , Figure 2 (MAX14764)                  |     | 1.04  | 1.6 | ms    |  |

| Enable Turn-Off Time            | t <sub>OFF</sub>  | (Figure 2)                                                                         |     | 110   | 400 | μs    |  |

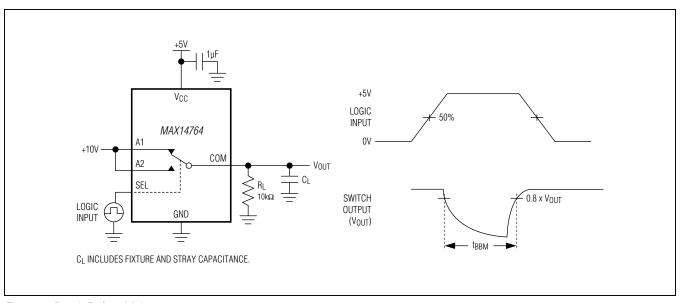

| Break-Before-Make Interval      | t <sub>BBM</sub>  | $V_{A} = 1V_{RMS}$ , $R_{L} = 10k\Omega$ ,<br>Figure 3 (MAX14764)                  |     | 740   |     | μs    |  |

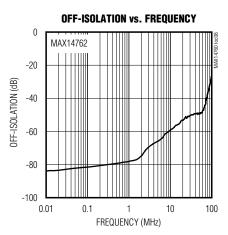

| Off-Isolation                   | V <sub>ISO</sub>  | $V_{A}$ = 1 $V_{RMS}$ , f = 100kHz, $R_L$ = 50 $\Omega$ , $C_L$ = 15pF, Figure 4   |     | -77   |     | dB    |  |

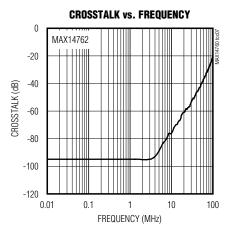

| Crosstalk                       | V <sub>CT</sub>   | $R_S = R_L = 50\Omega$ , $f = 100$ kHz, $V_{COM} = 1V_{RMS}$ , Figure 5 (MAX14764) |     | -92   |     | dB    |  |

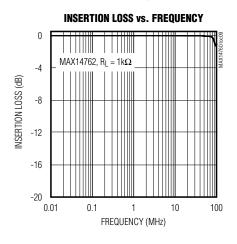

| -3dB Bandwidth                  | BW                | $R_S = 50\Omega$ , $R_L = 1k\Omega$ , $V_{A} = 1V_{P-P}$ , Figure 6                |     | 115   |     | MHz   |  |

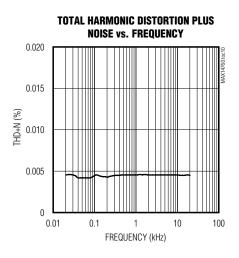

| Total Harmonic Distortion       | THD+N             | $R_S = R_L = 1k\Omega$ , $f = 20Hz$ to $20kHz$                                     |     | 0.005 |     | %     |  |

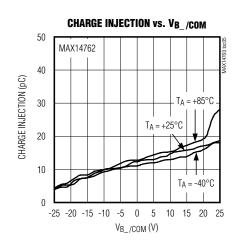

| Charge Injection                | Q                 | $V_{A}$ = GND, $C_{L}$ = 1nF, Figure 7                                             |     | 19    |     | рС    |  |

| Input Capacitance               | C <sub>IN</sub>   | At A, A1, A2, B, B1, B2, and COM pins                                              |     | 32    |     | pF    |  |

| THERMAL PROTECTION              |                   |                                                                                    |     |       |     | 1     |  |

| Thermal Shutdown Temperature    | t <sub>HYST</sub> |                                                                                    |     | +154  |     | °C    |  |

| Shutdown Temperature Hysteresis | tshut             |                                                                                    |     | 24    |     | °C    |  |

| ESD PROTECTION                  |                   |                                                                                    |     |       |     | 1     |  |

| All Pins                        |                   | Human Body Model                                                                   |     | ±2    |     | kV    |  |

Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Specifications over operating temperature range are guaranteed by design.

Note 3: The power-on time is defined as the settling time for the charge pump's output to reach steady-state value within 1%.

# Above- and Below-the-Rails Low-Leakage Analog Switches

### **Test Circuits/Timing Diagrams**

Figure 1. Leakage Current Measurement

Figure 2. Switching Time

# Above- and Below-the-Rails Low-Leakage Analog Switches

**Test Circuits/Timing Diagrams (continued)**

Figure 3. Break-Before-Make

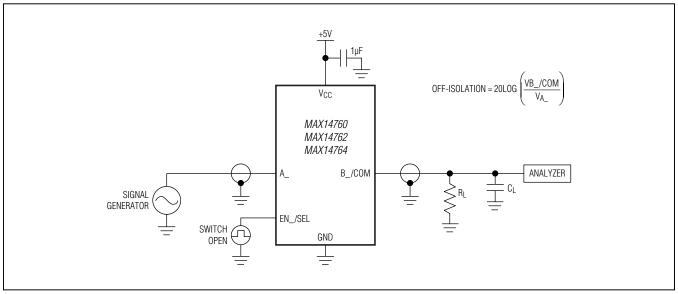

Figure 4. Off-Isolation

# Above- and Below-the-Rails Low-Leakage Analog Switches

**Test Circuits/Timing Diagrams (continued)**

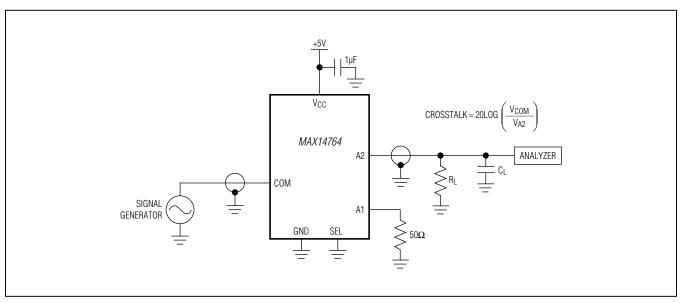

Figure 5. Crosstalk

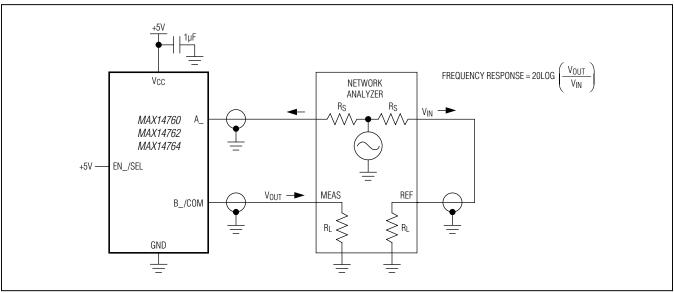

Figure 6. Insertion Loss

# Above- and Below-the-Rails Low-Leakage Analog Switches

**Test Circuits/Timing Diagrams (continued)**

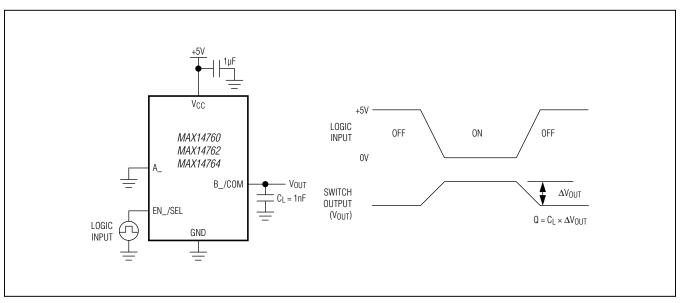

Figure 7. Charge Injection

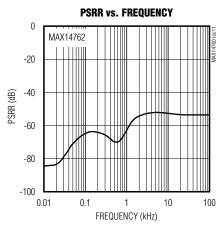

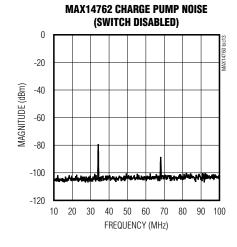

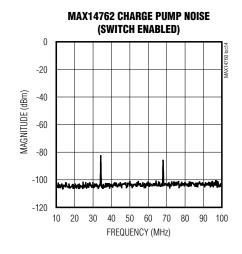

## **Typical Operating Characteristics**

$(T_A = +25$ °C, unless otherwise noted.)

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **Typical Operating Characteristics (continued)**

$(T_A = +25$ °C, unless otherwise noted.)

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **Typical Operating Characteristics (continued)**

$(T_A = +25$ °C, unless otherwise noted.)

# Above- and Below-the-Rails Low-Leakage Analog Switches

## **Pin Configurations**

# **Pin Description**

| PIN      |          |          |                |                                                                                                                                      |  |

|----------|----------|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX14760 | MAX14762 | MAX14764 | NAME           | FUNCTION                                                                                                                             |  |

| 1        | 1        | 1        | $V_{CC}$       | Positive-Supply Voltage Input. Bypass V <sub>CC</sub> to GND with a 1µF ceramic capacitor placed as close as possible to the device. |  |

| 2        | 2        | 2        | GND            | Ground                                                                                                                               |  |

| 3        | 4        | 3        | $V_N$          | Negative Voltage Output. Bypass V <sub>N</sub> to GND with a 0.1µF 50V ceramic capacitor placed as close as possible to the device.  |  |

| 4        | _        | _        | В              | Analog Switch Common Terminal                                                                                                        |  |

| _        | _        | 4        | COM            | M Analog Switch Common Terminal                                                                                                      |  |

| 5        | _        | _        | Α              | Analog Switch Normally Open Terminal                                                                                                 |  |

| 6        | 7        | 6        | V <sub>P</sub> | Positive Voltage Output. Bypass V <sub>P</sub> to GND with a 0.1µF 50V ceramic capar placed as close as possible to the device.      |  |

| 7        | _        | _        | N.C.           | No Connection. Leave unconnected.                                                                                                    |  |

| 8        | _        | _        | EN             | Switch Control Input. Drive EN high to close the switch or drive EN low to ope the switch.                                           |  |

| _        | 8        | 7        | A1             | Analog Switch 1 Normally Closed Terminal                                                                                             |  |

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### Pin Description (continued)

|          | PIN      |          | NAME | FUNCTION                                                                                                                |  |

|----------|----------|----------|------|-------------------------------------------------------------------------------------------------------------------------|--|

| MAX14760 | MAX14762 | MAX14764 |      | FUNCTION                                                                                                                |  |

| _        | 3        | _        | B1   | Analog Switch 1 Common Terminal                                                                                         |  |

| _        | 6        | 5        | A2   | Analog Switch 2 Normally Open Terminal                                                                                  |  |

| _        | 5        |          | B2   | Analog Switch 2 Common Terminal                                                                                         |  |

| _        | 10       | _        | EN1  | Switch 1 Control Input. Drive EN1 high to open switch 1 or drive EN1 low to close switch 1.                             |  |

| _        | 9        | _        | EN2  | Switch 2 Control Input. Drive EN2 high to close switch 2 or drive EN2 low to open switch 2.                             |  |

| _        | _        | 8        | SEL  | Switch Control Input. Drive SEL low to connect the COM terminal to A1 or dr SEL high to connect the COM terminal to A2. |  |

| _        | _        | _        | EP   | Exposed Pad. Connect EP to $V_N$ ; EP is not intended as an electrical connection.                                      |  |

#### **Detailed Description**

The MAX14760/MAX14762/MAX14764 analog switches are capable of handling signals above and below their rails. These devices operate from a single +3.0V to +5.5V supply and support signals in the -25V to +25V range.

#### **Integrated Bias Generation**

The MAX14760/MAX14762/MAX14764 contain a total of three charge pumps to generate bias voltages for the internal switches: a 5V regulated charge pump, a positive high-voltage (+35V) charge pump, and a negative high-voltage (-27V) charge pump. When  $V_{DD}$  is above 4.7V (typ), the 5V regulated charge pump is bypassed, and  $V_{DD}$  provides the input for the high-voltage charge pumps, reducing overall supply current. An external 0.1µF capacitor is required for each high-voltage charge pump between  $V_P/V_N$  and GND.

#### **Analog Signal Range**

The devices switch signals in the range from -25V to +25V that are above and below their rails. The on-resistance for these devices exhibits a high degree of flatness (58m $\Omega$ ) over the whole input voltage range of -25V to +25V. The analog switches allow bidirectional current flow, so A, A1, A2, B, B1, B2, and COM, can be used as either inputs or outputs.

#### **Bypass Capacitors**

Bias-stabilizing capacitors are required on the  $V_P$  and  $V_N$  pins.  $1\mu F$  ceramic capacitors are suggested for effective operation.  $V_P$  and  $V_N$  are not intended as a power supply for other circuitry.

#### **Applications Information**

#### **Nonpowered Condition**

The MAX14760/MAX14762/MAX14764 can tolerate input voltages on the A, B, or COM pins in the  $\pm 25 V$  range when it is not powered. When  $V_{DD}=0V$ , the DC input leakage current into the A, B, or COM pins is typically below 1µA. Some devices can have a larger leakage current up to the mA range due to technology spread.

With  $V_{DD}$  not powered, internal diodes between the analog pins and the  $V_P$  and  $V_N$  will charge up the external capacitors on  $V_P$  and  $V_N$  when positive and/or negative voltages are applied to these pins. This causes transient input current flow.

Large dv/dt on the inputs causes large capacitive charging currents, which have to be limited to 300mA to avoid destroying the internal diodes. Hence, the 100nF capacitors on  $V_P$  and  $V_N$ , the dv/dt must be limited to  $3V/\mu s$ . Once the capacitors reach their final voltage the input current decays to the leakage current levels mentioned above.

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **Ordering Information/Selector Guide**

| PART         | TEMP RANGE     | PIN-PACKAGE | FUNCTION | $R_{ON}$ (MAX) ( $\Omega$ ) |

|--------------|----------------|-------------|----------|-----------------------------|

| MAX14760ETA+ | -40°C to +85°C | 8 TDFN-EP*  | 1 x SPST | 20                          |

| MAX14762ETB+ | -40°C to +85°C | 10 TDFN-EP* | 2 x SPST | 20                          |

| MAX14764ETA+ | -40°C to +85°C | 8 TDFN-EP*  | 1 x SPDT | 20                          |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

#### **Chip Information**

#### **Package Information**

PROCESS: BICMOS

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO |

|-----------------|-----------------|----------------|--------------------|

| 8 TDFN          | T833+2          | <u>21-0137</u> | 90-0059            |

| 10 TDFN         | T1033+1         | 21-0137        | 90-0003            |

<sup>\*</sup>EP = Exposed pad.

# Above- and Below-the-Rails Low-Leakage Analog Switches

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                              | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 9/11             | Initial release                                                                                                                                                                          | _                |

| 1                  | 8/12             | Updated Electrical Characteristics table, updated Figures 1–7, added TOCs 13 and 14, updated Pin Configuration table, added Integrated Bias Generation and Nonpowered Condition sections | 3–7, 9–11        |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

MAX14760ETA+T MAX14762ETB+T MAX14764ETA+T