# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **General Description**

The MAX14611 is a quad bidirectional logic-level translator that provides the level shifting necessary to allow data transfer in a multivoltage system. Externally applied voltages,  $V_{CC}$  and  $V_L$ , set the logic levels on either side of the device. A low-voltage logic signal present on the  $V_L$  side of the device appears as a high-voltage logic signal on the  $V_{CC}$  side of the device, and vice-versa.

The device is ideal for I2C bus as well as MDIO bus applications where open-drain operation is often required. The device features a three-state output mode ( $\overline{\text{TS}}$ ). Drive  $\overline{\text{TS}}$  high to connect the pullup to the powered I/O port. This allows for continuous, undisrupted I<sup>2</sup>C operation on the powered side of the device while the level translation function is off. The MAX14611 is a pin-to-pin compatible upgrade to the MAX3378E in the TDFN package.

The MAX14611 features enhanced high-electrostatic-discharge (ESD) protection on all I/OVCC\_ ports up to  $\pm 6 \text{kV}$  HBM. The device operates over the -40°C to +85°C extended temperature range and is available in 3mm x 3mm, 14-pin TDFN and 4.9mm x 5.1mm, 14-pin TSSOP packages.

#### **Applications**

SPI, I<sup>2</sup>C, and MDIO Level Translation Low-Voltage ASIC Level Translation Portable Electronics Mobile Phones

POS Systems

Telecommunications

Equipment

#### **Benefits and Features**

- ♦ Improved Interoperability

- **♦ Meets I<sup>2</sup>C Specifications**

- $\diamond$  10k $\Omega$  Internal Pullup Resistor

- ♦ Pin-to-Pin Compatible with the MAX3377E and the MAX3378E

- ♦ 0.9V Operation on Low Voltage Supply

- ♦ Robust Logic-Level Translation

- **♦ ±0.5V Tolerances on All Pins**

- ±6kV Human Body Model ESD Protection on I/OVCC Lines

- ♦ Thermal Short-Circuit Protection

- **♦ Short to Ground Fault Protection on All Pins**

- → -40°C to +85°C Operating Temperature Range

- ♦ Increased Design Flexibility

- **♦ Ultra-Low Supply Current**

- → Pullup Resistor Enabled with a Single Power Supply when TS = High

- $\diamond$  10 $\Omega$  (max) Transmission Gate FET

- → Small, 14-Pin, 3.0mm x 3.0mm TDFN Package and 14-Pin, 4.9mm x 5.1mm TSSOP Package

Ordering Information appears at end of data sheet.

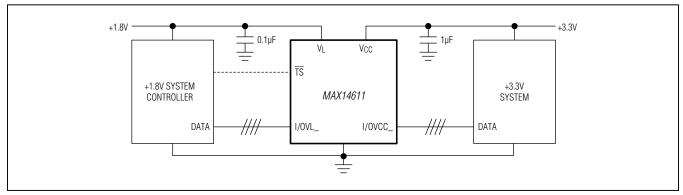

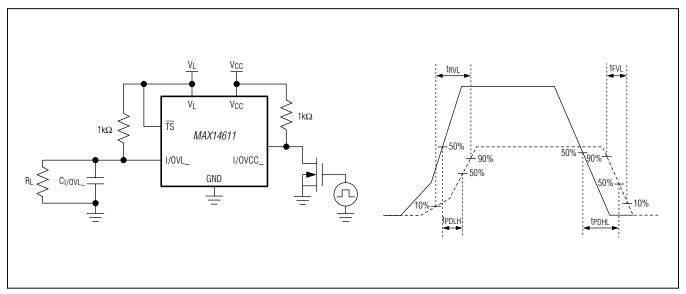

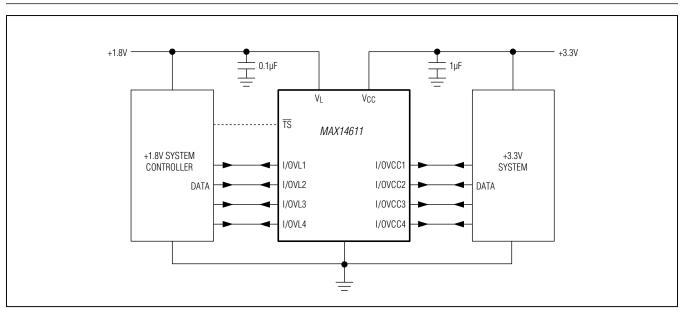

### **Typical Operating Circuit**

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX14611.related.

# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.)                       | Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|---------------------------------------------------------|-------------------------------------------------------|

| V <sub>CC</sub> 0.5V to +6V                             | TDFN (derate 24.4mW/°C above +70°C)1951.2mW           |

| V <sub>L</sub> 0.5V to +5.5V                            | TSSOP (derate 10mW/°C above +70°C)796.8mW             |

| 0.5V to +6V                                             | Operating Temperature Range40°C to +85°C              |

| I/OVCC0.5V to (V <sub>CC</sub> + 0.5V)                  | Maximum Junction Temperature+150°C                    |

| $I/OVL_{-}$ -0.5V to $(V_1 + 0.5V)$                     | Storage Temperature Range65°C to +150°C               |

| Short-Circuit Duration I/OVL_, I/OVCC_ to GNDContinuous | Lead Temperature (soldering, 10s)+300°C               |

| Continuous Current±50mA                                 | Soldering Temperature (reflow)+260°C                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

| •                                                               | •                                                           |

|-----------------------------------------------------------------|-------------------------------------------------------------|

| TDFN-EP                                                         | TSSOP                                                       |

| Junction-to-Ambient Thermal Resistance (θ <sub>JA</sub> )41°C/W | Junction-to-Ambient Thermal Resistance (θJA)100.4°C/W       |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> )8°C/W     | Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )30°C/W |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC}=+1.65 V \text{ to } +5.5 V, V_L=0.9 V \text{ to the lesser of } V_{CC}+0.3 V \text{ and } 5 V. T_A=T_J=-40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC}=+3.3 V, V_L=+1.8 V, T_A=+25 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  (Notes 2, 3)

| PARAMETER                                       | SYMBOL                | CONDITIONS                                                            | MIN  | TYP | MAX  | UNITS |  |

|-------------------------------------------------|-----------------------|-----------------------------------------------------------------------|------|-----|------|-------|--|

| POWER SUPPLIES                                  |                       |                                                                       |      |     |      |       |  |

| V <sub>L</sub> Supply Range                     | VL                    |                                                                       | 0.9  |     | 5    | V     |  |

| V <sub>CC</sub> Supply Range                    | V <sub>CC</sub>       |                                                                       | 1.65 |     | 5.5  | V     |  |

| V <sub>L</sub> Supply Current                   | I <sub>VL</sub>       | $I/OVCC_{-} = V_{CC}$ , $I/OVL_{-} = V_{L}$ , $\overline{TS} = V_{L}$ |      |     | 1    | μΑ    |  |

| V <sub>CC</sub> Supply Current                  | lvcc                  | $I/OVCC_{-} = V_{CC}, I/OVL_{-} = V_{L}, \overline{TS} = V_{L}$       |      |     | 35   | μA    |  |

| V Chutdown Mode Cupply                          |                       | TS = GND, I/OVCC = unconnected                                        |      | 0.1 | 1    |       |  |

| V <sub>CC</sub> Shutdown Mode Supply<br>Current | I <sub>SHDN_VCC</sub> | $\overline{TS} = V_{CC}, V_L = GND,$ I/OVCC = unconnected             |      | 0.1 | 1    | μΑ    |  |

| V <sub>I</sub> Shutdown Mode Supply             |                       | $\overline{TS} = GND$                                                 |      | 0.1 | 1    |       |  |

| Current Current                                 | I <sub>SHDN_</sub> VL | $\overline{TS} = V_L, V_{CC} = GND,$ I/OVL_ = unconnected             |      | 0.1 | 1    | μΑ    |  |

| I/OVCC_, I/OVL_, TS Leakage<br>Current          | ILEAK                 | $T_A = +25^{\circ}C, \overline{TS} = GND$                             |      | 0.1 | 1    | μA    |  |

| TS Input Leakage Current                        | I <sub>LEAK_TS</sub>  | $T_A = +25^{\circ}C$                                                  |      |     | 1    | μA    |  |

| V <sub>L</sub> Shutdown Threshold               | V <sub>TH_VL</sub>    |                                                                       |      | 0.3 | 0.85 | V     |  |

| V <sub>CC</sub> Shutdown Threshold              | V <sub>TH_VCC</sub>   |                                                                       |      | 0.8 | 1.35 | V     |  |

| I/OVL_ Pullup Resistor                          | R <sub>VL_PU</sub>    |                                                                       |      | 10  |      | kΩ    |  |

| I/OVCC_ Pullup Resistor                         | R <sub>VCC_PU</sub>   |                                                                       |      | 10  |      | kΩ    |  |

# Quad Bidirectional Low-Voltage Logic-Level Translator

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +1.65 \text{V to } +5.5 \text{V}, V_L = 0.9 \text{V to the lesser of } V_{CC} + 0.3 \text{V and } 5 \text{V}. T_A = T_J = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}, V_L = +1.8 \text{V}, T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 2, 3)

| PARAMETER                                 | SYMBOL                  | CONDITIONS                                                  | MIN                   | TYP  | MAX  | UNITS    |  |

|-------------------------------------------|-------------------------|-------------------------------------------------------------|-----------------------|------|------|----------|--|

| I/OVL_ to I/OVCC_ DC<br>Resistance        | R <sub>IOVL_IOVCC</sub> | Inferred from V <sub>OL</sub> measurements                  |                       | 5    | 10   | Ω        |  |

| I/OVL_ Input-Voltage High                 | V <sub>IHL</sub>        |                                                             | V <sub>L</sub> - 0.2  |      |      | V        |  |

| I/OVL_ Input-Voltage Low                  | V <sub>ILL</sub>        |                                                             |                       |      | 0.15 | V        |  |

| I/OVCC_ Input-Voltage High                | V <sub>IHC</sub>        |                                                             | V <sub>CC</sub> - 0.4 |      |      | V        |  |

| I/OVCC_ Input-Voltage Low                 | V <sub>ILC</sub>        |                                                             |                       |      | 0.2  | V        |  |

| I/OVL_ Output-Voltage High                | V <sub>OHL</sub>        | I/OVL_ source current = 10µA                                | 0.7 x V <sub>L</sub>  |      |      | V        |  |

| I/OVL_ Output-Voltage Low                 | V <sub>OLL</sub>        | I/OVL_ sink current = 2mA,<br>V <sub>I/OVCC</sub> ≤ 50mV    |                       |      | 0.4  | V        |  |

| I/OVCC_ Output-Voltage High               | V <sub>OHC</sub>        | I/OVCC_ source current = 10µA                               | 0.7 x V <sub>CC</sub> |      |      | V        |  |

| I/OVCC_ Output Voltage Low                | V <sub>OLC</sub>        | I/OVCC_ sink current = 2mA,<br>V <sub>I/OVL</sub> _ ≤ 150mV |                       |      | 0.4  | V        |  |

| TS Input-Voltage High Threshold           | V <sub>IH</sub>         |                                                             | V <sub>L</sub> - 0.2  |      |      | V        |  |

| TS Input-Voltage Low Threshold            | V <sub>IL</sub>         | V <sub>L</sub> > 1.3V                                       |                       |      | 0.2  | V        |  |

| Accelerator Pulse Duration                |                         | Inferred from timing measurements                           |                       |      | 30   | ns       |  |

| V <sub>L</sub> Output Accelerator Source  |                         | $V_L = 0.9V$                                                |                       | 70   |      | $\Omega$ |  |

| Impedance                                 |                         | $V_L = 3.3V$                                                |                       | 15   |      | 52       |  |

| V <sub>CC</sub> Output Accelerator Source |                         | $V_{CC} = 1.65V$                                            |                       | 50   |      | Ω        |  |

| Impedance                                 |                         | V <sub>CC</sub> = 5.0V                                      |                       | 10   |      |          |  |

| Thermal-Shutdown Threshold                |                         | 20°C hysteresis                                             |                       | +150 |      | °C       |  |

| ESD PROTECTION                            |                         |                                                             |                       |      |      |          |  |

| I/OVCC_                                   |                         | Human Body Model, $C_{VCC} = 1\mu F$ , $C_{VL} = 0.1\mu F$  |                       | ±6   |      | kV       |  |

| All Other Pins                            |                         | Human Body Model                                            |                       | ±2   |      | kV       |  |

# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **TIMING CHARACTERISTICS**

$(V_{CC} = +1.65 \text{V to } +5.5 \text{V}, V_L = +0.9 \text{V to the lesser of } V_{CC} + 0.3 \text{V and } 5 \text{V}, \overline{\text{TS}} = V_L, R_L = 1 \text{M}\Omega, C_{VCC} = 1 \mu\text{F}, C_{VL} = 0.1 \mu\text{F}, C_{I/OVCC} = 15 \text{pF}, C_{I/OVCL} = 15 \text{pF}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.}$

| PARAMETER               | SYMBOL                | CONDITIONS                                          | MIN | TYP | MAX | UNITS |  |

|-------------------------|-----------------------|-----------------------------------------------------|-----|-----|-----|-------|--|

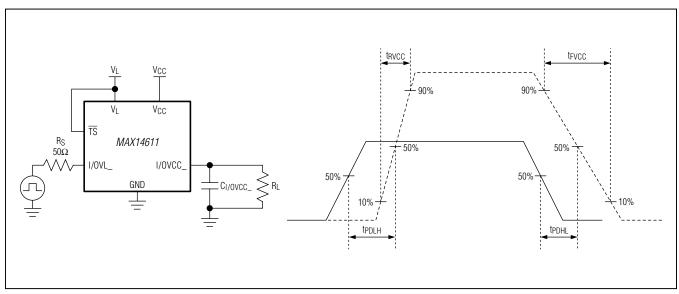

| LOVICC Bigg Time        | +                     | Push-pull driving (Figure 1)                        |     |     | 40  | no    |  |

| I/OVCC_ Rise Time       | tRVCC                 | Open-drain driving (Figure 2, Note 5)               |     |     | 100 | — ns  |  |

| L/OVCC Fall Time        | +                     | Push-pull driving (Figure 1)                        |     |     | 40  |       |  |

| I/OVCC_ Fall Time       | tFVCC                 | Open-drain driving (Figure 2, Note 5)               |     |     | 50  | ns    |  |

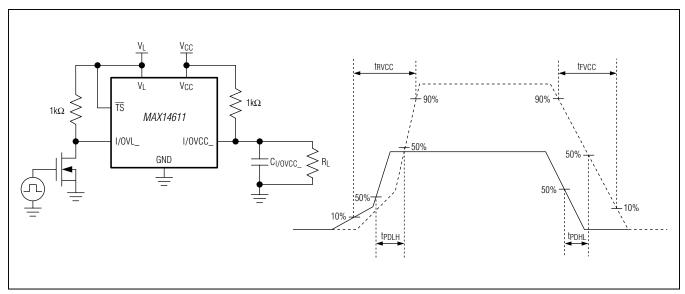

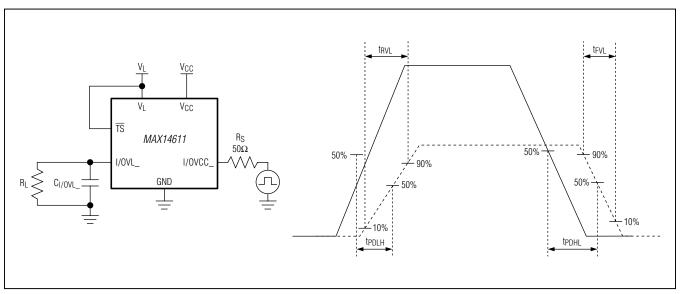

| I/OVI Diag Time         | +                     | Push-pull driving (Figure 3)                        |     |     | 30  |       |  |

| I/OVL_ Rise Time        | t <sub>RVL</sub>      | Open-drain driving (Figure 4, Note 5)               |     |     | 105 | ns    |  |

| LOVI. Fall Times        |                       | Push-pull driving (Figure 3)                        |     |     | 30  | ns    |  |

| I/OVL_ Fall Time        | t <sub>FVL</sub>      | Open-drain driving (Figure 4, Note 5)               |     |     | 30  |       |  |

| Drang gation Daloy      | I/O <sub>VL-VCC</sub> | Push-pull driving (Figure 1)                        |     |     | 40  | ns    |  |

| Propagation Delay       | I/O <sub>VL-VCC</sub> | Open-drain driving (Figure 2, Note 5)               |     |     | 150 |       |  |

| Dramagation Dalay       | I/O <sub>VCC-VL</sub> | Push-pull driving (Figure 3)                        |     |     | 30  |       |  |

| Propagation Delay       | I/O <sub>VCC-VL</sub> | Open-drain driving (Figure 4, Note 5)               |     |     | 105 | ns    |  |

| Channel-to-Channel Skew | and to Ohamad Cham    | Input rise time/fall time < 6ns, push-pull driving  |     |     | 20  |       |  |

| Charmer-to-Charmer Skew | t <sub>SKEW</sub>     | Input rise time/fall time < 6ns, open-drain driving |     |     | 50  | ns    |  |

| Maximum Data Rate       |                       | Push-pull operation                                 |     |     | 20  | Mbps  |  |

| iviaximum Data Rate     |                       | Open-drain operation (Notes 5, 6)                   |     |     | 6   | Mbps  |  |

- Note 2: All units are 100% production tested at T<sub>A</sub> = +25°C. Specifications over operating temperature range are guaranteed by design.

- Note 3: V<sub>L</sub> must be less than or equal to V<sub>CC</sub> during normal operation. However, V<sub>L</sub> can be greater than V<sub>CC</sub> during startup and shutdown conditions.

- Note 4: All timing is 10% to 90% for rise time and 90% to 10% for fall time.

- Note 5: Not production tested; guaranteed by design.

- Note 6: Requires the external pullup resistor.

# **Quad Bidirectional Low-Voltage Logic-Level Translator**

Figure 1. Push-Pull Driving I/OVL\_

Figure 2. Open-Drain Driving I/OVL\_

# **Quad Bidirectional Low-Voltage Logic-Level Translator**

Figure 3. Push-Pull Driving I/OVCC\_

Figure 4. Open-Drain Driving I/OVCC\_

# Quad Bidirectional Low-Voltage Logic-Level Translator

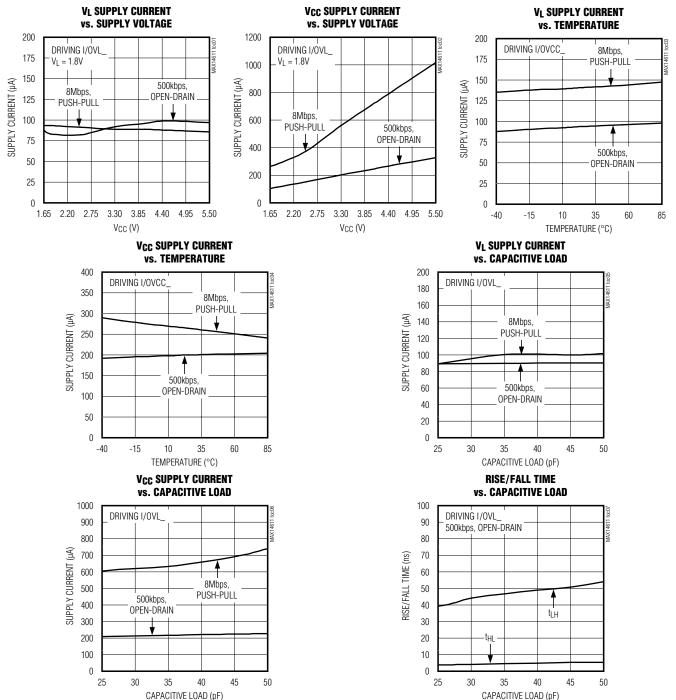

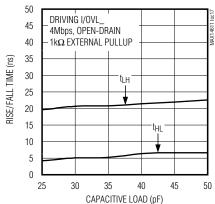

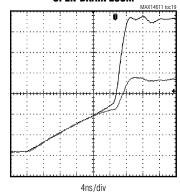

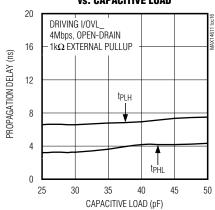

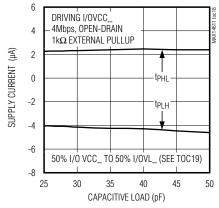

#### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, V_L = 1.8V, R_L = 1M\Omega, C_L = 15pF, T_A = +25^{\circ}C, data rate = 500kbps in open-drain operation and 8Mbps in push-pull operation, unless otherwise noted.)$

# Quad Bidirectional Low-Voltage Logic-Level Translator

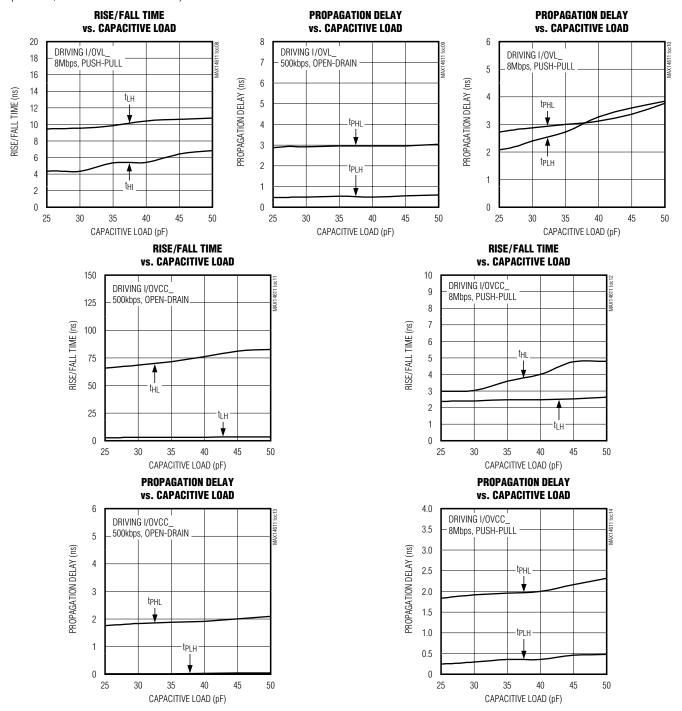

#### **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, V_L = 1.8V, R_L = 1M\Omega, C_L = 15pF, T_A = +25^{\circ}C$ , data rate = 500kbps in open-drain operation and 8Mbps in push-pull operation, unless otherwise noted.)

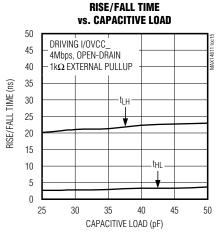

# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, V_L = 1.8V, R_L = 1M\Omega, C_L = 15pF, T_A = +25^{\circ}C$ , data rate = 500kbps in open-drain operation and 8Mbps in push-pull operation, unless otherwise noted.)

# RISE/FALL TIME vs. CAPACITIVE LOAD

#### LOW-TO-HIGH TRANSITION, OPEN-DRAIN ZOOM

# PROPAGATION DELAY vs. Capacitive Load

# PROPAGATION DELAY vs. CAPACITIVE LOAD

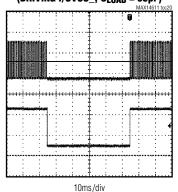

# ENTERING AND EXITING THREE-STATE MODE (DRIVING I/OVCC\_, CLOAD = 50pF)

# Quad Bidirectional Low-Voltage Logic-Level Translator

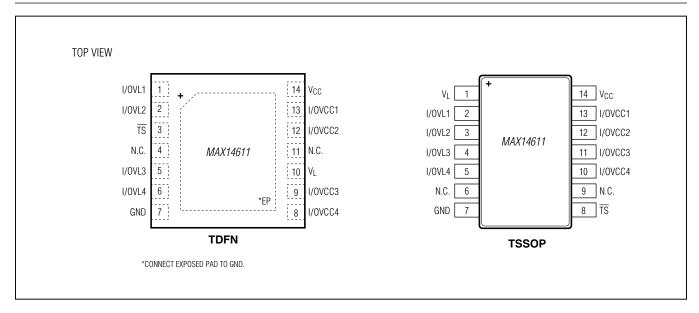

## **Pin Configurations**

## **Pin Description**

| PI      | PIN   |                 | EUNCTION                                                                                                                                                                                                                                                                    |  |  |

|---------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TDFN-EP | TSSOP | NAME            | FUNCTION                                                                                                                                                                                                                                                                    |  |  |

| 1       | 2     | I/OVL1          | Input/Output 1. Reference to V <sub>L</sub> .                                                                                                                                                                                                                               |  |  |

| 2       | 3     | I/OVL2          | Input/Output 2. Reference to V <sub>L</sub> .                                                                                                                                                                                                                               |  |  |

| 3       | 8     | TS              | Three-State Select Input. Drive TS low to place the device in three-state output mode. I/OVCC_ and I/OVL_ are high impedance in three-state output mode.  Note: Logic referenced to V <sub>L</sub> (for logic thresholds, see the <i>Electrical Characteristics</i> table). |  |  |

| 4, 11   | 6,9   | N.C.            | No Connection. Not internally connected.                                                                                                                                                                                                                                    |  |  |

| 5       | 4     | I/OVL3          | Input/Output 3. Reference to V <sub>L</sub> .                                                                                                                                                                                                                               |  |  |

| 6       | 5     | I/OVL4          | Input/Output 4. Reference to V <sub>L</sub> .                                                                                                                                                                                                                               |  |  |

| 7       | 7     | GND             | Ground                                                                                                                                                                                                                                                                      |  |  |

| 8       | 10    | I/OVCC4         | Input/Output 4. Reference to V <sub>CC</sub> .                                                                                                                                                                                                                              |  |  |

| 9       | 11    | I/OVCC3         | Input/Output 3. Reference to V <sub>CC</sub> .                                                                                                                                                                                                                              |  |  |

| 10      | 1     | VL              | Logic Supply Voltage Input, $0.9V \le V_L \le min$ (5.0V, ( $V_{CC} + 0.3V$ )). Connect a $0.1\mu F$ ceramic capacitor as close as possible to the pin.                                                                                                                     |  |  |

| 12      | 12    | I/OVCC2         | Input/Output 2. Reference to V <sub>CC</sub> .                                                                                                                                                                                                                              |  |  |

| 13      | 13    | I/OVCC1         | Input/Output 1. Reference to V <sub>CC</sub> .                                                                                                                                                                                                                              |  |  |

| 14      | 14    | V <sub>CC</sub> | Power Supply Input. The supply range is $1.65 \text{V} \le \text{V}_{\text{CC}} \le 5.5 \text{V}$ . Bypass $\text{V}_{\text{CC}}$ with a 1µF ceramic capacitor as close as possible to the pin to achieve higher ESD protection (±6kV HBM).                                 |  |  |

| _       | _     | EP              | Exposed Pad (TDFN Only). EP is internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical connection point.                                                                                                |  |  |

# Quad Bidirectional Low-Voltage Logic-Level Translator

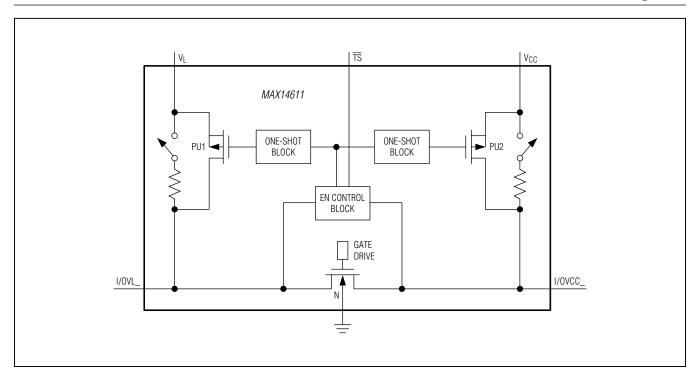

#### **Functional Diagram**

#### **Detailed Description**

The MAX14611 ESD-protected level translator provides the level shifting necessary to allow data transfer in a multivoltage system. Externally applied voltages,  $V_{CC}$  and  $V_{L}$ , set the logic levels on either side of the device. A low-voltage logic signal present on the  $V_{L}$  side of the device appears as a high-voltage logic signal on the  $V_{CC}$  side of the device, and vice-versa.

The MAX14611 bidirectional level translator utilizes a transmission-gate based design (see the *Functional Diagram*) to allow data translation in either direction ( $V_L$   $V_{CC}$ ) on any single data line. The device accepts  $V_L$  from +0.9V to +5.0V and  $V_{CC}$  from +1.65V to +5.5V, making it ideal for data transfer between low-voltage ASICs/PLDs and higher voltage systems.

The device features a three-state output mode, thermal short-circuit protection, and  $\pm 6 \text{kV}$  ESD protection on the V<sub>CC</sub> side for greater protection in applications that route signals externally.

#### **Level Translation**

For proper operation, ensure that +1.65V  $\leq$  V<sub>CC</sub>  $\leq$  +5.5V, 0.9V  $\leq$  V<sub>L</sub>  $\leq$  5.0V, and V<sub>L</sub>  $\leq$  (V<sub>CC</sub> + 0.3V). It is permissible for V<sub>L</sub> to exceed (V<sub>CC</sub> + 0.3V) during power-up sequencing. During power-supply sequencing, when V<sub>CC</sub> is disconnected and V<sub>L</sub> is powered up, a current can be sourced without a latchup or any damage to the device. The maximum data rate of the MAX14611 depends heavily on load capacitance (see the *Typical Operating Characteristics*), output impedance of the driver, and the operational voltage (see the *Timing Characteristics* table).

#### Speed-Up Circuitry

The device features a one-shot generator that decreases the rise time of the output. When triggered following a rising edge, MOSFETs PU1 and PU2 turn on for a short time to pull up I/OVL\_ and I/OVCC\_ to their respective supplies (see the *Functional Diagram*). This greatly reduces the rise time and propagation delay for the low-to-high transition.

# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **Rise-Time Accelerators (Figure 5)**

The device has internal rise-time accelerators, allowing operation up to 20Mbps. The rise-time accelerators are present on both sides of the device and act to speed up the rise time of the input and output of the device, regardless of the direction of the data. The triggering mechanism for these accelerators is both level and edge sensitive. To prevent false triggering of the rise-time accelerators, and to take full advantage of them, signal rise/fall times of less than 2ns/V are recommended for both sides of the device. In open-drain driving, the recommendation only applies for fall time. Under less noisy conditions, longer signal fall times can be acceptable.

#### Three-State Output Mode $(\overline{TS})$

Drive  $\overline{\text{TS}}$  low to place the device in three-state output mode. Connect  $\overline{\text{TS}}$  to V<sub>L</sub> (logic-high) for normal operation. Activating the three-state output mode disconnects the internal 10k $\Omega$  pullup resistors on the I/OVCC\_ and I/OVL\_ lines. This forces the I/O lines to a high-impedance state and decreases the supply current to less than 1µA. The high-impedance I/O lines in three-state output mode allow for use in a multidrop network. When in three-state output mode, keep the I/OVL\_ voltage below (V<sub>L</sub> + 0.3V), and keep the I/OVCC\_ voltage below (V<sub>CC</sub> + 0.3V).

#### **Thermal Short-Circuit Protection**

Thermal-overload detection protects the device from short-circuit fault conditions. In the event of a short-circuit fault and when the junction temperature ( $T_J$ ) reaches +150°C (typ), a thermal sensor signals the three-state output mode logic to force the device into three-state output mode. When  $T_J$  has cooled to +130°C (typ), normal operation resumes.

#### **High ESD Protection**

As with all Maxim devices, ESD-protection structures are incorporated on all pins to protect against electrostatic

discharges encountered during handling and assembly. The I/OVCC\_ lines have extra protection against static electricity. Maxim's engineers have developed state-of-the-art structures to protect these pins against ESD of ±6kV without damage.

The ESD structures withstand high ESD in all states: normal operation, three-state output mode, and powered down. After an ESD event, the device keeps working without latchup, whereas competing products can latch and must be powered down to remove latchup. ESD protection can be tested in various ways. The I/OVCC\_ lines of this product family are characterized for protection.to ±6kV using the Human Body Model.

#### **ESD Test Conditions**

Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### **Applications Information**

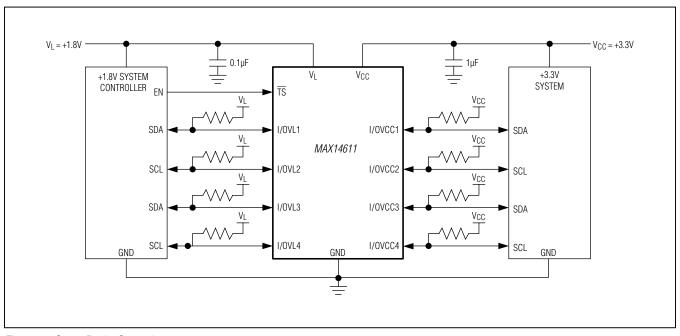

#### **Power-Supply Decoupling**

Bypass V<sub>L</sub> to ground with a 0.1 $\mu$ F capacitor to reduce ripple and ensure correct data transmission. See the *Typical Operating Circuit*. To ensure full ±6kV ESD protection, bypass V<sub>CC</sub> to ground with a 1 $\mu$ F capacitor. Place all capacitors as close as possible to the power-supply pins (V<sub>CC</sub> and V<sub>L</sub>).

#### Push-Pull vs. Open-Drain Driving

The device can be driven in a push-pull configuration. The device includes internal  $10k\Omega$  resistors that pull up I/OVL\_ and I/OVCC\_ to their respective power supplies, allowing operation of the I/O lines with open-drain devices. See the <code>Timing Characteristics</code> table for maximum data rates when using open-drain drivers (<code>Figure 1</code>, <code>Figure 2</code>, <code>Figure 3</code>, <code>Figure 4</code>).

# **Quad Bidirectional Low-Voltage Logic-Level Translator**

Figure 5. Open-Drain Operation

## **Applications Circuit**

# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **Ordering Information**

| PART           | TEMP RANGE     | PIN-PACKAGE |

|----------------|----------------|-------------|

| MAX14611ETD+   | -40°C to +85°C | 14 TDFN-EP* |

| MAX14611EUD+** | -40°C to +85°C | 14 TSSOP    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

PROCESS: BICMOS

### **Chip Information**

# Package Information

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 14 TDFN-EP      | T1433+2         | <u>21-0137</u> | 90-0063             |

| 14 TSSOP        | U14+1           | 21-0066        | 90-0113             |

<sup>\*</sup>EP = Exposed pad.

<sup>\*\*</sup>Future product—contact factory for availability.

# Quad Bidirectional Low-Voltage Logic-Level Translator

#### **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 4/12     | Initial release | _       |

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Analog Devices Inc.:

MAX14611ETD+T MAX14611ETD+ MAX14611EVKIT#