19-4794; Rev 0; 11/98 EVALUATION KIT AVAILABLE

# +5V Single-Supply, 1Msps, 14-Bit Self-Calibrating ADC

# General Description

The MAX1205 is a 14-bit, monolithic, analog-to-digital converter (ADC) capable of conversion rates up to 1Msps. This integrated circuit, built on a CMOS process, uses a fully differential, pipelined architecture with digital error correction and a short self-calibration procedure that corrects for capacitor and gain mismatches and ensures 14-bit linearity at full sample rates. An on-chip track/hold (T/H) maintains superb dynamic performance up to the Nyquist frequency. The MAX1205 operates from a single +5V supply.

The fully differential inputs allow an input swing of  $\pm$ VREF. The reference is also differential, with the positive reference (RFPF) typically connected to +4.096V and the negative reference (RFNF) connected to analog ground. Additional sensing pins (RFPS, RFNS) are provided to compensate for any resistive-divider action that may occur due to finite internal and external resistances in the reference traces and the on-chip resistance of the reference pins. A single-ended input is also possible using two operational amplifiers.

The power dissipation is typically 257mW at +5V, at a sampling rate of 1Msps. The device employs a CMOS-compatible, 14-bit parallel, two's complement output data format. For higher sampling rates, the MAX1201 is a 2.2Msps pin-compatible upgrade to the MAX1205.

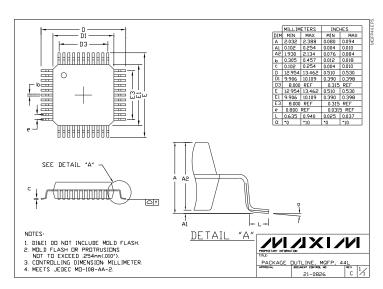

The MAX1205 is available in an MQFP package, and operates over the commercial (0°C to +70°C) and the extended (-40°C to +85°C) temperature ranges.

Applications

Imaging

Communications

Medical

Scanners

Data Acquisition

Features

- + Monolithic, 14-Bit, 1Msps ADC

- + +5V Single Supply

- SNR of 80dB for fIN = 500kHz

- SFDR of 87dB for fIN = 500kHz

- Low Power Dissipation: 257mW

- On-Demand Self-Calibration

- Differential Nonlinearity Error: ±0.3LSB

- Integral Nonlinearity Error: ±1.2LSB

- Three-State, Two's Complement Output Data

# **Ordering Information**

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX1205CMH | 0°C to +70°C   | 44 MQFP     |

| MAX1205EMH | -40°C to +85°C | 44 MQFP     |

#

\_ Maxim Integrated Products 1

*For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.*

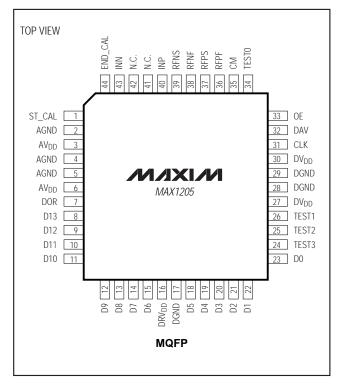

# Pin Configuration

# **ABSOLUTE MAXIMUM RATINGS**

|                                 | +7V<br>+7V                            |

|---------------------------------|---------------------------------------|

| DRV <sub>DD</sub> to DGND, AGND | +7V                                   |

| INP, INN, RFPF, RFPS, RFNF, F   | RFNS,                                 |

| CLK, CM                         | $(AGND - 0.3V)$ to $(AV_{DD} + 0.3V)$ |

| Digital Inputs to DGND          | 0.3V to (DV <sub>DD</sub> + 0.3V)     |

| Digital Output (DAV) to DGND.   | 0.3V to (DRV <sub>DD</sub> + 0.3V)    |

| Other Digital Outputs to DGND   | 0.3V to (DRV <sub>DD</sub> + 0.3V)    |

| W |

|---|

|   |

| С |

| С |

| С |

| С |

|   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = DRV_{DD} = +3.3V, V_{RFPS} = +4.096V, V_{RFNS} = AGND, V_{CM} = +2.048V, V_{IN} = -0.5dBFS, f_{CLK} = 2.048MHz, digital output load \leq 20pF, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                   | SYMBOL          | CONDITIONS                    | MIN   | TYP    | MAX  | UNITS             |

|---------------------------------------------|-----------------|-------------------------------|-------|--------|------|-------------------|

| ANALOG INPUT                                |                 |                               | I     |        |      | 1                 |

| Input Voltage Range                         | Max             | Single-ended                  |       | 4.096  | 4.5  | V                 |

| (Notes 2, 3)                                | V <sub>IN</sub> | Differential                  |       | ±4.096 | ±4.5 | - V               |

| Input Resistance (Note 4)                   | RI              |                               |       | 55     |      | kΩ                |

| Input Capacitance (Note 3)                  | CI              | Per side in track mode        |       | 21     |      | рF                |

| REFERENCE/EXTERNAL                          | L.              |                               | i.    |        |      |                   |

| Reference Voltage (Note 3)                  | VREF            |                               |       | 4.096  | 4.5  | V                 |

| Reference Input Resistance                  |                 |                               | 700   | 1000   |      | Ω                 |

| TRANSFER CHARACTERISTIC                     | S               |                               | ŀ     |        |      |                   |

| Resolution (no missing codes)<br>(Note 5)   | RES             | After calibration, guaranteed | 14    |        |      | Bits              |

| Integral Nonlinearity                       | INL             |                               |       | ±1.2   |      | LSB               |

| Differential Nonlinearity                   | DNL             |                               | -1    | ±0.3   | +1   | LSB               |

| Offset Error                                |                 |                               | -0.2  | ±0.003 | +0.2 | %FSR              |

| Gain Error                                  |                 |                               | -5    | -3.0   | +5   | %FSR              |

| Input-Referred Noise                        |                 |                               |       | 75     |      | μV <sub>RMS</sub> |

| DYNAMIC SPECIFICATIONS (1                   | Note 6)         |                               | Ľ     |        |      |                   |

| Maximum Sampling Rate                       | <b>f</b> SAMPLE | fsample = fclk / 2            | 1.024 |        |      | Msps              |

| Conversion Time (Pipeline<br>Delay/Latency) |                 |                               |       | 4      |      | fsample<br>Cycles |

| Acquisition Time                            | tacq            | To full-scale step (0.006%)   |       | 100    |      | ns                |

| Overvoltage Recovery Time                   | tovr            |                               |       | 410    |      | ns                |

| Aperture Delay                              | t <sub>AD</sub> |                               |       | 3      |      | ns                |

| Full-Power Bandwidth                        |                 |                               |       | 3.3    |      | MHz               |

| Small-Signal Bandwidth                      |                 |                               |       | 78     |      | MHz               |

**MAX1205**

# **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = DRV_{DD} = +3.3V, V_{RFPS} = +4.096V, V_{RFNS} = AGND, V_{CM} = +2.048V, V_{IN} = -0.5dBFS, f_{CLK} = 2.048MHz, digital output load \leq 20pF, T_A = T_{MIN}$  to T\_MAX, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 1)

| PARAMETER                                         | SYMBOL                | CONDITIONS                   | MIN  | TYP  | MAX              | UNITS |  |

|---------------------------------------------------|-----------------------|------------------------------|------|------|------------------|-------|--|

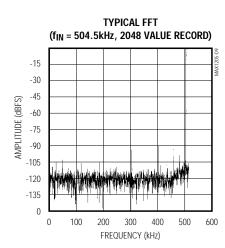

|                                                   |                       | $f_{IN} = 99.5 \text{kHz}$   | 78   | 83   |                  |       |  |

| Signal-to-Noise Ratio<br>(Note 5)                 | SNR                   | f <sub>IN</sub> = 300.5kHz   |      | 81.5 |                  | dB    |  |

|                                                   |                       | $f_{IN} = 504.5 \text{kHz}$  |      | 80   |                  |       |  |

|                                                   |                       | $f_{IN} = 99.5 \text{kHz}$   | 84   | 91   |                  |       |  |

| Spurious-Free Dynamic Range (Note 5)              | SFDR                  | f <sub>IN</sub> = 300.5kHz   |      | 88   |                  | dB    |  |

|                                                   |                       | $f_{IN} = 504.5 \text{kHz}$  |      | 87   |                  |       |  |

| <b>T</b>                                          |                       | $f_{IN} = 99.5 \text{kHz}$   |      | -86  | -80              |       |  |

| Total Harmonic Distortion<br>(Note 5)             | THD                   | $f_{IN} = 300.5 \text{kHz}$  |      | -85  |                  | dB    |  |

| (1016-3)                                          |                       | $f_{IN} = 504.5 \text{kHz}$  |      | -84  |                  |       |  |

|                                                   |                       | $f_{IN} = 99.5 \text{kHz}$   | 77   | 82   |                  |       |  |

| Signal-to-Noise Ratio plus<br>Distortion (Note 5) | SINAD                 | $f_{IN} = 300.5 \text{kHz}$  |      | 79   |                  | dB    |  |

|                                                   |                       | $f_{IN} = 504.5 \text{kHz}$  |      | 78   |                  |       |  |

| POWER REQUIREMENTS                                |                       |                              | ·    |      |                  |       |  |

| Analog Supply Voltage                             | AV <sub>DD</sub>      |                              | 4.75 | 5    | 5.25             | V     |  |

| Analog Supply Current                             | I(AV <sub>DD</sub> )  |                              |      | 51   | 70               | mA    |  |

| Digital Supply Voltage                            | DV <sub>DD</sub>      |                              | 3    |      | 5.25             | V     |  |

| Digital Supply Current                            | I(DV <sub>DD</sub> )  |                              |      | 0.4  | 1.2              | mA    |  |

| Output Drive Supply Voltage                       | DRV <sub>DD</sub>     |                              | 3    |      | DV <sub>DD</sub> | V     |  |

| Output Drive Supply Current                       | I(DRV <sub>DD</sub> ) | 10pF loads on D0–D13 and DAV |      | 0.1  | 0.6              | mA    |  |

| Power Dissipation                                 | PDSS                  |                              |      | 257  | 377              | mW    |  |

| Warm-Up Time                                      |                       |                              |      | 0.1  |                  | sec   |  |

| Dower Supply Dejection Datio                      | PSRR                  | Offset                       | 55   |      |                  | dB    |  |

| Power-Supply Rejection Ratio                      | FSKK                  | Gain                         | 55   |      |                  | uв    |  |

# TIMING CHARACTERISTICS

(AV<sub>DD</sub> = +5V ±5%, DV<sub>DD</sub> = DRV<sub>DD</sub> = +3.3V,  $f_{CLK}$  = 2.048MHz, TA = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 1)

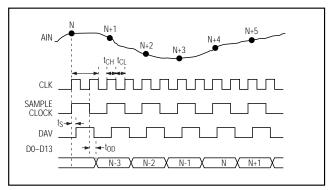

| PARAMETER              | SYMBOL           | CONDITIONS           | MIN | TYP                  | MAX | UNITS          |

|------------------------|------------------|----------------------|-----|----------------------|-----|----------------|

| Conversion Time        | tconv            |                      |     | 4 / fsample          | -   | ns             |

| Clock Period           | tclk             |                      |     | 488                  |     | ns             |

| Clock High Time        | t <sub>CH</sub>  |                      | 187 | 244                  | 301 | ns             |

| Clock Low Time         | t <sub>CL</sub>  |                      | 187 | 244                  | 301 | ns             |

| Acquisition Time       | tacq             |                      |     | t <sub>CLK</sub> / 2 |     | ns             |

| Output Delay           | top              |                      |     | 70                   | 150 | ns             |

| DAV Pulse Width        | t <sub>DAV</sub> |                      |     | 1 / fclk             |     | ns             |

| CLK-to-DAV Rising Edge | ts               |                      |     | 65                   | 145 | ns             |

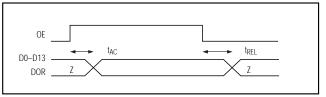

| Data Access Time       | t <sub>AC</sub>  | $C_L = 20 pF$        |     | 16                   | 75  | ns             |

| Bus Relinquish Time    | t <sub>REL</sub> |                      |     | 16                   | 75  | ns             |

| Calibration Time       | tcal             | ST_CAL = 1, Figure 8 |     | 17,400               |     | fCLK<br>cycles |

# **DIGITAL INPUTS AND OUTPUTS**

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = DRV_{DD} = +3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C.$ )

| PARAMETER                      | SYMBOL             | CONDITIONS                       | MIN                       | TYP                        | MAX | UNITS |

|--------------------------------|--------------------|----------------------------------|---------------------------|----------------------------|-----|-------|

| Input Low Voltage              | VIL                |                                  |                           |                            | 0.8 | V     |

| Input High Voltage             | V <sub>IH</sub>    |                                  | DV <sub>DD</sub><br>- 0.8 |                            |     | V     |

| Input Capacitance              |                    |                                  |                           | 4                          |     | pF    |

| CLK Input Low Voltage          | CLKVIL             |                                  |                           |                            | 0.8 | V     |

| CLK Input High Voltage         | CLK <sub>VIH</sub> |                                  | AV <sub>DD</sub><br>- 0.8 |                            |     | V     |

| CLK Input Capacitance          | CCLK               |                                  |                           | 9                          |     | pF    |

| Digital Input Current          | lin_               | $V_{IN} = 0 \text{ or } DV_{DD}$ |                           | ±0.1                       | ±10 | μA    |

| Clock Input Current            | ICLK               |                                  | -10                       | ±1                         | +10 | μA    |

| Output Low Voltage             | Vol                | I <sub>SINK</sub> = 1.6mA        |                           | 70                         | 400 | mV    |

| Output High Voltage            | Voh                | Isource = 200µA                  | DV <sub>DD</sub><br>- 0.4 | DV <sub>DD</sub><br>- 0.03 |     | V     |

| Three-State Leakage Current    | ILEAKAGE           |                                  |                           | ±0.1                       | ±10 | μA    |

| Three-State Output Capacitance | Cout               |                                  |                           | 3.5                        |     | рF    |

Note 1: Reference inputs driven by operational amplifiers for Kelvin-sensed operation.

**Note 2:** For unipolar mode, the analog input voltage  $V_{INP}$  must be within 0V and  $V_{REF}$ ,  $V_{INN} = V_{REF} / 2$ ; where  $V_{REF} = V_{RFPS} - V_{RFNS}$ . For differential mode, the analog inputs INP and INN must be within 0V and  $V_{REF}$ ; where  $V_{REF} = V_{RFPS} - V_{RFNS}$ . The common mode of the inputs INP and INN is  $V_{REF} / 2$ .

Note 3: Minimum and maximum parameters are not tested. Guaranteed by design.

Note 4:  $R_I$  varies inversely with sample rate.

**Note 5:** Calibration remains valid for temperature changes within  $\pm 20^{\circ}$ C and power-supply variations  $\pm 5\%$ .

Note 6: All AC specifications are shown for the differential mode.

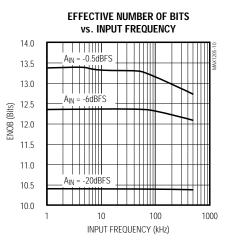

DIFFERENTIAL NONLINEARITY vs. INTEGRAL NONLINEARITY vs. SINGLE-TONE SPURIOUS-FREE DYNAMIC RANGE TWO'S COMPLEMENT OUTPUT CODE TWO'S COMPLEMENT OUTPUT CODE vs. INPUT AMPLITUDE (f<sub>IN</sub> = 99.5kHz) 1.0 1 25 120 1.00 dBF 110 0.75 100 0.5 0.50 90 (qB) DNL (LSB) 80 0 SFDR ( 0 70 -0.25 60 -0.50 dBc -0.5 50 -0.75 -1.00 40 -1.25 -1.0 30 -8192 -6144 -4096 -2048 0 2048 4096 6144 8192 -8192 -6144 -4096 -2048 0 2048 4096 6144 8192 -70 -50 -40 -80 -60 -30 -20 -10 0 TWO'S COMPLEMENT OUTPUT CODE TWO'S COMPLEMENT OUTPUT CODE INPUT AMPLITUDE (dBFS) TOTAL HARMONIC DISTORTION SIGNAL-TO-NOISE RATIO PLUS SIGNAL-TO-NOISE RATIO **DISTORTION vs. INPUT FREQUENCY** vs. INPUT FREQUENCY vs. INPUT FREQUENCY 84 85  $A_{IN} = -0.5 dBFS$ -76 82  $A_{IN} = -0.5 dBFS$ -20dBES AIN 80 -78 80 78 -80 -6dBFS  $A_{IN} = -6dBFS$  $A_{IN} = -6dBFS$ · Ain = 76 75 SINAD (dB) THD (dB) (dB) -82 74 SNR 72 70 -84 70 -86 68 65  $A_{IN} = -0.5 dBFS$ -88  $A_{IN} = -20 dBFS$ 66  $A_{IN} = -20 dBFS$ -90 64 60 1000 1000 1 10 100 10 100 10 100 1000 1 1 INPUT FREQUENCY (kHz) INPUT FREQUENCY (kHz) INPUT FREQUENCY (kHz) SIGNAL-TO-NOISE RATIO PLUS DISTORTION TYPICAL FFT vs. SAMPLING RATE (fin = 99.5kHz) (fIN = 99.5kHz, 2048 VALUE RECORD) 85 AIN = -0.5dBFS -15 -30 84 -45 AMPLITUDE (dBFS) 83 -60 SINAD (dB) -75 82 -90 -105 81 -120 -135 80 0 0.1 0 100 200 300 400 500 600 SAMPLE RATE (Msps) FREQUENCY (kHz)

# Typical Operating Characteristics

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = DRV_{DD} = +3.3V, V_{RFPS} = +4.096V, V_{RFNS} = AGND, V_{CM} = +2.048V, differential input, f_{CLK} = 2.048MHz, calibrated, T_A = +25°C, unless otherwise noted.)$

<u> MIXIM \_</u>

**MAX1205**

# Typical Operating Characteristics (continued)

$(AV_{DD} = +5V \pm 5\%, DV_{DD} = DRV_{DD} = +3.3V, V_{RFPS} = +4.096V, V_{RFNS} = AGND, V_{CM} = +2.048V, differential input, f_{CLK} = 2.048MHz, calibrated, T_A = +25°C, unless otherwise noted.)$

# Pin Description

| PIN        | NAME   | FUNCTION                                                                                                          |

|------------|--------|-------------------------------------------------------------------------------------------------------------------|

| 1          | ST_CAL | Digital Input to Start Calibration.<br>ST_CAL = 0: Normal conversion mode.<br>ST_CAL = 1: Start self-calibration. |

| 2, 4, 5    | AGND   | Analog Ground                                                                                                     |

| 3, 6       | AVDD   | Analog Power Supply, +5V ±5%                                                                                      |

| 7          | DOR    | Data Out-of-Range Bit                                                                                             |

| 8          | D13    | Bit 13 (MSB)                                                                                                      |

| 9          | D12    | Bit 12                                                                                                            |

| 10         | D11    | Bit 11                                                                                                            |

| 11         | D10    | Bit 10                                                                                                            |

| 12         | D9     | Bit 9                                                                                                             |

| 13         | D8     | Bit 8                                                                                                             |

| 14         | D7     | Bit 7                                                                                                             |

| 15         | D6     | Bit 6                                                                                                             |

| 16         | DRVDD  | Digital Power Supply for the Output Drivers, +3V to +5.25V, DRV <sub>DD</sub> $\leq$ DV <sub>DD</sub>             |

| 17, 28, 29 | DGND   | Digital Ground                                                                                                    |

| 18         | D5     | Bit 5                                                                                                             |

| 19         | D4     | Bit 4                                                                                                             |

| 20         | D3     | Bit 3                                                                                                             |

| 21         | D2     | Bit 2                                                                                                             |

| 22         | D1     | Bit 1                                                                                                             |

| 23         | D0     | Bit 0 (LSB)                                                                                                       |

| 24         | TEST3  | Test Pin 3. Leave unconnected.                                                                                    |

M/IXI/M

# Pin Description (continued)

| PIN    | NAME    | FUNCTION                                                                                                                |  |  |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------|--|--|

| 25     | TEST2   | Test Pin 2. Leave unconnected.                                                                                          |  |  |

| 26     | TEST1   | Test Pin 1. Leave unconnected.                                                                                          |  |  |

| 27, 30 | DVDD    | Digital Power Supply, +3V to +5.25V                                                                                     |  |  |

| 31     | CLK     | Input Clock. Receives power from AV <sub>DD</sub> to reduce jitter.                                                     |  |  |

| 32     | DAV     | Data Valid Clock Output. This clock can be used to transfer the data to a memory or any other data-acquisition system.  |  |  |

| 33     | OE      | Output Enable Input.<br>OE = 0: D0-D13 and DOR are high impedance.<br>OE = 1: All bits are active.                      |  |  |

| 34     | TESTO   | Test Pin 0. Leave unconnected.                                                                                          |  |  |

| 35     | СМ      | Common-Mode Voltage. Analog Input. Drive midway between positive and negative reference voltages.                       |  |  |

| 36     | RFPF    | Positive Reference Voltage. Force input.                                                                                |  |  |

| 37     | RFPS    | Positive Reference Voltage. Sense input.                                                                                |  |  |

| 38     | RFNF    | Negative Reference Voltage. Force input.                                                                                |  |  |

| 39     | RFNS    | Negative Reference Voltage. Sense input.                                                                                |  |  |

| 40     | INP     | Positive Input Voltage                                                                                                  |  |  |

| 41, 42 | N.C.    | Not Connected. No internal connection.                                                                                  |  |  |

| 43     | INN     | Negative Input Voltage                                                                                                  |  |  |

| 44     | END_CAL | Digital Output for End of Calibration.<br>END_CAL = 0: Calibration in progress.<br>END_CAL = 1: Normal conversion mode. |  |  |

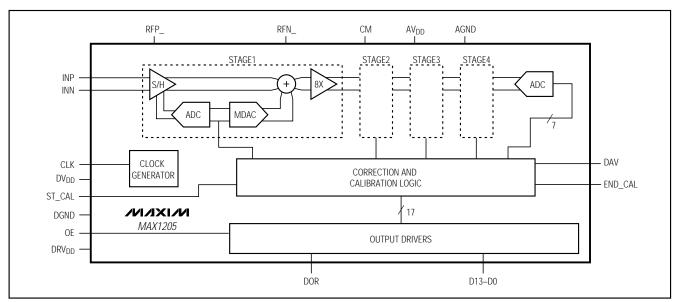

# **Detailed Description**

# **Converter Operation**

The MAX1205 is a 14-bit, monolithic, analog-to-digital converter (ADC) capable of conversion rates up to 1Msps. It uses a multistage, fully differential pipelined architecture with digital error correction and self-calibration to provide typically greater than 91dB spurious-free dynamic range at a 1Msps sampling rate. Its signal-to-noise ratio, harmonic distortion, and intermodulation products are also consistent with 14-bit accuracy up to the Nyquist frequency. This makes the device suitable for applications such as imaging, scanners, data acquisition, and digital communications.

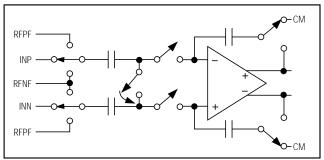

Figure 1 shows the simplified, internal structure of the ADC. A switched-capacitor pipelined architecture is used to digitize the signal at a high throughput rate. The first four stages of the pipeline use a low-resolution quantizer to approximate the input signal. The multiplying digital-to-analog converter (MDAC) stage is used to subtract the quantized analog signal from the input. The residue is then amplified with a fixed gain and

passed on to the next stage. The accuracy of the converter is improved by a digital calibration algorithm which corrects for mismatches between the capacitors in the switched capacitor MDAC. Note that the pipeline introduces latency of four sampling periods between the input being sampled and the output appearing at D13–D0.

While the device can handle both single-ended and differential inputs (see *Requirements for Reference and Analog Signal Inputs*), the latter mode of operation will guarantee best THD and SFDR performance. The differential input provides the following advantages compared to a single-ended operation:

- Twice as much signal input span

- Common-mode noise immunity

- Virtual elimination of the even-order harmonics

- Less stringent requirements on the input signal processing amplifiers

Figure 1. Internal Block Diagram

## Requirements for Reference and Analog Signal Inputs

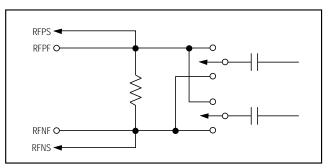

Fully differential switched-capacitor circuits (SC) are used for both the reference and analog inputs (Figure 2). This allows either single-ended or differential signals to be used in the reference and/or analog signal paths. The signal voltage on these pins (INP, INN, RFN\_, RFP\_) should never exceed the analog supply rail, AV<sub>DD</sub>, and should not fall below ground.

## **Choice of Reference**

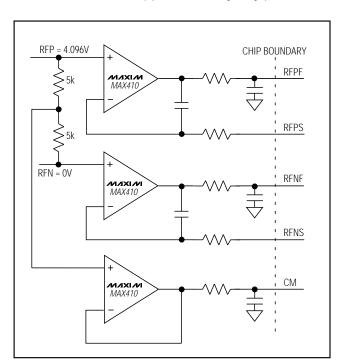

It is important to choose a low-noise reference, such as the MAX6341, which can provide both excellent load regulation and low temperature drift. The equivalent input circuit for the reference pins is shown in Figure 3. Note that the reference pins drive approximately  $1k\Omega$  of resistance on chip. They also drive a switched capacitor of 21pF. To meet the dynamic performance, the reference voltage is required to settle to 0.0015% within one clock cycle. Accomplish this by choosing an appropriate driving circuit (Figure 4). The capacitors at the reference pins (RFPF, RFNF) provide the dynamic charge required during each clock cycle, while the op amps ensure accuracy of the reference signals. These capacitors must have low dielectric-absorption characteristics, such as polystyrene or teflon capacitors.

The reference pins can be connected to either singleended or differential voltages within the specified maximum levels. Typically the positive reference pin (RFPF) would be driven to 4.096V, and the negative reference pin (RFNF) connected to analog ground. There are sense pins, RFPS and RFNS, which can be used with

Figure 2. Simplified MDAC Architecture

Figure 3. Equivalent Input at the Reference Pins. The sense pins should not draw any DC current.

external amplifiers to compensate for any resistive drop on these lines, internal or external to the chip. Ensure a correct reference voltage by using proper Kelvin connections at the sense pins.

## Common-Mode Voltage

The switched capacitor input circuit at the analog input allows signals between AGND and the analog power supply. Since the common-mode voltage has a strong influence on the performance of the ADC, the best results are obtained by choosing  $V_{CM}$  to be at half the difference between the reference voltages  $V_{RFP}$  and  $V_{RFN}$ . Achieve this by using a resistive divider between the two reference potentials. Figure 4 shows a typical driving circuit for good dynamic performance.

#### Analog Signal Conditioning

For single-ended inputs the negative analog input pin (INN) is connected to the common-mode voltage pin (CM), and the positive analog input pin (INP) is connected to the input.

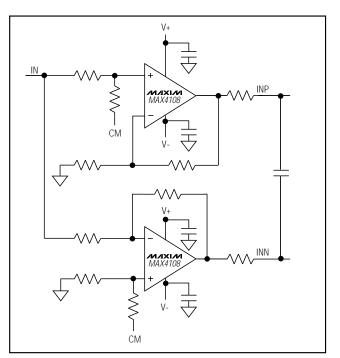

To take full advantage of the ADC's superior AC performance up to the Nyquist frequency, drive the chip with differential signals. In communication systems, the signals may inherently be available in differential mode. Medical and/or other applications may only provide single-ended inputs. In this case, convert the singleended signals into differential ones by using the circuit recommended in Figure 5. Use low-noise, wideband amplifiers such as the MAX4108 to maintain the signal purity over the full-power bandwidth of the MAX1205 input.

Lowpass or bandpass signals may be required to improve the signal-to-noise-and-distortion ratio of the incoming signal. For low-frequency signals (<100kHz), active filters may be used. For higher frequencies, passive filters are more convenient.

## Single-Ended to Differential Conversion Using Transformers

An alternative single-ended to differential-ended conversion method is a balun transformer such as the CTX03-13675 from Coiltronics. An important benefit of these transformers is their ability to level-shift singleended signals referred to ground on the primary side to optimum common-mode voltages on the secondary side. At frequencies below 20kHz, the transformer core begins to saturate, causing odd-order harmonics.

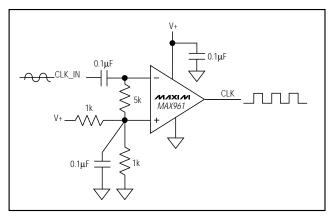

#### **Clock Source Requirements**

Pipelined ADCs typically need a 50% duty cycle clock. To avoid this constraint, the MAX1205 provides a

Figure 4. Drive Circuit for the Reference Pins and the Common-Mode Pin

Figure 5. A simple circuit generates differential signals from a single-ended input referred to analog ground. The commonmode voltage at INP and INN is the same as CM.

///XI//

divide-by-two circuit, which relaxes this requirement. The clock generator should be chosen commensurate with the frequency range, amplitude, and slew rate of the signal source. If the slew rate of the input signal is small, the jitter requirement on the clock is relaxed. However, if the slew rate is high, the clock jitter needs to be kept at a minimum. For a full-scale amplitude input sine wave, the maximum possible signal-to-noise ratio (SNR) due completely to clock jitter is given by:

$$SNR_{MAX} = \frac{1}{2\pi f_{IN}\sigma_{JITTER}}$$

For example, if  $f_{IN}$  is 0.5MHz and  $\sigma_{JITTER}$  is 20ps RMS, then the SNR limit due to jitter is about 84dB. Generating such a clock source requires a low-noise comparator and a low-phase-noise signal generator. The clock circuit shown in Figure 6 is a possible solution.

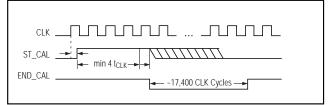

#### **Calibration Procedure**

Since the MAX1205 is based on a pipelined architecture, low-resolution quantizers ("coarse ADCs") are used to approximate the input signal. MDACs of the same resolution are then used to reconstruct the input signal, which is subtracted from the input and the residue amplified by the SC gain stage. This residue is then passed on to the next stage.

The accuracy of the MAX1205 is limited by the precision of the MDAC, which is strongly dependent on the matching of the capacitors used. The mismatch between the capacitors is determined and stored in an on-chip memory, which is later used during the conversion of the input signal.

During the calibration procedure, the clock must be running continuously. ST\_CAL (start of calibration) is

Figure 6. Clock Generation Circuit Using a Low-Noise Comparator

initiated by a positive pulse with a minimum width of four clock cycles, but no longer than about 17,400 clock cycles (Figure 8).

The ST\_CAL input may be asynchronous with the clock, since it is retimed internally. With ST\_CAL activated, END\_CAL goes low one or two clock cycles later and remains low until the calibration is complete. During this period, the reference voltages must be stable to less than 0.01%; otherwise the calibration will be invalid. During calibration, the analog inputs INP and INN are not used; however, better performance is achieved if these inputs are static. Once END\_CAL goes high (indicating that the calibration procedure is complete), the ADC is ready for conversion.

Once calibrated, the MAX1205 is insensitive to small changes (<5%) in power-supply voltage or temperature. Following calibration, if the temperature changes more than  $\pm 20^{\circ}$ C, the device should be recalibrated to maintain optimum performance.

Figure 7. Main Timing Diagram

Figure 8. Timing for Start and End of Calibration

Figure 9. Timing for Bus Access and Bus Relinquish— Controlled by Output Enable (OE)

## Two's Complement Output

The MAX1205 outputs data in two's complement format. Table 1 shows how to convert the various fullscale inputs into their two's complement output codes.

# \_Applications Information

## Signal-to-Noise Ratio (SNR)

For a waveform perfectly reconstructed from digital samples, the theoretical maximum SNR is the ratio of full-scale analog input (RMS value) to the RMS quantization error (residual error). The ideal, theoretical minimum analog-to-digital noise is caused by quantization error only and results directly from the ADC's resolution (N bits):

SNR(MAX) = (6.02N + 1.76)dB

In reality, there are other noise sources besides quantization noise including thermal noise, reference noise, clock jitter, etc. Therefore, SNR is computed by taking the ratio of the RMS signal to the RMS noise, which includes all spectral components minus the fundamental, the first nine harmonics, and the DC offset.

## Signal-to-Noise Plus Distortion (SINAD)

SINAD is the ratio of the fundamental input frequency's RMS amplitude to all other ADC output signals:

SINAD (dB) = 20log [(Signal<sub>RMS</sub> / (Noise + Distortion)<sub>RMS</sub>]

## Effective Number of Bits (ENOB)

ENOB indicates the global accuracy of an ADC at a specific input frequency and sampling rate. An ideal ADC's error consists of quantization noise only. With an input range equal to the full-scale range for the ADC,

Table 1. Two's Complement Conversion

the effective number of bits can be calculated as follows:

ENOB = (SINAD - 1.76) / 6.02

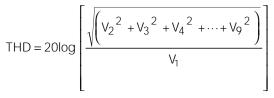

## Total Harmonic Distortion (THD)

THD is the ratio of the RMS sum of the first nine harmonics of the input signal to the fundamental itself. This is expressed as:

where  $V_1$  is the fundamental amplitude, and  $V_2$  through  $V_9$  are the amplitudes of the 2nd through 9th order harmonics.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio of RMS amplitude of the fundamental (maximum signal component) to the RMS value of the next largest spurious component, excluding DC offset.

#### Grounding and Power-Supply Decoupling

Grounding and power-supply decoupling strongly influence the performance of the MAX1205. At 14-bit resolution, unwanted digital crosstalk may couple through the input, reference, power-supply, and ground connections; this adversely affects the SNR or SFDR. In addition, electromagnetic interference (EMI) can either couple into or be generated by the MAX1205. Therefore, grounding and power-supply decoupling guidelines should be closely followed.

| SCALE       | OFFSET BINARY | TWO'S COMPLEMENT | ONE'S COMPLEMENT |

|-------------|---------------|------------------|------------------|

| +FSR - 1LSB | 11111111      | 01111111         | 01111111         |

| +3/4FSR     | 11100000      | 01100000         | 01100000         |

| +1/2FSR     | 11000000      | 01000000         | 01000000         |

| +1/4FSR     | 10100000      | 00100000         | 00100000         |

| +0          | 10000000      | 00000000         | 00000000         |

| -0          | _             | _                | 11111111         |

| -1/4FSR     | 01100000      | 11100000         | 11011111         |

| -1/2FSR     | 01000000      | 11000000         | 10111111         |

| -3/4FSR     | 00100000      | 10100000         | 10011111         |

| -FSR + 1LSB | 00000001      | 10000001         | 10000000         |

| -FSR        | 00000000      | 10000000         | _                |

# **MAX1205**

# +5V Single-Supply, 1Msps, 14-Bit Self-Calibrating ADC

First, a multilayer printed circuit board (PCB) with separate ground and power-supply planes is recommended. Run high-speed signal traces directly above the ground plane. Since the MAX1205 has separate analog and digital ground buses (AGND and DGND respectively), the PCB should also have separate analog and digital ground sections connected at only one point (star ground). Digital signals should run above the digital ground plane and analog signals should run above the analog ground plane. Digital signals should be kept far away from the sensitive analog inputs, reference inputs senses, common-mode input, and clock input.

The MAX1205 has three power-supply inputs: analog V<sub>DD</sub> (AV<sub>DD</sub>), digital V<sub>DD</sub> (DV<sub>DD</sub>), and drive V<sub>DD</sub> (DRV<sub>DD</sub>). Each AV<sub>DD</sub> input should be decoupled with parallel ceramic-chip capacitors of values  $0.1\mu$ F and  $0.001\mu$ F, with these capacitors as close to the pin as possible and with the shortest possible connection to the ground plane. The DV<sub>DD</sub> pins should also have separate  $0.1\mu$ F capacitors adjacent to their respective pins, as should the DRV<sub>DD</sub> pin. Minimize the digital load capacitance. However, if the total load capacitance on each digital output exceeds 20pF, the DRV<sub>DD</sub> decoupling capacitor should be increased or, preferably, digital buffers should be added.

The power-supply voltages should be decoupled with large tantalum or electrolytic capacitors at the point they enter the PCB. Ferrite beads with additional

decoupling capacitors forming a pi-network may improve performance.

The analog power-supply input (AV<sub>DD</sub>) for the MAX1205 is typically +5V while the digital supplies can vary from +5V to +3V. Usually, DV<sub>DD</sub> and DRV<sub>DD</sub> pins are connected to the same power supply. Note that the DV<sub>DD</sub> supply voltage must be greater than or equal to the DRV<sub>DD</sub> voltage. For example, a digital +3.3V supply could be connected to DRV<sub>DD</sub> while a cleaner +5V supply is connected to DV<sub>DD</sub>, resulting in slightly improved performance. Alternatively, the +3.3V supply could be connected to both DRV<sub>DD</sub> and DV<sub>DD</sub>. However, the +3.3V supply should not be connected to DV<sub>DD</sub> while the +5V supply is connected to DRV<sub>DD</sub> and DV<sub>DD</sub>.

Table 2. Power-Supply Voltage Combinations

| AV <sub>DD</sub> (V) | DV <sub>DD</sub> (V) | DRV <sub>DD</sub> (V) | ALLOWED/NOT ALLOWED |

|----------------------|----------------------|-----------------------|---------------------|

| +5                   | +5                   | +5                    | Allowed             |

| +5                   | +5                   | +3.3                  | Allowed             |

| +5                   | +3.3                 | +3.3                  | Allowed             |

| +5                   | +3.3                 | +5                    | Not Allowed         |

# \_Chip Information

TRANSISTOR COUNT: 56,577 SUBSTRATE CONNECTED TO: AGND

# Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Printed USA

#### \_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1998 Maxim Integrated Products

12

is a registered trademark of Maxim Integrated Products.

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: <u>MAX1205CMH+</u> <u>MAX1205CMH+T</u>