# I<sup>2</sup>C Slave Device Extender Over Rugged Differential Link

## **FEATURES**

- Up to 1MHz Serial Clock, Fast-mode Plus (Fm+)

- Selectable Link Baud Rates Extend I<sup>2</sup>C Up to 1200m

- Protected from Overvoltage Line Faults to ±60V

- ±40kV ESD on Link Pins

- IEC Level 4 ESD ±8kV and EFT ±5kV on Link Pins

- Extended Common Mode Range: ±15V

- Remote Interrupt/SMBALERT and Control Signals

- Low EMI Mode

- SMBus 3.0 Compatible

- I<sup>2</sup>C Idle Detection, and Stuck Bus Protection

- I<sup>2</sup>C Device Address Sharing

- 3V to 5.5V Supply Voltage

- 1.62V to 5.5V Logic Supply

- 4mm × 5mm 20-Lead QFN package

## **APPLICATIONS**

- Industrial Control and Sensors

- Lighting and Sound System Control

## DESCRIPTION

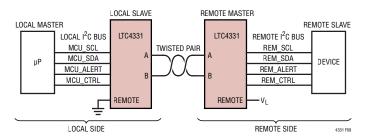

The LTC®4331 is a point-to-point SMBus compatible I<sup>2</sup>C slave device extender designed for operation in high noise industrial environments. Using a ±60V fault protected differential transceiver, the LTC4331 can extend an I<sup>2</sup>C/SMBus bus, including SMBALERT and a control signal, over a single twisted pair differential link up to 1200m. With an extended common mode operating range the solution provides tolerance to large ground differences between nodes. For EMI sensitive environments, a slew rate control pin reduces the EMI emitted from the differential link.

In addition, the LTC4331 can act as an I<sup>2</sup>C to I<sup>2</sup>C bridge allowing independent bus frequencies between the local and remote networks. The solution is completely transparent to the master requiring no additional code in most cases; however, a control interface is provided for additional configuration and fault monitoring.

A master controller fully supporting SCL clock-stretching is strongly recommended.

All registered trademarks and trademarks are the property of their respective owners. Patent Pending.

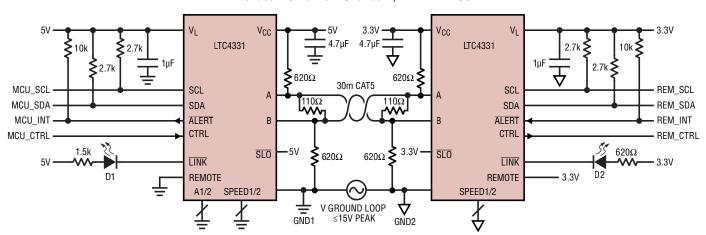

## TYPICAL APPLICATION

#### Extended I<sup>2</sup>C Network Over 30m. 1MHz Fm+ SCL

# LTC4331

# TABLE OF CONTENTS

| Features                            | 1  |

|-------------------------------------|----|

| Applications                        |    |

| Description                         | 1  |

| Typical Application                 |    |

| Absolute Maximum Ratings            |    |

| Pin Configuration                   |    |

| Order InformationOrder Information  |    |

| Electrical Characteristics          | 3  |

| Switching Characteristics           | 5  |

| Typical Performance Characteristics |    |

| Pin Functions                       |    |

| Block DiagramBlock Diagram          |    |

| Test Circuits                       |    |

| Timing Diagrams                     |    |

| Applications Information            |    |

| Typical Applications                |    |

| Package Description                 |    |

| Typical Application                 |    |

| Related Parts                       | 26 |

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Supply Voltages                           |

|-------------------------------------------|

| V <sub>CC</sub> 0.3V to 6V                |

| V <sub>L</sub> 0.3V to 6V                 |

| Logic Signals                             |

| ON, LINK, RDY, SCL, SDA,                  |

| ALERT, SLO0.3V to 6V                      |

| REMOTE, A1, A2, CTRL,                     |

| SPEED1, SPEED20.3V to 6.3 or $V_L + 0.3V$ |

| Interface I/O: A,B60V to 60V              |

| Operating Ambient Temperature Range       |

| LTC4331C0°C to 70°C                       |

| LTC4331I40°C to 85°C                      |

| LTC4331H40°C to 125°C                     |

| Storage Temperature Range65°C to 150°C    |

| Lead Temperature (Soldering, 10 sec)300°C |

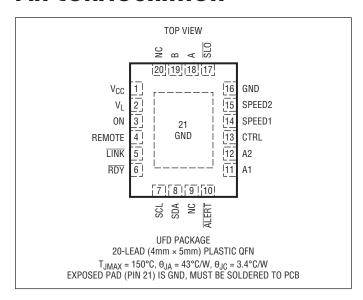

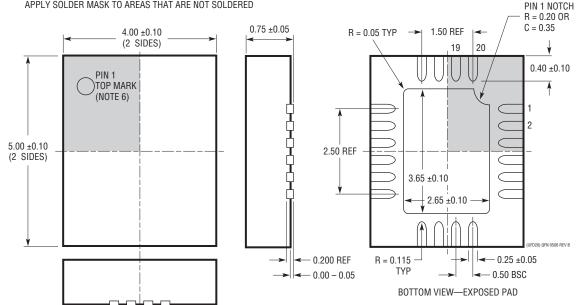

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|--------------|---------------------------------|-------------------|

| LTC4331CUFD#PBF  | LTC4331CUFD#TRPBF | 4331         | 20-Lead (4mm × 5mm) Plastic QFN | 0°C to 70°C       |

| LTC4331IUFD#PBF  | LTC4331IUFD#TRPBF | 4331         | 20-Lead (4mm × 5mm) Plastic QFN | -40°C to 85°C     |

| LTC4331HUFD#PBF  | LTC4331HUFD#TRPBF | 4331         | 20-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ , $V_{CC} = 5V$ , $V_L = 3.3V$ , GND = 0V unless otherwise noted.

| SYMBOL          | PARAMETER                | CONDITIONS                                                                                                       |   | MIN  | TYP | MAX            | UNITS          |

|-----------------|--------------------------|------------------------------------------------------------------------------------------------------------------|---|------|-----|----------------|----------------|

| Supplies        |                          |                                                                                                                  |   |      |     |                |                |

| V <sub>CC</sub> | Operating Supply Range   |                                                                                                                  | • | 3    |     | 5.5            | V              |

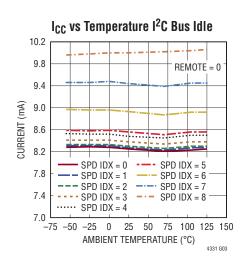

| I <sub>CC</sub> | Operating Supply Current | Low Power: ON = 0<br>Idle: ON = 1, I <sup>2</sup> C Bus Idle, Link = Fm+<br>Active: I <sup>2</sup> C Transaction | • |      | 1   | 40<br>12<br>65 | μΑ<br>mA<br>mA |

| $V_L$           | Logic Supply Range       |                                                                                                                  | • | 1.62 |     | 5.5            | V              |

| IL              | Logic Supply Current     |                                                                                                                  | • |      |     | 140            | μA             |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{CC} = 5V$ , $V_L = 3.3V$ , GND = 0V unless otherwise noted.

| SYMBOL             | PARAMETER                                                        | CONDITIONS                                     |   | MIN                    | TYP  | MAX                    | UNITS |

|--------------------|------------------------------------------------------------------|------------------------------------------------|---|------------------------|------|------------------------|-------|

| Differenti         | ial Driver                                                       |                                                |   |                        |      |                        |       |

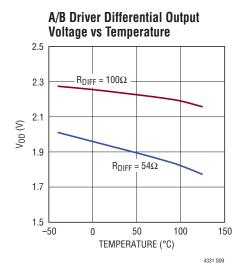

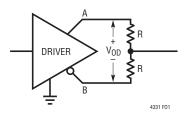

| V <sub>OD</sub>    | Differential Driver Output Voltage                               | $R = \infty$ $R = 27\Omega \text{ (Figure 1)}$ | • | 1.5<br>1.5             |      | V <sub>CC</sub><br>5   | V     |

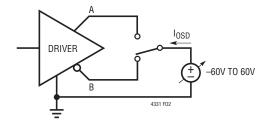

| I <sub>OSD</sub>   | Maximum Driver Short-Circuit Current                             | -60V ≤ (A or B) ≤ 60V (Figure 2)               | • |                        | ±150 | ±250                   | mA    |

| Different          | ial Receiver                                                     |                                                |   |                        |      |                        |       |

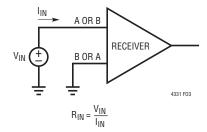

| R <sub>IN</sub>    | Receiver Input Resistance                                        | $0 \le V_{CC} \le 5.5V$ (Figure 3)             |   |                        | 112  |                        | kΩ    |

| V <sub>CM</sub>    | Receiver Common Mode Input Voltage                               |                                                | • |                        |      | ±15                    | V     |

| $V_{TH}$           | Differential Input Signal Threshold                              | -15V < V <sub>CM</sub> < 15V (Note 2)          | • |                        |      | ±200                   | mV    |

| Logic              |                                                                  |                                                |   |                        |      |                        |       |

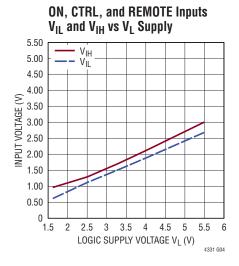

| V <sub>IH</sub>    | High Level Input Voltage (ON, CTRL, REMOTE)                      | 1.62V < V <sub>L</sub> < 5.5V                  | • | 0.8 • V <sub>L</sub>   |      |                        | V     |

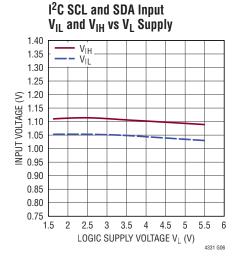

|                    | High Level Input Voltage (SCL, SDA, ALERT)                       | 1.62V < V <sub>L</sub> < 5.5V                  | • | 1.35                   |      |                        | V     |

|                    | High Level Input Voltage (SLO)                                   | 3V < V <sub>CC</sub> < 5.5V                    | • | 0.67 • V <sub>CC</sub> |      |                        | V     |

| V <sub>IH3ST</sub> | High Level Input Voltage (A1, A2, SPEED1, SPEED2)                |                                                | • | V <sub>L</sub> - 0.25  |      |                        | V     |

| V <sub>IM3ST</sub> | Mid Level Input Voltage (A1, A2, SPEED1, SPEED2)                 |                                                | • | 0.45 • V <sub>L</sub>  |      | 0.55 • V <sub>L</sub>  | V     |

| V <sub>IL3ST</sub> | Low Level Input Voltage (A1, A2, SPEED1, SPEED2)                 |                                                | • |                        |      | 0.25                   | V     |

| $V_{IL}$           | Low Level Input Voltage (ON, CTRL, REMOTE)                       | 1.62V < V <sub>L</sub> < 5.5V                  | • |                        |      | 0.2 • V <sub>L</sub>   | V     |

|                    | Low Level Input Voltage (SCL, SDA, ALERT)                        | 1.62V < V <sub>L</sub> < 5.5V                  | • |                        |      | 0.8                    | V     |

|                    | Low Level Input Voltage (SLO)                                    | 3V < V <sub>CC</sub> < 5.5V                    | • |                        |      | 0.33 • V <sub>CC</sub> | V     |

|                    | Digital Input Current (SCL, SDA, ALERT)                          | $V_{IN} = 0V \text{ to } V_{L}$                | • |                        |      | ±5                     | μА    |

|                    | Digital Input Current (ON, CTRL, A1, A2, REMOTE, SPEED1, SPEED2) | V <sub>IN</sub> = 0V to V <sub>L</sub>         | • |                        |      | ±60                    | μА    |

|                    | Digital Input Current (SLO)                                      |                                                | • |                        | 0    | ±5                     | μА    |

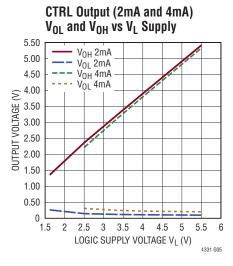

| $V_{OH}$           | High Level Output Voltage (CTRL)                                 | I <sub>LOAD</sub> = -500μA                     | • | V <sub>L</sub> - 0.2   |      |                        | V     |

| $V_{OL}$           | Low Level Output Voltage (LINK, RDY, ALERT, CTRL)                | I <sub>LOAD</sub> = 500μA                      | • |                        |      | 0.2                    | V     |

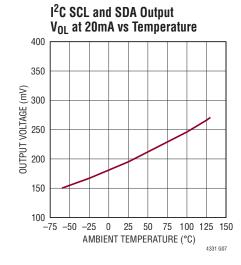

|                    | Low Level Output Voltage (SCL, SDA)                              | I <sub>LOAD</sub> = 20mA                       | • |                        |      | 0.4                    | V     |

| I <sub>OZ</sub>    | High-Z Output Leakage Current (SCL, SDA, ALERT, LINK)            |                                                | • |                        |      | ±5                     | μА    |

|                    | High-Z Output Leakage Current (RDY)                              |                                                | • |                        |      | -60                    | μА    |

|                    | Output Source Current (Short-Circuit) (CTRL)                     |                                                |   |                        | -80  |                        | mA    |

|                    | Output Sink Current (Short-Circuit) (LINK, RDY, ALERT, CTRL)     |                                                |   |                        | 80   |                        | mA    |

|                    | Short-Circuit Current (SCL, SDA)                                 |                                                |   |                        | 100  |                        | mA    |

| C <sub>IN</sub>    | Input Pin Capacitance                                            | SCL, SDA (Note 2)                              |   |                        | 10   |                        | pF    |

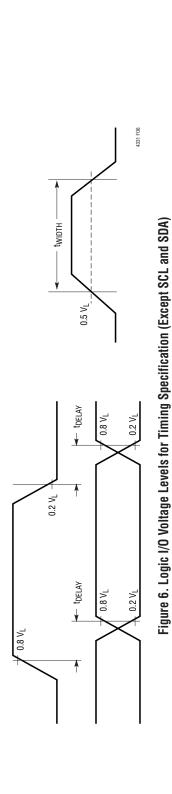

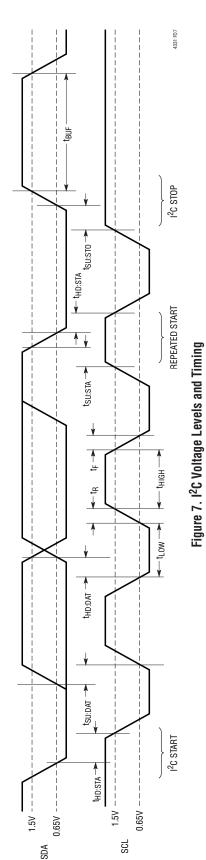

**SWITCHING CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $C_L = 20pF$ ,  $V_{CC} = 5V$ ,  $V_L = 3.3V$ , GND = 0V; unless otherwise noted. Conditions Fast-mode Plus, Fast-mode, and Standard-mode listed below as Fm+, Fm, and Sm respectively.

| SYMBOL                     | PARAMETER                                                   | CONDITIONS                                                      |     | MIN                | TYP               | MAX  | UNITS          |

|----------------------------|-------------------------------------------------------------|-----------------------------------------------------------------|-----|--------------------|-------------------|------|----------------|

| t <sub>ON_LOW</sub>        | Pulse Width of ON Low for Valid Reset Condition             |                                                                 | •   | 1                  |                   |      | μs             |

| Local Mode (REI            | MOTE = 0)                                                   |                                                                 |     |                    |                   |      |                |

| t <sub>READY</sub>         | Delay From ON Rise to RDY Low                               | I <sup>2</sup> C Bus IDLE                                       |     |                    | 65                |      | μs             |

| t <sub>REMOTE_RESET</sub>  | Delay From Local ON Low for Valid Remote Reset<br>Condition |                                                                 | •   | 180                |                   |      | ms             |

| f <sub>SCL:SLAVE</sub>     | Slave Device SCL Operating Frequency                        | (Note 3)                                                        | •   | 10                 | 1000              | 2000 | kHz            |

| t <sub>BUF:SLAVE</sub>     | Bus free Time between STOP and START                        | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 0.5<br>1.3<br>4.7  |                   |      | μs<br>μs<br>μs |

| t <sub>SU:STA:SLAVE</sub>  | Repeated Start Condition Setup Time                         | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | • • | 0.26<br>0.6<br>4.7 |                   |      | μs<br>μs<br>μs |

| t <sub>HD:STA:SLAVE</sub>  | Hold Time after START Condition                             | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 0.26<br>0.6<br>4   |                   |      | μs<br>μs<br>μs |

| tsu:sto:slave              | STOP Condition Setup Time                                   | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 0.26<br>0.6<br>4   |                   |      | μs<br>μs<br>μs |

| t <sub>SU:DAT:FSLAVE</sub> | Data Setup Time from LTC4331                                | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 50<br>100<br>250   |                   |      | ns<br>ns<br>ns |

| t <sub>SU:DAT:TSLAVE</sub> | Data Setup Time to LTC4331                                  |                                                                 | •   | 50                 |                   |      | ns             |

| t <sub>HD:DAT:TSLAVE</sub> | Data Hold Time to LTC4331                                   |                                                                 | •   | 0                  |                   |      | ns             |

| t <sub>HD:DAT:FSLAVE</sub> | Data Hold Time from LTC4331                                 |                                                                 | •   | 50                 |                   |      | ns             |

| t <sub>TIMEOUT:SLAVE</sub> | SCL Low Timeout Detection                                   |                                                                 | •   | 28                 | 31.5              | 35   | ms             |

| t <sub>LOW:SLAVE</sub>     | SCL Low Time                                                |                                                                 | •   | 0.25               |                   |      | μs             |

| t <sub>HIGH:SLAVE</sub>    | SCL High Time                                               |                                                                 | •   | 0.25               |                   | 50   | μs             |

| t <sub>HIGH:IDLE</sub>     | SCL High for Bus Idle Detection                             |                                                                 | •   | 70                 |                   |      | μs             |

| Remote Mode (F             | REMOTE = 1)                                                 |                                                                 |     |                    |                   |      |                |

| t <sub>SCL:MASTER</sub>    | Master Device SCL Operating Period                          | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 1<br>2.5<br>10     |                   |      | μs<br>μs<br>μs |

| t <sub>BUF:MASTER</sub>    | Bus Free Time between STOP and START                        | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | • • | 0.5<br>1.3<br>4.7  | 0.6<br>1.5<br>5   |      | μs<br>μs<br>μs |

| thd:sta:master             | Hold Time after START Condition                             | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 0.26<br>0.6<br>4   | 0.3<br>0.8<br>4.2 |      | μs<br>μs<br>μs |

| t <sub>SU:STA:MASTER</sub> | Repeated Start Condition Setup Time                         | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 0.26<br>0.6<br>4.7 | 0.3<br>0.8<br>4.8 |      | μs<br>μs<br>μs |

| t <sub>SU:STO:MASTER</sub> | Setup Time for STOP                                         | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm | •   | 0.26<br>0.6<br>4   | 0.3<br>0.8<br>4.2 |      | μs<br>μs<br>μs |

**SWITCHING CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $C_L = 20pF$ ,  $V_{CC} = 5V$ ,  $V_L = 3.3V$ , GND = 0V; unless otherwise noted. Conditions Fast-mode Plus, Fast-mode, and Standard-mode listed below as Fm+, Fm, and Sm respectively.

| SYMBOL                      | PARAMETER                                                      | CONDITIONS                                                                                                                   |   | MIN               | TYP            | MAX              | UNITS          |

|-----------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---|-------------------|----------------|------------------|----------------|

| t <sub>HD:DAT:FMASTER</sub> | Data Hold from LTC4331                                         |                                                                                                                              | • | 50                |                |                  | ns             |

| t <sub>HD:DAT:TMASTER</sub> | Data Hold to LTC4331                                           | (Note 2)                                                                                                                     | • | 0                 |                |                  | ns             |

| t <sub>SU:DAT:FMASTER</sub> | Data Setup from LTC4331                                        | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm                                                              | • | 50<br>100<br>250  |                |                  | ns<br>ns<br>ns |

| t <sub>SU:DAT:TMASTER</sub> | Data Setup to LTC4331                                          |                                                                                                                              | • | 50                |                |                  | ns             |

| t <sub>TIMEOUT:MASTER</sub> | SCL Low Timeout Detection                                      |                                                                                                                              | • | 28                | 31.5           | 35               | ms             |

| t <sub>LOW:MASTER</sub>     | SCL Low Time                                                   | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm                                                              | • | 0.6<br>1.5<br>5.8 |                |                  | μs<br>μs<br>μs |

| thigh:master                | SCL High Time                                                  | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm<br>SPEED1/SPEED2 = Sm                                                              | • | 0.4<br>1<br>3.8   |                |                  | μs<br>μs<br>μs |

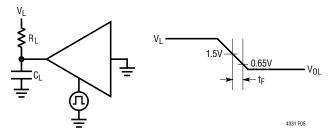

| t <sub>F</sub>              | Fall Time (SDA, SCL) (Note 5)                                  | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm, Sm<br>$C_L = 550$ pF, $R_L = 1$ k $\Omega$ (Figure 5) (Note 2)                    | • |                   |                | 120<br>300<br>25 | ns<br>ns<br>ns |

| t <sub>R</sub>              | Rise Time (SDA, SCL) (Note 5)                                  | SPEED1/SPEED2 = Fm+<br>SPEED1/SPEED2 = Fm, Sm                                                                                | • |                   |                | 120<br>300       | ns<br>ns       |

| t <sub>SPIKE</sub>          | Noise Spike Suppression Time (SDA, SCL)                        |                                                                                                                              | • | 0                 |                | 50               | ns             |

| Transceiver                 |                                                                |                                                                                                                              |   |                   |                |                  |                |

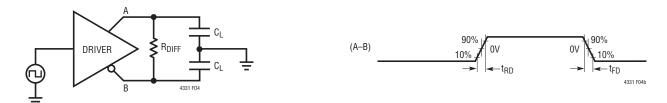

| $t_{RD,} t_{FD}$            | Driver Rise or Fall Time (Figure 4)                            | $R_{DIFF} = 54\Omega$ , $C_L = 100pF$ , $\overline{SLO} = 1$<br>$R_{DIFF} = 54\Omega$ , $C_L = 100pF$ , $\overline{SLO} = 0$ | • | 500               | 4<br>800       | 15<br>1200       | ns<br>ns       |

| t <sub>LINK_TIMEOUT</sub>   | Response Time for LINK = 1 after Disconnection                 | REMOTE = 1<br>REMOTE = 0 (Note 4)                                                                                            |   |                   | 168<br>96 • SF |                  | ms<br>µs       |

| System                      |                                                                |                                                                                                                              |   |                   |                |                  |                |

| t <sub>ALT_PROP</sub>       | ALERT Propagation Delay, Remote to Local                       | I <sup>2</sup> C Bus idle (Note 4)                                                                                           |   | 0.8 • SF          | 2 • SF         | 26 • SF          | μs             |

| t <sub>CTRL_PROP</sub>      | Local CTRL Propagation Delay to Remote CTRL                    | I <sup>2</sup> C Bus idle (Note 4)                                                                                           |   | 0.8 • SF          | 2 • SF         | 26 • SF          | μs             |

| t <sub>START_PROP</sub>     | I <sup>2</sup> C START Link Propagation Delay, Local to Remote | (Note 4)                                                                                                                     |   |                   | 2 • SF         |                  | μs             |

| t <sub>LDAT_PROP</sub>      | I <sup>2</sup> C DATA Link Propagation Delay, Local to Remote  | (Note 4)                                                                                                                     |   |                   | 2 • SF         |                  | μs             |

| t <sub>STOP_PROP</sub>      | I <sup>2</sup> C STOP Link Propagation Delay, Local to Remote  | (Note 4)                                                                                                                     |   |                   | 2 • SF         |                  | μs             |

| t <sub>RDAT_PROP</sub>      | I <sup>2</sup> C DATA Link Propagation Delay, Remote to Local  | (Note 4)                                                                                                                     |   |                   | 2 • SF         |                  | μs             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Guaranteed by design, not production tested.

**Note 3:** Local SCL frequencies between 1000kHz and 2000kHz are allowed, however the effective link throughput maximum is 1000kHz. SCL low clock-stretching by the LTC4331 must be respected.

Note 4: SF = Speed Factor. See Table 3.

**Note 5:** SCL and SDA rise and fall time measurement limits are defined as follows:

Rise Time Limit: 0.65V to 1.5V Fall Time Limit: 1.5V to 0.65V

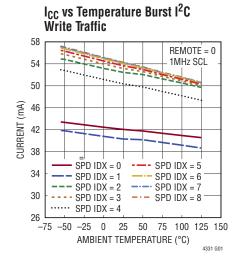

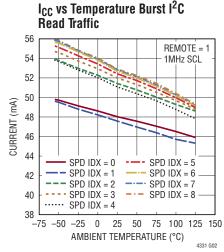

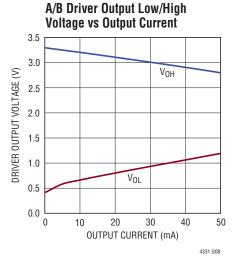

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{CC} = 5V$ , $V_L = 3.3V$ , GND = 0V, unless otherwise noted

## PIN FUNCTIONS

Logic (All Logic Side Inputs and Outputs Referenced to GND and  $V_L$  Except  $\overline{SLO}$ , which Is Referenced to GND and  $V_{CC}$ )

$V_{CC}$  (Pin 1): Supply Voltage.  $3V < V_{CC} < 5.5V$ . Bypass with 4.7µF ceramic capacitor to GND.

$V_L$  (Pin 2): Logic Supply Voltage. 1.62V <  $V_L$  < 5.5V. Bypass with 1 $\mu$ F ceramic capacitor to GND.

**ON (Pin 3):** Enable Input. Set high for operation. Set low for low power mode, in which the internal reset is held and outputs are disabled. Connect to  $V_{\rm I}$  if unused.

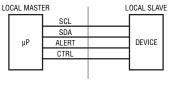

**REMOTE (Pin 4):** Operating Mode Select Input. Set low for local I<sup>2</sup>C slave mode. Set high for I<sup>2</sup>C master mode when used on the remote side. REMOTE is weakly pulled to GND.

**LINK** (**Pin 5**): Link Status Open-Drain Output. When in remote mode,  $\overline{LINK}$  is driven low when the device establishes link communication. When in local mode,  $\overline{LINK}$  is driven low after the LTC4331's I<sup>2</sup>C interface has joined the I<sup>2</sup>C bus in addition to establishing link communication. The link status function is only valid when an LTC4331 configured to local mode (REMOTE set low) connects to a second LTC4331 configured to remote mode (REMOTE set high). Connect to an external pull-up to V<sub>L</sub> to monitor status, otherwise float or connect to GND.

$\overline{RDY}$  (Pin 6): I<sup>2</sup>C Ready Status Open-Drain Output.  $\overline{RDY}$  is driven low after the device's I<sup>2</sup>C interface has joined the bus. Use to detect when the LTC4331's control interface is available in the absence of a connected link.  $\overline{RDY}$  has a weak internal pull-up to  $V_L$  and is only valid when in local mode. In remote mode the pin can be unconnected.

**SCL (Pin 7):** I<sup>2</sup>C Serial Clock. Low side output driver and input. Connect to an external pull-up.

**SDA (Pin 8):** I<sup>2</sup>C Serial Data. Low side output driver and input. Connect to an external pull-up.

**NC (Pins 9, 20):** Unconnected Pins. Float or connect to GND.

ALERT (Pin 10): SMBALERT/Interrupt. ALERT is an opendrain output in local mode and an input in remote mode. Values set on the remote side ALERT propagate to the local side ALERT pin. In addition, ALERT is the SMBALERT

function for the local side's  $I^2C$  control interface when enabled. The  $\overline{ALERT}$  pin switches to a level-sensitive active low interrupt signal when register field INTR\_MODE = 1. Connect to an external pull-up on the local side. Do not allow the  $\overline{ALERT}$  pin to float on the remote side.

**A1 (Pin 11):** I<sup>2</sup>C Device Address Select 1. A1 is a 3-state input. A1 in conjunction with A2 selects one of eight possible I<sup>2</sup>C addresses assigned to the internal slave device. Float pins A1 and A2 to disable the internal I<sup>2</sup>C device. Set to high, low, or float as defined in Table 4.

**A2 (Pin 12):** I<sup>2</sup>C Device Address Select 2. A2 is a 3-State input. A2 in conjunction with A1 selects one of eight possible I<sup>2</sup>C addresses assigned to the internal slave device. Float pins A1 and A2 to disable the internal I<sup>2</sup>C device. Set to high, low, or float as defined in Table 4.

**CTRL (Pin 13):** Local to Remote Control. Values set on the local side CTRL pin propagate to the remote side CTRL pin over the differential link. On the remote side, CTRL is not driven at startup until the differential link is established. CTRL has a weak pull-up to  $V_L$  and can be unconnected if not used.

**SPEED1 (Pin 14):** Link and Interface Timing Select 1. SPEED1 is a 3-state input and in conjunction with SPEED2 selects link baud rate and I<sup>2</sup>C bus timing. Set to high, low, or float as defined in Table 2.

**SPEED2** (**Pin 15**): Link and Interface Timing Select 2. SPEED2 is a 3-state input and in conjunction with SPEED1 selects link baud rate and I<sup>2</sup>C bus timing. Set to high, low, or float as defined in Table 2.

GND (Pin 16): Ground.

$\overline{\text{SLO}}$  (Pin 17): Link Slow Mode Input. Set low to limit the link transmitter slew rate which also limits the maximum link rate set by SPEED1 and SPEED2. Only valid for SPEED INDEX 0 and 1.  $\overline{\text{SLO}}$  is referenced to GND and  $V_{CC}$ . Do not allow pin  $\overline{\text{SLO}}$  to float.

#### Link

A (Pin 18): Noninverting Link Transceiver Pin.

**B** (Pin 19): Inverting Link Transceiver Pin.

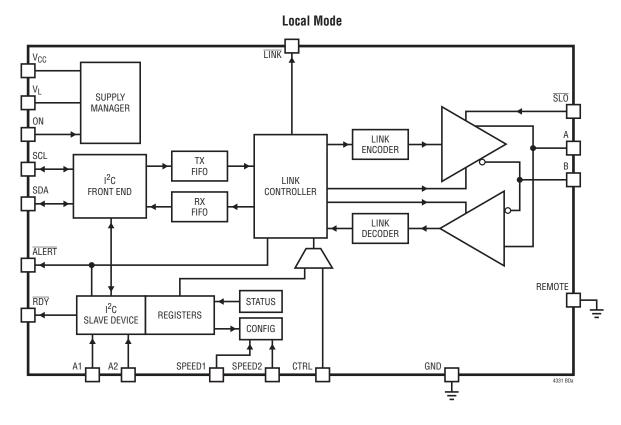

# **BLOCK DIAGRAM**

## **Remote Mode** LINK SL0 SUPPLY MANAGER ON LINK ENCODER SCL TX FIF0 I<sup>2</sup>C FRONT END LINK CONTROLLER SDA RX FIFO LINK DECODER ALERT REMOTE CONFIG $\overline{\text{RDY}}$ SPEED2 CTRL

## **TEST CIRCUITS**

Figure 1. Driver DC Characteristics

Figure 2. Driver Output Short-Circuit Current

Figure 3. Receiver Input Current and Input Resistance

Figure 4. Driver Timing Measurement

Figure 5. SCL and SDA Driver Timing Measurement

# TIMING DIAGRAMS

1.5 .0.2VL - tstop\_prop -1.5V tctrl\_prop  $-0.2 V_{\rm L} = 0.8 V_{\rm L}$ \_0.65V -0.65V trdat\_prop LOCAL\_CTRL REMOTE\_CTRL < — tLDAT\_PROP \_\_ 0.2VL 0.657 1.5V 0.65V<sub>L</sub>tALT\_PROP - tstart\_prop --0.8V<sub>L</sub> \_0.2VL 0.65V<sub>L</sub> LOCAL\_I2C SCL SDA SCL REMOTE\_I2C ===== REMOTE\_nALERT LOCAL\_nALERT

Figure 8. Propagation Timing

#### Overview

Two LTC4331 devices are required for a complete extended I<sup>2</sup>C network. Using the REMOTE pin, one LTC4331 is configured to local mode and acts as a full-featured SMBus compatible I<sup>2</sup>C slave device. Through this local interface a master can address a remote slave device up to 1200m away along a differential cable. On the remote network a second LTC4331 configured to remote mode acts as an I<sup>2</sup>C master device connected to the remote slave devices. The master interface mirrors the local I<sup>2</sup>C transactions on the remote network and transmits the remote slave responses back to the local network. In most cases the link is transparent; the remote slave devices appear as local devices to a local master.

A separate addressable slave device contained in the local side LTC4331 provides a control interface for optional configuration and event monitoring of the link.

BREAK CONNECTIONS AND INSERT LTC4331 SOLUTION

Figure 9. LTC4331 Solution Inserted Into an I<sup>2</sup>C Network.

#### **Local Mode**

On the local side, set the REMOTE pin low to put the LTC4331 in local mode. In this mode the LTC4331 operates as a slave device. The I<sup>2</sup>C interface is designed to be compatible with I<sup>2</sup>C Fast-mode Plus, Fast-mode, or Standard-mode class timing specifications selectable using pins SPEED1 and SPEED2.

When operating as a slave-receiver the LTC4331 captures I<sup>2</sup>C START, STOP, and data events sent by a local I<sup>2</sup>C master. The device transmits these events across the

differential link as an encoded bit-stream to a second LTC4331 which is set to remote mode. After an  $I^2C$  bus turnaround, the device operates as a slave-transmitter and the differential link direction is reversed. The remote LTC4331 transmits the response data measured from the remote  $I^2C$  bus onto the twisted pair cable. The local side LTC4331 then decodes the transmitted bit-stream into  $I^2C$  data events and drives them onto the local  $I^2C$  bus.

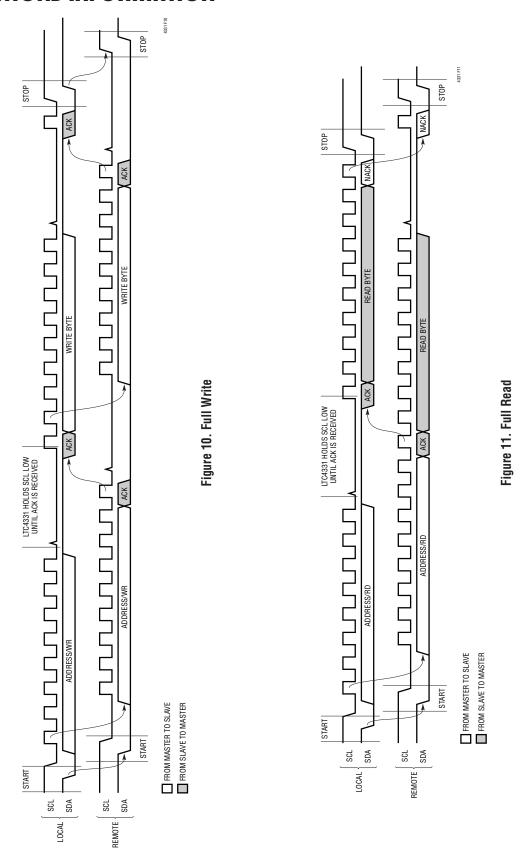

When operating as a slave-transmitter, the local LTC4331 must periodically stall the local I<sup>2</sup>C bus to account for remote I<sup>2</sup>C bus and link latencies. It does this by clock-stretching whenever a valid response is not yet available. Therefore it is recommended that the local I<sup>2</sup>C master device fully support SCL clock-stretching for each response (N)ACK and data bit. See section Considerations.

By using SCL clock-stretching to account for link and remote device latency, the local I<sup>2</sup>C clock rate is decoupled from the link baud rate and remote I<sup>2</sup>C clock rate. This allows independent I<sup>2</sup>C bus rates between the local and remote networks.

#### Remote Mode

On the remote side, set the REMOTE pin high to put the LTC4331 in remote mode. In this mode the LTC4331 operates as an I<sup>2</sup>C master device. In normal operation the remote master mirrors the I<sup>2</sup>C events produced by the local I<sup>2</sup>C master. The device recreates the events using Fast-mode Plus, Fast-mode, or Standard-mode class timing specifications. The timing class is selected by pins SPEED1 and SPEED2.

The LTC4331 does not support multiple masters on the remote  $I^2C$  networks. The LTC4331's  $I^2C$  master device interface is the only allowed master on the remote side network. Remote slaves are also forbidden to switch to master mode, for example as part of a host-notify operation.

The LTC4331 master interface fully supports slave device clock-stretching for all data bits in the packet.

#### I<sup>2</sup>C Transactions

A local master initiates a transaction by sending an I<sup>2</sup>C START along with the slave address byte. The LTC4331

device, configured for local mode, encodes and transmits the captured I<sup>2</sup>C events to the remote I<sup>2</sup>C network where they are recreated on the remote I<sup>2</sup>C bus. If additional LTC4331 devices configured as slaves, REMOTE set low, are connected to the remote I<sup>2</sup>C network, they also transmit the events to the 3rd tier I<sup>2</sup>C network, and so on. The local side LTC4331 always holds SCL low on the 9th bit waiting for an (N)ACK response from the remote slave device(s). When the local side LTC4331 receives the response, SCL is released with the response data set on the I<sup>2</sup>C bus. If the R/W bit is set to Write, the bus turns around after the ACK and the local LTC4331 switches back to slave-receive mode in order to capture the incoming write data. After the 8th SCL clock, the bus and link direction reverse in order to retrieve the (N)ACK response from the remote slave device. This sequence continues until the master sends a START or STOP condition. Data to be transferred across the link is stored in a buffer if the local I<sup>2</sup>C transaction is faster than the effective link rate. See Figure 10.

If a local LTC4331 detects that all remote slaves have NACK'd the slave address byte, it ceases transmitting further I<sup>2</sup>C data to the remote side until a STOP or REPEATED START condition is detected. This feature prevents the LTC4331 from stalling the bus unnecessarily when the transaction is addressed to a separate local slave device. Note that in this scenario, the remote side SCL is held low until a STOP or START condition is detected. Unusually long cycle times could activate the t<sub>TIMEOUT</sub> condition.

In the case of a read transaction to a remote slave device, the local LTC4331 slave device stalls the bus during the read data phase. During this time, the remote LTC4331 I<sup>2</sup>C master prefetches the next byte from the remote slave device. The read data byte is transmitted across the differential link and stored in a local buffer. As bits become available in the local buffer, the local LTC4331 drives them onto SDA and releases SCL according to the configured setup time t<sub>SU:DAT:SLAVE</sub>. After the complete byte has been read, the I<sup>2</sup>C bus and differential link are turned around. The local I<sup>2</sup>C master either ACKs or NACKs during this time. If the master ACKs, the sequence is repeated. This bus and link direction is reversed, and the next byte is prefetched from the remote slave device. If the master then NACKs, the bus and link do not reverse direction.

The master is then expected to send a STOP or START event. See Figure 11.

#### **Differential Link**

Internally, the LTC4331 utilizes a high performance RS485 compliant transceiver to communicate over the link. The A and B pins are fault protected to ±60V. In addition, the transceiver operates over an extended common mode range of ±15V making it suitable for noisy environments or systems with ground potential differences. Data is exchanged between the LTC4331 devices using a custom packet which has a selectable baud rate based on the configuration of the SPEED1 and SPEED2 pins. Selectable baud rates over the cable allow balancing performance with cable length specific to the application. Both sides of the link must be set to the same speed configuration in order to match the baud rates and allow communication.

The LTC4331 allows slew rate limiting over the differential link outputs to reduce EMI in sensitive applications. Setting the  $\overline{SLO}$  pin low activates the slew rate limiting circuit. Once in slew limiting mode, SPEED1 and SPEED2 pins must only be configured for Speed Index 0 or 1. Setting SPEED1/2 to a speed index of 2 or higher when  $\overline{SLO}$  is low results in link data corruption regardless of cable length.

The LTC4331 I<sup>2</sup>C slave device extension solution is point-to-point only. Multidrop or multipoint configurations on the differential link are not allowed.

#### ±40kV ESD Protection

The LTC4331 features exceptionally robust ESD protection. The link interface pins (A, B) feature protection to  $\pm 40 \text{kV}$  HBM with respect to GND,  $V_{CC}$  (with a  $4.7 \mu F$  capacitor to GND), A or B without latchup or damage, during all modes of operation or while unpowered.

#### **Level 4 IEC ESD and EFT Protection**

The improved ESD protection of the LTC4331 provides a high level of protection in the IEC ESD and EFT (Electrical Fast Transient) tests. The IEC ESD stress exceeds that of the HBM test in peak current, amplitude, and rise time, while the EFT test provides a prolonged repetitive stress. Combined with the HBM test, the IEC tests help ensure that the LTC4331 is robust under a wide range of real

world hazards. The LTC4331 passes the following tests on the A, B pins:

- IEC 61000-4-2 Edition 2.0 2008-12 ESD Level 4: ±8kV contact (A or B to GND, direct discharge to bus pins with transceiver and protection circuit mounted on a test card with a low impedance ground discharge path from board GND to ESD gun return lead, per Figure 4 of the standard)

- IEC 61000-4-4 Second Edition 2004-07 EFT Level 4: ±5kV (A or B to GND, 5kHz repetition rate, 15ms burst duration, 60 second test duration, discharge coupled to bus pins through 100pF capacitor per paragraph 7.3.2 of the standard). V<sub>CC</sub> pin requires a low inductance capacitor of at least 4.7μF to meet Level 4 rating.

#### Startup and Shutdown

Startup occurs when supply voltages are applied to pins  $V_{CC}$  and  $V_L$  and the ON pin is high. All output pins are tristated during the first part of startup. After an initialization sequence, the  $I^2C$  interface and other pins are functional. The local side LTC4331 monitors the  $I^2C$  bus for inactivity and probes the differential link. When the device detects an idle condition on the local  $I^2C$  bus, it drives pin  $\overline{RDY}$  low to indicate that it is ready to respond to  $I^2C$  transactions. Thereafter a master can access the internal control interface. In addition, once the device establishes link communication with a remote LTC4331, it drives pin  $\overline{LINK}$  low and the remote  $I^2C$  network can be accessed.

The ON pin can be used to set the LTC4331 to a lower power state. By setting ON low, the LTC4331 is held in reset, all programmed configuration is set to the default value, all output drivers are disabled, and the differential transceiver is put into low power mode. If not used, tie ON to  $V_{\rm L}$ .

#### **Link Status**

The LTC4331 provides the  $\overline{LINK}$  pin which indicates if the remote I<sup>2</sup>C network has joined with the local I<sup>2</sup>C network.  $\overline{LINK}$  is driven low when bidirectional link communication is established and the I<sup>2</sup>C interface is ready. It is an open-drain output and requires an external pull-up to V<sub>L</sub> if used. At startup, the  $\overline{LINK}$  pin output driver is disabled.

Link status can also be monitored using the control interface. See section Control Interface.

Ensure that the values set on local side SPEED1 and SPEED2 pins match the values set on remote side. Also, do not exceed the cable length listed in Table 2 for the given SPEED setting. The LTC4331 will not link if these conditions are not met.

Note that the link status is indeterminate if the REMOTE pin is incorrectly configured on either the local or remote side LTC4331 device.

#### **Ready Status**

The  $\overline{RDY}$  pin is driven low when the local side LTC4331 control interface is ready for access. It is an open-drain output and only valid in local mode. When the device is first powered and pin ON is set high, the low output driver on  $\overline{RDY}$  is disabled and the pin is weakly pulled to  $V_L$ . An internal  $I^2C$  bus idle detection circuit prevents the interface from interrupting an active transaction. This circuit drives  $\overline{RDY}$  low when either pin SCL is high for  $t_{READY:IDLE}$  or it detects an  $I^2C$  STOP which indicates the interface is ready and has joined the bus. The status of the link connection does not affect the ready function. If pin  $\overline{LINK}$  is high when  $\overline{RDY}$  is low, only the local side LTC4331 control interface is available for access. The  $\overline{RDY}$  pin is internally pulled to  $V_L$ . It is valid only in local mode.

A secondary function of  $\overline{RDY}$  indicates if the internal buffer has filled, see section Considerations for more detail.

#### Interrupt/SMBALERT

The LTC4331 supports an interrupt signal that is mirrored from the remote network to the local network using the differential link. On the remote side  $\overline{ALERT}$  is an input pin that can be connected to remote I<sup>2</sup>C slave devices. While on the local side  $\overline{ALERT}$  operates as an open-drain type output that can be connected to a shared local interrupt line.  $\overline{ALERT}$  is periodically sampled and has a propagation time of  $t_{ALT}$  PROP.

If enabled, the local LTC4331's control interface uses the ALERT pin to report link and fault events. The local side ALERT output is the logical AND of the remote ALERT and the internal endpoint interrupt signal.

By default the local addressable slave device in the LTC4331 recognizes the Alert Response Address (ARA) and participates in the Alert Response protocol. If an EVENT is triggered and its corresponding ALERT EN bit is set high, ALERT is driven low. If the master transmits the Alert Response protocol and the LTC4331's internal slave address is the lowest numerically, then the LTC4331 releases its local alert output. Note that local ALERT could continue to be low due to a low value from a remote ALERT pin. The remote ALERT function in the LTC4331 is not directly affected by an Alert Response transaction. The signal on the remote ALERT pin is always propagated to the local side if connected. If using SMBus slave devices on both sides of the link that respond to the ARA, the remote slaves must have higher priority device addresses than the devices on the local side, see section Considerations.

The LTC4331's internal slave device can be programmed to ignore the ARA and switch the function of pin ALERT from SMBALERT to interrupt mode. To switch to interrupt mode set INTR\_MODE in the CONFIG register to 1. To clear the interrupt set the triggered event or the corresponding event enable bit to 0. This method is also valid in SMBALERT mode in lieu of the ARA protocol.

#### Control

Through the CTRL pin, the LTC4331 provides an additional signal to control a remote device's input pin. When in remote mode, the CTRL pin is an output and reflects the value either on the local side CTRL pin or the value

programmed into the bit field SW\_CTRL. A separate bit field CTRL\_SEL selects pin or register control. By default the value on local CTRL pin is used. Local CTRL values transfer to the remote side CTRL only when the communication link is established and pin  $\overline{\text{LINK}}$  is low.

At startup the CTRL output driver is disabled and a weak internal pull-up prevents the pin from floating. The CTRL pin's output driver enables only when link communication is established. Thereafter, the remote CTRL pin's output driver is always enabled except after a remote reset event where it is disabled until link communication is reestablished.

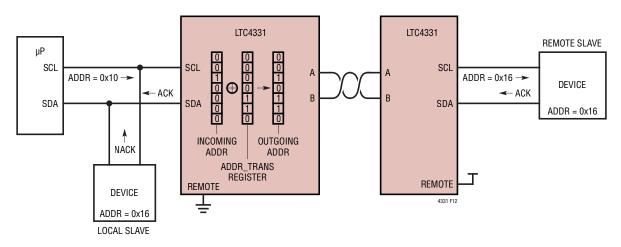

### I<sup>2</sup>C Address Translation

The address translation feature allows the use of multiple I<sup>2</sup>C slave devices with fixed or limited device address ranges on the same network. The LTC4331 I<sup>2</sup>C slave device automatically translates the incoming address using an XOR function against the internal register ADDR\_TRANS. Address translation is enabled by setting this register to a non-zero value. ADDR\_TRANS must be programmed before any accesses to the remote slave if that slave requires address translation or there will be a collision. See Figure 12.

#### **Timeouts**

The LTC4331 respects SMBus SMBCLK low timeouts on the SCL pin. When in local mode and SCL is held low for a minimum of t<sub>TIMEOUT:SLAVE:MAX</sub>, the I<sup>2</sup>C Interface is reset and SCL and SDA are released if held low. On the remote

Figure 12. Address 0x10 Is Translated to 0x16 for the Remote Device

side, the LTC4331 acting as an I<sup>2</sup>C master also releases SCL and SDA if an remote slave is signaling a timeout. In addition, the LTC4331 master sends a STOP event and requires a local side STOP event before allowing further remote I<sup>2</sup>C transactions. This ensures the local and remote are synchronized.

In addition, the local side LTC4331 slave interface contains an SDA stuck-low prevention circuit which ensures the LTC4331 does not hold SDA low when the  $I^2C$  bus is idle. This typically occurs when there is a loss of  $I^2C$  protocol synchronization between the master and slave devices. If the LTC4331 is holding SDA low while SCL is high for 35ms, the interface is reset and SDA is released.

#### Remote Stuck Bus Protection

On the remote side, the LTC4331 master device can detect and attempt recovery from I<sup>2</sup>C bus faults. If the master device senses that SDA is low when it should be high, it considers SDA stuck by a slave device. The LTC4331 enters a bus recovery routine which drives 16 SCL clocks onto the bus and then issues a STOP event. This routine is also entered if SDA is sensed low after a startup. If successful, the LTC4331 master then ignores further local I<sup>2</sup>C bus transactions until the local bus transmits a STOP condition. If the routine is unsuccessful, it retries whenever a local side master initiates a new transaction.

If the remote LTC4331 detects that SCL is stuck, it automatically NACKs all I<sup>2</sup>C transactions from the local bus until it measures SCL high and receives a STOP command from a local I<sup>2</sup>C master.

For both SCL and SDA fault conditions, the remote LTC4331 sends a FAULT response to the local LTC4331 which sets the EXT I2C FAULT EVENT bit.

#### Remote Reset

The local side LTC4331 can trigger a remote side LTC4331 reset by holding the ON pin low for a minimum of  $t_{REMOTE\_RESET}$ . In addition, the remote LTC4331 is automatically reset after  $t_{REMOTE\_RESET}$  if the link is disconnected. A remote reset disables all remote side outputs, including pin CTRL, until link communication is reestablished.

#### **Considerations**

• The LTC4331 relies on SCL clock-stretching to account for link and remote bus latencies. Using a local master, either hardware or software based, that fully supports clock-stretching is highly recommended for best performance. Alternately, the SCL frequency can also be reduced such that the LTC4331's SCL configured low time and remote response time is less than the master's programmed SCL low time. The total clock-stretching time of the local LTC4331 I<sup>2</sup>C slave device depends on SPEED1 and SPEED2 pin settings and remote I<sup>2</sup>C Slave device timing requirements. This is not recommended. See Figure 13.

Table 1. Known I<sup>2</sup>C Master Devices Incompatible with LTC4331 SCL Clock-Stretching

| DEVICE                                           | ISSUE                                                               | WORKAROUND                                                                   |

|--------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------|

| All Raspberry Pi<br>models (Broadcom<br>BCM283X) | Hardware I <sup>2</sup> C<br>peripheral clock-<br>stretching issues | Use software based I <sup>2</sup> C that fully supports SCL clock-stretching |

| Analog Devices<br>DC590B QuikEval<br>controller  | SCL signal path is not bidirectional                                | Use Analog Devices<br>Linduino® w/DC590<br>sketch                            |

- The LTC4331 I<sup>2</sup>C Slave Extender does not support remote I<sup>2</sup>C devices acting as masters. Therefore the SMBus Address Resolution Protocol and Host Notify Protocol are not supported.

- When using SMBus ARA, if there are SMBus slave devices on the local and remote side of the extender,

Figure 13. SCL Frequency Range when the I<sup>2</sup>C Master Ignores Slave SCL Low Stretching

all local slave device addresses must be greater (lower priority) than the remote slave device address. This is to allow proper slave address negotiation.

- Care must be taken when interrupting an I<sup>2</sup>C transaction with a START or STOP. A START or STOP can only be issued when the local side LTC4331 is in slave-receive mode. Since internally the data is sampled on the rising edge, the local I<sup>2</sup>C bus is considered slave driven after the last rising edge of SCL in a master driven data cycle.

- The LTC4331 supports a faster local I<sup>2</sup>C clock rate relative to the effective link rate. The device has a fixed length internal buffer to hold a complete byte as it is transferred across the link at the rate set by SPEED1 and SPEED2. During this time the local I<sup>2</sup>C bus stalls preventing further I<sup>2</sup>C data from entering the buffer. If however, a local master sends multiple consecutive START/STOP commands faster than the effective link rate, this buffer can overflow. The LTC4331 provides two status indicators for this event. First, if the buffer is full, then RDY rises indicating that the local I<sup>2</sup>C interface is not ready and further START, STOP, or write data event can be lost. Second, a TX\_BUFFER\_OVERFLOW FAULT event occurs if a local master writes additional I<sup>2</sup>C events while RDY is high.

- A remote slave device will not see a SCL timeout condition (bus reset) initiated by a local slave device if a remote device is not the target of the local Master.

New I<sup>2</sup>C transactions should not start in the time window of 28ms to 35ms following the end of the last transaction. New transactions starting in this window may fail with a local side NAK. In many cases, the extender link self recovers, and subsequent transactions occurs normally after waiting a short time, 28ms to 35ms. In some situations, the link cannot recover without a reset. See Remote Reset.

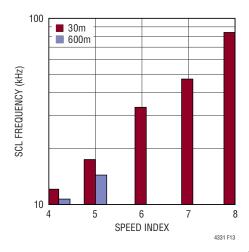

#### **Link Speed**

The link baud rate is set using the SPEED1 and SPEED2 pins as shown in Table 2. Column I<sup>2</sup>C Class shows the timing mode set on the local and remote I<sup>2</sup>C interfaces. The Effective I<sup>2</sup>C Link Rate shows the rate I<sup>2</sup>C data propagates across the link. The local SCL frequency can exceed this rate though increased clock-stretching times occur as the Effective Link Rate decreases relative to the local SCL frequency. The SPEED INDEX must be set to the same value on each side of the link.

**Table 3. Speed Factors**

| SPEED INDEX | SPEED FACTOR (SF) |

|-------------|-------------------|

| 8           | 1×                |

| 7           | 2×                |

| 6           | 4×                |

| 5           | 8×                |

| 4           | 10×               |

| 3           | 16×               |

| 2           | 32×               |

| 1           | 50×               |

| 0           | 80×               |

Table 2. Link Speed

| SPEED1<br>(Note 1) | SPEED2<br>(Note 1) | SPEED INDEX | I <sup>2</sup> C CLASS | EFFECTIVE I <sup>2</sup> C<br>Link rate | MAX CABLE<br>LENGTH (m) (Note 2) | SLEW RATE LIMITING OPTION (Note 3) |

|--------------------|--------------------|-------------|------------------------|-----------------------------------------|----------------------------------|------------------------------------|

| L                  | L                  | 8           | Fm+                    | 1MHz                                    | 30                               | No                                 |

| Float              | L                  | 7           | Fm                     | 500kHz                                  | 60                               | No                                 |

| Н                  | L                  | 6           | Fm                     | 250kHz                                  | 200                              | No                                 |

| L                  | Float              | 5           | Fm                     | 125kHz                                  | 600                              | No                                 |

| L                  | Н                  | 4           | Sm                     | 100kHz                                  | 1200                             | No                                 |

| Н                  | Float              | 3           | Sm                     | 63kHz                                   | 1200+                            | No                                 |

| Float              | Float              | 2           | Sm                     | 31kHz                                   | 1200+                            | No                                 |

| Float              | Н                  | 1           | Sm                     | 20kHz                                   | 1200+                            | Yes                                |

| Н                  | Н                  | 0           | Sm                     | 12.5kHz                                 | 1200+                            | Yes                                |

Note 1: For assignments to float, 0.5 • V<sub>L</sub> can also be applied to pin.

Note 2: Evaluated with Cat5E Ethernet cable in a lab environment. Actual maximum cable length depends on type of cable and application environment.

Note 3: Using SLO.

Propagation times across the link for the SYSTEM timing specifications are based on the SPEED1 and SPEED2 pins.

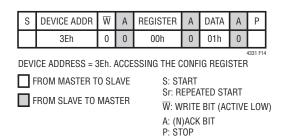

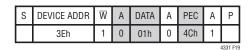

#### **Control Interface**

The LTC4331 contains an addressable slave device providing a control interface for configuration and monitoring.

The internal slave is enabled by configuring pins A1 and A2 to assign the device a unique I<sup>2</sup>C address. When both pins are unconnected, the internal slave is disabled. The internal slave device recognizes the SMBus Write Byte and

Figure 14. Write Byte

| 3Eh 0 0 00h 0 01h 0 9Ah 0 | S                         | S         DEVICE ADDR         W         A         REGISTER         A         DATA         A         PEC           3Fh         0         0         00h         0         01h         0         9Ab |  |  |  |  |  |  |   | А | Р |

|---------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|---|---|---|

|                           | 3Eh 0 0 00h 0 01h 0 9Ah 0 |                                                                                                                                                                                                   |  |  |  |  |  |  | 0 |   |   |

Figure 15. Write Byte + PEC

| S | DEVICE ADDR | W | А | REGISTER | Α | Sr | DEVICE ADDR | W | А | DATA | Α | Р |

|---|-------------|---|---|----------|---|----|-------------|---|---|------|---|---|

|   | 3Eh         | 0 | 0 | 00h      | 0 |    | 3Eh         | 1 | 0 | 01h  | 1 |   |

Figure 16. Read Byte

| S | DEVICE ADDR | W | А | REGISTER | А | Sr | DEVICE ADDR | W | А | DATA | Α | PEC | Α | Р |

|---|-------------|---|---|----------|---|----|-------------|---|---|------|---|-----|---|---|

|   | 3Eh         | 0 | 0 | 00h      | 0 |    | 3Eh         | 1 | 0 | 01h  | 0 | 96h | 1 |   |

Figure 17. Read Byte + PEC

| S | DEVICE ADDR | W | А | DATA | Α | Р        |

|---|-------------|---|---|------|---|----------|

|   | 3Eh         | 1 | 0 | 01h  | 1 |          |

|   |             |   |   |      |   | 4331 F19 |

Figure 18. Receive Byte

Figure 19. Receive Byte + PEC

Read/Receive Byte protocols with or without Packet Error Correction (PEC) as shown in Figures 14 to 19.

The PEC byte is calculated as a CRC-8 checksum over all bytes between the START and STOP conditions excluding the ACK/NACK and Sr bits and last CRC byte. The polynomial used is  $x^8 + x^2 + x + 1$  initialized to zero.

PEC transfers are recommended in high noise environments or high reliability systems.

**Table 4. Device Address**

| A1 (Note 1) | A2 (Note 1) | DEVICE ADDR (7-Bit) |

|-------------|-------------|---------------------|

| L           | L           | 3Eh                 |

| Float       | L           | 3Ch                 |

| Н           | L           | 3Fh                 |

| L     | Float | 3Dh                               |

|-------|-------|-----------------------------------|

| Н     | Float | 75h                               |

| L     | Н     | 76h                               |

| Float | Н     | 74h                               |

| Н     | Н     | 77h                               |

| Float | Float | Internal Slave Device is Disabled |

Note 1: For assignments to Float,  $0.5 \cdot V_L$  can also be applied to pin.

## **Register Naming Conventions**

RW Read-Write

RO Read Only

WOC Write Zero to Clear

#### Table 5. Register Map

| REGISTER | NAME       |       |         |           |       | DATA            |               |              |                 | DEFAULT |

|----------|------------|-------|---------|-----------|-------|-----------------|---------------|--------------|-----------------|---------|

|          |            | Bit 7 | Bit 6   | Bit 5     | Bit 4 | Bit 3           | Bit 2         | Bit 1        | Bit 0           |         |

| 00h      | CONFIG     | -     | _       | _         | _     | _               | -             | CTRL_SEL     | INTR_MODE       | 0x00    |

| 01h      | STATUS     |       | SPEE    | D_IDX     |       | Reserved        | EXT_NALERT    | NALERT       | NLINK           | -       |

| 02h      | EVENT      | -     | _       | _         | _     | _               | FAULT         | LINK_LOST    | LINK_GOOD       | 0x00    |

| 03h      | ALERT_EN   | _     | _       | _         | _     | _               | FAULT_EN      | LINK_LOST_EN | LINK_GOOD_EN    | 0x00    |

| 04h      | FAULT      | -     | _       | _         | _     | TX_BUF_OVERFLOW | EXT_I2C_FAULT | LINK_FAULT   | I2C_WRITE_FAULT | 0x00    |

| 05h      | SCRATCH    |       | SCRATCH |           |       |                 |               |              | 0x08            |         |

| 06h      | ADDR_TRANS | -     |         | I2C_TRANS |       |                 |               |              |                 | 0x00    |

| 07h      | CTRL       | -     | _       | _         | _     | _               | _             | _            | SW_CTRL         | 0x00    |

### **CONFIG Register (RW)**

| FIELD     | DESCRIPTION                                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTR_MODE | When low, the internal slave interrupt behavior on pin ALERT is SMBALERT. The internal slave device recognizes and responses to an ARA. When high, the internal slave device ignores the ARA. |

| CTRL_SEL  | When low, the local CTRL pin input is mirrored to the remote CTRL output pin. When high, the value in register CTRL is used instead.                                                          |

## STATUS (RO)

| FIELD      | DESCRIPTION                                                                         |

|------------|-------------------------------------------------------------------------------------|

| NLINK      | The level driven by pin LINK. High impedance is interpreted as 1.                   |

| NALERT     | The level driven by the local side pin ALERT. High impedance is interpreted as 1.   |

| EXT_NALERT | The level driven into the remote ALERT pin. Link must be established.               |

| SPEED_IDX  | <0-8>. Encoded index from values set on SPEED1 and SPEED2. See Table 2. Link Speed. |

#### **EVENT (WOC): Events Are Set by the System and Cleared by the User**

| FIELD     | DESCRIPTION                                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| LINK_GOOD | The local and remote I <sup>2</sup> C networks are connected.                                                         |

| LINK_LOST | The local and remote I <sup>2</sup> C networks have lost link communication.                                          |

| FAULT     | Set if any field in the FAULT register is set by the system. Clearing this bit clears all bits in the FAULT register. |

## ALERT\_EN (RW): Asserts ALERT if Corresponding EVENT Bit Is Set

# FAULT (RO): If the FAULT EVENT Bit Is Set, at Least One of the Following Bits Is Set. To Clear, Clear the FAULT Event Bit

| FIELD           | DESCRIPTION                                                                            |

|-----------------|----------------------------------------------------------------------------------------|

| I2C_WRITE_FAULT | An incomplete write transaction after the internal address byte or PEC error detected. |

| LINK_FAULT      | Link communication corruption detected.                                                |

| EXT_I2C_FAULT   | A fault, or stuck bus recovery occurred on the remote I <sup>2</sup> C bus.            |

| TX_BUF_OVERFLOW | The transmit buffer overflowed, I <sup>2</sup> C events lost.                          |

#### SCRATCH (RW)

| FIELD   | DESCRIPTION                                              |

|---------|----------------------------------------------------------|

| SCRATCH | Used to test read/write access to the control interface. |

## ADDR\_TRANS (RW)

| FIELD     | DESCRIPTION                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| I2C_TRANS | Incoming 7-bit $I^2C$ addresses are translated to the remote network by: Address <sub>OUT</sub> = $I2C_TRANS$ XOR Address <sub>IN</sub> |

### CTRL (RW)

| FIELD   | DESCRIPTION                                                         |

|---------|---------------------------------------------------------------------|

| SW_CTRL | Sets the output value of the remote CTRL pin when CTRL_SEL is high. |

### **PCB** Layout

A ground plane layout is recommended. A  $4.7\mu F$  bypass capacitor should be placed no more than 7mm away from the  $V_{CC}$  pin. The PC board traces connected to signals A and B should be symmetrical and as short as possible to maintain good differential signal integrity. Route the differential signals A and B as an edge coupled microstrip with a differential impedance approximately matching the cable impedance.

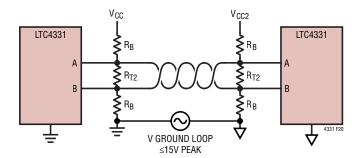

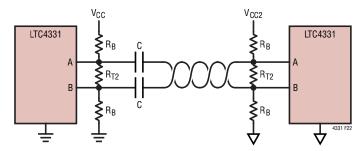

#### **Link Termination and Biasing**

To minimize the transmission line reflections over the link, a termination resistor should be connected between pins A and B at each node. Each resistor's value should

closely match the characteristic impedance of the differential cable to reduce reflections.

A bias resistor network should also be inserted at each node to maintain the idle state during link turnaround when all drivers are momentarily disabled. See Figure 20. For DC-coupled (non-isolated) link applications, select  $R_B$  and  $R_{T2}$  such that  $200\Omega \leq R_B \leq 620\Omega$  and  $100\Omega \leq R_{T2} \leq 110\Omega$ .

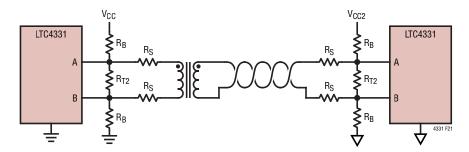

#### Isolation

Galvanically isolating the link is supported with the LTC4331 allowing applications with safety requirements or applications with independent ground potentials. A bias network along with termination resistors must be used

Rev

on both sides of the link. For transformer applications, series resistors must be added to the A and B pins on each side of the link. Use resistor values from  $25\Omega$  to  $50\Omega$ . See Figure 21.

Table 6. Typical Resistor Values for Transformer Applications

| V <sub>CC</sub> (V) | R <sub>B</sub> (Ω) | R <sub>S</sub> (Ω) | R <sub>T2</sub> (Ω) |

|---------------------|--------------------|--------------------|---------------------|

| 3.3                 | 200                | 25                 | 110                 |

| 5.0                 | 270                | 50                 | 110                 |

For capacitive isolation, select  $R_B$  such that  $200\Omega \leq R_B \leq 320\Omega.$  C =  $1\mu F$  rated capacitors support all SPEED INDEX values. Smaller value capacitors can be used if the application only utilizes higher SPEED INDEX values. Ensure the capacitors' working voltages are much higher than the expected ground offset voltage. See Figure 25.

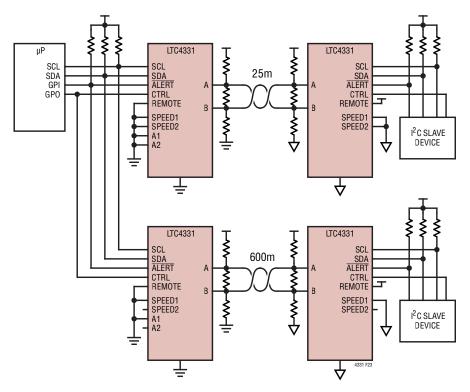

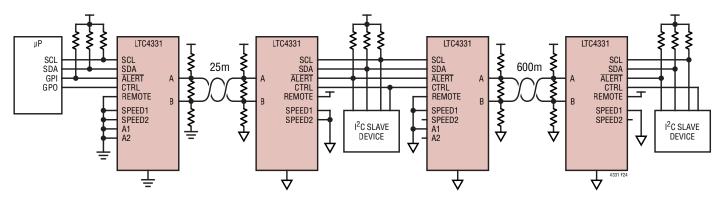

#### **Multiple Local Extender Network**

Multiple LTC4331 devices operating in slave device mode can be connected to the same local SMBus network unlike other extension solutions which typically restrict usage to one extender device. This allows a star network of parallel LTC4331 devices extending separate remote SMBus networks.

LINK indicates when the remote system is ready. Optionally RDY can also be monitored to determine when the local side control interface is ready to access in the absence of a link. See Figure 23.

#### **Multi-Tier Extender Network**

The LTC4331 also supports chaining remote segments into a single multi-tiered network. The maximum depth of the I<sup>2</sup>C link network is limited only by the t<sub>TIMEOUT</sub> parameters of the I<sup>2</sup>C devices on the network. As the depth increases, the clock-stretched low time of the devices increases. No other I<sup>2</sup>C timing parameter is affected by depth. See Figure 24.

Auxiliary Protection for 5kV Surge, 5kV EFT, and 30kV IEC ESD

An interface transceiver used in an industrial setting may be exposed to extremely high levels of electrical overstress due to phenomena such as lightning surge, electrical fast transient (EFT) from switching high current inductive loads, and electrostatic discharge (ESD) from the discharge of electrically charged personnel or equipment. The LTC4331 is designed for high robustness against ESD, but the on-chip protection is not able to absorb the energy associated with the 61000-4-5 surge transients. Therefore, a properly designed external protection network is necessary to achieve a high level of surge protection, and can also extend the ESD and EFT performance of the LTC4331 to extremely high levels.

Refer to section Auxiliary Protection for IEC Surge, EFT and ESD on page 17 of Analog Devices LTC2862A Datasheet for a detailed description and diagram of the external protection network.

The network provides the following protection:

- EC 61000-4-2 ESD Level 4: ±30kV contact, ±30kV air (line to GND, direct discharge to bus pins with transceiver and protection circuit mounted on a ground referenced test card per Figure 4 of the standard)

- IEC 61000-4-4 EFT Level 4: ±5kV (line to GND, 5kHz repetition rate, 15ms burst duration, 60 second test duration, discharge coupled to bus pins through 100pF capacitor per paragraph 7.3.2 of the standard)

- IEC 61000-4-5 Surge Level 4:  $\pm 5$ kV (line to GND, line to line,  $8/20\mu s$  waveform, each line coupled to generator through  $80\Omega$  resistor per Figure 14 of the standard)

**Table 7. Recommended Transformers**

| MANUFACTURER | PART NUMBER | ISOLATION VOLTAGE    | CENTER TAP | CM CHOKE | SPEED INDEX SUPPORTED |

|--------------|-------------|----------------------|------------|----------|-----------------------|

| Murata       | 78601/9JC   | 1kV <sub>RMS</sub>   | No         | No       | ALL                   |

| Pulse        | PE-68386NL  | 1500V <sub>RMS</sub> | No         | No       | 3, 4, 5, 6, 7, 8      |

Figure 20. Resistor Bias Network

Figure 21. Transformer Application Resistor Network

Figure 22. Capacitive Isolation Resistor Network

## TYPICAL APPLICATIONS

Figure 23. Multiple Local Extender Network

Figure 24. Multi-Tier Extender Network

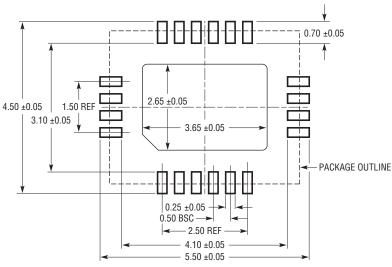

## PACKAGE DESCRIPTION

#### **UFD Package** 20-Lead Plastic QFN (4mm × 5mm)

(Reference LTC DWG # 05-08-1711 Rev B)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

#### NOTE:

- 1. DRAWING PROPOSED TO BE MADE A JEDEC PACKAGE OUTLINE MO-220 VARIATION (WXXX-X). 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# **REVISION HISTORY**

| REV | DATE | DESCRIPTION            | PAGE NUMBER |

|-----|------|------------------------|-------------|

| Α   | 2/23 | Updated Considerations | 18          |

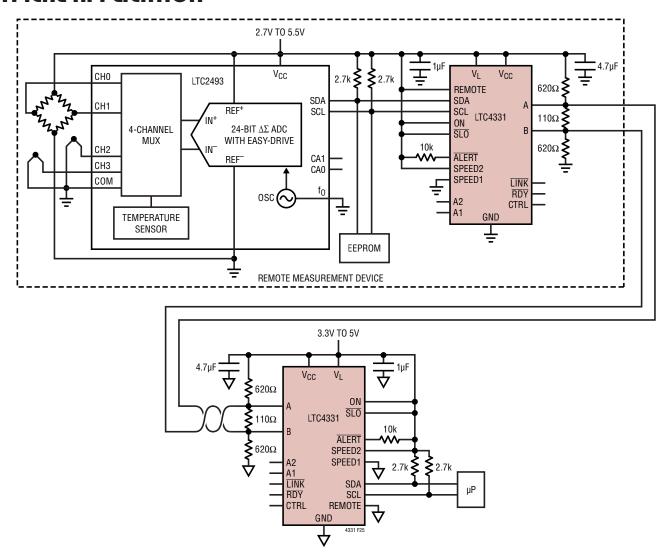

## TYPICAL APPLICATION

Figure 25. Extending an LTC2439 4-Channel ADC for Remote Measuring

# **RELATED PARTS**

| PART NUMBER                 | DESCRIPTION                                                                                    | COMMENTS                                                                                                                                                                  |

|-----------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC4316/LTC4317/<br>LTC4318 | Single I <sup>2</sup> C/SMBus Address Translator                                               | Resistor Configurable, 2.5V, 3.3V, and 5V Busses                                                                                                                          |

| LTC4312/LTC4314             | Pin-Selectable, 2-Channel, 2-Wire Multiplexer with Bus<br>Buffers                              | Two or Four Pin Selectable Downstream Busses, V <sub>IL</sub> Up to 0.3V • V <sub>CC</sub> , Rise Time Accelerators, 45ms Stuck Bus Disconnect and Recovery, ±4kV HBM ESD |

| LTC4305/LTC4306             | 2-Channel, 2-Wire Bus Multiplexer with Capacitance<br>Buffering                                | Two or Four Software Selectable Downstream Busses, Stuck Bus<br>Disconnect, Rise Time Accelerators, Fault Reporting, ±10kV HBM ESD                                        |

| LTC4310                     | Hot-Swappable I <sup>2</sup> C Isolators                                                       | Bidirectional I <sup>2</sup> C Communication between Two Isolated Busses                                                                                                  |

| LTM2892                     | SPI/Digital or I <sup>2</sup> C µModule Isolator                                               | 3500V <sub>RMS</sub> Isolation, 6 Channels                                                                                                                                |

| LTM2883/LTM2886/<br>LTM2887 | SPI/Digital or $I^2C$ $\mu$ Module Isolator with Adjustable $\pm 12.5V$ and 5V Regulated Power | 2500V <sub>RMS</sub> Isolation with Power in BGA Package                                                                                                                  |

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Analog Devices Inc.:

LTC4331CUFD#PBF LTC4331CUFD#TRPBF LTC4331HUFD#PBF LTC4331HUFD#TRPBF LTC4331IUFD#TRPBF DC2754A