# Dual Downconverter with DVGA and PLL/VCO, 450 MHz to 2700 MHz

**Data Sheet**

# **ADRF6650**

#### **FEATURES**

Dual down-converter with integrated fractional-N PLL/VCO RF: 450 MHz to 2700 MHz continuous LO frequency: 450 MHz to 2900 MHz, high-side or low-side injection 43 dB gain control range Gain control with up/down and SPI Integrated RF balun for single-ended 50 Ω inputs Power supply: 3.3 and 5 V 8 mm × 8 mm, 56-lead LFCSP package

#### **APPLICATIONS**

Multiband/multistandard cellular base station diversity receivers

Wideband radio link diversity downconverters Multimode cellular extenders and picocells

#### **GENERAL DESCRIPTION**

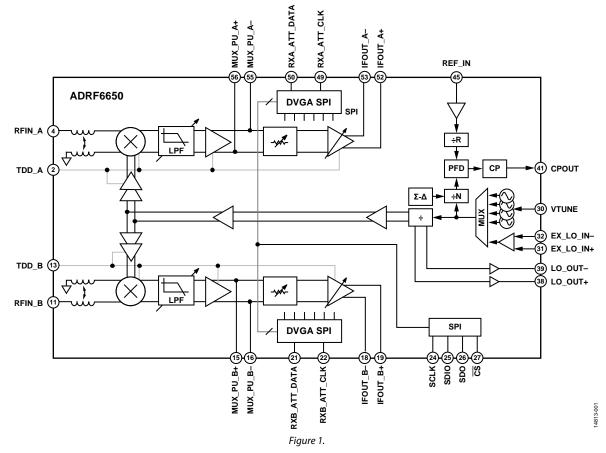

The ADRF6650 is a highly integrated downconverter that integrates dual mixers, dual digital switched attenuators, dual digital variable gain amplifiers, a phase-locked loop (PLL), and voltage controlled oscillators (VCOs). In addition, the ADRF6650 integrates two radio frequency (RF) baluns, serial gain control (SGC) controls, and fast enable inputs for time division duplex (TDD) operation. The on-chip RF baluns enable the ADRF6650 to support 50  $\Omega$  terminated RF inputs. The integrated passive mixer provides a highly linear downconversion for a 200 MHz, sliding, intermediate frequency (IF) window. The ADRF6650 uses broadband square wave limiting local oscillator (LO) amplifiers to achieve an RF bandwidth of 450 MHz to 2700 MHz. Unlike conventional narrow-band sine wave LO amplifier solutions, this amplifier permits the LO to be applied either above or below the RF input over an extremely wide bandwidth.

The ADRF6650 offers two alternatives for generating the differential LO input signal: internally via the on-chip fractional-N synthesizer with low phase noise VCOs, or externally via a low phase noise LO signal. The integrated PLL/VCO enables continuous LO coverage from 450 MHz to 2900 MHz. The PLL reference input supports a wide frequency range and includes integrated reference dividers before the phase frequency detector (PFD).

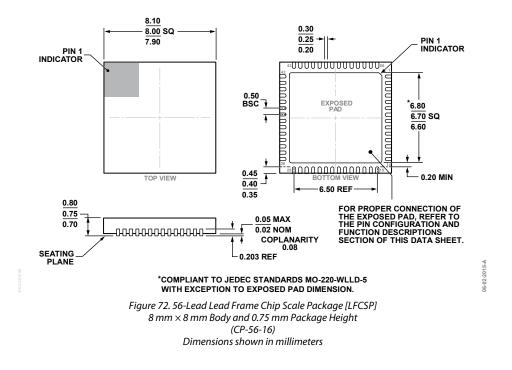

The ADRF6650 is fabricated using an advanced silicon-germanium (SiGe) bipolar complementary metal-oxide semiconductor (BiCMOS) process. It is available in a 56-lead, RoHS-compliant, 8 mm  $\times$  8 mm, lead frame chip scale package (LFCSP) package with an exposed pad. Performance is specified over the -40°C to +105°C maximum paddle temperature.

Rev. A

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2019 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **TABLE OF CONTENTS**

| Features                                      |

|-----------------------------------------------|

| Applications1                                 |

| General Description                           |

| Revision History 2                            |

| Functional Block Diagram                      |

| Specifications                                |

| RF Input to IF Output System Specifications   |

| Gain Control Specifications                   |

| PLL/VCO Specifications                        |

| Digital Logic Specifications8                 |

| Absolute Maximum Ratings10                    |

| Thermal Resistance10                          |

| ESD Caution10                                 |

| Pin Configuration and Function Descriptions11 |

| Typical Performance Characteristics           |

| Phase-Locked Loop (PLL)18                     |

| Spurious Performance21                        |

| Theory of Operation                           |

| RF Balun                                      |

| Mixers                                     | 22 |

|--------------------------------------------|----|

| Low-Pass Filters                           | 22 |

| IF Amplifiers                              | 22 |

| DVGA                                       | 22 |

| TDD Operation                              | 24 |

| LO Generation Block                        | 24 |

| Serial Port Interface                      |    |

| Applications Information                   |    |

| Basic Connections                          |    |

| RF Frequency and IF Bandwidth Optimization | 31 |

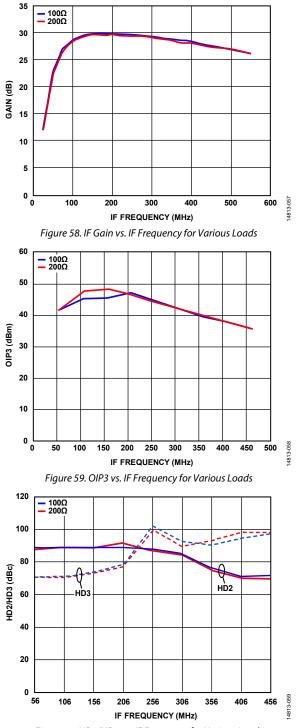

| IF DVGA vs. Load                           |    |

| ADC Interfacing                            | 32 |

| Power Modes                                | 33 |

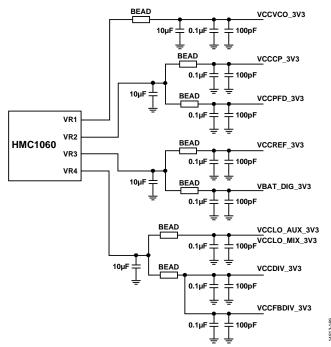

| Power Supply Configuration                 |    |

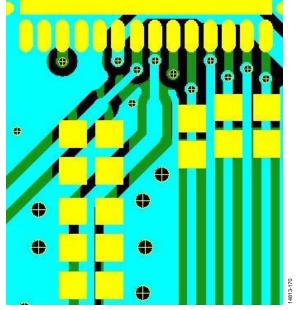

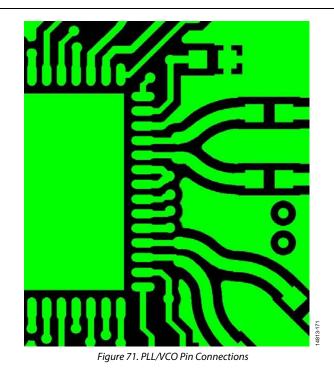

| Layout                                     | 35 |

| Register Map                               | 37 |

| Register Details                           | 40 |

| Outline Dimensions                         | 61 |

| Ordering Guide                             | 61 |

#### **REVISION HISTORY**

11/2019—Revision A

# FUNCTIONAL BLOCK DIAGRAM

# **SPECIFICATIONS**

$VCC\_DVGA\_A/VCC\_DVGA\_B = 5 V, remaining supplies = 3.3 V, T_A = 25^{\circ}C, low-side LO injection, f_{\rm IF} = 184 MHz, internal LO, maximum and the second states and the second states and the second states are second states and the second states are second states and the second states are second state$ gain setting, 5 V high performance settings, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

| Parameter                              | Test Conditions/Comments                                                                                                    | Min  | Тур  | Max  | Unit |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| RF INPUT INTERFACE                     |                                                                                                                             |      |      |      |      |

| Return Loss                            | RFIN_A/RFIN_B internally matched to 50 $\Omega$                                                                             |      | -10  |      | dB   |

| Input Impedance                        |                                                                                                                             |      | 50   |      | Ω    |

| RF Frequency Range                     |                                                                                                                             | 450  |      | 2700 | MHz  |

| IF OUTPUT INTERFACE                    |                                                                                                                             |      |      |      |      |

| Return loss                            | IF output with 100 $\Omega$ differential load (25 $\Omega$ external resistors are required on each differential output pin) |      | -10  |      | dB   |

| Output Impedance                       | Differential impedance                                                                                                      |      | 10   |      | Ω    |

| LO INPUT INTERFACE                     | External LO operation, differential                                                                                         |      |      |      |      |

| Required Input Power                   |                                                                                                                             | -6   |      | +6   | dBm  |

| Input Impedance                        |                                                                                                                             |      | 100  |      | Ω    |

| Return Loss                            |                                                                                                                             |      | -10  |      | dB   |

| Frequency Range                        | Low-side or high-side LO                                                                                                    | 450  |      | 2900 | MHz  |

| LO OUTPUT INTERFACE                    | Differential                                                                                                                |      |      |      |      |

| Power <sup>1</sup>                     | TRM_XLODRV_DRV_POUT = 01                                                                                                    |      |      |      |      |

| $f_{LO} = 900 \text{ MHz}$             |                                                                                                                             |      | 0    |      | dBm  |

| $f_{LO} = 1800 \text{ MHz}$            |                                                                                                                             |      | 1    |      | dBm  |

| $f_{LO} = 2700 \text{ MHz}$            |                                                                                                                             |      | 0    |      | dBm  |

| Output Impedance                       |                                                                                                                             |      | 50   |      | Ω    |

| Return Loss                            |                                                                                                                             |      | -10  |      | dB   |

| Frequency Range                        | Low-side or high-side LO                                                                                                    | 450  |      | 2900 | MHz  |

| POWER SUPPLY                           |                                                                                                                             |      |      |      |      |

| VCC_DVGA_A and VCC_DVGA_B <sup>2</sup> | 5 V mode                                                                                                                    | 4.75 | 5.0  | 5.25 | V    |

|                                        | 3.3 V mode                                                                                                                  | 3.1  | 3.3  | 3.5  | V    |

| PLL/VCO Supplies <sup>3</sup>          |                                                                                                                             | 3.2  | 3.3  | 3.4  | V    |

| RF and IF Supplies                     |                                                                                                                             | 3.1  | 3.3  | 3.5  | V    |

| POWER CONSUMPTION                      | Total                                                                                                                       |      |      |      |      |

| $f_{LO} = 1050 \text{ MHz}$            | Internal LO                                                                                                                 |      | 2.6  |      | W    |

|                                        | Internal LO, auxiliary LO output buffer disabled                                                                            |      | 2.4  |      | W    |

| $f_{LO} = 1565 \text{ MHz}$            | Internal LO                                                                                                                 |      | 2.7  |      | W    |

|                                        | Internal LO, auxiliary LO output buffer disabled                                                                            |      | 2.5  |      | W    |

| $f_{LO} = 2350 \text{ MHz}$            | Internal LO                                                                                                                 |      | 2.6  |      | W    |

|                                        | Internal LO, auxiliary LO output buffer disabled                                                                            |      | 2.47 |      | W    |

<sup>1</sup> For details on LO output power setting, see the LO Generation Block section.

<sup>2</sup> For the 3.3 V DVGA supply option, see the Applications Information section.

<sup>3</sup> Design practices for the best noise performance are discussed in the Applications Information section.

#### **RF INPUT TO IF OUTPUT SYSTEM SPECIFICATIONS**

$VCC_DVGA_A/VCC_DVGA_B = 5 V$ , remaining supplies = 3.3 V,  $T_A = 25^{\circ}C$ , low-side LO injection,  $f_{IF} = 184 MHz$ , internal LO, maximum gain setting, 5 V high performance settings, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

| Parameter                                          | Test Conditions/Comments                                                                                  | Min | Тур   | Max | Unit |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| DYNAMIC PERFORMANCE AT RF Frequency                | High-side LO                                                                                              |     | -76   |     |      |

| $(f_{RF}) = 900 \text{ MHz}$                       |                                                                                                           |     |       |     |      |

| Power Gain                                         |                                                                                                           |     | 30    |     | dB   |

| Output 1 dB Compression Point (OP1dB)              | Maximum gain                                                                                              |     | 16    |     | dBm  |

|                                                    | Gain = 1 dB                                                                                               |     | 8     |     | dBm  |

| Output Third-Order Intercept Point (OIP3)          | Output power ( $P_{OUT}$ ) = -4 dBm/tone, 1 MHz to 40 MHz separation                                      |     | 44    |     | dBm  |

|                                                    | Maximum gain minus 16 dB, $P_{OUT} = -4 \text{ dBm/tone}$ , 1 MHz to 40 MHz separation                    |     | 38    |     | dBm  |

| Noise Figure                                       | Maximum gain and maximum gain minus 5 dB                                                                  |     | 9.5   |     | dB   |

| Noise Figure Under Blocker                         | Internal LO, 3 MHz offset blocking, $P_{IN} = 0$ dBm, $P_{OUT} = 1$ dBm                                   |     | 21    |     | dB   |

| Second Harmonic Distortion (HD2)                   | $P_{IN} = 0 \text{ dBm}, P_{OUT} = 1 \text{ dBm}$                                                         |     | -66.7 |     | dBc  |

| Third Harmonic Distortion (HD3)                    | $P_{IN} = 0 \text{ dBm}, P_{OUT} = 1 \text{ dBm}$                                                         |     | -58   |     | dBc  |

| LO to IF Leakage                                   |                                                                                                           |     | -22.5 |     | dBm  |

| LO to RF Leakage                                   |                                                                                                           |     | -54   |     | dBm  |

| RF to IF Leakage                                   |                                                                                                           |     | -46   |     | dBc  |

| Isolation                                          | Channel to channel                                                                                        |     | 52    |     | dBc  |

| DYNAMIC PERFORMANCE AT $f_{RF} = 1800 \text{ MHz}$ | Low-side LO                                                                                               |     | -     |     |      |

| Power Gain                                         |                                                                                                           |     | 29    |     | dB   |

| OP1dB                                              | Maximum gain                                                                                              |     | 16    |     | dBm  |

|                                                    | Gain = 1 dB                                                                                               |     | 9     |     | dBm  |

| OIP3                                               | $P_{OUT} = -4 \text{ dBm/tone}, 1 \text{ MHz to } 40 \text{ MHz separation}$                              |     | 43    |     | dBm  |

|                                                    | Maximum gain minus 16 dB, $P_{OUT} = -4$ dBm/tone, 1 MHz to 40 MHz separation                             |     | 41    |     | dBm  |

| Noise Figure                                       | Maximum gain and maximum gain minus 5 dB                                                                  |     | 11    |     | dB   |

| Noise Figure Under Blocker                         | Internal LO, 3 MHz offset blocking, input power $(P_{IN}) = 0 \text{ dBm}$ ,<br>$P_{OUT} = 1 \text{ dBm}$ |     | 22.5  |     | dB   |

| HD2                                                | $P_{IN} = 0 \text{ dBm}, P_{OUT} = 1 \text{ dBm}$                                                         |     | -75   |     | dBc  |

| HD3                                                | $P_{IN} = 0 \text{ dBm}, P_{OUT} = 1 \text{ dBm}$                                                         |     | -67   |     | dBc  |

| LO to IF Leakage                                   |                                                                                                           |     | -37.5 |     | dBm  |

| LO to RF Leakage                                   |                                                                                                           |     | -55   |     | dBm  |

| RF to IF Leakage                                   |                                                                                                           |     | -68   |     | dBc  |

| Isolation                                          | Channel to channel                                                                                        |     | 50    |     | dBc  |

| DYNAMIC PERFORMANCE AT $f_{RF} = 2700 \text{ MHz}$ | High-side LO                                                                                              |     |       |     | 1    |

| Power Gain                                         |                                                                                                           |     | 29    |     | dB   |

| OP1dB                                              | Maximum gain                                                                                              |     | 16    |     | dBm  |

|                                                    | Gain = 1 dB                                                                                               |     | 9     |     | dBm  |

| OIP3                                               | $P_{OUT} = -4 \text{ dBm/tone}, 1 \text{ MHz to } 40 \text{ MHz separation}$                              |     | 43.5  |     | dBm  |

|                                                    | Maximum gain minus 16 dB, $P_{OUT} = -4 \text{ dBm/tone}$ , 1 MHz to 40 MHz separation                    |     | 40    |     | dBm  |

| Noise Figure                                       | Maximum gain and maximum gain minus 5 dB                                                                  |     | 11.5  |     | dB   |

| Noise Figure Under Blocker                         | Internal LO, 3 MHz offset blocking, $P_{IN} = 0 \text{ dBm}$ , $P_{OUT} = 1 \text{ dBm}$                  |     | 23.5  |     | dB   |

| HD2                                                | $P_{IN} = 0 \text{ dBm}, P_{OUT} = 1 \text{ dBm}$                                                         |     | -59   |     | dBc  |

| HD3                                                | $P_{IN} = 0 \text{ dBm}, P_{OUT} = 1 \text{ dBm}$                                                         |     | -63   |     | dBc  |

| LO to IF Leakage                                   |                                                                                                           |     | -43   |     | dBm  |

| LO to RF Leakage                                   |                                                                                                           |     | -46   |     | dBm  |

| RF to IF Leakage                                   |                                                                                                           |     | -81   |     | dBc  |

| Isolation                                          | Channel to channel                                                                                        |     | 57    |     | dBc  |

| Parameter                                     | Test Conditions/Comments                                                                                                                                                                               | Min | Тур | Мах | Unit |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| MxN SPURS                                     | See the Spurious Performance section                                                                                                                                                                   |     |     |     |      |

| RF TO IF DELAY DIFFERENCE BETWEEN<br>CHANNELS | Channel A = 5 dB attenuation, Channel B sweep attenuation from 0 dB to 40 dB                                                                                                                           |     | 1   |     | ns   |

| TDD SWITCH TIME                               | Level sensitive, from effective level of control signal to<br>99%/1% of final RF signal level; the amplitude response,<br>phase response, and group delay must all be settled in this<br>time interval |     | 1   | 2   | μs   |

#### GAIN CONTROL SPECIFICATIONS

Table 3.

| Parameter                    | Test Conditions/Comments                                                                                                                                                | Min | Тур  | Max | Unit    |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------|

| GAIN ADJUSTMENT              |                                                                                                                                                                         |     |      |     |         |

| Range                        |                                                                                                                                                                         |     | 43   |     | dB      |

| Step                         |                                                                                                                                                                         |     | 1    |     | dB      |

| Gain Step Error              | Between any two adjacent steps                                                                                                                                          |     | ±0.2 |     | dB      |

| Cumulative Gain Error        | Error vs. line (maximum gain reference)                                                                                                                                 |     | 1    |     | dB      |

| Phase Error                  | $f_{RF} = 200 \text{ MHz}$ and with 20 dB gain change                                                                                                                   |     | 10   |     | Degrees |

| Gain Adjustment Setting Time | At any gain settings, this specification must be met with any gain adjustment between 1 dB to 16 dB and the output power settled within $\pm 1$ dB of the final value   |     | 15   |     | ns      |

| Gain Adjustment Setting Time | At any gain settings, this specification must be met with any gain adjustment between 1 dB to 16 dB and the output power settled within $\pm 0.1$ dB of the final value |     | 70   |     | ns      |

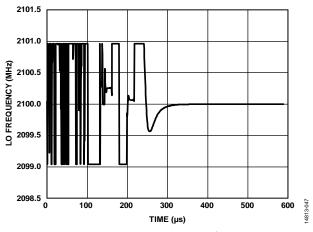

#### PLL/VCO SPECIFICATIONS

VCC\_x and VCC\_DVGA\_A/VCC\_DVGA\_B = 5 V, remaining supplies = 3.3 V,  $T_A = 25^{\circ}\text{C}$ ,  $f_{REF} = 122.88 \text{ MHz}$ ,  $f_{REF}$  power = 2.5 V p-p, PFD frequency ( $f_{PFD}$ ) = 30.72 MHz, charge pump current setting of 7, and loop filter bandwidth = 20 kHz, unless otherwise noted.

Table 4. Parameter **Test Conditions/Comments** Min Max Unit Тур PLL REFERENCE **PLL Reference Frequency** 10 30.72 250 MHz PLL Reference Level For PLL lock condition, 50  $\Omega$  to ground required 0.7 3.3 Vp-p close to REF\_IN pin Step Size 240 kHz Lock Time 0.4 ms PFD FREQUENCY 30.72 61.44 MHz INTERNAL VCO RANGE 4000 8000 MHz **OPEN-LOOP VCO PHASE NOISE** VCO Frequency ( $f_{VCO}$ ) = 4200 MHz 10 kHz offset -86 dBc/Hz 100 kHz offset dBc/Hz -112 1 MHz offset -133 dBc/Hz 10 MHz offset -153 dBc/Hz  $f_{VCO} = 4700 \text{ MHz}$ 10 kHz offset -84 dBc/Hz 100 kHz offset dBc/Hz -112 1 MHz offset -134 dBc/Hz 10 MHz offset -154 dBc/Hz  $f_{VCO} = 5440 \text{ MHz}$ 10 kHz offset -83 dBc/Hz 100 kHz offset dBc/Hz -110 1 MHz offset -132 dBc/Hz 10 MHz offset -152 dBc/Hz

| Parameter                                                                                   | Test Conditions/Comments                                        | Min Typ I | Max Unit |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------|----------|

| f <sub>vco</sub> = 6260 MHz                                                                 | 10 kHz offset                                                   | -82       | dBc/Hz   |

|                                                                                             | 100 kHz offset                                                  | -108      | dBc/Hz   |

|                                                                                             | 1 MHz offset                                                    | -130      | dBc/Hz   |

|                                                                                             | 10 MHz offset                                                   | -150      | dBc/Hz   |

| f <sub>vco</sub> = 7060 MHz                                                                 | 10 kHz offset                                                   | -80       | dBc/Hz   |

|                                                                                             | 100 kHz offset                                                  | -106      | dBc/Hz   |

|                                                                                             | 1 MHz offset                                                    | -127      | dBc/Hz   |

|                                                                                             | 10 MHz offset                                                   | -147      | dBc/Hz   |

| SYNTHESIZER SPECIFICATIONS                                                                  |                                                                 |           |          |

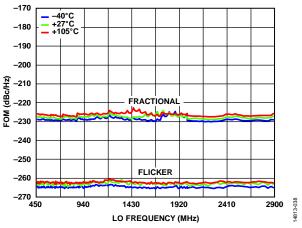

| Fractional Figure of Merit (FOM)                                                            |                                                                 | -227      | dBc/Hz   |

| Flicker FOM                                                                                 |                                                                 | -262      | dBc/Hz   |

| f <sub>PFD</sub> Spurs <sup>1</sup>                                                         | At the input of internal mixer and daisy-chained ADRF6650 mixer |           |          |

| $f_{PFD} \times 1$                                                                          |                                                                 | -90       | dBc      |

| $f_{PFD} \times 2$                                                                          |                                                                 | -95       | dBc      |

| $f_{PFD} \times 3$ and Higher                                                               |                                                                 | -95       | dBc      |

| Unwanted Spurs (Other Than PFD and Harmonics) <sup>1</sup>                                  | At the input of internal mixer and daisy-chained ADRF6650 mixer | -70       | dBc      |

| LO Frequency ( $f_{LO}$ ) = 1050 MHz, $f_{VCO}$ = 4200 MHz                                  |                                                                 |           |          |

| Closed-Loop Phase Noise                                                                     | 1 kHz offset                                                    | -110      | dBc/Hz   |

|                                                                                             | 10 kHz offset                                                   | -107      | dBc/Hz   |

|                                                                                             | 100 kHz offset                                                  | -122      | dBc/Hz   |

|                                                                                             | 600 kHz offset                                                  | -141      | dBc/Hz   |

|                                                                                             | 800 kHz offset                                                  | -143      | dBc/Hz   |

|                                                                                             | 1.6 MHz offset                                                  | -149      | dBc/Hz   |

|                                                                                             | 3 MHz offset                                                    | -153      | dBc/Hz   |

|                                                                                             | 10 MHz offset                                                   | -157      | dBc/Hz   |

|                                                                                             | 100 MHz offset                                                  | -159      | dBc/Hz   |

| Integrated Phase Noise and Spurs                                                            | 100 Hz to 10 MHz integration bandwidth                          | 0.08      | °rms     |

| $f_{LO} = 1565 \text{ MHz}, f_{VCO} = 6260 \text{ MHz}$                                     |                                                                 |           |          |

| Closed-Loop Phase Noise                                                                     | 1 kHz offset                                                    | -106      | dBc/Hz   |

| ·                                                                                           | 10 kHz offset                                                   | -102      | dBc/Hz   |

|                                                                                             | 100 kHz offset                                                  | -119      | dBc/Hz   |

|                                                                                             | 600 kHz offset                                                  | -137      | dBc/Hz   |

|                                                                                             | 800 kHz offset                                                  | -140      | dBc/Hz   |

|                                                                                             | 1.6 MHz offset                                                  | -145      | dBc/Hz   |

|                                                                                             | 3 MHz offset                                                    | -151      | dBc/Hz   |

|                                                                                             | 10 MHz offset                                                   | -156      | dBc/Hz   |

|                                                                                             | 100 MHz offset                                                  | -157      | dBc/Hz   |

| Integrated Phase Noise and Spurs $f_{L0} = 1765 \text{ MHz}$ , $f_{VC0} = 7060 \text{ MHz}$ | 100 Hz to 10 MHz integration bandwidth                          | 0.13      | °rms     |

| Closed-Loop Phase Noise                                                                     | 1 kHz offset                                                    | -102      | dBc/Hz   |

|                                                                                             | 10 kHz offset                                                   | -97       | dBc/Hz   |

|                                                                                             | 100 kHz offset                                                  | -117      | dBc/Hz   |

|                                                                                             | 950 kHz offset                                                  | -138      | dBc/Hz   |

|                                                                                             | 2.1 MHz offset                                                  | -145      | dBc/Hz   |

|                                                                                             | 3.5 MHz offset                                                  | -149      | dBc/Hz   |

|                                                                                             | 7.5 MHz offset                                                  | -153      | dBc/Hz   |

|                                                                                             | 10 MHz offset                                                   | -156      | dBc/Hz   |

|                                                                                             | 100 MHz offset                                                  | -158      | dBc/Hz   |

| Integrated Phase Noise and Spurs                                                            | 100 Hz to 10 MHz integration bandwidth                          | 0.2       | °rms     |

| Parameter                                               | Test Conditions/Comments               | Min | Тур  | Max | Unit   |

|---------------------------------------------------------|----------------------------------------|-----|------|-----|--------|

| $f_{LO} = 2350 \text{ MHz}, f_{VCO} = 4700 \text{ MHz}$ |                                        |     |      |     |        |

| Closed-Loop Phase Noise                                 | 1 kHz offset                           |     | -103 |     | dBc/Hz |

|                                                         | 10 kHz offset                          |     | -101 |     | dBc/Hz |

|                                                         | 100 kHz offset                         |     | -116 |     | dBc/Hz |

|                                                         | 950 kHz offset                         |     | -140 |     | dBc/Hz |

|                                                         | 2.1 MHz offset                         |     | -147 |     | dBc/Hz |

|                                                         | 3.5 MHz offset                         |     | -151 |     | dBc/Hz |

|                                                         | 7.5 MHz offset                         |     | -156 |     | dBc/Hz |

|                                                         | 10 MHz offset                          |     | -156 |     | dBc/Hz |

|                                                         | 100 MHz offset                         |     | -157 |     | dBc/Hz |

| Integrated Phase Noise and Spurs                        | 100 Hz to 10 MHz integration bandwidth |     | 0.16 |     | °rms   |

| $f_{LO} = 2720 \text{ MHz}, f_{VCO} = 5440 \text{ MHz}$ |                                        |     |      |     |        |

| Closed-Loop Phase Noise                                 | 1 kHz offset                           |     | -102 |     | dBc/Hz |

|                                                         | 10 kHz offset                          |     | -99  |     | dBc/Hz |

|                                                         | 100 kHz offset                         |     | -114 |     | dBc/Hz |

|                                                         | 950 kHz offset                         |     | -137 |     | dBc/Hz |

|                                                         | 2.1 MHz offset                         |     | -144 |     | dBc/Hz |

|                                                         | 3.5 MHz offset                         |     | -148 |     | dBc/Hz |

|                                                         | 7.5 MHz offset                         |     | -153 |     | dBc/Hz |

|                                                         | 10 MHz offset                          |     | -155 |     | dBc/Hz |

|                                                         | 100 MHz offset                         |     | -156 |     | dBc/Hz |

| Integrated Phase Noise and Spurs                        | 100 Hz to 10 MHz integration bandwidth |     | 0.2  |     | °rms   |

<sup>1</sup> Auxiliary LO output measurements are performed under daisy-chain configuration with another ADRF6650 device. Measurements are taken from the auxiliary LO output of the daisy-chained ADRF6650.

#### DIGITAL LOGIC SPECIFICATIONS

Table 5.

| Parameter                  | Symbol          | Test Conditions/Comments                                                                   | Min  | Тур | Max  | Unit |

|----------------------------|-----------------|--------------------------------------------------------------------------------------------|------|-----|------|------|

| ALL DIGITAL INPUTS/OUTPUTS |                 |                                                                                            |      |     |      |      |

| Input Voltage              |                 |                                                                                            |      |     |      |      |

| Logic Low                  | VIL             |                                                                                            | 0    |     | 0.5  | V    |

| Logic High                 | VIH             |                                                                                            | 1.2  |     | 3.6  | V    |

| Input Current              |                 |                                                                                            |      |     |      |      |

| Logic High                 | Іін             |                                                                                            | -100 |     | +100 | μΑ   |

| Logic Low                  | lı∟             |                                                                                            | -100 |     | +100 | μΑ   |

| Output Voltage             |                 |                                                                                            |      |     |      |      |

| Logic Low                  | Vol             |                                                                                            | 0    |     | 0.4  | V    |

| Logic High                 | V <sub>OH</sub> | When driving loads with complementary metal-<br>oxide semiconductor (CMOS) 1.8 V interface | 1.4  |     | 1.8  | V    |

|                            |                 | When driving loads with CMOS 3.3 V interface                                               | 2.4  |     | 3.3  | V    |

| Output Driving Current     |                 |                                                                                            |      |     |      |      |

| Logic High                 | Іон             |                                                                                            |      | 1   | 2    | mA   |

| Logic Low                  | IOL             |                                                                                            |      | 1   | 2    | mA   |

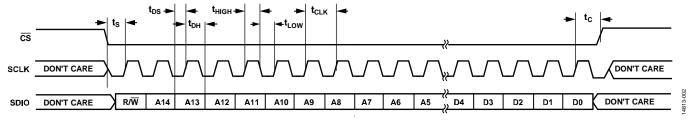

#### Serial Peripheral Interface (SPI) Timing

#### Table 6.

| Parameter               | Description                                                               | Min | Тур | Max | Unit |

|-------------------------|---------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>DS</sub>         | SDI to SCLK rising edge setup                                             | 8   |     |     | ns   |

| t <sub>DH</sub>         | SCLK rising edge to SDI hold                                              | 8   |     |     | ns   |

| <b>t</b> <sub>CLK</sub> | Period of SCLK                                                            | 50  |     |     | ns   |

| tніgн                   | High width of SCLK                                                        | 25  |     |     | ns   |

| t <sub>LOW</sub>        | Low width of SCLK                                                         | 25  |     |     | ns   |

| ts                      | CS falling edge to SCLK rising edge, setup time                           | 10  |     |     | ns   |

| tc                      | SCLK rising edge to $\overline{CS}$ rising edge, hold time                | 30  |     |     | ns   |

| t <sub>DV</sub>         | SCLK falling edge to valid readback data, SDIO/SDO; not shown in Figure 2 | 18  |     |     | ns   |

#### SPI Timing Diagram

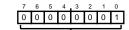

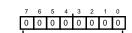

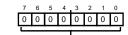

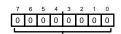

Figure 2. Serial Control Port Write Timing—MSB First, 16-Bit Instruction

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 7.

| 1.0010 / 1                                                                                                                   |                     |

|------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Parameter                                                                                                                    | Rating              |

| VCC_MIX_A, VCC_LOA_S2, VCC_LOA_S1,<br>VCC_LOB_S1, VCC_LOB_S2, VCC_MIX_B,<br>MIX_PU_A+, MIX_PU_A-, MIX_PU_B+,<br>MIX_PU_B-    | –0.3 V to +3.6 V    |

| VCC_DVGA_B, VCC_DVGA_A                                                                                                       | –0.3 V to +5.4 V    |

| VCCVCO_3V3, VCCDIV_3V3, VCCFBDIV_3V3,<br>VCCLO_MIX_3V3, VCCLO_AUX_3V3,<br>VCCCP_3V3, VCCPFD_3V3, VCCREF_3V3,<br>VBAT_DIG_3V3 | –0.3 V to +3.6 V    |

| RF Input Power (RFIN_A, RFIN_B)                                                                                              | 20 dBm              |

| External LO Input Power                                                                                                      | 10 dBm differential |

| VTUNE, CPOUT, REF_IN, DCL_BIAS                                                                                               | –0.3 V to +3.6 V    |

| TDD_A, TDD_B, RXA_ATT_CLK,<br>RXA_ATT_DATA, RXB_ATT_CLK,<br>RXB_ATT_DATA                                                     | –0.3 V to +3.6 V    |

| SCLK, SDIO, SDO, <del>CS</del>                                                                                               | –0.3 V to +3.6 V    |

| Maximum Junction Temperature                                                                                                 | 125°C               |

| Operating Temperature Range<br>(Measured at Pad)                                                                             | –40°C to +105°C     |

| Storage Temperature Range                                                                                                    | –65°C to +150°C     |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

Typical  $\theta_{JA}$  and  $\theta_{JC}$  are specified vs. the number of PCB layers. The use of appropriate thermal management techniques is recommended to ensure that the maximum junction temperature does not exceed the limits shown in Table 7.

#### Table 8. Thermal Resistance

| Package Type                         | θ <sub>JA</sub>  | θις | Unit |

|--------------------------------------|------------------|-----|------|

| CP-56-16 <sup>1</sup>                |                  |     |      |

| JEDEC 1s0p Board <sup>2</sup>        | N/A <sup>4</sup> | 3.3 | °C/W |

| Cold Plate Only, No PCB <sup>3</sup> | N/A <sup>4</sup> | 2.8 | °C/W |

| JEDEC 2s2p Board <sup>2</sup>        | 29.3             | N/A | °C/W |

<sup>1</sup> The maximum junction temperature of 125°C cannot be exceeded.

<sup>2</sup> Per JEDEC JESD51-12.

<sup>3</sup> For nonstandardized testing where the paddle of the device is directly connected to a cold plate. This approach can be useful to estimate junction temperature when the exact paddle temperature is known in the application.

<sup>4</sup> N/A means not applicable.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

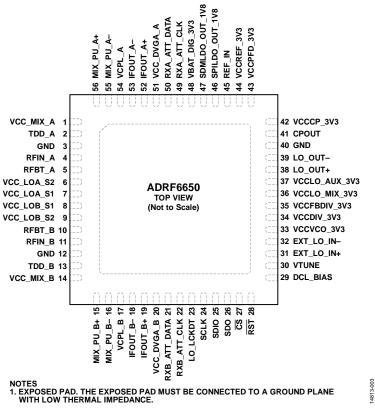

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

| Pin No. | Mnemonic     | Description                                                |  |

|---------|--------------|------------------------------------------------------------|--|

| 1       | VCC_MIX_A    | Channel A Mixer IF Amplifier Vcc.                          |  |

| 2       | TDD_A        | TDD Enable, Channel A.                                     |  |

| 3       | GND          | Ground.                                                    |  |

| 4       | RFIN_A       | Channel A Single-Ended, RF, 50 $\Omega$ Input.             |  |

| 5       | RFBT_A       | Channel A RF Balun Low Frequency Inductor Connection.      |  |

| 6       | VCC_LOA_S2   | Channel A LO Path $V_{cc}$ (Stage 3 and Stage 4).          |  |

| 7       | VCC_LOA_S1   | Channel A LO Path V $_{ m CC}$ (Stage 1 and Stage 2).      |  |

| 8       | VCC_LOB_S1   | Channel B LO Path $V_{cc}$ (Stage 1 and Stage 2).          |  |

| 9       | VCC_LOB_S2   | Channel B LO Path V <sub>CC</sub> (Stage 3 and Stage 4).   |  |

| 10      | RFBT_B       | Channel B RF Balun Low Frequency Inductor Connection.      |  |

| 11      | RFIN_B       | Channel B Single-Ended, RF, 50 $\Omega$ Input.             |  |

| 12      | GND          | Ground.                                                    |  |

| 13      | TDD_B        | TDD Enable, Channel B.                                     |  |

| 14      | VCC_MIX_B    | Channel B Mixer IF Amplifier Vcc.                          |  |

| 15      | MIX_PU_B+    | Channel B Mixer IF Amplifier Positive Output Pull-Up.      |  |

| 16      | MIX_PU_B-    | Channel B Mixer IF Amplifier Negative Output Pull-Up.      |  |

| 17      | VCPL_B       | Channel B Variable Gain Amplifier (VGA) Decouple Output.   |  |

| 18      | IFOUT_B-     | Channel B VGA Negative Output.                             |  |

| 19      | IFOUT_B+     | Channel B VGA Positive Output.                             |  |

| 20      | VCC_DVGA_B   | Channel B Digital Step Attenuator (DSA) and VGA $V_{cc}$ . |  |

| 21      | RXB_ATT_DATA | Channel B VGA Serial Gain Control (Up/Down) Data.          |  |

| 22      | RXB_ATT_CLK  | Channel B VGA Serial Gain Control (Up/Down) Clock.         |  |

| 23      | LO_LCKDT     | LO Lock Detect.                                            |  |

| 24      | SCLK         | SPI Clock.                                                 |  |

| Pin No. | Mnemonic       | Description                                                                                  |

|---------|----------------|----------------------------------------------------------------------------------------------|

| 25      | SDIO           | SPI Data Input/Output (3-Wire Mode); Input Only (4-Wire Mode).                               |

| 26      | SDO            | SPI Data Output (4-Wire Mode); Not Used (3-Wire Mode).                                       |

| 27      | CS             | SPI Chip Select (Active Low).                                                                |

| 28      | RST            | Reset (Active Low).                                                                          |

| 29      | DCL_BIAS       | VCO Core Bias Decouple Output.                                                               |

| 30      | VTUNE          | Tuning Voltage (V <sub>TUNE</sub> ) Input.                                                   |

| 31      | EXT_LO_IN+     | External LO Positive Input.                                                                  |

| 32      | EXT_LO_IN-     | External LO Negative Input.                                                                  |

| 33      | VCCVCO_3V3     | VCO 3.3 V Supply.                                                                            |

| 34      | VCCDIV_3V3     | LO Chain and Divider 3.3 V Supply.                                                           |

| 35      | VCCFBDIV_3V3   | PLL Feedback Divider 3.3 V Supply.                                                           |

| 36      | VCCLO_MIX_3V3  | LO Mixer Output Buffer 3.3 V Supply.                                                         |

| 37      | VCCLO_AUX_3V3  | LO External Output Buffer 3.3 V Supply.                                                      |

| 38      | LO_OUT+        | External LO Positive Output.                                                                 |

| 39      | LO_OUT-        | External LO Negative Output.                                                                 |

| 40      | GND            | Charge Pump GND.                                                                             |

| 41      | CPOUT          | Charge Pump Output.                                                                          |

| 42      | VCCCP_3V3      | Charge Pump 3.3 V Supply.                                                                    |

| 43      | VCCPFD_3V3     | PFD 3.3 V Supply.                                                                            |

| 44      | VCCREF_3V3     | Reference Input Buffer 3.3 V Supply.                                                         |

| 45      | REF_IN         | Reference Input Buffer.                                                                      |

| 46      | SPILDO_OUT_1V8 | SPI 1.8 V LDO External Decouple Output.                                                      |

| 47      | SDMLDO_OUT_1V8 | SDM 1.8 V LDO External Decouple Output.                                                      |

| 48      | VBAT_DIG_3V3   | SPI and SDM LDO 3.3 V Supply.                                                                |

| 49      | RXA_ATT_CLK    | Channel A VGA Serial Gain Control (Up/Down) Clock.                                           |

| 50      | RXA_ATT_DATA   | Channel A VGA Serial Gain Control (Up/Down) Data.                                            |

| 51      | VCC_DVGA_A     | Channel A DSA and VGA V <sub>cc</sub> .                                                      |

| 52      | IFOUT_A+       | Channel A VGA Positive Output.                                                               |

| 53      | IFOUT_A-       | Channel A VGA Negative Output.                                                               |

| 54      | VCPL_A         | Channel A VGA Decouple Output.                                                               |

| 55      | MIX_PU_A-      | Channel A Mixer Amplifier Negative Output Pull-Up.                                           |

| 56      | MIX_PU_A+      | Channel A Mixer Amplifier Positive Output Pull-Up.                                           |

|         | EPAD           | Exposed Pad. The exposed pad must be connected to a ground plane with low thermal impedance. |

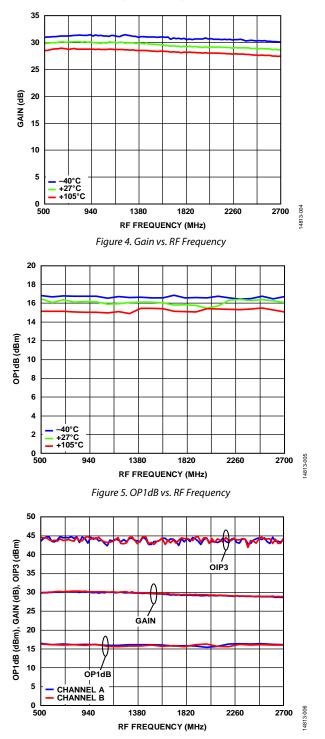

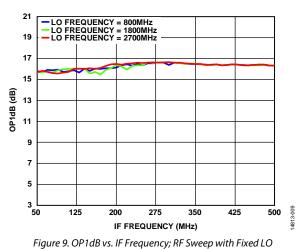

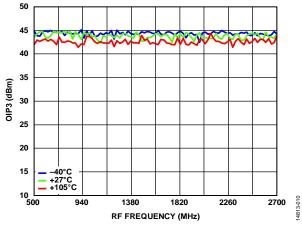

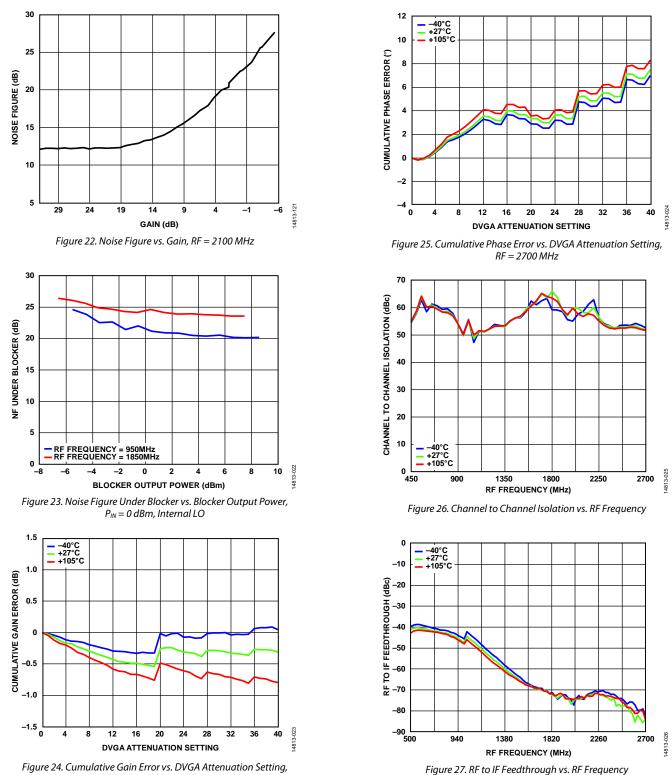

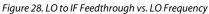

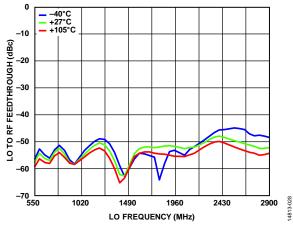

# **TYPICAL PERFORMANCE CHARACTERISTICS**

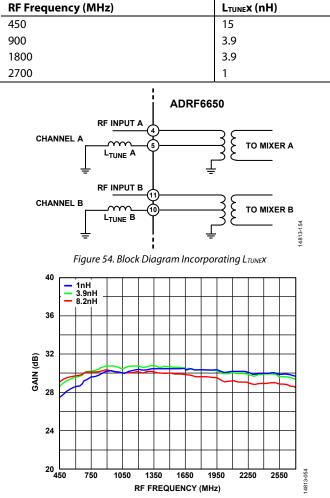

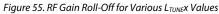

VCC\_DVGA\_x = 5 V, VCCx = 3.3 V,  $T_A = 27^{\circ}$ C,  $f_{IF} = 184$  MHz, internal LO, digital variable gain amplifier (DVGA) attenuation = 0 dB, L<sub>TUNE</sub> = 1 nH, L<sub>SHUNT</sub> = 150 nH, and 25  $\Omega$  external resistors on each differential leg, 5 V high power mode, low-pass filter setting = 7, unless otherwise noted. The LO is high-side for RF frequencies lower than 1 GHz and higher than 2.5 GHz, and LO is low-side for the remaining RF frequencies. For two-tone measurements, IF output power is -4 dBm/tone and 10 MHz tone spacing, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

Figure 6. OP1dB, Gain, and OIP3 vs. RF Frequency, Channel Comparison

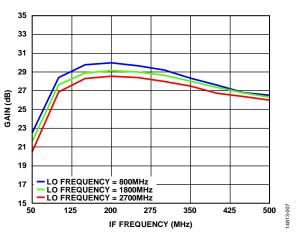

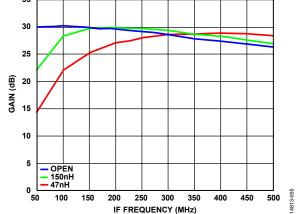

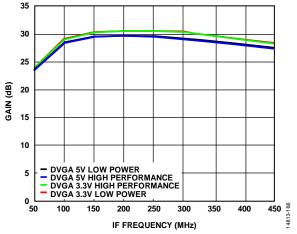

Figure 7. Gain vs. IF Frequency; RF Sweep with Fixed LO, LSHUNTX = 150 nH

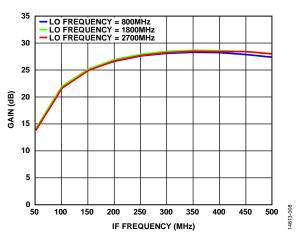

Figure 8. Gain vs. IF Frequency; RF Sweep with Fixed LO,  $L_{SHUNT}x = 47 \text{ nH}$

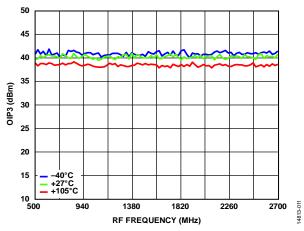

Figure 10. OIP3 vs. RF Frequency; Maximum Gain, L<sub>SHUNT</sub>x = 150 nH

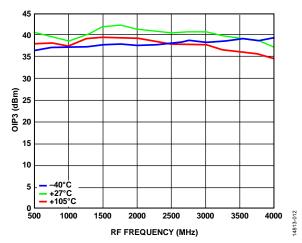

Figure 11. OIP3 vs. RF Frequency; Maximum Gain,  $L_{SHUNT}x = 47$  nH, IF = 368 MHz

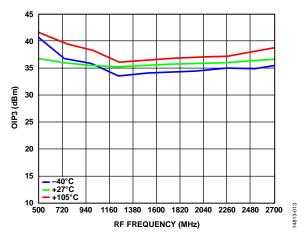

Figure 12. OIP3 vs. RF Frequency; Maximum Gain – 16 dB, L<sub>SHUNT</sub>x = 150 nH

Figure 13. OIP3 vs. RF Frequency; Maximum Gain – 16 dB,  $L_{SHUNTX} = 47$  nH, IF = 368 MHz

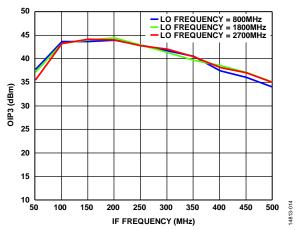

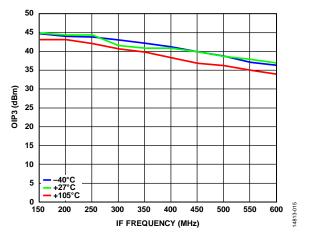

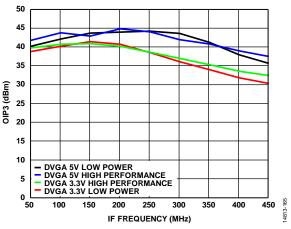

Figure 14. OIP3 vs. IF Frequency; RF Sweep with Fixed LO, Maximum Gain,  $L_{SHUNT}x = 150 \text{ nH}$

Figure 15. OIP3 vs. IF Frequency; RF Sweep with Fixed LO, Maximum Gain,  $L_{SHUNT}x = 47$  nH, IF = 368 MHz

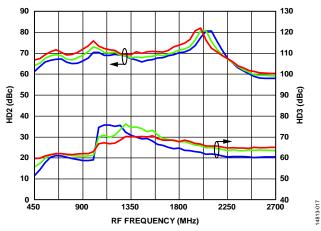

### **Data Sheet**

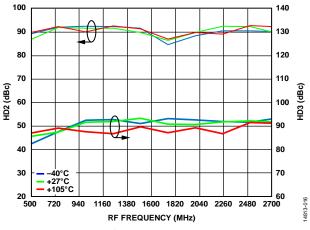

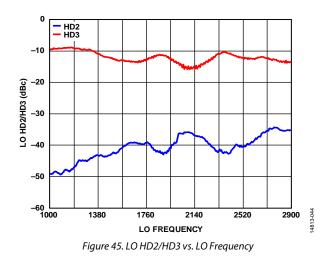

Figure 16. HD2 and HD3 vs. RF Frequency, Maximum Gain

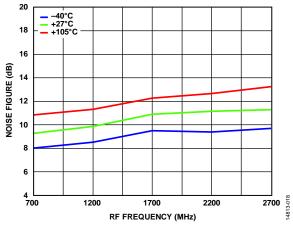

Figure 18. Noise Figure vs. RF Frequency; Maximum Gain

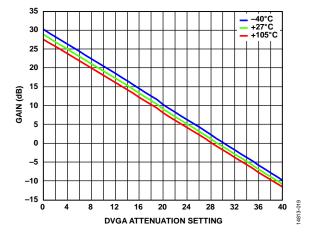

Figure 19. Gain vs. DVGA Attenuation Setting, RF = 2700 MHz

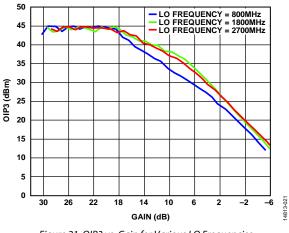

Figure 21. OIP3 vs. Gain for Various LO Frequencies

RF = 2700 MHz

### **Data Sheet**

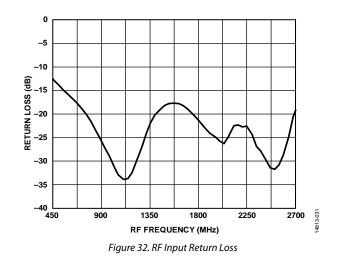

0 -40°C +27°C +105°C -10 LO TO IF FEEDTHROUGH (dBc) -20 -30 -40 -50 -60 -70 L 650 14813-027 1100 1550 2000 2450 2900 LO FREQUENCY (MHz)

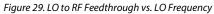

Figure 30. RF/IF 3.3 V, DVGA 5 V, and PLL/VCO 3.3 V Supply Currents vs. LO Frequency

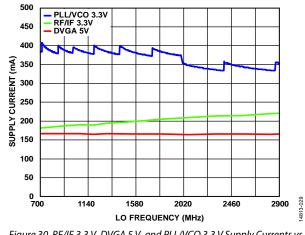

Figure 31. IF Output Return Loss , External 25  $\Omega$  on Each Differential Leg

#### PHASE-LOCKED LOOP (PLL)

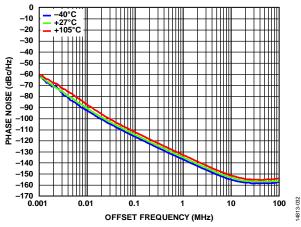

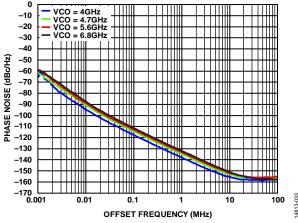

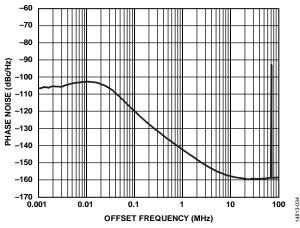

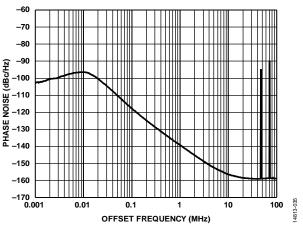

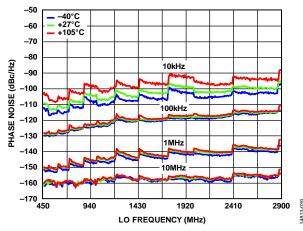

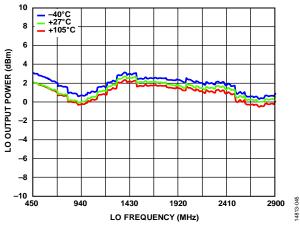

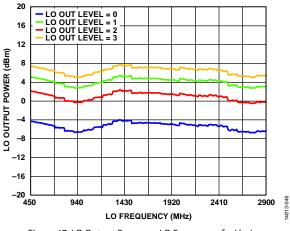

VCC\_DVGA\_x = 5 V, VCCx = 3.3 V,  $T_A = 27^{\circ}$ C,  $f_{PFD} = 30.72$  MHz,  $f_{REF} = 122.88$  MHz, 20 kHz loop filter, measured at the LO output, unless otherwise noted. All losses from input and output traces and baluns are de-embedded from results.

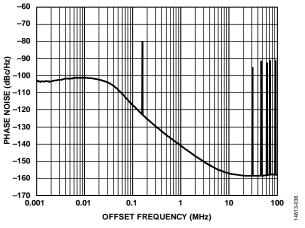

Figure 33. Open-Loop VCO Phase Noise vs. Offset Frequency,  $f_{LO} = 2350$  MHz,  $f_{VCO} = 4700$  MHz

Figure 34. Open-Loop VCO Phase Noise vs. Offset Frequency, for Various VCO Frequencies, Divide by 2 Selected

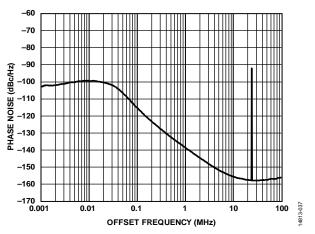

*Figure 35. Closed-Loop Phase Noise vs. Offset Frequency for*  $f_{LO} = 1565 \text{ MHz}$

Figure 36. Closed-Loop Phase Noise vs. Offset Frequency for  $f_{LO} = 1765$  MHz

Figure 37. Closed-Loop Phase Noise vs. Offset Frequency for  $f_{LO} = 2350 \text{ MHz}$

Figure 38. Closed-Loop Phase Noise vs. Offset Frequency for  $f_{LO} = 2720$  MHz

### **Data Sheet**

Figure 39. PLL Figure of Merit (FOM) vs. LO Frequency

Figure 40. Closed-Loop LO Phase Noise vs. LO Frequency for Various Offset Frequencies

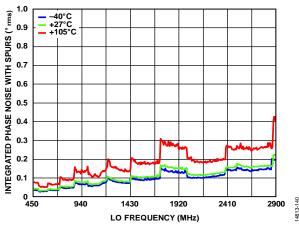

Figure 41. 100 Hz to 10 MHz Integrated Phase Noise vs. LO Frequency

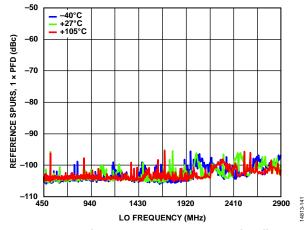

Figure 42. Reference Spurs vs. LO Frequency,  $1 \times f_{PFD}$  Offset, Daisy-Chain Measurement

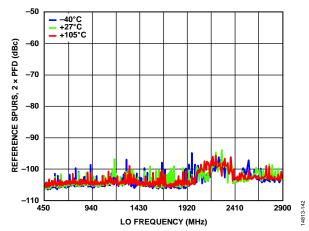

Figure 43. Reference Spurs vs. LO Frequency,  $2 \times f_{PFD}$  Offset, Daisy-Chain Measurement

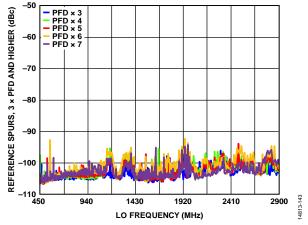

Figure 44. Reference Spurs vs. LO Frequency, 3 and Higher  $\times$   $f_{\mbox{\tiny PFD}}$  Offset, Daisy-Chain Measurement

**Data Sheet**

Figure 46. LO Output Power vs. LO Frequency

Figure 47. LO Output Power vs. LO Frequency, for Various Output Power Level Settings

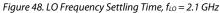

Figure 49. Auxiliary Output Return Loss, External LO Input Return Loss vs. LO Frequency

#### **SPURIOUS PERFORMANCE**

$(N \times f_{RF}) - (M \times f_{LO})$  spur measurements were made using the standard evaluation board. Mixer spurious products were measured in decibels (dB) relative to the carrier (dBc) from the IF output power level. IF = 184 MHz, and RF spur frequency is found with the formula;  $f_{RF\_SPUR} = ((M \times f_{LO}) + f_{IF}))/N$ . Data is shown for all spurious components greater than -115 dBc and frequencies of less than 2.7 GHz.

#### Table 10. 900 MHz Spurious Performance

| Ν | M = 1          | M = 2          | M = 3          | M = 4          | M = 5          | M = 6          |

|---|----------------|----------------|----------------|----------------|----------------|----------------|

| 1 | Not applicable | -53            | -10.5          | -49            | -17            | Not applicable |

| 2 | Not applicable | -84            | Not applicable | Not applicable | Not applicable | Not applicable |

| 3 | Not applicable | Not applicable | -115           | Not applicable | -115           | Not applicable |

| 4 | Not applicable |

| 5 | Not applicable |

| 6 | Not applicable |

## THEORY OF OPERATION

The ADRF6650 is a wideband, highly integrated, dual-channel downconverter ideally suited for multiple input, multiple output (MIMO) applications. Additionally, the ADRF6650 integrates an LO generation block consisting of a synthesizer and a multicore VCO with an octave range and low phase noise. The synthesizer uses a fractional-N PLL to enable continuous LO coverage from 450 MHz to 2900 MHz. The wideband frequency response and flexible frequency programming simplifies the receiver design, saves on-board space, and minimizes the need for external components.

The RF subsystem of the ADRF6650 consists of an integrated, wideband, low loss RF balun; a double balanced, passive metaloxide semiconductor field-effect transistor (MOSFET) mixer; a tunable filter; a fixed gain IF amplifier; a DVGA, and fractional synthesizer with on-chip VCO.

#### **RF BALUN**

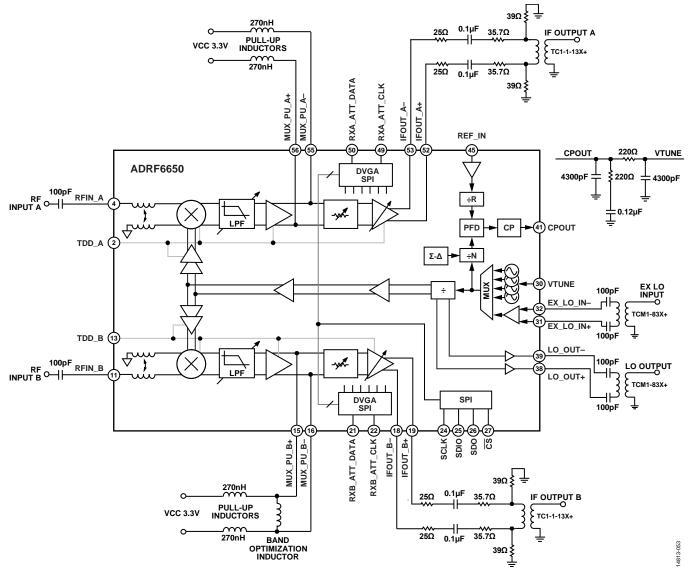

The ADRF6650 integrates a wideband balun operating over a frequency range from 450 MHz to 2700 MHz. The RF balun offers the benefit of ease of drivability from a single-ended 50  $\Omega$  RF input, and the single-ended to differential conversion of the balun optimizes common-mode rejection. The balun uses an external compensation inductor to improve the balance for low RF frequency. See the RF Frequency and IF Bandwidth Optimization section for details.

#### MIXERS

The output of the balun is applied to a passive mixer that commutates the RF input in accordance with the output of the LO subsystem. The passive mixer is essentially a balanced, low loss switch that adds minimum noise to the frequency translation. The only noise contribution from the mixer is due to the resistive loss of the switches, which is in the order of a few ohms.

#### LOW-PASS FILTERS

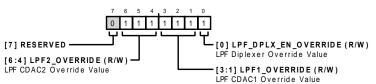

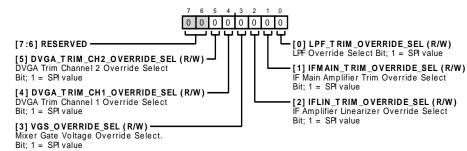

Because the mixer is inherently broadband and bidirectional, it is necessary to properly terminate all idler (M × N product) frequencies generated by the mixing process. Terminating the mixer avoids the generation of unwanted intermodulation products and reduces the level of unwanted signals at the input of the IF amplifier, where high peak signal levels can compromise the compression and intermodulation performance of the system. This termination is accomplished by the addition of a programmable low-pass filter (LPF) network between the IF amplifier and the mixer and in the feedback elements in the IF amplifier. The LPF filter has programmable filter bandwidths and is tuned by switching parallel capacitances on the primary and secondary sides by writing to the LPF\_OVERRIDE register (Register 0x0300). Therefore, selecting the proper combination of LPF1\_OVERRIDE (Register 0x0300, Bits[3:1]) and LPF2\_OVERRIDE (Register 0x0300, Bits[6:4]) sets the desired bandwidth. It is recommended to set the LPF1 OVERRIDE and LPF2 OVERRIDE bit fields to the same value.

In addition, the input side of the LPF has a series 50  $\Omega$  resistor on each differential leg which improves the mixer termination for low RF frequencies (<1 GHz). The resistors can be bypassed by DPLX\_EN\_OVERRIDE (Register 0x0300, Bit 0).

#### **IF AMPLIFIERS**

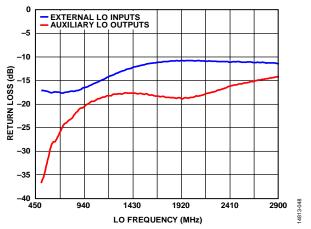

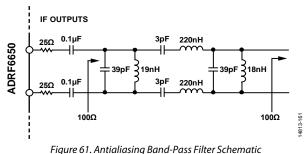

The IF amplifier following the LPF is a fixed gain, balanced feedback design that simultaneously provides the desired gain, noise figure, and input impedance that is required to achieve the overall performance. The balanced open-collector output of the IF amplifier, with an impedance modified by the feedback within the amplifier, connects internally to the DSA stage, but requires external pull-up inductors of approximately 220 nH. It is also possible to use a tuned load to improve the filtering of unwanted mixing products but can limit the signal bandwidth for wide bandwidth applications.

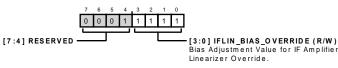

The IP3 performance can be optimized by adjusting the lowpass filter between the mixer and the IF amplifier. Further optimization can be made, via SPI control, by adjusting the IF main bias current, IFMAIN\_BIAS\_OVERRIDE (Register 0x0301, Bits[3:0]), and a linearizing optimization current, IFLIN\_BIAS\_ OVERRIDE (Register 0x0302, Bits[3:0]). The linearization current generally maintains the same IP3 for a given IF frequency but may need to be adjusted for different IF frequencies.

#### DVGA

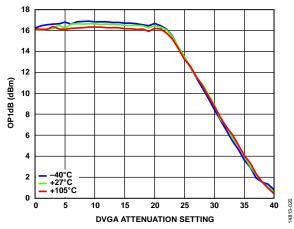

The ADRF6650 integrates a differential variable gain amplifier consisting of a differential, digitally controlled passive attenuator (DSA) followed by a DVGA. The total attenuation range is 43 dB, in 1 dB steps, with the first 12 dB of attenuation provided by the DVGA and the remaining 31 dB provided by the DSA. The 12 dB of attenuation from the DVGA has less than 1 dB degradation of the ADRF6650 noise figure for the entire 12 dB range. The OIP3 also remains nearly constant over that attenuation range, as shown in Figure 21. The input digitally controlled binary weighted attenuator has a 31 dB range in 1 dB steps. The noise figure for this attenuator increases 1 dB for each dB of attenuation of this 31 dB attenuation range.

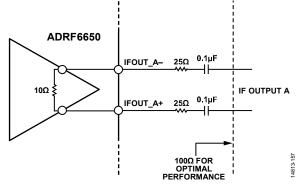

#### **Output Impedance and Matching**

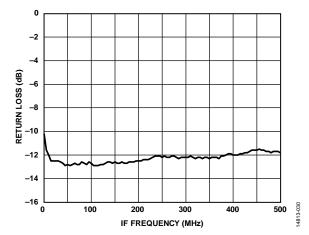

The differential output impedance of each channel of the ADRF6650 is 10  $\Omega$ . External series resistors are required to increase the output impedance for matching considerations, but reduce the maximum output power of the ADRF6650. A series resistor of 25  $\Omega$  on each differential leg of each output provides a –10 dB return loss for a 100  $\Omega$  differential load and the maximum output power.

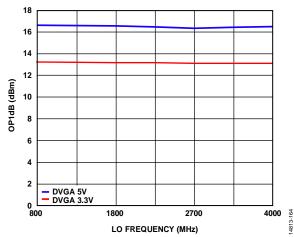

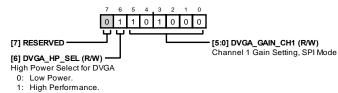

#### Power Supply and Common Mode

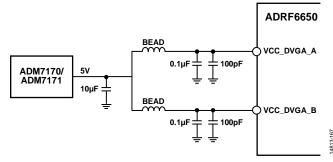

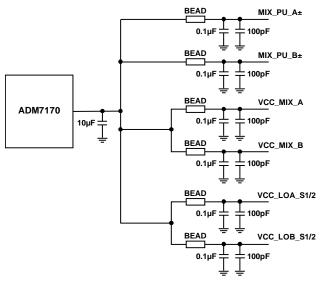

The DVGA in each channel of the ADRF6650 can be powered either at 3.3 V or 5.0 V through the VCC\_DVGA\_A and VCC\_ DVGA\_B pins. A 5.0 V supply provides increased performance, mainly in OIP3 and in OP1dB but results in increased power consumption. The current consumption of the DVGA is maintained at the same level for each power voltage (approximately 75 mA) and is controlled by DVGA\_5V\_SEL (Register 0x0103, Bit 7). If desired, the current can be reduced for lower power consumption and reduced performance. The performance mode select is controlled by DVGA\_HP\_SEL (Register 0x0104, Bit 6).

TheADRF6650 is also flexible in terms of input/output coupling. It can be ac-coupled or dc-coupled at the outputs within the specified output common-mode levels of 1.2 V to 2.8 V, depending on the supply voltage. The output commonmode voltage can be set by VCPL\_A and VCPL\_B, which allows the driving of an analog-to-digital converter (ADC) directly without external components. If no external output commonmode voltage is applied, the output common mode is  $V_{CC}/2$ .

#### **Gain Control Modes**

The attenuation of the DVGA can be controlled by several different modes:

- SPI mode through a dedicated register for each channel in the main SPI.

- Up/down mode through the serial gain control 2-wire SPI port for each channel.

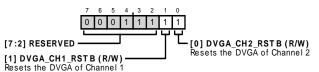

The mode is set by DVGA\_GAIN\_MODE (Register 0x0103, Bits[2:0]) as shown in Table 11. The attenuation setting at any configuration can be read from the ATTEN\_READBACK\_CH1 register (Register 0x003C) and ATTEN\_READBACK\_CH2 register (Register 0x003D) for Channel A and Channel B, respectively. When the gain control mode is changed between different modes, a reset needs to be issued through DVGA\_ CH1\_RSTB (Register 0x0021, Bit 1) and DVGA\_CH2\_RSTB (Register 0x0021, Bit 0) to the Channel A DVGA and Channel B DVGA, respectively. See the description details for the DVGA\_CH1\_RSTB and DVGA\_CH2\_RSTB registers.

#### Table 11. DVGA Gain Modes

| DVGA_GAIN_MODE<br>(Register 0x0103, Bits[2:0]) | DVGA Mode |

|------------------------------------------------|-----------|

| 01                                             | SPI       |

| 11                                             | Up/down   |

#### SPI Mode

In SPI mode, the DVGA gain is controlled by DVGA\_GAIN1 (Register 0x0104, Bits[5:0]) and DVGA\_GAIN2 (Register 0x0104, Bits[5:0]), as shown in Table 12.

#### Table 12. DVGA Attenuation Setting

| DVGA_GAIN_CH1 (Register 0x0104,<br>Bits[5:0]) and DVGA_GAIN_CH2<br>(Register 0x0105, Bits[5:0]) | Attenuation |

|-------------------------------------------------------------------------------------------------|-------------|

| 000000                                                                                          | 0           |

| 000001                                                                                          | 1           |

|                                                                                                 |             |

| 101010                                                                                          | 42          |

| 101011                                                                                          | 43          |

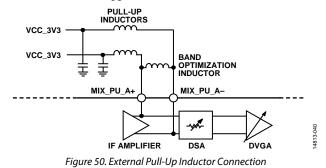

#### Up/Down Mode

The up/down interface reuses the RXx\_ATT\_DATA and RXx\_ ATT\_CLK pins to control the gain. Gain is increased by a clock pulse on RXx\_ATT\_CLK (rising edges) when RXx\_ATT\_DATA is low. Gain is decreased by a clock pulse on RXx\_ATT\_CLK when RXx\_ATT\_DATA is high. Reset is detected by a rising edge latching data having one polarity with the falling edge latching the opposite polarity. Reset results in minimum gain code 111111 (binary).

The step size is selectable via DVGA\_UPDN\_STEP (Register 0x0103, Bits[4:3]), as shown in Table 13. The default step size is 1 dB. The gain code count rails at the top and bottom of the control range.

#### Table 13. Up/Down Step Size

| DVGA_UPDN_STEP               |           |

|------------------------------|-----------|

| (Register 0x0103, Bits[4:3]) | Step Size |

| 00                           | 1         |

| 01                           | 2         |

| 10                           | 4         |

| 11                           | 8         |

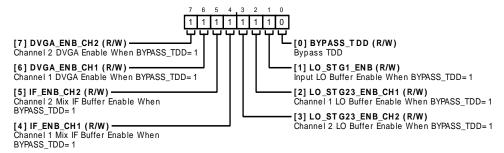

#### **TDD OPERATION**

The ADRF6650 provides two separate pins to control the channels (enable/disable) in TDD operation. When the TDD\_A (Pin 2) and TDD\_B (Pin 13) pins are pulled low, Channel A and Channel B are active, respectively. When TDD\_A and TDD\_B are pulled high, the channels are disabled.

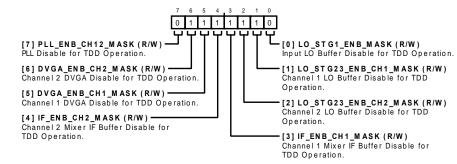

The ADRF6650 also provides TDD enable masks to enable/ disable certain blocks during TDD operation. The TDD enable masks select which blocks are disabled during TDD off time. The EN\_MASK register (Register 0x0102) includes the mask bits for the LO stages, the IF amplifiers, the DVGAs, and the PLL. When set to 1, the bits shown in Table 14 disable the related block during TDD off time. The enable mask bits for the LO Stage 23, the IF amplifiers, and the DVGA disable the related block (when set to 1) when either one of the TDD\_A and TDD\_B pins is set to high. Alternatively, the LO\_STG1\_ ENB\_MASK bit (Register 0x0102, Bit 0) disables the LO stage amplifier only when both TDD\_A and TDD\_B are high. In the same manner, the PLL\_ENB\_CH12\_MASK bit (Register 0x0102, Bit 7) disables the PLL/VCO only when both TDD\_A and TDD\_B are high.

#### Table 14. TDD Enable Mask Register (Register 0x0102)

| TDD Enable Mask Bit   | Default | Block                  |

|-----------------------|---------|------------------------|

| LO_STG1_ENB_MASK      | 0       | LO Stage 1             |

| LO_STG23_ENB_CH1_MASK | 1       | Channel A LO Stage 23  |

| LO_STG23_ENB_CH2_MASK | 1       | Channel B LO Stage 23  |

| IF_ENB_CH1_MASK       | 1       | Channel A IF amplifier |

| IF_ENB_CH2_MASK       | 1       | Channel B IF amplifier |

| DVGA_ENB_CH1_MASK     | 1       | Channel A DVGA         |

| DVGA_ENB_CH1_MASK     | 1       | Channel B DVGA         |

| PLL_ENB_CH12_MASK     | 0       | PLL                    |

#### LO GENERATION BLOCK

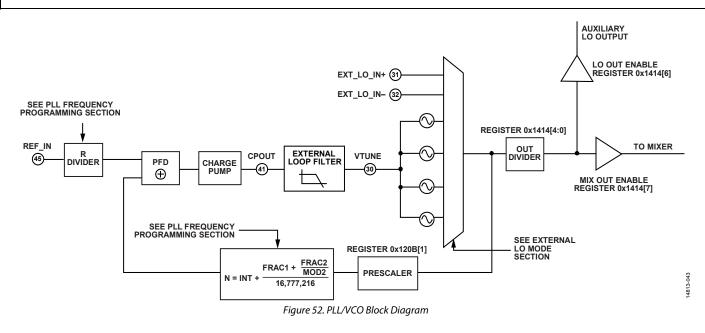

The ADRF6650 supports the use of both internal and external LO signals for the mixers. The internal LO is generated by an on-chip VCO, which is tunable over a frequency range of 4000 MHz to 8000 MHz. The output of the VCO is phase-locked to an external reference clock through a fractional-N PLL that is programmable through the SPI control registers. To produce LO signals over the 450 MHz to 2900 MHz frequency range to drive the mixers, the VCO outputs passes through an output divider. Alternatively, an external signal can be used to supply the LO signals to the mixers.

#### Internal LO Mode

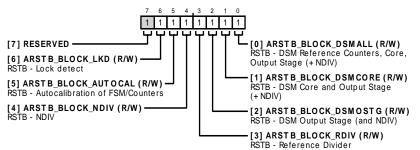

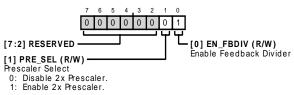

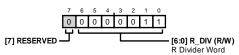

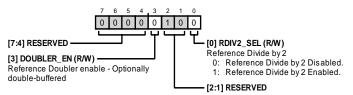

For internal LO mode, the ADRF6650 uses the on-chip PLL and VCO to synthesize the frequency of the LO signal. The PLL, shown in Figure 52, consists of a reference path, phase and frequency detector (PFD), charge pump, and a programmable integer divider with a prescaler. The reference path takes in a reference clock and divides it down by a value calculated with the R divider together with doubler bit and prescaler bit. Then the divided down reference signal passes to the PFD. The PFD compares this signal to the divided down signal from the VCO. The PFD sends an up/down signal to the charge pump if the VCO signal is slow/fast compared to the reference frequency. The charge pump sends a current pulse to the off-chip loop filter to increase or decrease the tuning voltage ( $V_{TUNE}$ ).

The ADRF6650 integrates a multicore VCO covering an octave range of 4 GHz to 8 GHz. The suitable VCO is selected with the autotune functionality built in the chip. After the user determines the necessary register values, a write to the INT\_L register (Register 0x1200) initiates the autotune process.

#### LO Frequency and Dividers

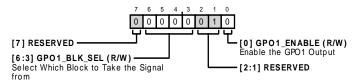

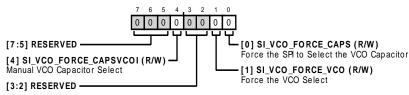

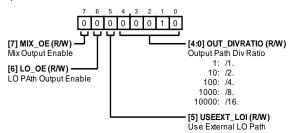

The signal originating from the VCO or the external LO inputs goes through a series of dividers before it is buffered to drive the mixer. The programmable divide by two stages divide the frequency of the incoming signal by 1, 2, 4, 8, and 16 before reaching to the mixers. The control bits (Register 0x1414, Bits[4:0]) needed to select the different LO frequency ranges are listed in Table 15.

| Tuble 151 Sulput Divide Ratio for Hequency Ranges               |       |                        |  |

|-----------------------------------------------------------------|-------|------------------------|--|

| LO Frequency OUT_DIVRATIO<br>(MHz) (Register 0x1414, Bits[4:0]) |       | VCO Frequency<br>(MHz) |  |

| 450 to 500                                                      | 10000 | LO × 16                |  |

| 500 to 1000                                                     | 01000 | LO × 8                 |  |

| 1000 to 2000                                                    | 00100 | $LO \times 4$          |  |

| 2000 to 2900                                                    | 00010 | $LO \times 2$          |  |

#### Table 15. Output Divide Ratio for Frequency Ranges

### **Data Sheet**

#### PLL Frequency Programming

The INT, FRAC1, FRAC2, and MOD values, in conjunction with the R counter, make it possible to generate output frequencies that are spaced by fractions of the PFD frequency ( $f_{PFD}$ ). Calculate the VCO frequency (VCOOUT) by

$$VCOOUT = f_{PFD} \times N$$

(1)

where:

*VCOOUT* is the output frequency of the VCO (without using the output divider).

$f_{PFD}$  is the frequency of the phase frequency detector. N is the desired value of the feedback counter.

Calculate fPFD by

$$f_{PFD} = REF_{IN} \times ((1+D)/(R \times (1+T)))$$

(2)

where:

*REF*<sub>IN</sub> is the reference input frequency.

*D* is the reference doubler bit (Register 0x120E, Bit 3). *R* is the preset divide ratio of the binary 7-bit programmable reference counter (1 to 255) (Register 0x120C, Bits[6:0]). *T* is the reference divide by 2 bit (0 or 1) (Register 0x120E, Bit 0).

N comprises

$$N = INT + \frac{FRAC1 + \frac{FRAC2}{MOD}}{16,777,216}$$

(3)

where:

*INT* is the 16-bit integer value (23 to 32,767 for the 4/5 prescaler, 75 to 65,535 for the 8/9 prescaler) referenced with Register 0x1201 and Register 0x1200.

*FRAC1* is the 24-bit numerator of the primary modulus (0 to 16,777,215) with Register 0x1204, Register 0x1203, and Register 0x1202.

*FRAC2* is the numerator of the 14-bit auxiliary modulus (0 to 16,383) with Register 0x1234, Bits[5:0] and Register 0x1233. *MOD* is the programmable, 14-bit auxiliary fractional modulus (2 to 16,383), referenced with Register 0x1209, Bits[5:0] and Register 0x1208.

Equation 3 results in a very fine frequency resolution with no residual frequency error. To apply this formula, take the following steps:

- 1. Calculate N by VCOOUT/ $f_{\text{PFD}}$ . The integer value of this number forms INT.

- 2. Subtract the INT value from the full N value.

- 3. Multiply the remainder by 2<sup>24</sup>. The integer value of this number forms FRAC1.

- 4. Calculate MOD based on the channel spacing  $(f_{CHSP})$  by

$$MOD = f_{PFD}/GCD(f_{PFD}, f_{CHSP})$$

where:

GCD( $f_{PFD}$ ,  $f_{CHSP}$ ) is the greatest common divider of the PFD frequency and the channel spacing frequency.  $f_{CHSP}$  is the desired channel spacing frequency. 5. Calculate FRAC2 by the following equation:

$$FRAC2 = (N - INT) \times 224 - FRAC1) \times MOD$$

(5)

The FRAC2 and MOD fraction results in outputs with zero frequency error for channel spacings when

$$f_{PFD}/\text{GCD}(f_{PFD}/f_{CHSP}) < 16,383 \tag{6}$$

where:

$f_{PFD}$  is the frequency of the phase frequency detector. GCD is a greatest common denominator function.  $f_{CHSP}$  is the desired channel spacing frequency.

After determining the necessary register values for PLL, also set the SD\_EN\_FRAC0 bit (Register 0x122A, Bit 4) to 1.

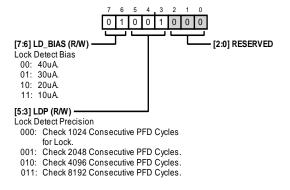

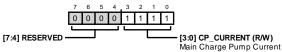

It is recommended to set the charge pump current to be 2.4 mA by setting the CP\_CURRENT bit (Register 0x122E, Bits[3:0]) to 7. Together with a 20 kHz loop filter, the charge pump current setting results in an optimized performance.

#### **Bleed Setting**

The PFD circuitry compares the PFD and divided down VCO signals. The ADRF6650 employs a bleed circuit to put the PFD circuit in the linear operation region. The bleed circuit introduces a delay to the incoming PFD signal, indicated as PFD\_OFFSET in Equation 7. Calculate the bleed current, BICP (Register 0x122F, Bits[7:0]), from the desired PFD\_OFFSET, as shown in Equation 7.

$$BICP = \text{integer}(\text{round}(\text{float}(I_{CP} \times PFD_OFFSET \times f_{PFD})/960)/255))$$

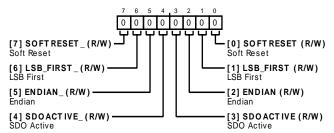

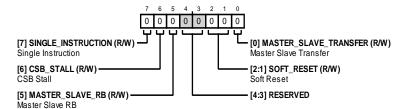

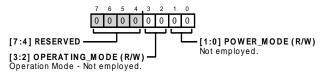

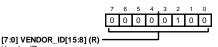

(7)