# Programmable Low Voltage 1:10 LVDS Clock Driver

Data Sheet ADN4670

#### **FEATURES**

Low output skew <30 ps (typical)

Distributes one differential clock input to 10 LVDS clock

outputs

Programmable—one of two differential clock inputs can be selected (CLKO, CLK1) and individual differential clock outputs enabled/disabled

Signaling rate up to 1.1 GHz (typical)

2.375 V to 2.625 V power supply range

±100 mV differential input threshold

Input common-mode range from rail-to-rail

I/O pins fail-safe during power-down: V<sub>DD</sub> = 0 V

Available in 32-lead LFCSP and LQFP packages

Industrial operating temperature range: -40°C to +85°C

#### **APPLICATIONS**

**Clock distribution networks**

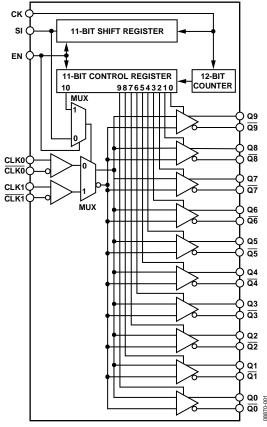

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

## **GENERAL DESCRIPTION**

The ADN4670 is a low voltage differential signaling (LVDS) clock driver that expands a differential clock input signal to 10 differential clock outputs. The device is programmable using a simple serial interface, so that one of two clock inputs can be selected (CLK0/CLK0 or CLK1/CLK1) and any of the differential outputs (Q0/Q0 to Q9/Q9) can be enabled or disabled (tristated). The ADN4670 is designed for use in 50  $\Omega$  transmission line environments.

When the enable input EN is high, the device may be programmed by clocking 11 data bits into the shift register. The

first 10 bits determine which outputs are enabled (0 = disabled, 1 = enabled), while the  $11^{th}$  bit selects the clock input (0 = CLK0, 1 = CLK1). A  $12^{th}$  clock pulse transfers data from the shift register to the control register.

The ADN4670 is fully specified over the industrial temperature range and is available in a 32-lead LFCSP and LQFP packages.

# **TABLE OF CONTENTS**

|   | reatures                             |

|---|--------------------------------------|

|   |                                      |

| 1 | Applications                         |

| 1 | Functional Block Diagram             |

| 1 | General Description                  |

| 2 | Revision History                     |

| 3 | Specifications                       |

| 3 | Jitter Characteristics               |

| 4 | LVDS Switching Characteristics       |

|   | Programming Logic AC Characteristics |

| 3 | Revision History                     |

| Absolute Maximum Ratings                    | 6 |

|---------------------------------------------|---|

| ESD Caution                                 | 6 |

| Pin Configuration and Function Descriptions | 7 |

| Theory of Operation                         | 8 |

| LVDS Reciever Input Termination             | 8 |

| Fail-Safe Operation                         | 8 |

| Programming                                 | 8 |

| Outline Dimensions                          | 9 |

| Ordering Guide                              | 9 |

## **REVISION HISTORY**

1/12—Rev. 0 to Rev. A

| Added LQFP Package         | . Throughout |

|----------------------------|--------------|

| Updated Outline Dimensions | 9            |

| Changes to Ordering Guide  | 9            |

4/10—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\text{DD}}$  = 2.375 V to 2.625 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}\text{, unless otherwise noted.}$

Table 1.

| Parameter                                      | Symbol                            | Min                 | Тур  | Max                     | Unit | Conditions/Comments                                                        |

|------------------------------------------------|-----------------------------------|---------------------|------|-------------------------|------|----------------------------------------------------------------------------|

| RECEIVER                                       |                                   |                     |      |                         |      |                                                                            |

| Input High Threshold at CLK0/CLK0 or CLK1/CLK1 | $V_{TH}$                          |                     |      | 100                     | mV   |                                                                            |

| Input Low Threshold at CLK0/CLK0 or CLK1/CLK1  | $V_{TL}$                          | -100                |      |                         | mV   |                                                                            |

| Differential Input Voltage                     | V <sub>ID</sub>                   | 200                 |      |                         | mV   |                                                                            |

| Input Common-Mode Voltage                      | V <sub>IC</sub>                   | 0.5 V <sub>ID</sub> |      | $V_{DD} - 0.5  V_{ID} $ |      |                                                                            |

| Input Current at CLK0, CLK0, CLK1, or CLK1     | I <sub>IH</sub> , I <sub>IL</sub> | -5                  |      | +5                      | μΑ   | $V_I = V_{DD}$ or $V_I = 0$ V                                              |

| Input Capacitance                              | Cı                                |                     | 3    |                         | рF   | $V_I = V_{DD}$ or GND                                                      |

| DRIVER                                         |                                   |                     |      |                         |      |                                                                            |

| Differential Output Voltage                    | V <sub>OD</sub>                   | 250                 | 450  | 600                     | mV   | $R_L = 100 \Omega$                                                         |

| V <sub>OD</sub> Magnitude Change               | $\Delta V_{\text{OD}}$            |                     |      | 50                      | mV   |                                                                            |

| Offset Voltage                                 | Vos                               | 0.95                | 1.2  | 1.45                    | ٧    | -40°C to +85°C                                                             |

| Vos Magnitude Change                           | $\Delta V_{OS}$                   |                     |      | 350                     | mV   |                                                                            |

| Output Short Circuit Current                   | los                               |                     |      | -20                     | mA   | $V_O = 0 V$                                                                |

|                                                |                                   |                     |      | 20                      | mA   | $ V_{OD}  = 0 V$                                                           |

| Reference Output Voltage                       | $V_{BB}$                          | 1.15                | 1.25 | 1.35                    | V    | $V_{DD} = 2.5 \text{ V, I} = -100 \mu\text{A}$                             |

| Output Capacitance                             | Co                                |                     | 3    |                         | рF   | $V_O = V_{DD}$ or GND                                                      |

| SUPPLY CURRENT                                 |                                   |                     |      |                         |      |                                                                            |

| Supply Current                                 | $I_{DD}$                          |                     |      | 35                      | mA   | All outputs tristated, $f = 0$ Hz                                          |

|                                                |                                   |                     | 100  | 110                     | mA   | All outputs enabled and loaded, $R_L = 100 \Omega$ , $f = 100 MHz$         |

|                                                |                                   |                     | 150  | 160                     | mA   | All outputs enabled and loaded, $R_L = 100 \Omega$ , $f = 800 \text{ MHz}$ |

## **JITTER CHARACTERISTICS**

Table 2.

| Parameter                                                                           | Symbol                   | Min            | Тур | Max | Unit               | Conditions/Comments                           |

|-------------------------------------------------------------------------------------|--------------------------|----------------|-----|-----|--------------------|-----------------------------------------------|

| Additive Phase Jitter from Input to LVDS Outputs, Q3 and $\overline{\overline{Q3}}$ | t <sub>JITTER LVDS</sub> | itter LVDs 281 |     |     | f <sub>s</sub> rms | 12 kHz to 5 MHz, f <sub>OUT</sub> = 30.72 MHz |

|                                                                                     |                          |                | 111 |     | fs rms             | 12 kHz to 20 MHz, fouт = 125 MHz              |

## LVDS SWITCHING CHARACTERISTICS

$V_{DD}$  = 2.375 V to 2.625 V; all specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 3.

| Parameter                             | Symbol              | Min | Тур  | Max <sup>1</sup> | Unit | Conditions/Comments                                                                                     |

|---------------------------------------|---------------------|-----|------|------------------|------|---------------------------------------------------------------------------------------------------------|

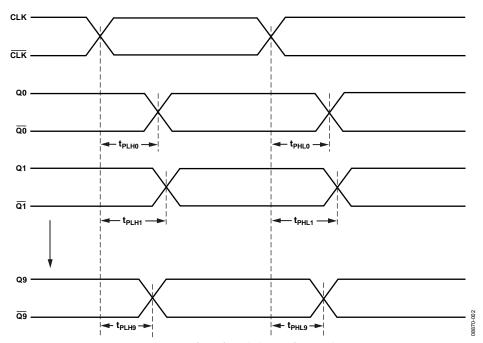

| Propagation Delay Low to High         | t <sub>PLHx</sub>   |     | 2    | 3                | ns   | From CLK0/ $\overline{\text{CLK0}}$ or CLK1/ $\overline{\text{CLK1}}$ to any Qx/ $\overline{\text{Qx}}$ |

| Propagation Delay High to Low         | t <sub>PHLx</sub>   |     | 2    | 3                | ns   | From CLK0/ $\overline{\text{CLK0}}$ or CLK1/ $\overline{\text{CLK1}}$ to any Qx/ $\overline{\text{Qx}}$ |

| Duty Cycle                            | t <sub>DUTY</sub>   | 45  |      | 55               | %    | From CLK0/ $\overline{\text{CLK0}}$ or CLK1/ $\overline{\text{CLK1}}$ to any Qx/ $\overline{\text{Qx}}$ |

| Output Skew <sup>2</sup>              | t <sub>SK(O)</sub>  |     | 30   |                  | ps   | Any Qx/Qx                                                                                               |

| Pulse Skew³                           | t <sub>SK(P)</sub>  |     |      | 50               | ps   | Any Qx/Qx                                                                                               |

| Part-to-Part Output Skew <sup>4</sup> | t <sub>SK(PP)</sub> |     |      | 600              | ps   | Any Qx/Qx                                                                                               |

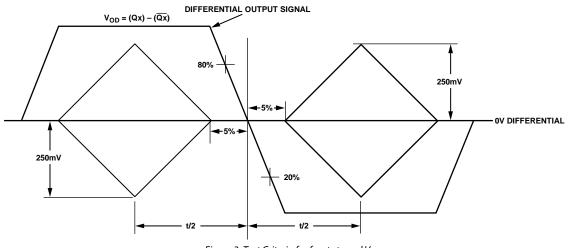

| Output Rise Time                      | t <sub>r</sub>      |     |      | 350              | ps   | Any Qx/ $\overline{Qx}$ , 20% to 80%, R <sub>L</sub> = 100 $\Omega$ C <sub>L</sub> = 5 pF               |

| Output Fall Time                      | t <sub>f</sub>      |     |      | 350              |      | Any Qx/ $\overline{Qx}$ , 80% to 20%, R <sub>L</sub> = 100 $\Omega$ C <sub>L</sub> = 5 pF               |

| Maximum Input Frequency               | f <sub>CLK</sub>    | 900 | 1100 |                  | MHz  | From CLK0/CLK0 or CLK1/ CLK1 to any Qx/Qx                                                               |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization.

<sup>&</sup>lt;sup>3</sup> Pulse skew is defined as the magnitude of the maximum difference between t<sub>PLH</sub> and t<sub>PHL</sub> for any channel of a device, that is, |t<sub>PHLx</sub> - t<sub>HLPx</sub>|.

<sup>4</sup> Part-to-part output skew is defined as the difference between the largest and smallest values of T<sub>PLHx</sub> across multiple devices or the difference between the largest and smallest values of T<sub>PHLx</sub> across multiple devices, whichever of the two is greater.

Figure 2. Waveforms for Calculation of  $t_{SK(O)}$  and  $t_{SK(PP)}$

<sup>&</sup>lt;sup>2</sup> Output skew is defined as the difference between the largest and smallest values of T<sub>PLHx</sub> within a device or the difference between the largest and smallest values of T<sub>PHLx</sub> within a device, whichever of the two is greater.

Figure 3. Test Criteria for  $f_{CLK}$ ,  $t_r$ ,  $t_f$ , and  $V_{OD}$

## **PROGRAMMING LOGIC AC CHARACTERISTICS**

$V_{\text{DD}}$  = 2.375 V to 2.625 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

Table 4.

| 1 aute 4.                                 |                  |     |     |     |      |                                                                   |

|-------------------------------------------|------------------|-----|-----|-----|------|-------------------------------------------------------------------|

| Parameter                                 | Symbol           | Min | Тур | Max | Unit | Conditions/Comments                                               |

| Maximum Frequency at CK Input             | f <sub>MAX</sub> | 100 | 150 |     | MHz  |                                                                   |

| Setup Time, SI to CK                      | t <sub>su</sub>  |     |     | 2   | ns   | Time for which SI must not change before the CK 0-to-1 transition |

| Hold Time, CK to SI                       | t <sub>H</sub>   |     |     | 1.5 | ns   | Time for which SI must not change after the CK 0-to-1 transition  |

| EN to CK Removal Time                     | tremoval         |     |     | 1.5 | ns   | Removal time, EN to CK                                            |

| Start-Up Time                             | <b>t</b> STARTUP |     |     | 1   | μs   | Start-up time after disable through SI                            |

| Minimum Clock Pulse Width                 | tw               | 3   |     |     | ns   |                                                                   |

| Logic Input High Level                    | V <sub>IH</sub>  | 2   |     |     | V    | $V_{DD} = 2.5 \text{ V}$                                          |

| Logic Input Low Level                     | V <sub>IL</sub>  |     |     | 8.0 | V    | $V_{DD} = 2.5 \text{ V}$                                          |

| High Level Logic Input Current, CK        | I <sub>IH</sub>  | -5  |     | +5  | μΑ   | $V_{I} = V_{DD}$                                                  |

| High Level Logic Input Current, SI and EN |                  | +10 |     | -30 | μΑ   | $V_{I} = V_{DD}$                                                  |

| Low Level Logic Input Current, CK         | I <sub>IL</sub>  | -10 |     | +30 | μΑ   | $V_i = GND$                                                       |

| Low Level Logic Input Current, SI and EN  |                  | -5  |     | +5  | μΑ   | $V_1 = GND$                                                       |

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 3.

| Parameter                             | Rating                                                             |

|---------------------------------------|--------------------------------------------------------------------|

| V <sub>CC</sub> to GND                | -0.3 V to +2.8 V                                                   |

| Input Voltage to GND                  | $-0.2 \mathrm{V}$ to $(\mathrm{V}_{\mathrm{DD}} + 0.2) \mathrm{V}$ |

| Output Voltage to GND                 | $-0.2 \mathrm{V}$ to $(\mathrm{V}_{\mathrm{DD}} + 0.2) \mathrm{V}$ |

| Operating Temperature Range           |                                                                    |

| Industrial                            | −40°C to +85°C                                                     |

| Storage Temperature Range             | −65°C to +150°C                                                    |

| Junction Temperature (T₁ max)         | 150°C                                                              |

| Power Dissipation                     | $(T_J \max - T_A)/\theta_{JA}$                                     |

| LFCSP Package                         |                                                                    |

| $\theta_{JA}$ Thermal Impedance       | 32.5°C/W                                                           |

| LQFP Package                          |                                                                    |

| $\theta_{JA}$ Thermal Impedance       | 59°C/W                                                             |

| Reflow Soldering Peak Temperature     |                                                                    |

| Pb-Free                               | 260°C ± 5°C                                                        |

| ESD (Human Body Model, 1.5 kΩ 100 pF) | 4000 V                                                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

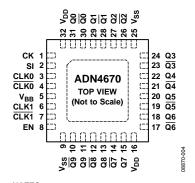

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

THE EXPOSED PAD CAN BE CONNECTED TO GROUND OR LEFT FLOATING.

Figure 4. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.                                   | Mnemonic        | Description                                                                                                                                                                                                                                                                                |

|-------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                         | CK              | Programming Clock. Programming data is clocked in on a low-to-high transition at this input. If left open-circuit, it is pulled high by a 120 k $\Omega$ resistor.                                                                                                                         |

| 2                                         | SI              | Serial Data Input. This is the input for programming data. If left open-circuit, it is pulled low by a 120 k $\Omega$ resistor.                                                                                                                                                            |

| 3                                         | CLK0            | Noninverting Differential Clock Input 0.                                                                                                                                                                                                                                                   |

| 4                                         | CLK0            | Inverting Differential Clock Input 0.                                                                                                                                                                                                                                                      |

| 5                                         | $V_{BB}$        | Reference Voltage Output.                                                                                                                                                                                                                                                                  |

| 6                                         | CLK1            | Noninverting Differential Clock Input 1.                                                                                                                                                                                                                                                   |

| 7                                         | CLK1            | Inverting Differential Clock Input 1.                                                                                                                                                                                                                                                      |

| 8                                         | EN              | Active-High Enable Input. When this input is high, programming is enabled. If left open-circuit, it is pulled low by a 120 k $\Omega$ resistor.                                                                                                                                            |

| 9, 25                                     | $V_{SS}$        | Device Ground.                                                                                                                                                                                                                                                                             |

| 10, 12, 14, 17, 19,<br>21, 23, 26, 28, 30 | Q9 to Q0        | Inverted Clock Output. When the differential input voltage is between CLKx and $\overline{\text{CLKx}} > 100 \text{ mV}$ , this output sinks current. When the differential input voltage is between CLKx and $\overline{\text{CLKx}} < -100 \text{ mV}$ , this output sources current.    |

| 11, 13, 15, 18, 20,<br>22, 24, 27, 29, 31 | Q9 to Q0        | Noninverted Clock Output. When the differential input voltage is between CLKx and $\overline{\text{CLKx}} > 100 \text{ mV}$ , this output sources current. When the differential input voltage is between CLKx and $\overline{\text{CLKx}} < -100 \text{ mV}$ , this output sinks current. |

| 16, 32                                    | $V_{\text{DD}}$ | Power Supply Input. This part can be operated from 2.375 V to 2.625 V.                                                                                                                                                                                                                     |

## THEORY OF OPERATION

The ADN4670 is a clock driver/expander for low voltage differential signaling (LVDS). It takes a differential clock signal of typically 350 mV and expands it to 10 differential clock outputs with very low skew (typically < 30 ps). The device receives a differential current signal from a source such as a twisted pair cable, which develops a voltage of typically  $\pm 350$  mV across a 100  $\Omega$  terminating resistor. This signal passes via a differential multiplexer to 10 drivers that each output a differential current signal.

The device is programmable using a simple serial interface. One of two differential clock inputs (CLK0/CLK0 or CLK1/ $\overline{\text{CLK1}}$ ), can be selected and any of the differential outputs (Q0/ $\overline{\text{Q0}}$  to Q9/ $\overline{\text{Q9}}$ ) can be enabled or disabled.

## LVDS RECIEVER INPUT TERMINATION

Terminate the clock inputs with 100  $\Omega$  resistors from CLK0 to  $\overline{\text{CLK0}}$  and CLK1 to  $\overline{\text{CLK1}}$ , placed as close as possible to the input pins.

## **FAIL-SAFE OPERATION**

In power-down mode ( $V_{\rm DD}$  = 0 V), the ADN4670 has fail-safe input and output pins. In power-on mode, fail-safe biasing can be achieved by connecting 10 k $\Omega$  pull-up resistors from CLK0 and CLK1 to  $V_{\rm DD}$  and 10 k $\Omega$  pull-down resistors from  $\overline{CLK0}$  and  $\overline{CLK1}$  to GND.

**PROGRAMMING**

Three control inputs are provided for programming the ADN4670. EN is the enable input, which allows programming when high, SI is the serial data input, and CK is the serial clock input, which clocks data into the device on a low-to-high clock transition. Each of these inputs has an internal pull-up or pull-down resistor of 120 k $\Omega$ . EN and SI are pulled low if left open-circuit while CK is pulled high.

The default condition if these inputs are left open-circuit is that all outputs are enabled, and the state of SI selects the inputs  $(0 = CLK0/\overline{CLK0})$ ,  $1 = CLK1/\overline{CLK1}$ . This is the standard operating mode for which no programming of the device is required.

Programming is enabled by taking EN high. The data on SI is then clocked into the device on each 0-to-1 transition of CK. Data on SI must be stable for the setup time ( $t_{SU}$ ) before the clock transition and remain stable for the hold time ( $t_{H}$ ) after the clock transition. To program the device, 11 bits of data are needed, starting with Bit 0, which enables or disables outputs Q9/Q9, through to Bit 10, which selects either CLK0/CLK0 or CLK1/CLK1 as the inputs. A  $12^{th}$  clock pulse is then required to transfer data from the shift register to the control register.

A low-to-high transition on EN resets the control register and the next 12 CK pulses are programmed.

**Table 5. Control Logic Truth Table**

| СК | EN | SI | CLK0 | CLK0 | CLK1 | CLK1 | Q0 to Q9 | Q0 to Q9 |

|----|----|----|------|------|------|------|----------|----------|

| L  | L  | L  | L    | Н    | X    | Χ    | L        | Н        |

| L  | L  | L  | Н    | L    | Χ    | X    | Н        | L        |

| L  | L  | L  | Open | Open | Х    | Χ    | L        | Н        |

| L  | L  | Н  | X    | X    | L    | Н    | L        | Н        |

| L  | L  | Н  | Χ    | X    | Н    | L    | Н        | L        |

| _L | L  | Н  | Χ    | Χ    | Open | Open | L        | Н        |

## **Table 6. State Machine Inputs**

| EN | SI | CK       | Output                                                                                   |

|----|----|----------|------------------------------------------------------------------------------------------|

| L  | L  | Χ        | Default state with all outputs enabled, CLKO selected, and the control register disabled |

| L  | Н  | Χ        | All outputs enabled, CLK1 selected, and the control register disabled                    |

| Н  | L  | 1        | First stage stores low, other stage stores data of previous stage                        |

| Н  | Н  | <b>↑</b> | First stage stores high, other stage stores data of previous stage                       |

| L  | Χ  | Χ        | Reset the state machine, control register, and shift register                            |

## **Table 7. Serial Input Sequence**

| Bit 10  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| CLK_SEL | Q0    | Q1    | Q2    | Q3    | Q4    | Q5    | Q6    | Q7    | Q8    | Q9    |

## **Table 8. Control Register**

| Bit 10 | Bit[9:0] | Qx[9:0]          |

|--------|----------|------------------|

| L      | Н        | CLK0             |

| Н      | Н        | CLK1             |

| Χ      | L        | Outputs disabled |

## **OUTLINE DIMENSIONS**

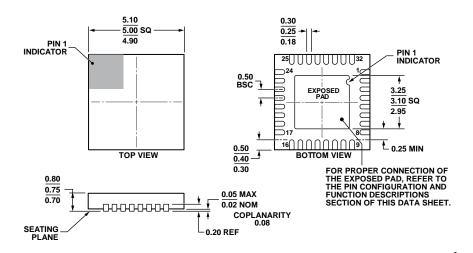

#### COMPLIANT TO JEDEC STANDARDS MO-220-WHHD.

Figure 5. 32-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 5 mm × 5 mm Body, Very Very Thin Quad (CP-32-7) Dimensions shown in millimeters

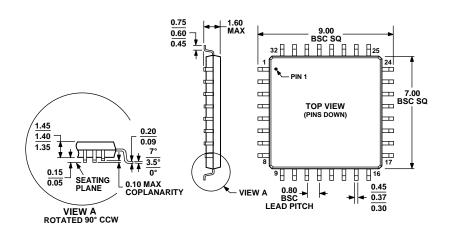

## COMPLIANT TO JEDEC STANDARDS MS-026-BBA

Figure 6. 32-Lead Low Profile Quad Flat Package [LQFP] (ST-32-2) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option |

|--------------------|-------------------|--------------------------------------------------|----------------|

| ADN4670BCPZ        | -40°C to +85°C    | 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-32-7        |

| ADN4670BCPZ-REEL7  | -40°C to +85°C    | 32-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-32-7        |

| ADN4670BSTZ        | -40°C to +85°C    | 32-Lead Low Profile Quad Flat Package [LQFP]     | ST-32-2        |

| ADN4670BSTZ-REEL7  | -40°C to +85°C    | 32-Lead Low Profile Quad Flat Package [LQFP]     | ST-32-2        |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

# **NOTES**

# **NOTES**

**NOTES**

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

ADN4670BCPZ ADN4670BCPZ-REEL7 ADN4670BSTZ ADN4670BSTZ-REEL7