# 24 GHz, ISM Band, Multichannel FMCW Radar Transmitter

Data Sheet ADF5902

#### **FEATURES**

24 GHz to 24.25 GHz VCO (industrial, scientific, and medical (ISM) radio band)

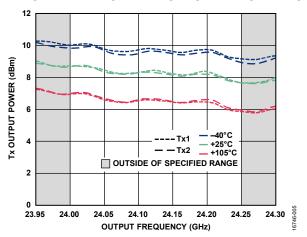

2-channel 24 GHz power amplifier with 8 dBm output

Single-ended outputs

2-channel muxed outputs with mute function

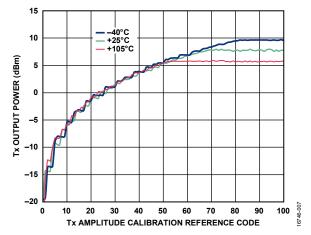

**Programmable output power**

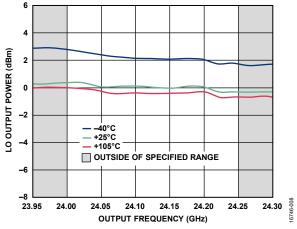

LO output buffer

RF frequency range: 24 GHz to 24.25 GHz

Power control detector

**Auxiliary 8-bit ADC**

High and low speed FMCW ramp generation

25-bit fixed modulus allows subhertz frequency resolution

PFD frequencies up to 110 MHz

Normalized phase noise floor of -222 dBc/Hz

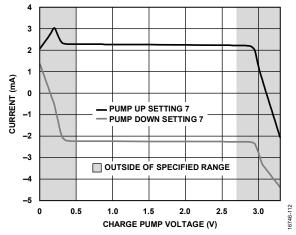

Programmable charge pump currents

±5°C temperature sensor

4-wire SPI

**ESD** performance

HBM: 2000 V CDM: 250 V

Qualified for automotive applications

#### **APPLICATIONS**

Automotive radars Industrial radars

Microwave radar sensors

#### **GENERAL DESCRIPTION**

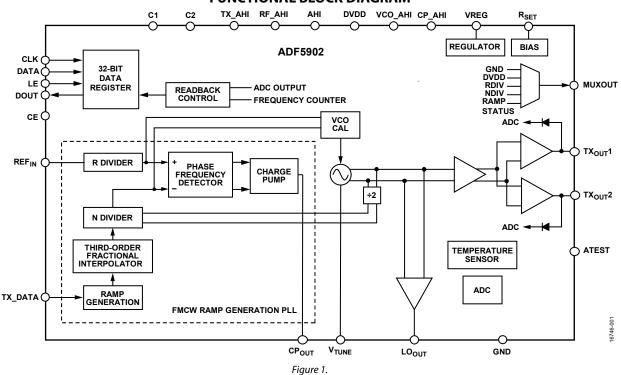

The ADF5902 is a 24 GHz transmitter (Tx) monolithic microwave integrated circuit (MMIC) with an on-chip, 24 GHz voltage controlled oscillator (VCO). The VCO features a fractional-N frequency synthesizer with waveform generation capability with programmable grid array (PGA) and dual transmitter channels for radar systems. The on-chip, 24 GHz VCO generates the 24 GHz signal for the two transmitter channels and the local oscillator (LO) output. Each transmitter channel contains a power control circuit. There is also an on-chip temperature sensor.

Control of all the on-chip registers is through a simple, 4-wire serial peripheral interface (SPI).

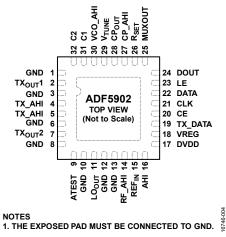

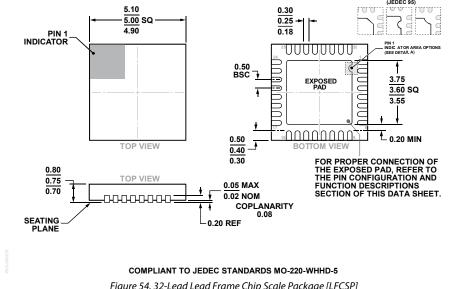

The ADF5902 comes in a compact, 32-lead, 5 mm  $\times$  5 mm LFCSP package.

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

**Data Sheet**

# **ADF5902**

# **TABLE OF CONTENTS**

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1            |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1            |

| Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1            |

| Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2            |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3            |

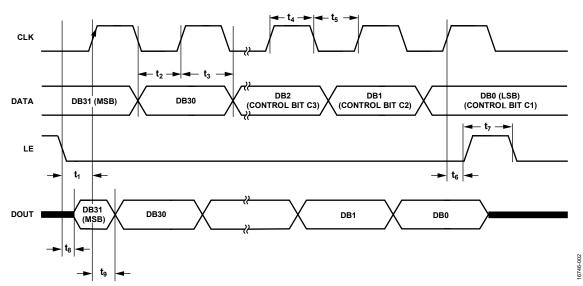

| Timing Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5            |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <del>6</del> |

| Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6            |

| ESD Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <i>6</i>     |

| Pin Configuration and Function Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7            |

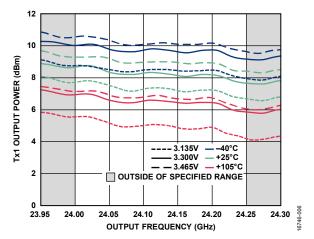

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9            |

| Theory of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11           |

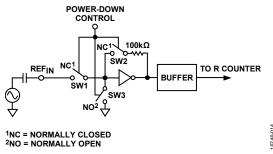

| Reference Input Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11           |

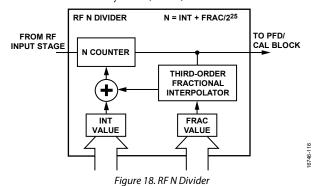

| RF INT Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11           |

| INT, FRAC, and R Relationship                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11           |

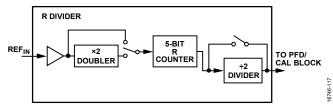

| R Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11           |

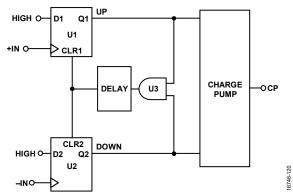

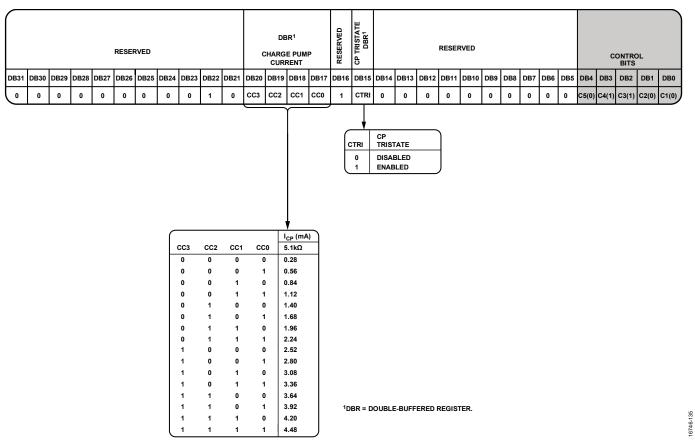

| PFD and Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11           |

| Input Shift Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11           |

| Program Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12           |

| Register Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13           |

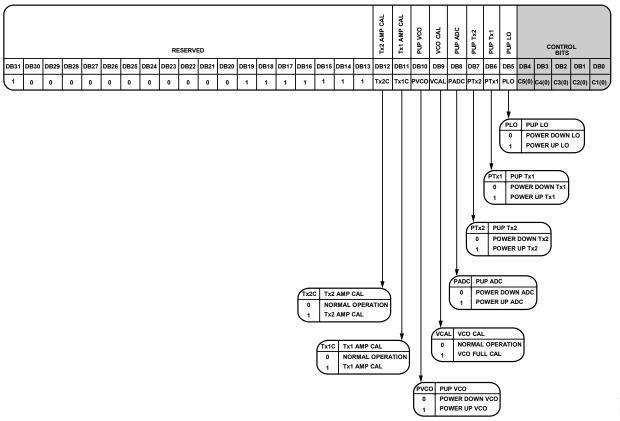

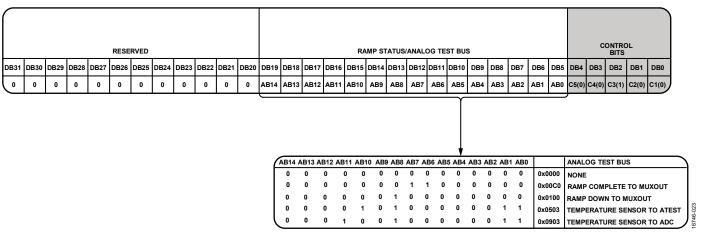

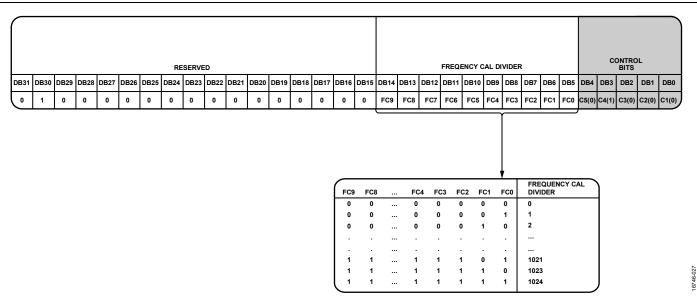

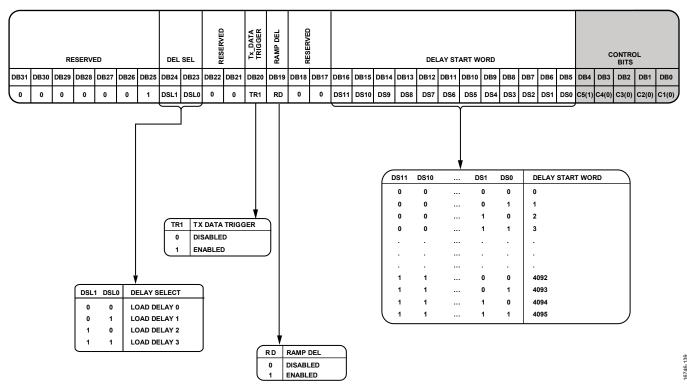

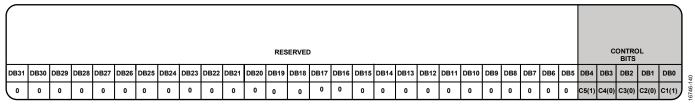

| Register 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16           |

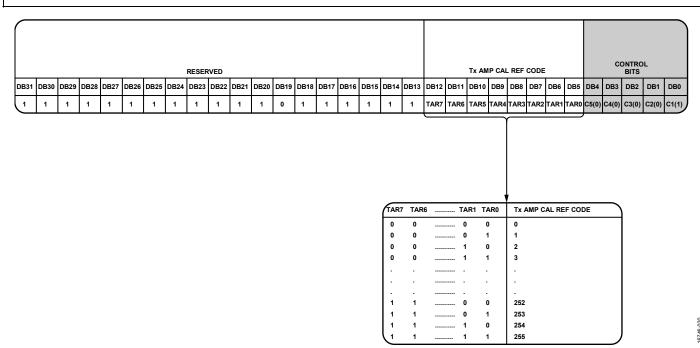

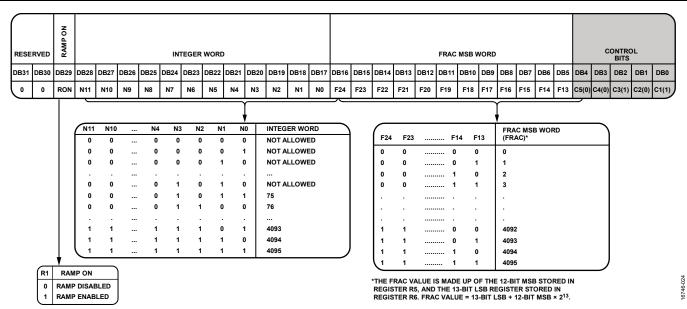

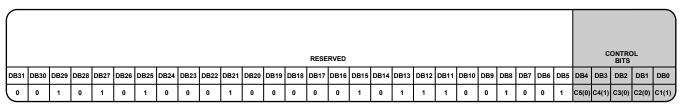

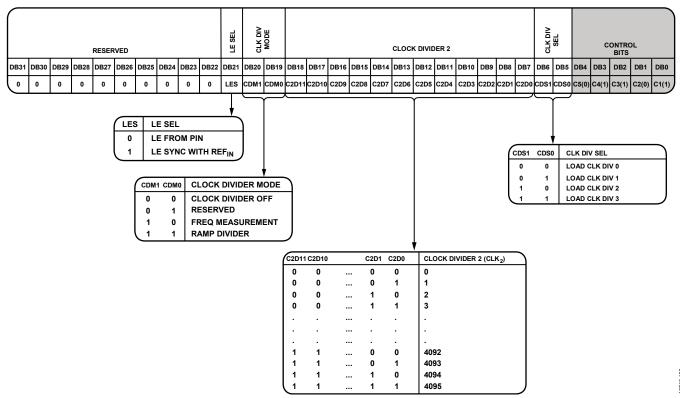

| Register 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17           |

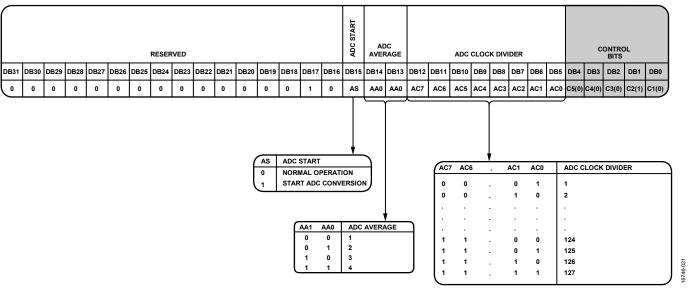

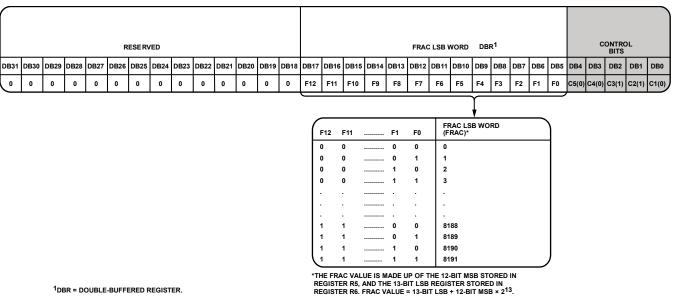

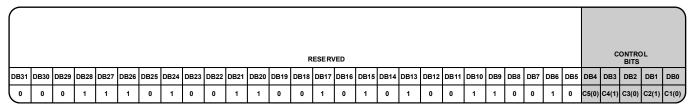

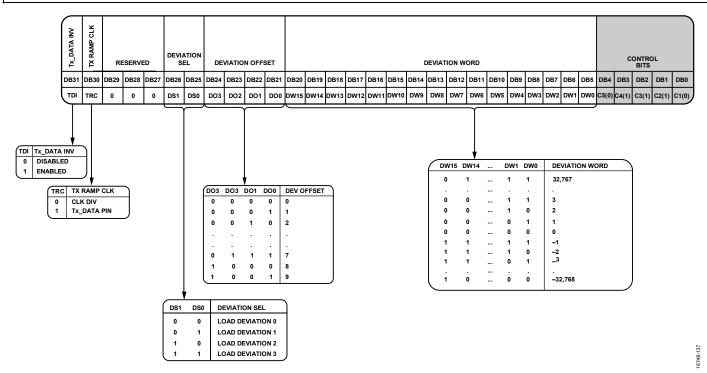

| Register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18           |

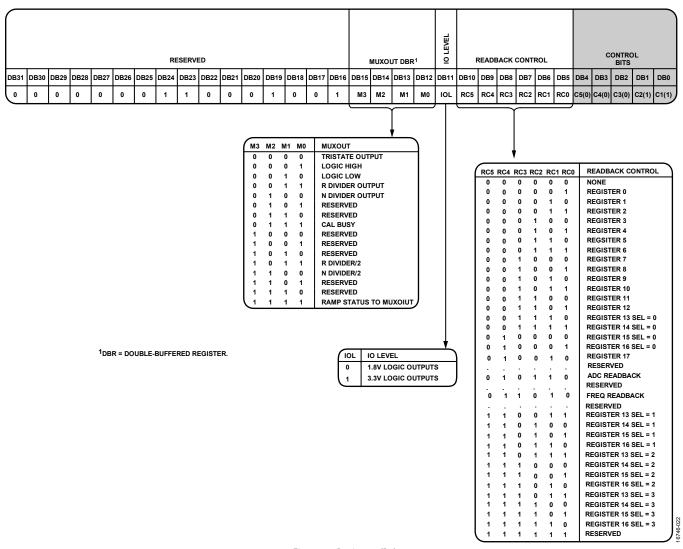

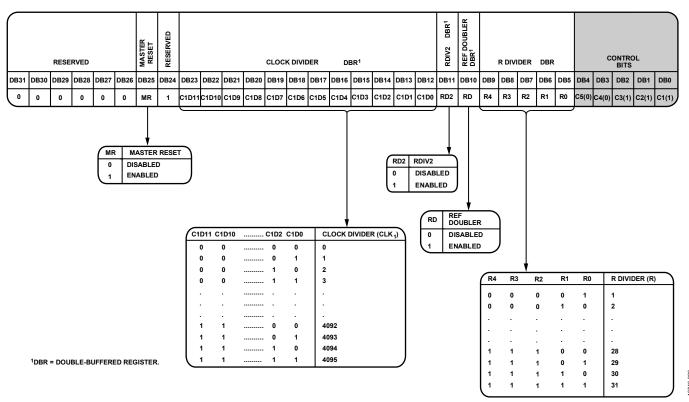

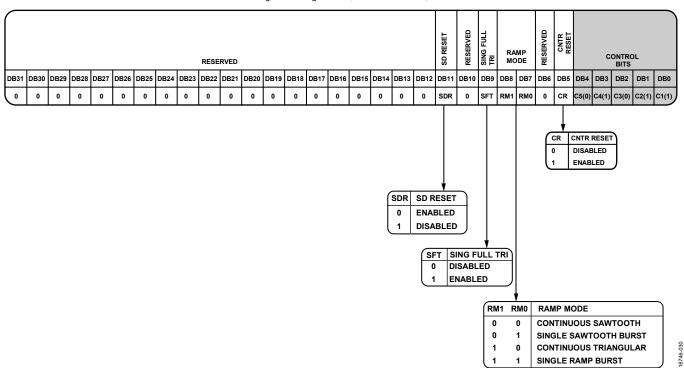

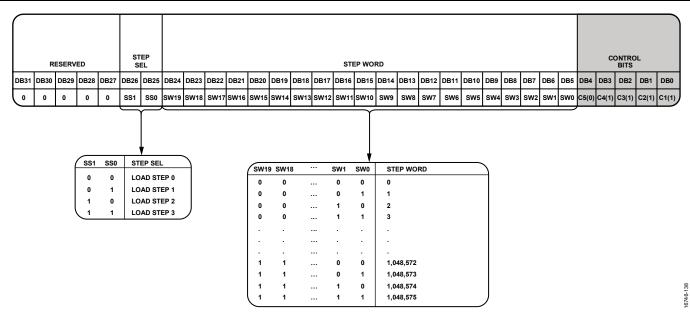

| Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19           |

| Register 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20           |

| Register 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| 1/2020—Rev. 0 to Rev. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

| Changes to Figure 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| VALUED SET OF THE SET | 71           |

|    | Register 7                               | 23 |

|----|------------------------------------------|----|

|    | Register 8                               | 24 |

|    | Register 9                               | 24 |

|    | Register 10                              | 25 |

|    | Register 11                              | 25 |

|    | Register 12                              | 26 |

|    | Register 13                              | 27 |

|    | Register 14                              | 28 |

|    | Register 15                              | 29 |

|    | Register 16                              | 30 |

|    | Register 17                              | 30 |

| Ap | pplications Information                  | 31 |

|    | Initialization Sequence                  | 31 |

|    | Recalibration Sequence                   | 32 |

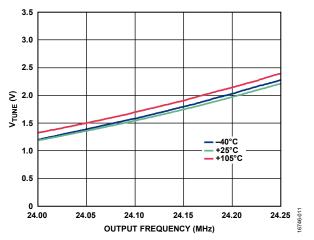

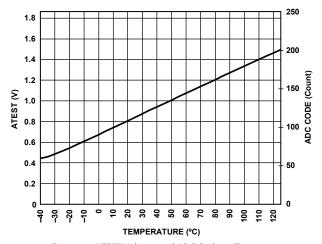

|    | Temperature Sensor                       | 33 |

|    | RF Synthesis: A Worked Example           | 33 |

|    | Reference Doubler                        | 33 |

|    | Frequency Measurement Procedure          | 34 |

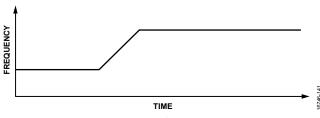

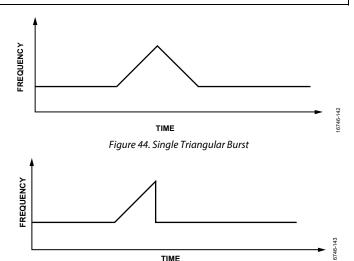

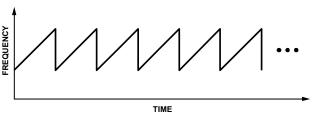

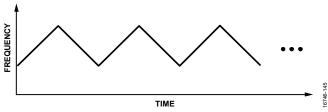

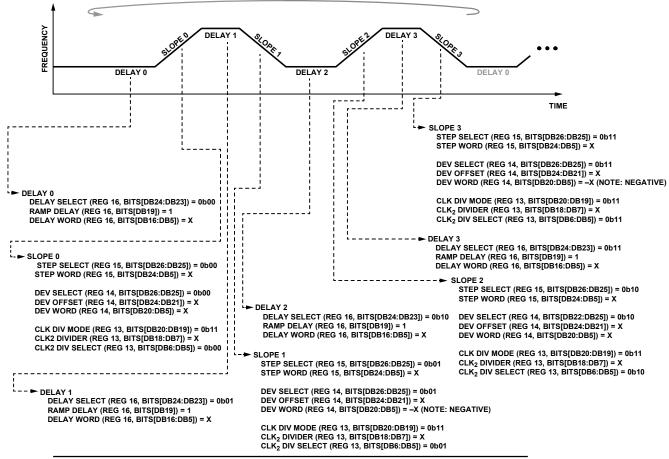

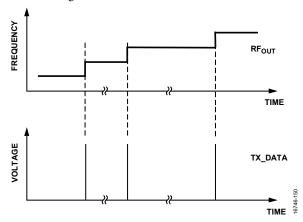

|    | Waveform Generation                      | 34 |

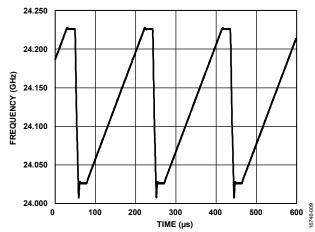

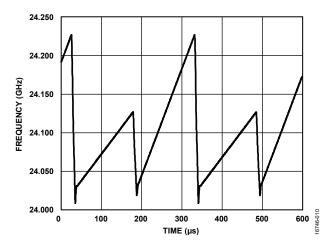

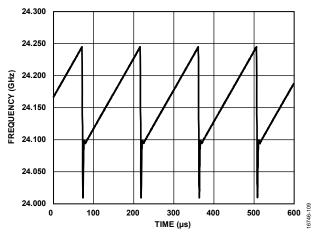

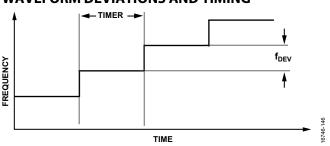

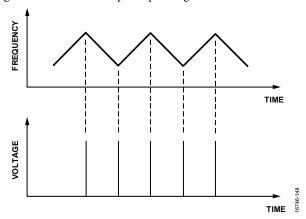

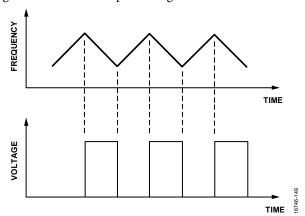

|    | Waveform Deviations and Timing           | 34 |

|    | Ramp and Modulation                      | 35 |

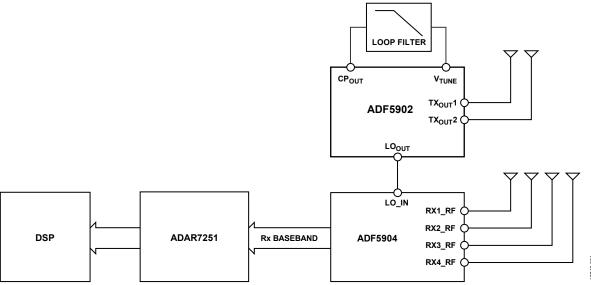

|    | Application of the ADF5902 in FMCW Radar | 37 |

| O  | utline Dimensions                        | 39 |

|    | Ordering Guide                           | 39 |

|    | Automotive Products                      | 39 |

| 1/2020—Rev. 0 to Rev. A |    |

|-------------------------|----|

| Changes to Figure 23    | 15 |

| Changes to Figure 41    | 3( |

11/2018—Revision 0: Initial Version

# **SPECIFICATIONS**

AHI = TX\_AHI = RF\_AHI = VCO\_AHI = DVDD = CP\_AHI = 3.3 V  $\pm$  5%, GND = 0 V, dBm referred to 50  $\Omega$ ,  $T_A$  =  $T_{MAX}$  to  $T_{MIN}$ , unless otherwise noted. The operating temperature range is  $-40^{\circ}$ C to  $+105^{\circ}$ C.

Table 1.

| Parameter                                                        | Min   | Тур        | Max   | Unit      | Test Conditions/Comments                                                                                                                                                                |

|------------------------------------------------------------------|-------|------------|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPERATING CONDITIONS                                             |       |            |       |           |                                                                                                                                                                                         |

| RF Frequency Range                                               | 24    |            | 24.25 | GHz       |                                                                                                                                                                                         |

| VCO CHARACTERISTICS                                              |       |            |       |           |                                                                                                                                                                                         |

| $V_{TUNE}$                                                       | 0.5   |            | 2.5   | ٧         |                                                                                                                                                                                         |

| V <sub>TUNE</sub> Impedance                                      |       | 100        |       | kΩ        |                                                                                                                                                                                         |

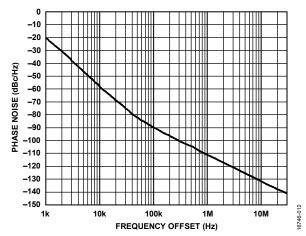

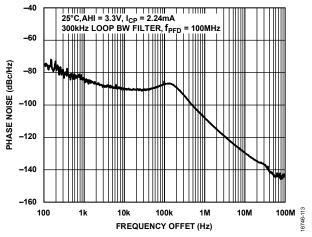

| VCO Phase Noise Performance                                      |       |            |       |           | Closed-loop, 10 kHz loop filter                                                                                                                                                         |

| At 100 kHz Offset                                                |       | -88        |       | dBc/Hz    |                                                                                                                                                                                         |

| At 1 MHz Offset                                                  |       | -108       |       | dBc/Hz    |                                                                                                                                                                                         |

| At 10 MHz Offset                                                 |       | -128       |       | dBc/Hz    |                                                                                                                                                                                         |

| Amplitude Noise                                                  |       | -150       |       | dBc/Hz    | At 1 MHz offset                                                                                                                                                                         |

| Static Pulling VCO Frequency (fvco) Change                       |       | ±2         |       | MHz       | Open-loop into 2:1 voltage standing wave ratio (VSWR) load                                                                                                                              |

| vs. Load                                                         |       | +10        |       | MHz       | Open-loop                                                                                                                                                                               |

| Dynamic Pulling Transmitter On or Off Switch Change              |       | ±10        |       | IVITIZ    | Ореп-100р                                                                                                                                                                               |

| Dynamic Pulling Transmitter to Transmitter<br>Switch Change      |       | ±5         |       | MHz       | Open-loop                                                                                                                                                                               |

| Pushing fvco Change vs. AHI Change                               |       | ±5         |       | MHz/V     | Open-loop                                                                                                                                                                               |

| Spurious Level Harmonics                                         |       | -30        |       | dBc       |                                                                                                                                                                                         |

| Spurious Level Nonharmonics                                      |       | <-70       |       | dBc       |                                                                                                                                                                                         |

| POWER SUPPLIES                                                   |       |            |       |           |                                                                                                                                                                                         |

| AHI, TX_AHI, RF_AHI, VCO_AHI, DVDD, CP_AHI                       | 3.135 | 3.3        | 3.465 | ٧         |                                                                                                                                                                                         |

| Total Current (I <sub>TOTAL</sub> ) <sup>1</sup>                 |       | 190        |       | mA        |                                                                                                                                                                                         |

| Software Power-Down Mode                                         |       | 1.2        |       | mA        |                                                                                                                                                                                         |

| Hardware Power-Down Mode                                         |       | 200        |       | μΑ        |                                                                                                                                                                                         |

| TRANSMITTER OUTPUT                                               |       |            |       | ·         |                                                                                                                                                                                         |

| Output Power                                                     | 2     | 8          | 12    | dBm       |                                                                                                                                                                                         |

| Output Impedance                                                 |       | 50         |       | Ω         |                                                                                                                                                                                         |

| On to Off Isolation                                              |       | 30         |       | dB        | Single transmitter output switched on to off                                                                                                                                            |

| Transmitter to Transmitter Isolation                             |       | 25         |       | dB        |                                                                                                                                                                                         |

| Power-Up/Power-Down Time                                         |       | 200        |       | ns        |                                                                                                                                                                                         |