# Low Power, High Speed CCD Buffer Amplifier

**ADA4800**

#### **FEATURES**

Integrated active load and gain of 1 buffer

Very low buffer power consumption

As low as 20 mW on chip

Power save feature to reduce active load current by GPO

control

High buffer speed

400 MHz, –3 dB bandwidth

415 V/µs slew rate

Fast settling time to 1%, 2 V step: 5 ns

Adjustable buffer bandwidth

Push-pull output stage

Adjustable active load current

Small package: 1.6 mm × 1.6 mm × 0.55

Small package: 1.6 mm  $\times$  1.6 mm  $\times$  0.55 mm

#### **APPLICATIONS**

CCD image sensor output buffer Digital still cameras Camcorders

#### **GENERAL DESCRIPTION**

The ADA4800 is voltage buffer integrated with an active load. The buffer is a low power, high speed, low noise, high slew rate, fast settling, fixed gain of 1 monolithic amplifier for charge-coupled device (CCD) applications. For CCD applications, the active load current source ( $I_{AL}$ ) can load the open source CCD sensor outputs and the buffer can drive the AFE load. The active current load can also be switched off, to use the ADA4800 as just a unity gain buffer. The buffer consumes only 20 mW of static power. In applications where power savings is critical, the ADA4800 features a power save mode (see the Power Save Mode section), which further reduces the total current consumption. The bandwidth of the ADA4800 buffer is also fully adjustable through the IDRV pin.

The buffer of the ADA4800 employs a push-pull output stage architecture, providing drive current and maximum slew capability for both rising and falling signal transitions. At a 5 mA quiescent current setting, it provides 400 MHz, –3 dB bandwidth, which makes this buffer well suited for CCD sensors from machine vision to digital still camera applications.

The ADA4800 is ideal for driving the input of the Analog Devices, Inc., 12-bit and 14-bit high resolution analog front ends (AFE) such as the AD9928, AD9990, AD9920A, AD9923A, and AD997x family.

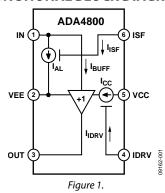

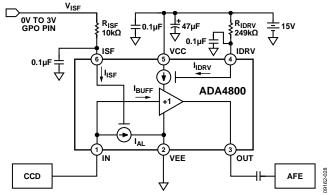

#### **FUNCTIONAL BLOCK DIAGRAM**

The versatility of the ADA4800 allows for seamless interfacing with many CCD sensors from various manufacturers.

The ADA4800 is designed to operate at supply voltages as low as 4 V and up to 17 V. It is available in a 1.6 mm  $\times$  1.6 mm  $\times$  0.55 mm, 6-lead LFCSP package and is rated to operate over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

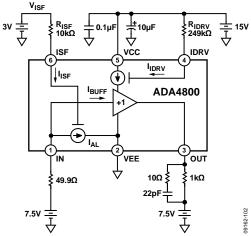

Figure 2. Typical Test Circuit

# **TABLE OF CONTENTS**

| Teatures                                       | . 1 |

|------------------------------------------------|-----|

| Applications                                   | . 1 |

| Functional Block Diagram                       | . 1 |

| General Description                            | . 1 |

| Revision History                               | . 2 |

| Specifications                                 | . 3 |

| Buffer Electrical Characteristics              | . 3 |

| Active Current Load Electrical Characteristics | . 3 |

| Absolute Maximum Ratings                       | 4   |

| Thermal Resistance                             | . 4 |

| ESD Caution                                    | 4   |

| Pin Configuration and Function Descriptions    | . 5 |

| Typical Performance Characteristics          | 6  |

|----------------------------------------------|----|

| Test Circuit                                 | 9  |

| Theory of Operation                          | 10 |

| Setting Active Load Current with Pin 6 (ISF) | 10 |

| Setting Bandwidth with Pin 4 (IDRV)          | 10 |

| Applications Information                     | 11 |

| Open Source CCD Output Buffer                | 11 |

| Power Save Mode                              | 11 |

| Power Supply Bypassing                       | 12 |

| Power Sequencing                             | 12 |

| Outline Dimensions                           | 13 |

| Ordering Guide                               | 13 |

#### **REVISION HISTORY**

#### 7/10—Rev. 0 to Rev. A

| Deleted Figure 15                                             | . 7 |

|---------------------------------------------------------------|-----|

| Changes to Setting Active Load Current with Pin 6 ISF Section | 1   |

| and Setting Bandwidth with Pin 4 (IDRV) Section               | 10  |

6/10—Revision 0: Initial Version

### **SPECIFICATIONS**

#### **BUFFER ELECTRICAL CHARACTERISTICS**

$T_A = 25$ °C,  $V_{CC} = 15$  V,  $V_{EE} = 0$  V,  $R_{IDRV} = 249$  k $\Omega$  connected to  $V_{IDRV}$ ,  $R_{LOAD} = 1$  k $\Omega$  in parallel with 22 pF in series with 10  $\Omega$ ,  $V_{IN} = 7.5$  V, unless otherwise noted (see Figure 2 for a test circuit).

Table 1.

| Parameter                    | Condition                                                                                        | Min            | Тур   | Max          | Unit   |

|------------------------------|--------------------------------------------------------------------------------------------------|----------------|-------|--------------|--------|

| GAIN                         |                                                                                                  |                |       |              |        |

| Voltage Gain                 | $V_{IN} = 6.5 \text{ V to } 8.5 \text{ V}, R_{ISF} = 0 \Omega$                                   | 0.995          | 0.998 | 1.005        | V/V    |

| INPUT/OUTPUT CHARACTERISTICS |                                                                                                  |                |       |              |        |

| I/O Offset Voltage           |                                                                                                  |                | 30    | 41           | mV     |

| IDRV Current                 | $R_{IDRV} = 249 \text{ k}\Omega$ , $V_{IDRV} = 15 \text{ V}$                                     |                | 52    | 59           | μΑ     |

| Input/Output Voltage Range   |                                                                                                  | $V_{EE} + 1.4$ |       | $V_{CC}-1.4$ | V      |

| Input Bias Current (IBUFF)   |                                                                                                  |                | 1     |              | μΑ     |

| DYNAMIC PERFORMANCE          |                                                                                                  |                |       |              |        |

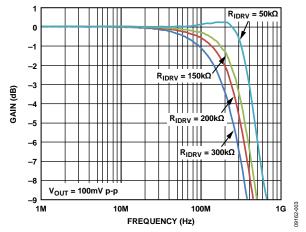

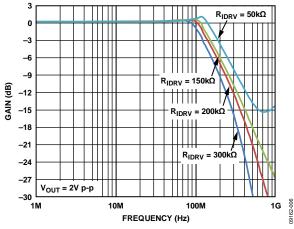

| –3 dB Bandwidth              | $R_{IDRV} = 300 \text{ k}\Omega \text{ (I}_{CC} = 1.1 \text{ mA), } V_{OUT} = 0.1 \text{ V p-p}$ |                | 182   |              | MHz    |

|                              | $R_{IDRV} = 150 \text{ k}\Omega \text{ (I}_{CC} = 2.1 \text{ mA)}, V_{OUT} = 0.1 \text{ V p-p}$  |                | 288   |              | MHz    |

|                              | $R_{IDRV} = 50 \text{ k}\Omega \text{ (I}_{CC} = 4.7 \text{ mA), V}_{OUT} = 0.1 \text{ V p-p}$   |                | 400   |              | MHz    |

| Slew Rate                    | V <sub>OUT</sub> = 2 V step                                                                      |                | 415   |              | V/µs   |

| Rise Time                    | $V_{IN} = 7.5 \text{ V to } 8.5 \text{ V}, 10\% \text{ to } 90\%$                                | 2.2            |       | ns           |        |

| Fall Time                    | $V_{IN} = 8.5 \text{ V to } 7.5 \text{ V}, 10\% \text{ to } 90\%$                                | 1.8            |       | ns           |        |

| 1% Settling Time             | $V_{IN} = 9.5 \text{ V to } 7.5 \text{ V (falling edge)}$                                        |                | 5     |              | ns     |

|                              | $V_{IN} = 7.5 \text{ V to } 9.5 \text{ V (rising edge)}$                                         |                | 4.5   |              | ns     |

|                              | $V_{IN} = 8.5 \text{ V to } 7.5 \text{ V (falling edge)}$                                        |                | 4.5   |              | ns     |

|                              | $V_{IN} = 7.5 \text{ V to } 8.5 \text{ V (rising edge)}$                                         |                | 4     |              | ns     |

| I/O Delay Time               | $V_{IN} = 8.5 \text{ V to } 7.5 \text{ V (falling edge)}$                                        |                | 0.4   |              | ns     |

|                              | $V_{IN} = 7.5 \text{ V to } 8.5 \text{ V (rising edge)}$                                         |                | 0.35  |              | ns     |

| Output Voltage Noise         | @ 20 MHz                                                                                         |                | 1.5   |              | nV/√Hz |

| POWER SUPPLY                 |                                                                                                  |                |       |              |        |

| Supply Voltage Range         |                                                                                                  | 4              | 15    | 17           | V      |

| Supply Current (Icc)         |                                                                                                  |                | 1.4   | 1.8          | mA     |

| OPERATING TEMPERATURE RANGE  |                                                                                                  | -40            |       | +85          | °C     |

#### **ACTIVE CURRENT LOAD ELECTRICAL CHARACTERISTICS**

$T_A = 25^{\circ}\text{C}$ ,  $V_{EE} = 0$  V,  $V_{ISF} = 3$  V,  $R_{ISF} = 10$  k $\Omega$  connected to  $V_{ISF}$ ,  $V_{IN} = 7.5$  V, unless otherwise noted (see Figure 2 for a test circuit).

Table 2.

| Parameter                              | Condition                      | Min                   | Тур  | Max      | Unit |

|----------------------------------------|--------------------------------|-----------------------|------|----------|------|

| INPUT/OUTPUT CHARACTERISTICS           |                                |                       |      |          |      |

| Active Load Current (I <sub>AL</sub> ) | $V_{ISF} = 0 V$                |                       | 1    |          | μΑ   |

|                                        | $V_{ISF} = 3 V$                |                       | 3    |          | mA   |

|                                        | $V_{ISF} = 7.5 V$              |                       | 12.7 |          | mA   |

| ISF Current (I <sub>ISF</sub> )        | $R_{ISF} = 10 \text{ k}\Omega$ |                       | 111  | 120      | μΑ   |

| Input Voltage Range                    |                                | V <sub>EE</sub> + 1.7 |      | $V_{CC}$ | V    |

| OPERATING TEMPERATURE RANGE            |                                | -40                   |      | +85      | °C   |

#### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 2.

| Parameter                   | Rating                             |

|-----------------------------|------------------------------------|

| Supply Voltage              | 18 V                               |

| Input Voltage               | V <sub>EE</sub> to V <sub>CC</sub> |

| ISF Pin                     | V <sub>EE</sub> to V <sub>CC</sub> |

| IDRV Pin                    | V <sub>EE</sub> to V <sub>CC</sub> |

| Storage Temperature Range   | −65°C to +150°C                    |

| Operating Temperature Range | −40°C to +85°C                     |

| Junction Temperature Range  | −65°C to +150°C                    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | Unit |

|--------------|-----------------|------|

| 6-Lead LFCSP | 160             | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

# ADA4800 IN 1 6 ISF VEE 2 EPAD 5 VCC OUT 3 4 IDRV NOTES 1. EXPOSED PAD IS NOT INTERNALLY CONNECTED TO DIE. CONNECT TO ANY LOW IMPEDANCE NODE OR LEAVE FLOATING.

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IN       | Input. Connect this pin to the CCD sensor output.                                                                                                                                                                                                                                          |

| 2       | VEE      | Negative Power Supply Voltage.                                                                                                                                                                                                                                                             |

| 3       | OUT      | Output. Connect this pin to the AFE input.                                                                                                                                                                                                                                                 |

| 4       | IDRV     | Bandwidth Adjustment Pin. Connect this pin to VCC or an external voltage with an external resistor. This pin allows bandwidth to be controlled by adjusting Icc. This pin can also be used to power down the buffer.                                                                       |

| 5       | VCC      | Positive Power Supply Voltage.                                                                                                                                                                                                                                                             |

| 6       | ISF      | Active Load Current Adjustment Pin. Connect to VCC or an external voltage with an external resistor. This pin can also be connected to the microcontroller logic output through an external resistor for power save mode. This pin can also be used to power down the active current load. |

| EPAD    | EPAD     | Exposed Pad. Not internally connected to die. Connect to any low impedance node or leave floating.                                                                                                                                                                                         |

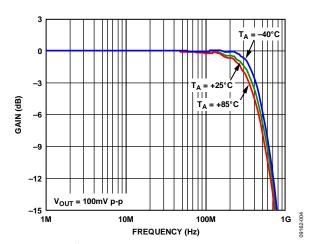

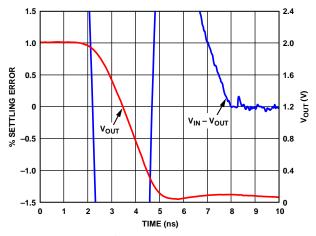

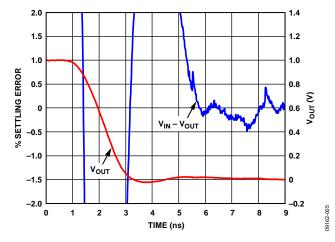

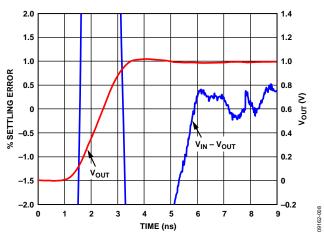

#### TYPICAL PERFORMANCE CHARACTERISTICS

$T_{A}=25^{\circ}C,\ V_{CC}=7.5\ V,\ V_{EE}=-7.5\ V,\ R_{IDRV}=249\ k\Omega\ connected\ to\ V_{IDRV},\ V_{ISF}=-4.5\ V,\ R_{ISF}=10\ k\Omega\ connected\ to\ V_{ISF},\ V_{IN}\ shunt\ terminated\ with\ 49.9\ \Omega\ to\ 0\ V,\ R_{LOAD}=1\ k\Omega\ in\ parallel\ with\ 22\ pF\ in\ series\ with\ 10\ \Omega\ to\ 0\ V.$

Figure 4. Small Signal Frequency Response with Various IDRV Resistances

Figure 7. Large Signal Frequency Response with Various IDRV Resistances

Figure 5. Small Signal Frequency Response at Various Temperatures

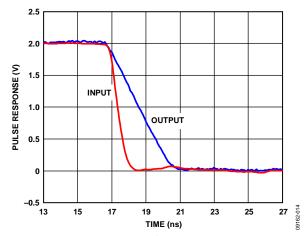

Figure 8. Settling Time, 2 V to 0 V Output Transition

Figure 6. Settling Time, 1 V to 0 V Output Transition

Figure 9. Settling Time, 0 V to 1 V Output Transition

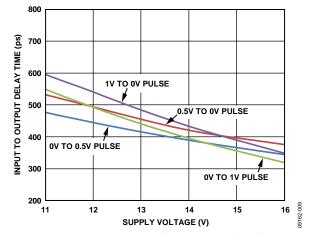

Figure 10. Input to Output Delay Time vs. Supply Voltage

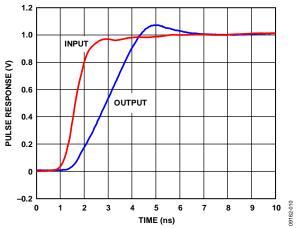

Figure 11. Positive Pulse Response, 0 V to 1 V

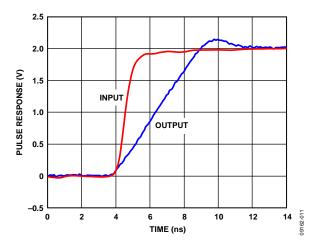

Figure 12. Positive Pulse Response, 0 V to 2 V

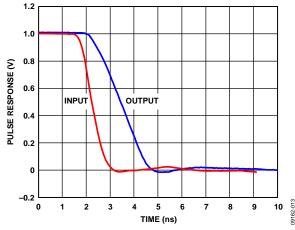

Figure 13. Negative Pulse Response, 1 V to 0 V

Figure 14. Negative Pulse Response, 2 V to 0 V

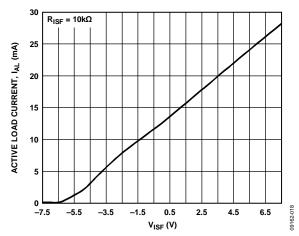

Figure 15. Input Current vs. Voltage on ISF Pin (V<sub>ISF</sub>)

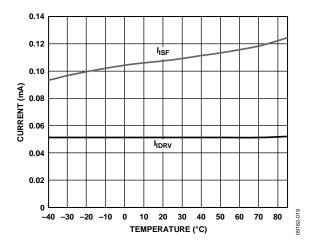

Figure 16. ISF and IDRV Currents vs. Temperature

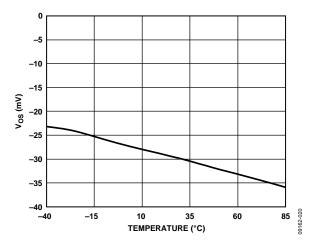

Figure 17. Vos vs. Temperature

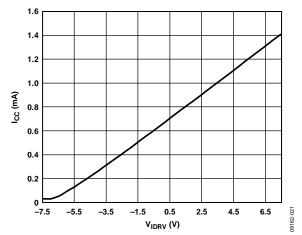

Figure 18. Icc vs. Voltage on IDRV Pin (V<sub>IDRV</sub>)

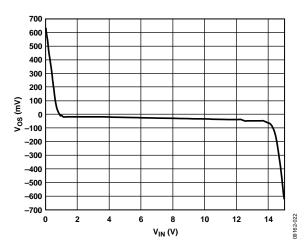

Figure 19. Output Offset Voltage vs. Input Voltage

# **TEST CIRCUIT**

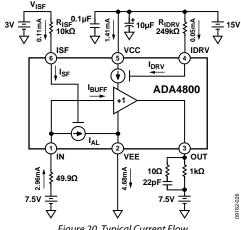

Figure 20. Typical Current Flow

#### THEORY OF OPERATION

The ADA4800 is a buffer integrated with an active load. Each element (the active load and the buffer) operates independently, as described in the following sections.

#### **SETTING ACTIVE LOAD CURRENT WITH PIN 6 (ISF)**

The ISF pin is used to establish the value of the active current load ( $I_{AL}$ ). Set the ISF current using Equation 1.

$$I_{ISF} = \frac{V_{ISF} - 1.55 \text{ V}}{R_{ISF} + 3 \text{ k}\Omega} \tag{1}$$

where:

$V_{\rm ISF}$  is referenced to Pin 2.  $V_{\rm ISF}$  can be an external voltage source,  $V_{\rm CC}$ , or a GPO output as explained in the following paragraphs.  $R_{\rm ISF}$  is the external resistor between the ISF pin and  $V_{\rm ISF}$ .

The active load current (into the IN pin) is directly proportional to  $I_{\rm ISF}$  and can be calculated by Equation 2.

$$I_{AL} = I_{ISF} \times 27 \tag{2}$$

The ADA4800 allows for additional power savings by reducing the active load current. The active load current can be logically controlled by connecting the ISF pin to any general-purpose output (GPO) pin of a system microcontroller through an external resistor. A GPO logic high enables the flow of the active load current. Appling  $-V_{\rm S}$  or connecting a high-Z to the ISF pin places the ADA4800 into power save mode by shutting down the active load current.

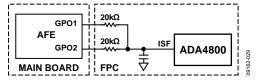

Figure 22 illustrates an ADA4800 application configuration for using this power save feature.

An external resistor connected between the ISF and the microcontroller GPO pin determines the amount of current that flows into the input pin. This current can be calculated by using Equation 1 and Equation 2.

#### **SETTING BANDWIDTH WITH PIN 4 (IDRV)**

The IDRV pin establishes the buffer's  $I_{\rm CC}$  quiescent current. As  $I_{\rm CC}$  is increased, power dissipation and bandwidth both increase. Set the current using Equation 3.

$$I_{IDRV} = \frac{V_{IDRV} - 0.8 \,\mathrm{V}}{R_{IDRV} + 28 \,\mathrm{k}\Omega} \tag{3}$$

where:

$V_{IDRV}$  is referenced to Pin 2.  $V_{IDRV}$  can be an external voltage source or  $V_{CC}$ .

$R_{IDRV}$  is the external resistor between the IDRV pin and  $V_{IDRV}$ .

The  $I_{\text{CC}}$  current is directly proportional to  $I_{\text{IDRV}}$  and can be calculated by Equation 4.

$$I_{CC} = I_{IDRV} \times 26 \tag{4}$$

Applying –V<sub>s</sub> to the IDRV pin shuts down the buffer.

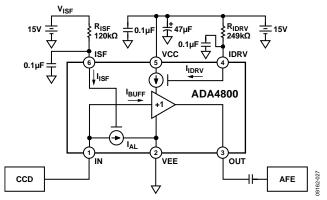

# APPLICATIONS INFORMATION OPEN SOURCE CCD OUTPUT BUFFER

With low power, high slew rate, and fast settling time, the ADA4800 is the ideal solution for an output buffer for CCD sensors with an open source output configuration. Figure 21 shows a typical application circuit for the ADA4800 as a CCD sensor output buffer.

The output of the CCD is connected directly to the IN pin of the ADA4800, whose OUT pin is then ac-coupled into the input of the analog front end.

Figure 21. Typical Application Block Diagram

To help reduce the effects of power supply noise coupling into the ISF and IDRV pins, use 0.1  $\mu F$  ceramic bypass decoupling capacitors. For best performance, place these capacitors as close to each of these pins as is physically possible.

#### **POWER SAVE MODE**

The buffer of the ADA4800 consumes only 20 mW of static power. To achieve even more power savings, the ADA4800 active load current can be switched off during standby mode or reduced during monitoring mode. Figure 22 illustrates the

ADA4800 as an open source CCD buffer configured for using this power save feature. Power save mode allows  $I_{AL}$  current to be logically controlled by connecting the ISF pin to any general-purpose output (GPO) pin of the system microcontroller through an external resistor. A GPO logic high enables the flow of input sink current, while a logic low disables the input sink current and asserts the power save mode.

Figure 22. Using GPO to Drive ISF Voltage

Figure 23 shows an example of the ADA4800 power save feature.

Figure 23. Example Block Diagram for Sink Current Selection

Three combinations of  $I_{AL}$  are provided with Figure 23. Selection of the  $I_{AL}$  is controlled by the logic signals applied to the GPO1 and GPO2 pins. Table 5 summarizes the  $I_{AL}$  selections.

**Table 5. Input Sink Current Selection**

| Mode    | GPO1   | GPO2   | Resistance (kΩ) | Active Load Current, I <sub>AL</sub> (mA) |  |  |

|---------|--------|--------|-----------------|-------------------------------------------|--|--|

| Standby | High-Z | High-Z | High-Z          | 0                                         |  |  |

|         | 0      | 0      | N/A             |                                           |  |  |

| Sleep   | High-Z | 1      | 20              | 1.90                                      |  |  |

|         | 1      | High-Z | 20              |                                           |  |  |

| Active  | 1      | 1      | 10              | 3.36                                      |  |  |

#### **POWER SUPPLY BYPASSING**

Attention must be paid to bypassing the power supply pin of the ADA4800. Use high quality capacitors with low equivalent series resistance (ESR), such as multilayer ceramic capacitors (MLCCs), to minimize supply voltage ripple and power dissipation. A large, usually tantalum, 2.2  $\mu F$  to 47  $\mu F$  capacitor located in close proximity to the ADA4800 is required to provide good decoupling for lower frequency signals. The actual value is determined by the circuit transient and frequency requirements. In addition, 0.1  $\mu F$  MLCC decoupling capacitors should be located as close to the power supply pin as is physically possible, no more than  $\frac{1}{2}$  inch away. The ground returns should terminate immediately into the ground plane. Locating the bypass capacitor return close to the load return minimizes ground loops and improves performance.

#### **POWER SEQUENCING**

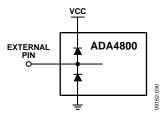

All I/O pins are ESD protected with internal back-to-back diodes connected to VCC and GND as shown in Figure 24. With the ADA4800 supply turned off ( $V_{\rm CC}=0~{\rm V}$ ), a voltage on an I/O pin can turn on the protection diodes and cause permanent damage or destroy the IC. To prevent this condition during power-on, no voltages should be applied to any I/O pins until VCC is fully on and settled. During power-off, I/O pin voltages should be removed or reduced to 0 V before VCC is turned off.

Figure 24. Simplified Input/Output Circuitry

In the presence of a voltage on an I/O pin with  $V_{\rm CC}$  = 0 V, the current should be limited to 5 mA or less by the source or by adding a series resistor.

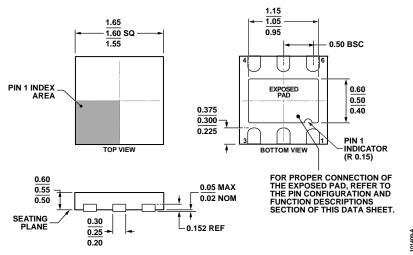

# **OUTLINE DIMENSIONS**

Figure 25. 6-Lead Lead Frame Chip Scale Package [LFCSP\_UD] 1.60 mm × 1.60 mm Body, Ultra Thin, Dual Lead (CP-6-4) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                             | Package Option | Branding |

|--------------------|-------------------|-------------------------------------------------|----------------|----------|

| ADA4800ACPZ-R2     | −40°C to +85°C    | 6-Lead Lead Frame Chip Scale Package [LFCSP_UD] | CP-6-4         | H2E      |

| ADA4800ACPZ-R7     | −40°C to +85°C    | 6-Lead Lead Frame Chip Scale Package [LFCSP_UD] | CP-6-4         | H2E      |

| ADA4800ACPZ-RL     | −40°C to +85°C    | 6-Lead Lead Frame Chip Scale Package [LFCSP_UD] | CP-6-4         | H2E      |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**

# **NOTES**

NOTES

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

ADA4800ACPZ-RL ADA4800ACPZ-R7