# **CAT-5** Receiver with **Adjustable Line Equalization**

**AD8128 Data Sheet**

#### **FEATURES**

Tuned to compensate for Category-5 (CAT-5) cable losses Up to 100 meters at 120 MHz

2 voltage controlled frequency response adjustment pins High frequency peaking adjustment **Broadband gain adjustment**

2700 V/us slew rate

Low output noise

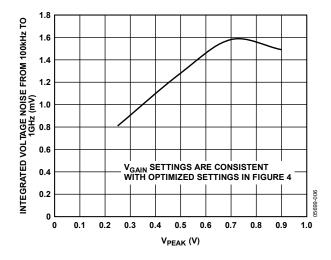

1.5 mV rms integrated noise (1 GHz) at 100 meters equalized bandwidth

DC output offset adjust

Low offset voltage error: 7 mV typ

Equalized pass-band ripple ±1 dB to 70 MHz

Input: differential or single ended Supply current: 24 mA on ±5 V Small 8-lead 3 mm × 3 mm LFCSP

#### **APPLICATIONS**

Keyboard-video-mouse (KVM) RGB video over unshielded twisted pair (UTP) cable receivers Professional video projection and distribution Security video

#### **GENERAL DESCRIPTION**

The AD8128 is a high speed, differential receiver/equalizer that compensates for the transmission losses of unshielded twisted pair (UTP) CAT-5 cables. Various frequency dependent gain stages are summed together to best approximate the inverse frequency response of CAT-5/CAT-5e cable. An equalized bandwidth of 120 MHz can be achieved for 100 meters of cable.

The AD8128 can be used as a standalone receiver/equalizer or in conjunction with the AD8143, triple differential receiver, to provide a complete low cost solution for receiving RGB over UTP cable in such applications as KVM.

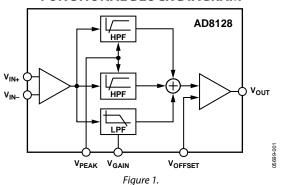

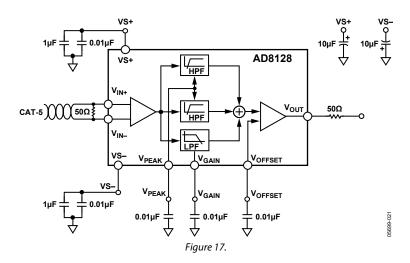

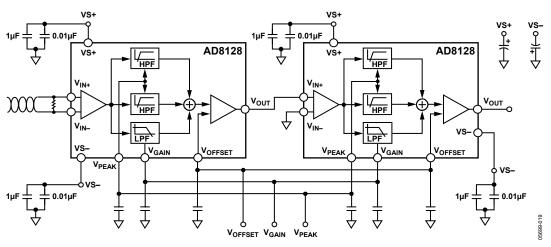

#### FUNCTIONAL BLOCK DIAGRAM

The AD8128 has three control pins for optimal CAT-5/CAT-5e compensation. The equalized cable length is directly proportional to the voltage applied to the VPEAK pin, which controls the amount of high frequency peaking. V<sub>GAIN</sub> adjusts the broadband gain from 0 dB to 3 dB, compensating for the resistive cable loss. Voffset allows the output to be shifted by ±2.5 V, adding flexibility for dc-coupled systems.

Low integrated output noise and offset voltage adjust make the AD8128 an excellent choice for dc-coupled wideband RGB-over-CAT-5 applications. For systems where the UTP cable is longer than 100 meters, two AD8128 devices can be cascaded to compensate for up to 200 meters of CAT-5/CAT-5e.

The AD8128 is available in a 3 mm  $\times$  3 mm 8-lead LFCSP and is rated to operate over the extended temperature range of -40°C to +85°C.

# **TABLE OF CONTENTS**

| reatures                                    |     |

|---------------------------------------------|-----|

| Applications                                | . 1 |

| Functional Block Diagram                    | . 1 |

| General Description                         | . 1 |

| Revision History                            | . 2 |

| Specifications                              | . 3 |

| Absolute Maximum Ratings                    | . 4 |

| Thermal Resistance                          | . 4 |

| ESD Caution                                 | . 4 |

| Pin Configuration and Function Descriptions | . 5 |

| Typical Performance Characteristics         | . 6 |

| Test Circuit                                | . 8 |

|                                             |     |

| Theory of Operation                               |    |

|---------------------------------------------------|----|

| Input Common-Mode Voltage Range Considerations    | 9  |

| Applications Information                          | 10 |

| KVM Applications                                  | 10 |

| DC Control Pins                                   | 10 |

| Cascaded Applications                             | 11 |

| Exposed Pad (EP)                                  | 11 |

| Layout and Power Supply Decoupling Considerations | 11 |

| Evaluation Boards                                 | 11 |

| Outline Dimensions                                | 12 |

| Ordering Guide                                    | 12 |

## **REVISION HISTORY**

10/2005—Revision 0: Initial Version

# **SPECIFICATIONS**

$T_A = 25^{\circ}\text{C}$ ,  $V_S = \pm 5$  V,  $R_L = 150$   $\Omega$ , Belden cable,  $V_{OFFSET} = 0$  V,  $V_{GAIN}$  and  $V_{PEAK}$  set to optimized settings (see Figure 4), unless otherwise noted.

Table 1.

| Parameter                            | Test Conditions/Comments                                                  | Min   | Тур     | Max     | Unit   |

|--------------------------------------|---------------------------------------------------------------------------|-------|---------|---------|--------|

| DYNAMIC PERFORMANCE                  |                                                                           |       |         |         |        |

| -3 dB Large Signal Bandwidth         | $V_{OUT} = 2 V p-p$ , 100 meter CAT-5                                     |       | 120     |         | MHz    |

| ±1 dB Equalized Bandwidth Flatness   | V <sub>OUT</sub> = 2 V p-p                                                |       | 70      |         | MHz    |

| Rise/Fall Time                       | $V_{OUT} = 2 V \text{ step, } 50 \text{ meter CAT-5}$                     |       | 2       |         | ns     |

| Rise/Fall Time                       | $V_{OUT} = 2 V \text{ step, } 100 \text{ meter CAT-5}$                    |       | 3.6     |         | ns     |

| Settling Time to 2%                  | $V_{OUT} = 2 V \text{ step, } 50 \text{ meter CAT-5}$                     |       | 26      |         | ns     |

| Settling Time to 2%                  | $V_{OUT} = 2 V \text{ step, } 100 \text{ meter CAT-5}$                    |       | 36.4    |         | ns     |

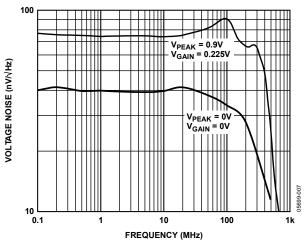

| Integrated Output Voltage Noise      | $V_{PEAK} = 0.9 \text{ V}, V_{GAIN} = 225 \text{ mV}, BW = 1 \text{ GHz}$ |       | 1.5     |         | mV rms |

| DC PERFORMANCE                       |                                                                           |       |         |         |        |

| Input Bias Current                   |                                                                           |       | 15.5    | 24      | μΑ     |

| Voffset Pin Current                  |                                                                           |       | 1.7     | 8.2     | μΑ     |

| V <sub>GAIN</sub> Pin Current        |                                                                           |       | 2       | 3.4     | μΑ     |

| V <sub>PEAK</sub> Pin Current        |                                                                           |       | 4.2     | 6.8     | μΑ     |

| INPUT CHARACTERISTICS                |                                                                           |       |         |         |        |

| Input Differential Voltage           |                                                                           |       | ±2.8    |         | V      |

| Input Common-Mode Voltage            |                                                                           |       | ±3.0    |         | V      |

| Input Resistance                     | Common mode                                                               |       | 380     |         | kΩ     |

|                                      | Differential                                                              |       | 675     |         | kΩ     |

| Input Capacitance                    |                                                                           |       | 1.7     |         | pF     |

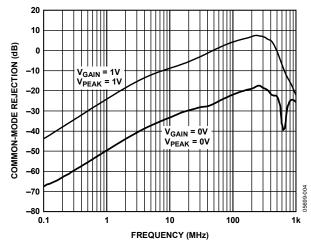

| Common-Mode Rejection Ratio (CMRR)   | 200 kHz, ΔV <sub>OUT</sub> /ΔV <sub>IN, cm</sub>                          | -63   | -74     |         | dB     |

| ADJUSTMENT PINS                      |                                                                           |       |         |         |        |

| V <sub>PEAK</sub> Input Voltage      | Relative to ground                                                        | 0     |         | 1       | V      |

| Maximum Peak Gain                    | At 120 MHz, V <sub>PEAK</sub> = 1 V                                       |       | 20      |         | dB     |

| V <sub>GAIN</sub> Input              | Relative to ground                                                        | 0     |         | 1       | V      |

| Maximum Broadband Gain               | V <sub>GAIN</sub> = 1 V                                                   |       | 3       |         | dB     |

| Voffset Input Range                  | Relative to ground                                                        |       | ±2.5    |         | V      |

| Voffset to Vout Gain                 |                                                                           |       | 1       |         | V/V    |

| OUTPUT CHARACTERISTICS               |                                                                           |       |         |         |        |

| Output Voltage Swing                 |                                                                           | -2.55 |         | +2.7    | V      |

| Output Offset Voltage                | V <sub>OFFSET</sub> = 0 V, RTO                                            | -10.9 | +7      | +18.7   | mV     |

| Output Offset Voltage Drift          |                                                                           |       | -5.5    |         | μV/°C  |

| Short-Circuit Output Current         |                                                                           |       | 100     |         | mA     |

| POWER SUPPLY                         |                                                                           |       |         |         |        |

| Operating Voltage Range              |                                                                           | ±4.5  |         | ±5.5    | V      |

| Quiescent Supply Current, Icc/IEE    | At ±5 V                                                                   |       | +24/-21 | +31/-27 | mA     |

| Supply Current Drift, Icc/IEE        |                                                                           |       | +86/-77 |         | μΑ/°C  |

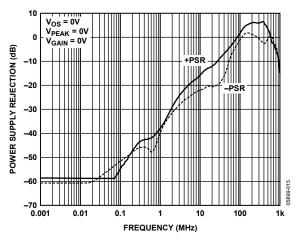

| +Power Supply Rejection Ratio (PSRR) | RTO                                                                       | -48   | -59     |         | dB     |

| –Power Supply Rejection Ratio (PSRR) | RTO                                                                       | -48   | -61     |         | dB     |

| TEMPERATURE RANGE                    |                                                                           | -40   |         | +85     | °C     |

# **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                            | Rating                            |

|------------------------------------------------------|-----------------------------------|

| Supply Voltage                                       | ±5.5 V                            |

| Input Voltage                                        | ±V <sub>S</sub>                   |

| V <sub>PEAK</sub> and V <sub>GAIN</sub> Control Pins | $-3 V to +V_s$                    |

| Voffset Control Pins                                 | ± <b>V</b> s                      |

| Operating Temperature Range                          | -40°C to +85°C<br>-65°C to +125°C |

| Storage Temperature Range                            | −65°C to +125°C                   |

| Lead Temperature (Soldering 10 sec)                  | 300°C                             |

| Junction Temperature                                 | 150°C                             |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

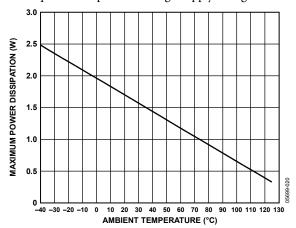

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | θις | Unit |

|--------------|-----------------|-----|------|

| 8-Lead LFCSP | 77              | 14  | °C/W |

### **Maximum Power Dissipation**

The maximum safe power dissipation in the AD8128 package is limited by the associated rise in junction temperature (T<sub>1</sub>) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes the properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8128. Exceeding a junction temperature of 150°C for an extended period can result in changes in the silicon devices potentially causing failure.

The power dissipated in the package  $(P_D)$  is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for the output. The quiescent power is the voltage between the supply pins  $(V_S)$  times the quiescent current  $(I_S)$ . The power dissipated due to the load drive depends upon the particular application. For each output, the power due to load drive is calculated by multiplying the load current by the associated voltage drop across the

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . Also, more metal directly in contact with the package leads from metal traces, through-holes, ground, and power planes reduces the  $\theta_{JA}$ . The exposed pad on the underside of the package must be soldered to a pad on the PCB surface, which is thermally connected to a copper plane to achieve the specified  $\theta_{JA}$ .

Figure 2 shows the maximum safe power dissipation in the package vs. the ambient temperature for the 8-lead LFCSP (48.5°C/W) on a JEDEC standard 4-layer board with the underside pad soldered to a pad that is thermally connected to a PCB plane. Extra thermal relief is required for operation at high supply voltages.

Figure 2. Maximum Power Dissipation vs. Temperature

## **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

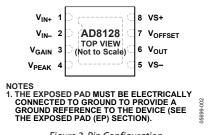

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic          | Description                                                                                                                                                                |

|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>IN+</sub>  | Positive Equalizer Input                                                                                                                                                   |

| 2       | V <sub>IN</sub> - | Negative Equalizer Input                                                                                                                                                   |

| 3       | $V_{GAIN}$        | 0 V to 1 V Broadband Gain Control                                                                                                                                          |

| 4       | V <sub>PEAK</sub> | 0 V to 1 V High Frequency Gain Control                                                                                                                                     |

| 5       | VS-               | Negative Power Supply                                                                                                                                                      |

| 6       | V <sub>OUT</sub>  | Equalizer Output                                                                                                                                                           |

| 7       | Voffset           | DC Offset Adjust                                                                                                                                                           |

| 8       | VS+               | Positive Power Supply                                                                                                                                                      |

| EP      | GND               | Ground Reference and Thermal Pad. The exposed pad must be electrically connected to ground to provide a ground reference to the device (see the Exposed Pad (EP) section). |

# TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C,  $V_S = \pm 5$  V,  $R_L = 150$   $\Omega$ , Belden cable,  $V_{OFFSET} = 0$  V, unless otherwise noted.

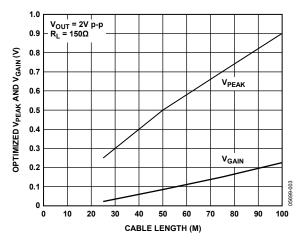

Figure 4. VPEAK and VGAIN Settings vs. Cable Length

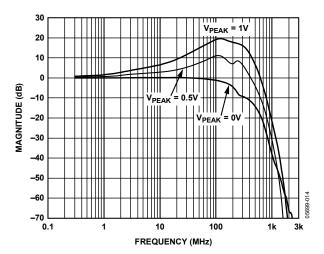

Figure 5. Frequency Response for Various V<sub>PEAK</sub> Settings Without Cable

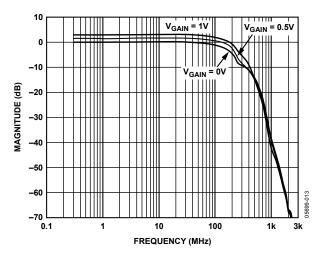

Figure 6. Frequency Response for Various V<sub>GAIN</sub> Settings Without Cable

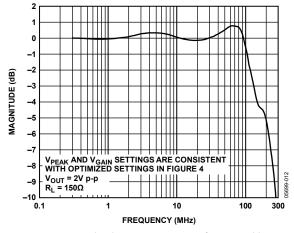

Figure 7. Equalized Frequency Response for 50 M Cable

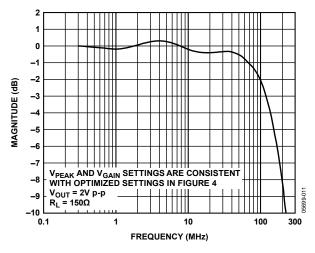

Figure 8. Equalized Frequency Response for 100 M Cable

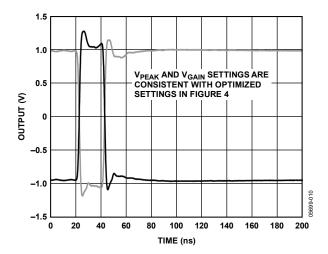

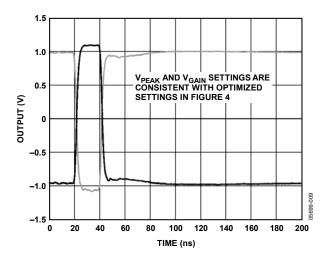

Figure 9. Equalized Pulse Response for 50 M of Cable

Figure 10. Equalized Pulse Response for 100 M of Cable

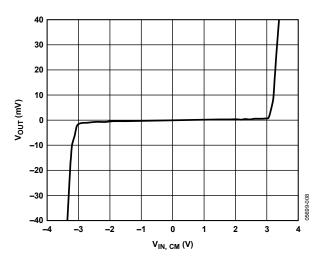

Figure 11. Output Voltage vs. Common-Mode Input Voltage

Figure 12. Voltage Noise vs. Frequency

Figure 13. Integrated Voltage Noise vs. V<sub>PEAK</sub>

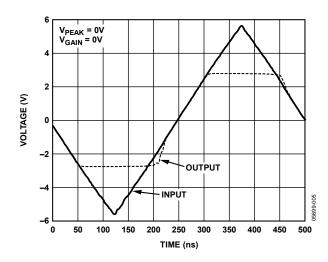

Figure 14. Overdrive Recovery Time

Figure 15. Common-Mode Rejection vs. Frequency

Figure 16. Power Supply Rejection vs. Frequency

## **TEST CIRCUIT**

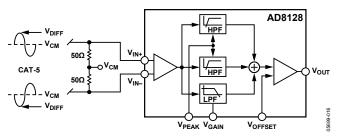

# THEORY OF OPERATION

The AD8128 is a high speed, low noise analog line equalizer that compensates for losses in CAT-5/CAT-5e cables up to 100 meters with  $\pm 1$  dB flatness in the pass band out to 70 MHz (see Figure 8). Two continuously adjustable control voltages alter the frequency response to add flexibility to the system by allowing for the compensation of various cable lengths as well as for variations in the cable itself. The dc control voltage pin  $V_{GAIN}$  adjusts ac broadband gain from 0 dB to 3 dB (see Figure 6) to account for dc resistive losses present in the cable. A second dc control voltage pin  $V_{PEAK}$  adjusts the amount of high frequency peaking (see Figure 5) from 0 dB to 20 dB. This compensates for the high frequency loss due to the skin effect of the cable.

The AD8128 has a high impedance differential input that allows it to receive dc-coupled signals directly from the cable. For systems with very high CMRR specifications, the AD8128 can also be used with a dedicated receiver, such as the AD8130 or AD8143, placed in front of it. The output of the AD8128 is low impedance and is capable of driving a 150  $\Omega$  load resistor and up to 20 pF of load capacitance at the output. For systems with high parasitic capacitances at the output, it is recommended that a small series resistor be placed between the output and capacitive load to reduce ringing in the pulse response.

The AD8128 is designed to be used in medium-length systems that have stringent low noise requirements as well as longer-length systems that can tolerate more noise. For the medium-length requirements, a single AD8128 is able to compensate up to 100 meters of cable with only 1.5 mV rms of output noise. For longer-length applications that require equalization of up to 200 meters of cable, two AD8128 devices can be cascaded together to achieve the desired equalization, while keeping approximately the same pass-band bandwidth, but with a slight degradation in settling time and slew rate.

The frequency response of the AD8128 approximates the inverse frequency response of a lossy transmission line, which is given by

$$H(f) = e^{kl(1+j)\sqrt{f}} \tag{1}$$

where:

f is the frequency.

l is the length.

k is the line constant.

The AD8128 approximates the magnitude response of Equation 1 by summing multiple zero-poles pairs offset at different frequencies. Equalization adjustment due to varying line lengths is done by changing the weighting factors of each of the zero-pole pairs.

# INPUT COMMON-MODE VOLTAGE RANGE CONSIDERATIONS

When using the AD8128 as a receiver, it is important to ensure that the input common-mode (CM) voltage range of the AD8128 stays within the specified range. The input CM level can be easily calculated by adding the CM level of the driver, the amplitude of any sync pulses, and the other possible induced common-mode signals from power lines and fluorescent lights.

$$V_{ICM} = V_{CM} + V_{SYNC} + V_{OTHER}$$

(2)

For example, when using a single 5 V supply on the drive side, the CM voltage of the line typically becomes the midsupply voltage,  $V_{\text{CM}} = 2.5 \text{ V}$ . Furthermore, an addition of a sync signal,  $V_{\text{SYNC}} = 0.5 \text{ V}$ , on to the common mode puts the peak CM voltage at 3 V. Assuming that both the driver and receiver have exactly the same ground potential, the signal is marginally below the upper end of the common-mode input range of 3.1 V. Other CM signals that can be picked up by the CAT-5 cable result in exceeding the CM input range of the AD8128.

The most effective way of not exceeding the CM level of the AD8128 is to lower the CM level on the driver. In the previous example, this was the primary contributor to the CM input level. If this is not possible, a dedicated receiver with a wider CM input range, such as the AD8130 or AD8143, must be used.

# APPLICATIONS INFORMATION KVM APPLICATIONS

In KVM applications, cable equalization typically occurs at the root of the KVM network. In a star configuration, a driver is located at each of the end nodes and a receiver/equalizer is located at the single root node. In a daisy-chain configuration, each of the end nodes are connected to one another, and one of them is connected to the root. Similarly, the drivers are placed on the nodes, and the receivers/equalizers are placed at the root.

In both of these aforementioned configurations, three AD8128 receiver/equalizers can be used at the root node to equalize the transmitted red (R), green (G), and blue (B) channels for up to 100 meters of cable. Since the skew between two pairs of cables in CAT-5 is less than 1%, the control pins can be tied together and used as a single set of controls.

If the common-mode levels of the inputs permit using the AD8128 as a receiver (see the Input Common-Mode Voltage Range Considerations section), the input signal must be terminated by a  $100~\Omega$  shunt resistor between the pairs, or by two  $50~\Omega$  shunt resistors with a common-mode tap in the middle. This CM tap can extract the sync information from the signal if sync-on-common-mode is used.

Figure 18. Single Receiver Configuration for CAT-5 Equalizer

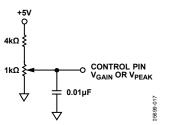

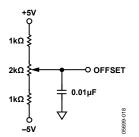

## **DC CONTROL PINS**

The AD8128 uses two control pins ( $V_{GAIN}$  and  $V_{PEAK}$ ) to adjust the equalization based on the length of the cable and one pin ( $V_{OFFSET}$ ) to adjust the dc output offset.  $V_{GAIN}$  is a user-adjustable 0 V to 1 V broadband gain control pin, and  $V_{PEAK}$  is a 0 V to 1 V adjustable high frequency gain pin to equalize for the skin effect in CAT-5 cable. The values of both  $V_{PEAK}$  and  $V_{GAIN}$  are linearly correlated to the length of the cable to be equalized. A simple formula can approximate the desired values for both of these pins.

$$V_{GAIN} = \frac{length(m)}{425 \text{m/V}} \tag{3}$$

$$V_{PEAK} = \frac{length(m)}{110\text{m/V}} \tag{4}$$

While these equations give a close approximation of the desired value for each pin, to achieve optimal performance, it can be necessary to adjust these values slightly.

Figure 19 and Figure 20 illustrate circuits that adjusts the control pins on the AD8128. In Figure 19, a 1 k $\Omega$  potentiometer adjusts the control pin voltage between the specified range of 0 V to 1 V. In Figure 20, a 2 k $\Omega$  potentiometer controls the offset pin from –2.5 V to +2.5 V. For both of these configurations, a ±5V supply is assumed.

Figure 19. Circuit to Control V<sub>GAIN</sub> and V<sub>PEAK</sub> (0 V to 1 V)

Figure 20. Circuit to Control VOFFSET (±2.5 V)

Figure 21. Cascaded AD8128 Configuration

## **CASCADED APPLICATIONS**

To equalize distances longer than the specified 100 meters, the AD8128 can be cascaded to provide equalization for longer distances. When combining two AD8128 devices in series, it is possible to link the control pins together and use them like a single control pin for up to 200 meters of equalization.

In this configuration, it is important to note that some key video specifications can be slightly degraded. By combining two equalizers in series, specifications such as rise time and settling time both increase while 3 dB bandwidth decreases slightly. Also, integrated noise is increased because the second equalizer adds gain. Subjective testing must be done to determine the appropriate setting for the three control pins for optimum equalization.

## **EXPOSED PAD (EP)**

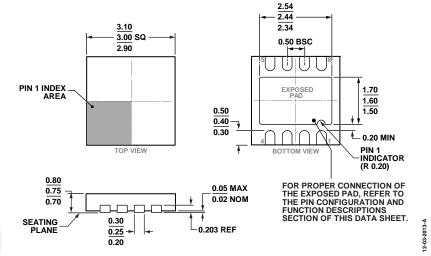

The 8-lead LFCSP has an exposed pad on the underside of the body. To achieve the specified thermal resistance, it must have a good thermal connection to one of the PCB planes. The exposed pad must be soldered to a pad on top of the board connected to an inner plane with several thermal vias. For the AD8128, this pad must also be electrically connected to ground to provide a ground reference to the device.

# LAYOUT AND POWER SUPPLY DECOUPLING CONSIDERATIONS

Standard high speed PCB layout practices must be adhered to when designing with the AD8128. A solid ground plane is recommended and good wideband power supply decoupling networks must be placed as close as possible to the supply pins and control pins. Small surface-mount ceramic capacitors are recommended for these networks, and tantalum capacitors are recommended for bulk supply decoupling.

### **EVALUATION BOARDS**

There are two evaluation boards available for easy characterization of the AD8128. A general-purpose evaluation board consisting of a single AD8128, with an option of also using a dedicated receiver, is available for simple characterization of the device. Additionally, a KVM application specific evaluation board is available. This evaluation board consists of six AD8128 devices to equalize each of the RGB channels up to 200 meters, a 16-pin 26C32 comparator for sync-on-common-mode extract and a triple op amp to provide additional gain if necessary.

# **OUTLINE DIMENSIONS**

Figure 22. 8-Lead Lead Frame Chip Scale Package [LFCSP] 3 mm × 3 mm Body and 0.75 mm Package Height (CP-8-21) Dimensions shown in millimeters

## **ORDERING GUIDE**

| AA 1 11            |                   |                                              |                |          |

|--------------------|-------------------|----------------------------------------------|----------------|----------|

| Model <sup>1</sup> | Temperature Range | Package Description                          | Package Option | Branding |

| AD8128ACPZ-R2      | −40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP] | CP-8-21        | HZB      |

| AD8128ACPZ-RL      | -40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP] | CP-8-21        | HZB      |

| AD8128ACPZ-R7      | −40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP] | CP-8-21        | HZB      |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

AD8128ACPZ-R7 AD8128ACPZ-RL AD8128ACPZ-R2