# 2.7 V to 5.5 V, 400 kSPS 8-/10-Bit Sampling ADC

AD7813

# FEATURES

8-/10-Bit ADC with 2.3  $\mu$ s Conversion Time On-Chip Track and Hold Operating Supply Range: 2.7 V to 5.5 V Specifications at 2.7 V-3.6 V and 5 V  $\pm$  10% 8-Bit Parallel Interface 8-Bit + 2-Bit Read Power Performance Normal Operation 10.5 mW, V<sub>DD</sub> = 3 V Automatic Power-Down 34.6  $\mu$ W @ 1 kSPS, V<sub>DD</sub> = 3 V Analog Input Range: 0 V to V<sub>REF</sub> Reference Input Range: 1.2 V to V<sub>DD</sub>

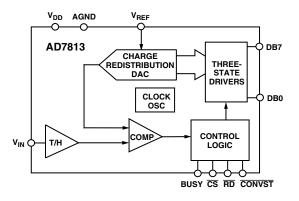

# FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The AD7813 is a high-speed, microprocessor-compatible, 8-/10-bit analog-to-digital converter with a maximum throughput of 400 kSPS. The converter operates off a single 2.7 V to 5.5 V supply and contains a 2.3  $\mu$ s successive approximation A/D converter, track/hold circuitry, on-chip clock oscillator and 8-bit wide parallel interface. The parallel interface is designed to allow easy interfacing to microprocessors and DSPs. The 10-bit conversion result is read by carrying out two 8-bit read operations. The first read operation accesses the 8 MSBs of the ADC conversion result and the second read accesses the 2 LSBs. Using only address decoding logic the AD7813 is easily mapped into the microprocessor address space.

When used in its power-down mode, the AD7813 automatically powers down at the end of a conversion and powers up at the start of a new conversion. This feature significantly reduces the power consumption of the part at lower throughput rates. The AD7813 can also operate in a high speed mode where the part is not powered down between conversions. In this mode of operation the part is capable of providing 400 kSPS throughput.

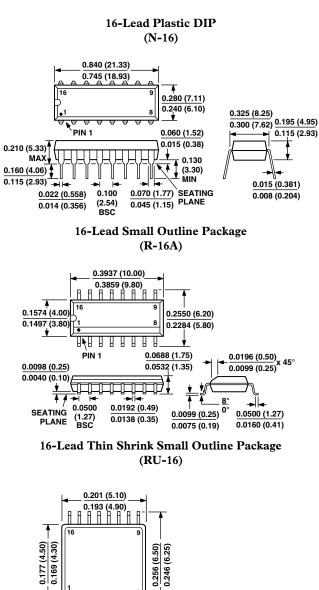

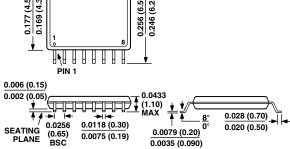

The part is available in a small, 16-lead, 0.3" wide, plastic dualin-line package (DIP), in a 16-lead, 0.15" wide, narrow body small outline IC (SOIC) and in a 16-lead thin shrink small outline package (TSSOP).

# **PRODUCT HIGHLIGHTS**

Low Power, Single Supply Operation The AD7813 operates from a single 2.7 V to 5.5 V supply and typically consumes only 10.5 mW of power. The power dissipation can be significantly reduced at lower through-

put rates by using the automatic power-down mode.

2. Automatic Power-Down

The automatic power-down mode, whereby the AD7813 goes into power-down mode at the end of a conversion and powers up before the next conversion, means the AD7813 is ideal for battery powered applications; e.g.,  $34.6 \,\mu\text{W}$  (*a*) 1 kSPS. (See Power vs. Throughput Rate section.)

3. Parallel Interface

An easy to use 8-bit-wide parallel interface allows interfacing to most popular microprocessors and DSPs with minimal external circuitry.

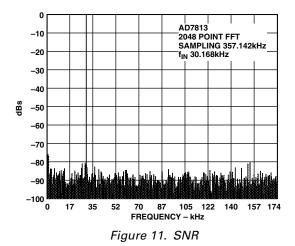

4. Dynamic Specifications for DSP Users

In addition to the traditional ADC specifications, the AD7813 is specified for ac parameters, including signal-to-noise ratio and distortion.

#### REV. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

# $\label{eq:addition} AD7813 \mbox{-} SPECIFICATIONS^1 \ \ \ \ (GND = 0 \ V, \ V_{REF} = V_{DD} = 3 \ V \pm 10\% \ to \ 5 \ V \pm 10\%. \ \ All \ specifications \ \ -40^\circ C \ to \ \ +105^\circ C \ unless \ otherwise \ noted.)$

| Parameter                                                                                                                                                                                                 | Y Version                                                                 | Unit                                             | <b>Test Conditions/Comments</b>                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE<br>Signal to (Noise + Distortion) Ratio <sup>1</sup><br>Total Harmonic Distortion (THD) <sup>1</sup><br>Peak Harmonic or Spurious Noise <sup>1</sup>                                  | 58<br>66<br>66                                                            | dB min<br>dB max<br>dB max                       | $f_{IN} = 30 \text{ kHz}, f_{SAMPLE} = 350 \text{ kHz}$                    |

| Intermodulation Distortion <sup>2</sup><br>2nd Order Terms<br>3rd Order Terms                                                                                                                             | -67<br>-67                                                                | dB typ<br>dB typ                                 | fa = 29.1 kHz, fb = 29.8 kHz                                               |

| DC ACCURACY<br>Resolution                                                                                                                                                                                 | 10                                                                        | Bits                                             |                                                                            |

| Minimum Resolution for Which<br>No Missing Codes Are Guaranteed<br>Relative Accuracy <sup>1</sup><br>Differential Nonlinearity (DNL) <sup>1</sup><br>Gain Error <sup>1</sup><br>Offset Error <sup>1</sup> | $ \begin{array}{c} 10 \\ \pm 1 \\ \pm 1 \\ \pm 2 \\ \pm 2.0 \end{array} $ | Bits<br>LSB max<br>LSB max<br>LSB max<br>LSB max |                                                                            |

| ANALOG INPUT                                                                                                                                                                                              |                                                                           |                                                  |                                                                            |

| Input Voltage Range<br>Input Leakage Current <sup>2</sup><br>Input Capacitance <sup>2</sup>                                                                                                               | $\begin{matrix} 0 \\ V_{REF} \\ \pm 1 \\ 20 \end{matrix}$                 | V min<br>V max<br>μA max<br>pF max               |                                                                            |

| REFERENCE INPUTS <sup>2</sup>                                                                                                                                                                             |                                                                           | · · ·                                            |                                                                            |

| V <sub>REF</sub> Input Voltage Range                                                                                                                                                                      | 1.2<br>V <sub>DD</sub>                                                    | V min<br>V max                                   |                                                                            |

| Input Leakage Current<br>Input Capacitance                                                                                                                                                                | ±3<br>15                                                                  | μA max<br>pF max                                 |                                                                            |

| LOGIC INPUTS <sup>2</sup><br>$V_{INH}$ , Input High Voltage<br>$V_{INL}$ , Input Low Voltage<br>Input Current, I <sub>IN</sub><br>Input Capacitance, C <sub>IN</sub>                                      | $2.0 \\ 0.4 \\ \pm 1 \\ 8$                                                | V min<br>V max<br>μA max<br>pF max               | (0.8 V max, $V_{DD}$ = 5 V)<br>Typically 10 nA, $V_{IN}$ = 0 V to $V_{DD}$ |

| LOGIC OUTPUTS<br>Output High Voltage, V <sub>OH</sub><br>Output Low Voltage, V <sub>OL</sub><br>High Impedance Leakage Current<br>High Impedance Capacitance                                              | $2.4 \\ 0.4 \\ \pm 1 \\ 15$                                               | V min<br>V max<br>µA max<br>pF max               | $I_{SOURCE} = 200 \ \mu A$ $I_{SINK} = 200 \ \mu A$                        |

| CONVERSION RATE<br>Conversion Time<br>Track/Hold Acquisition Time <sup>1</sup>                                                                                                                            | 2.3<br>100                                                                | μs max<br>ns max                                 |                                                                            |

| POWER SUPPLY<br>V <sub>DD</sub><br>I <sub>DD</sub>                                                                                                                                                        | 2.7–5.5                                                                   | Volts                                            | For Specified Performance<br>Digital Inputs = 0 V or V <sub>DD</sub>       |

| Normal Operation<br>Power-Down<br>Power Dissipation                                                                                                                                                       | 3.5<br>1                                                                  | mA max<br>μA max                                 | $V_{DD} = 5 V$                                                             |

| Normal Operation<br>Power-Down<br>Auto Power-Down                                                                                                                                                         | 17.5<br>5                                                                 | mW max<br>µW max                                 | $V_{DD} = 5 V$<br>$V_{DD} = 3 V$                                           |

| 1 kSPS Throughput<br>10 kSPS Throughput<br>100 kSPS Throughput                                                                                                                                            | 34.6<br>346.5<br>3.46                                                     | μW max<br>μW max<br>mW max                       |                                                                            |

NOTES

<sup>1</sup>See Terminology section.

<sup>2</sup>Sample tested during initial release and after any redesign or process change that may affect this parameter.

Specifications subject to change without notice.

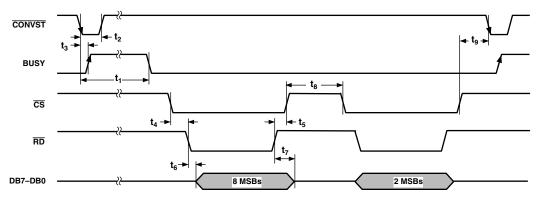

| Parameter             | $V_{DD}$ = 3 V ± 10% | $V_{DD} = 5 V \pm 10\%$ | Unit     | Conditions/Comments                                                                             |

|-----------------------|----------------------|-------------------------|----------|-------------------------------------------------------------------------------------------------|

| t <sub>POWER-UP</sub> | 1.5                  | 1.5                     | μs (max) | Power-Up Time of AD7813 after Rising Edge of CONVST.                                            |

| t <sub>1</sub>        | 2.3                  | 2.3                     | μs (max) | Conversion Time.                                                                                |

| t <sub>2</sub>        | 20                   | 20                      | ns (min) | CONVST Pulsewidth.                                                                              |

| t <sub>3</sub>        | 30                   | 30                      | ns (max) | CONVST Falling Edge to BUSY Rising Edge Delay.                                                  |

| t <sub>4</sub>        | 0                    | 0                       | ns (min) | $\overline{\text{CS}}$ to $\overline{\text{RD}}$ Setup Time.                                    |

| t <sub>5</sub>        | 0                    | 0                       | ns (min) | $\overline{\text{CS}}$ Hold Time after $\overline{\text{RD}}$ High.                             |

| $t_{6}^{3}$           | 10                   | 10                      | ns (max) | Data Access Time after $\overline{RD}$ Low.                                                     |

| $t_7^{3, 4}$          | 10                   | 10                      | ns (max) | Bus Relinquish Time after $\overline{\text{RD}}$ High.                                          |

|                       | 5                    | 5                       | ns (min) |                                                                                                 |

| t <sub>8</sub>        | 10                   | 10                      | ns (min) | Minimum Time Between MSB and LSB Reads.                                                         |

| $t_9^{3}$             | 50                   | 50                      | ns (min) | Rising Edge of $\overline{CS}$ or $\overline{RD}$ to Falling Edge of $\overline{CONVST}$ Delay. |

# TIMING CHARACTERISTICS<sup>1, 2</sup> (-40°C to +105°C, unless otherwise noted)

NOTES

<sup>1</sup>Sample tested to ensure compliance.

<sup>2</sup>See Figures 12, 13 and 14.

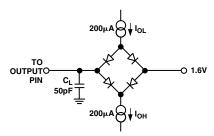

<sup>3</sup>These numbers are measured with the load circuit of Figure 1. They are defined as the time required for the o/p to cross 0.8 V or 2.4 V for V<sub>DD</sub> = 5 V  $\pm$  10% and 0.4 V or 2 V for V<sub>DD</sub> = 3 V  $\pm$  10%.

\_ ...

. . . .

<sup>4</sup>Derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 1. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the time,  $t_{7}$ , quoted in the Timing Characteristics is the true bus relinquish time of the part and as such is independent of external bus loading capacitances.

### **ABSOLUTE MAXIMUM RATINGS\***

| $V_{DD}$ to DGND                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------|

| Digital Input Voltage to DGND                                                                                                        |

| $(\overline{\text{CONVST}}, \overline{\text{RD}}, \overline{\text{CS}}) \dots -0.3 \text{ V}, \text{ V}_{\text{DD}} + 0.3 \text{ V}$ |

| Digital Output Voltage to DGND                                                                                                       |

| (BUSY, DB0–DB7)–0.3 V, V <sub>DD</sub> + 0.3 V                                                                                       |

| REF <sub>IN</sub> to AGND $\dots -0.3 \text{ V}, \text{ V}_{\text{DD}} + 0.3 \text{ V}$                                              |

| Analog Input $\dots \dots \dots$     |

| Storage Temperature Range                                                                                                            |

| Junction Temperature150°C                                                                                                            |

| Plastic DIP Package, Power Dissipation 450 mW                                                                                        |

| $\theta_{JA}$ Thermal Impedance 105°C/W                                                                                              |

| Lead Temperature, (Soldering 10 sec)                                                                                                 |

| SOIC Package, Power Dissipation 450 mW                                                                                               |

| θ <sub>JA</sub> Thermal Impedance                                                                                                    |

| Lead Temperature, Soldering                                                                                                          |

| Vapor Phase (60 sec)                                                                                                                 |

| Infrared (15 sec)                                                                                                                    |

| SSOP Package, Power Dissipation 450 mW                                                                                               |

| $\theta_{JA}$ Thermal Impedance 115°C/W                                                                                              |

| Lead Temperature, Soldering                                                                                                          |

| Vapor Phase (60 sec)                                                                                                                 |

| Infrared (15 sec)                                                                                                                    |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 1. Load Circuit for Digital Output Timing Specifications

# **ORDERING GUIDE**

| Model                             | Linearity                  | Package                                                                 | Package                |

|-----------------------------------|----------------------------|-------------------------------------------------------------------------|------------------------|

|                                   | Error                      | Description                                                             | Option                 |

| AD7813YN<br>AD7813YR<br>AD7813YRU | ±1 LSB<br>±1 LSB<br>±1 LSB | Plastic DIP<br>Small Outline IC<br>Thin Shrink Small Outline<br>(TSSOP) | N-16<br>R-16A<br>RU-16 |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7813 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

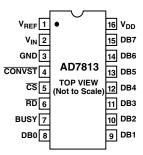

| Pin<br>No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                        |

|------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | V <sub>REF</sub> | Reference Input, 1.2 V to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                        |

| 2          | V <sub>IN</sub>  | Analog Input, 0 V to V <sub>REF</sub> .                                                                                                                                                                                                                                                                                                                            |

| 3          | GND              | Analog and Digital Ground.                                                                                                                                                                                                                                                                                                                                         |

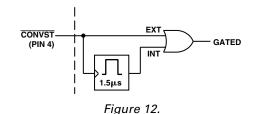

| 4          | CONVST           | Convert Start. A low-to-high transition on this pin initiates a 1.5 $\mu$ s pulse on an internally generated<br><u>CONVST</u> signal. A high-to-low transition on this line initiates the conversion process if the internal<br><u>CONVST</u> signal is low. Depending on the signal on this pin at the end of a conversion, the AD7813 automatically powers down. |

| 5          | CS               | Chip Select. This is a logic input. $\overline{CS}$ is used in conjunction with $\overline{RD}$ to enable outputs.                                                                                                                                                                                                                                                 |

| 6          | RD               | Read Pin. This is a logic input. When $\overline{CS}$ is low and $\overline{RD}$ goes low, the DB7–DB0 leave their high impedance state and data is driven onto the data bus.                                                                                                                                                                                      |

| 7          | BUSY             | ADC Busy Signal. This is a logic output. This signal goes logic high during the conversion process.                                                                                                                                                                                                                                                                |

| 8-15       | DB0–DB7          | Data Bit 0 to 7. These outputs are three-state TTL-compatible.                                                                                                                                                                                                                                                                                                     |

| 16         | V <sub>DD</sub>  | Positive power supply voltage, 2.7 V to 5.5 V.                                                                                                                                                                                                                                                                                                                     |

# PIN FUNCTION DESCRIPTIONS

# PIN CONFIGURATION DIP/SOIC

# TERMINOLOGY

# Signal to (Noise + Distortion) Ratio

This is the measured ratio of signal to (noise + distortion) at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_S/2$ ), excluding dc. The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by:

Signal to (Noise + Distortion) = (6.02N + 1.76) dB

Thus for an 10-bit converter, this is 62 dB.

### **Total Harmonic Distortion**

Total harmonic distortion (THD) is the ratio of the rms sum of harmonics to the fundamental. For the AD7813 it is defined as:

THD (dB) = 20 log

$$\frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$  and  $V_6$  are the rms amplitudes of the second through the sixth harmonics.

### Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_s/2$  and excluding dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for parts where the harmonics are buried in the noise floor, it will be a noise peak.

#### **Intermodulation Distortion**

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products at sum and difference frequencies of mfa  $\pm$  nfb where m, n = 0, 1, 2, 3, etc. Intermodulation terms are those for which neither m nor n are equal to zero. For example, the second order terms include (fa + fb) and (fa - fb), while the third order terms include (2fa + fb), (2fa - fb), (fa + 2fb) and (fa - 2fb).

The AD7813 is tested using the CCIF standard, where two input frequencies near the top end of the input bandwidth are used. In this case, the second and third order terms are of different significance. The second order terms are usually distanced in frequency from the original sine waves, while the third order terms are usually at a frequency close to the input frequencies. As a result, the second and third order terms are specified separately. The calculation of the intermodulation distortion is as per the THD specification where it is the ratio of the rms sum of the individual distortion products to the rms amplitude of the fundamental expressed in dBs.

#### **Relative Accuracy**

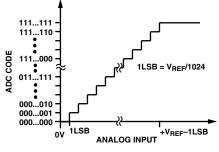

Relative accuracy or endpoint nonlinearity is the maximum deviation from a straight line passing through the endpoints of the ADC transfer function.

### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

### **Offset Error**

This is the deviation of the first code transition  $(0000 \dots 000)$  to  $(0000 \dots 001)$  from the ideal, i.e., AGND + 1 LSB.

# **Offset Error Match**

This is the difference in Offset Error between any two channels.

### **Gain Error**

This is the deviation of the last code transition (1111...110) to (1111...111) from the ideal, i.e., VREF – 1 LSB, after the offset error has been adjusted out.

### **Gain Error Match**

This is the difference in Gain Error between any two channels.

### **Track/Hold Acquisition Time**

Track/hold acquisition time is the time required for the output of the track/hold amplifier to reach its final value, within  $\pm 1/2$  LSB, after the end of conversion (the point at which the track/hold returns to track mode). It also applies to situations where a change in the selected input channel takes place or where there is a step input change on the input voltage applied to the selected V<sub>IN</sub> input of the AD7813. It means that the user must wait for the duration of the track/hold acquisition time after the end of conversion, or after a step input change to V<sub>IN</sub>, before starting another conversion, to ensure that the part operates to specification.

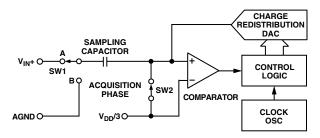

# CIRCUIT DESCRIPTION

# **Converter Operation**

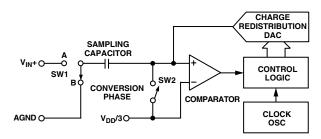

The AD7813 is a successive approximation analog-to-digital converter based around a charge redistribution DAC. The ADC can convert analog input signals in the range 0 V to  $V_{DD}$ . Figures 2 and 3 below show simplified schematics of the ADC. Figure 2 shows the ADC during its acquisition phase. SW2 is closed and SW1 is in Position A, the comparator is held in a balanced condition and the sampling capacitor acquires the signal on  $V_{IN+}$ .

Figure 2. ADC Track Phase

When the ADC starts a conversion (see Figure 3), SW2 will open and SW1 will move to Position B, causing the comparator to become unbalanced. The Control Logic and the Charge Redistribution DAC are used to add and subtract fixed amounts of charge from the sampling capacitor so as to bring the comparator back into a balanced condition. When the comparator is rebalanced the conversion is complete. The Control Logic generates the ADC output code. Figure 7 shows the ADC transfer function.

Figure 3. ADC Conversion Phase

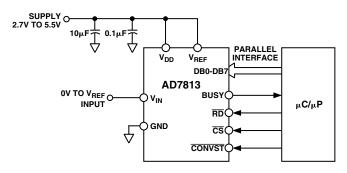

# TYPICAL CONNECTION DIAGRAM

Figure 4 shows a typical connection diagram for the AD7813. The parallel interface is implemented using an 8-bit data bus, the falling edge of  $\overline{\text{CONVST}}$  brings the BUSY signal high, and at the end of conversion the falling edge of BUSY is used to initiate an Interrupt Service Routine (ISR) on a microprocessor—see Parallel Interface section for more details. V<sub>REF</sub> is connected to a well decoupled V<sub>DD</sub> pin to provide an analog input range of 0 V to V<sub>DD</sub>. When V<sub>DD</sub> is first connected the AD7813 powers up in a low current mode, i.e., power-down. A rising edge on an internal  $\overline{\text{CONVST}}$  input will cause the part to power up—see Power-Up Times. If power consumption is of concern, the automatic power-down at the end of a conversion should be used to improve power performance. See Power vs. Throughput Rate section of the data sheet.

Figure 4. Typical Connection Diagram

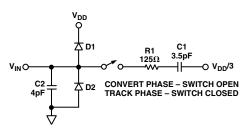

# Analog Input

Figure 5 shows an equivalent circuit of the analog input structure of the AD7813. The two diodes, D1 and D2, provide ESD protection for the analog inputs. Care must be taken to ensure that the analog input signal never exceeds the supply rails by more than 200 mV. This will cause these diodes to become forward biased and start conducting current into the substrate. The maximum current these diodes can conduct without causing irreversible damage to the part is 20 mA. The capacitor C2, in Figure 5, is typically about 4 pF and can be primarily attributed to pin capacitance. The resistor R1 is a lumped component made up of the on resistance of a multiplexer and a switch. This resistor is typically about  $125 \Omega$ . The capacitor C1 is the ADC sampling capacitor and has a capacitance of 3.5 pF.

Figure 5. Equivalent Analog Input Circuit

# **DC** Acquisition Time

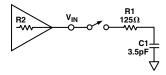

The ADC starts a new acquisition phase at the end of a conversion and ends on the falling edge of the  $\overline{\text{CONVST}}$  signal. At the end of a conversion there is a settling time associated with the sampling circuit. This settling time lasts approximately 100 ns. The analog signal on  $V_{\rm IN}$  is also being acquired during this settling time; therefore, the minimum acquisition time needed is approximately 100 ns.

Figure 6 shows the equivalent charging circuit for the sampling capacitor when the ADC is in its acquisition phase. R2 represents the source impedance of a buffer amplifier or resistive network, R1 is an internal multiplexer resistance and C1 is the sampling capacitor.

Figure 6. Equivalent Sampling Circuit

During the acquisition phase the sampling capacitor must be charged to within a 1/2 LSB of its final value. The time it takes to charge the sampling capacitor ( $T_{CHARGE}$ ) is given by the following formula:

$$T_{CHARGE} = 7.6 \times (R2 + 125 \Omega) \times 3.5 \ pF$$

For small values of source impedance, the settling time associated with the sampling circuit (100 ns) is, in effect, the acquisition time of the ADC. For example, with a source impedance (R2) of 10  $\Omega$  the charge time for the sampling capacitor is approximately 4 ns. The charge time becomes significant for source impedances of 2 k $\Omega$  and greater.

# **AC Acquisition Time**

In ac applications it is recommended to always buffer analog input signals. The source impedance of the drive circuitry must be kept as low as possible to minimize the acquisition time of the ADC. Large values of source impedance will cause the THD to degrade at high throughput rates.

# ADC TRANSFER FUNCTION

The output coding of the AD7813 is straight binary. The designed code transitions occur at successive integer LSB values (i.e., 1 LSB, 2 LSBs, etc.). The LSB size is =  $V_{REF}/1024$ . The ideal transfer characteristic for the AD7813 is shown in Figure 7.

Figure 7. Transfer Characteristic

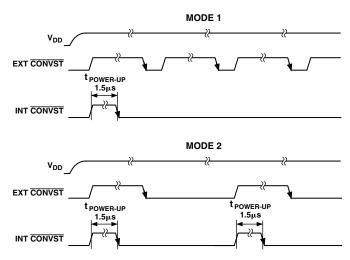

# **POWER-UP TIMES**

The AD7813 has a 1.5  $\mu$ s power-up time. When V<sub>DD</sub> is first connected, the AD7813 is in a low current mode of operation. In order to carry out a conversion the AD7813 must first be powered up. The ADC is powered up by a rising edge on an internally generated  $\overline{\text{CONVST}}$  signal, which occurs as a result of a rising edge on the external  $\overline{\text{CONVST}}$  pin. The rising edge of the external  $\overline{\text{CONVST}}$  signal initiates a 1.5  $\mu$ s pulse on the internal  $\overline{\text{CONVST}}$  signal. This pulse is present to ensure the part has enough time to power up before a conversion is initiated, as a conversion is initiated on the falling edge of gated  $\overline{\text{CONVST}}$ . See Timing and Control section. Care must be taken to ensure that the  $\overline{\text{CONVST}}$  pin of the AD7813 is logic low when V<sub>DD</sub> is first applied.

When operating in Mode 2, the ADC is powered down at the end of each conversion and powered up again before the next conversion is initiated. (See Figure 8.)

Figure 8. Power-Up Times

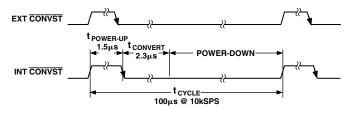

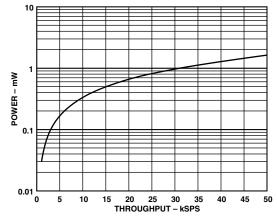

### POWER VS. THROUGHPUT RATE

By operating the AD7813 in Mode 2, the average power consumption of the AD7813 decreases at lower throughput rates.

Figure 9 shows how the Automatic Power-Down is implemented using the external  $\overrightarrow{\text{CONVST}}$  signal to achieve the optimum power performance for the AD7813. The AD7813 is operated in Mode 2, and the duration of the external  $\overrightarrow{\text{CONVST}}$  pulse is set to be equal to or less than the power-up time of the device. As the throughput rate is reduced, the device remains in its powerdown state longer and the average power consumption over time drops accordingly.

### Figure 9. Automatic Power-Down

For example, if the AD7813 is operated in a continuous sampling mode, with a throughput rate of 10 kSPS, the power consumption is calculated as follows. The power dissipation during normal operation is 10.5 mW,  $V_{DD}$  = 3 V. If the power-up time is 1.5 µs and the conversion time is 2.3 µs, the AD7813 can then be said to dissipate 10.5 mW for 3.8 µs (worst-case) during each conversion cycle. If the throughput rate is 10 kSPS, the cycle time is 100 µs and the average power dissipated during each cycle is (3.8/100) × (10.5 mW) = 400 µW.

# **Typical Performance Characteristics**

Figure 10. Power vs. Throughput

# TIMING AND CONTROL

The AD7813 has only one input for timing and control, i.e., the CONVST (convert start signal). The rising edge of this CONVST signal initiates a 1.5 µs pulse on an internally generated  $\overline{\text{CONVST}}$  signal. This pulse is present to ensure the part has enough time to power up before a conversion is initiated. If the external **CONVST** signal is low, the falling edge of the internal **CONVST** signal will cause the sampling circuit to go into hold mode and initiate a conversion. If, however, the external CONVST signal is high when the internal CONVST goes low, it is upon the falling edge of the external CONVST signal that the sampling circuitry will go into hold mode and initiate a conversion. The use of the internally generated 1.5 µs pulse, as previously described, can be likened to the configuration shown in Figure 12. The application of a CONVST signal at the  $\overline{\text{CONVST}}$  pin triggers the generation of a 1.5 µs pulse. Both the external  $\overline{\text{CONVST}}$  and this internal  $\overline{\text{CONVST}}$  are input to an OR gate. The resulting signal has the duration of the longer of the two input signals. Once a conversion has been initiated the BUSY signal goes high to indicate a conversion is in progress.

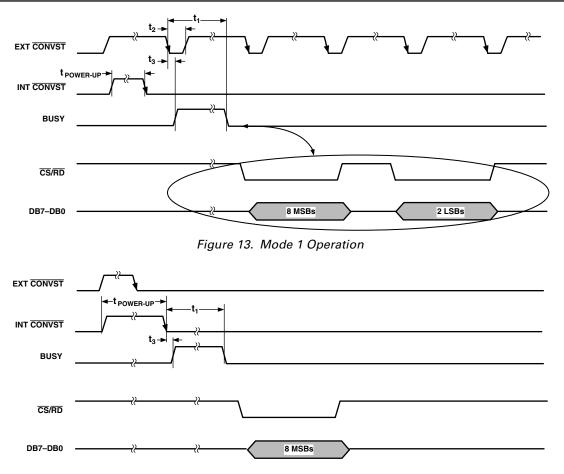

At the end of conversion the sampling circuit goes back into its tracking mode again. The end of conversion is indicated by the BUSY signal going low. This signal may be used to initiate an ISR on a microprocessor. At this point the conversion result is latched into the output register where it may be read. The AD7813 has an 8-bit wide parallel interface. The 10-bit conversion result is accessed by performing two successive read operations. The first 8-bit read accesses the 8 MSBs of the conversion result and the second read accesses the 2 LSBs, as illustrated in Figure 13, where one performance of the two successive reads is highlighted after the falling edge of BUSY. The state of the external CONVST signal at the end of conversion also establishes the mode of operation of the AD7813.

### Mode 1 Operation (High Speed Sampling)

If the external CONVST is logic high when BUSY goes low, the part is said to be in Mode 1 operation. While operating in Mode 1, the AD7813 will not power down between conversions. The AD7813 should be operated in Mode 1 for high speed sampling applications, i.e., throughputs greater than 100 kSPS. Figure 13 shows the timing for Mode 1 operation. From this diagram one can see that a minimum delay of the sum of the conversion time and read time must be left between two successive falling edges of the external CONVST. This is to ensure that a conversion is not initiated during a read.

### Mode 2 Operation (Automatic Power-Down)

At slower throughput rates the AD7813 may be powered down between conversions to give a superior power performance. This is Mode 2 Operation and it is achieved by bringing the CONVST signal logic low before the falling edge of BUSY. Figure 14, overleaf, shows the timing for Mode 2 Operation. The falling edge of the external  $\overline{\text{CONVST}}$  signal may occur before or after the falling edge of the internal **CONVST** signal, but it is the later occurring falling edge of both that controls when the first conversion will take place. If the falling edge of the external **CONVST** occurs after that of the internal CONVST, it means that the moment of the first conversion is controlled exactly, regardless of any jitter associated with the internal  $\overline{\text{CONVST}}$  signal. The parallel interface is still fully operational while the AD7813 is powered down. The AD7813 is powered up again on the rising edge of the  $\overline{\text{CONVST}}$  signal. The gated **CONVST** pulse will now remain high long enough for the AD7813 to fully power up, which takes about 1.5 µs. This is ensured by the internal CONVST signal, which will remain high for 1.5 µs.

Figure 14. Mode 2 Operation

# PARALLEL INTERFACE

The parallel interface of the AD7813 is eight bits wide. The output data buffers are activated when both  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  are logic low. At this point the contents of the data register are placed on the 8-bit data bus. Figure 15 shows the timing diagram for the parallel port. As previously explained, two successive read operations must take place in order to access the 10-bit conversion result. The first read places the 8 MSBs on the data bus and the second read places the 2 LSBs on the data bus. The 2 LSBs appear on DB7 and DB6, with DB5–DB0 set to logic zero.

Further read operations will access the 8 MSBs and 2 LSBs of the 10-bit ADC conversion result again. The parallel interface of the AD7813 is reset when BUSY goes logic high. This feature allows the AD7813 to be used as an 8-bit converter if the user only wishes to access the 8 MSBs of the conversion. Care must be taken to ensure that a read operation does not occur while BUSY is high. Data read from the AD7813 while BUSY is high will be invalid. For optimum performance the read operation should end at least 100 ns ( $t_{10}$ ) prior to the falling edge of the next CONVST.

Figure 15. Parallel Port Timing

# MICROPROCESSOR INTERFACING

The parallel port on the AD7813 allows the device to be interfaced to a range of many different microcontrollers. This section explains how to interface the AD7813 with some of the more common microcontroller parallel interface protocols.

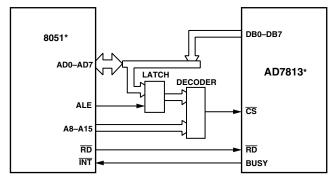

# AD7813 to 8051

Figure 16 shows a parallel interface between the AD7813 and the 8051 microcontroller. The BUSY signal on the AD7813 provides an interrupt request to the 8051 when a conversion begins. Port 0 of the 8051 may serve as an input or output port, or as in this case when used together, may be used as a bidirectional low-order address and data bus. The address latch enable output of the 8051 is used to latch the low byte of the address during accesses to the device, while the high-order address byte is supplied from Port 2. Port 2 latches remain stable when the AD7813 is addressed, as they do not have to be turned around (set to 1) for data input as is the case for Port 0.

\*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 16. Interfacing to the 8051

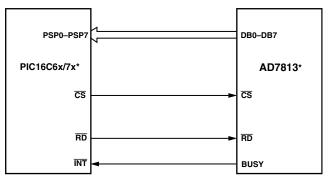

# AD7813 to PIC16C6x/7x

Figure 17 shows a parallel interface between the AD7813 and the PIC16C64/65/74. The BUSY signal on the AD7813 provides an interrupt request to the microcontroller when a conversion begins. Of the PIC16C6x/7x range of microcontrollers only the PIC16C64/65/74 can provide the option of a parallel slave port. Port D of the microcontroller will operate as an 8-bit wide parallel slave port when control bit PSPMODE in the TRISE register is set. Setting PSPMODE enables the port pin RE0 to be the  $\overline{\text{RD}}$  output and RE2 to be the  $\overline{\text{CS}}$  output. For this functionality, the corresponding data direction bits of the TRISE register must be configured as outputs (reset to 0). See PIC16/17 Microcontroller User Manual.

\*ADDITIONAL PINS OMITTED FOR CLARITY

Figure 17. Interfacing to the PIC16C6x/7x

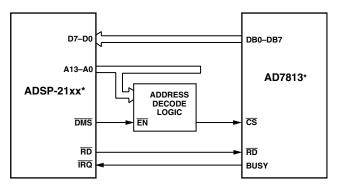

# AD7813 to ADSP-21xx

Figure 18 shows a parallel interface between the AD7813 and the ADSP-21xx series of DSPs. As before, the BUSY signal on the AD7813 provides an interrupt request to the DSP when a conversion begins.

\*ADDITIONAL PINS OMITTED FOR CLARITY Figure 18. Interfacing to the ADSP-21xx

**OUTLINE DIMENSIONS** Dimensions shown in inches and (mm).

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

AD7813YNZ AD7813YRUZ AD7813YRZ-REEL7 AD7813YRZ AD7813YRUZ-REEL7