16-bit resolution and monotonicity

## ANALOG Single-Channel, 16-Bit Current and Voltage DAC with DEVICES Dynamic Power Control and HART Connectivity **Dynamic Power Control and HART Connectivity**

**Data Sheet** AD5753

#### **FEATURES**

Positive and negative DPC for thermal management Current or voltage output available on a single terminal Current output ranges: 0 mA to 20 mA, 4 mA to 20 mA, 0 mA to 24 mA, ±20 mA, ±24 mA, and -1 mA to +22 mA Voltage output ranges (with 20% overrange): 0 V to 5 V, 0 V to 10 V, ±5 V, and ±10 V User programmable offset and gain Advanced on-chip diagnostics, including a 12-bit ADC 2 external ADC input pins **On-chip reference** Robust architecture, including output fault protection -40°C to +115°C temperature range 40-lead, 6 mm × 6 mm LFCSP package

## **APPLICATIONS**

**Process control Actuator control** Channel isolated analog outputs Programmable logic controller (PLC) and distributed control systems (DCS) applications **HART network connectivity**

#### **GENERAL DESCRIPTION**

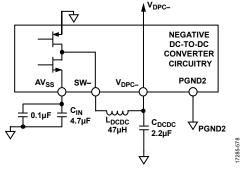

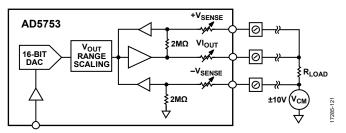

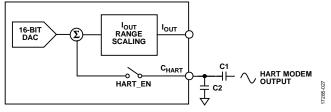

The AD5753 is a single-channel, voltage and current output digital-to-analog converter (DAC) that operates with a power supply range from a minimum of -33 V on AVss to a maximum of +33 V on AV<sub>DD1</sub> with a maximum operating voltage of 60 V between the two rails. On-chip dynamic power control (DPC) minimizes package power dissipation. This minimization is achieved by using buck dc-to-dc converters optimized for minimum on-chip power dissipation to regulate the voltage  $(V_{DPC+} \text{ and } V_{DPC-})$  that is sent to the  $VI_{OUT}$  output driver circuitry from the  $\pm 5$  V to  $\pm 27$  V supply voltage. The  $C_{HART}$  pin enables a Highway Addressable Remote Transducer® (HART) signal to be coupled on the current output.

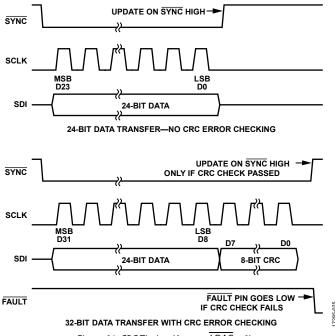

The AD5753 uses a versatile, 4-wire, serial peripheral interface (SPI) that operates at clock rates of up to 50 MHz and is compatible with standard SPI, QSPI™, MICROWIRE™, digital signal processor (DSP), and microcontroller interface standards. The interface features an optional SPI cyclic redundancy check (CRC) and a watchdog timer (WDT). The AD5753 offers improved diagnostic features from earlier versions of similar DACs, such as output current monitoring and an integrated, 12-bit diagnostic analog-to-digital converter (ADC). The inclusion of a line protector on the VI<sub>OUT</sub>, +V<sub>SENSE</sub>, and -V<sub>SENSE</sub> pins provides additional robustness.

#### **PRODUCT HIGHLIGHTS**

- Range of advanced diagnostic features, including integrated ADC with two external input pins.

- DPC, using integrated buck dc-to-dc converters for thermal management, which enables higher channel count in small size module housing.

- 3. Programmable power control (PPC) mode to enable faster than DPC settling time (15 µs typical).

- Highly robust with output protection from miswire events (±38 V).

- 5. HART compliant.

#### **COMPANION PRODUCTS**

Product Family: AD5758, AD5755-1, AD5422

HART Modems: AD5700, AD5700-1

External References: ADR431, ADR3425, ADR4525

Digital Isolators: ADuM142D, ADuM141D Power: LT8300, ADP2360, ADM6339, ADP1031

Trademarks and registered trademarks are the property of their respective owners.

**Data Sheet**

## **AD5753**

## **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Product Highlights                          | 1  |

| Companion Products                          | 1  |

| Revision History                            | 2  |

| Functional Block Diagram                    | 3  |

| Specifications                              | 4  |

| AC Performance Characteristics              | 10 |

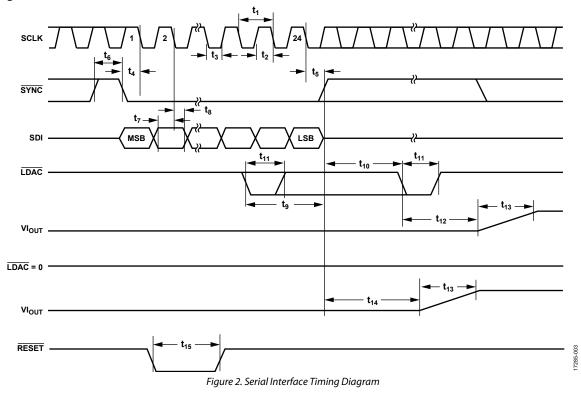

| Timing Characteristics                      | 11 |

| Absolute Maximum Ratings                    | 15 |

| Thermal Resistance                          | 15 |

| ESD Caution                                 | 15 |

| Pin Configuration and Function Descriptions | 16 |

| Typical Performance Characteristics         | 18 |

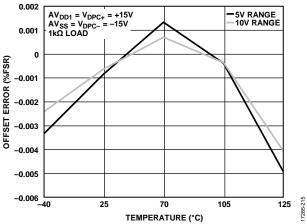

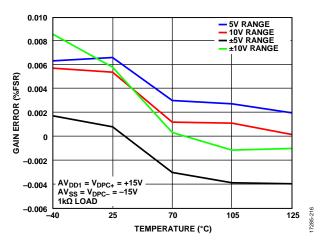

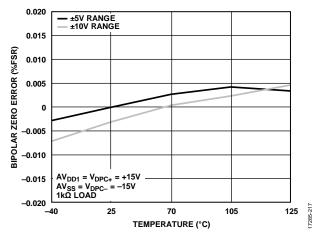

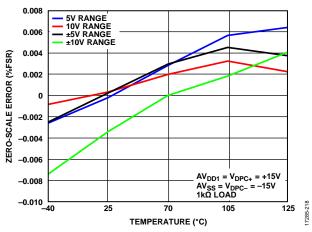

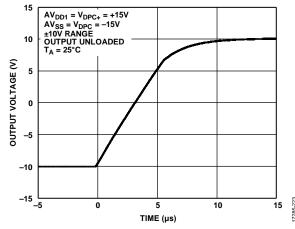

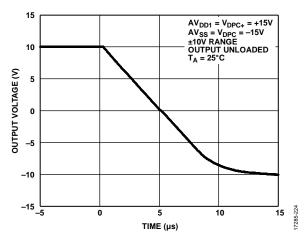

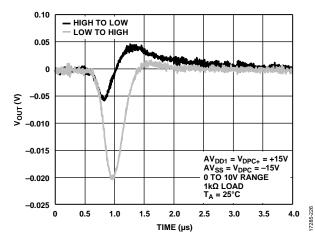

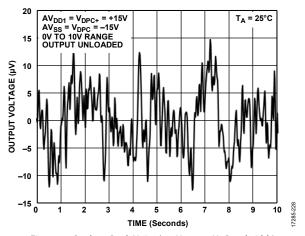

| Voltage Output                              | 18 |

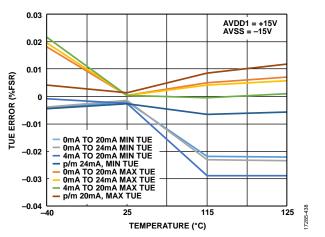

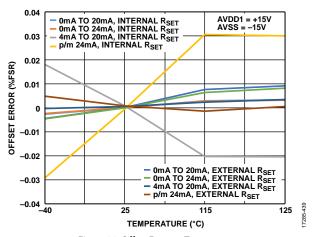

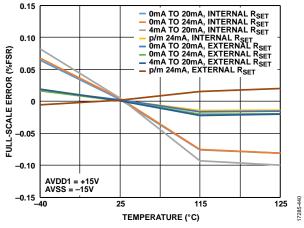

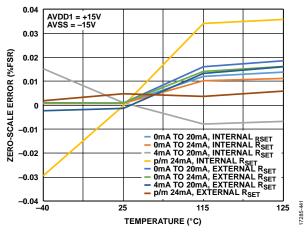

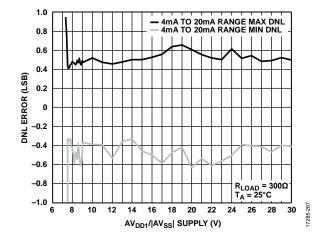

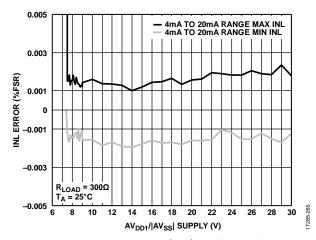

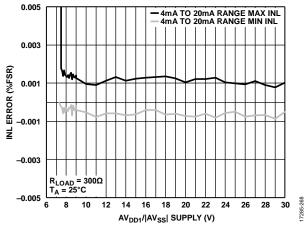

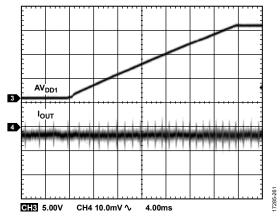

| Current Outputs                             | 22 |

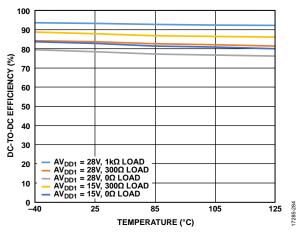

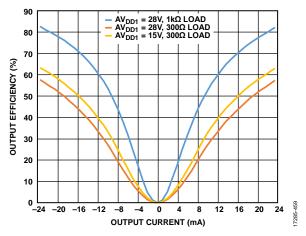

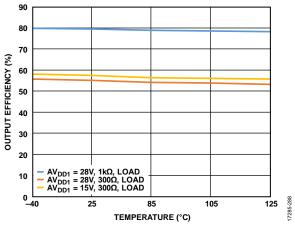

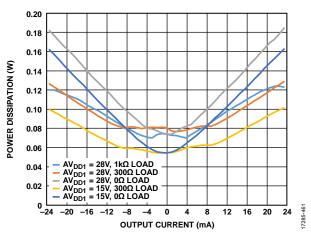

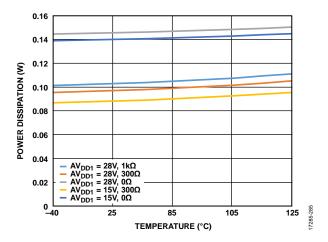

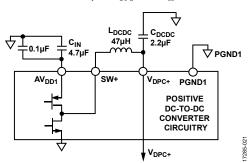

| DC-to-DC Block                              | 27 |

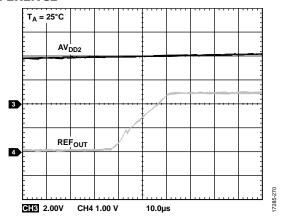

| Reference                                   | 28 |

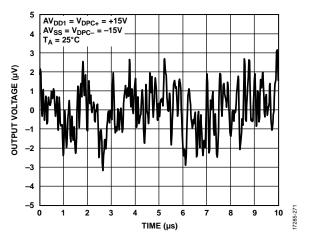

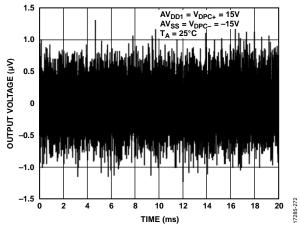

| General                                     | 29 |

| Terminology                                 | 30 |

| Theory of Operation                         | 32 |

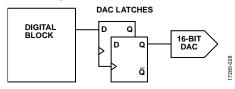

| DAC Architecture                            | 32 |

| Serial Interface                            | 32 |

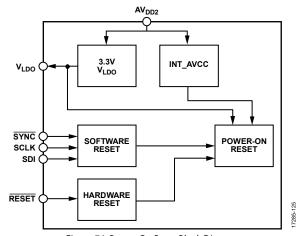

| Power-On State of the AD5753                | 33 |

| Power Supply Considerations                 | 33 |

| Device Features and Diagnostics             | 35 |

| Power Dissipation Control                   | 35 |

| Interdie 3-Wire Interface                   | 36 |

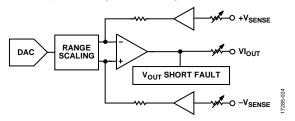

| 7   | Voltage Output                                   | 37 |

|-----|--------------------------------------------------|----|

| F   | Fault Protection                                 | 37 |

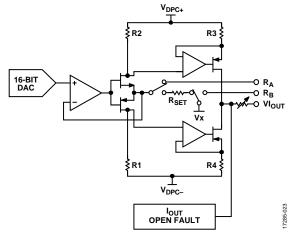

| (   | Current Output                                   | 38 |

| ŀ   | HART Connectivity                                | 38 |

| Ι   | Digital Slew Rate Control                        | 38 |

| A   | Address Pins                                     | 39 |

| V   | WDT                                              | 40 |

| Ţ   | User Digital Offset and Gain Control             | 40 |

| Ι   | DAC Output Update and Data Integrity Diagnostics | 41 |

| (   | GPIO Pins                                        | 42 |

| Ţ   | Use of Key Codes                                 | 42 |

| S   | Software Reset                                   | 42 |

| (   | Calibration Memory CRC                           | 42 |

| I   | nternal Oscillator Diagnostics                   | 43 |

| S   | Sticky Diagnostic Results Bits                   | 43 |

| F   | Background Supply and Temperature Monitoring     | 43 |

| (   | Output Fault                                     | 43 |

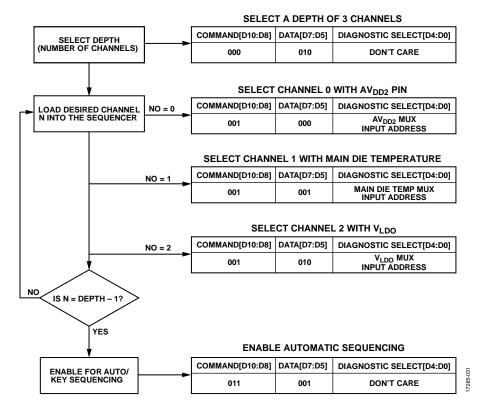

| A   | ADC Monitoring                                   | 44 |

| Reg | gister Map                                       | 49 |

| V   | Writing to Registers                             | 49 |

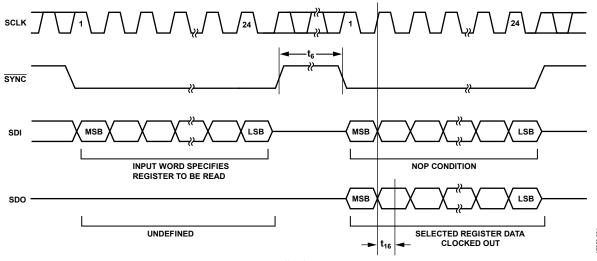

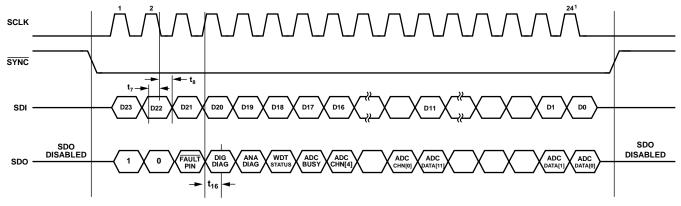

| F   | Reading from Registers                           | 50 |

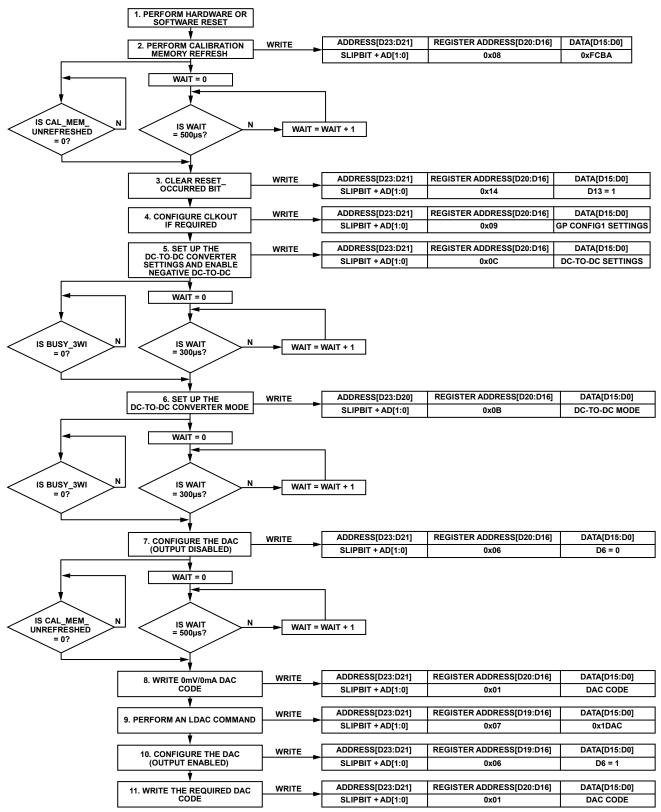

| F   | Programming Sequence to Enable the Output        | 53 |

| F   | Register Details                                 | 55 |

| Apj | plications Information                           | 71 |

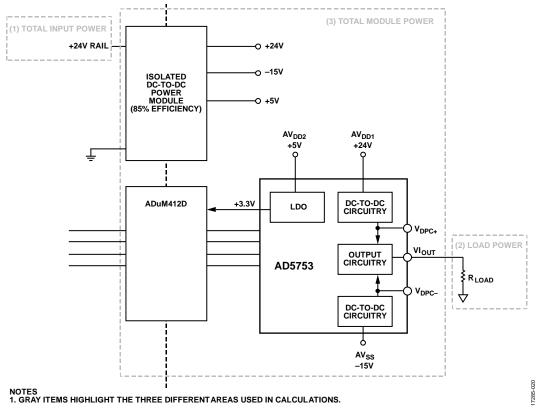

| I   | Example Module Power Calculation                 | 71 |

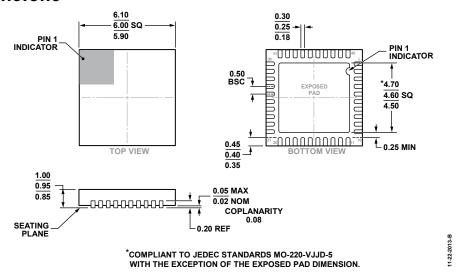

| Ou  | tline Dimensions                                 | 73 |

| (   | Ordering Guide                                   | 73 |

## **REVISION HISTORY**

5/2019—Revision 0: Initial Version

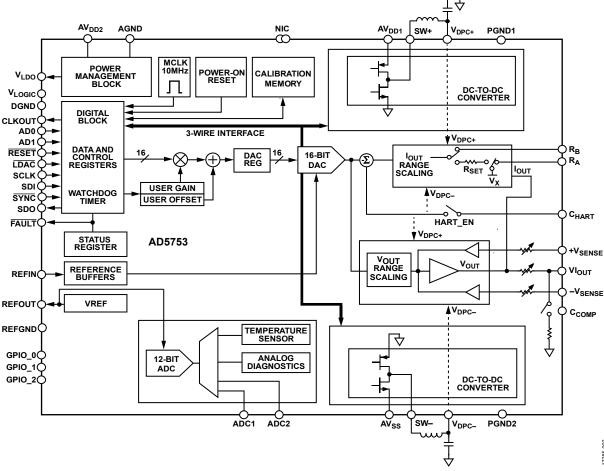

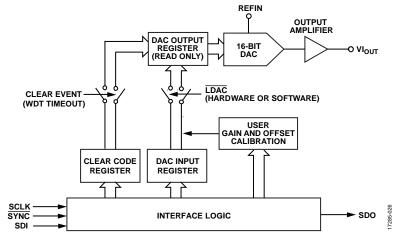

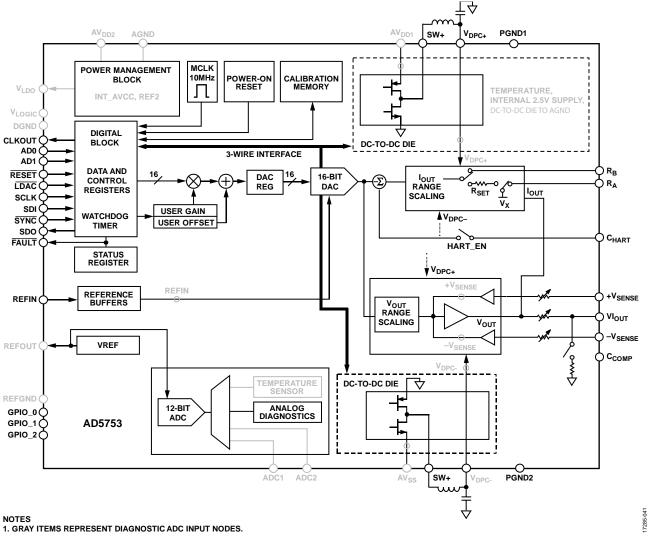

## **FUNCTIONAL BLOCK DIAGRAM**

## **SPECIFICATIONS**

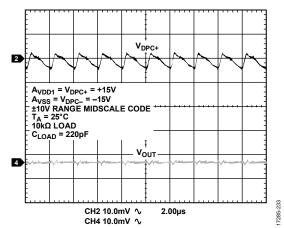

$AV_{DD1} = V_{DPC+} = 15 \text{ V, dc-to-dc converter disabled, } \\ AV_{DD2} = 5 \text{ V, } \\ AV_{SS} = V_{DPC-} = -15 \text{ V, } \\ V_{LOGIC} = 1.71 \text{ V to } 5.5 \text{ V, } \\ AGND = DGND = REFGND = PGND1 = 0 \text{ V, } \\ REFIN = 2.5 \text{ V external, voltage output: load resistance } \\ (R_{LOAD}) = 1 \text{ k}\Omega, \text{ load capacitor } \\ (C_{LOAD}) = 220 \text{ pF, current output: } \\ R_{LOAD} = 300 \text{ }\Omega. \text{ All specifications at } \\ T_A = -40^{\circ}\text{C to } +115^{\circ}\text{C, } \\ T_J \text{ (junction temperature)} < 125^{\circ}\text{C, unless otherwise noted.} \\ N_{AB} = 1.71 \text{ V to } \\ N_{AB} = 1.71 \text{$

Table 1.

| Parameter                                                     | Min    | Тур    | Max    | Unit       | Test Conditions/Comments                                                        |

|---------------------------------------------------------------|--------|--------|--------|------------|---------------------------------------------------------------------------------|

| OUTPUT VOLTAGE (V <sub>OUT</sub> )                            | 0      |        | 5      | V          | Trimmed V <sub>OUT</sub> ranges                                                 |

|                                                               | 0      |        | 10     | V          |                                                                                 |

|                                                               | -5     |        | +5     | V          |                                                                                 |

|                                                               | -10    |        | +10    | V          |                                                                                 |

| Output Voltage Overranges                                     | 0      |        | 6      | V          | Untrimmed overranges                                                            |

| . 3                                                           | 0      |        | 12     | V          |                                                                                 |

|                                                               | -6     |        | +6     | V          |                                                                                 |

|                                                               | -12    |        | +12    | V          |                                                                                 |

| Output Voltage Offset Ranges                                  | -0.3   |        | +5.7   | v          | Untrimmed negatively offset ranges                                              |

| o aspar voltage o liser hanges                                | -0.4   |        | +11.6  | v          | Chamming negatively chiservaliges                                               |

| Resolution                                                    | 16     |        | 111.0  | Bits       |                                                                                 |

| VOLTAGE OUTPUT ACCURACY                                       | 10     |        |        | Dits       | Loaded and unloaded, accuracy specifications                                    |

| VOLIAGE OUTFUT ACCORACT                                       |        |        |        |            | refer to trimmed V <sub>OUT</sub> ranges only, unless otherwise noted           |

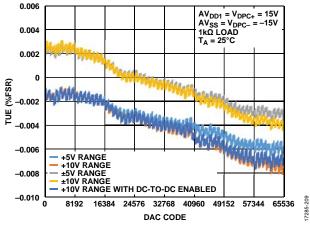

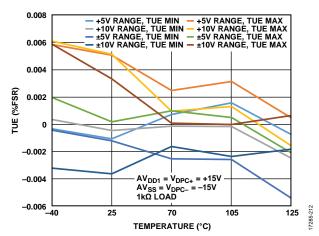

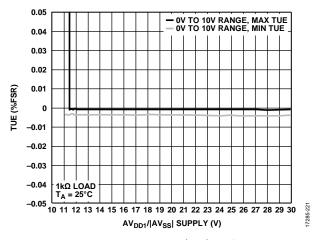

| Total Unadjusted Error (TUE)                                  | -0.05  |        | +0.05  | % FSR      |                                                                                 |

| •                                                             | -0.01  |        | +0.01  | % FSR      | T <sub>A</sub> = 25°C                                                           |

| TUE Long-Term Stability <sup>1</sup>                          |        | 15     |        | ppm FSR    | Drift after 1000 hours, T <sub>J</sub> = 150°C                                  |

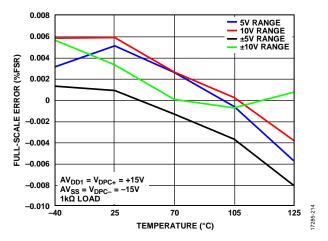

| Output Drift                                                  |        | 0.35   | 1.5    | ppm FSR/°C | Output drift                                                                    |

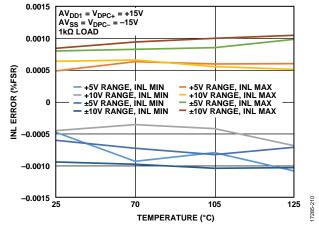

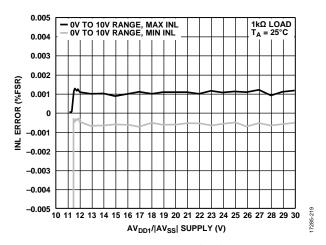

| Integral Nonlinearity (INL)                                   | -0.006 |        | +0.006 | % FSR      | All ranges                                                                      |

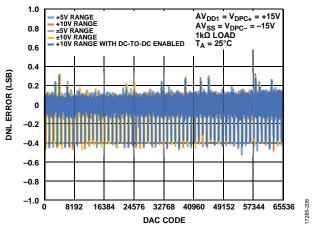

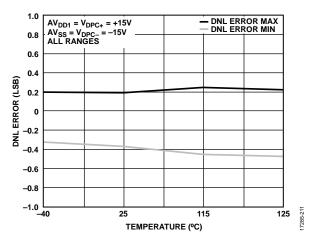

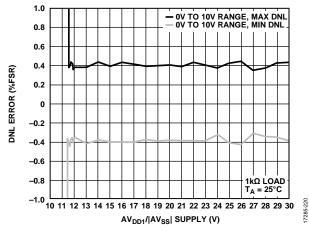

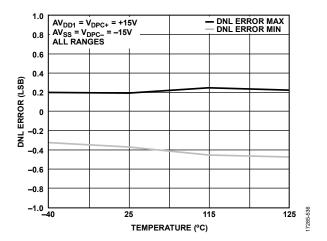

| Differential Nonlinearity (DNL)                               | -1     |        | +1     | LSB        | Guaranteed monotonic, all ranges                                                |

| Zero-Scale Error                                              | -0.02  | ±0.002 | +0.02  | % FSR      |                                                                                 |

| Zero-Scale Error Temperature<br>Coefficient (TC) <sup>2</sup> |        | ±0.3   |        | ppm FSR/°C |                                                                                 |

| Bipolar Zero Error                                            | -0.017 | +0.001 | +0.017 | % FSR      | ±5 V, ±10 V                                                                     |

| Bipolar Zero Error TC <sup>2</sup>                            |        | ±0.4   |        | ppm FSR/°C | ±5 V, ±10 V                                                                     |

| Offset Error                                                  | -0.022 | ±0.002 | +0.022 | % FSR      | ,                                                                               |

| Offset Error TC <sup>2</sup>                                  |        | ±0.3   |        | ppm FSR/°C |                                                                                 |

| Gain Error                                                    | -0.022 | ±0.001 | +0.022 | % FSR      |                                                                                 |

| Gain Error TC <sup>2</sup>                                    |        | ±0.6   |        | ppm FSR/°C |                                                                                 |

| Full-Scale Error                                              | -0.022 | ±0.001 | +0.022 | % FSR      |                                                                                 |

| Full-Scale Error TC <sup>2</sup>                              |        | ±0.5   |        | ppm FSR/°C |                                                                                 |

| VOLTAGE OUTPUT CHARACTERISTICS                                |        |        |        | Tr.        |                                                                                 |

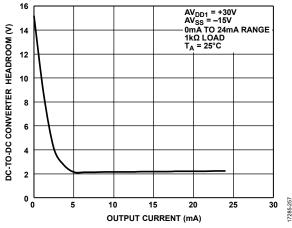

| Headroom                                                      | 2      |        |        | V          | Minimum voltage required between VI <sub>OUT</sub> and                          |

|                                                               |        |        |        |            | V <sub>DPC+</sub> supply                                                        |

| Footroom                                                      | 2      |        |        | V          | Minimum voltage required between VI <sub>OUT</sub> and V <sub>DPC</sub> supply  |

| Short-Circuit Current                                         |        | 16     |        | mA         | ,                                                                               |

| Load <sup>2</sup>                                             | 1      |        |        | kΩ         | For specified performance                                                       |

| Capacitive Load Stability <sup>2</sup>                        |        |        | 10     | nF         |                                                                                 |

| ,                                                             |        |        | 2      | μF         | External compensation capacitor of 220 pF connected                             |

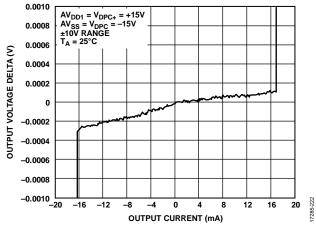

| DC Output Impedance                                           |        | 7      |        | mΩ         |                                                                                 |

| DC Power Supply Rejection<br>Ratio (PSRR)                     |        | 10     |        | μV/V       |                                                                                 |

| Vout and -Vsense Common-<br>Mode Rejection Ratio<br>(CMRR)    |        | 10     |        | μV/V       | Error in V <sub>OUT</sub> voltage due to changes in –V <sub>SENSE</sub> voltage |

| Parameter                                                         | Min          | Тур            | Max    | Unit                | Test Conditions/Comments                               |

|-------------------------------------------------------------------|--------------|----------------|--------|---------------------|--------------------------------------------------------|

| OUTPUT CURRENT (Iout)                                             | 0            |                | 24     | mA                  |                                                        |

|                                                                   | 0            |                | 20     | mA                  |                                                        |

|                                                                   | 4            |                | 20     | mA                  |                                                        |

|                                                                   | -20          |                | +20    | mA                  |                                                        |

|                                                                   | -24          |                | +24    | mA                  |                                                        |

|                                                                   | -1           |                | +22    | mA                  |                                                        |

| Resolution                                                        | 16           |                |        | Bits                |                                                        |

| CURRENT OUTPUT ACCURACY (EXTERNAL R <sub>SET</sub> ) <sup>3</sup> |              |                |        |                     | Assumes ideal 13.7 kΩ resistor                         |

| Unipolar Ranges                                                   |              |                |        |                     | 4 mA to 20 mA, 0 mA to 20 mA, and 0 mA to 24 mA ranges |

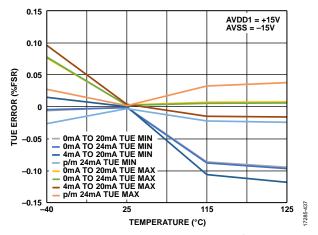

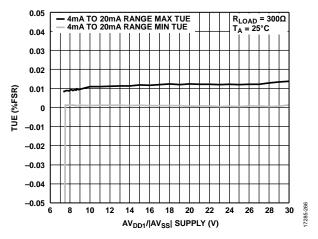

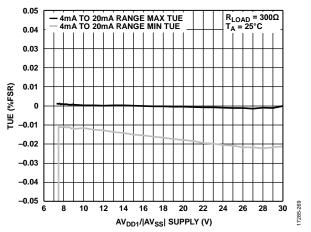

| TUE                                                               | -0.05        |                | +0.05  | % FSR               | _                                                      |

|                                                                   | -0.01        |                | +0.01  | % FSR               | T <sub>A</sub> = 25°C                                  |

| TUE Long-Term Stability                                           |              | 125            |        | ppm FSR             | Drift after 1000 hours, T <sub>J</sub> = 150°C         |

| Output Drift                                                      |              | 2              | 5      | ppm FSR/°C          |                                                        |

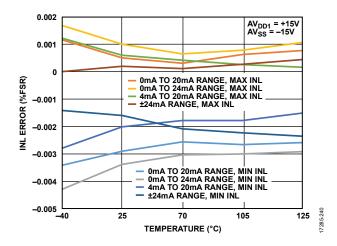

| INL                                                               | -0.007       |                | +0.007 | % FSR               |                                                        |

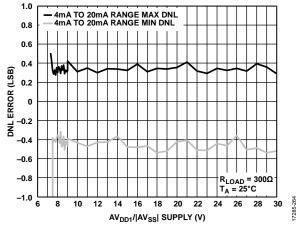

| DNL                                                               | -1           |                | +1     | LSB                 | Guaranteed monotonic                                   |

| Zero-Scale Error                                                  | -0.03        | ±0.002         | +0.03  | % FSR               |                                                        |

| Zero-Scale TC <sup>2</sup>                                        |              | ±0.5           |        | ppm FSR/°C          |                                                        |

| Offset Error                                                      | -0.03        | ±0.001         | +0.03  | % FSR               |                                                        |

| Offset Error TC <sup>2</sup>                                      |              | ±0.7           |        | ppm FSR/°C          |                                                        |

| Gain Error                                                        | -0.05        | ±0.002         | +0.05  | % FSR               |                                                        |

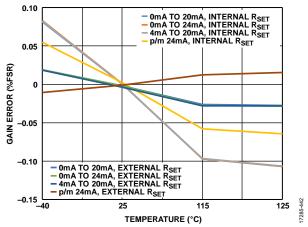

| Gain Error TC <sup>2</sup>                                        | 0.00         | ±3             | . 0.00 | ppm FSR/°C          |                                                        |

| Full-Scale Error                                                  | -0.05        | ±0.002         | +0.05  | % FSR               |                                                        |

| Full-Scale Error TC <sup>2</sup>                                  | 0.03         | ±3             | 10.03  | ppm FSR/°C          |                                                        |

| Bipolar Ranges                                                    |              | <u> </u>       |        | ppiiii Siv C        | ±20 mA, ±24 mA, and -1 mA to +22 mA range              |

| TUE                                                               | -0.06        |                | +0.06  | % FSR               | 220 m/, 22 m/, and 1 m/ (6 + 22 m/ (ange.              |

| 101                                                               | -0.012       |                | +0.012 | % FSR               | T <sub>A</sub> = 25°C                                  |

| TUE Long-Term Stability <sup>1</sup>                              | 0.012        | 125            | 10.012 | ppm FSR             | Drift after 1000 hours, T <sub>J</sub> = 150°C         |

| Output Drift                                                      |              | 123            | 15.5   | ppm FSR/°C          | Diff after 1000 flours, 1) = 130 C                     |

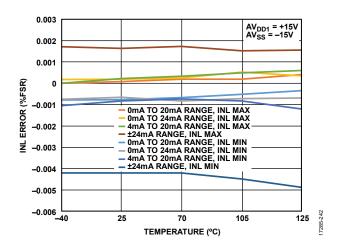

| INL                                                               | -0.013       | 12             | +0.013 | % FSR               |                                                        |

| DNL                                                               | -0.013<br>-1 |                | +1     | LSB                 | Guaranteed monotonic                                   |

| Zero-Scale Error                                                  | -0.04        | ±0.003         | +0.04  | % FSR               | duaranteed monotonic                                   |

| Zero-Scale TC <sup>2</sup>                                        | -0.04        | ±0.003<br>±0.5 | +0.04  | ppm FSR/°C          |                                                        |

|                                                                   | -0.02        | ±0.5<br>±0.003 | +0.02  | % FSR               |                                                        |

| Bipolar Zero Error                                                | -0.02        |                | +0.02  |                     |                                                        |

| Bipolar Zero Error TC <sup>2</sup><br>Offset Error                | -0.04        | ±0.4<br>±0.002 | +0.04  | ppm FSR/°C<br>% FSR |                                                        |

| Offset Error TC <sup>2</sup>                                      | -0.04        |                | +0.04  |                     |                                                        |

|                                                                   | 0.06         | ±0.6<br>±0.002 | .0.06  | ppm FSR/°C          |                                                        |

| Gain Error                                                        | -0.06        |                | +0.06  | % FSR               |                                                        |

| Gain Error TC <sup>2</sup>                                        | 0.06         | ±3             | . 0.06 | ppm FSR/°C          |                                                        |

| Full-Scale Error                                                  | -0.06        | ±0.003         | +0.06  | % FSR               |                                                        |

| Full-Scale Error TC <sup>2</sup>                                  |              | ±3             |        | ppm FSR/°C          |                                                        |

| CURRENT OUTPUT ACCURACY (INTERNAL RSET)                           |              |                |        |                     |                                                        |

| Unipolar Ranges                                                   |              |                |        |                     | 4 mA to 20 mA, 0 mA to 20 mA, and 0 mA to 24 mA ranges |

| TUE                                                               | -0.12        |                | +0.12  | % FSR               | 27 mainges                                             |

|                                                                   | -0.12        | 380            | +0.12  |                     | Drift after 1000 hours, T₁ = 150°C                     |

| TUE Long-Term Stability <sup>1</sup>                              |              |                | 6      | ppm FSR             |                                                        |

| Output Drift                                                      | 0.01         | 3              | 6      | ppm FSR/°C          | Output drift                                           |

| INL                                                               | -0.01        |                | +0.01  | % FSR               | Cuaranteed monetonic                                   |

| DNL                                                               | -1           | 10.001         | +1     | LSB                 | Guaranteed monotonic                                   |

| Zero-Scale Error                                                  | -0.04        | ±0.001         | +0.04  | % FSR               |                                                        |

| Zero-Scale TC <sup>2</sup>                                        | 0.04         | ±0.5           | .001   | ppm FSR/°C          |                                                        |

| Offset Error                                                      | -0.04        | ±0.001         | +0.04  | % FSR               |                                                        |

| Parameter                                      | Min      | Тур    | Max   | Unit       | Test Conditions/Comments                                                                                                                        |

|------------------------------------------------|----------|--------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset Error TC <sup>2</sup>                   |          | ±1     |       | ppm FSR/°C |                                                                                                                                                 |

| Gain Error                                     | -0.1     | ±0.003 | +0.1  | % FSR      |                                                                                                                                                 |

| Gain Error TC <sup>2</sup>                     |          | ±3     |       | ppm FSR/°C |                                                                                                                                                 |

| Full-Scale Error                               | -0.12    | ±0.003 | +0.12 | % FSR      |                                                                                                                                                 |

| Full-Scale Error TC <sup>2</sup>               |          | ±3     |       | ppm FSR/°C |                                                                                                                                                 |

| Bipolar Ranges                                 |          |        |       |            | $\pm$ 20 mA, $\pm$ 24 mA, and $-$ 1 mA to $\pm$ 22 mA ranges                                                                                    |

| TUE                                            | -0.12    |        | +0.12 | % FSR      |                                                                                                                                                 |

| TUE Long-Term Stability <sup>1</sup>           |          | 380    |       | ppm FSR    | Drift after 1000 hours, T <sub>J</sub> = 150°C                                                                                                  |

| Output Drift                                   |          | 3      | 6     | ppm FSR/°C | Output drift                                                                                                                                    |

| INL                                            | -0.02    |        | +0.02 | % FSR      |                                                                                                                                                 |

| DNL                                            | -1       |        | +1    | LSB        | Guaranteed monotonic                                                                                                                            |

| Zero-Scale Error                               | -0.06    | ±0.001 | +0.06 | % FSR      |                                                                                                                                                 |

| Zero-Scale TC <sup>2</sup>                     |          | ±2     |       | ppm FSR/°C |                                                                                                                                                 |

| Bipolar Zero Error                             | -0.02    | ±0.002 | +0.02 | % FSR      |                                                                                                                                                 |

| Bipolar Zero Error TC <sup>2</sup>             |          | ±0.3   |       | ppm FSR/°C |                                                                                                                                                 |

| Offset Error                                   | -0.06    | ±0.001 | +0.06 | % FSR      |                                                                                                                                                 |

| Offset Error TC <sup>2</sup>                   |          | ±1     |       | ppm FSR/°C |                                                                                                                                                 |

| Gain Error                                     | -0.12    | ±0.003 | +0.12 | % FSR      |                                                                                                                                                 |

| Gain Error TC <sup>2</sup>                     |          | ±3     |       | ppm FSR/°C |                                                                                                                                                 |

| Full-Scale Error                               | -0.12    | ±0.003 | +0.12 | % FSR      |                                                                                                                                                 |

| Full-Scale Error TC <sup>2</sup>               |          | ±3     |       | ppm FSR/°C |                                                                                                                                                 |

| CURRENT OUTPUT CHARACTERISTICS                 |          |        |       |            |                                                                                                                                                 |

| Headroom                                       | 2.3      |        |       | V          | Minimum voltage required between Vlout and VDPC+ supply                                                                                         |

| Footroom                                       | 2.3 or 0 |        |       | V          | Minimum voltage required between Vlout and VDPC- supply; unipolar ranges do not require any footroom and takes on the 0 value                   |

| Resistive Load <sup>2</sup>                    |          |        | 1000  | Ω          | The dc-to-dc converter is characterized with a maximum load of 1 k $\Omega$ , chosen such that headroom and footroom compliance is not exceeded |

| Output Impedance                               |          | 100    |       | ΜΩ         | Midscale output                                                                                                                                 |

| DC PSRR                                        |          | 0.1    |       | μA/V       | '                                                                                                                                               |

| REFERENCE INPUT/OUTPUT                         |          |        |       | •          |                                                                                                                                                 |

| Reference Input                                |          |        |       |            |                                                                                                                                                 |

| Reference Input Voltage <sup>4</sup>           |          | 2.5    |       | V          | For specified performance                                                                                                                       |

| DC Input Impedance                             | 55       | 120    |       | ΜΩ         |                                                                                                                                                 |

| Reference Output                               |          |        |       |            |                                                                                                                                                 |

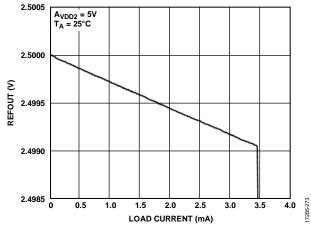

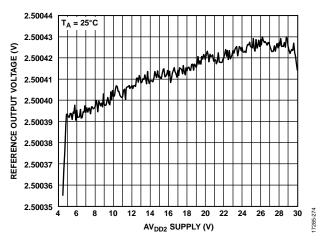

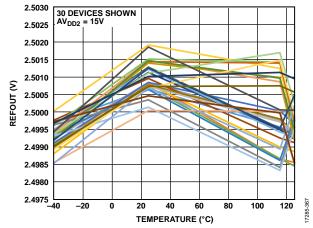

| Output Voltage                                 | 2.495    | 2.5    | 2.505 | V          | $T_A = 25$ °C (including drift after 1000 hours at $T_J = 150$ °C)                                                                              |

| Reference TC <sup>2</sup>                      | -10      |        | +10   | ppm/°C     | ,                                                                                                                                               |

| Output Noise (0.1 Hz to<br>10 Hz) <sup>2</sup> |          | 7      |       | μV p-p     |                                                                                                                                                 |

| Noise Spectral Density <sup>2</sup>            |          | 80     |       | nV/√Hz     | At 10 kHz                                                                                                                                       |

| Capacitive Load <sup>2</sup>                   |          |        | 1000  | nF         |                                                                                                                                                 |

| Load Current                                   |          | 3      |       | mA         |                                                                                                                                                 |

| Short-Circuit Current                          |          | 5      |       | mA         |                                                                                                                                                 |

| Line Regulation                                |          | 1      |       | ppm/V      |                                                                                                                                                 |

| Load Regulation                                |          | 140    |       | ppm/mA     |                                                                                                                                                 |

|                                                | 1        |        |       | rr,,       |                                                                                                                                                 |

| Parameter                                                                           | Min   | Тур  | Max     | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------|-------|------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

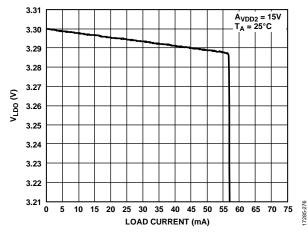

| V <sub>LDO</sub> OUTPUT                                                             |       |      |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Output Voltage                                                                      |       | 3.3  |         | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Output Voltage TC <sup>2</sup>                                                      |       | 30   |         | ppm/°C |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Output Voltage Accuracy                                                             | -2    |      | +2      | %      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Externally Available Current                                                        |       |      | 30      | mA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Short-Circuit Current                                                               |       | 55   |         | mA     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Load Regulation                                                                     |       | 0.8  |         | mV/mA  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Capacitive Load                                                                     |       | 0.1  |         | μF     | Recommended operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DC-TO-DC                                                                            |       |      |         |        | - Necestime and operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Start-Up Time                                                                       |       | 1.25 |         | ms     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Switch                                                                              |       | 1.23 |         | 1113   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

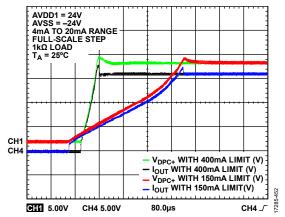

| Peak Current Limit <sup>2</sup>                                                     | 150   |      | 400     | l mA   | User programmable in 50 mA steps via the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                     | 130   |      | 400     | IIIA   | DCDC_CONFIG2 register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

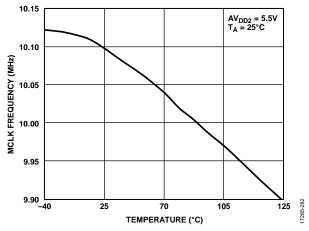

| Oscillator                                                                          |       |      |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Oscillator Frequency (f <sub>sw</sub> )                                             |       | 500  |         | kHz    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Minimum Duty Cycle                                                                  |       | 5    |         | %      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Current Output DPC Mode                                                             |       |      |         |        | Current output dynamic power control mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>DPC+</sub> and V <sub>DPC-</sub> Voltage<br>Range                            | ±4.95 |      | ±27     | V      | Assuming sufficient supply margin between $AV_{DD1}$ and $V_{DPC+}$ , and $AV_{SS}$ and $V_{DPC-}$ ; see the Power Dissipation Control section for further details; maximum operating range of $ V_{DPC+}$ to $V_{DPC-}  = 50 \text{ V}$                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>DPC+</sub> and V <sub>DPC-</sub> Headroom                                    |       | 2.3  | 2.5     | V      | Typical voltage headroom between $V_{\text{DPC+}}$ and $V_{\text{DPC+}}$ ; only applicable when dc-to-dc converter is in regulation, that is, when the load is sufficiently high                                                                                                                                                                                                                                                                                                                                                                                                                    |

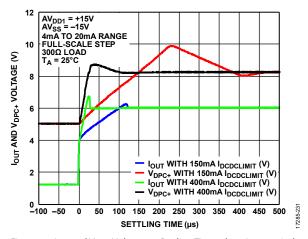

| Current Output PPC Mode                                                             |       |      |         |        | Programmable power control mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DPC+</sub> and V <sub>DPC-</sub> Voltage<br>Range                            | ±5    |      | ±25.677 | V      | Assuming sufficient supply margin between $(AV_{DD1} \text{ and } V_{DPC+})$ and $(AV_{SS} \text{ and } V_{DPC-})$ ; see the Power Dissipation Control section for further details; maximum operating range of $ V_{DPC+} $ to $ V_{DPC-}  = 50 \text{ V}$                                                                                                                                                                                                                                                                                                                                          |

| $V_{DPC+}$ and $V_{DPC-}$ Voltage Accuracy                                          | -500  |      | +500    | mV     | Only applicable when dc-to-dc is operating in regulation, that is, when the load is sufficiently high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Voltage Output DPC Mode<br>V <sub>DPC+</sub> and V <sub>DPC-</sub> Voltage<br>Range | ±5    | ±15  | ±25     | V      | Voltage output dynamic power control mode $5 \text{ V} = -\text{V}_{\text{SENSE}(MIN)} + 15 \text{ V}; 25 \text{ V} = -\text{V}_{\text{SENSE}(MAX)} + 15 \text{ V};$ where $\text{V}_{\text{SENSE}(MIN)} = -10 \text{ V}$ and $\text{V}_{\text{SENSE}(MAX)} = +10 \text{ V};$ assuming sufficient supply margin between $\text{AV}_{DD1}$ and $\text{V}_{\text{DPC+}}$ , and $\text{AV}_{\text{SS}}$ and $\text{V}_{\text{DPC-}}$ ; see the Power Dissipation Control section for further details; maximum operating range of $ \text{V}_{\text{DPC+}}$ to $\text{V}_{\text{DPC-}}  = 50 \text{ V}$ |

| V <sub>DPC+</sub> and V <sub>DPC</sub> – Voltage<br>Accuracy                        | -250  |      | +250    | mV     | Only applicable when dc-to-dc is operating in regulation, that is, when the is load sufficiently high                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| VI <sub>OUT</sub> LINE PROTECTOR                                                    |       |      |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| On Resistance, R <sub>ON</sub>                                                      |       | 12   |         | Ω      | T <sub>A</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Overvoltage Response Time,<br>t <sub>response</sub>                                 |       | 250  |         | ns     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Overvoltage Leakage Current                                                         |       | ±100 |         | μΑ     | Line protector fault detect block sinks current for a positive fault and sources current for a negative fault                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Parameter                                                     | Min                      | Тур                   | Max                      | Unit  | Test Conditions/Comments                                                            |

|---------------------------------------------------------------|--------------------------|-----------------------|--------------------------|-------|-------------------------------------------------------------------------------------|

| ADC                                                           |                          |                       |                          |       |                                                                                     |

| Resolution                                                    |                          | 12                    |                          | Bits  |                                                                                     |

| Input Voltage Range                                           |                          |                       |                          |       |                                                                                     |

| ADC1 Pin                                                      | 0                        |                       | 0.5                      | V     | ADC_IP_SELECT = 10000                                                               |

|                                                               | -0.5                     |                       | +0.5                     | V     | ADC_IP_SELECT = 10010, AVss must be $\leq -1 \text{ V}$                             |

|                                                               | 0                        |                       | 1.25                     | V     | ADC_IP_SELECT = 01111                                                               |

|                                                               | 0                        |                       | 2.5                      | V     | ADC_IP_SELECT = 10001                                                               |

| ADC2 Pin                                                      | <b>–15</b>               |                       | +15                      | V     |                                                                                     |

| Total Error                                                   |                          |                       |                          |       |                                                                                     |

| ADC1 Pin                                                      | -0.25                    |                       | +0.25                    | % FSR | 2.5 V input range                                                                   |

| 7.50.1.111                                                    | -0.3                     |                       | +0.3                     | % FSR | 1.25 V input range                                                                  |

|                                                               | -0.5                     |                       | +0.5                     | % FSR | 0 V to 0.5 V and ±0.5 V input ranges                                                |

| ADC2 Pin                                                      | -0.5<br>-0.5             |                       | +0.5                     | % FSR | o v to 0.5 v and ±0.5 v input ranges                                                |

| All other ADC Inputs                                          | -0.5                     | ±0.3                  | T0.5                     | % FSR | Table 18 lists all ADC input nodes                                                  |

|                                                               |                          |                       |                          |       | Table 18 lists all ADC Input Houes                                                  |

| Conversion Time <sup>2</sup>                                  |                          | 100                   |                          | μς    |                                                                                     |

| GENERAL-PURPOSE INPUT/OUTPUT OUTPUT                           |                          |                       |                          |       |                                                                                     |

| Isource or Isink <sup>5</sup>                                 |                          | $V_{LOGIC}/1~k\Omega$ |                          | mA    | Assume 1 $k\Omega$ is connected to the GPIO pin                                     |

| Output Voltage                                                |                          |                       |                          |       |                                                                                     |

| Low, V <sub>OL</sub>                                          |                          |                       | 0.4                      | V     | Isource = 2 mA                                                                      |

| High, V <sub>он</sub>                                         | $V_{\text{LOGIC}} - 0.2$ |                       |                          | V     | I <sub>SOURCE</sub> = 2 mA                                                          |

| GPIO INPUT                                                    |                          |                       |                          |       |                                                                                     |

| Input Voltage                                                 |                          |                       |                          |       |                                                                                     |

| High, V <sub>ℍ</sub>                                          | $0.7 \times V_{LOGIC}$   |                       |                          | V     |                                                                                     |

| Low, V <sub>IL</sub>                                          |                          |                       | $0.3 \times V_{LOGIC}$   | V     |                                                                                     |

| Input Current                                                 |                          | 1.35                  |                          | μΑ    |                                                                                     |

| Input Capacitance                                             |                          | 2.6                   |                          | pF    |                                                                                     |

| DIGITAL OUTPUTS                                               |                          |                       |                          | ρ.    |                                                                                     |

| SDO                                                           |                          |                       |                          |       |                                                                                     |

| Output Voltage                                                |                          |                       |                          |       |                                                                                     |

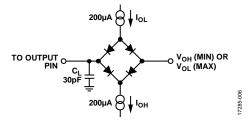

| Low, Vol                                                      |                          |                       | 0.4                      | V     | Sinking = 200 μA                                                                    |

| High, V <sub>OH</sub>                                         | $V_{LOGIC} - 0.2$        |                       | 0.4                      | V     | Sourcing = 200 μA                                                                   |

| High Impedance Leakage                                        | -1                       |                       | +1                       | μΑ    | Sourcing – 200 μA                                                                   |

| Current                                                       | -1                       |                       | +1                       | μΑ    |                                                                                     |

| High Impedance Output                                         |                          | 2.2                   |                          | pF    |                                                                                     |

| Capacitance <sup>2</sup>                                      |                          | 2.2                   |                          | Pi    |                                                                                     |

| FAULT .                                                       |                          |                       |                          |       |                                                                                     |

| Output Voltage                                                |                          |                       |                          |       |                                                                                     |

| Low, Vol                                                      |                          |                       | 0.4                      | V     | 10 kΩ pull-up resistor to V <sub>LOGIC</sub>                                        |

| LOW, VOL                                                      |                          | 0.6                   | 0.4                      | V     | At 2.5 mA                                                                           |

| High, V <sub>OH</sub>                                         | V <sub>LOGIC</sub> –     | 0.0                   |                          | V     | 10 kΩ pull-up resistor to V <sub>LOGIC</sub>                                        |

| підп, уон                                                     | 0.05                     |                       |                          | \ \ \ | 10 K2 pull-up resistor to vlogic                                                    |

| DIGITAL INPUTS                                                | 0.03                     |                       |                          |       |                                                                                     |

| Input Voltage                                                 |                          |                       |                          |       |                                                                                     |

| $3 \text{ V} \leq \text{V}_{\text{LOGIC}} \leq 5.5 \text{ V}$ |                          |                       |                          |       |                                                                                     |

| High, V <sub>H</sub>                                          | $0.7 \times V_{LOGIC}$   |                       |                          | V     |                                                                                     |

| Low, V <sub>IL</sub>                                          | O., A VLOGIC             |                       | $0.3 \times V_{LOGIC}$   | V     |                                                                                     |

| 1.71 V $\leq$ V <sub>LOGIC</sub> $<$ 3 V                      |                          |                       | U.J A V LOGIC            | *     |                                                                                     |

|                                                               | 0.8 × V <sub>LOGIC</sub> |                       |                          | V     |                                                                                     |

| High, V <sub>H</sub>                                          | U.O X VLOGIC             |                       | 02×1/                    | V     |                                                                                     |

| Low, V <sub>IL</sub>                                          | 1.5                      |                       | 0.2 × V <sub>LOGIC</sub> | 1 -   | Day win intermed well down an CCLY CDI DECET                                        |

| Input Current                                                 | -1.5                     |                       | +1.5                     | μΑ    | Per pin, internal pull-down on SCLK, SDI, RESET, and LDAC; internal pull-up on SYNC |

| Pin Capacitance <sup>2</sup>                                  |                          | 2.4                   |                          | pF    | Per pin                                                                             |

| Parameter                              | Min   | Тур   | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                                                                                                                        |

|----------------------------------------|-------|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER REQUIREMENTS                     |       | -     |      |      |                                                                                                                                                                                                                                                                                                                 |

| Supply Voltages                        |       |       |      |      |                                                                                                                                                                                                                                                                                                                 |

| AV <sub>DD1</sub> <sup>6</sup>         | 7     |       | 33   | V    | Maximum operating range of $ AV_{DD1} $ to $AV_{SS} = 60 \text{ V}$                                                                                                                                                                                                                                             |

| $AV_DD2$                               | 5     |       | 33   | V    | Maximum operating range of $ AV_{DD2} $ to $AV_{SS} = 50 \text{ V}$                                                                                                                                                                                                                                             |

| AV <sub>SS</sub> <sup>6</sup>          | -33   |       | 0    | V    | Maximum operating range of $ AV_{DD1}$ to $AV_{SS}  = 60 \text{ V}$ ; for bipolar output ranges, $V_{OUT}$ or $I_{OUT}$ headroom must be obeyed when calculating $AV_{SS}$ maximum; for unipolar current output ranges, $AV_{SS}$ maximum = 0 V; for unipolar voltage output ranges, $AV_{SS}$ maximum = -2.5 V |

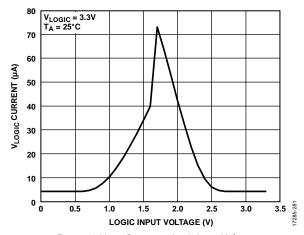

| $V_{LOGIC}$                            | 1.71  |       | 5.5  | V    |                                                                                                                                                                                                                                                                                                                 |

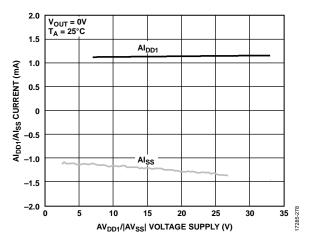

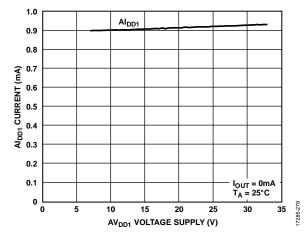

| Supply Quiescent Currents <sup>6</sup> |       |       |      |      | Quiescent current, assuming no load current                                                                                                                                                                                                                                                                     |

| Al <sub>DD1</sub> <sup>7</sup>         |       | 0.05  | 0.11 | mA   | Voltage output mode, dc-to-dc converter enabled but not active                                                                                                                                                                                                                                                  |

|                                        |       | 0.05  | 0.11 | mA   | Current output mode, dc-to-dc converter enabled but not active                                                                                                                                                                                                                                                  |

| $Al_{DD2}^7$                           |       | 3.3   | 3.6  | mA   | Voltage output mode, dc-to-dc converter enabled but not active                                                                                                                                                                                                                                                  |

|                                        |       | 2.9   | 3.1  | mA   | Current output mode, dc-to-dc converter enabled but not active                                                                                                                                                                                                                                                  |

| Alss <sup>7</sup>                      | -0.11 | -0.05 |      | mA   | Voltage output mode                                                                                                                                                                                                                                                                                             |

|                                        | -0.11 | 0.05  |      | mA   | Current output mode                                                                                                                                                                                                                                                                                             |

| I <sub>LOGIC</sub> 7                   |       |       | 0.01 | mA   | $V_{IH} = V_{LOGIC}, V_{IL} = DGND$                                                                                                                                                                                                                                                                             |

| I <sub>DPC+</sub> <sup>7</sup>         |       | 1.0   | 1.3  | mA   | Voltage output mode                                                                                                                                                                                                                                                                                             |

|                                        |       | 0.8   | 1    | mA   | Unipolar current output mode                                                                                                                                                                                                                                                                                    |

|                                        |       | 2.3   | 3.1  | mA   | Bipolar current output mode                                                                                                                                                                                                                                                                                     |

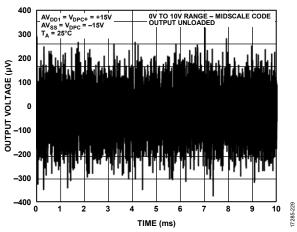

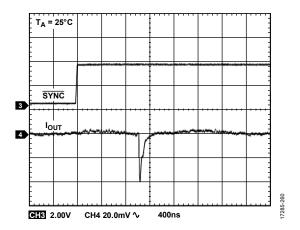

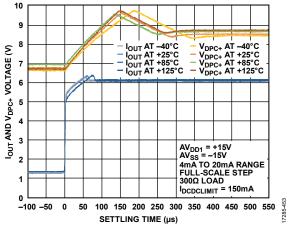

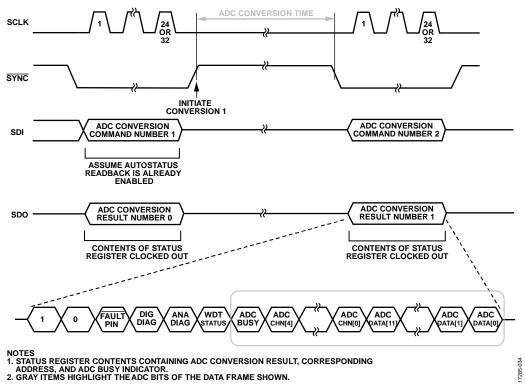

| I <sub>DPC</sub> <sup>7</sup>          | -1.3  | -1.0  |      | mA   | Voltage output mode                                                                                                                                                                                                                                                                                             |