# Universal Input Analog Front End with 24-Bit ADC for Industrial Process Control Systems

Data Sheet AD4110-1

### **FEATURES**

2 software programmable input terminals

Current up to ±20 mA Voltage up to ±10 V Thermocouple

RTC

**Replaces existing 3-terminal solutions**

Field power supply for loop powered current sensors

HV input overvoltage protected up to  $\pm 30\,\text{V}$

Internal current sense resistor

Option to use external current sense resistor

Current limited input even with no power supply

Diagnostic functions for overrange and open wire detect

Fast and flexible output data rates: 5 SPS to 125 kSPS

16 noise free bits at 62 kSPS

18 noise free bits at 2.5 kSPS

20 noise free bits at 50 SPS/60 SPS

Simultaneous 50 Hz and 60 Hz rejection

Serial interface for configuration and diagnostics

4-wire interface compatible with SPI®, QSPI™,

MICROWIRE®, and DSP

Power supply:  $\pm 12 \text{ V}$  to  $\pm 20 \text{ V}$ ,  $\pm 5 \text{ V}$

Operating temperature: -40°C to +105°C

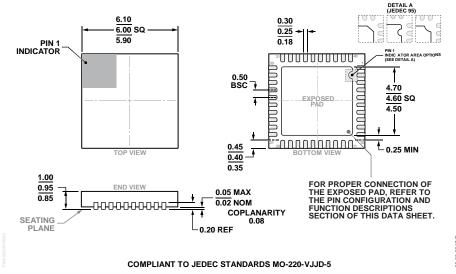

Package: 40-lead, 6 mm × 6 mm LFCSP

### **APPLICATIONS**

Process control and industrial automation Remote and distributed control systems Instrumentation and measurement Sensor and data acquisition

#### **GENERAL DESCRIPTION**

The AD4110-1 is a complete, single-channel, universal input analog-to-digital front end for industrial process control systems where sensor type flexibility is required.

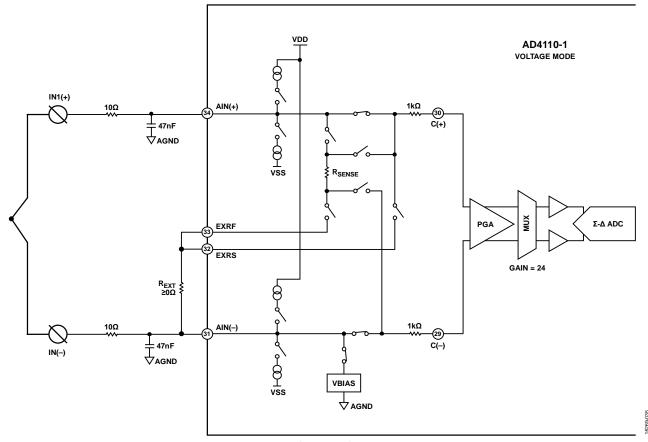

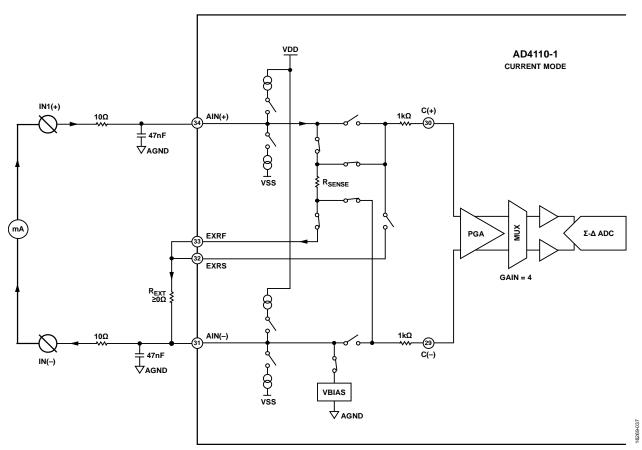

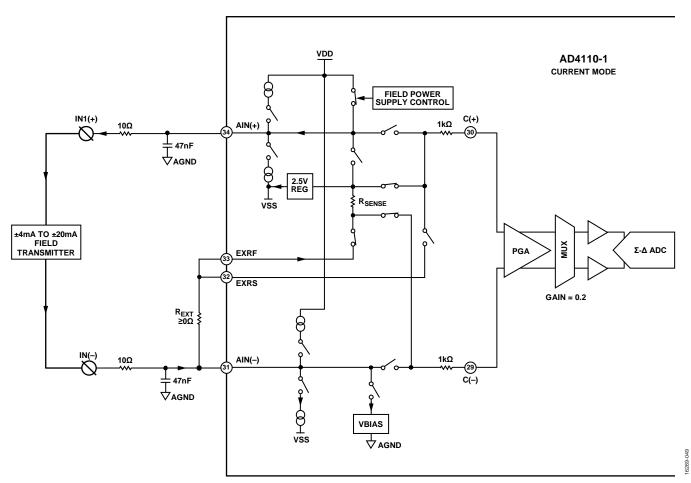

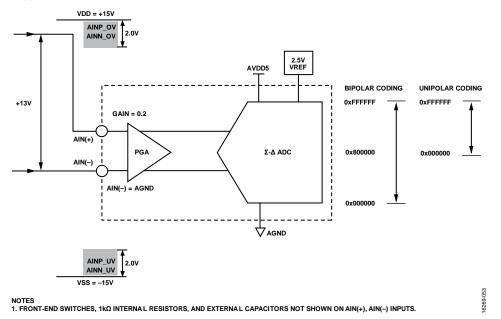

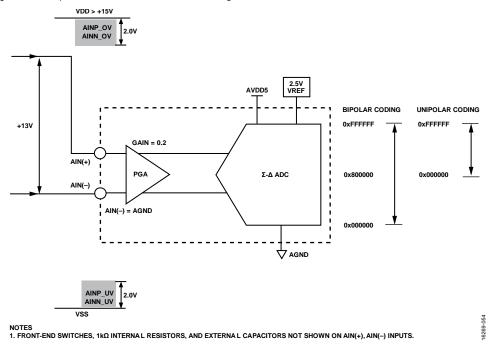

The high voltage input is fully software configurable for current or voltage signals and allows direct interface to all standard industrial analog signal sources such as  $\pm 20$  mA,  $\pm 4$  mA to  $\pm 20$  mA,  $\pm 10$  V, and all thermocouple types. Field power can be supplied for loop powered current output sensors. A range of excitation current sources for resistance temperature detector (RTD) sensors and other resistive sensors are included. The integrated, fully differential programmable gain amplifier (PGA) offers 16 gain settings from 0.2 to 24.

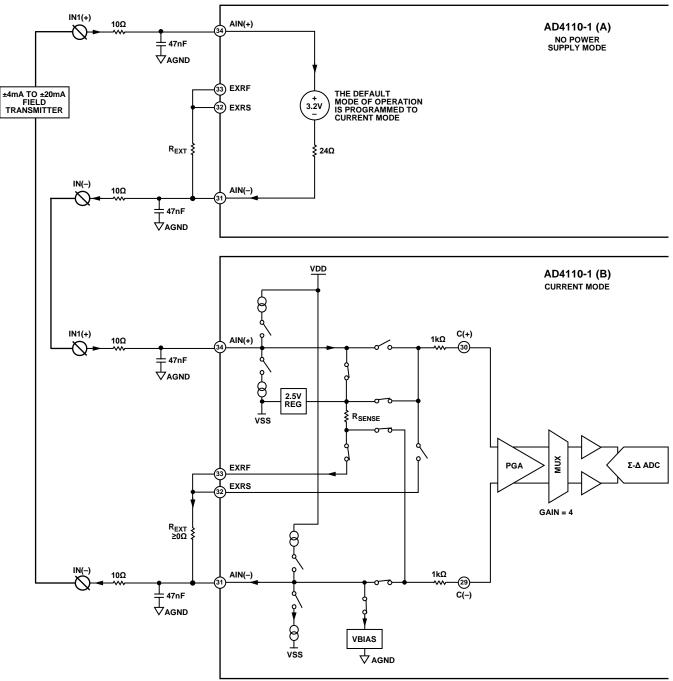

The high voltage input can be programmed to power up in either voltage mode or current mode. When programmed to current mode, the unique input circuit architecture provides a path for the loop current, even in the absence of the system module power supply.

The AD4110-1 provides internal, front-end diagnostic functions to indicate overvoltage, undervoltage, open wire, overcurrent, and overtemperature conditions. The high voltage input is thermally protected, overcurrent limited, and overvoltage protected.

The AD4110-1 incorporates a precision 24-bit,  $\Sigma$ - $\Delta$ , analog-to-digital converter (ADC) offering conversion rates from 5 SPS to 125 kSPS with simultaneous 50 Hz and 60 Hz noise rejection.

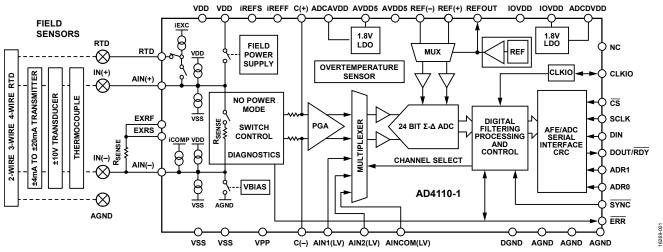

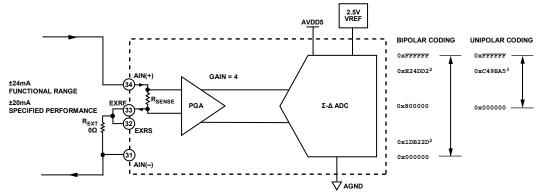

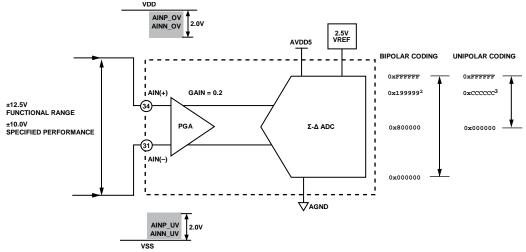

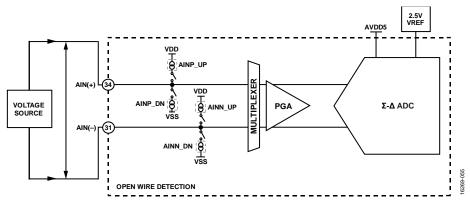

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

# AD4110-1

# **TABLE OF CONTENTS**

| Features                                                 | Input Auto Sequencing                              | 21 |

|----------------------------------------------------------|----------------------------------------------------|----|

| Applications1                                            | Single Conversion Mode                             | 22 |

| General Description1                                     | ADC Conversion Delay                               | 22 |

| Functional Block Diagram1                                | Bias Voltage Generator                             | 22 |

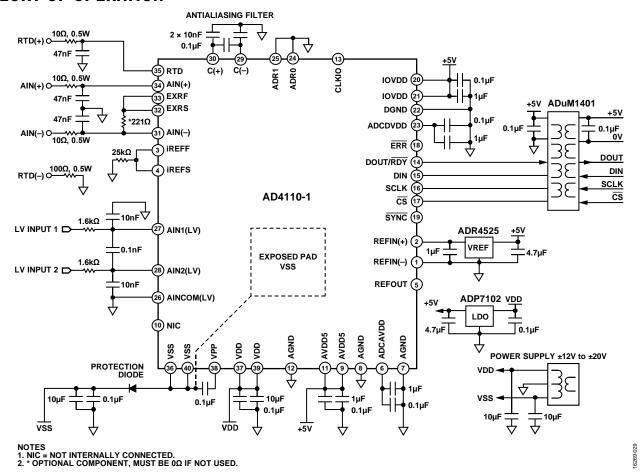

| Revision History                                         | Antialiasing Filter Circuit                        | 23 |

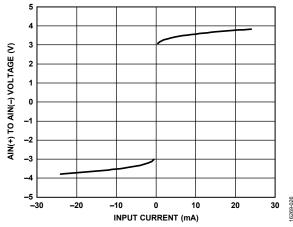

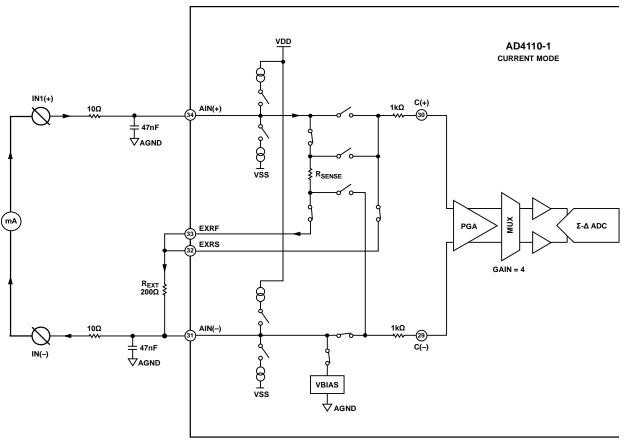

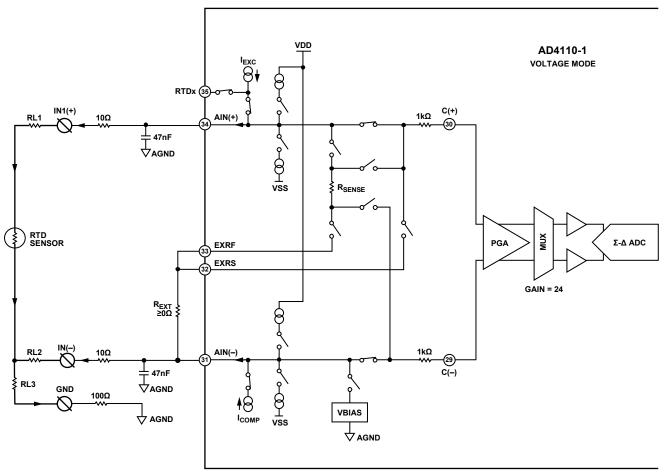

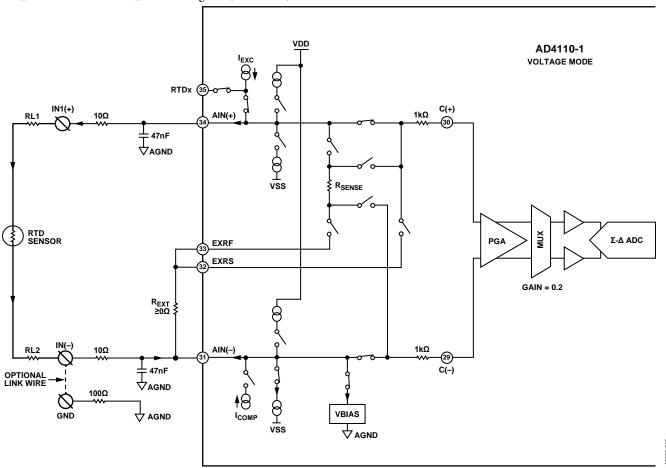

| Specifications4                                          | Current Mode                                       | 24 |

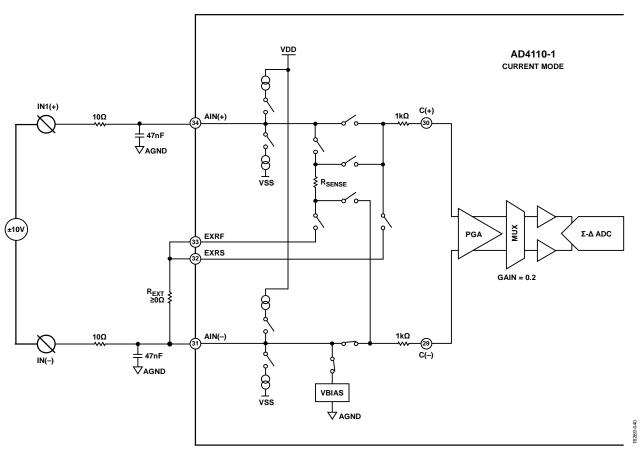

| Timing Specifications                                    | Voltage and Thermocouple Mode                      | 27 |

| Absolute Maximum Ratings10                               | RTD Mode                                           | 30 |

| Thermal Resistance                                       | Field Power Supply Mode                            | 35 |

| ESD Caution                                              | No Power Supply Mode                               | 36 |

| Pin Configuration and Function Descriptions11            | Gain Calibration Data Register                     | 38 |

| Typical Performance Characteristics                      | Gain Calibration in Voltage Mode                   | 38 |

| Theory of Operation17                                    | Gain Calibration in Current Mode                   | 38 |

| Power Supply Sequence                                    | Scaling Factor                                     | 38 |

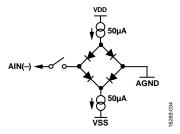

| Protection Diode18                                       | Autocalibration Modes                              | 39 |

| Analog Input18                                           | Application Examples                               | 40 |

| Pull-Up/Pull-Down Currents                               | Diagnostics and Protection                         | 41 |

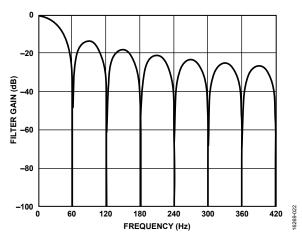

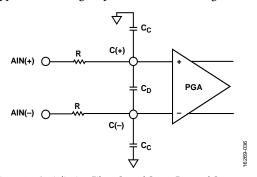

| Antialiasing Filter                                      | Diagnostic Flags                                   | 41 |

| RTD Excitation Currents                                  | Error Pin                                          | 41 |

| Field Power Supply Mode18                                | Overtemperature Detection and Thermal Shutdown     | 41 |

| No Power Supply Mode18                                   | Overvoltage and Undervoltage Detection             | 42 |

| Bias Voltage Generator                                   | Overvoltage Protection                             | 42 |

| PGA18                                                    | Diagnosing Overvoltage and Undervoltage Conditions | 43 |

| Calibration Registers                                    | Open Wire Detection                                | 44 |

| Serial Interface                                         | Diagnostics for RTD Measurements and RTD Flags     | 44 |

| Clock                                                    | Noise, Settling Time, and Digital Filtering        | 45 |

| ADC18                                                    | Digital Filter                                     | 45 |

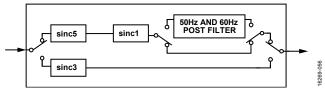

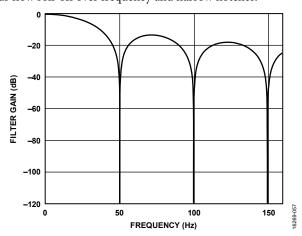

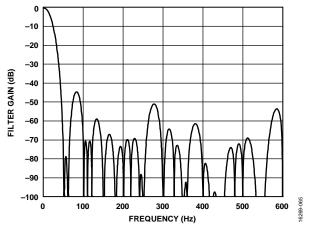

| ADC Filter Registers                                     | Sinc5 + Sinc1 Filter                               | 45 |

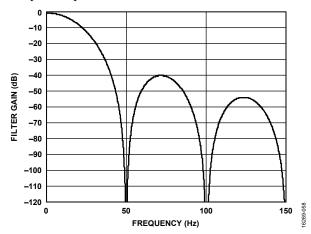

| ADC Gain and Offset Registers                            | Sinc3 Filter                                       | 45 |

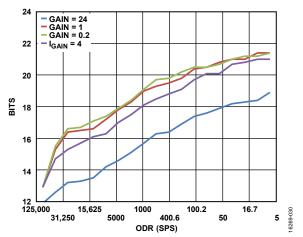

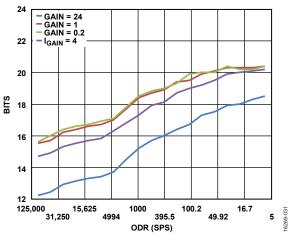

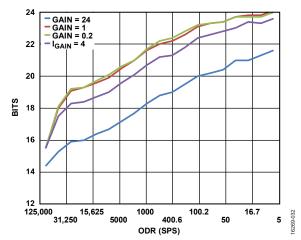

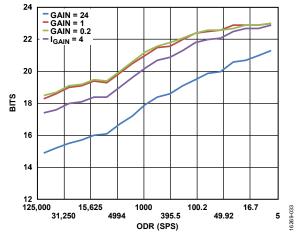

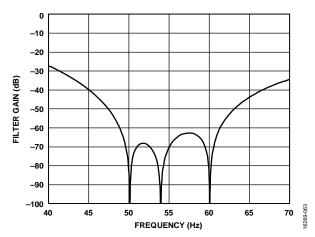

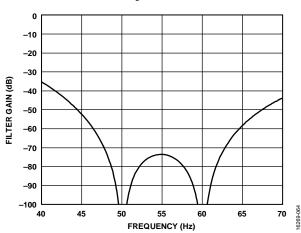

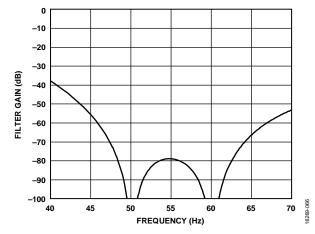

| Noise Performance and Resolution19                       | Enhanced 50 Hz and 60 Hz Rejection Filters         | 48 |

| Modes of Operation20                                     | RTD Mode Noise Performance                         | 50 |

| Default Mode of Operation on Power-Up20                  | Serial Peripheral Interface                        | 51 |

| Changing The Default Mode of Operation for Future Power- | Resetting the AD4110-1                             | 51 |

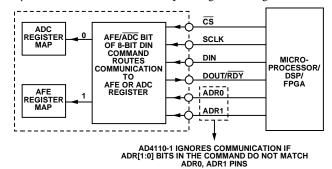

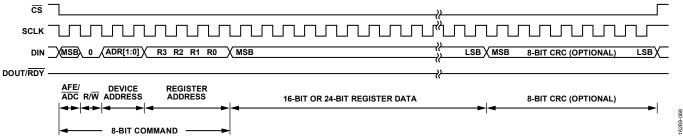

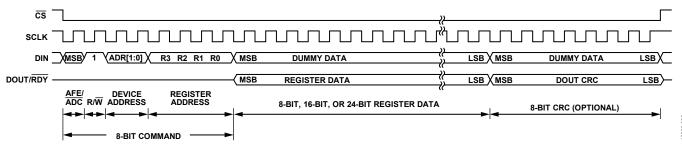

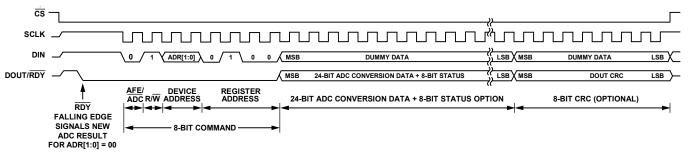

| Up Cycles                                                | SPI Command to Communications Register             | 51 |

| Power Supply Requirements                                | DOUT/RDY Pin                                       | 52 |

| System Clock Requirements                                | Write Operation                                    | 52 |

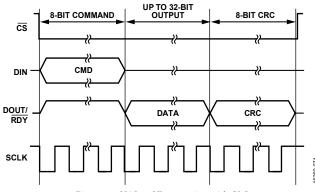

| Bipolar and Unipolar Output21                            | Read Operation                                     | 53 |

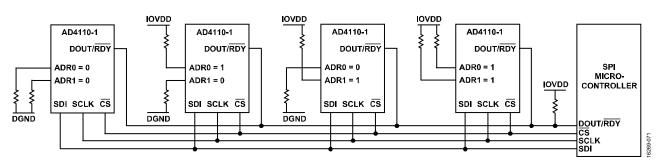

| Auxiliary Low Voltage Inputs21                           | Multiple Devices on the SPI Bus                    | 54 |

| Digital Filter                                           | CRC Checksum                                       | 55 |

| Continuous Conversion Mode21                             | CRC Checksum Methods                               | 55 |

| Register Details          | 58 |

|---------------------------|----|

| AFE Register Map          | 58 |

| AFE Register Descriptions | 59 |

| ADC Register Map          | 66 |

| ADC Register Descriptions | 67 |

|---------------------------|----|

| Outline Dimensions        | 74 |

| Ordering Guide            | 74 |

### **REVISION HISTORY**

3/2019—Revision 0: Initial Version

# **SPECIFICATIONS**

VDD = +12 V to 20 V, VSS = -12 V to -20 V, AVDD5 = +5 V, IOVDD = +5 V, AGND = DGND = 0 V, VBIAS function = off, REFIN(+) = 2.5 V (external reference), REFIN(-) = 0 V, MCLK = 8 MHz (internal ADC clock),  $T_A = -40 ^{\circ}\text{C}$  to  $+105 ^{\circ}\text{C}$ , all gains, unless otherwise noted.

Table 1.

| Parameter                                                                                 | Min                     | Тур   | Max                     | Unit    | Test Conditions/Comments                                                                                                                                                       |

|-------------------------------------------------------------------------------------------|-------------------------|-------|-------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HIGH VOLTAGE ANALOG INPUTS, AIN(±) Pins                                                   |                         |       |                         |         |                                                                                                                                                                                |

| Differential Input Voltage Range,<br>Reference Voltage ( $V_{REF}$ ) $\leq 2.5 \text{ V}$ | –V <sub>REF</sub> /Gain |       | +V <sub>REF</sub> /Gain | V       | For specified performance, gain > 0.2                                                                                                                                          |

|                                                                                           | -10                     |       | +10                     | V       | For specified performance, gain = 0.2                                                                                                                                          |

|                                                                                           | -12.5                   |       | +12.5                   | V       | Functional range, gain = 0.2                                                                                                                                                   |

| Absolute AIN Voltage                                                                      | VSS + 3                 |       | VDD – 3                 | V       | For specified performance                                                                                                                                                      |

| Overvoltage Protection 1, 2                                                               |                         |       |                         |         |                                                                                                                                                                                |

| AIN(+) – AGND, AIN(–) – AGND,<br>AIN(+) – AIN(–) Pins                                     |                         |       | ±30                     | V       | Using input resistor-capacitor (RC) low-pass filter with resistor (R) = $10 \Omega$ , 0.5 W and capacitor (C) = $47 \text{ nF} 50 \text{ V}$ , VDD/VSS $\leq \pm 15 \text{ V}$ |

| VOLTAGE INPUT MODE                                                                        |                         |       |                         |         |                                                                                                                                                                                |

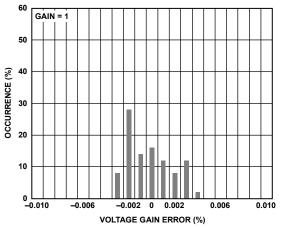

| Gain Error                                                                                |                         |       |                         |         |                                                                                                                                                                                |

| Before Calibration <sup>3</sup>                                                           | -1                      |       | +1                      | %       | T <sub>A</sub> = 25°C                                                                                                                                                          |

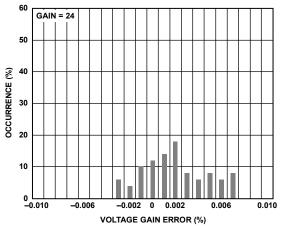

| Using Calibration Coefficient⁴                                                            | -0.03                   |       | +0.03                   | %       | $T_A = 25$ °C, VDD/VSS = $\pm 15$ V                                                                                                                                            |

| Gain Drift vs. Temperature <sup>2</sup>                                                   | -3                      |       | +3                      | ppm/°C  | All gains except gain = 1                                                                                                                                                      |

|                                                                                           | -8                      |       | +8                      | ppm/°C  | Gain = 1                                                                                                                                                                       |

| Gain Drift vs. Time⁵                                                                      |                         | ±30   |                         | ppm     | Over 1000 hours                                                                                                                                                                |

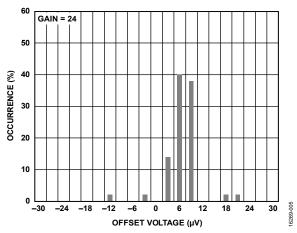

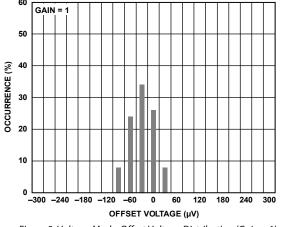

| Input Offset Error <sup>6</sup>                                                           | -350/Gain               |       | +350/Gain               | μV      | Gain = 0.2 to 3                                                                                                                                                                |

|                                                                                           | -100                    |       | +100                    | μV      | Gain = 4 to 24                                                                                                                                                                 |

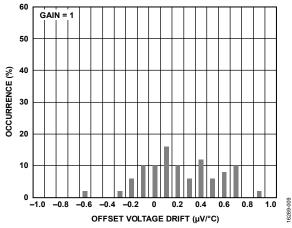

| Input Offset Drift vs. Temperature <sup>2</sup>                                           |                         | 2     | 14                      | μV/°C   | Gain = 0.2, referred to input                                                                                                                                                  |

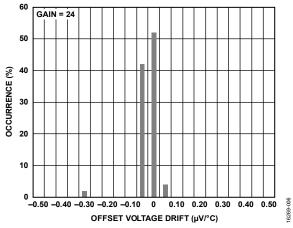

|                                                                                           |                         | 0.2   | 0.5                     | μV/°C   | Gain = 24, referred to input                                                                                                                                                   |

| Input Offset Drift vs. Time⁵                                                              |                         | ±50   |                         | μV      | Gain = 0.2, over 1000 hours                                                                                                                                                    |

|                                                                                           |                         | ±25   |                         | μV      | Gain = 1, over 1000 hours                                                                                                                                                      |

|                                                                                           |                         | ±4    |                         | μV      | Gain = 24, over 1000 hours                                                                                                                                                     |

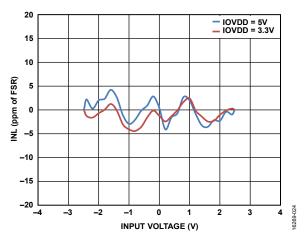

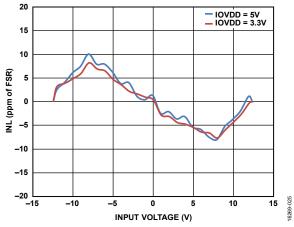

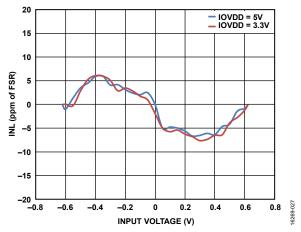

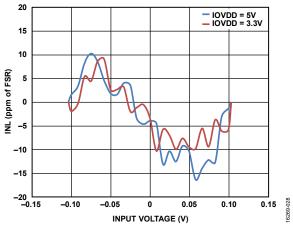

| Integral Nonlinearity                                                                     |                         | 6     |                         | ppm/FSR | Gain = 0.2, full-scale range (FSR) = $2 \times$ full scale (FS)                                                                                                                |

|                                                                                           |                         | 25    | 75                      | ppm/FSR | Gain = 24                                                                                                                                                                      |

| Input Bias Current, AIN(+), AIN(-) Pins <sup>2</sup>                                      | -0.5                    |       | +0.5                    | μΑ      |                                                                                                                                                                                |

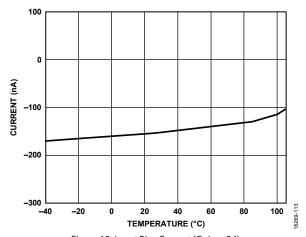

| Input Bias Current, AIN(+) Pin                                                            | -0.25                   | -0.15 | -0.05                   | μА      | AIN(+) – AIN(–) < $\pm$ 100 mV, AIN(–) = 0 V, VBIAS on/off, gain = 24, source impedance < 5 k $\Omega$                                                                         |

| Input Bias Current Drift <sup>2</sup>                                                     |                         | 1     | 2.5                     | nA/°C   | AIN(+) and AIN(-)                                                                                                                                                              |

| Input Offset Current <sup>2</sup>                                                         | -100                    |       | +100                    | nA      |                                                                                                                                                                                |

| Input Impedance <sup>7</sup>                                                              |                         | >1    |                         | GΩ      | $\Delta V_{IN} \div \Delta I_{IN}$                                                                                                                                             |

| Input Voltage Noise and Resolution <sup>2</sup>                                           |                         |       |                         |         | See Table 16 to Table 21                                                                                                                                                       |

| Input Common-Mode Rejection, DC                                                           |                         | 125   |                         | dB      | Gain = 24                                                                                                                                                                      |

|                                                                                           |                         | 100   |                         | dB      | Gain = 0.2                                                                                                                                                                     |

| Input Common-Mode Rejection, AC                                                           |                         | 130   |                         | dB      | 50 Hz/60 Hz                                                                                                                                                                    |

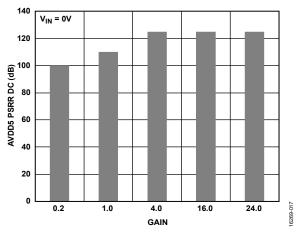

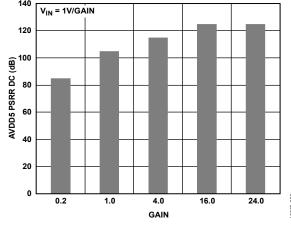

| Power Supply Rejection, DC <sup>8</sup>                                                   |                         | 120   |                         | dB      | Related to VSS and VDD                                                                                                                                                         |

|                                                                                           |                         | 83    |                         | dB      | Related to AVDD5, gain = 1, $V_{IN} = 1 \text{ V}$                                                                                                                             |

| Normal Mode Rejection, 50 Hz/60 Hz                                                        |                         | 40    |                         | dB      | Sinc5 + sinc1 filter, ±0.5 Hz, external clock                                                                                                                                  |

|                                                                                           |                         | 100   |                         | dB      | Sinc3 filter, ±1 Hz                                                                                                                                                            |

| Parameter                                                             | Min       | Тур        | Max       | Unit    | Test Conditions/Comments                                             |

|-----------------------------------------------------------------------|-----------|------------|-----------|---------|----------------------------------------------------------------------|

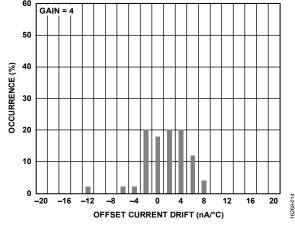

| CURRENT INPUT MODE USING<br>INTERNAL SENSE RESISTOR <sup>9</sup>      |           |            |           |         | Gain = 4                                                             |

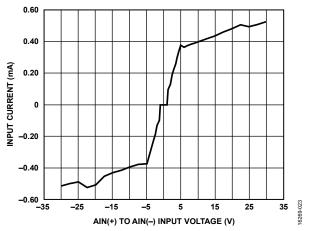

| Input Current Range <sup>10</sup>                                     | -20       |            | +20       | mA      | Specified performance range                                          |

|                                                                       | -24       |            | +24       | mA      | Functional range                                                     |

| Transimpedance Gain                                                   |           | 96         |           | mV/mA   | Gain = 4, sense resistor ( $R_{SENSE}$ ) = 24 $\Omega$               |

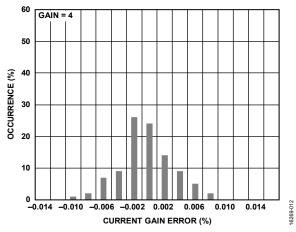

| Gain Error                                                            |           |            |           |         |                                                                      |

| Before Calibration <sup>3</sup>                                       |           | ±30        |           | %       |                                                                      |

| Using Calibration Coefficient⁴                                        | -0.1      |            | +0.1      | %       | $T_A = 25$ °C, $I_{IN} = 20 \text{ mA}$                              |

| Gain Drift vs. Temperature <sup>2</sup>                               | -50       |            | +50       | ppm/°C  | Excludes reference drift, includes R <sub>SENSE</sub> resistor drift |

| Gain Drift vs. Time⁵                                                  |           | 250        |           | ppm     | Over 1000 hours                                                      |

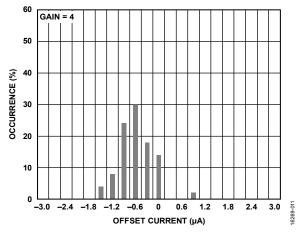

| Input Offset Error                                                    | -5        |            | +5        | μΑ      |                                                                      |

| Input Offset Drift vs. Temperature <sup>2</sup>                       |           |            | 50        | nA/°C   |                                                                      |

| Input Offset Drift vs. Time⁵                                          |           | ±200       |           | nA      | Over 1000 hours                                                      |

| Integral Nonlinearity                                                 |           | 25         | 75        | ppm/FSR | $FSR = 2 \times FS$                                                  |

| Input Overcurrent Detection                                           |           | ±35        |           | mA      |                                                                      |

| Input Current Internal Limit10                                        |           | ±40        |           | mA      | Overcurrent self-protection                                          |

| Input Impedance <sup>2, 11</sup>                                      | 30        | 45         | 60        | Ω       | Input current <±24 mA                                                |

| Input Current Noise and Resolution                                    |           |            |           |         | See Table 16 to Table 21                                             |

| Input Common-Mode Rejection, DC                                       |           | 0.15       |           | μΑ/V    |                                                                      |

| Power Supply Rejection, DC <sup>8</sup>                               |           | 0.01       |           | μΑ/V    | Related to VDD and VSS                                               |

| CURRENT INPUT MODE USING<br>EXTERNAL SENSE RESISTOR <sup>12, 13</sup> |           |            |           |         | External sense resistor ( $R_{EXT}$ ) = 200 $\Omega$ , gain = 0.5    |

| Input Current Range <sup>7</sup>                                      | -20       |            | +20       | mA      | Specified performance range                                          |

| · ·                                                                   | -24       |            | +24       | mA      | Functional range                                                     |

| Input Overcurrent Detection                                           |           | ±35        |           | mA      |                                                                      |

| Input Current Internal Limit <sup>7</sup>                             |           | ±40        |           | mA      | Overcurrent self-protection                                          |

| Gain Drift vs. Temperature <sup>2</sup>                               |           |            | 2.5       | ppm/°C  | Excludes reference drift and drift of external sense resistor        |

| ADC SPEED AND PERFORMANCE                                             |           |            |           |         |                                                                      |

| Output Data Rate <sup>2</sup>                                         | 5         |            | 125,000   | SPS     |                                                                      |

| No Missing Codes <sup>2</sup>                                         | 24        |            |           | Bits    | Sinc5 + sinc1 filter setting                                         |

| Resolution                                                            |           |            |           |         | See Table 16 to Table 21                                             |

| NO POWER SUPPLY MODE                                                  |           |            |           |         |                                                                      |

| Input Voltage Drop                                                    |           | 5          |           | V       | Current mode, input current = 24 mA                                  |

| Input Current Internal Limit <sup>2</sup>                             |           | ±55        | ±70       | mA      | Current mode, overcurrent self-<br>protection                        |

| Input Current Loss                                                    |           | 70         |           | μА      | Current mode, 24 mA, GND connected                                   |

| Input Current in Voltage Mode                                         |           | ±0.5       |           | mA      | Voltage mode                                                         |

| FIELD POWER SUPPLY MODE                                               |           |            |           |         |                                                                      |

| Output Voltage, AIN(+) Pin <sup>2</sup>                               | VDD - 2.5 | VDD - 1.5  |           | V       | Output current = 24 mA                                               |

| -                                                                     |           | VDD - 0.1  | VDD       | V       | No load                                                              |

| Output Current, AIN(+) Pin                                            |           |            | -24       | mA      |                                                                      |

| Output Current Limit, AIN(+) Pin <sup>2</sup>                         | -35       | <b>-45</b> | -55       | mA      | Overcurrent self-protection                                          |

| Voltage, AIN(–) Pin <sup>2</sup>                                      |           | VSS + 3.6  | VSS + 4.2 | V       | AIN(–) with 24 mA, no VSS diode                                      |

| -                                                                     | VSS + 2.2 | VSS + 2.7  |           | V       | No load, no VSS diode                                                |

| Input Current Limit, AIN(–) Pin                                       |           | +40        |           | mA      |                                                                      |

| Parameter                                                  | Min          | Тур            | Max          | Unit                     | Test Conditions/Comments                                                 |

|------------------------------------------------------------|--------------|----------------|--------------|--------------------------|--------------------------------------------------------------------------|

| RTD EXCITATION CURRENTS <sup>14</sup>                      |              |                |              |                          | External reference voltage (V <sub>REF</sub> ) = 2.5 V ± 0%              |

| Current Outputs                                            |              | 0.1 to 1       |              | mA                       | Programmable (see Table 30)                                              |

| Initial Error, Internal Reference<br>Resistor              | -0.3         |                | +0.3         | %                        | Current ≥ 400 μA, T <sub>A</sub> = 25°C                                  |

|                                                            | -1           |                | +1           | %                        | Current = 100 $\mu$ A, $T_A$ = 25°C                                      |

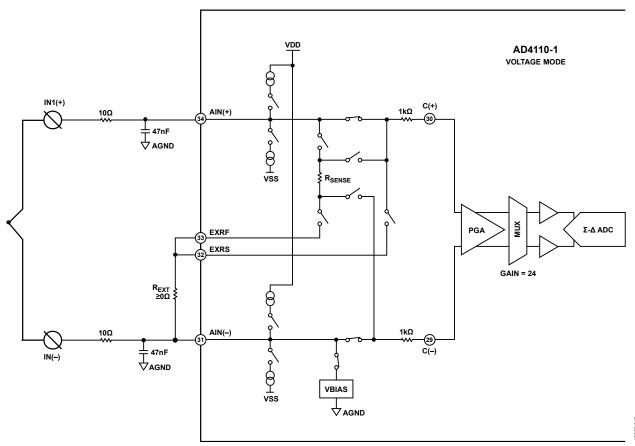

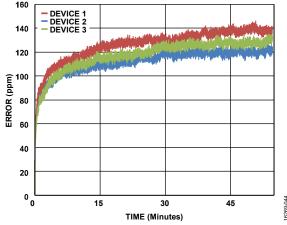

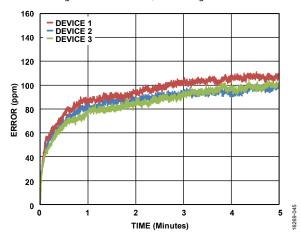

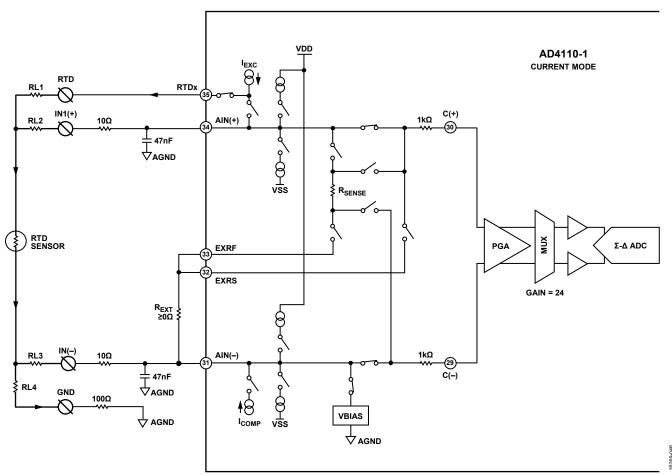

| Initial Drift                                              |              | 130            |              | ppm                      | See Figure 44 and Figure 45                                              |

| Drift vs. Temperature <sup>2</sup>                         | -45          |                | +45          | ppm/°C                   | Internal reference resistor (including reference resistor drift)         |

|                                                            | -18          |                | +18          | ppm/°C                   | External reference resistor (excluding reference resistor drift)         |

| Drift vs. Time <sup>5, 15</sup>                            |              | 150            |              | ppm                      | Internal resistor, over 1000 hours                                       |

|                                                            |              | 150            |              | ppm                      | External resistor, over 1000 hours                                       |

| Load Regulation <sup>2</sup>                               |              |                | 0.01         | %/V                      |                                                                          |

| Line Regulation <sup>2</sup>                               |              | 4              |              | ppm/V                    | Related to VSS and VDD                                                   |

| Noise <sup>2</sup>                                         | See Table 22 | 2 and Table 23 |              | ' '                      | $T_A = 25$ °C                                                            |

| Current Matching <sup>15</sup>                             |              | 0.05           |              | %                        | AIN(+) and AIN(–) pins, excludes 100 μA                                  |

| Current Matching Drift                                     |              | 0.0002         |              | %/°C                     | AIN(+) and AIN(–) pins, excludes<br>100 μA                               |

| Compliance                                                 |              |                | VDD – 5      | V                        |                                                                          |

| REFERENCE VOLTAGE (INPUT)                                  |              |                |              |                          |                                                                          |

| Reference Voltage Input, V <sub>REF</sub> <sup>2, 14</sup> | 1            | 2.5            | AVDD5 – 1.6  | V                        | REFIN(+) – REFIN(–) = $V_{REF}$<br>RTD mode disabled                     |

|                                                            | 2.45         | 2.5            | 2.55         | ٧                        | RTD mode enabled                                                         |

| V <sub>REF</sub> Input Current                             |              | 200            |              | nA                       | V <sub>REF</sub> + reference buffer on                                   |

|                                                            |              | 100            |              | μΑ                       | V <sub>REF</sub> — reference buffer on                                   |

|                                                            |              | 36             |              | μA/V                     | V <sub>REF</sub> + reference buffer off                                  |

|                                                            |              | 75             |              | μA/V                     | V <sub>REF</sub> — reference buffer off                                  |

| V <sub>REF</sub> Input Current Drift                       |              | 1.3            |              | nA/°C                    | V <sub>REF</sub> + reference buffer on                                   |

| ·                                                          |              | -3.5           |              | nA/°C                    | V <sub>REF</sub> - reference buffer on                                   |

|                                                            |              | 10             |              | nA/V/°C                  | V <sub>REF</sub> + reference buffer off                                  |

|                                                            |              | 10             |              | nA/V/°C                  | V <sub>RFF</sub> — reference buffer off                                  |

| Absolute REFIN Voltage Limits                              | AGND - 0.05  |                | AVDD5 + 0.05 | V                        |                                                                          |

| , issolute i.e. iit voitage eiiiiis                        | AGND         |                | AVDD5        | V                        | Reference buffer on                                                      |

| Common-Mode Rejection                                      | AGNE         | 95             | 7.0003       | dB                       | neierence baner on                                                       |

| REFERENCE VOLTAGE (OUTPUT)                                 |              |                |              |                          |                                                                          |

| Output Voltage                                             |              | 2.5            |              | V                        | REFOUT pin                                                               |

| Initial Accuracy <sup>2</sup>                              | -0.16        | 2.3            | +0.16        | V                        | $T_A = 25^{\circ}C$                                                      |

| Temperature Coefficient <sup>2</sup>                       | 0.10         | 10             | 50           | ppm/°C                   |                                                                          |

| Long Term Stability <sup>5</sup>                           |              | 600            | 30           | ppm                      | Over 1000 hours                                                          |

| Reference Load Current, I <sub>LOAD</sub>                  |              | 000            | 10           | mA                       | over root hours                                                          |

| Power Supply Rejection                                     |              | 93             | 10           | dB                       |                                                                          |

| Load Regulation                                            |              | 95<br>75       |              | μV/mA                    |                                                                          |

| VBIAS                                                      |              | , ,            |              | M*/11//                  |                                                                          |

| Voltage                                                    |              | AGND           |              | V                        |                                                                          |

| Output Current Limit                                       |              | ±50            |              | μΑ                       | Source or sink, depending on the AIN(–) pin potential referenced to AGND |

| OPEN WIRE DETECTION CURRENTS                               |              |                |              |                          |                                                                          |

| Current Output                                             | ±0.71        | ±1<br>±100     | ±1.45        | μ <b>Α</b><br>μ <b>Α</b> |                                                                          |

| Compliance                                                 | VSS + 2      |                | VDD – 2      | V                        |                                                                          |

| Compilance                                                 | V 3 3 T Z    |                | V D D - Z    | v                        |                                                                          |

| Parameter                                                                | Min                | Тур           | Max       | Unit  | Test Conditions/Comments                                  |

|--------------------------------------------------------------------------|--------------------|---------------|-----------|-------|-----------------------------------------------------------|

| INPUT OVERVOLTAGE DETECTION                                              |                    |               |           |       |                                                           |

| Positive Overvoltage Threshold                                           |                    | VDD - 2.0     | VDD – 2.8 | V     |                                                           |

| Negative Overvoltage Threshold                                           |                    | VSS + 2.0     | VSS + 2.8 | V     |                                                           |

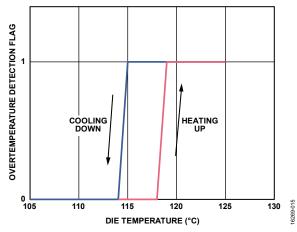

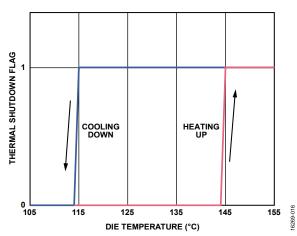

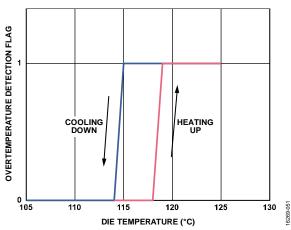

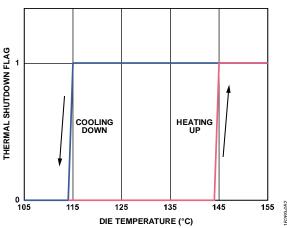

| OVERTEMPERATURE PROTECTION                                               |                    |               |           |       |                                                           |

| Overtemperature Detection<br>Threshold                                   |                    | 120           |           | °C    | Junction temperature                                      |

| Thermal Shutdown Threshold                                               |                    | 145           |           | °C    | Junction temperature                                      |

| Thermal Shutdown Hysteresis                                              |                    | 30            |           | °C    |                                                           |

| ANTIALIASING FILTER RESISTOR                                             |                    |               |           |       |                                                           |

| $AIN(\pm)$ to $C(\pm)$ Resistance                                        |                    | 1600          |           | Ω     | Includes internal switch resistance                       |

| Resistance Variation <sup>2</sup>                                        |                    |               | ±35       | %     |                                                           |

| Mismatch                                                                 |                    | 0.2           |           | %     | Resistor pair per channel                                 |

| LOW VOLTAGE ANALOG INPUTS,<br>AIN1(LV), AIN2(LV), AND AINCOM(LV)         |                    |               |           |       |                                                           |

| Differential Input Range                                                 |                    | $\pm V_{REF}$ |           | V     |                                                           |

| Absolute Voltage Limit                                                   | AGND               |               | AVDD5     | V     |                                                           |

| Input Current                                                            |                    | ±65           |           | nA    |                                                           |

| Input Current Drift                                                      |                    | ±75           |           | pA/°C | AGND + 0.2 V to AVDD5 – 0.2 V                             |

|                                                                          |                    | ±1            |           | nA/°C | AGND to AVDD5                                             |

| High Voltage (HV) to Low Voltage<br>(LV) Channel Crosstalk <sup>16</sup> |                    | -120          |           | dB    | Input frequency $(f_{IN}) = 1$ kHz, Gain (HV Channel) = 1 |

| Input Common-Mode Rejection, DC                                          |                    | 95            |           | dB    |                                                           |

| Input Common-Mode Rejection, AC                                          |                    | 120           |           | dB    | 50 Hz/60 Hz, V <sub>IN</sub> = 1 V                        |

| DIGITAL INPUTS                                                           |                    |               |           |       |                                                           |

| Input High Voltage, V <sub>IH</sub> <sup>2</sup>                         | $0.7 \times IOVDD$ |               |           | V     | IOVDD = 2 V to 5.5 V                                      |

| Input Low Voltage, V <sub>IL</sub> <sup>2</sup>                          |                    |               | 0.8       | V     | IOVDD = 3.3 V to 5.5 V                                    |

|                                                                          |                    |               | 0.4       | V     | IOVDD = 2 V                                               |

| Hysteresis                                                               |                    | 100           |           | mV    |                                                           |

| Input Leakage Current                                                    | -10                |               | +10       | μΑ    |                                                           |

| Input Pin Capacitance                                                    |                    | 10            |           | pF    |                                                           |

| DIGITAL OUTPUTS                                                          |                    |               |           |       |                                                           |

| $V_{OH}{}^2$                                                             | 0.8 × IOVDD        |               |           | V     | IOVDD = 5 V, source current (I <sub>SOURCE</sub> ) = 1 mA |

|                                                                          | 0.8 × IOVDD        |               |           | V     | $IOVDD = 3.3 \text{ V, } I_{SOURCE} = 500  \mu\text{A}$   |

|                                                                          | 0.8 × IOVDD        |               |           | V     | $IOVDD = 2 V$ , $I_{SOURCE} = 500 \mu A$                  |

| $V_{OL}^2$                                                               |                    |               | 0.4       | V     | $IOVDD = 5 V$ , sink current $(I_{SINK}) = 2 \text{ mA}$  |

|                                                                          |                    |               | 0.4       | V     | $IOVDD = 3.3 \text{ V}, I_{SINK} = 1 \text{ mA}$          |

|                                                                          |                    |               | 0.4       | V     | $IOVDD = 2 V$ , $I_{SINK} = 1 mA$                         |

| Floating State Leakage Current                                           | -10                |               | +10       | μΑ    |                                                           |

| Floating State Output Capacitance                                        |                    | 12            |           | рF    |                                                           |

| ERROR OUTPUT (OPEN DRAIN)                                                |                    |               |           |       |                                                           |

| Output Low Voltage, Vol                                                  |                    |               | 0.4       | V     | $I_{SINK} = -100  \mu A$                                  |

| Output High Leakage Current, I <sub>OH</sub>                             | -10                |               | +10       | μΑ    | Output voltage (V <sub>OUT</sub> ) = 5 V                  |

| CLOCK INPUT/OUTPUT                                                       |                    |               |           |       |                                                           |

| Internal Oscillator                                                      |                    | 8             |           | MHz   |                                                           |

| Internal Oscillator Accuracy                                             | -3.5               |               | +3.5      | %     | ADC clock                                                 |

| Clock Input Frequency                                                    |                    | 8             |           | MHz   |                                                           |

| Duty Cycle, External Clock <sup>2</sup>                                  | 45                 | 50            | 55        | %     |                                                           |

| $V_{IH}^2$                                                               | 0.8 × IOVDD        |               |           | V     |                                                           |

| V <sub>он</sub>                                                          | 0.8 × IOVDD        |               |           | V     |                                                           |

| $V_{OL}$                                                                 |                    |               | 0.4       | V     |                                                           |

| $V_{lL}^2$                                                               | 1                  |               | 0.4       | V     |                                                           |

| Parameter                          | Min | Тур       | Max   | Unit | Test Conditions/Comments                                                                          |

|------------------------------------|-----|-----------|-------|------|---------------------------------------------------------------------------------------------------|

| Input Leakage Current              | -10 |           | +10   | μΑ   |                                                                                                   |

| Pin Capacitance                    |     | 12        |       | pF   |                                                                                                   |

| Duty Cycle, Internal Clock         |     | 50        |       | %    |                                                                                                   |

| POWER REQUIREMENTS                 |     |           |       |      | See the Power Supply Sequence section                                                             |

| VDD – VSS Voltage                  | 24  | 30        | 40    | V    |                                                                                                   |

| AGND Voltage                       |     | (VDD – V: | SS)/2 | V    |                                                                                                   |

| AVDD5 – AGND Voltage               | 4.5 | 5         | 5.5   | V    |                                                                                                   |

| DGND Voltage                       |     | AGND      |       | V    |                                                                                                   |

| IOVDD – DGND Voltage               | 2.0 | 5         | 5.5   | V    |                                                                                                   |

| VDD Supply Current                 |     |           |       |      |                                                                                                   |

| Field Power Supply Off             |     | 5.5       | 8     | mA   | All current sources off and disabled                                                              |

|                                    |     | 7.5       | 10    | mA   | RTD current sources on, other current sources off, VBIAS off                                      |

| Field Power Supply On <sup>2</sup> |     | 29.5      |       | mA   | Field power supply current = 24 mA<br>to AGND, all current sources off and<br>disabled, VBIAS off |

| VSS Supply Current                 |     |           |       |      |                                                                                                   |

| Field Power Supply Off             |     | -5.5      | -8    | mA   | All current sources off and disabled                                                              |

|                                    |     | -5.5      | -10   | mA   | RTD current sources on, other current sources off, VBIAS off                                      |

| Field Power Supply On <sup>2</sup> |     | -5.8      |       | mA   | Field power supply current = 24 mA<br>to AGND, all current sources off and<br>disabled, VBIAS off |

| AVDD5 Supply Current               |     | 10        | 12    | mA   |                                                                                                   |

| IOVDD Supply Current               |     | 2.5       | 3.5   | mA   |                                                                                                   |

$<sup>^1</sup>$  The device is specified to operate with an input voltage from VSS + 3 V to VDD − 3 V on any AlN(±) pin. The device is protected against overvoltage on the AlN(+) and AlN(−) pins up to ±30 V (referred to the AGND supply). The limitation of VDD = VSS ≤ ± 15 V only applies when field power supply mode is enabled. Applying a voltage to a high voltage pin that is more negative than the potential of the system negative power supply can only be accomplished by connecting an external diode from the VSS pin to the system negative power supply (see Figure 29). The absolute maximum ratings must not be exceeded at any time (see Table 3).

<sup>2</sup> Specification is not production tested, but is supported by characterization data at initial product release.

<sup>&</sup>lt;sup>3</sup> Gain error prior to applying software error correction algorithm. See the Gain Calibration Data Register section.

<sup>&</sup>lt;sup>4</sup> Gain error after applying software error correction algorithm. See the Gain Calibration Application Examples section.

<sup>&</sup>lt;sup>5</sup> Data based on the following test methods: - Moisture/Reflow Sensitivity (MSL) Classification for nonhermetic Solid State Surface Mount Devices and High Temperature Operating Life (HTOL).

<sup>&</sup>lt;sup>6</sup> Offset voltage seen at the inputs in voltage mode. Note that RTD currents can cause an additional I × R offset voltage (±V) due to any mismatch in IC or PCB trace resistance. System calibration may be required when changing RTD excitation and compensation current levels.

<sup>&</sup>lt;sup>7</sup> DC input impedance is derived from measuring the change in input current for a change in input voltage,  $(\Delta V_{\mathbb{N}} \div \Delta I_{\mathbb{N}})$ .

<sup>&</sup>lt;sup>8</sup> Referred to input.

<sup>&</sup>lt;sup>9</sup> PGA gain = 4 for all specifications related to the current input mode with internal sense resistor.

<sup>10</sup> Input current in current input mode must be within ±20 mA for fully specified performance. The device is functional up to ±24 mA. The internal protection limits the input overcurrent to approximately 40 mA.

<sup>11</sup> Current mode input impedance is the total impedance between the AIN(+) and AIN(-) pins, which includes the on-chip sense resistor, on-chip current mode switches, and other on-chip circuits. The relationship between the analog input current and the analog output voltage is represented by the gain and offset specifications.

$<sup>^{12}</sup>$   $\dot{R}_{EXT}$  = 200  $\Omega$  and gain = 0.5 for all specifications related to the current input mode with external sense resistor.

<sup>&</sup>lt;sup>13</sup> The external resistor transfers the input current to a voltage for additional signal processing in this mode. The AD4110-1 specifications exclude the effect of any changes in the external resistor resistance. Performance of the external resistor must be considered to assess system performance in this mode.

<sup>&</sup>lt;sup>14</sup> The AD4110-1 RTD excitation currents are designed to operate with a 2.5 V reference voltage. The AD4110-1 RTD excitation current value scales proportionally to small changes in the V<sub>REF</sub> input voltage. The AD4110-1 RTD excitation current specifications exclude the effect of any changes in the V<sub>REF</sub> input voltage.

<sup>15</sup> RTD current source enabled and current flowing continuously.

<sup>&</sup>lt;sup>16</sup> This specification relates to the worst high voltage and low voltage channel pair. A 20 V p-p, 1 kHz sine wave input on the HV channel is attenuated by this amount on the other LV channels. The interferer signal is applied to an unselected channel. The filter network connected to C(+) and C(-) is implemented as shown in Figure 29. There is no filter network implemented on the input terminals.

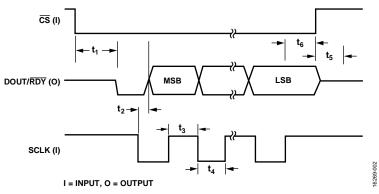

### **TIMING SPECIFICATIONS**

IOVDD = 2 V to 5.5 V, AGND = DGND = 0 V,  $C_{LOAD} = 20 pF$ ,  $T_A = -40 ^{\circ}C$  to  $+105 ^{\circ}C$ , unless otherwise noted.

Table 2.

| Parameter                   | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description <sup>1, 2</sup>                                 |  |  |  |

|-----------------------------|----------------------------------------------|--------|-------------------------------------------------------------|--|--|--|

| t <sub>3</sub>              | 50                                           | ns min | SCLK high pulse width                                       |  |  |  |

| t <sub>4</sub>              | 50                                           | ns min | SCLK low pulse width                                        |  |  |  |

| READ OPERATION              |                                              |        |                                                             |  |  |  |

| t <sub>1</sub>              | 0                                            | ns min | CS falling edge to DOUT/RDY active time                     |  |  |  |

|                             | 15                                           | ns max | IOVDD = 4.5 V to 5.5 V                                      |  |  |  |

|                             | 20                                           | ns max | IOVDD = 3.0  V to  3.6  V                                   |  |  |  |

|                             | 40                                           | ns max | IOVDD = 2.0 V                                               |  |  |  |

| $t_2$ <sup>3</sup>          | 0                                            | ns min | SCLK active edge to data valid delay⁴                       |  |  |  |

|                             | 15                                           | ns max | IOVDD = 4.5 V to 5.5 V                                      |  |  |  |

|                             | 20                                           | ns max | IOVDD = 3.0 V to 3.6 V                                      |  |  |  |

|                             | 40                                           | ns max | IOVDD = 2.0 V                                               |  |  |  |

| t <sub>5</sub> <sup>5</sup> | 20                                           | ns max | Bus relinquish time after CS inactive edge                  |  |  |  |

| t <sub>6</sub>              | 0                                            | ns min | SCLK inactive edge to CS inactive edge                      |  |  |  |

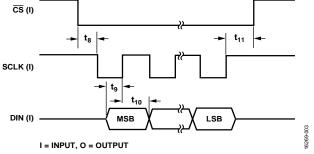

| WRITE OPERATION             |                                              |        |                                                             |  |  |  |

| t <sub>8</sub>              | 0                                            | ns min | CS falling edge to SCLK active edge setup time <sup>4</sup> |  |  |  |

| <b>t</b> <sub>9</sub>       | 8                                            | ns min | Data valid to SCLK edge setup time                          |  |  |  |

| t <sub>10</sub>             | 8                                            | ns min | Data valid to SCLK edge hold time                           |  |  |  |

| t <sub>11</sub>             | 10                                           | ns min | CS rising edge to SCLK edge hold time                       |  |  |  |

<sup>&</sup>lt;sup>1</sup> Sample tested during initial release to ensure compliance.

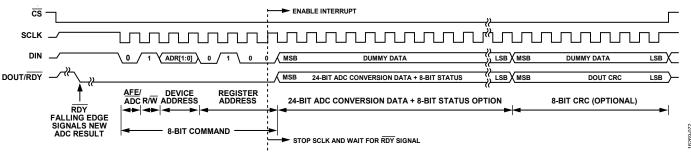

### **Timing Diagrams**

Figure 2. Data Read Timing Diagram

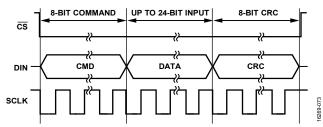

Figure 3. Data Write Timing Diagram

<sup>&</sup>lt;sup>2</sup> See Figure 2 and Figure 3.

$<sup>^{3}</sup>$  t<sub>2</sub> is the time required for the output to cross the V<sub>OL</sub> or V<sub>OH</sub> limit.

<sup>&</sup>lt;sup>4</sup> The SC<u>LK active edge is the falling edge of SCLK.</u>

<sup>&</sup>lt;sup>5</sup> DOUT/RDY returns high after a read of the data register. In single conversion mode and continuous conversion mode, the same data can be read again, if required, while DOUT/RDY is high, although care must be taken to ensure that subsequent reads do not occur close to the next output update.

### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                                                     | Rating                  |

|---------------------------------------------------------------|-------------------------|

| Any HV Pin to VSS <sup>1, 2</sup>                             | -0.3 V to +60 V         |

| VDD to VSS <sup>3</sup>                                       | −0.3 V to +50 V         |

| AIN(+) to AIN(-) <sup>4</sup>                                 | ±50 V                   |

| AVDD5 to AGND, DGND <sup>3,5</sup>                            | −0.3 V to +6.5 V        |

| IOVDD to AGND, DGND <sup>3, 5</sup>                           | -0.3 V to +6.5 V        |

| AGND to DGND <sup>5</sup>                                     | −0.3 V to +0.3 V        |

| AGND to VSS                                                   | $AGND \ge VSS - 0.3 V$  |

| AVDD5 to VDD                                                  | $AVDD5 \le VDD + 0.3 V$ |

| REFIN(+), REFIN(–), AIN1(LV),<br>AIN2(LV), AINCOM(LV) to AGND | -0.3 V to AVDD5 + 0.3 V |

| Digital Inputs and Outputs to DGND                            | -0.3 V to IOVDD + 0.3 V |

| Operating Temperature Range                                   | −40°C to +105°C         |

| Storage Temperature Range                                     | −65°C to +150°C         |

| Maximum Junction Temperature                                  | 150°C                   |

| Electrostatic Discharge (ESD),<br>Human Body Model            | 700 V                   |

| Field Induced Charge Device<br>Model (FICDM)                  | 1250 V                  |

| Reflow Soldering (Pb-Free)                                    | JEDEC J-STD-020         |

| Peak Temperature                                              | 260°C                   |

| Time at Peak Temperature                                      | 10 sec to 40 sec        |

<sup>&</sup>lt;sup>1</sup> HV pins are AIN(+), AIN(-), RTD, EXRS, and EXRF.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

**Table 4. Thermal Resistance**

| Package Type          | θ <sub>JA</sub> | Unit |

|-----------------------|-----------------|------|

| CP-40-15 <sup>1</sup> | 35              | °C/W |

$<sup>^{1}</sup>$   $\theta_{JA}$  is specified for a device soldered on a JEDEC 4-layer test board for surface-mount packages with 16 thermal vias. The values listed in Table 4 are based on simulated data.

### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Applying a voltage to an HV pin that is more negative than the potential of the system negative power supply can only be accomplished by connecting an external diode from the VSS pin to the system negative power supply (see Figure 29).

<sup>&</sup>lt;sup>3</sup> Pins with the same name must be shorted together.

$<sup>^4</sup>$  Using an input RC low-pass filter with R = 10  $\Omega$ , 0.5 W and C = 47 nF, 50 V.

<sup>&</sup>lt;sup>5</sup> It is recommended to short AGND and DGND pins together as close to the device as possible.

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

Table 5. Pin Function Descriptions<sup>1</sup>

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | REFIN(-) | Reference Input Negative. This pin works with the REFIN(+) pin. Connect to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2       | REFIN(+) | Reference Input Positive. Connect an external reference voltage between the REFIN(+) and REFIN(–) pins. The RTD excitation current functionality operates with a 2.5 V reference only.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3       | iREFF    | RTD Excitation Current External Reference Resistor Force Pin. This pin is used when an external precision resistor is required as the reference for generating the RTD excitation currents. This pin forces the REFIN(+) voltage across the external resistor. Connect this pin and the iREFS pin in a star point to the top of the external precision resistor. Minimize the pin capacitance by placing the precision resistor as close as possible to the iREFS and iREFF pins. For more information, see the RTD Mode section. No other circuit connections are allowed.               |

| 4       | iREFS    | RTD Excitation Current External Reference Resistor Sense Pin. This pin is used when an external precision resistor is required as the reference for generating the RTD excitation currents. This pin senses the RTD reference current flowing through the external resistor. Connect this pin and the iREFF pin in a star point to the top of the external precision resistor. Minimize the pin capacitance by placing the precision resistor as close as possible to the iREFS and iREFF pins. For more information, see the RTD Mode section. No other circuit connections are allowed. |

| 5       | REFOUT   | Internal 2.5 V Reference Output Pin. Decouple this pin to GND using a 100 nF capacitor when the internal reference is selected. Leave this pin open circuit when operating the device with an external reference applied to the REFIN(+) and REFIN(-) pins.                                                                                                                                                                                                                                                                                                                               |

| 6       | ADCAVDD  | Decoupling Node for the Internal Linear Regulator Output. Decouple this pin using a 1 µF capacitor to AGND (Pin 7).                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7       | AGND     | Analog Ground (0 V). Ground for the ADC core. It is recommended to short the AGND and DGND pins together, as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8       | AGND     | Analog Ground (0 V). Ground for the analog front end (AFE). It is recommended to short the AGND and DGND pins together as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9       | AVDD5    | Analog Power Supply (5 V). Power supply for the ADC core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10      | NIC      | Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11      | AVDD5    | Analog Power Supply (5 V). Power supply for the AFE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 12      | AGND     | Analog Ground (0 V). Ground for the AFE. It is recommended to short the AGND and DGND pins together as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                         |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13      | CLKIO            | Clock Input/Output. This pin is the input for an external clock or the output of the on-chip clock.                                                                                                                                                                                                                                                 |

| 14      | DOUT/RDY         | Serial Interface Data Output (DOUT). This pin functions as a serial data output to access the output register of the ADC. The data is placed on the DOUT/RDY pin after the SCLK falling edge and is valid on the SCLK rising edge. When CS is high, the DOUT/RDY output is tristated.                                                               |

|         |                  | Data Ready Output (RDY). When CS is low, DOUT/RDY operates as a data ready pin, going low to indicate the completion of a conversion. If the data is not read after the conversion, the pin goes high before the next update occurs. The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. |

| 15      | DIN              | Serial Interface Data Input. Digital input.                                                                                                                                                                                                                                                                                                         |

| 16      | SCLK             | Serial Interface Clock. Digital input.                                                                                                                                                                                                                                                                                                              |

| 17      | CS               | Serial Interface Chip Select/Frame. Digital input.                                                                                                                                                                                                                                                                                                  |

| 18      | ERR              | Error Input/Output. Open-drain digital output.                                                                                                                                                                                                                                                                                                      |

| 19      | SYNC             | ADC Synchronization Input. When SYNC is brought low, the ADC aborts any active ADC conversion, and brings RDY high if it is low. When SYNC is brought high, the ADC starts a new conversion within a number of clock cycles. If multiple ADC channels are enabled the conversions restart with the first channel in the sequence.                   |

| 20, 21  | IOVDD            | Digital Power Supply (2 V to 5 V). Power supply for digital inputs and outputs.                                                                                                                                                                                                                                                                     |

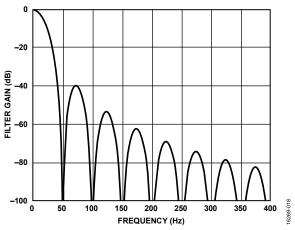

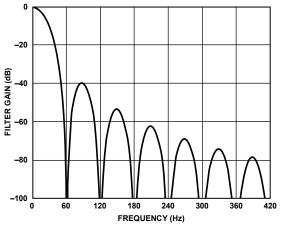

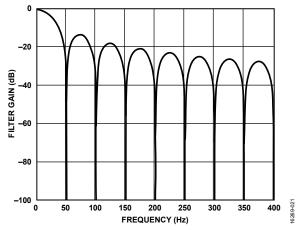

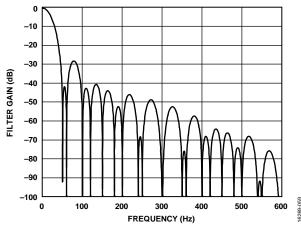

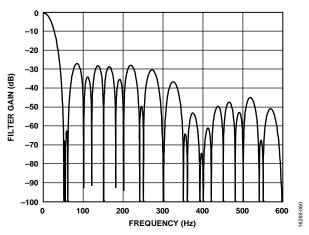

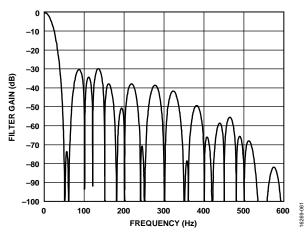

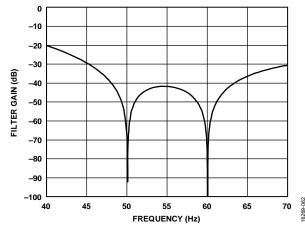

| 22      | DGND             | Digital Ground (0 V). Reference ground for the digital inputs and outputs. It is recommended to short the AGND and DGND pins together as close to the device as possible.                                                                                                                                                                           |