280MHz, 2.9ns Comparator Family with Rail-to-Rail Inputs and CMOS Outputs

#### **FEATURES**

- Very High Toggle Rate: 280MHz

- Low Propagation Delay: 2.9ns

- Rail-to-Rail Inputs Extend Beyond Both Rails

- Output Current Capability: ±22mA

- Low Quiescent Current: 4.5mA

- Features within the LTC6752 Family:

- 2.45V to 5.25V Input Supply and 1.71V to 3.5V Output Supply (Separate Supply Option)

- 2.45V to 3.5V Supply (Single Supply Option)

- Shutdown Pin for Reduced Power

- Output Latch and Adjustable Hysteresis

- Complementary Outputs

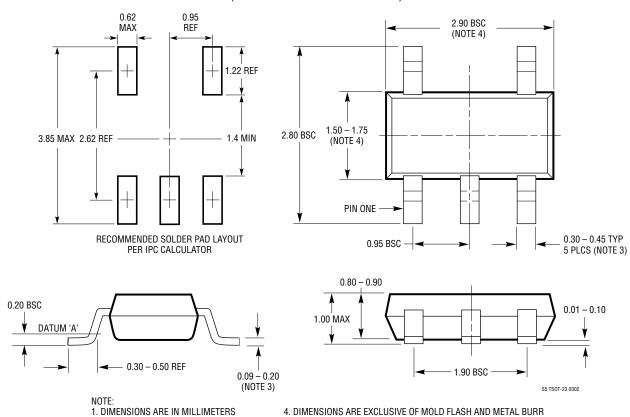

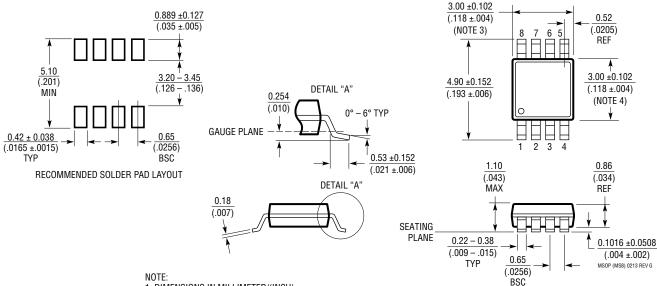

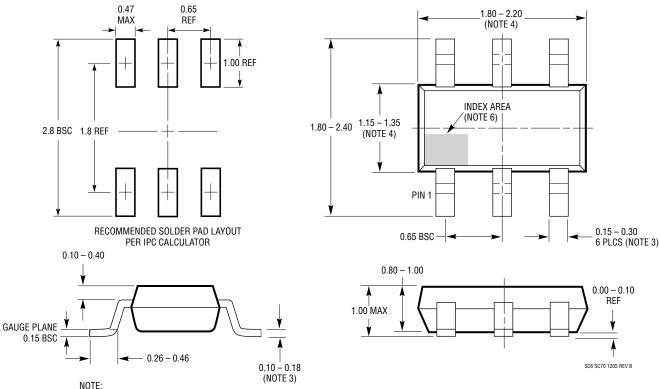

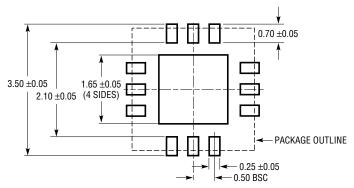

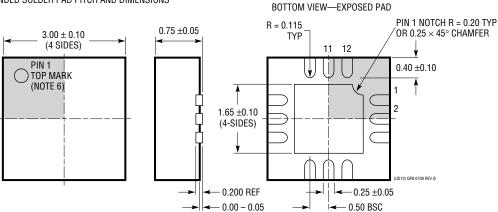

- Packages: TSOT-23, SC70, MSOP, 3mm × 3mm QFN

- Direct Replacement for ADCMP60X Family

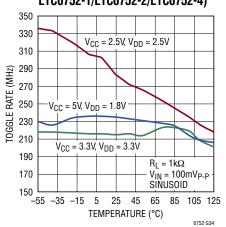

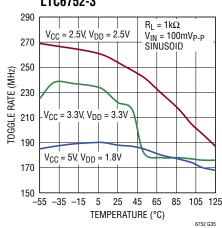

- Fully Specified from -55°C to 125°C

#### **APPLICATIONS**

- Clock and Data Recovery

- Level Shifting

- High Speed Data Acquisition Systems

- Window Comparators

- High Speed Line Receivers

- Fast Crystal Oscillators

- Time of Flight Measurements

- Time Domain Reflectometry

#### DESCRIPTION

The LTC®6752 is a family of very high speed comparators capable of supporting toggle rates up to 280MHz. These comparators exhibit low propagation delays of 2.9ns, and fast rise/fall times of 1.2ns. There are a total of 5 members in the LTC6752 family, with different options for separate input and output supplies, shutdown, output latch, adjustable hysteresis, complementary outputs, and package.

The LTC6752 comparators have rail-to-rail inputs that operate from 2.45V, up to 3.5V or 5.25V, depending on the option. The outputs are CMOS and the separate supply options can operate down to 1.71V, allowing for directly interfacing to 1.8V logic devices.

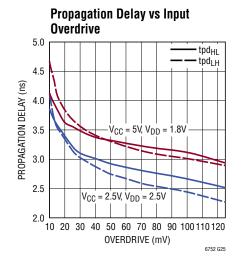

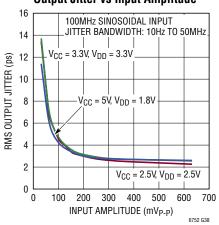

The low propagation delay of only 2.9ns combined with low dispersion of only 1.8ns (10mV to 125mV overdrive variation) makes these comparators an excellent choice for critical timing applications. Similarly, the fast toggle rate and the low jitter of 4.5ps RMS (100mV<sub>P-P</sub>, 100MHz input) make the LTC6752 family ideally suited for high frequency line driver and clock recovery circuits.

$\mathcal{L}\mathcal{T}$ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Analog Devices, Inc. All other trademarks are the property of their respective owners.

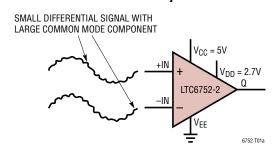

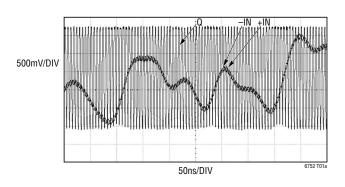

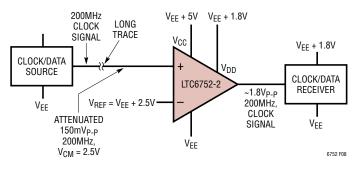

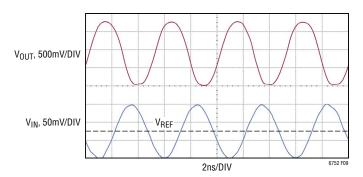

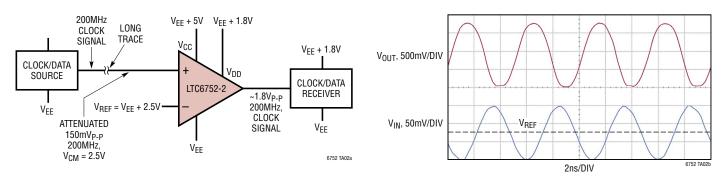

#### TYPICAL APPLICATION

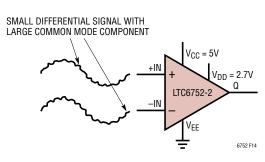

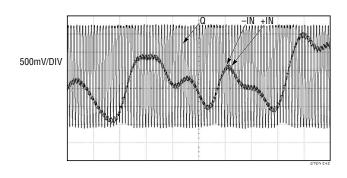

#### High Speed Differential Line Receiver with Excellent Common Mode Rejection

#### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| lotal Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> ) |       |

|------------------------------------------------------------|-------|

| (LTC6752-2/LTC6752-3/LTC6752-4)                            | 5.5V  |

| (LTC6752/LTC6752-1)                                        | 3.6V  |

| Total Supply Voltage (V <sub>DD</sub> to V <sub>FF</sub> ) |       |

| Input Current (+IN, -IN, SHDN, LE/HYST)                    |       |

| (Note 2)                                                   | ±10mA |

| Output Current (Q, $\overline{Q}$ ) (Note 3)               | ±50mA |

|                                                            |       |

| Specified Temperature Range (Note | 4)            |

|-----------------------------------|---------------|

| LTC6752I                          | 40°C to 85°C  |

| LTC6752H                          | 40°C to 125°C |

| LTC6752MP                         | 55°C to 125°C |

| Storage Temperature Range         | 65°C to 125°C |

| Maximum Junction Temperature (No  | ote 3) 150°C  |

| Lead Temperature Soldering (10s)  | 300°C         |

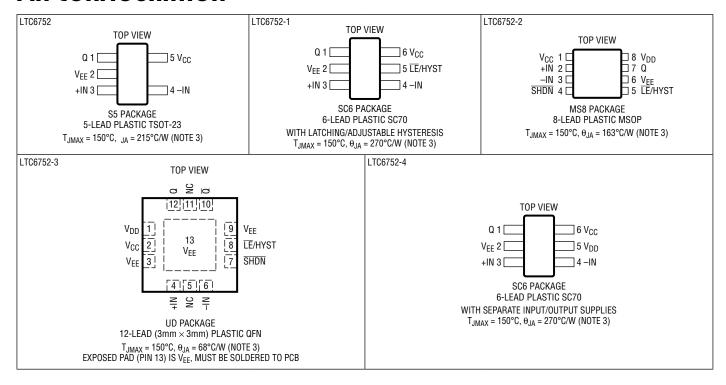

#### PIN CONFIGURATION

Table 1. Features and Part Numbers

| PART#     | LATCHING/ADJUSTABLE<br>Hysteresis | SEPARATE INPUT/<br>OUTPUT SUPPLIES | SHUTDOWN | COMPLEMENTARY OUTPUTS | PACKAGE OFFERING |

|-----------|-----------------------------------|------------------------------------|----------|-----------------------|------------------|

| LTC6752   |                                   |                                    |          |                       | TS0T-23-5        |

| LTC6752-1 | •                                 |                                    |          |                       | SC70-6           |

| LTC6752-2 | •                                 | •                                  | •        |                       | MS8              |

| LTC6752-3 | •                                 | •                                  | •        | •                     | 3mm × 3mm QFN    |

| LTC6752-4 |                                   | •                                  |          |                       | SC70-6           |

#### ORDER INFORMATION http://www.linear.com/product/LTC6752#orderinfo

#### **Lead Free Finish**

| TAPE AND REEL (MINI) | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION    | SPECIFIED TEMPERATURE RANGE |

|----------------------|---------------------|---------------|------------------------|-----------------------------|

| LTC6752IS5#TRMPBF    | LTC6752IS5#TRPBF    | LTGKT         | 5-Lead Plastic TSOT-23 | -40°C to 85°C               |

| LTC6752HS5#TRMPBF    | LTC6752HS5#TRPBF    | LTGKT         | 5-Lead Plastic TSOT-23 | -40°C to 125°C              |

| LTC6752MPS5#TRMPBF   | LTC6752MPS5#TRPBF   | LTGKT         | 5-Lead Plastic TSOT-23 | -55°C to 125°C              |

| LTC6752ISC6-1#TRMPBF | LTC6752ISC6-1#TRPBF | LGQK          | 6-Lead Plastic SC-70   | -40°C to 85°C               |

| LTC6752HSC6-1#TRMPBF | LTC6752HSC6-1#TRPBF | LGQK          | 6-Lead Plastic SC-70   | -40°C to 125°C              |

| LTC6752ISC6-4#TRMPBF | LTC6752ISC6-4#TRPBF | LGQM          | 6-Lead Plastic SC-70   | -40°C to 85°C               |

| LTC6752HSC6-4#TRMPBF | LTC6752HSC6-4#TRPBF | LGQM          | 6-Lead Plastic SC-70   | -40°C to 125°C              |

TRM = 500 pieces. \*Temperature grades are identified by a label on the shipping container.

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | SPECIFIED TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-----------------------------|

| LTC6752IMS8-2#PBF | LTC6752IMS8-2#TRPBF | LTGKW         | 8-Lead Plastic MSOP             | -40°C to 85°C               |

| LTC6752HMS8-2#PBF | LTC6752HMS8-2#TRPBF | LTGKW         | 8-Lead Plastic MSOP             | -40°C to 125°C              |

| LTC6752IUD-3#PBF  | LTC6752IUD-3#TRPBF  | LGKV          | 12-Lead Plastic QFN (3mm × 3mm) | -40°C to 85°C               |

| LTC6752HUD-3#PBF  | LTC6752HUD-3#TRPBF  | LGKV          | 12-Lead Plastic QFN (3mm × 3mm) | -40°C to 125°C              |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/ Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** $(V_{CC} = 2.5V, V_{DD} = 2.5V, V_{EE} = 0)$ . The denotes the specifications which apply over the specified temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . LE/HYST, SHDN pins floating, $C_L = 5pF$ , $V_{OVERDRIVE} = 50mV$ , $-IN = V_{CM} = 300mV$ , $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL                            | PARAMETER                                                                   | CONDITIONS                                                                      |   | MIN                   | TYP   | MAX                   | UNITS                    |

|-----------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|---|-----------------------|-------|-----------------------|--------------------------|

| V <sub>CC</sub> - V <sub>EE</sub> | Supply Voltage (Note 5)                                                     | LTC6752/LTC6752-1 (Total Supply)<br>LTC6752-2/LTC6752-3/LTC6752-4 (Input Stage) | • | 2.45<br>2.45          |       | 3.5<br>5.25           | V                        |

| V <sub>DD</sub> - V <sub>EE</sub> | Output Stage Supply Voltage (Note 5)                                        | LTC6752-2/LTC6752-3/LTC6752-4                                                   | • | 1.71                  |       | 3.5                   | V                        |

| $V_{CMR}$                         | Input Voltage Range (Note 7)                                                |                                                                                 | • | V <sub>EE</sub> - 0.2 |       | V <sub>CC</sub> + 0.1 | V                        |

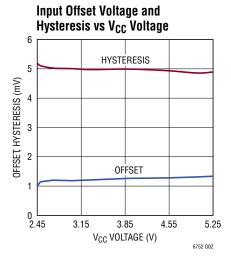

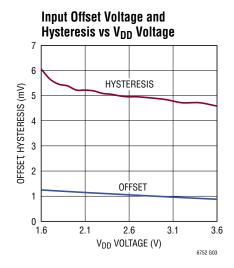

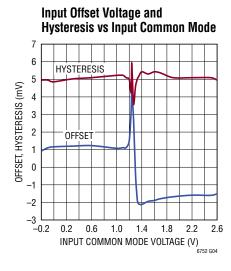

| V <sub>OS</sub>                   | Input Offset Voltage (Note 6)                                               |                                                                                 | • | -5.5<br>-8.5          | ±1.2  | 5.5<br>8.5            | mV<br>mV                 |

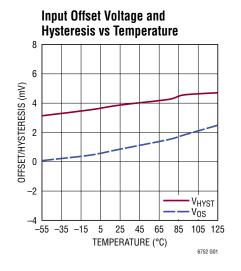

| TCV <sub>OS</sub>                 | Input Offset Voltage Drift                                                  |                                                                                 | • |                       | 18    |                       | μV/°C                    |

| V <sub>HYST</sub>                 | Input Hysteresis Voltage (Note 6)                                           | LE/HYST Pin Floating                                                            |   |                       | 5     |                       | mV                       |

| C <sub>IN</sub>                   | Input Capacitance                                                           |                                                                                 |   |                       | 1.1   |                       | pF                       |

| $R_{DM}$                          | Differential Mode Resistance                                                |                                                                                 |   |                       | 57    |                       | kΩ                       |

| R <sub>CM</sub>                   | Common Mode Resistance                                                      |                                                                                 |   |                       | 6.4   |                       | MΩ                       |

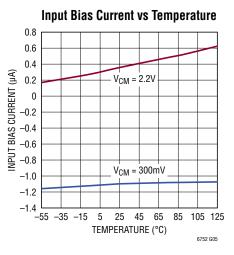

| I <sub>B</sub>                    | Input Bias Current                                                          | $V_{CM} = V_{EE} + 0.3V$                                                        | • | -3.8<br>-4            | -1.35 |                       | μ <b>Α</b><br>μ <b>Α</b> |

|                                   |                                                                             | $V_{CM} = V_{CC} - 0.3V$                                                        | • |                       | 0.3   | 1.25<br>2.1           | μA<br>μA                 |

| I <sub>OS</sub>                   | Input Offset Current                                                        |                                                                                 | • | -0.75                 | ±0.1  | 0.75                  | μA                       |

| CMRR_<br>LVCM                     | Common Mode Input Range, Low V <sub>CM</sub><br>Region                      | $V_{CM} = V_{EE} - 0.2V \text{ to } V_{CC} - 1.5V$                              | • | 51<br>46              | 69    |                       | dB<br>dB                 |

| CMRR_FR                           | Common Mode Rejection Ratio (Measured at Extreme Ends of V <sub>CMR</sub> ) | $V_{CM} = V_{EE} - 0.2V \text{ to } V_{CC} + 0.1V$                              | • | 50<br>45.5            | 65    |                       | dB<br>dB                 |

**ELECTRICAL CHARACTERISTICS**  $(V_{CC} = 2.5V, V_{DD} = 2.5V, V_{EE} = 0)$ . The denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . LE/HYST, SHDN pins floating,  $C_L = 5pF$ ,  $V_{OVERDRIVE} = 50mV$ ,  $-IN = V_{CM} = 300mV$ ,  $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                                               | CONDITIONS                                                                                                                                                                                                                                                                                                  |   | MIN      | TYP              | MAX         | UNITS          |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------------------|-------------|----------------|

| PSRR_V <sub>CC</sub> | Input Power Supply Rejection Ratio                                                                                      | V <sub>CM</sub> = 0.3V, V <sub>DD</sub> = 2.5V, V <sub>CC</sub> Varied from 2.45V to 5.25V (LTC6752-2/LTC6752-3/LTC6752-4)                                                                                                                                                                                  | • | 59<br>57 | 74               |             | dB<br>dB       |

|                      | Total Power Supply Rejection Ratio                                                                                      | V <sub>CM</sub> = 0.3V, V <sub>CC</sub> Varied from 2.45V to 3.5V (LTC6752/LTC6752-1)                                                                                                                                                                                                                       | • | 53<br>51 | 73               |             | dB<br>dB       |

| PSRR_V <sub>DD</sub> | Output Power Supply Rejection Ratio                                                                                     | V <sub>CM</sub> = 0.3V, V <sub>DD</sub> Varied from 1.71V to 3.5V (LTC6752-2/LTC6752-3/LTC6752-4)                                                                                                                                                                                                           | • | 56<br>51 | 71               |             | dB<br>dB       |

| A <sub>VOL</sub>     | Open Loop Gain                                                                                                          | LTC6752-1/LTC6752-2/LTC6752-3, Hysteresis<br>Removed (Note 12)                                                                                                                                                                                                                                              |   |          | 6000             |             | V/V            |

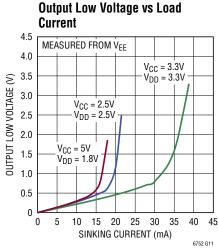

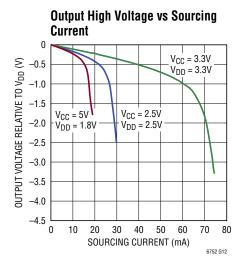

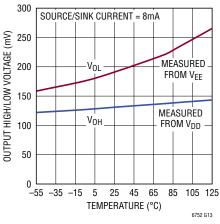

| V <sub>OH</sub>      | Output High Voltage (Amount Below V <sub>DD</sub> (LTC6752-2/LTC5752-3/LTC6752-4), V <sub>CC</sub> (LTC6752/LTC6752-1)) | I <sub>SOURCE</sub> = 8mA                                                                                                                                                                                                                                                                                   | • |          | 130              | 260<br>340  | mV<br>mV       |

| V <sub>OL</sub>      | Output Low Voltage (Referred to V <sub>EE</sub> )                                                                       | I <sub>SINK</sub> = 8mA                                                                                                                                                                                                                                                                                     | • |          | 200              | 340<br>400  | mV<br>mV       |

| I <sub>SC</sub>      | Output Short-Circuit Current                                                                                            | Source                                                                                                                                                                                                                                                                                                      | • | 16<br>12 | 30               |             | mA<br>mA       |

|                      |                                                                                                                         | Sink                                                                                                                                                                                                                                                                                                        | • | 15<br>9  | 22               |             | mA<br>mA       |

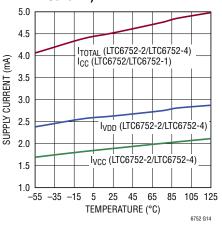

| I <sub>VCC</sub>     | V <sub>CC</sub> Supply Current, Device On                                                                               | LTC6752/LTC6752-1                                                                                                                                                                                                                                                                                           | • |          | 4.5              | 5.0<br>5.9  | mA<br>mA       |

|                      |                                                                                                                         | LTC6752-2/LTC6752-3/LTC6752-4                                                                                                                                                                                                                                                                               | • |          | 1.9              | 2.25<br>2.5 | mA<br>mA       |

| I <sub>VDD</sub>     | V <sub>DD</sub> Supply Current, Device On                                                                               | LTC6752-2/LTC6752-4                                                                                                                                                                                                                                                                                         | • |          | 2.6              | 3.2<br>3.4  | mA<br>mA       |

|                      |                                                                                                                         | LTC6752-3                                                                                                                                                                                                                                                                                                   | • |          | 4.3              | 4.75<br>5.2 | mA<br>mA       |

| I <sub>TOTAL</sub>   | Total Supply Current, Device On                                                                                         | LTC6752/LTC6752-1/LTC6752-2/LTC6752-4                                                                                                                                                                                                                                                                       | • |          | 4.5              | 5.0<br>5.9  | mA<br>mA       |

|                      |                                                                                                                         | LTC6752-3                                                                                                                                                                                                                                                                                                   | • |          | 6.2              | 6.65<br>7.7 | mA<br>mA       |

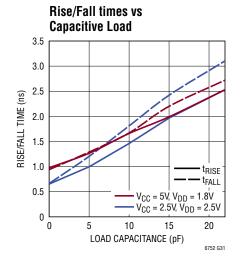

| $t_R$ , $t_F$        | Rise/Fall time                                                                                                          | 10% to 90%                                                                                                                                                                                                                                                                                                  |   |          | 1.2              |             | ns             |

| t <sub>PD</sub>      | Propagation Delay (Note 8)                                                                                              | V <sub>OVERDRIVE</sub> = 50mV                                                                                                                                                                                                                                                                               | • |          | 2.9              | 5<br>5.5    | ns<br>ns       |

| t <sub>SKEW</sub>    | Propagation Delay Skew, Rising to Falling<br>Transition (Note 9)                                                        |                                                                                                                                                                                                                                                                                                             |   |          | 300              |             | ps             |

| $\overline{t_{ODD}}$ | Overdrive Dispersion (Note 8)                                                                                           | Overdrive Varied from 10mV to 125mV                                                                                                                                                                                                                                                                         |   |          | 1.8              |             | ns             |

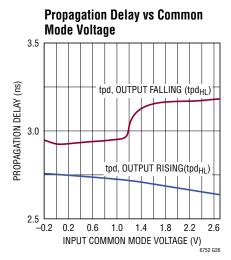

| t <sub>CMD</sub>     | Common Mode Dispersion                                                                                                  | V <sub>CM</sub> Varied from V <sub>EE</sub> – 0.2V to V <sub>CC</sub> + 0.1V                                                                                                                                                                                                                                |   |          | 240              |             | ps             |

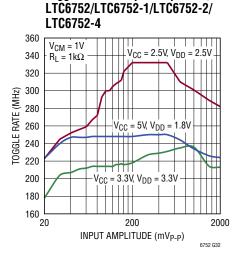

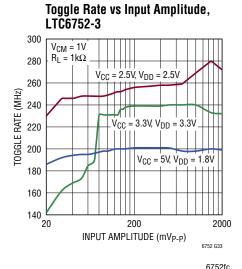

| TR                   | Toggle Rate (Note 11)                                                                                                   | 100mV <sub>P-P</sub> Input, LTC6752/LTC6752-1/<br>LTC6752-2/LTC6752-4<br>100mV <sub>P-P</sub> Input, LTC6752-3                                                                                                                                                                                              |   |          | 280<br>250       |             | MHz<br>MHz     |

| t <sub>JITTER</sub>  | RMS Jitter                                                                                                              | $\begin{split} V_{IN} &= 100 \text{mV}_{\text{P-P}}, \\ f_{IN} &= 100 \text{MHz}, \text{Jitter BW} = 10 \text{Hz} - 50 \text{MHz} \\ f_{IN} &= 61.44 \text{MHz}, \text{Jitter BW} = 10 \text{Hz} - 30.72 \text{MHz} \\ f_{IN} &= 10 \text{MHz}, \text{Jitter BW} = 10 \text{Hz} - 5 \text{MHz} \end{split}$ |   |          | 4.5<br>6.0<br>30 |             | ps<br>ps<br>ps |

**ELECTRICAL CHARACTERISTICS**  $(V_{CC} = 2.5V, V_{DD} = 2.5V, V_{EE} = 0)$ . The denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . LE/HYST, SHDN pins floating,  $C_L = 5pF$ ,  $V_{OVERDRIVE} = 50mV$ ,  $-IN = V_{CM} = 300mV$ ,  $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL                         | PARAMETER                                     | CONDITIONS                               |   | MIN  | TYP  | MAX        | UNITS    |

|--------------------------------|-----------------------------------------------|------------------------------------------|---|------|------|------------|----------|

| Latching/Adju                  | ustable Hysteresis Characteristics (LTC6752-1 | /LTC6752-2/LTC6752-3 Only)               |   |      |      |            |          |

| V <sub>LE/HYST</sub>           | LE/HYST Pin Voltage                           | Open Circuit                             | • | 1.05 | 1.25 | 1.45       | V        |

| R <sub>HYST</sub>              | Resistance Looking Into LE/HYST               | LE/HYST Pin Voltage < Open Circuit Value | • | 15   | 20   | 25         | kΩ       |

| V <sub>HYST_LARGE</sub>        | Hysteresis Voltage                            | $V_{\overline{LE}/HYST} = 800 \text{mV}$ |   |      | 40   |            | mV       |

| $V_{IL}\overline{LE}$          | Latch Pin Voltage, Latch Guaranteed           |                                          | • |      |      | 0.3        | V        |

| V <sub>IH_LE</sub>             | Latch Pin Voltage, Hysteresis Disabled        | Output Not Latched                       | • | 1.7  |      |            | V        |

| I <sub>IH_LE</sub>             | Latch Pin Current High                        | $V_{\overline{LE}/HYST} = 1.7V$          | • |      | 30   | 72         | μA       |

| I <sub>IL_EE</sub>             | Latch Pin Current Low                         | $V_{\overline{LE}/HYST} = 0.3V$          | • | -70  | -47  |            | μA       |

| t <sub>SETUP</sub>             | Latch Setup Time (Note 10)                    |                                          |   |      | -2   |            | ns       |

| t <sub>HOLD</sub>              | Latch Hold Time (Note 10)                     |                                          |   |      | 2    |            | ns       |

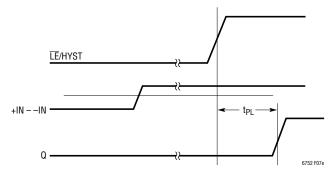

| t <sub>PL</sub>                | Latch to Output Delay                         |                                          |   |      | 7    |            | ns       |

| Shutdown Ch                    | aracteristics (LTC6752-2/LTC6752-3 Only)      |                                          |   |      |      |            |          |

| I <sub>SD_VCC</sub>            | Shutdown Mode Input Stage Supply Current      | $V_{\overline{SHDN}} = 0.6V$             | • |      | 400  | 585<br>620 | μA<br>μA |

| I <sub>SD_VDD</sub>            | Shutdown Mode Output Stage Supply<br>Current  | V <sub>SHDN</sub> = 0.6V, LTC6752-2      | • |      | 185  | 340<br>380 | μA<br>μA |

|                                |                                               | V <sub>SHDN</sub> = 0.6V, LTC6752-3      | • |      | 250  | 650<br>680 | μA<br>μA |

| $t_{SD}$                       | Shutdown Time                                 | Output Hi-Z                              |   |      | 80   |            | ns       |

| V <sub>IH_SD</sub>             | Shutdown Pin Voltage High                     | Part Guaranteed to Be Powered On         | • | 1.3  |      |            | V        |

| $\overline{V_{\text{IL\_SD}}}$ | Shutdown Pin Voltage Low                      | Part Guaranteed to Be Powered Off        | • |      | -    | 0.6        | V        |

| t <sub>WAKEUP</sub>            | Wake-Up Time from Shutdown                    | V <sub>OD</sub> = 100mV, Output Valid    |   |      | 100  |            | ns       |

$(V_{CC}=3.3V,\,V_{DD}=3.3V,\,V_{EE}=0)$ . The ullet denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A=25^{\circ}C$ .  $\overline{LE}/HYST$ ,  $\overline{SHDN}$  pins floating,  $C_L=5pF,\,V_{OVERDRIVE}=50mV,\,-IN=V_{CM}=300mV,\,+IN=-IN+V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL                            | PARAMETER                         | CONDITIONS                                                                      |   | MIN                   | TYP  | MAX                   | UNITS    |

|-----------------------------------|-----------------------------------|---------------------------------------------------------------------------------|---|-----------------------|------|-----------------------|----------|

| V <sub>CC</sub> - V <sub>EE</sub> | Supply Voltage (Note 5)           | LTC6752/LTC6752-1 (Total Supply)<br>LTC6752-2/LTC6752-3/LTC6752-4 (Input Stage) | • | 2.45<br>2.45          |      | 3.5<br>5.25           | V<br>V   |

| V <sub>DD</sub> - V <sub>EE</sub> | Output Supply Voltage (Note 5)    | LTC6752-2/LTC6752-3/LTC6752-4                                                   | • | 1.71                  |      | 3.5                   | V        |

| V <sub>CMR</sub>                  | Input Voltage Range (Note 7)      |                                                                                 | • | V <sub>EE</sub> – 0.2 |      | V <sub>CC</sub> + 0.1 | V        |

| V <sub>OS</sub>                   | Input Offset Voltage (Note 6)     |                                                                                 | • | -5.5<br>-9            | ±1.2 | 5.5<br>9              | mV<br>mV |

| TCV <sub>OS</sub>                 | Input Offset Voltage Drift        |                                                                                 | • |                       | 18   |                       | μV/°C    |

| V <sub>HYST</sub>                 | Input Hysteresis Voltage (Note 6) | LE/HYST Pin Floating                                                            |   |                       | 4.7  |                       | mV       |

| C <sub>IN</sub>                   | Input Capacitance                 |                                                                                 |   |                       | 1.1  |                       | pF       |

| $R_{DM}$                          | Differential Mode Resistance      |                                                                                 |   |                       | 57   |                       | kΩ       |

| R <sub>CM</sub>                   | Common Mode Resistance            |                                                                                 |   |                       | 6.4  |                       | MΩ       |

| I <sub>B</sub>                    | Input Bias Current                | $V_{CM} = V_{EE} + 0.3V$                                                        | • | -3.8<br>-4.1          | -1.4 |                       | μA<br>μA |

|                                   |                                   | $V_{CM} = V_{CC} - 0.3V$                                                        | • |                       | 0.33 | 1.5<br>2.3            | μA<br>μA |

| I <sub>OS</sub>                   | Input Offset Current              |                                                                                 | • | -0.75                 | ±0.1 | 0.75                  | μA       |

**ELECTRICAL CHARACTERISTICS**  $(V_{CC} = 3.3V, V_{DD} = 3.3V, V_{EE} = 0)$ . The denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . LE/HYST, SHDN pins floating,  $C_L = 5pF$ ,  $V_{OVERDRIVE} = 50mV$ ,  $-IN = V_{CM} = 300mV$ ,  $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL               | PARAMETER                                                                                                               | CONDITIONS                                                                                                                |   | MIN      | TYP       | MAX          | UNITS    |

|----------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---|----------|-----------|--------------|----------|

| CMRR_<br>LVCM        | Common Mode Input Range, Low V <sub>CM</sub><br>Region                                                                  | $V_{CM} = V_{EE} - 0.2V$ to $V_{CC} - 1.5V$                                                                               | • | 52<br>48 | 70        |              | dB<br>dB |

| CMRR_FR              | Common Mode Rejection Ratio (Measured at Extreme Ends of V <sub>CMR</sub> )                                             | $V_{CM} = V_{EE} - 0.2V \text{ to } V_{CC} + 0.1V$                                                                        | • | 50<br>46 | 66        |              | dB<br>dB |

| PSRR_V <sub>CC</sub> | Input Power Supply Rejection Ratio                                                                                      | V <sub>CM</sub> = 0.3V, V <sub>DD</sub> = 3.3V,V <sub>CC</sub> Varied from 2.45V to 5.25V (LTC6752-2/LTC6752-3/LTC6752-4) | • | 59<br>57 | 75        |              | dB       |

|                      | Total Power Supply Rejection Ratio                                                                                      | V <sub>CM</sub> = 0.3V,V <sub>CC</sub> Varied from 2.45V to 3.5V (LTC6752/LTC6752-1)                                      | • | 53<br>51 | 73        |              | dB<br>dB |

| PSRR_V <sub>DD</sub> | Output Power Supply Rejection Ratio                                                                                     | V <sub>CM</sub> = 0.3V, V <sub>DD</sub> Varied from 1.71V to 3.5V (LTC6752-2/LTC6752-3/LTC6752-4)                         | • | 56<br>51 | 71        |              | dB<br>dB |

| A <sub>VOL</sub>     | Open Loop Gain                                                                                                          | LTC6752-1/LTC6752-2/LTC6752-3,Hysteresis<br>Removed (Note 12)                                                             |   |          | 7000      |              | V/V      |

| V <sub>OH</sub>      | Output High Voltage (Amount Below V <sub>DD</sub> (LTC6752-2/LTC5752-3/LTC6752-4), V <sub>CC</sub> (LTC6752/LTC6752-1)) | I <sub>SOURCE</sub> = 8mA                                                                                                 | • |          | 81        | 200<br>300   | mV<br>mV |

| V <sub>OL</sub>      | Output Low Voltage (Referred to V <sub>EE</sub> )                                                                       | I <sub>SINK</sub> = 8mA                                                                                                   | • |          | 155       | 320<br>350   | mV<br>mV |

| I <sub>SC</sub>      | Output Short-Circuit Current                                                                                            | Source                                                                                                                    | • | 35<br>30 | 70        |              | mA<br>mA |

|                      |                                                                                                                         | Sink                                                                                                                      | • | 20<br>15 | 39        |              | mA<br>mA |

| I <sub>VCC</sub>     | V <sub>CC</sub> Supply Current, Device On                                                                               | LTC6752/LTC6752-1                                                                                                         | • |          | 4.8       | 5.8<br>6.2   | mA<br>mA |

|                      |                                                                                                                         | LTC6752-2/LTC6752-3/LTC6752-4                                                                                             | • |          | 1.9       | 2.35<br>2.55 | mA<br>mA |

| I <sub>VDD</sub>     | V <sub>DD</sub> Supply Current, Device On                                                                               | LTC6752-2/LTC6752-4                                                                                                       | • |          | 2.9       | 3.45<br>3.65 | mA<br>mA |

|                      |                                                                                                                         | LTC6752-3                                                                                                                 | • |          | 4.75      | 5.35<br>5.75 | mA<br>mA |

| I <sub>TOTAL</sub>   | Total Supply Current, Device On                                                                                         | LTC6752/LTC6752-1/LTC6752-2/LTC6752-4                                                                                     | • |          | 4.8       | 5.8<br>6.2   | mA<br>mA |

|                      |                                                                                                                         | LTC6752-3                                                                                                                 | • |          | 6.6       | 7.7<br>8.3   | mA<br>mA |

| $t_R$ , $t_F$        | Rise/Fall Time                                                                                                          | 10% to 90%                                                                                                                |   |          | 1.35      |              | ns       |

| t <sub>PD</sub>      | Propagation Delay (Note 8)                                                                                              | V <sub>OVERDRIVE</sub> = 50mV                                                                                             | • |          | 3.00      | 5<br>5.5     | ns<br>ns |

| t <sub>SKEW</sub>    | Propagation Delay Skew, Rising to Falling<br>Transition (Note 9)                                                        |                                                                                                                           |   |          | 600       |              | ps       |

| $\overline{t_{ODD}}$ | Overdrive Dispersion (Note 8)                                                                                           | Overdrive Varied from 10mV to 125mV                                                                                       |   |          | 1.8       |              | ns       |

| t <sub>CMD</sub>     | Common Mode Dispersion                                                                                                  | V <sub>CM</sub> Varied from V <sub>EE</sub> —0.2V to V <sub>CC</sub> + 0.1V                                               |   |          | 240       |              | ps       |

| TR                   | Toggle Rate (Note 11)                                                                                                   | 100mV <sub>P-P</sub> Input                                                                                                |   |          | 215       |              | MHz      |

| t <sub>JITTER</sub>  | RMS jitter                                                                                                              | V <sub>IN</sub> = 100mV <sub>P-P</sub> , f <sub>IN</sub> = 100MHz,<br>Jitter BW = 10Hz – 50MHz                            |   |          | 4.8       |              | ps       |

|                      |                                                                                                                         | $f_{IN}$ = 61.44MHz, Jitter BW = 10Hz – 30.72MHz $f_{IN}$ = 10MHz, Jitter BW = 10Hz – 5MHz                                |   |          | 5.8<br>29 | _            | ps<br>ps |

**ELECTRICAL CHARACTERISTICS**  $(V_{CC} = 3.3V, V_{DD} = 3.3V, V_{EE} = 0)$ . The denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . LE/HYST, SHDN pins floating,  $C_L = 5pF$ ,  $V_{OVERDRIVE} = 50mV - IN = V_{CM} = 300mV$ ,  $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL                  | PARAMETER                                     | CONDITIONS                               |   | MIN  | TYP  | MAX        | UNITS    |

|-------------------------|-----------------------------------------------|------------------------------------------|---|------|------|------------|----------|

| Latching/Adju           | istable Hysteresis Characteristics (LTC6752-1 | /LTC6752-2/LTC6752-3 Only)               |   |      | -    |            |          |

| V <sub>LE/HYST</sub>    | LE/HYST Pin Voltage                           | Open Circuit                             | • | 1.05 | 1.25 | 1.45       | V        |

| R <sub>HYST</sub>       | Resistance Looking Into LE/HYST               | LE/HYST Pin Voltage < Open Circuit Value | • | 15   | 20   | 25         | kΩ       |

| V <sub>HYST_LARGE</sub> | Hysteresis Voltage                            | $V_{\overline{LE}/HYST} = 800mV$         |   |      | 40   |            | mV       |

| $V_{IL}\overline{LE}$   | Latch Pin Voltage, Latch Guaranteed           |                                          | • |      |      | 0.3        | V        |

| V <sub>IH_LE</sub>      | Latch Pin Voltage, Hysteresis Disabled        | Output Not Latched                       | • | 1.7  |      |            | V        |

| I <sub>IH_LE</sub>      | Latch Pin Current High                        | $V_{\overline{LE}/HYST} = 1.7V$          | • |      | 30   | 72         | μА       |

| I <sub>IL_TE</sub>      | Latch Pin Current Low                         | $V_{\overline{LE}/HYST} = 0.3V$          | • | -70  | -47  |            | μA       |

| t <sub>SETUP</sub>      | Latch Setup Time (Note 10)                    |                                          |   |      | -2   |            | ns       |

| t <sub>HOLD</sub>       | Latch Hold Time (Note 10)                     |                                          |   |      | 2    |            | ns       |

| $t_{PL}$                | Latch to Output Delay                         |                                          |   |      | 7    |            | ns       |

| Shutdown Ch             | aracteristics (LTC6752-2/LTC6752-3 Only)      |                                          |   |      |      |            |          |

| I <sub>SD_VCC</sub>     | Shutdown Mode Input Stage Supply Current      | $V_{\overline{SHDN}} = 0.6V$             | • |      | 430  | 600<br>660 | μA<br>μA |

| I <sub>SD_VDD</sub>     | Shutdown Mode Output Stage Supply<br>Current  | V <sub>SHDN</sub> = 0.6V, LTC6752-2      | • |      | 200  | 420<br>450 | μA<br>μA |

|                         |                                               | V <sub>SHDN</sub> = 0.6V, LTC6752-3      | • |      | 300  | 700<br>800 | μA<br>μA |

| $t_{SD}$                | Shutdown Time                                 | Output Hi-Z                              |   |      | 80   |            | ns       |

| V <sub>IH_SD</sub>      | Shutdown Pin Voltage High                     | Part Guaranteed to Be Powered On         | • | 1.3  |      |            | V        |

| $V_{IL\_SD}$            | Shutdown Pin Voltage Low                      | Part Guaranteed to Be Powered Off        | • |      |      | 0.6        | V        |

| t <sub>WAKEUP</sub>     | Wake-Up Time from Shutdown                    | V <sub>OD</sub> = 100mV, Output Valid    |   |      | 100  |            | ns       |

$(V_{CC} = 5V, V_{DD} = 1.8V, V_{EE} = 0, LTC6752-2/LTC6752-3/LTC6752-4 only)$ . The  $\bullet$  denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $\overline{LE}/HYST$ ,  $\overline{SHDN}$  pins floating,  $C_L = 5pF$ ,  $V_{OVERDRIVE} = 50mV$ ,  $-IN = V_{CM} = 300mV$ ,  $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL                            | PARAMETER                         | CONDITIONS               |   | MIN                   | TYP  | MAX                   | UNITS    |

|-----------------------------------|-----------------------------------|--------------------------|---|-----------------------|------|-----------------------|----------|

| V <sub>CC</sub> - V <sub>EE</sub> | Input Supply Voltage (Note 5)     |                          | • | 2.45                  |      | 5.25                  | V        |

| V <sub>DD</sub> - V <sub>EE</sub> | Output Supply Voltage (Note5)     |                          | • | 1.71                  |      | 3.5                   | V        |

| V <sub>CMR</sub>                  | Input Voltage Range (Note 7)      |                          | • | V <sub>EE</sub> – 0.2 |      | V <sub>CC</sub> + 0.1 | V        |

| V <sub>OS</sub>                   | Input Offset Voltage (Note 6)     |                          | • | -5.5<br>-9            | ±1.2 | 5.5<br>9              | mV<br>mV |

| TCV <sub>OS</sub>                 | Input Offset Voltage Drift        |                          | • |                       | 14   |                       | μV/°C    |

| V <sub>HYST</sub>                 | Input Hysteresis Voltage (Note 6) | LE/HYST Pin Floating     |   |                       | 5.2  |                       | m۷       |

| C <sub>IN</sub>                   | Input Capacitance                 |                          |   |                       | 1.1  |                       | pF       |

| R <sub>DM</sub>                   | Differential Mode Resistance      |                          |   |                       | 57   | ,                     | kΩ       |

| R <sub>CM</sub>                   | Common Mode Resistance            |                          |   |                       | 6.4  |                       | MΩ       |

| I <sub>B</sub>                    | Input Bias Current                | $V_{CM} = V_{EE} + 0.3V$ | • | -3.9<br>-4.2          | -1.5 |                       | μA<br>μA |

|                                   |                                   | $V_{CM} = V_{CC} - 0.3V$ | • |                       | 0.36 | 1.6<br>2.5            | μA<br>μA |

# **ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5V$ , $V_{DD} = 1.8V$ , $V_{EE} = 0$ , LTC6752-2/LTC6752-3/LTC6752-4 only). The • denotes the specifications which apply over the specified temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . LE/HYST, $\overline{S}HD\overline{N}$ pins floating, $C_L = 5pF$ , $V_{OVERDRIVE} = 50mV$ , $-IN = V_{CM} = 300mV$ , $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL               | PARAMETER                                                                   | CONDITIONS                                                                                                                                                                        |   | MIN       | TYP              | MAX          | UNITS          |

|----------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|------------------|--------------|----------------|

| I <sub>OS</sub>      | Input Offset Current                                                        |                                                                                                                                                                                   | • | -0.9      | ±0.1             | 0.9          | μA             |

| CMRR_<br>LVCM        | Common Mode Input Range, Low V <sub>CM</sub><br>Region                      | $V_{CM} = V_{EE} - 0.2V \text{ to } V_{CC} - 1.5V$                                                                                                                                | • | 54<br>51  | 70               |              | dB<br>dB       |

| CMRR_FR              | Common Mode Rejection Ratio (Measured at Extreme Ends of V <sub>CMR</sub> ) | $V_{CM} = V_{EE} - 0.2V \text{ to } V_{CC} + 0.1V$                                                                                                                                | • | 53<br>48  | 68               |              | dB<br>dB       |

| PSRR_V <sub>CC</sub> | Input Power Supply Rejection Ratio                                          | $V_{CM} = 0.3V$ , $V_{DD} = 1.8V$ , $V_{CC}$ Varied from 2.45V to 5.25V                                                                                                           | • | 59<br>57  | 75               |              | dB             |

| PSRR_V <sub>DD</sub> | Output Power Supply Rejection Ratio                                         | V <sub>CM</sub> = 0.3V, V <sub>DD</sub> Varied from 1.71V to 3.5V                                                                                                                 | • | 57<br>51  | 71               |              | dB<br>dB       |

| A <sub>VOL</sub>     | Open Loop Gain                                                              | LTC6752-2/LTC6752-3 Hysteresis Removed (Note 12)                                                                                                                                  |   |           | 3500             |              | V/V            |

| V <sub>OH</sub>      | Output High Voltage (Amount Below V <sub>DD</sub> )                         | I <sub>SOURCE</sub> = 5.5mA                                                                                                                                                       | • |           | 200              | 400<br>450   | mV<br>mV       |

| V <sub>0L</sub>      | Output Low Voltage (Referred to V <sub>EE</sub> )                           | I <sub>SINK</sub> = 5.5mA                                                                                                                                                         | • |           | 200              | 400<br>550   | mV<br>mV       |

| I <sub>SC</sub>      | Output Short-Circuit Current                                                | Source                                                                                                                                                                            | • | 9<br>6.2  | 17               |              | mA<br>mA       |

|                      |                                                                             | Sink                                                                                                                                                                              | • | 11<br>6.2 | 19               |              | mA<br>mA       |

| I <sub>VCC</sub>     | V <sub>CC</sub> Supply Current, Device On                                   |                                                                                                                                                                                   | • |           | 2.1              | 2.65<br>2.85 | mA<br>mA       |

| I <sub>VDD</sub>     | V <sub>DD</sub> Supply Current, Device On                                   | LTC6752-2/LTC6752-4                                                                                                                                                               | • |           | 2.5              | 3<br>3.25    | mA<br>mA       |

|                      |                                                                             | LTC6752-3                                                                                                                                                                         | • |           | 3.4              | 4.4<br>4.8   | mA<br>mA       |

| I <sub>TOTAL</sub>   | Total Supply Current, Device On                                             | LTC6752-2/LTC6752-4                                                                                                                                                               | • |           | 4.5              | 5.65<br>6.1  | mA<br>mA       |

|                      |                                                                             | LTC6752-3                                                                                                                                                                         | • |           | 6                | 7.05<br>7.65 | mA<br>mA       |

| $t_R$ , $t_F$        | Rise/Fall Time                                                              | 10% to 90%                                                                                                                                                                        |   |           | 1.25             |              | ns             |

| t <sub>PD</sub>      | Propagation Delay (Note 8)                                                  | V <sub>OVERDRIVE</sub> = 50mV                                                                                                                                                     | • |           | 3.4              | 5.3<br>5.7   | ns<br>ns       |

| t <sub>SKEW</sub>    | Propagation Delay Skew, Rising to Falling<br>Transition (Note 9)            |                                                                                                                                                                                   |   |           | 400              |              | ps             |

| $\overline{t_{ODD}}$ | Overdrive Dispersion (Note 8)                                               | Overdrive Varied from 10mV to 125mV                                                                                                                                               |   |           | 1.8              |              | ns             |

| t <sub>CMD</sub>     | Common Mode Dispersion                                                      | V <sub>CM</sub> Varied from V <sub>EE</sub> – 0.2V to V <sub>CC</sub> + 0.1V                                                                                                      |   |           | 240              |              | ps             |

| TR                   | Toggle Rate (Note 11)                                                       | 100mV <sub>P-P</sub> Input, LTC6752-2/LTC6752-4<br>100mV <sub>P-P</sub> Input, LTC6752-3                                                                                          |   |           | 230<br>185       |              | MHz<br>MHz     |

| t <sub>JITTER</sub>  | RMS Jitter                                                                  | $V_{IN}$ = 100mV <sub>P-P</sub> , $f_{IN}$ = 100MHz,<br>Jitter BW = 10Hz – 50MHz<br>$f_{IN}$ = 61.44MHz, Jitter BW = 10Hz – 30.72MHz<br>$f_{IN}$ = 10MHz, Jitter BW = 10Hz – 5MHz |   |           | 4.3<br>5.8<br>28 |              | ps<br>ps<br>ps |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 5V$ ,  $V_{DD} = 1.8V$ ,  $V_{EE} = 0$ , LTC6752-2/LTC6752-3 only). The • denotes the specifications which apply over the specified temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . LE/HYST, SHDN pins floating,  $C_L = 5pF$ ,  $V_{OVERDRIVE} = 50mV$ ,  $-IN = V_{CM} = 300mV$ ,  $+IN = -IN + V_{OVERDRIVE}$ , 150mV step size unless otherwise noted.

| SYMBOL                         | PARAMETER                                     | CONDITIONS                               |     | MIN  | TYP  | MAX        | UNITS    |

|--------------------------------|-----------------------------------------------|------------------------------------------|-----|------|------|------------|----------|

| Latching/Adju                  | istable Hysteresis Characteristics (LTC6752-2 | /LTC6752-3 Only)                         |     |      |      |            |          |

| V <sub>LE/HYST</sub>           | LE/HYST Pin Voltage                           | Open Circuit                             | •   | 1.05 | 1.25 | 1.45       | V        |

| R <sub>HYST</sub>              | Resistance Looking Into LE/HYST               | LE/HYST Pin Voltage < Open Circuit Value | •   | 15   | 20   | 25         | kΩ       |

| V <sub>HYST_LARGE</sub>        | Modified Input Hysteresis Voltage (Note 2)    | V <sub>LE/HYST</sub> = 800mV             |     |      | 40   |            | mV       |

| $V_{IL}\overline{LE}$          | Latch Pin Voltage, Latch Guaranteed           |                                          | •   |      |      | 0.3        | V        |

| V <sub>IH_</sub> LE            | Latch Pin Voltage, Hysteresis Disabled        | Output Not Latched                       | •   | 1.7  |      |            | V        |

| I <sub>IH_LE</sub>             | Latch Pin Current High                        | V <sub>LE/HYST</sub> = 1.7V              | •   |      | 30   | 72         | μA       |

| I <sub>IL_</sub> <u>L</u> E    | Latch Pin Current Low                         | $V_{\overline{LE}/HYST} = 0.3V$          | •   | -70  | -47  |            | μA       |

| t <sub>SETUP</sub>             | Latch Setup Time (Note 10)                    |                                          |     |      | -2   |            | ns       |

| t <sub>HOLD</sub>              | Latch Hold Time (Note 10)                     |                                          |     |      | 2    |            | ns       |

| $t_{PL}$                       | Latch To Output Delay                         |                                          |     |      | 7    |            | ns       |

| Shutdown Ch                    | aracteristics (LTC6752-2/LTC6752-3 Only)      |                                          |     |      |      |            |          |

| I <sub>SD_VCC</sub>            | Shutdown Mode Input Stage Supply Current      | $V_{\overline{SHDN}} = 0.6V$             | •   |      | 500  | 650<br>750 | μA<br>μA |

| I <sub>SD_VDD</sub>            | Shutdown Mode Output Stage Supply<br>Current  | V <sub>SHDN</sub> = 0.6V, LTC6752-2      | •   |      | 170  | 400<br>450 | μA<br>μA |

|                                |                                               | V <sub>SHDN</sub> = 0.6V, LTC6752-3      | •   |      | 240  | 600<br>650 | μA<br>μA |

| $t_{SD}$                       | Shutdown Time                                 | Output Hi-Z                              |     |      | 80   |            | ns       |

| $\overline{V_{\text{IH\_SD}}}$ | Shutdown Pin Voltage High                     | Part Guaranteed to Be Powered On         | •   | 1.3  |      |            | V        |

| V <sub>IL_SD</sub>             | Shutdown Pin Voltage Low                      | Part Guaranteed to Be Powered Off        | •   |      |      | 0.6        | V        |

| t <sub>WAKEUP</sub>            | Wake-Up Time from Shutdown                    | V <sub>OD</sub> = 100mV, Output Valid    | 100 |      | ns   |            |          |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Reverse biased ESD protection diodes exist on all input, shutdown, latching/hysteresis and output pins. If the voltage on these pins goes 300mV beyond either supply rail, the current should be limited to less than 10mA. This parameter is guaranteed to meet specification through design and/or characterization. It is not production tested.

**Note 3:** A heat sink may be required to keep the junction temperature below the absolute maximum rating. This parameter is guaranteed to meet specified performance through design and/or characterization. It is not production tested.

**Note 4:** The LTC6752I/LTC6752-1I/LTC6752-2I/LTC6752-3I/LTC6752-4I are guaranteed to meet specified performance from –40°C to 85°C. The LTC6752H/LTC6752-1H/LTC6752-2H/LTC6752-3H/LTC6752-4H are guaranteed to meet specified performance from –40°C to 125°C.

**Note 5:** Total output supply voltage range is guaranteed by the PSRR\_V\_DD test. Total input supply voltage range for the LTC6752-2, LTC6752-3 and LTC6752-4 is guaranteed by the PSRR\_V\_CC test. For the LTC6752 and LTC6752-1, the supply voltage range is guaranteed by the PSRR\_V\_CC test. The LTC6752MP is guaranteed to meet specified performance from  $-55^{\circ}$ C to 125°C.

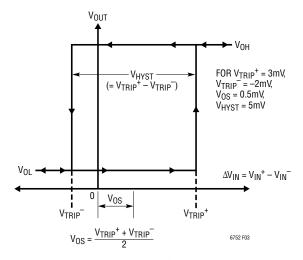

**Note 6:** Both hysteresis and offset are measured by determining positive and negative trip points (input values needed to change the output in the opposite direction). Hysteresis is defined as the difference of the two trip points and offset as the average of the two trip points.

Note 7: Guaranteed by CMRR test.

**Note 8:** Propagation delays are measured with a step size of 150mV.

**Note 9:** Propagation delay skew is defined as the difference of the propagation delays for positive and negative steps for the LTC6752, LTC6752-1, LTC6752-2 and LTC6752-4, and the difference in propagation delays between the complementary outputs for the LTC6752-3.

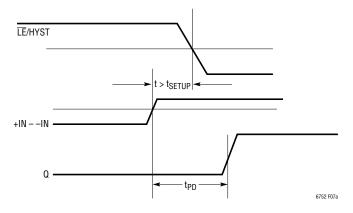

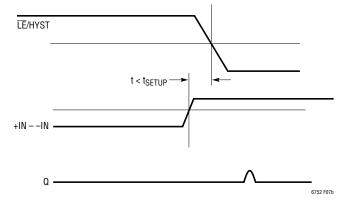

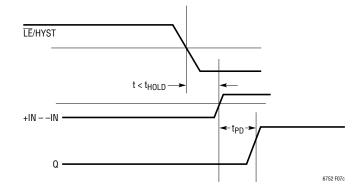

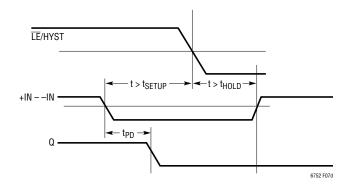

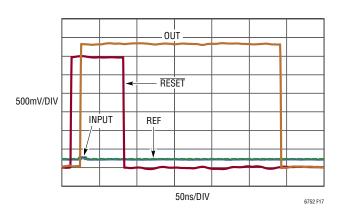

**Note 10:** Latch setup time is defined as the minimum time before the  $\overline{\text{LE}}/\text{HYST}$  pin is asserted low for an input signal change to be acquired and held at the output. Latch hold time is defined as the minimum time before an input signal change for a high to low transition on the  $\overline{\text{LE}}/\text{HYST}$  pin to prevent the output from changing. See Figure 7 for a graphical definition of these terms.

**Note 11:** Toggling is defined to be valid if the output swings as follows: from 10% of  $V_{DD}$  -  $V_{EE}$  to 90% of  $V_{DD}$  -  $V_{EE}$  for the LTC6752-2/LTC6752-4, and from 10% of  $V_{CC}$  -  $V_{EE}$  to 90% of  $V_{CC}$  -  $V_{EE}$  for the LTC6752/LTC6752-1. It is tested with a  $1k\Omega$  load to  $V_{CM}$

Note 12: The devices have effectively infinite gain when hysteresis is enabled.

#

LTC6752-4.

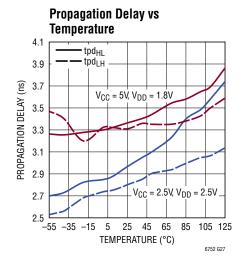

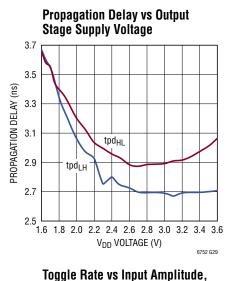

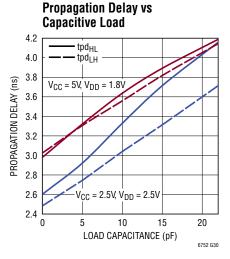

TYPICAL PERFORMANCE CHARACTERISTICS DC  $v_{CC} = v_{DD} = 2.5 \text{V}, C_{LOAD} = 5 \text{pF}, V_{OVERDRIVE} = 50 \text{mV}, V_{CM} = 300 \text{mV}, T_A = 25^{\circ}\text{C}$  unless otherwise noted.  $v_{CC} \neq v_{DD}$  conditions applicable only to the LTC6752-2/ LTC6752-3/ LTC6752-4.

**Output High/Low Voltage vs Temperature**

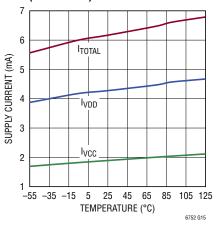

**Supply Current vs Temperature** (LTC6752/LTC6752-1/LTC6752-2/ LTC6752-4)

**Supply Current vs Temperature** (LTC6752-3)

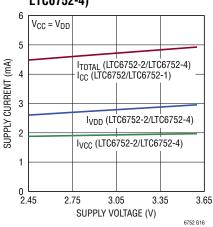

**Supply Current vs Supply Voltage** (LTC6752/LTC6752-1/LTC6752-2/ LTC6752-4)

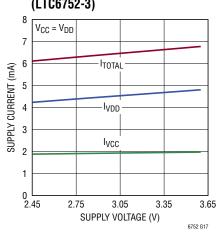

**Supply Current vs Supply Voltage** (LTC6752-3)

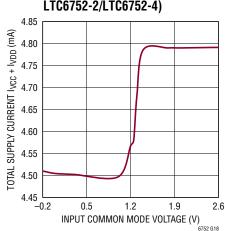

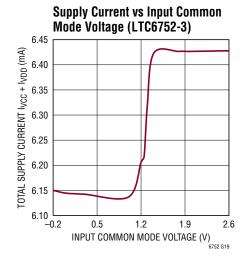

**Supply Current vs Input Common** Mode Voltage (LTC6752/LTC6752-1/ LTC6752-2/LTC6752-4)

# TYPICAL PERFORMANCE CHARACTERISTICS DC $V_{CC} = V_{DD} = 2.5V$ , $C_{LOAD} = 5pF$ , $V_{OVERDRIVE} = 50mV$ , $V_{CM} = 300mV$ , $V_{A} = 25^{\circ}C$ unless otherwise noted. $V_{CC} \neq V_{DD}$ conditions applicable only to the LTC6752-2/LTC6752-3/LTC6752-4.

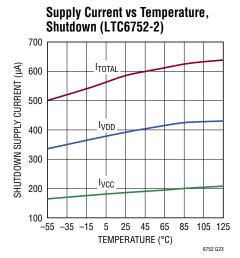

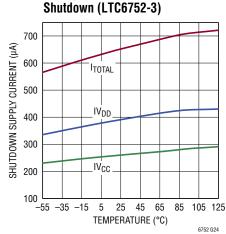

Supply Current vs Temperature,

$\begin{array}{ll} \textbf{TYPICAL PERFORMANCE CHARACTERISTICS AC} & \nu_{CC} = \nu_{DD} = 2.5 \text{V}, \ C_{LOAD} = 5 \text{pF}, \\ \nu_{OVERDRIVE} = 50 \text{mV}, \ \nu_{CM} = 300 \text{mV}, \ T_A = 25 ^{\circ}\text{C}, \ transient input voltage 10MHz}, \ 150 \text{mV}_{P-P} \ square wave unless otherwise noted}. \\ \nu_{CC} \neq \nu_{DD} \ conditions \ applicable \ only \ to \ the \ LTC6752-2/LTC6752-3/LTC6752-4}. \end{array}$

# TYPICAL PERFORMANCE CHARACTERISTICS AC $v_{CC} = v_{DD} = 2.5v$ , $c_{LOAD} = 5pF$ , $v_{OVERDRIVE} = 50mV$ , $v_{CM} = 300mV$ , $v_{A} = 25^{\circ}C$ , transient input voltage 10MHz, 150mV<sub>P-P</sub> square wave unless otherwise noted.

$V_{CC} \neq V_{DD}$  conditions applicable only to the LTC6752-2/LTC6752-3/LTC6752-4.

## Toggle Rate vs Temperature, (LTC6752/LTC6752-1/LTC6752-2/LTC6752-4)

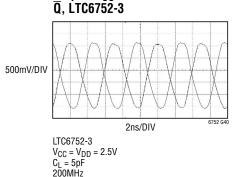

Toggle Rate vs Temperature, LTC6752-3

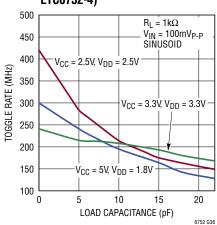

Toggle Rate vs Capacitive Load, (LTC6752/LTC6752-1/LTC6752-2/ LTC6752-4)

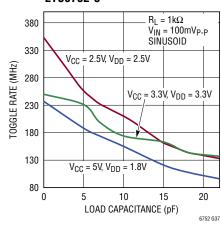

Toggle Rate vs Capacitive Load, LTC6752-3

**Output Jitter vs Input Amplitude**

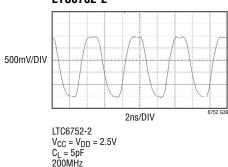

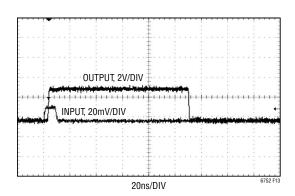

## Output Toggle Waveform, LTC6752-2

### Output Toggle Waveforms Q and O ITC6752-3

#### PIN FUNCTIONS

**+IN:** Positive Input of the Comparator. The voltage range of this pin can go from V<sub>EE</sub> to V<sub>CC</sub>.

**–IN:** Negative Input of the Comparator. The voltage range of this pin can go from  $V_{FF}$  to  $V_{CC}$ .

**V<sub>CC</sub>:** Positive Supply Voltage for the LTC6752/LTC6752-1, Positive Supply Voltage for the Input Stage of the LTC6752-2/LTC6752-3/LTC6752-4.

**V<sub>DD</sub>**: Positive Supply Voltage for the Output Stage of the LTC6752-2/LTC6752-3/LTC6752-4. Typically the voltage is from 1.71V to 3.5V. See the section High Speed Board Design Techniques for proper power supply layout and bypassing.

$V_{EE}$ : Negative power supply, normally tied to ground. This can be tied to a voltage other than ground as long as the constraints for total supply voltage relative to  $V_{CC}$  (and  $V_{DD}$  for separate supply operation) are maintained.

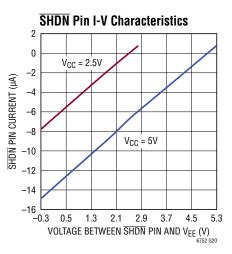

**SHDN**: Active low comparator shutdown, threshold is 0.6V above V<sub>EE</sub>. The comparator is enabled when this pin is left unconnected.

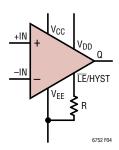

$\overline{\text{LE}}/\text{HYST}$ : This pin allows the user to adjust the comparator's hysteresis as well as latch the output state if the pin voltage is taken within 300mV above  $V_{EE}$ . Hysteresis can be increased or disabled by voltage, current or a resistor to  $V_{EE}$ . Leaving the pin unconnected results in a typical hysteresis of 5mV.

**Q**: Comparator Output. Q is driven high when +IN > -IN and driven low when +IN < -IN.

**Q**: Comparator Complementary Output (Available on LTC6752-3 Only). Logical inversion of Q.

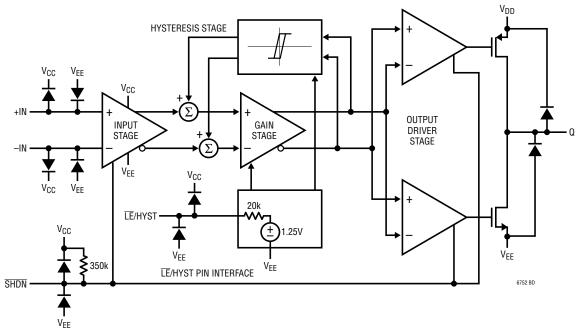

### **BLOCK DIAGRAM**

Figure 1. LTC6752/LTC6752-1/LTC6752-2/LTC6752-4 Block Diagram

#### **Circuit Description**

The block diagram is shown in Figure 1. There are differential inputs (+IN, -IN), a negative power supply ( $V_{EE}$ ), two positive supply pins:  $V_{CC}$  for the input stage and  $V_{DD}$  for the output stage, an output pin (Q), a pin for latching and adjusting hysteresis ( $\overline{LE}$ /HYST), and a pin to put the device in a low power mode ( $\overline{S}$ HDN). In the LTC6752 and LTC6752-1, the two positive supply pins are bonded together and referred to as  $V_{CC}$ . The signal path consists of a rail-to-rail input stage, an intermediate gain stage, and an output stage driving a pair of complementary FETs capable of taking the output pin to either supply rail. A Latching/Hysteresis interface block allows the user to latch the output state and/or remove or adjust the comparator input hysteresis. All of the internal signal paths make use of low voltage swings for high speed at low power.

The LTC6752-3 has an additional inverted output stage (not shown) for a complementary logic output signal.

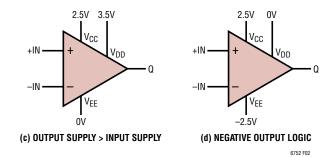

#### **Power Supply Configurations**

The LTC6752-2/LTC6752-3/LTC6752-4 have separate positive supply pins for the input and output stages that allow for separate voltage ranges for the analog input, and the output logic. Figure 2 shows a few possible configurations. For reliable and proper operation, the input supply pin should be between 2.45V and 5.25V above the negative supply pin, and the output supply pin should be between 1.71V and 3.5V above the negative supply pin. There are no restrictions regarding the sequence in which the supplies are applied, as long as the absolute-maximum ratings are not violated.

The LTC6752 and LTC6752-1 have only one positive supply pin. The supply voltage should be between 2.45V and 3.5V for proper and reliable operation.

#

#### **Input Voltage Range and Offset**

The LTC6752 family uses a rail-to-rail input stage that consists of a pnp pair and an npn pair that are active over different input common mode ranges. The pnp pair is active for inputs between  $V_{EE} - 0.2V$  and approximately  $V_{CC}$ - 1.5V (low common mode region of operation). The npn pair is active for inputs between approximately  $V_{CC} - 1V$ and  $V_{CC}$  + 0.1V (high common mode region of operation). Partial activation of both pairs occurs when one input is in the low common mode region of operation and the other input is in the high common mode region of operation, or either of the inputs is between approximately  $V_{CC} - 1.5V$ and  $V_{CC} - 1V$  (transition region). The device has small, trimmed offsets as long as both inputs are completely in the low or high common mode region of operation. In the transition region, the offset voltage may increase. Applications that require good DC precision should avoid the transition region.

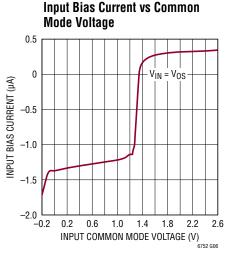

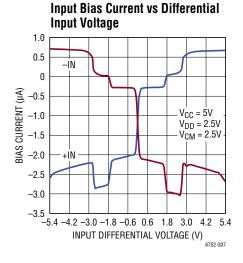

#### **Input Bias Current**

When both inputs are in the low common mode region, the input bias current is negative, with current flowing out of the input pins. When both inputs are in the high common mode region, the input bias current is positive, with current flowing into the input pins.

The input stage has been designed to accommodate large differential input voltages without large increases in input bias current. With one input at the positive input supply rail and the other input at the negative supply rail, the magnitude of the input bias currents at either pin is typically less than  $3.5\mu A$ .

Figure 2. Typical Power Supply Configurations (Applicable to the LTC6752-2/LTC6752-3/LTC6752-4)

#### **Input Protection**

The input stage is protected against damage from conditions where the voltage on either pin exceeds the supply voltage ( $V_{CC}$  to  $V_{EE}$ ) without external protection. External input protection circuitry is only needed if input currents can exceed the absolute maximum rating. For example, if an input is taken beyond 300mV of either the positive or negative supply, an internal ESD protection diode will conduct and an external resistor should be used to limit the current to less than 10mA.

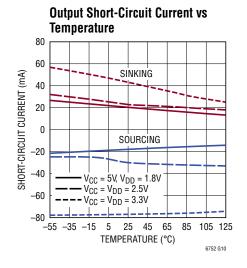

#### Outputs

The LTC6752 family has excellent drive capability. The comparators can deliver typically ±22mA output current for an output supply of 2.5V, and ±39mA output current for a 3.3V output supply. Attention must be paid to keep the junction temperature of the IC below 150°C should the output have a continuous short-circuit condition.

#### **Logic Drive Capability**

The LTC6752 family has been designed to drive CMOS logic with a supply of 3.3V, 2.5V and 1.8V. For device reliability, the output power supply ( $V_{DD}$ ) should not be higher than 3.6V above the negative supply. When  $V_{DD}$  is 3V or higher the CMOS outputs of the LTC6752 family provide valid TTL logic threshold levels and can easily interface with TTL logic devices operating with a 5V supply. This is possible because all of the threshold levels associated with TTL logic ( $V_{IH}/V_{IL}/V_{OH}/V_{OL}$ ) are less than or equal to 2.4V

#### **Capacitive Loads**

The LTC6752 family can drive capacitive loads. Transient performance parameters in the Electrical Characteristics Tables and Typical Characteristics section are for a load of 5pF, corresponding to a standard TTL/CMOS load. The devices are fully functional for larger capacitive loads, however speed performance will degrade. The graphs titled Propagation Delay vs Capacitive Load and Toggle Rate vs Capacitive Load illustrate the impact of changes to the total capacitive load. For optimal speed performance, output load capacitance should be reduced as much as possible.

#### **ESD**

The LTC6752 family members have reverse-biased ESD protection diodes on pins as shown in Figure 1.

There are additional clamps between the positive and negative supplies that further protect the device during ESD strikes. Hot-plugging of the device into a powered socket is not recommended since this can trigger the clamp resulting in large currents flowing between the supply pins.

#### **Hysteresis**

Comparators have very high open-loop gain. With slow input signals that are close to each other, input noise can cause the output voltage to switch randomly. This can be addressed by hysteresis which is positive feedback that increases the trip point in the direction of the input signal transition when the output switches. This pulls the inputs away from each other, and prevents continuous switching back and forth. The addition of positive feedback also has the effect of making the small signal gain infinite around the trip points. Hysteresis is designed into most comparators and the LTC6752 family has adjustable hysteresis with a default hysteresis of 5mV.

The input-output transfer characteristic is illustrated in Figure 3 showing the definitions of  $V_{OS}$  and HYST based upon the two measurable trip points.

In some cases, additional noise immunity is required above what is provided by the nominal 5mV hysteresis.

Figure 3

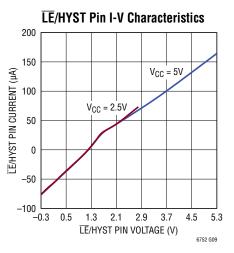

Conversely, when processing small or fast differential signals, hysteresis may need to be eliminated. The LTC6752-1/LTC6752-2/LTC6752-3 provide a hysteresis pin,  $\overline{\text{LE}}/\text{HYST}$ , that can be used to increase the internal hysteresis, completely remove it, or enable the output to latch. For these 3 options of the LTC6752, the internal hysteresis is disabled when the  $\overline{\text{LE}}/\text{HYST}$  pin voltage is above 1.7V. Although eliminating hysteresis does reduce the voltage gain of the comparator to a finite value, in many cases it will be high enough (typically 6000V/V) to process small input signals. The output will latch when the  $\overline{\text{LE}}/\text{HYST}$  pin voltage is below 0.3V. The internal hysteresis will increase as the voltage of the pin is adjusted from its default open circuit value of 1.25V to 800mV.

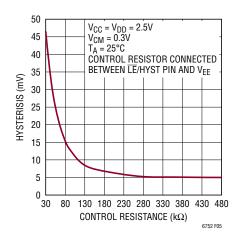

The  $\overline{\text{LE}}/\text{HYST}$  pin can be modeled as a 1.25V voltage source in series with a 20k resistor. The simplest method to increase the internal hysteresis is to connect a single resistor as shown in Figure 4 between the  $\overline{\text{LE}}/\text{HYST}$  pin and  $V_{\text{EE}}$  to adjust hysteresis. Figure 5 shows how hysteresis typically varies with the value of the resistor.

Figure 4. Adjusting Hysteresis Using an External Resistor at the  $\overline{\text{LE}}/\text{HYST}$  Pin

Figure 5. Hysteresis vs Control Resistor

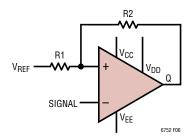

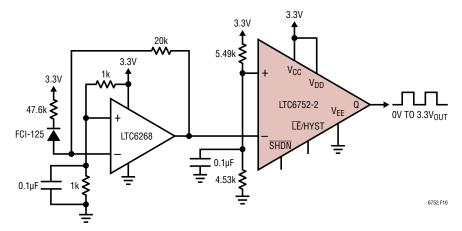

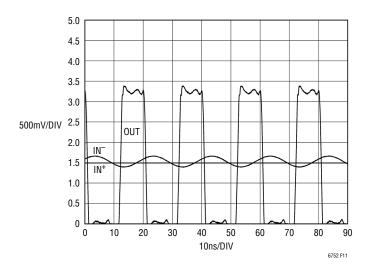

In addition to adjusting hysteresis using the  $\overline{\text{LE}}/\text{HYST}$  pin, additional hysteresis can be added using positive feedback from the output back to the positive input, as shown in Figure 6.

Figure 6. Additional Hysteresis Using Positive Feedback

The offset (with respect to the input signal) and hysteresis become

$$V_{OS\_FB} = \frac{(V_{DD} + V_{EE})}{2} \frac{R1}{R1 + R2} + V_{REF} \frac{R2}{R1 + R2} - V_{OS}$$

$$-\frac{V_{OH}}{2} \frac{R1}{R1 + R2} + V_{OL} \frac{R2}{R1 + R2} \longrightarrow (1)$$

$$V_{HYST\_FB} = (V_{DD} - V_{EE}) \frac{R1}{R1 + R2} + V_{OL} \frac{R2}{R1 + R2} + V_{OL} \frac{R1}{R1 + R2} +$$

$V_{OS\_FB}$  and  $V_{HYST\_FB}$  denote the values of offset and hysteresis with positive feedback present.  $V_{HYST}$  denotes the hysteresis of the device without positive feedback. For light loads,  $V_{OH}$  (output swing high) and  $V_{OL}$  (output swing low) are typically a few mV (typically are less than 10mV for a 500 $\mu A$  load).

On a 3.0V total supply with  $V_{EE}=0V$ , an increase in hysteresis of approximately 300mV can be obtained with  $V_{REF}=1.25V$ ,  $R2=4.53k\Omega$ ,  $R1=511\Omega$ , with an induced offset of approximately 1.275V.

#### Latching

The internal latch of the LTC6752-1/LTC6752-2/LTC6752-3 retains the output state when the  $\overline{\text{LE}}/\text{HYST}$  pin is taken to less than 300mV above the negative supply.

Figures 7a to 7e illustrate the latch timing definitions. The latch setup time is defined as the time for which the input should be stable before the latch pin is asserted low to ensure that the correct state will be held at the output. The latch hold time is the interval after which the latch pin is asserted in which the input signal must remain stable for the output to be the correct state at the time latch was asserted. The latch to output delay  $(t_{PL})$  is the time taken for the output to return to input control after the latch pin is released. Latching is disabled if the  $\overline{\text{LE}}/\text{HYST}$  pin is left floating. Both outputs of the LTC6752-3 are latch controlled simultaneously.

Figure 7a. Input State Change Properly Latched

Figure 7b. Input Change Setup Time Too Short

Figure 7c. Input State Not Held Long Enough. Wrong Output State Latched

Figure 7d. Short Input Pulse Properly Captured and Latched

Figure 7e. Latched Output Disabled

#### Shutdown

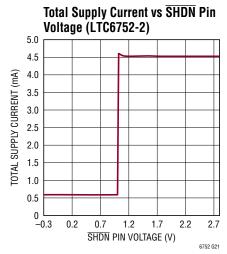

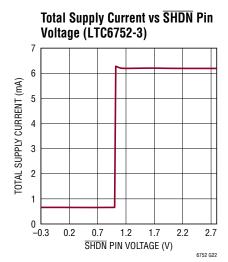

The LTC6752-2 and LTC6752-3 have shutdown pins  $(\overline{SHDN})$ , active low) that can reduce the total supply current to a typical value of  $580\mu A$  for the LTC6752-2 and  $650\mu A$  for the LTC6752-3 (2.5V supply). When the part is in shutdown, the outputs are placed in a high-impedance state, since PFET and NFET output transistors whose drains

are tied to the output pins are cut off and cannot source/ sink any current. The shutdown pin needs to be taken to within 600mV of the negative supply for the part to shut down. When left floating, the shutdown pin is internally pulled towards the positive supply, and the comparator remains fully biased on.

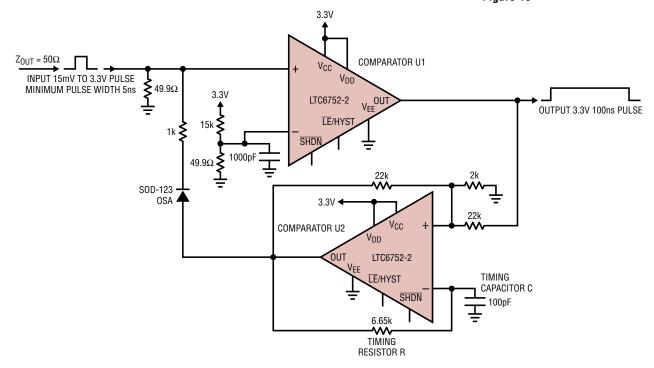

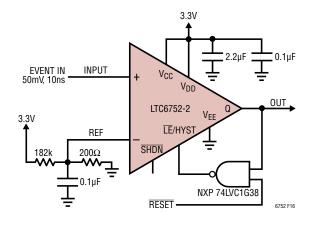

#### **Dispersion**