### LTC4269-2

### FEATURES

- 25.5W IEEE 802.3at Compliant (Type-2) PD

- PoE<sup>+</sup> 2-Event Classification

- IEEE 802.3at High Power Available Indicator

- Integrated State-of-the-Art Synchronous Forward Controller

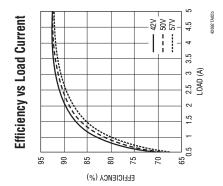

- Isolated Power Supply Efficiency >94%

- Flexible Auxiliary Power Interface

- Superior EMI Performance

- Robust 100V 0.7Ω (Typ) Integrated Hot Swap™ MOSFET

- Integrated Signature Resistor, Programmable Class Current, UVLO, OVLO and Thermal Protection

- Short-Circuit Protection with Auto-Restart

- Programmable Switching Frequency from 100kHz to 500kHz

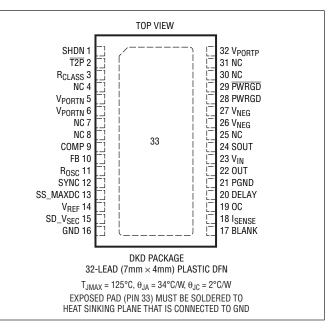

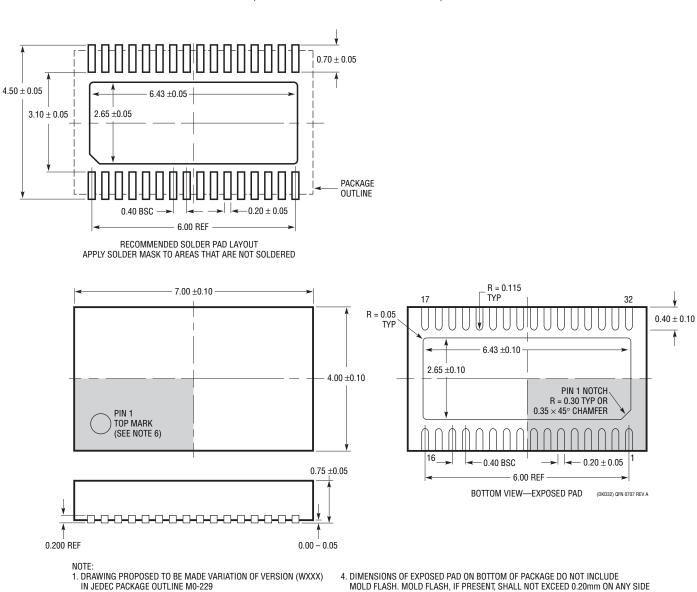

- Thermally Enhanced 7mm × 4mm DFN Package

### **APPLICATIONS**

- IP Phones with Large Color Screens

- Dual Radio 802.11n Access Points

- PTZ Security Cameras

### IEEE 802.3at High Power PD and Synchronous Forward Controller with AUX Support DESCRIPTION

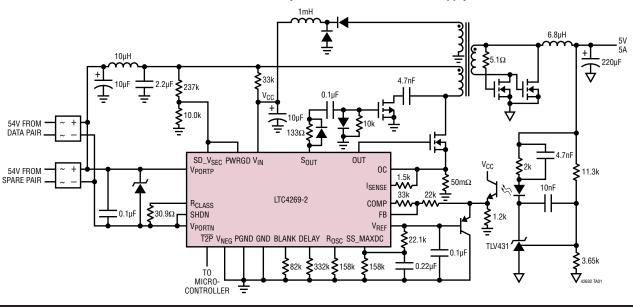

The LTC®4269-2 is an integrated Powered Device (PD) interface and power supply controller featuring 2-event classification signaling, flexible auxiliary power options, and a power supply controller suitable for synchronously rectified forward supplies. These features make the LTC4269-2 ideally suited for an IEEE802.3at PD application.

The PD controller features a 100V MOSFET that isolates the power supply during detection and classification, and provides 100mA inrush current limit. Also included are power good outputs, an undervoltage/overvoltage lockout and thermal protection. The current mode forward controller allows for synchronous rectification, resulting in an extremely high efficiency, green product. Soft-start for controlled output voltage start-up and fault recovery is included. Programmable frequency over 100kHz to 500kHz allows flexibility in efficiency vs size and low EMI.

∠7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and Hot Swap, ThinSOT are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

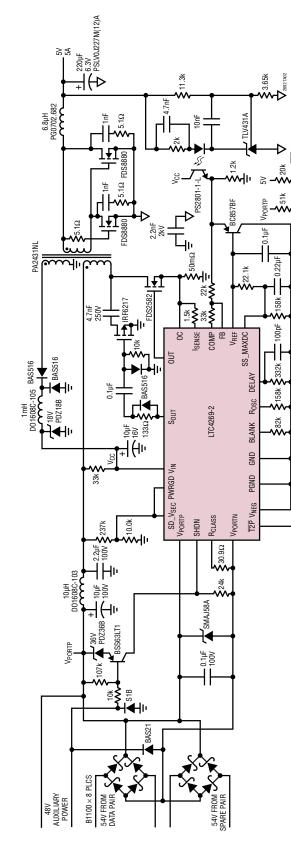

### TYPICAL APPLICATION

### ABSOLUTE MAXIMUM RATINGS

. .

#### (Notes 1, 2)

| Pins with Respect to V <sub>PORTN</sub>                  |

|----------------------------------------------------------|

| V <sub>PORTP</sub> Voltage –0.3V to 100V                 |

| V <sub>NEG</sub> Voltage0.3V to V <sub>PORTP</sub>       |

| V <sub>NEG</sub> Pull-Up Current                         |

| SHDN0.3V to 100V                                         |

| R <sub>CLASS</sub> , Voltage0.3V to 7V                   |

| R <sub>CLASS</sub> Source Current                        |

| PWRGD Voltage (Note 3)                                   |

| Low Impedance Source $V_{NEG} - 0.3V$ to $V_{NEG} + 11V$ |

| Sink Current5mA                                          |

| PWRGD, T2P Voltage –0.3V to 100V                         |

| PWRGD, T2P Sink Current10mA                              |

| Pins with Respect to GND                                 |

| $V_{IN}$ (Note 4)0.3V to 25V                             |

| SYNC, SS_MAXDC, SD_V <sub>SEC</sub> ,                    |

| I <sub>SENSE</sub> , OC–0.3V to 6V                       |

| COMP, BLANK, DELAY                                       |

| FB                                                       |

| R <sub>OSC</sub> Current50µA                             |

| V <sub>BFF</sub> Source Current10mA                      |

| Onevoting Ambient Temperature Dange                      |

#### Operating Ambient Temperature Range

| LTC4269C-2 | 0°C to  | 70°C |

|------------|---------|------|

| LTC4269I-2 | 40°C to | 85°C |

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION                    | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|----------------------------------------|-------------------|

| LTC4269CDKD-2#PBF | LTC4269CDKD-2#TRPBF | 42692         | 32-Lead (7mm $\times$ 4mm) Plastic DFN | 0°C to 70°C       |

| LTC4269IDKD-2#PBF | LTC4269IDKD-2#TRPBF | 42692         | 32-Lead (7mm $\times$ 4mm) Plastic DFN | -40°C to 85°C     |

| LEAD BASED FINISH | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION                    | TEMPERATURE RANGE |

| LTC4269CDKD-2     | LTC4269CDKD-2#TR    | 42692         | 32-Lead (7mm $\times$ 4mm) Plastic DFN | 0°C to 70°C       |

| LTC4269IDKD-2     | LTC4269IDKD-2#TR    | 42692         | 32-Lead (7mm $\times$ 4mm) Plastic DFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

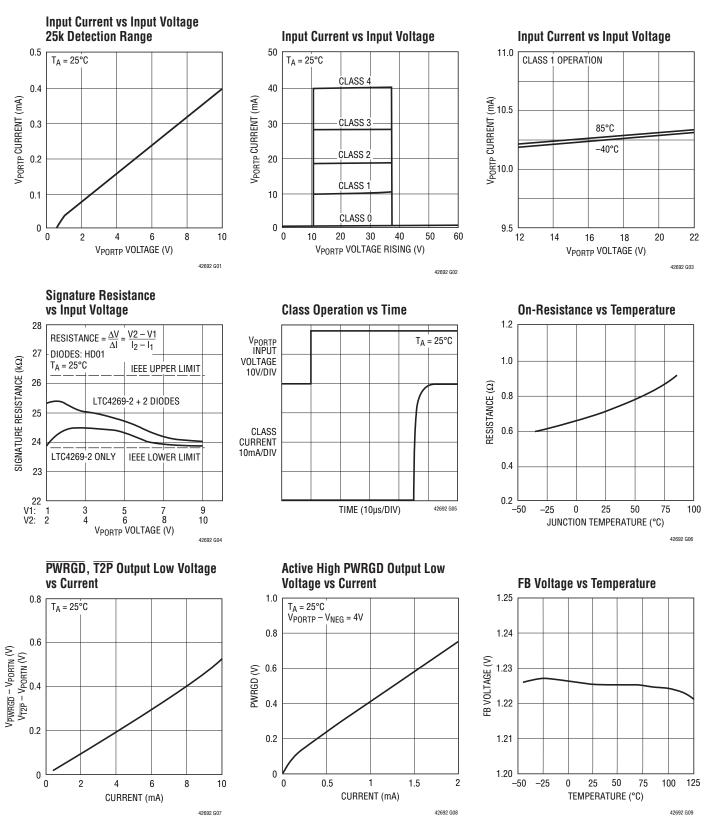

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C.

| PARAMETER                                                                                                                       | CONDITIONS                                                                                                        |   | MIN                  | ТҮР  | MAX                       | UNITS                      |

|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---|----------------------|------|---------------------------|----------------------------|

| Interface Controller (Note 5)                                                                                                   |                                                                                                                   |   |                      |      | 1                         |                            |

| Operating Input Voltage<br>Signature Range<br>Classification Range<br>On Voltage<br>Undervoltage Lockout<br>Overvoltage Lockout | At V <sub>PORTP</sub> (Note 6)                                                                                    | • | 1.5<br>12.5<br>30.0  | 71.0 | 60<br>9.8<br>21.0<br>37.2 | V<br>V<br>V<br>V<br>V<br>V |

| ON/UVLO Hysteresis Window                                                                                                       |                                                                                                                   | • | 4.1                  | -    |                           | V                          |

| Signature/Class Hysteresis Window                                                                                               |                                                                                                                   | • | 1.4                  |      |                           | V                          |

| Reset Threshold                                                                                                                 | State Machine Reset for 2-Event Classification                                                                    | • | 2.57                 |      | 5.40                      | V                          |

| Supply Current                                                                                                                  |                                                                                                                   |   |                      |      |                           |                            |

| Supply Current at 57V                                                                                                           | Measured at V <sub>PORTP</sub> Pin                                                                                |   |                      |      | 1.35                      | mA                         |

| Class O Current                                                                                                                 | V <sub>PORTP</sub> = 17.5V, No R <sub>CLASS</sub> Resistor                                                        | • |                      |      | 0.40                      | mA                         |

| Signature                                                                                                                       |                                                                                                                   |   | 1                    |      |                           |                            |

| Signature Resistance                                                                                                            | $1.5V \le V_{PORTP} \le 9.8V$ (Note 7)                                                                            |   | 23.25                |      | 26.00                     | kΩ                         |

| Invalid Signature Resistance, SHDN Invoked                                                                                      | $1.5V \le V_{PORTP} \le 9.8V$ , $V_{SHDN} = 3V$ (Note 7)                                                          | • |                      |      | 11                        | kΩ                         |

| Invalid Signature Resistance During Mark Event                                                                                  | (Notes 7, 8)                                                                                                      | • |                      |      | 11                        | kΩ                         |

| Classification                                                                                                                  |                                                                                                                   |   |                      |      | 1                         |                            |

| Class Accuracy                                                                                                                  | 10mA < I <sub>CLASS</sub> < 40mA, 12.5V < V <sub>PORTP</sub> < 21V<br>(Notes 9, 10)                               | • |                      |      | ±3.5                      | %                          |

| Classification Stability Time                                                                                                   | $V_{PORTP}$ Pin Step to 17.5V, $R_{CLASS} = 30.9\Omega$ ,<br>$I_{CLASS}$ within 3.5% of Ideal Value (Notes 9, 10) | • |                      |      | 1                         | ms                         |

| Normal Operation                                                                                                                | ·                                                                                                                 |   |                      |      |                           |                            |

| Inrush Current                                                                                                                  | V <sub>PORTP</sub> = 54V, V <sub>NEG</sub> = 3V                                                                   |   | 60                   | 100  | 180                       | mA                         |

| Power FET On-Resistance                                                                                                         | Tested at 600mA into V <sub>NEG</sub> , V <sub>PORTP</sub> = 54V                                                  | • |                      | 0.7  | 1.0                       | Ω                          |

| Power FET Leakage Current at V <sub>NEG</sub>                                                                                   | $V_{PORTP} = SHDN = V_{NEG} = 57V$                                                                                | • |                      |      | 1                         | μA                         |

| Digital Interface                                                                                                               | · ·                                                                                                               |   |                      |      |                           |                            |

| SHDN Input High Level Voltage                                                                                                   |                                                                                                                   |   | 3                    |      |                           | V                          |

| SHDN Input Low Level Voltage                                                                                                    |                                                                                                                   | • |                      |      | 0.45                      | V                          |

| SHDN Input Resistance                                                                                                           | V <sub>PORTP</sub> = 9.8V, SHDN = 9.65V                                                                           | • | 100                  |      |                           | kΩ                         |

| PWRGD, T2P Output Low Voltage                                                                                                   | Tested at 1mA, V <sub>PORTP</sub> = 57V, For T2P, Must<br>Complete 2-Event Classification to See Active Low       | • |                      |      | 0.15                      | V                          |

| PWRGD, T2P Leakage Current                                                                                                      | Pin Voltage Pulled 57V, V <sub>PORTP</sub> = V <sub>PORTN</sub> = 0V                                              | • |                      |      | 1                         | μA                         |

| PWRGDP Output Low Voltage                                                                                                       | Tested at 0.5mA, $V_{PORTP}$ = 52V, $V_{NEG}$ = 4V, Output Voltage is with Respect to $V_{NEG}$                   | • |                      |      | 0.4                       | V                          |

| PWRGDP Clamp Voltage                                                                                                            | Tested at 2mA, $V_{NEG}$ = 0V, Voltage is with Respect to $V_{NEG}$                                               | • | 12.0                 |      | 16.5                      | V                          |

| PWRGDP Leakage Current                                                                                                          | $V_{PWRGD}$ = 11V, $V_{NEG}$ = 0V, Voltage is with Respect to $V_{NEG}$                                           | • |                      |      | 1                         | μA                         |

| PWM Controller (Note 11)                                                                                                        |                                                                                                                   |   |                      |      |                           |                            |

| Operational Input Voltage                                                                                                       | I <sub>VREF</sub> = 0μA                                                                                           |   | V <sub>IN(OFF)</sub> |      | 25                        | V                          |

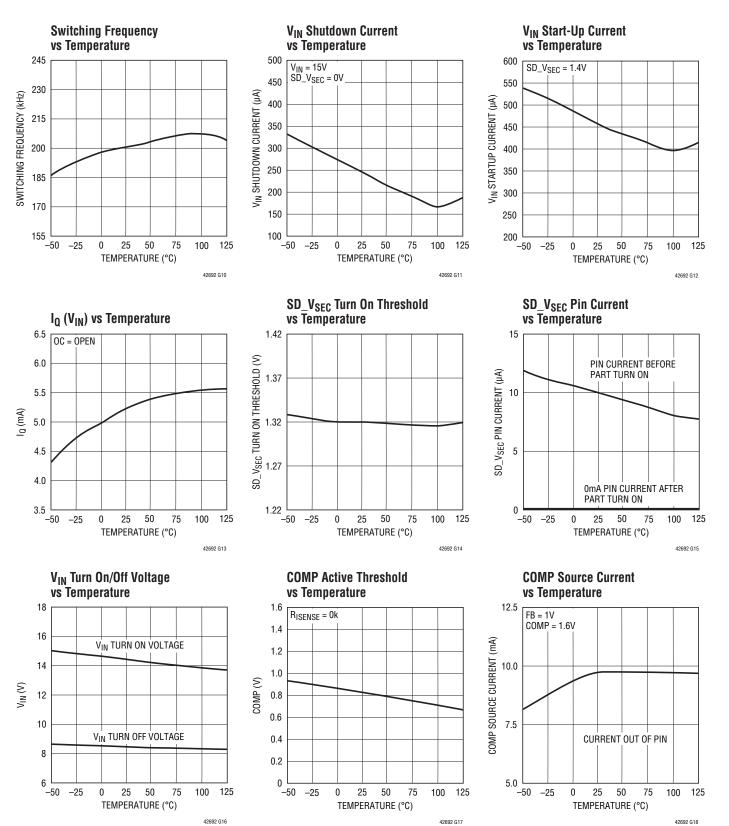

| V <sub>IN</sub> Quiescent Current                                                                                               | $I_{VREF} = 0\mu A$ , $I_{SENSE} = 0C = Open$                                                                     |   |                      | 5.2  | 6.5                       | mA                         |

| V <sub>IN</sub> Start-Up Current                                                                                                | FB = 0V, SS_MAXDC = 0V (Notes 12, 13)                                                                             | • |                      | 460  | 700                       | μA                         |

| V <sub>IN</sub> Shutdown Current                                                                                                | SD_V <sub>SEC</sub> = 0V (Notes 12, 13)                                                                           | • |                      | 240  | 350                       | μA                         |

| SD_V <sub>SEC</sub> Threshold                                                                                                   | 10V < SD < 25V                                                                                                    |   | 1.261                | 1.32 | 1.379                     | V                          |

|                                                                                                                                 | •                                                                                                                 |   |                      |      |                           | 42692fb                    |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| PARAMETER                                           | CONDITIONS                                                                         |     | MIN   | ТҮР   | MAX   | UNITS |

|-----------------------------------------------------|------------------------------------------------------------------------------------|-----|-------|-------|-------|-------|

| SD_V <sub>SEC(ON)</sub> Current                     | SD_V <sub>SEC</sub> = SD_V <sub>SEC</sub> Threshold +100mV                         |     |       | 0     |       | μA    |

| SD_V <sub>SEC(OFF)</sub> Current                    | SD_V <sub>SEC</sub> = SD_V <sub>SEC</sub> Threshold – 100mV                        |     | 8.3   | 10    | 11.7  | μA    |

| VIN(ON)                                             |                                                                                    |     |       | 14.25 | 15.75 | V     |

| VIN(OFF)                                            |                                                                                    |     |       | 8.75  | 9.25  | V     |

| VIN(HYST)                                           |                                                                                    |     | 3.75  | 5.5   | 7.0   | V     |

| V <sub>REF</sub>                                    |                                                                                    |     |       |       |       |       |

| Output Voltage                                      | I <sub>VREF</sub> = 0                                                              |     | 2.425 | 2.5   | 2.575 | V     |

| Line Regulation                                     | I <sub>VREF</sub> = 0, 10V < V <sub>IN</sub> < 25V                                 |     |       | 1     | 10    | mV    |

| Load Regulation                                     | 0mA < I <sub>VREF</sub> < 2.5mA                                                    |     |       | 1     | 10    | mV    |

| Oscillator                                          |                                                                                    |     |       |       |       |       |

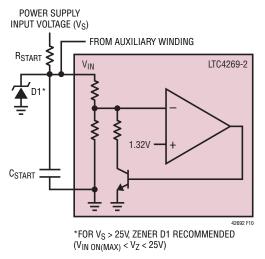

| Frequency, f <sub>OSC</sub>                         | R <sub>OSC</sub> = 178k, FB = 1V, SS_MAXDC = 1.84V                                 |     | 165   | 200   | 240   | kHz   |

| fosc(MIN)                                           | R <sub>OSC</sub> = 365k, FB = 1V                                                   |     | 80    | 100   | 120   | kHz   |

| fosc(MAX)                                           | R <sub>OSC</sub> = 64.9k, COMP = 2.5V, SD_V <sub>SEC</sub> = 2.64V                 |     | 440   | 500   | 560   | kHz   |

| SYNC Input Resistance                               |                                                                                    |     |       | 18    |       | kΩ    |

| SYNC Switching Threshold                            | FB = 1V                                                                            |     |       | 1.5   | 2.2   | V     |

| SYNC Frequency/f <sub>OSC</sub>                     | FB = 1V (Note 14)                                                                  |     |       | 1.25  | 1.5   |       |

| f <sub>OSC</sub> Line Regulation                    | R <sub>OSC</sub> = 178k; 10V < V <sub>IN</sub> < 25V, SS_MAXDC = 1.84V             |     |       | 0.05  | 0.33  | %/V   |

| V <sub>ROSC</sub>                                   | R <sub>OSC</sub> Pin Voltage                                                       |     |       | 1     |       | V     |

| Error Amplifier                                     |                                                                                    |     |       |       |       |       |

| FB Reference Voltage                                | 10V < V <sub>IN</sub> < 25V, V <sub>OL</sub> + 0.2V < COMP < V <sub>OH</sub> - 0.2 |     | 1.201 | 1.226 | 1.250 | V     |

| FB Input Bias Current                               | FB = FB Reference Voltage                                                          |     |       | -75   | -200  | nA    |

| Open-Loop Voltage Gain                              | V <sub>0L</sub> + 0.2V < COMP < V <sub>0H</sub> - 0.2                              |     | 65    | 85    |       | dB    |

| Unity-Gain Bandwidth                                | (Note 15)                                                                          |     |       | 3     |       | MHz   |

| COMP Source Current                                 | FB = 1V, COMP = 1.6V                                                               |     | -4    | -9    |       | mA    |

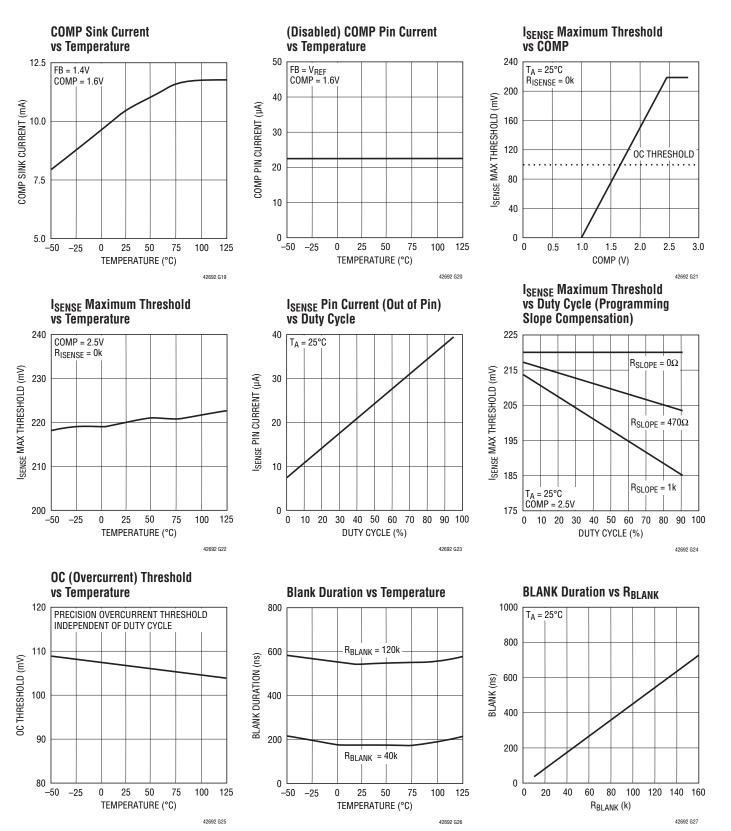

| COMP Sink Current                                   | COMP = 1.6V                                                                        |     | 4     | 10    |       | mA    |

| COMP Current (Disabled)                             | FB = V <sub>REF</sub> , COMP = 1.6V                                                |     | 18    | 23    | 28    | μA    |

| COMP High Level V <sub>OH</sub>                     | FB = 1V, I <sub>COMP</sub> = -250μA                                                |     | 2.7   | 3.2   |       | V     |

| COMP Active Threshold                               | FB = 1V, SOUT Duty Cycle > 0%                                                      |     | 0.7   | 0.8   |       | V     |

| COMP Low Level V <sub>OL</sub>                      | I <sub>COMP</sub> = 250μA                                                          |     |       | 0.15  | 0.4   | V     |

| Current Sense                                       |                                                                                    |     |       |       |       |       |

| I <sub>SENSE</sub> Maximum Threshold                | COMP = 2.5V, FB =1V                                                                |     | 197   | 220   | 243   | mV    |

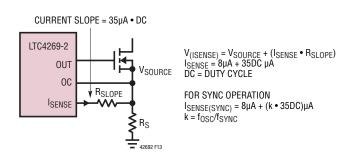

| I <sub>SENSE</sub> Input Current (Duty Cycle = 0%)  | COMP = 2.5V, FB = 1V (Note 12)                                                     |     |       | -8    |       | μA    |

| I <sub>SENSE</sub> Input Current (Duty Cycle = 80%) | COMP = 2.5V, FB = 1V (Note 12)                                                     |     |       | -35   |       | μA    |

| OC Threshold                                        | COMP = 2.5V, FB = 1V                                                               |     | 98    | 107   | 116   | mV    |

| OC Input Current                                    | (0C = 100mV)                                                                       |     |       | -50   | -100  | nA    |

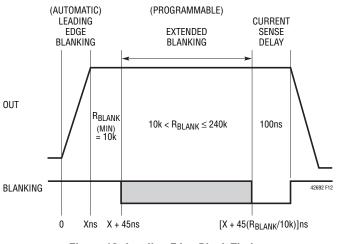

| Default Blanking Time                               | COMP = 2.5V, FB = 1V, R <sub>BLANK</sub> = 40k (Note 16)                           |     |       | 180   |       | ns    |

| Adjustable Blanking Time                            | COMP = 2.5V, FB = 1V, R <sub>BLANK</sub> = 120k                                    |     |       | 540   |       | ns    |

| V <sub>BLANK</sub>                                  |                                                                                    |     |       | 1     |       | V     |

| SOUT Driver                                         |                                                                                    | . 1 |       |       |       |       |

| SOUT Clamp Voltage                                  | I <sub>GATE</sub> = 0μA, COMP = 2.5V, FB = 1V                                      |     | 10.54 | 12    | 13.5  | V     |

| SOUT Low Level                                      | $I_{GATE} = 25 \text{mA}$                                                          |     |       | 0.5   | 0.75  | V     |

### **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_{e} = 25^{\circ}$ C

temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .

| PARAMETER                                                           | CONDITIONS                                                                                                                                                                                                                                                                                                                       | MIN         | ТҮР          | MAX         | UNITS    |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|-------------|----------|

| SOUT High Level                                                     | I <sub>GATE</sub> = -25mA, V <sub>IN</sub> = 12V COMP = 2.5V, FB = 1V                                                                                                                                                                                                                                                            | 10          |              |             | V        |

| SOUT Active Pull-Off in Shutdown                                    | V <sub>IN</sub> = 5V, SD_V <sub>SEC</sub> = 0V, SOUT = 1V                                                                                                                                                                                                                                                                        | 1           |              |             | mA       |

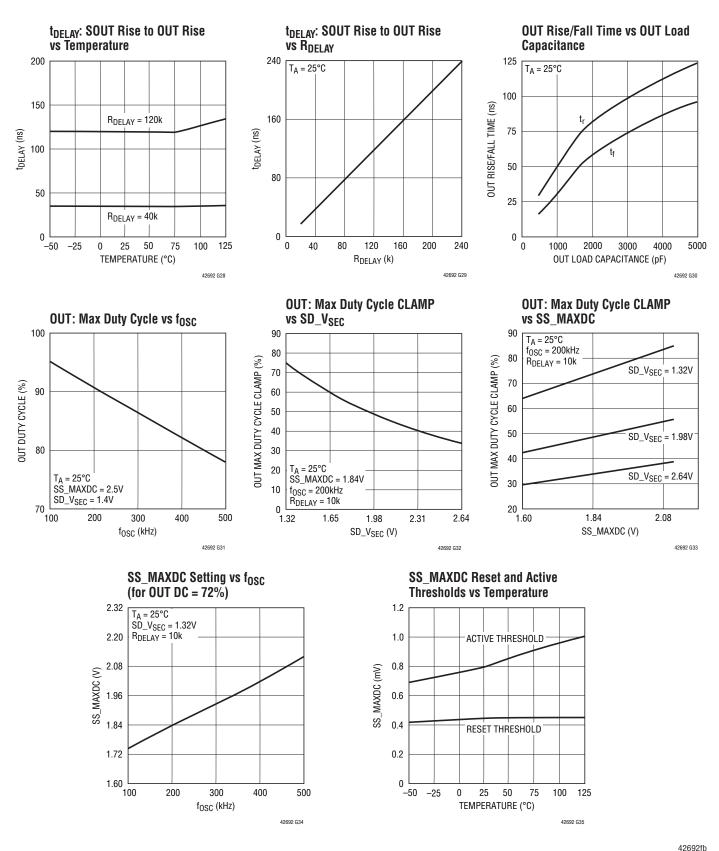

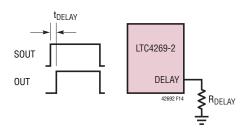

| SOUT to OUT (Rise) DELAY (t <sub>DELAY</sub> )                      | COMP = 2.5V, FB = 1V (Note 16)<br>R <sub>DELAY</sub> = 120k                                                                                                                                                                                                                                                                      |             | 40<br>120    |             | ns<br>ns |

| V <sub>DELAY</sub>                                                  |                                                                                                                                                                                                                                                                                                                                  |             | 0.9          |             | V        |

| OUT Driver                                                          |                                                                                                                                                                                                                                                                                                                                  |             |              |             |          |

| OUT Rise Time                                                       | FB = 1V, C <sub>L</sub> = 1nF (Notes 15, 16)                                                                                                                                                                                                                                                                                     |             | 50           |             | ns       |

| OUT Fall Time                                                       | FB = 1V, C <sub>L</sub> = 1nF (Notes 15, 16)                                                                                                                                                                                                                                                                                     |             | 30           |             | ns       |

| OUT Clamp Voltage                                                   | I <sub>GATE</sub> = 0μA, COMP = 2.5V, FB = 1V                                                                                                                                                                                                                                                                                    | 11.5        | 13           | 14.5        | V        |

| OUT Low Level                                                       | I <sub>GATE</sub> = 20mA<br>I <sub>GATE</sub> = 200mA                                                                                                                                                                                                                                                                            |             | 0.45<br>1.25 | 0.75<br>1.8 | V<br>V   |

| OUT High Level                                                      | I <sub>GATE</sub> = -20mA, V <sub>IN</sub> = 12V COMP = 2.5V, FB = 1V<br>I <sub>GATE</sub> = -200mA, V <sub>IN</sub> = 12V COMP = 2.5V, FB = 1V                                                                                                                                                                                  | 9.9<br>9.75 |              |             | V<br>V   |

| OUT Active Pull-Off in Shutdown                                     | V <sub>IN</sub> = 5V, SD_V <sub>SEC</sub> = 0V, OUT = 1V                                                                                                                                                                                                                                                                         | 20          |              |             | mA       |

| OUT Max Duty Cycle                                                  | $\begin{array}{l} \mbox{COMP} = 2.5 \mbox{V}, \mbox{FB} = 1 \mbox{V}, \mbox{R}_{DELAY} = 10 \mbox{k} \mbox{(} \mbox{f}_{OSC} = 200 \mbox{kHz}), \\ \mbox{V}_{IN} = 10 \mbox{V}, \mbox{SD}_V \mbox{Sec} = 1.4 \mbox{V}, \mbox{SS}_M \mbox{AXDC} = \mbox{V}_{REF} \end{array}$                                                     | 83          | 90           |             | %        |

| OUT Max Duty Cycle Clamp                                            | $\begin{array}{l} \mbox{COMP} = 2.5 \mbox{V}, \mbox{FB} = 1 \mbox{V}, \mbox{R}_{DELAY} = 10 \mbox{K} \mbox{(} f_{OSC} = 200 \mbox{KHz}), \\ \mbox{V}_{IN} = 10 \mbox{V} \\ \mbox{SD}_V_{SEC} = 1.32 \mbox{V}, \mbox{SS}_MAXDC = 1.84 \mbox{V} \\ \mbox{SD}_V_{SEC} = 2.64 \mbox{V}, \mbox{SS}_MAXDC = 1.84 \mbox{V} \end{array}$ | 63.5<br>25  | 72<br>33     | 80.5<br>41  | %        |

| Soft-Start                                                          |                                                                                                                                                                                                                                                                                                                                  |             |              |             |          |

| SS_MAXDC Low Level: V <sub>OL</sub>                                 | $I_{SS\_MAXDC} = 150\mu A, OC = 1V$                                                                                                                                                                                                                                                                                              |             | 0.2          |             | V        |

| SS_MAXDC Soft-Start Reset Threshold                                 | Measured on SS_MAXDC                                                                                                                                                                                                                                                                                                             |             | 0.45         |             | V        |

| SS_MAXDC Active Threshold                                           | FB + 1V, DC > 0%                                                                                                                                                                                                                                                                                                                 |             | 0.8          |             | V        |

| SS_MAXDC Input Current<br>(Soft-Start Pull-Down: I <sub>DIS</sub> ) | SS_MAXDC = 1V, SD_V <sub>SEC</sub> = 1.4V, OC = 1V                                                                                                                                                                                                                                                                               |             | 800          |             | μA       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Pins with 100V absolute maximum guaranteed for  $T \ge 0^{\circ}C$ , otherwise 90V.

Note 3: PWRGD voltage clamps at 14V with respect to V<sub>NEG</sub>.

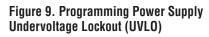

**Note 4:** In applications where the V<sub>IN</sub> pin is supplied via an external RC network from a system V<sub>IN</sub> > 25V, an external Zener with clamp voltage V<sub>IN ON(MAX)</sub> < V<sub>Z</sub> < 25V should be connected from the V<sub>IN</sub> pin to GND.

**Note 5:** All voltages are with respect to V<sub>PORTN</sub> pin unless otherwise noted. **Note 6:** Input voltage specifications are defined with respect to LTC4269-2 pins and meet IEEE 802.3af/at specifications when the input diode bridge is included.

**Note 7:** Signature resistance is measured via the  $\Delta V/\Delta I$  method with the minimum  $\Delta V$  of 1V. The LTC4269-2 signature resistance accounts for the additional series resistance in the input diode bridge.

**Note 8:** An invalid signature after the 1st classification event is mandated by IEEE 802.3at standard. See the Applications Information section.

**Note 9:** Class accuracy is respect to the ideal current defined as  $1.237/R_{CLASS}$  and does not include variations in  $R_{CLASS}$  resistance.

Note 10: This parameter is assured by design and wafer level testing.

**Note 11:** Voltages are with respect to GND unless otherwise specified. Tested with COMP open,  $V_{FB} = 1.4V$ ,  $R_{ROSC} = 178k$ ,  $V_{SYNC} = 0V$ ,  $V_{SS(MAXDC)}$  set to  $V_{REF}$  (but electrically isolated),  $C_{VREF} = 0.1\mu$ F,  $V_{SD\_VSEC} = 2V$ ,  $R_{BLANK} = 121k$ ,  $R_{DELAY} = 121k$ ,  $V_{ISENSE} = 0V$ ,  $V_{OC} = 0V$ ,  $C_{OUT} = 1n$ F,  $V_{IN} = 15V$ , SOUT open, unless otherwise specified.

Note 12: Guaranteed by correlation to static test.

**Note 13:**  $V_{IN}$  start-up current is measured at  $V_{IN} = V_{IN(ON)} - 0.25V$  and scaled by  $\times 1.18$  (to correlate to worst-case  $V_{IN}$  start-up current at  $V_{IN(ON)}$ . **Note 14:** Maximum recommended SYNC frequency = 500kHz.

Note 15: Guaranteed but not tested.

Note 16: Timing for R = 40k derived from measurement with R = 240k.

$\overline{}$

### PIN FUNCTIONS

**SHDN (Pin 1):** Shutdown Input. Use this pin for auxiliary power application. Drive SHDN high to disable LTC4269-2 operation and corrupt the signature resistance. If unused, tie SHDN to V<sub>PORTN</sub>.

**T2P** (Pin 2): Type-2 PSE Indicator, Open-Drain. Low impedance indicates the presence of a Type-2 PSE.

$R_{CLASS}$  (Pin 3): Class Select Input. Connect a resistor between  $R_{CLASS}$  and  $V_{PORTN}$  to set the classification load current.

**V**<sub>PORTN</sub> (**Pins 5, 6**): Power Input. Tie to the PD input through the diode bridge. Pins 5 and 6 must be electrically tied together at the package.

NC (Pins 4, 7, 8, 25, 30, 31): No Connect.

**COMP (Pin 9):** Output Pin of the Error Amplifier. The error amplifier is an op amp, allowing various compensation networks to be connected between the COMP pin and FB pin for optimum transient response in a nonisolated supply. The voltage on this pin corresponds to the peak current of the external FET. Full operating voltage range is between 0.8V and 2.5V corresponding to 0mV to 220mV at the I<sub>SENSE</sub> pin. For applications using the 100mV OC pin for overcurrent detection, typical operating range for the COMP pin is 0.8V to 1.6V. For isolated applications where COMP is controlled by an opto-coupler, the COMP pin output drive can be disabled with FB = V<sub>REF</sub>, reducing the COMP pin current to (COMP – 0.7)/40k.

**FB (Pin 10):** In a nonisolated supply, FB monitors the output voltage via an external resistor divider and is compared with an internal 1.23V reference by the error amplifier. FB connected to  $V_{REF}$  disables error amplifier output.

**R**<sub>OSC</sub> (**Pin11**): A resistor to GND programs the operating frequency of the IC between 100kHz and 500kHz. Nominal voltage on the R<sub>OSC</sub> pin is 1.0V.

**SYNC (Pin 12):** Used to synchronize the internal oscillator to an external signal. It is directly logic compatible and can be driven with any signal between 10% and 90% duty cycle. If unused, the pin should be connected to GND.

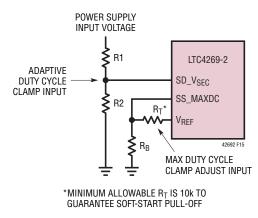

**SS\_MAXDC (Pin 13):** The external resistor divider from  $V_{REF}$  sets the maximum duty cycle clamp (SS\_MAXDC = 1.84V, SD\_V\_{SEC} = 1.32V gives 72% duty cycle). Capacitor on SS\_MAXDC pin in combination with external resistor divider sets soft-start timing.

$V_{REF}$  (Pin 14): The output of an internal 2.5V reference which supplies internal control circuitry. Capable of sourcing up to 2.5mA drive for external use. Bypass to GND with a 0.1µF ceramic capacitor.

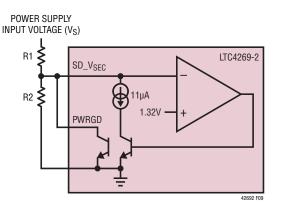

**SD\_V\_{SEC}** (Pin 15): The SD\_V\_{SEC} pin, when pulled below its accurate 1.32V threshold, is used to turn off the IC and reduce current drain from V<sub>IN</sub>. The SD\_V\_SEC pin is connected to system input voltage through a resistor divider to define undervoltage lockout (UVLO) for the power supply and to provide a volt-second clamp on the OUT pin. An 11µA pin current hysteresis allows external programming of UVLO hysteresis.

GND (Pin 16): Analog Ground. Tie to V<sub>NEG</sub>.

**BLANK (Pin 17):** A resistor to GND adjusts the extended blanking period of the overcurrent and current sense amplifier outputs during FET turn-on—to prevent false current limit trip. Increasing the resistor value increases the blanking period.

$I_{SENSE}$  (Pin 18): The Current Sense Input for the Control Loop. Connect this pin to the sense resistor in the source of the external power MOSFET. A resistor in series with the  $I_{SENSE}$  pin programs slope compensation.

### PIN FUNCTIONS

**OC (Pin 19):** OC is an accurate 107mV threshold, independent of duty cycle, for overcurrent detection and trigger of soft-start. Connect this pin directly to the sense resistor in the source of the external power MOSFET.

**DELAY (Pin 20):** A resistor to GND adjusts the delay period between SOUT rising edge and OUT rising edge. Used to maximize efficiency in forward converter applications by adjusting the timing. Increasing the resistor value increases the delay period.

**PGND (Pin 21):** Power Ground. Carries the gate driver's return current. Tie to  $V_{NEG}$ .

**OUT (Pin 22):** Drives the gate of an N-channel MOSFET between OV and  $V_{IN}$  with a maximum limit of 13V on OUT pin set by an internal clamp. Active pull-off exists in shutdown (see electrical specification).

$V_{IN}$  (Pin 23): Input Supply for the Power Supply Controller. It must be closely decoupled to GND. An internal undervoltage lockout threshold exists for  $V_{IN}$  at approximately 14.25V on and 8.75V off.

**SOUT (Pin 24):** Switched Output in Phase with OUT Pin. Provides sync signal for control of secondary-side FETs in forward converter applications requiring highly efficient synchronous rectification. SOUT is actively clamped to 12V. Active pull-off exists in shutdown (see electrical specification). Can also be used to drive the active clamp FET of an active clamp forward supply. **V<sub>NEG</sub> (Pins 26, 27):** Power Output. Connects the PoE return line to the power supply through the internal Hot Swap power MOSFET. Pins 26 and 27 must be electrically tied together at the package.

**PWRGD (Pin 28):** Active High Power Good Output, Open Collector. Signals that the internal Hot Swap MOSFET is on. High Impedance indicates power is good. PWRGD is referenced to  $V_{NEG}$  and is low impedance during inrush and in the event of thermal overload. PWRGD is clamped 14V above  $V_{NEG}$ .

**PWRGD** (Pin 29): Active Low Power Good Output, Open Drain. Signals that the internal Hot Swap MOSFET is on. Low Impedance indicates power is good. **PWRGD** is referenced to  $V_{PORTN}$  and is high impedance during inrush and in the event of thermal overload. **PWRGD** has no internal clamps.

**V**<sub>PORTP</sub> (**Pin 32**): Input Voltage Positive Rail. This pin is connected to the PD's positive rail.

Exposed Pad (Pin 33): Tie to GND and PCB heat sink.

42692ft

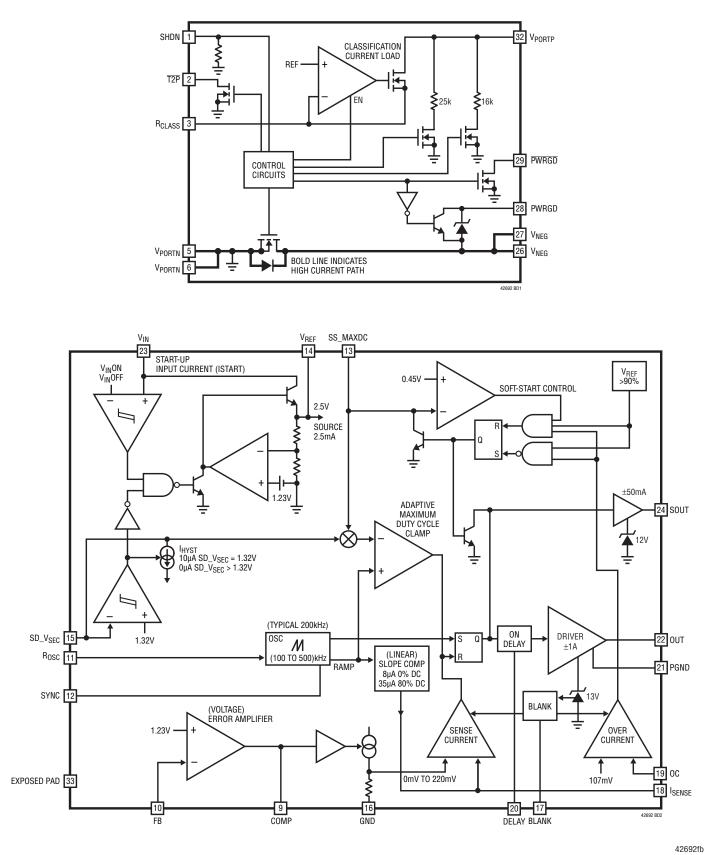

### **BLOCK DIAGRAMS**

12

#### **OVERVIEW**

Power over Ethernet (PoE) continues to gain popularity as more products are taking advantage of having DC power and high speed data available from a single RJ45 connector. As PoE continues to grow in the marketplace, Powered Device (PD) equipment vendors are running into the 12.95W power limit established by the IEEE 802.3af standard.

The IEE802.3at standard establishes a higher power allocation for Power over Ethernet while maintaining backwards compatibility with the existing IEEE 802.3af systems. Power Sourcing Equipment (PSE) and Powered Devices are distinguished as Type 1 complying with the IEEE 802.3af power levels, or Type 2 complying with the IEEE 802.3at power levels. The maximum available power of a Type 2 PD is 25.5W.

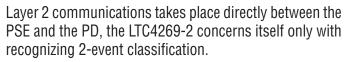

The IEEE 802.3at standard also establishes a new method of acquiring power classification from a PD and communicating the presence of a Type 2 PSE. A Type 2 PSE has the option of acquiring PD power classification by performing 2-event classification (Layer 1) or by communicating with the PD over the data line (Layer 2). In turn, a Type 2 PD must be able to recognize both layers of communications and identify a Type 2 PSE.

The LTC4269-2 is specifically designed to support a PD that must operate under the IEEE 802.3at standard. In particular, the LTC4269-2 provides the T2P indicator bit which recognizes 2-event classification. This indicator bit may be used to alert the LTC4269-2 output load that a Type 2 PSE is present. With an internal signature resistor, classification circuitry, inrush control, and thermal shutdown, the LTC4269-2 is a complete PD interface solution capable of supporting in the next generation PD applications. In addition to the PD front end, the LTC4269-2 also incorporates a high efficiency synchronous forward controller that minimizes component sizes while maximizing output power.

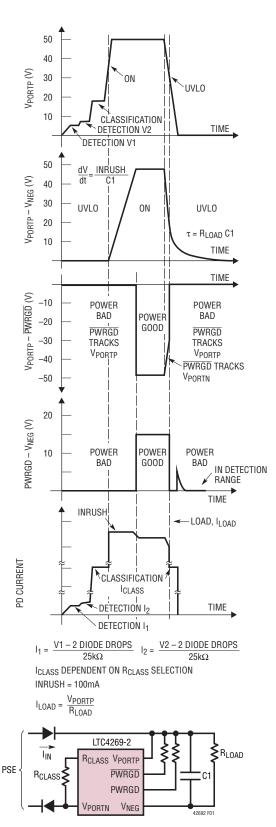

#### **MODES OF OPERATION**

The LTC4269-2 has several modes of operation depending on the input voltage applied between the  $V_{PORTP}$  and  $V_{PORTN}$  pins. Figure 1 presents an illustration of voltage

Figure 1. Output Voltage, PWRGD, PWRGD and PD Current as a Function of Input Voltage

and current waveforms the LTC4269-2 may encounter with the various modes of operation summarized in Table 1.

## Table 1. LTC4269-2 Modes of Operation as a Function of Input Voltage

| V <sub>PORTP</sub> – V <sub>PORTN</sub> (V) | LTC4269-2 MODES OF OPERATION                                                                                                           |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0V to 1.4V                                  | Inactive (Reset after 1st Classification Event)                                                                                        |

| 1.5V to 9.8V<br>(5.4V to 9.8V)              | 25k Signature Resistor Detection Before 1st<br>Classification Event<br>(Mark, 11k Signature Corrupt After 1st<br>Classification Event) |

| 12.5V to On/UVLO                            | Classification Load Current Active                                                                                                     |

| On/UVLO to 60V                              | Inrush and Power Applied to PD Load                                                                                                    |

| >71V                                        | Overvoltage Lockout, Classification and Hot Swap are Disabled.                                                                         |

On/UVLO includes hysteresis. Rising input threshold: 37.2V max. Falling input threshold: 30.0V min.

These modes satisfy the requirements defined in the IEEE 802.3af/at specification.

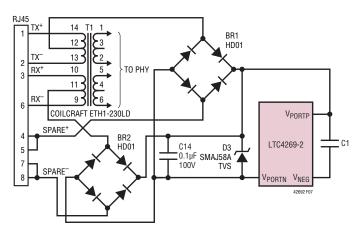

#### **INPUT DIODE BRIDGE**

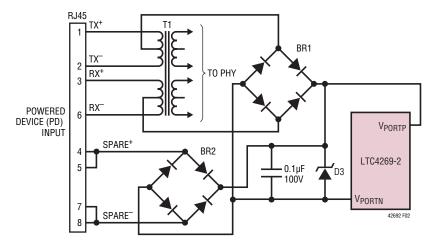

In the IEEE 802.3af/at standard, the modes of operation reference the input voltage at the PD's RJ45 connector. Since the PD must handle power received in either polarity from either the data or the spare pair, input diode bridges BR1 and BR2 are connected between the RJ45 connector and the LTC4269-2 (Figure 2).

The input diode bridge introduces a voltage drop that affects the range for each mode of operation. The LTC4269-2 compensates for these voltage drops so that a PD built with the LTC4269-2 meets the IEEE 802.3af/at-established voltage ranges. Note that the Electrical Specifications are referenced with respect to the LTC4269-2 package pins.

#### DETECTION

During detection, the PSE looks for a 25k signature resistor which identifies the device as a PD. The PSE will apply two voltages in the range of 2.8V to 10V and measures the corresponding currents. Figure 1 shows the detection voltages V1 and V2 and the corresponding PD current. The PSE calculates the signature resistance using the  $\Delta V/\Delta I$  measurement technique.

The LTC4269-2 presents its precision, temperature-compensated 25k resistor between the  $V_{PORTP}$  and  $V_{PORTN}$  pins, alerting the PSE that a PD is present and requests power to be applied. The LTC4269-2 signature resistor also compensates for the additional series resistance introduced by the input diode bridge. Thus a PD built with the LTC4269-2 conforms to the IEEE 802.3af/at detection specifications.

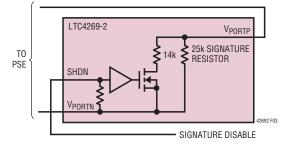

#### SIGNATURE CORRUPT OPTION

In some designs that include an auxiliary power option, it is necessary to prevent a PD from being detected by a PSE. The LTC4269-2 signature resistance can be corrupted with the SHDN pin (Figure 3). Taking the SHDN pin high will reduce the signature resistor below 11k which is an invalid signature per the IEEE 802.3af/at specifications, and alerts the PSE not to apply power. Invoking the SHDN pin

Figure 2. PD Front End Using Diode Bridge on Main and Spare Inputs

Figure 3. 25k Signature Resistor with Disable

also ceases operation for classification and turns off the internal Hot Swap FET. If this feature is not used, connect SHDN to  $V_{\text{PORTN}}$ .

#### CLASSIFICATION

Classification provides a method for more efficient power allocation by allowing the PSE to identify a PD power classification. Class 0 is included in the IEEE specification for PDs that don't support classification. Class 1-3 partitions PDs into three distinct power ranges. Class 4 includes the new power range under IEEE 802.3at (see Table 2).

During classification probing, the PSE presents a fixed voltage between 15.5V and 20.5V to the PD (Figure 1). The LTC4269-2 asserts a load current representing the PD power classification. The classification load current is programmed with a resistor  $R_{CLASS}$  that is chosen from Table 2.

Table 2. Summary of Power Classifications and LTC4269-2  $R_{\mbox{CLASS}}$  Resistor Selection

| CLASS | USAGE  | MAXIMUM<br>POWER LEVELS<br>AT INPUT OF PD<br>(W) | NOMINAL<br>Classification<br>Load current<br>(ma) | LTC4269-2<br>R <sub>CLASS</sub><br>RESISTOR<br>(Ω, 1%) |

|-------|--------|--------------------------------------------------|---------------------------------------------------|--------------------------------------------------------|

| 0     | Type 1 | 0.44 to 12.95                                    | <0.4                                              | Open                                                   |

| 1     | Type 1 | 0.44 to 3.84                                     | 10.5                                              | 124                                                    |

| 2     | Type 1 | 3.84 to 6.49                                     | 18.5                                              | 69.8                                                   |

| 3     | Type 1 | 6.49 to 12.95                                    | 28                                                | 45.3                                                   |

| 4     | Type 2 | 12.95 to 25.5                                    | 40                                                | 30.9                                                   |

#### 2-EVENT CLASSIFICATION AND THE $\overline{12P}$ PIN

A Type 2 PSE may declare the availability of high power by performing a 2-event classification (Layer 1) or by communicating over the high speed data line (Layer 2). A Type 2 PD must recognize both layers of communication. Since

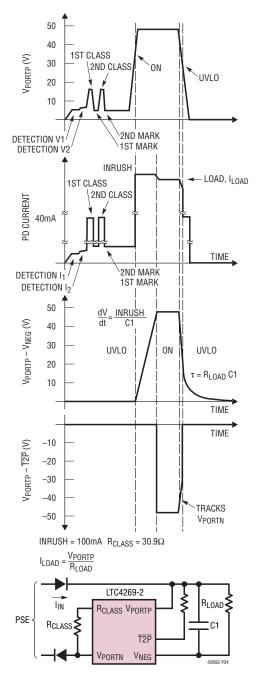

In 2-event classification, a Type 2 PSE probes for power classification twice. Figure 4 presents an example of a 2-event classification. The 1st classification event occurs

Figure 4.  $V_{NEG}, \overline{T2P}$  and PD Current as a Result of 2-Event Classification

when the PSE presents an input voltage between 15.5V to 20.5V and the LTC4269-2 presents a Class 4 load current. The PSE then drops the input voltage into the mark voltage range of 7V to 10V, signaling the 1st mark event. The PD in the mark voltage range presents a load current between 0.25mA to 4mA.

The PSE repeats this sequence, signaling the 2nd Classification and 2nd mark event occurrence. This alerts the LTC4269-2 that a Type 2 PSE is present. The Type 2 PSE then applies power to the PD and the LTC4269-2 charges up the reservoir capacitor C1 with a controlled inrush current. When C1 is fully charged, and the LTC4269-2 declares power good, the T2P pin presents an active low signal, or low impedance output with respect to V<sub>PORTN</sub>. The T2P output becomes inactive when the LTC4269-2 input voltage falls below the PoE undervoltage lockout threshold.

#### SIGNATURE CORRUPT DURING MARK

As a member of the IEEE 802.3at working group, Linear noted that it is possible for a Type 2 PD to receive a false indication of a 2-event classification if a PSE port is precharged to a voltage above the detection voltage range before the first detection cycle. The IEEE working group modified the standard to prevent this possibility by requiring a Type 2 PD to corrupt the signature resistance during the mark event, alerting the PSE not to apply power. The LTC4269-2 conforms to this standard by internally corrupting the signature resistance. This also discharges the port before the PSE begins the next detection cycle.

#### PD STABILITY DURING CLASSIFICATION

Classification presents a challenging stability problem due to the wide range of possible classification load current. The onset of the classification load current introduces a voltage drop across the cable and increases the forward voltage of the input diode bridge. This may cause the PD to oscillate between detection and classification with the onset and removal of the classification load current.

The LTC4269-2 prevents this oscillation by introducing a voltage hysteresis window between the detection and classification ranges. The hysteresis window accommodates

the voltage changes a PD encounters at the onset of the classification load current, thus providing a trouble-free transition between detection and classification modes.

The LTC4269-2 also maintains a positive I-V slope throughout the classification range up to the on voltage. In the event a PSE overshoots beyond the classification voltage range, the available load current aids in returning the PD back into the classification voltage range. (The PD input may otherwise be "trapped" by a reverse-biased diode bridge and the voltage held by the  $0.1\mu$ F capacitor.)

#### **INRUSH CURRENT**

Once the PSE detects and optionally classifies the PD, the PSE then applies power to the PD. When the LTC4269-2 port voltage rises above the on voltage threshold, LTC4269-2 connects  $V_{NEG}$  to  $V_{PORTN}$  through the internal power MOSFET.

To control the power-on surge currents in the system, the LTC4269-2 provides a fixed inrush current, allowing C1 to ramp up to the line voltage in a controlled manner.

The LTC4269-2 keeps the PD inrush current below the PSE current limit to provide a well-controlled power-up characteristic that is independent of the PSE behavior. This ensures a PD using the LTC4269-2 interoperability with any PSE.

#### POE UNDERVOLTAGE LOCKOUT

The IEEE 802.3af/at specification for the PD dictates a maximum turn-on voltage of 42V and a minimum turn-off voltage of 30V. This specification provides an adequate voltage to begin PD operation, and to discontinue PD operation when the port voltage is too low. In addition, this specification allows PD designs to incorporate an on-off hysteresis window to prevent start-up oscillations.

The LTC4269-2 features a PoE undervoltage lockout (UVLO) hysteresis window (See Figure 5) that conforms with the IEEE 802.3af/at specification and accommodates the voltage drop in the cable and input diode bridge at the onset of the inrush current.

Once C1 is fully charged, the LTC4269-2 turns on its internal MOSFET and passes power to the PD. The LTC4269-2

#### LTC4269-2 C1 -PD VPORTP 5μF LOAD MIN T0 UNDERVOLTAGE OVERVOLTAGE PSE LOCKOUT CIRCUIT VNEG PORTN CURRENT-LIMITED TURN ON LTC4269-2 POWER MOSFET V<sub>PORTP</sub> – V<sub>PORTN</sub> OV TO ON\* OFF >0N\* ON <UVL0' OFF >0VL0 OFF **\*INCLUDES ON-UVLO HYSTERESIS** ON THRESHOLD ≈ 36.1V UVL0 THRESHOLD ≅ 30.7V OVLO THRESHOLD $\simeq 71.0V$

### APPLICATIONS INFORMATION

#### Figure 5. LTC4269-2 Undervoltage and Overvoltage Lockout

continues to power the PD load as long as the port voltage does not fall below the UVLO threshold. When the LTC4269-2 port voltage falls below the UVLO threshold, the PD is disconnected, and classification mode resumes. C1 discharges through the LTC4269-2 circuitry.

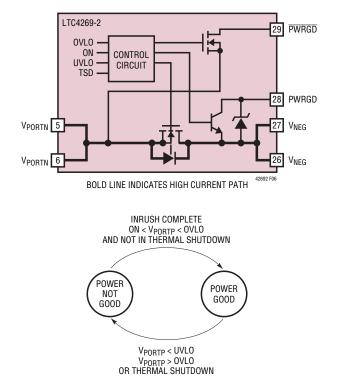

#### **COMPLEMENTARY POWER GOOD**

When LTC4269-2 fully charges the load capacitor (C1), power good is declared and the LTC4269-2 load can safely begin operation. The LTC4269-2 provides complementary power good signals that remain active during normal operation and are deasserted when the port voltage falls below the PoE UVLO threshold, when the voltage exceeds the overvoltage lockout (OVLO) threshold, or in the event of a thermal shutdown. See Figure 6.

The PWRGD pin features an open-collector output referenced to  $V_{NEG}$  which can interface directly with the SD\_V\_{SEC} pin. When power good is declared and active, the PWRGD pin is high impedance with respect to  $V_{NEG}$ . An internal 14V clamp limits the PWRGD pin voltage. Connecting the PWRGD pin to the SD\_V\_{SEC} pin prevents the DC/DC converter from commencing operation before the PDI interface completely charges the reservoir capacitor, C1.

The active low  $\overline{PWRGD}$  pin connects to an internal, opendrain MOSFET referenced to  $V_{PORTN}$  and can interface directly to the shutdown pin of a DC/DC converter product.

Figure 6. LTC4269-2 Power Good Functional and State Diagram

When power good is declared and active, the  $\overline{\text{PWRGD}}$  pin is low impedance with respect to  $V_{\text{PORTN}}$ .

#### **PWRGD PIN WHEN SHDN IS INVOKED**

In PD applications where an auxiliary power supply invokes the SHDN feature, the PWRGD pin becomes high impedance. This prevents the PWRGD pin that is connected to the "RUN" pin of the DC/DC converter from interfering with the DC/DC converter operations when powered by an auxiliary power supply.

#### **OVERVOLTAGE LOCKOUT**

The LTC4269-2 includes an Overvoltage Lockout (OVLO) feature (Figure 5) which protects the LTC4269-2 and its load from an overvoltage event. If the input voltage exceeds the OVLO threshold, the LTC4269-2 discontinues PD operation. Normal operations resume when the input voltage falls below the OVLO threshold and when C1 is charged up.

#### THERMAL PROTECTION

The IEEE 802.3af/at specification requires a PD to withstand any applied voltage from 0V to 57V indefinitely. However, there are several possible scenarios where a PD may encounter excessive heating.

During classification, excessive heating may occur if the PSE exceeds the 75ms probing time limit. At turn-on, when the load capacitor begins to charge, the instantaneous power dissipated by the PD interface can be large before it reaches the line voltage. And if the PD experiences a fast input positive voltage step in its operational mode (for example, from 37V to 57V), the instantaneous power dissipated by the PD Interface can be large.

The LTC4269-2 includes a thermal protection feature which protects the LTC4269-2 from excessive heating. If the LTC4269-2 junction temperature exceeds the overtemperature threshold, the LTC4269-2 discontinues PD operations. Normal operation resumes when the junction temperature falls below the overtemperature threshold and when C1 is charged up and power good becomes inactive.

#### EXTERNAL INTERFACE AND COMPONENT SELECTION

#### Transformer

Nodes on an Ethernet network commonly interface to the outside world via an isolation transformer. For PDs, the isolation transformer must also include a center tap on the RJ45 connector side (see Figure 7).

Figure 7. PD Front End with Isolation Transformer, Diode Bridges, Capacitors and a Transient Voltage Suppressor (TVS) The increased current levels in a Type 2 PD over a Type 1 increase the current imbalance in the magnetics which can interfere with data transmission. In addition, proper termination is also required around the transformer to provide correct impedance matching and to avoid radiated and conducted emissions. Transformer vendors such as Bel Fuse, Coilcraft, Halo, Pulse and Tyco (Table 4) can assist in selecting an appropriate isolation transformer and proper termination methods.

| VENDOR            | CONTACT INFORMATION                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------|

| Bel Fuse Inc.     | 206 Van Vorst Street<br>Jersey City, NJ 07302<br>Tel: 201-432-0463<br>www.belfuse.com                 |

| Coilcraft Inc.    | 1102 Silver Lake Road<br>Gary, IL 60013<br>Tel: 847-639-6400<br>www.coilcraft.com                     |

| Halo Electronics  | 1861 Landings Drive<br>Mountain View, CA 94043<br>Tel: 650-903-3800<br>www.haloelectronics.com        |

| PCA Electronics   | 16799 Schoenborn Street<br>North Hills, CA 91343<br>Tel: 818-892-0761<br>www.pca.com                  |

| Pulse Engineering | 12220 World Trade Drive<br>San Diego, CA 92128<br>Tel: 858-674-8100<br>www.pulseeng.com               |

| Tyco Electronics  | 308 Constitution Drive<br>Menlo Park, CA 94025-1164<br>Tel: 800-227-7040<br>www.circuitprotection.com |

#### **Input Diode Bridge**

Figure 2 shows how two diode bridges are typically connected in a PD application. One bridge is dedicated to the data pair while the other bridge is dedicated to the spare pair. The LTC4269-2 supports the use of either silicon or Schottky input diode bridges. However, there are trade-offs in the choice of diode bridges.

An input diode bridge must be rated above the maximum current the PD application will encounter at the temperature the PD will operate. Diode bridge vendors typically call out the operating current at room temperature, but derate the maximum current with increasing temperature. Consult the diode bridge vendors for the operating current de-rating curve.

A silicon diode bridge can consume over 4% of the available power in some PD applications. Using Schottky diodes can help reduce the power loss with a lower forward voltage.

A Schottky bridge may not be suitable for some high temperature PD applications. The leakage current has a temperature and voltage dependency that can reduce the perceived signature resistance. In addition, the IEEE 802.3af/at specification mandates the leakage back-feeding through the unused bridge cannot generate more than 2.8V across a 100k resistor when a PD is powered with 57V.

#### **Sharing Input Diode Bridges**

At higher temperatures, a PD design may be forced to consider larger bridges in a bigger package because the maximum operating current for the input diode bridge is drastically derated. The larger package may not be acceptable in some space-limited environments.

One solution to consider is to reconnect the diode bridges so that only one of the four diodes conducts current in each package. This configuration extends the maximum operating current while maintaining a smaller package profile. Figure 7 shows how the reconnect the two diode bridges. Consult the diode bridge vendors for the de-rating curve when only one of four diodes is in operation.

#### **Input Capacitor**

The IEEE 802.3af/at standard includes an impedance requirement in order to implement the AC disconnect function. A  $0.1\mu$ F capacitor (C14 in Figure 7) is used to meet this AC impedance requirement. Place this capacitor as close to the LTC4269-2 as possible.

#### Transient Voltage Suppressor

The LTC4269-2 specifies an absolute maximum voltage of 100V and is designed to tolerate brief overvoltage events. However, the pins that interface to the outside world can routinely see excessive peak voltages. To protect the LTC4269-2, install a transient voltage suppressor (D3) between the input diode bridge and the LTC4269-2 as close to the LTC4269-2 as possible as shown in Figure 7.

#### **Classification Resistor (R<sub>CLASS</sub>)**

The R<sub>CLASS</sub> resistor sets the classification load current, corresponding to the PD power classification. Select the value of R<sub>CLASS</sub> from Table 2 and connect the resistor between the R<sub>CLASS</sub> and V<sub>PORTN</sub> pins as shown in Figure 4, or float the R<sub>CLASS</sub> pin if the classification load current is not required. The resistor tolerance must be 1% or better to avoid degrading the overall accuracy of the classification circuit.

#### **Load Capacitor**

The IEEE 802.3af/at specification requires that the PD maintains a minimum load capacitance of  $5\mu$ F and does not specify a maximum load capacitor. However, if the load capacitor is too large, there may be a problem with inadvertent power shutdown by the PSE.

This occurs when the PSE voltage drops quickly. The input diode bridge reverses bias, and the PD load momentarily powers off the load capacitor. If the PD does not draw power within the PSE's 300ms disconnection delay, the PSE may remove power from the PD. Thus, it is necessary to evaluate the load current and capacitance to ensure that an inadvertent shutdown cannot occur.

The load capacitor can store significant energy when fully charged. The PD design must ensure that this energy is not inadvertently dissipated in the LTC4269-2. For example, if the  $V_{PORTP}$  pin shorts to  $V_{PORTN}$  while the capacitor is charged, current will flow through the parasitic body diode of the internal MOSFET and may cause permanent damage to the LTC4269-2.

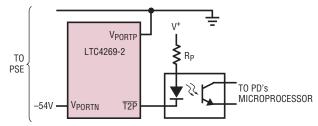

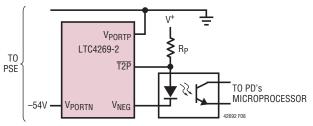

#### **T2P** Interface

When a 2-event classification sequence successfully completes, the LTC4269-2 recognizes this sequence, and provides an indicator bit, declaring the presence of a Type 2 PSE. The open-drain output provides the option to use this signal to communicate to the LTC4269-2 load, or to leave the pin unconnected.

Figure 8 shows two interface options using the  $\overline{T2P}$  pin and the opto-isolator. The  $\overline{T2P}$  pin is active low and connects to an optoisolater to communicate across the

OPTION 1: SERIES CONFIGURATION FOR ACTIVE LOW/LOW IMPEDANCE OUTPUT

OPTION 2: SHUNT CONFIGURATION FOR ACTIVE HIGH/OPEN COLLECTOR OUTPUT

Figure 8. T2P Interface Examples

DC/DC converter isolation barrier. The pull-up resistor  $R_P$  is sized according to the requirements of the opto-isolator operating current, the pull-down capability of the T2P pin, and the choice of V<sup>+</sup>. V<sup>+</sup> for example can come from the PoE supply rail (which the LTC4269-2 V<sub>PORTP</sub> is tied to), or from the voltage source that supplies power to the DC/DC converter. Option 1 has the advantage of not drawing power unless T2P is declared active.

#### Shutdown Interface

To corrupt the signature resistance, the SHDN pin can be driven high with respect to  $V_{PORTN}.$  If unused, connect SHDN directly to  $V_{PORTN}.$

#### Exposed Pad

The LTC4269-2 uses a thermally enhanced DFN12 package that includes an Exposed Pad. The Exposed Pad should be electrically connected to the GND pin's PCB copper plane. This plane should be large enough to serve as the heat sink for the LTC4269-2.

#### **Auxiliary Power Source**

In some applications, it is desirable to power the PD from an auxiliary power source such as a wall adapter. Auxiliary power can be injected into the PD at several locations with priority chosen between PoE or auxiliary power sources. These options come with various trade-offs and design considerations. Contact Linear Technology applications support for detailed information on implementing custom auxiliary power sources.

#### IEEE 802.3AT SYSTEM POWER-UP REQUIREMENT

Under the IEEE 802.3at standard, a PD must operate under 12.95W in accordance with IEEE 802.3at standard until it recognizes a Type 2 PSE. Initializing PD operation in 12.95W mode eliminates interoperability issue in case a Type 2 PD connects to a Type 1 PSE. Once the PD recognizes a Type 2 PSE, the IEEE 802.3at standard requires the PD to wait 80ms in 12.95W operation before 25.5W operation can commence.

#### **MAINTAIN POWER SIGNATURE**

In an IEEE 802.3af/at system, the PSE uses the maintain power signature (MPS) to determine if a PD continues to require power. The MPS requires the PD to periodically draw at least 10mA and also have an AC impedance less than 26.25k in parallel with  $0.05\mu$ F. If one of these conditions is not met, the PSE may disconnect power to the PD.

#### Isolation

The 802.3 standard requires Ethernet ports to be electrically isolated from all other conductors that are user accessible. This includes the metal chassis, other connectors, and any auxiliary power connection. For PDs, there are two common methods to meet the isolation requirement. If there are any user-accessible connections to the PD, then an isolated DC/DC converter is necessary to meet the isolation requirements. If user connections can be avoided, then it is possible to meet the safety requirement by completely enclosing the PD in an insulated housing.

#### Switcher Controller Operation

The LTC4269-2 has a current mode synchronous PWM controller optimized for control of a forward converter topology. The LTC4269-2 is ideal for power systems where very high efficiency and reliability, low complexity and cost are required in a small space. Key features of the LTC4269-2 include an adaptive maximum duty cycle clamp.

An additional output signal is included for synchronous rectifier control or active clamp control. A precision 107mV threshold senses overcurrent conditions and triggers soft-start for low stress short-circuit protection and control. The key functions of the LTC4269-2 PWM controller are shown in the Block Diagrams.

#### Part Start-Up

In normal operation, the SD\_V<sub>SEC</sub> pin must exceed 1.32V and the V<sub>IN</sub> pin must exceed 14.25V to allow the part to turn on. This combination of pin voltages allows the 2.5V V<sub>REF</sub> pin to become active, supplying the LTC4269-2 control circuitry and providing up to 2.5mA external drive. SD\_V<sub>SEC</sub> threshold can be used for externally programming the power supply undervoltage lockout (UVLO) threshold on the input voltage to the forward converter. Hysteresis on the UVLO threshold can also be programmed since the SD\_V<sub>SEC</sub> pin draws 11µA just before part turn-on and 0µA after part turn-on.

With the LTC4269-2 turned on, the V<sub>IN</sub> pin can drop as low as 8.75V before part shutdown occurs. This V<sub>IN</sub> pin hysteresis (5.5V) combined with low 460µA start-up input current allows low power start-up using a resistor/capacitor network from power supply input voltage to supply the V<sub>IN</sub> pin (Figure 10). The V<sub>IN</sub> capacitor value is chosen to prevent V<sub>IN</sub> falling below its turn-off threshold before a bias winding in the converter takes over supply to the V<sub>IN</sub> pin.

#### **Output Drivers**

The LTC4269-2 has two outputs, SOUT and OUT. The OUT pin provides a  $\pm 1A$  peak MOSFET gate drive clamped to 13V. The SOUT pin has a  $\pm 50$ mA peak drive clamped to 12V and provides sync signal timing for synchronous rectification control or active clamp control.

For SOUT and OUT turn-on, a PWM latch is set at the start of each main oscillator cycle. OUT turn-on is delayed from SOUT turn-on by a time,  $t_{DELAY}$  (Figure 14).  $t_{DELAY}$  is programmed using a resistor from the DELAY pin to GND and is used to set the timing control of the secondary synchronous rectifiers for optimum efficiency.

SOUT and OUT turn off at the same time each cycle by one of three methods:

- (1) MOSFET peak current sense at  $\mathsf{I}_{\mathsf{SENSE}}$  pin

- (2) Adaptive maximum duty cycle clamp reached during load/line transients

- (3) Maximum duty cycle reset of the PWM latch

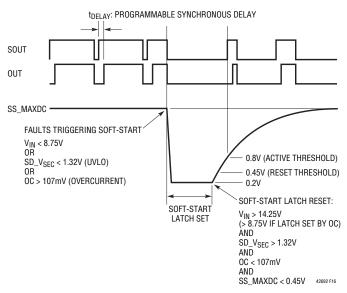

During any of the following conditions—low  $V_{IN}$ , low SD\_V<sub>SEC</sub> or overcurrent detection at the OC pin—a soft-start event is latched and both SOUT and OUT turn off immediately (Figure 11).

#### Leading Edge Blanking

To prevent MOSFET switching noise causing premature turn-off of SOUT or OUT, programmable leading edge blanking exists. This means both the current sense comparator and overcurrent comparator outputs are ignored during MOSFET turn-on and for an extended period after the OUT leading edge (Figure 12). The extended blanking period is programmable by adjusting a resistor from the BLANK pin to GND.

#### Adaptive Maximum Duty Cycle Clamp (Volt-Second Clamp)

For forward converter applications, a maximum switch duty cycle clamp which adapts to transformer input voltage is necessary for reliable control of the MOSFET. This volt-second clamp provides a safeguard for transformer reset that prevents transformer saturation. Instantaneous load changes can cause the converter loop to demand maximum duty cycle. If the maximum duty cycle of the switch is too great, the transformer reset voltage can exceed the voltage rating of the primary-side MOSFETs with catastrophic damage. Many converters solve this problem by limiting the operational duty cycle of the MOSFET to 50% or less—or by using a fixed (non-adaptive) maximum duty cycle clamp with very large voltage rated MOSFETs. The LTC4269-2 provides a volt-second clamp to allow MOSFET duty cycles well above 50%. This gives greater power utilization for the MOSFETs, rectifiers and transformer resulting in less space for a given power output. In addition, the volt-second clamp can allow a reduced voltage rating on the MOSFET resulting in lower RDS(ON) for greater efficiency. The volt-second clamp defines a maximum duty cycle 'guard rail' which falls when power supply input voltage increases. 42692fb

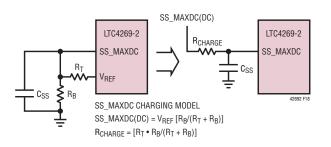

An increase of voltage at the SD\_V<sub>SEC</sub> pin causes the maximum duty cycle clamp to decrease. If SD\_V<sub>SEC</sub> is resistively divided down from power supply input voltage, a volt-second clamp is realized. To adjust the initial maximum duty cycle clamp, the SS\_MAXDC pin voltage is programmed by a resistor divider from the 2.5V V<sub>REF</sub> pin to GND. An increase of programmed voltage on SS\_MAXDC pin provides an increase of switch maximum duty cycle clamp.

#### Soft-Start

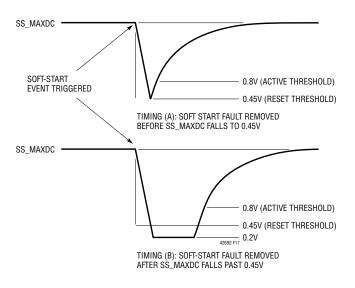

The LTC4269-2 provides true PWM soft-start by using the SS\_MAXDC pin to control soft-start timing. The proportional relationship between SS\_MAXDC voltage and switch maximum duty cycle clamp allows the SS\_MAXDC pin to slowly ramp output voltage by ramping the maximum switch duty cycle clamp—until switch duty cycle clamp seamlessly meets the natural duty cycle of the converter. A soft-start event is triggered whenever V<sub>IN</sub> is too low, SD\_V<sub>SEC</sub> is too low (power supply UVLO), or a 107mV overcurrent threshold at OC pin is exceeded. Whenever a soft-start event is triggered, switching at SOUT and OUT is stopped immediately.

The SS\_MAXDC pin is discharged and only released for charging when it has fallen below its reset threshold of 0.45V and all faults have been removed. Increasing voltage on the SS\_MAXDC pin above 0.8V will increase switch maximum duty cycle. A capacitor to GND on the SS\_MAXDC pin in combination with a resistor divider from  $V_{\text{REF}}$ , defines the soft-start timing.

#### Current Mode Topology (I<sub>SENSE</sub> Pin)

The LTC4269-2 current mode topology eases frequency compensation requirements because the output inductor does not contribute to phase delay in the regulator loop. This current mode technique means that the error amplifier (nonisolated applications) or the opto-coupler (isolated applications) commands current (rather than voltage) to be delivered to the output. This makes frequency compensation easier and provides faster loop response to output load transients. A resistor divider from the application's output voltage generates a voltage at the inverting FB input of the LTC4269-2 error amplifier (or to the input of an external opto-coupler) and is compared to an accurate reference (1.23V for LTC4269-2). The error amplifier output (COMP) defines the input threshold (I<sub>SENSE</sub>) of the current sense comparator. COMP voltages between 0.8V (active threshold) and 2.5V define a maximum I<sub>SENSE</sub> threshold from 0mV to 220mV. By connecting I<sub>SENSE</sub> to a sense resistor in series with the source of an external power MOSFET, the MOSFET peak current trip point (turn off) can be controlled by COMP level and hence by the output voltage. An increase in output load current causing the output voltage to fall, will cause COMP to rise, increasing I<sub>SENSE</sub> threshold, increasing the current delivered to the output. For isolated applications, the error amplifier COMP output can be disabled to allow the opto-coupler to take control. Setting  $FB = V_{RFF}$  disables the error amplifier COMP output, reducing pin current to (COMP - 0.7)/40k.

#### **Slope Compensation**

The current mode architecture requires slope compensation to be added to the current sensing loop to prevent subharmonic oscillations which can occur for duty cycles above 50%. Unlike most current mode converters which have a slope compensation ramp that is fixed internally, placing a constraint on inductor value and operating frequency, the LTC4269-2 has externally adjustable slope compensation. Slope compensation can be programmed by inserting an external resistor ( $R_{SLOPE}$ ) in series with the  $I_{SENSE}$  pin. The LTC4269-2 has a linear slope compensation ramp which sources current out of the  $I_{SENSE}$  pin of approximately 8µA at 0% duty cycle to 35µA at 80% duty cycle.

#### **Overcurrent Detection and Soft-Start (OC Pin)**