## LTC3862-1

### FEATURES

- Wide V<sub>IN</sub> Range: 8.5V to 36V Operation

- 2-Phase Operation Reduces Input and Output Capacitance

- Fixed Frequency, Peak Current Mode Control

- 10V Gate Drive for High Voltage MOSFETs

- Adjustable Slope Compensation Gain

- Adjustable Max Duty Cycle (Up to 96%)

- Adjustable Leading Edge Blanking

- ±1% Internal Voltage Reference

- Programmable Operating Frequency with One External Resistor (75kHz to 500kHz)

- Phase-Lockable Fixed Frequency 50kHz to 650kHz

- SYNC Input and CLKOUT for 2-, 3-, 4-, 6- or 12-Phase Operation (PHASEMODE Programmable)

- Internal 10V LDO Regulator

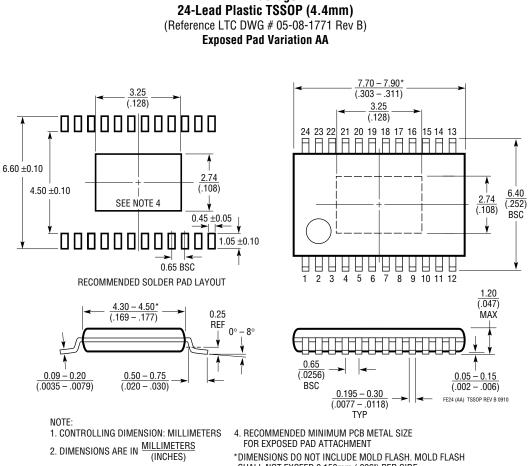

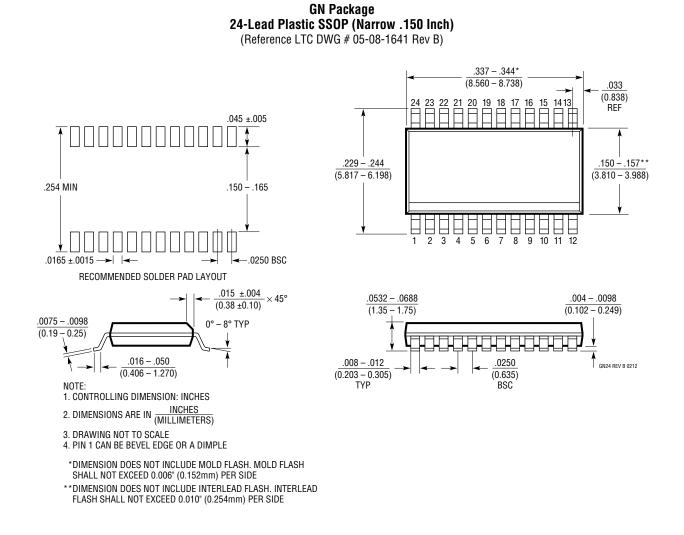

- 24-Lead Narrow SSOP Package

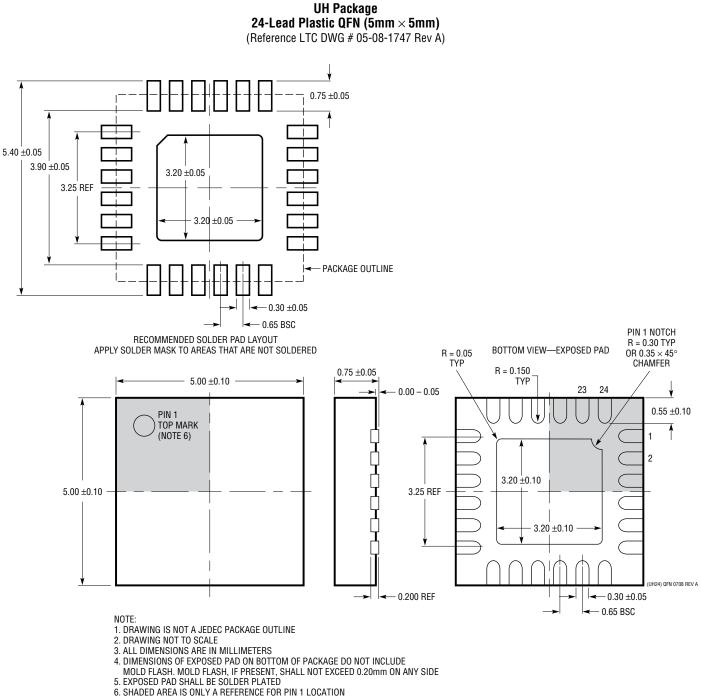

- 5mm × 5mm QFN Package with 0.65mm Lead Pitch

- 24-Lead Thermally Enhanced TSSOP Package

### **APPLICATIONS**

Automotive, Telecom and Industrial Power Supplies

### Multi-Phase Current Mode Step-Up DC/DC Controller **DESCRIPTION**

The LTC<sup>®</sup>3862-1 is a two phase constant frequency, current mode boost and SEPIC controller that drives N-channel power MOSFETs. Two phase operation reduces system filtering capacitance and inductance requirements.

The operating frequency can be set with an external resistor over a 75kHz to 500kHz range and can be synchronized to an external clock using the internal PLL. Multi-phase operation is possible using the SYNC input, the CLKOUT output and the PHASEMODE control pin allowing 2-, 3-, 4-, 6- or 12-phase operation.

Other features include an internal 10V LDO with undervoltage lockout protection for the gate drivers, a precision RUN pin threshold with programmable hysteresis, soft-start and programmable leading edge blanking and maximum duty cycle.

| PART NUMBER | INTV <sub>CC</sub> | V <sub>IN</sub> ON | V <sub>IN</sub> OFF |

|-------------|--------------------|--------------------|---------------------|

| LTC3862     | 5V                 | 3.3V               | 2.9V                |

| LTC3862-1   | 10V                | 7.5V               | 7.0V                |

| LTC3862-2   | 10V                | 4.4V               | 3.9V                |

### ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| Input Supply Voltage (V <sub>IN</sub> )                           |                           | SS, PLLFLTR Voltage          |

|-------------------------------------------------------------------|---------------------------|------------------------------|

| INTV <sub>CC</sub> Voltage                                        | –0.3V to 11V              | ITH Voltage                  |

| INTV <sub>CC</sub> LDO RMS Output Current .                       | 50mA                      | FB Voltage                   |

| RUN Voltage                                                       |                           | FREQ Voltage                 |

| SYNC Voltage                                                      | 0.3V to 6V                | Operating Junction Temperatu |

| SLOPE, PHASEMODE, D <sub>MAX</sub> ,                              |                           | LTC3862-1E                   |

| BLANK Voltage                                                     | –0.3V to V <sub>3V8</sub> | LTC3862-11                   |

| SENSE1 <sup>+</sup> , SENSE1 <sup>-</sup> , SENSE2 <sup>+</sup> , |                           | LTC3862-1H                   |

| SENSE2 <sup>-</sup> Voltage                                       | –0.3V to V <sub>3V8</sub> | Storage Temperature Range    |

| 0                                                                 | 010                       | Potlow Pook Rody Tomporatur  |

####

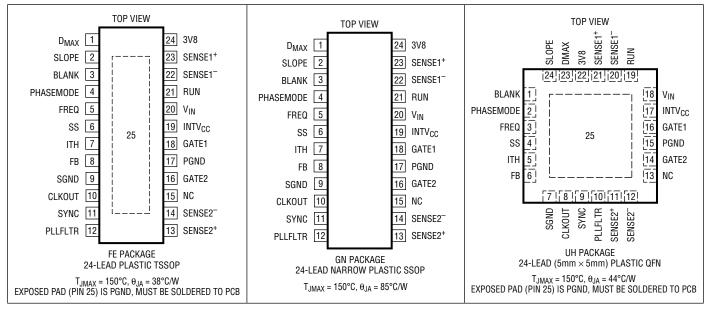

### PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION   | TEMPERATURE RANGE |

|------------------|--------------------|---------------|-----------------------|-------------------|

| LTC3862EFE-1#PBF | LTC3862EFE-1#TRPBF | LTC3862FE-1   | 24-Lead Plastic TSSOP | -40°C to 85°C     |

| LTC3862IFE-1#PBF | LTC3862IFE-1#TRPBF | LTC3862FE-1   | 24-Lead Plastic TSSOP | -40°C to 125°C    |

| LTC3862HFE-1#PBF | LTC3862HFE-1#TRPBF | LTC3862FE-1   | 24-Lead Plastic TSSOP | -40°C to 150°C    |

| LTC3862EGN-1#PBF | LTC3862EGN-1#TRPBF | LTC3862GN-1   | 24-Lead Plastic SSOP  | -40°C to 85°C     |

| LTC3862IGN-1#PBF | LTC3862IGN-1#TRPBF | LTC3862GN-1   | 24-Lead Plastic SSOP  | -40°C to 125°C    |

| LTC3862HGN-1#PBF | LTC3862HGN-1#TRPBF | LTC3862GN-1   | 24-Lead Plastic SSOP  | -40°C to 150°C    |

## **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION                    | TEMPERATURE RANGE |

|------------------|--------------------|---------------|----------------------------------------|-------------------|

| LTC3862EUH-1#PBF | LTC3862EUH-1#TRPBF | 38621         | 24-Lead (5mm $\times$ 5mm) Plastic QFN | -40°C to 85°C     |

| LTC3862IUH-1#PBF | LTC3862IUH-1#TRPBF | 38621         | 24-Lead (5mm $\times$ 5mm) Plastic QFN | -40°C to 125°C    |

| LTC3862HUH-1#PBF | LTC3862HUH-1#TRPBF | 38621         | 24-Lead (5mm $\times$ 5mm) Plastic QFN | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** (Notes 2, 3) The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 12V, RUN = 2V and SS = open, unless otherwise noted.

| SYMBOL                              | PARAMETER                                                               | CONDITIONS                                                                                          |   | MIN            | ТҮР            | MAX            | UNITS    |

|-------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|----------|

| Supply Input an                     | d INTV <sub>CC</sub> Linear Regulator                                   |                                                                                                     |   |                |                |                | ·        |

| V <sub>IN</sub>                     | V <sub>IN</sub> Supply Voltage Range                                    |                                                                                                     | ٠ | 8.5            |                | 36             | V        |

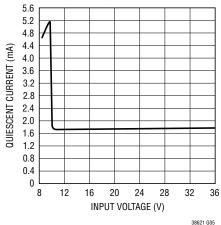

| I <sub>VIN</sub>                    | V <sub>IN</sub> Supply Current<br>Normal Mode, No Switching<br>Shutdown | (Note 5)<br>V <sub>RUN</sub> = 0V                                                                   | • |                | 1.8<br>30      | 3.0<br>80      | mA<br>μA |

| INTV <sub>CC</sub>                  | LDO Regulator Output Voltage                                            |                                                                                                     |   | 9.5            | 10.0           | 10.5           | V        |

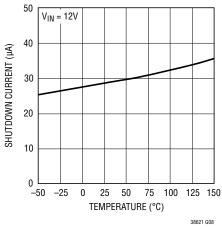

| dV <sub>INTVCC(LINE)</sub>          | Line Regulation                                                         | 12V < V <sub>IN</sub> < 36V                                                                         |   |                | 0.002          | 0.02           | %/V      |

| dV <sub>INTVCC(LOAD)</sub>          | Load Regulation                                                         | Load = 0mA to 20mA                                                                                  |   | -2             |                |                | %        |

| V <sub>UVLO</sub>                   | INTV <sub>CC</sub> UV <sup>+</sup> Voltage                              | Rising INTV <sub>CC</sub>                                                                           |   |                | 7.5            |                | V        |

|                                     | INTV <sub>CC</sub> UV <sup>-</sup> Voltage                              | Falling INTV <sub>CC</sub>                                                                          |   |                | 7.0            |                | V        |

| 3V8                                 | LDO Regulator Output Voltage                                            |                                                                                                     |   |                | 3.8            |                | V        |

| Switcher Contro                     | ol Loop                                                                 |                                                                                                     |   |                |                |                | ·        |

| V <sub>FB</sub>                     | Reference Voltage                                                       | V <sub>ITH</sub> = 0.8V (Note 6) E-Grade (Note 3)<br>I-Grade and H-Grade (Note 3)                   | • | 1.210<br>1.199 | 1.223<br>1.223 | 1.235<br>1.248 | V<br>V   |

| dV <sub>FB</sub> /dV <sub>IN</sub>  | Feedback Voltage V <sub>IN</sub> Line Regulation                        | V <sub>IN</sub> = 8.5V to 36V (Note 6)                                                              |   |                | ±0.002         | 0.01           | %/V      |

| dV <sub>FB</sub> /dV <sub>ITH</sub> | Feedback Voltage Load Regulation                                        | V <sub>ITH</sub> = 0.5V to 1.2V (Note 6)                                                            |   |                | 0.01           | 0.1            | %        |

| 9 <sub>m</sub>                      | Transconductance Amplifier Gain                                         | $V_{ITH} = 0.8V$ (Note 6), ITH Pin Load = $\pm 5\mu A$                                              |   |                | 660            |                | μMho     |

| f <sub>0dB</sub>                    | Error Amplifier Unity-Gain Crossover<br>Frequency                       | (Note 7)                                                                                            |   |                | 1.8            |                | MHz      |

| V <sub>ITH</sub>                    | Error Amplifier Maximum Output Voltage<br>(Internally Clamped)          | V <sub>FB</sub> = 1V, No Load                                                                       |   |                | 2.7            |                | V        |

|                                     | Error Amplifier Minimum Output Voltage                                  | V <sub>FB</sub> = 1.5V, No Load                                                                     |   |                | 50             |                | mV       |

| I <sub>ITH</sub>                    | Error Amplifier Output Source Current                                   |                                                                                                     |   |                | -30            |                | μA       |

|                                     | Error Amplifier Output Sink Current                                     |                                                                                                     |   |                | 30             |                | μA       |

| I <sub>FB</sub>                     | Error Amplifier Input Bias Currents                                     | (Note 6)                                                                                            |   |                | -50            | -200           | nA       |

| VITH(PSKIP)                         | Pulse Skip Mode Operation ITH Pin Voltage                               | Rising ITH Voltage (Note 6)                                                                         |   |                | 0.275          |                | V        |

|                                     |                                                                         | Hysteresis                                                                                          |   |                | 25             |                | mV       |

| SENSE(ON)                           | SENSE Pin Current                                                       |                                                                                                     |   |                | 0.01           | 2              | μA       |

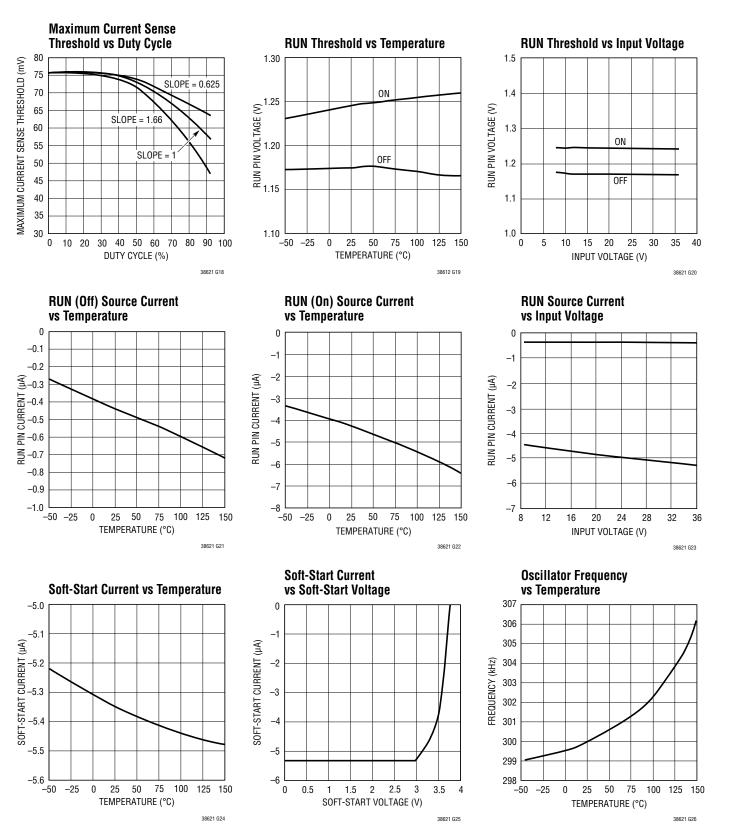

| V <sub>SENSE(MAX)</sub>             | Maximum Current Sense Input Threshold                                   | V <sub>SLOPE</sub> = Float, Low Duty Cycle<br>(Note 3)                                              | • | 65<br>60       | 75<br>75       | 85<br>90       | mV<br>mV |

| V <sub>SENSE</sub> (MATCH)          | CH1 to CH2 Maximum Current Sense<br>Threshold Matching                  | V <sub>SLOPE</sub> = Float, Low Duty Cycle (Note 3)<br>(V <sub>SENSE1</sub> - V <sub>SENSE2</sub> ) | • | -10            |                | 10             | mV       |

| RUN/Soft-Start                      |                                                                         |                                                                                                     |   |                |                |                |          |

| I <sub>RUN</sub>                    | RUN Source Current                                                      | V <sub>RUN</sub> = 0V<br>V <sub>RUN</sub> = 1.5V                                                    |   |                | -0.5<br>-5     |                | μΑ<br>μΑ |

| V <sub>RUN</sub>                    | High Level RUN Channel Enable Threshold                                 |                                                                                                     |   |                | 1.22           |                | V        |

### **ELECTRICAL CHARACTERISTICS** (Notes 2, 3) The • denotes the specifications which apply over the specified

operating junction temperature range, otherwise specifications are at  $T_A = 25$ °C.  $V_{IN} = 12V$ , RUN = 2V and SS = open, unless otherwise noted.

| SYMBOL                | PARAMETER                                       | CONDITIONS                                                                                    |   | MIN        | ТҮР               | MAX        | UNITS             |

|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------|---|------------|-------------------|------------|-------------------|

| V <sub>RUNHYS</sub>   | RUN Threshold Hysteresis                        |                                                                                               |   |            | 80                |            | mV                |

| I <sub>SS</sub>       | SS Pull-Up Current                              | V <sub>SS</sub> = 0V                                                                          |   |            | -5                |            | μA                |

| R <sub>SS</sub>       | SS Pull-Down Resistance                         | V <sub>RUN</sub> = 0V                                                                         |   |            | 10                |            | kΩ                |

| Oscillator            |                                                 | -                                                                                             |   |            |                   |            |                   |

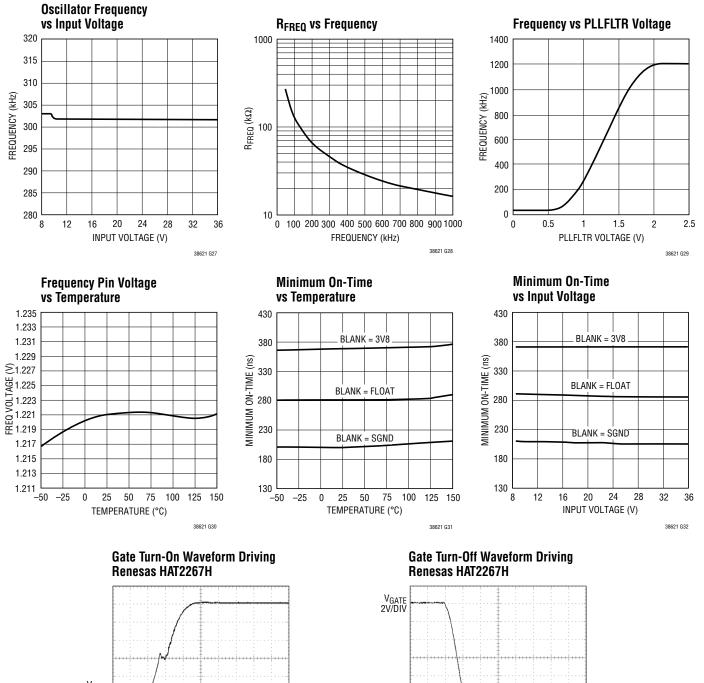

| f <sub>OSC</sub>      | Oscillator Frequency                            | R <sub>FREQ</sub> = 45.6k<br>R <sub>FREQ</sub> = 45.6k                                        | • | 280<br>260 | 300<br>300        | 320<br>340 | kHz<br>kHz        |

|                       | Oscillator Frequency Range                      |                                                                                               | • | 75         |                   | 500        | kHz               |

| V <sub>FREQ</sub>     | Nominal FREQ Pin Voltage                        | R <sub>FREQ</sub> = 45.6k                                                                     |   |            | 1.223             |            | V                 |

| f <sub>SYNC</sub>     | SYNC Minimum Input Frequency                    | V <sub>SYNC</sub> = External Clock                                                            | • |            |                   | 50         | kHz               |

|                       | SYNC Maximum Input Frequency                    | V <sub>SYNC</sub> = External Clock                                                            | • | 650        |                   |            | kHz               |

| V <sub>SYNC</sub>     | SYNC Input Threshold                            | Rising Threshold                                                                              |   |            | 1.5               |            | V                 |

| I <sub>PLLFLTR</sub>  | Phase Detector Sourcing Output Current          | $f_{SYNC} > f_{OSC}$                                                                          |   |            | -15               |            | μA                |

|                       | Phase Detector Sinking Output Current           | f <sub>SYNC</sub> < f <sub>OSC</sub>                                                          |   |            | 15                |            | μA                |

| CH1-CH2               | Channel 1 to Channel 2 Phase Relationship       | V <sub>PHASEMODE</sub> = 0V<br>V <sub>PHASEMODE</sub> = Float<br>V <sub>PHASEMODE</sub> = 3V8 |   |            | 180<br>180<br>120 |            | Deg<br>Deg<br>Deg |

| CH1-CLKOUT            | Channel 1 to CLKOUT Phase Relationship          | V <sub>PHASEMODE</sub> = 0V<br>V <sub>PHASEMODE</sub> = Float<br>V <sub>PHASEMODE</sub> = 3V8 |   |            | 90<br>60<br>240   |            | Deg<br>Deg<br>Deg |

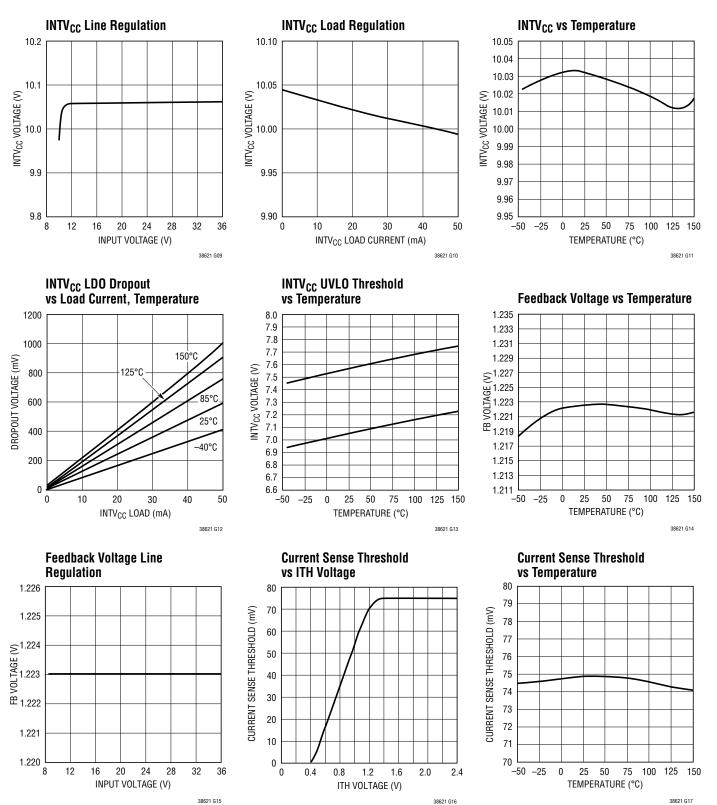

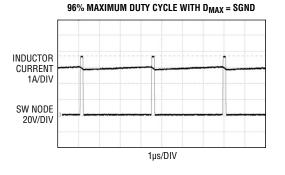

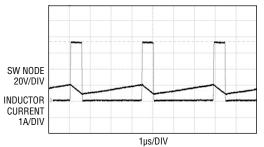

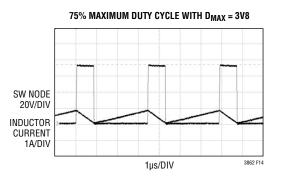

| D <sub>MAX</sub>      | Maximum Duty Cycle                              | V <sub>DMAX</sub> = 0V (Note 9)<br>V <sub>DMAX</sub> = Float<br>V <sub>DMAX</sub> = 3V8       |   |            | 96<br>84<br>75    |            | %<br>%<br>%       |

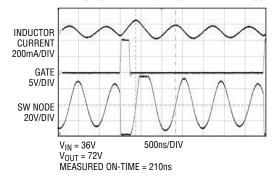

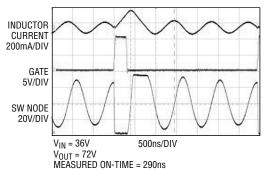

| t <sub>ON(MIN)1</sub> | Minimum On-Time                                 | V <sub>BLANK</sub> = 0V (Note 8)                                                              |   |            | 210               |            | ns                |

| t <sub>ON(MIN)2</sub> | Minimum On-Time                                 | V <sub>BLANK</sub> = Float (Note 8)                                                           |   |            | 290               |            | ns                |

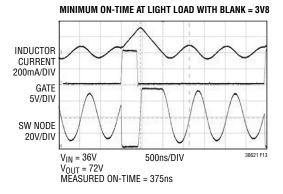

| t <sub>ON(MIN)3</sub> | Minimum On-Time                                 | V <sub>BLANK</sub> = 3V8 (Note 8)                                                             |   |            | 375               |            | ns                |

| Gate Driver           |                                                 |                                                                                               |   |            |                   |            |                   |

| R <sub>DS(ON)</sub>   | Driver Pull-Up R <sub>DS(ON)</sub>              |                                                                                               |   |            | 3                 |            | Ω                 |

| · ·                   | Driver Pull-Down R <sub>DS(ON)</sub>            |                                                                                               |   |            | 0.9               |            | Ω                 |

| Overvoltage           |                                                 |                                                                                               |   |            |                   |            |                   |

| V <sub>FB(OV)</sub>   | V <sub>FB</sub> , Overvoltage Lockout Threshold | V <sub>FB(OV)</sub> – V <sub>FB(NOM)</sub> in Percent                                         |   | 8          | 10                | 12         | %                 |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

**Note 3:** The LTC3862E-1 is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3862I-1 is guaranteed over the full -40°C to 125°C operating temperature range and the LTC3862H-1 is guaranteed over the full -40°C to 150°C operating temperature range. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 4**: This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 5:** Supply current in normal operation is dominated by the current needed to charge the external MOSFET gates. This current will vary with supply voltage and the external MOSFETs used.

Note 6: The IC is tested in a feedback loop that adjusts  $V_{FB}$  to achieve a specified error amplifier output voltage.

Note 7: Guaranteed by design, not subject to test.

**Note 8:** The minimum on-time condition is specified for an inductor peakto-peak ripple current = 30% (see Minimum On-Time Considerations in the Applications Information section).

**Note 9:** The maximum duty cycle limit is derived from an internal clock that runs at 12x the programmed switching frequency. See the Applications Information for additional information.

Inductor Current at Light Load

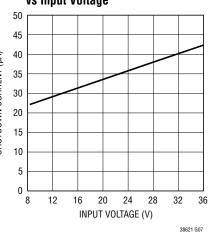

Quiescent Current vs Input Voltage

Shutdown Quiescent Current vs Input Voltage

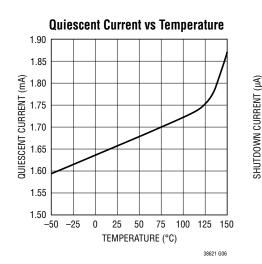

Shutdown Quiescent Current vs Temperature

VGATE 2V/DIV 200s/DIV VIN = 24V VOIT = 72V ILOAD = 0.25A

#### For more information www.linear.com/LTC3862-1

20ns/DIV

$V_{IN} = 24V$  $V_{OUT} = 72V$  $I_{LOAD} = 0.25A$  38621 G34

### PIN FUNCTIONS (SSOP/QFN/TSSOP)

**3V8 (Pin 24/Pin 22/Pin 24):** Output of the Internal 3.8V LDO from  $INTV_{CC}$ . Supply pin for the low voltage analog and digital circuits. A low ESR 1nF ceramic bypass capacitor should be connected between 3V8 and SGND, as close as possible to the IC.

**BLANK (Pin 3/Pin 1/Pin 3):** Blanking Time. Floating this pin provides a nominal minimum on-time of 290ns. Connecting this pin to 3V8 provides a minimum on-time of 375ns, while connecting it to SGND provides a minimum on-time of 210ns.

**CLKOUT (Pin 10/Pin 8/Pin 10):** Digital Output Used for Daisy-Chaining Multiple LTC3862-1 ICs in Multi-Phase Systems. The PHASEMODE pin voltage controls the relationship between CH1 and CH2 as well as between CH1 and CLKOUT.

**D**<sub>MAX</sub> (**Pin 1/Pin 23/Pin 1**): Maximum Duty Cycle. This pin programs the maximum duty cycle. Floating this pin provides 84% duty cycle. Connecting this pin to 3V8 provides 75% duty cycle, while connecting it to SGND provides 96% duty cycle. The maximum duty cycle limit is derived from an internal clock that runs at 12x the programmed switching frequency. As a result, the maximum duty cycle limit D<sub>MAX</sub> is extremely precise.

**FB (Pin 8/Pin 6/Pin 8):** Error Amplifier Input. The FB pin should be connected through a resistive divider network to V<sub>OUT</sub> to set the output voltage.

**FREQ (Pin 5/Pin 3/Pin 5):** A resistor from FREQ to SGND sets the operating frequency.

**GATE1 (Pin 18/Pin 16/Pin 18):** Gate Drive Output. The LTC3862-1 provides a 10V gate drive referenced to PGND to drive a high voltage MOSFET. The GATE pin is rated for an absolute maximum voltage of –0.3V minimum and 11V maximum.

**GATE2 (Pin 16/Pin 14/Pin 16):** Gate Drive Output. The LTC3862-1 provides a 10V gate drive referenced to PGND to drive a high voltage MOSFET. The GATE pin is rated for an absolute maximum voltage of –0.3V minimum and 11V maximum.

**INTV<sub>CC</sub> (Pin 19/Pin 17/Pin 19):** Output of the Internal 10V Low Dropout Regulator (LDO). A low ESR  $4.7\mu$ F (X5R or better) ceramic bypass capacitor should be connected between INTV<sub>CC</sub> and PGND, as close as possible to the IC.

**ITH (Pin 7/Pin 5/Pin 7):** Error Amplifier Output. The current comparator trip threshold increases with the ITH control voltage. The ITH pin is also used for compensating the control loop of the converter.

**PGND (Pin 17/Pin 15, Exposed Pad Pin 25/Pin 17, Exposed Pad Pin 25):** Power Ground. Connect this pin close to the sources of the power MOSFETs. PGND should also be connected to the negative terminals of  $V_{IN}$  and INTV<sub>CC</sub> bypass capacitors. PGND is electrically isolated from the SGND pin. The Exposed Pad of the QFN and FE packages is connected to PGND and must be soldered to PCB ground for electrical contact and rated thermal performance.

**PHASEMODE (Pin 4/Pin 2/Pin 4):** The PHASEMODE pin voltage programs the phase relationship between CH1 and CH2 rising gate signals, as well as the phase relationship between CH1 gate signal and CLKOUT. Floating this pin or connecting it to either 3V8, or SGND changes the phase relationship between CH1, CH2 and CLKOUT.

**PLLFLTR (Pin 12/Pin 10/Pin 12):** PLL Lowpass Filter Input. When synchronizing to an external clock, this pin serves as the lowpass filter input for the PLL. A series resistor and capacitor connected from PLLFLTR to SGND compensate the PLL feedback loop.

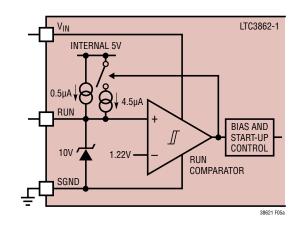

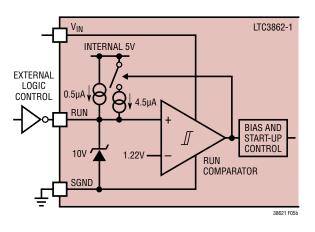

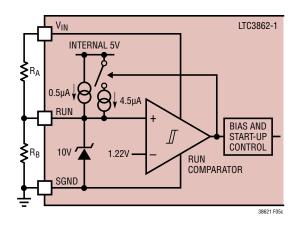

**RUN (Pin 21/Pin 19/Pin 21):** Run Control Input. A voltage above 1.22V on the pin turns on the IC. Forcing the pin below 1.22V causes the IC to shut down. There is a  $0.5\mu$ A pull-up current for this pin. Once the RUN pin raises above 1.22V, an additional 4.5 $\mu$ A pull-up current is added to the pin for programmable hysteresis.

**SENSE1<sup>+</sup>** (Pin 23/Pin 21/Pin 23): Positive Inputs to the Current Comparators. The ITH pin voltage programs the current comparator offset in order to set the peak current trip threshold. This pin is normally connected to a sense resistor in the source of the power MOSFET.

### PIN FUNCTIONS (SSOP/QFN/TSSOP)

**SENSE2+** (Pin 13/Pin 11/Pin 13): Positive Inputs to the Current Comparators. The ITH pin voltage programs the current comparator offset in order to set the peak current trip threshold. This pin is normally connected to a sense resistor in the source of the power MOSFET.

**SENSE1<sup>-</sup> (Pin 22/Pin 20/Pin 22):** Negative Inputs to the Current Comparators. This pin is normally connected to the bottom of the sense resistor.

**SENSE2<sup>-</sup>** (Pin 14/Pin 12/Pin 14): Negative Inputs to the Current Comparators. This pin is normally connected to the bottom of the sense resistor.

**SGND (Pin 9/Pin 7/Pin 9):** Signal Ground. All feedback and soft-start connections should return to SGND. For optimum load regulation, the SGND pin should be kelvin connected to the PCB location between the negative terminals of the output capacitors.

**SLOPE (Pin 2/Pin 24/Pin 2):** This pin programs the gain of the internal slope compensation. Floating this pin provides a normalized slope compensation gain of 1.00. Connecting this pin to 3V8 increases the normalized

slope compensation by 66%, and connecting it to SGND decreases the normalized slope compensation by 37.5%. See Applications Information for more details.

**SS (Pin 6/Pin 4/Pin 6):** Soft-Start Input. For soft-start operation, connecting a capacitor from this pin to SGND will clamp the output of the error amp. An internal  $5\mu$ A current source will charge the capacitor and set the rate of increase of the peak switch current of the converter.

**SYNC (Pin 11/Pin 9/Pin 11):** PLL Synchronization Input. Applying an external clock between 50kHz and 650kHz will cause the operating frequency to synchronize to the clock. SYNC is pulled down by a 50k internal resistor. The rising edge of the SYNC input waveform will align with the rising edge of GATE1 in closed-loop operation. A SYNC signal with an amplitude greater than 1.6V is considered an active high, while any signal below 0.9V is considered an active low.

$V_{\rm IN}$  (Pin 20/Pin 18/Pin 20): Main Supply Input. A low ESR ceramic capacitor should be connected between this pin and SGND.

### FUNCTIONAL DIAGRAM

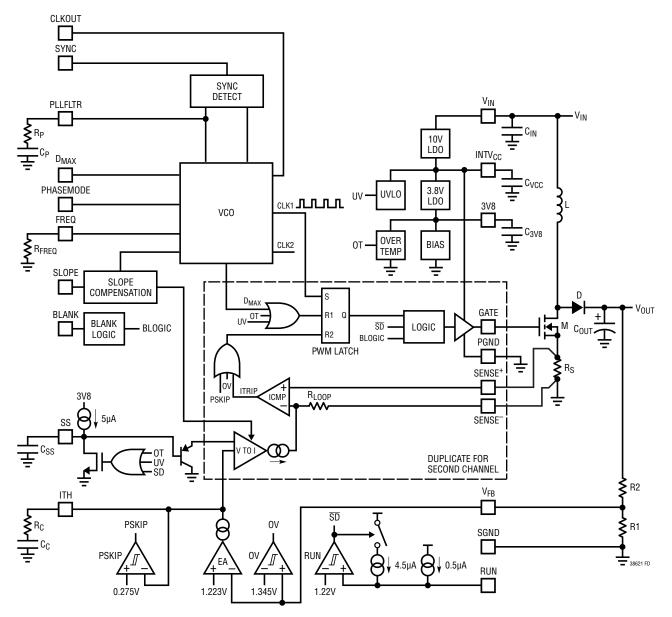

#### The Control Loop

The LTC3862-1 uses a constant frequency, peak current mode step-up architecture with its two channels operating 180 degrees out of phase. During normal operation, each external MOSFET is turned on when the clock for that channel sets the PWM latch, and is turned off when the main current comparator, ICMP, resets the latch. The peak inductor current at which ICMP trips and resets the latch is controlled by the voltage on the ITH pin, which is the output of the error amplifier, EA. The error amplifier compares the output feedback signal at the V<sub>FB</sub> pin to the internal 1.223V reference and generates an error signal at the ITH pin. When the load current increases it causes a slight decrease in V<sub>FB</sub> relative to the reference voltage, which causes the EA to increase the ITH voltage until the average inductor current matches the new load current. After the MOSFET is turned off, the inductor current flows through the boost diode into the output capacitor and load, until the beginning of the next clock cycle.

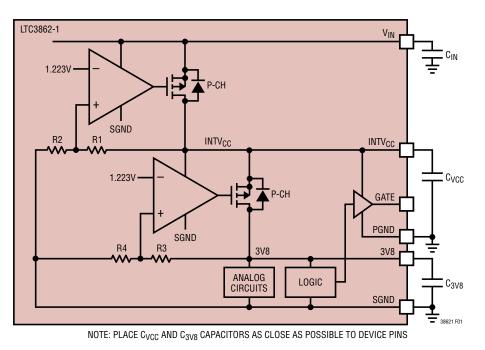

# Cascaded LDOs Supply Power to the Gate Driver and Control Circuitry

The LTC3862-1 contains two cascaded PMOS output stage low dropout voltage regulators (LDOs), one for the gate

drive supply (INTV<sub>CC</sub>) and one for the low voltage analog and digital control circuitry (3V8). A block diagram of this power supply arrangement is shown in Figure 1.

### The Gate Driver Supply LDO (INTV<sub>CC</sub>)

The 10V output (INTV<sub>CC</sub>) of the first LDO is powered from  $V_{IN}$  and supplies power to the power MOSFET gate drivers. The INTV<sub>CC</sub> pin should be bypassed to PGND with a minimum of 4.7µF of ceramic capacitance (X5R or better), placed as close as possible to the IC pins. If two power MOSFETs are connected in parallel for each channel in order to increase the output power level, or if a single MOSFET with a Q<sub>G</sub> greater than 50nC is used, then it is recommended that the bypass capacitance be increased to a minimum of 10µF.

An undervoltage lockout (UVLO) circuit senses the INTV<sub>CC</sub> regulator output in order to protect the power MOSFETs from operating with inadequate gate drive. For the LTC3862-1 the rising UVLO threshold is typically 7.5V and the hysteresis is typically 500mV. The LTC3862-1 was optimized for high voltage power MOSFETs and applications. For applications requiring logic-level power MOSFETs, please refer to the LTC3862 data sheet.

Figure 1. Cascaded LDOs Provide Gate Drive and Control Circuitry Power

In multi-phase applications, all of the FB pins are connected together and all of the error amplifier output pins (ITH) are connected together. The INTV<sub>CC</sub> pins, however, should not be connected together. The INTV<sub>CC</sub> regulator is capable of sourcing current but is not capable of sinking current. As a result, when two or more INTV<sub>CC</sub> regulator outputs are connected together, the highest voltage regulator supplies all of the gate drive and control circuit current, and the other regulators are off. This would place a thermal burden on the highest output voltage LDO and could cause the maximum die temperature to be exceeded. In multi-phase LTC3862-1 applications, each INTV<sub>CC</sub> regulator output should be independently bypassed to its respective PGND pin as close as possible to each IC.

#### The Low Voltage Analog and Digital Supply LDO (3V8)

The second LDO within the LTC3862-1 is powered off of  $INTV_{CC}$  and serves as the supply to the low voltage analog and digital control circuitry, as shown in Figure 1. The output voltage of this LDO (which also has a PMOS output device) is 3.8V. Most of the analog and digital control circuitry is powered from the internal 3V8 LDO. The 3V8 pin should be bypassed to SGND with a 1nF ceramic capacitor (X5R or better), placed as close as possible to the IC pins. This LDO is not intended to be used as a supply for external circuitry.

### Thermal Considerations and Package Options

The LTC3862-1 is offered in three package options. The 5mm  $\times$  5mm QFN package (UH24) has a thermal resistance R<sub>TH(JA)</sub> of 34°C/W, the 24-pin TSSOP (FE24) package has a thermal resistance of 38°C/W, and the 24-pin SSOP (GN24) package has a thermal resistance of 85°C/W. The QFN and TSSOP package options have a lead pitch of 0.65mm, and the GN24 option has a lead pitch of 0.025in.

The  $INTV_{CC}$  regulator can supply up to 50mA of total current. As a result, care must be taken to ensure that

the maximum junction temperature of the IC is never exceeded. The junction temperature can be estimated using the following equations:

$$I_{Q(TOT)} = I_Q + Q_{G(TOT)} \bullet f$$

$$P_{DISS} = V_{IN} \bullet (I_Q + Q_{G(TOT)} \bullet f)$$

$$T_J = T_A + P_{DISS} \bullet R_{TH(JA)}$$

The total quiescent current  $(I_{Q(TOT)})$  consists of the static supply current  $(I_Q)$  and the current required to charge the gate capacitance of the power MOSFETs. The value of  $Q_{G(TOT)}$  should come from the plot of  $V_{GS}$  vs  $Q_G$  in the Typical Performance Characteristics section of the MOSFET data sheet. The value listed in the electrical specifications may be measured at a higher  $V_{GS}$ , such as 15V, whereas the value of interest is at the 10V INTV<sub>CC</sub> gate drive voltage.

As an example of the required thermal analysis, consider a 2-phase boost converter with a 8.5V to 24V input voltage range and an output voltage of 72V at 1.5A. The switching frequency is 150kHz and the maximum ambient temperature is 70°C. The power MOSFET used for this application is the Renesas HAT2267H, which has a typical  $R_{DS(ON)}$  of 13m $\Omega$  at  $V_{GS}$  = 10V. From the plot of  $V_{GS}$  vs  $Q_G$ , the total gate charge at  $V_{GS}$  = 10V is 30nC (the temperature coefficient of the gate charge is low). One power MOSFET is used for each phase. For the QFN package option:

$I_{Q(TOT)} = 3mA + 2 \cdot 30nC \cdot 150kHz = 12mA$   $P_{DISS} = 24V \cdot 12mA = 288mW$  $T_{.1} = 70^{\circ}C + 288mW \cdot 34^{\circ}C/W = 79.8^{\circ}C$

In this example, the junction temperature rise is only 9.8°C. These equations demonstrate how the gate charge current typically dominates the quiescent current of the IC, and how the choice of package option and board heat sinking can have a significant effect on the thermal performance of the solution.

To prevent the maximum junction temperature from being exceeded, the input supply current to the IC should be checked when operating in continuous mode (heavy load) at maximum  $V_{IN}$ . A tradeoff between the operating frequency and the size of the power MOSFETs may need to be made in order to maintain a reliable junction temperature. Finally, it is important to verify the calculations by performing a thermal analysis of the final PCB using an infrared camera or thermal probe. As an option, an exernal regulator shown in Figure 3 can be used to reduce the total power dissipation on the IC.

### Thermal Shutdown Protection

In the event of an overtemperature condition (external or internal), an internal thermal monitor will shut down the gate drivers and reset the soft-start capacitor if the die temperature exceeds 170°C. This thermal sensor has a hysteresis of 10°C to prevent erratic behavior at hot temperatures. The LTC3862-1's internal thermal sensor is intended to protect the device during momentary overtemperature conditions. Continuous operation above the specified maximum operating junction temperature, however, may result in device degradation.

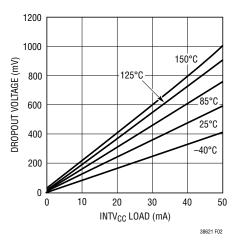

### **Operation at Low Supply Voltage**

The LTC3862-1 has a minimum input voltage of 8.5V, making it a good choice for applications that require high voltage power MOSFETs. The gate driver for the LTC3862-1 consists of PMOS pull-up and NMOS pull-down devices, allowing the full INTV<sub>CC</sub> voltage to be applied to the gates during power MOSFET switching. Nonetheless, care should be taken to determine the minimum gate drive supply voltage (INTV<sub>CC</sub>) in order to choose the optimum power MOSFETs. Important parameters that can affect the minimum gate drive voltage are the minimum input voltage (V<sub>IN(MIN)</sub>), the LDO dropout voltage, the Q<sub>G</sub> of the power MOSFETs, and the operating frequency. If the input voltage  $V_{\text{IN}}$  is low enough for the  $\text{INTV}_{\text{CC}}$  LDO to be in dropout, then the minimum gate drive supply voltage is:

$V_{INTVCC} = V_{IN(MIN)} - V_{DROPOUT}$

The LDO dropout voltage is a function of the total gate drive current and the quiescent current of the IC (typically 3mA). A curve of dropout voltage vs output current for the LDO is shown in Figure 2. The temperature coefficient of the LDO dropout voltage is approximately 6000ppm/°C.

The total Q-current  $(I_{Q(TOT)})$  flowing in the LDO is the sum of the controller quiescent current (3mA) and the total gate charge drive current.

$I_{Q(TOT)} = I_Q + Q_{G(TOT)} \bullet f$

After the calculations have been completed, it is important to measure the gate drive waveforms and the gate driver supply voltage (INTV<sub>CC</sub> to PGND) over all operating conditions (low V<sub>IN</sub>, nominal V<sub>IN</sub> and high V<sub>IN</sub>, as well as from light load to full load) to ensure adequate power MOSFET enhancement. Consult the power MOSFET data sheet to determine the actual  $R_{DS(ON)}$  for the measured V<sub>GS</sub>, and verify your thermal calculations by measuring the component temperatures using an infrared camera or thermal probe.

Figure 2. INTV<sub>CC</sub> LDO Dropout Voltage vs Current

### **Operation at High Supply Voltage**

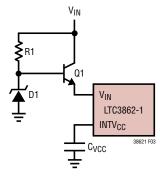

At high input voltages, the LTC3862-1's internal LDO can dissipate a significant amount of power, which could cause the maximum junction temperature to be exceeded. Conditions such as a high operating frequency, or the use of more than one power MOSFET per channel, could push the junction temperature rise to high levels. If the thermal equations above indicate too high a rise in the junction temperature, an external bias supply can always be used to reduce the power dissipation on the IC, as shown in Figure 3.

For example, a 12V system rail that is available would be more suitable than the 24V main input power rail to power the LTC3862-1. Also, the bias power can be generated with a separate switching or LDO regulator. An example of an LDO regulator is shown in Figure 3. The output voltage of the LDO regulator can be set by selecting an appropriate Zener diode to be higher than 10V but low enough to divide the power dissipation between LTC3862-1 and Q1 in Figure 3. The absolute maximum voltage rating of the INTV<sub>CC</sub> pin is 11V.

Figure 3. Using the LTC3862-1 with an External Bias Supply

### **Power Supply Sequencing**

As shown in Figure 1, there are body diodes in parallel with the PMOS output transistors in the two LDO regulators in the LTC3862-1. As a result, it is not possible to bias the INTV<sub>CC</sub> and  $V_{IN}$  pins of the chip from separate power

supplies. Independently biasing the INTV<sub>CC</sub> pin from a separate power supply can cause one of two possible failure modes during supply sequencing. If the INTV<sub>CC</sub> supply comes up before the V<sub>IN</sub> supply, high current will flow from the external INTV<sub>CC</sub> supply, through the body diode of the LDO PMOS device, to the input capacitor and V<sub>IN</sub> pin. This high current flow could trigger a latchup condition and cause catastrophic failure of the IC.

If, however, the  $V_{IN}$  supply to the IC comes up before the INTV<sub>CC</sub> supply, the external INTV<sub>CC</sub> supply will act as a load to the internal LDO in the LTC3862-1, and the LDO will attempt to charge the INTV<sub>CC</sub> output with its short-circuit current. This will result in excessive power dissipation and possible thermal overload of the LTC3862-1.

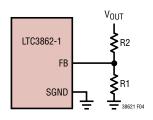

#### Programming the Output Voltage

The output voltage is set by a resistor divider according to the following formula:

$$V_{\text{OUT}} = 1.223 \, \text{V} \left( 1 + \frac{\text{R2}}{\text{R1}} \right)$$

The external resistor divider is connected to the output as shown in Figure 4. Resistor R1 is normally chosen so that the output voltage error caused by the current flowing out of the  $V_{FB}$  pin during normal operation is negligible compared to the current in the divider. For an output voltage error due to the error amp input bias current of less than 0.5%, this translates to a maximum value of R1 of about 30k.

Figure 4. Programming the Output Voltage with a Resistor Divider

#### Operation of the RUN Pin

The control circuitry in the LTC3862-1 is turned on and off using the RUN pin. Pulling the RUN pin below 1.22V forces shutdown mode and releasing it allows a  $0.5\mu$ A current source to pull this pin up, allowing a "normally on" converter to be designed. Alternatively, the RUN pin can be externally pulled up or driven directly by logic. Care must be taken not to exceed the absolute maximum rating of 8V for this pin.

The comparator on the RUN pin can also be used to sense the input voltage, allowing an undervoltage detection circuit to be designed. This is helpful in boost converter applications where the input current can reach very high levels at low input voltage:

$$I_{IN} = \frac{I_{OUT} \bullet V_{OUT}}{V_{IN}}$$

The 1.22V input threshold of the RUN comparator is derived from a precise bandgap reference, in order to maximize the accuracy of the undervoltage-sensing function. The RUN comparator has 80mV built-in hysteresis. When the voltage on the RUN pin exceeds 1.22V, the current sourced into the RUN pin is switched from  $0.5\mu$ A to  $5\mu$ A current. The user can therefore program both the rising threshold and the amount of hysteresis using the values of the resistors in the external divider, as shown in the following equations:

$$V_{IN(ON)} = 1.22V \left(1 + \frac{R_A}{R_B}\right) - 0.5\mu \bullet R_A$$

$$V_{IN(OFF)} = 1.22V \left(1 + \frac{R_A}{R_B}\right) - 5\mu \bullet R_A$$

Several of the possible RUN pin control techniques are illustrated in Figure 5.

### Frequency Selection and the Phase Lock Loop

The selection of the switching frequency is a tradeoff between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires a larger inductor and output capacitor to maintain low output ripple.

Figure 5a. Using the RUN Pin for a "Normally On" Converter

Figure 5b. On/Off Control Using External Logic

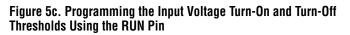

The LTC3862-1 uses a constant frequency architecture that can be programmed over a 75kHz to 500kHz range using a single resistor from the FREQ pin to ground. Figure 6 illustrates the relationship between the FREQ pin resistance and the operating frequency.

Figure 6. FREQ Pin Resistor Value vs Frequency

The operating frequency of the LTC3862-1 can be approximated using the following formula:

$R_{FREQ} = 5.5096E9(f_{OSC})^{-0.9255}$

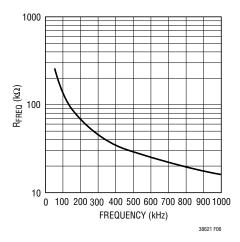

A phase-lock loop is available on the LTC3862-1 to synchronize the internal oscillator to an external clock source connected to the SYNC pin. Connect a series RC network from the PLLFLTR pin to SGND to compensate PLL's feedback loop. Typical compensation components are a  $0.01\mu$ F capacitor in series with a 10k resistor. The PLLFLTR pin is both the output of the phase detector and the input to the voltage controlled oscillator (VCO). The LTC3862-1 phase detector adjusts the voltage on the PLLFLTR pin to align the rising edge of GATE1 to the leading edge of the external clock signal, as shown in Figure 7. The rising edge of GATE2 will depend upon the voltage on the PHASEMODE pin. The capture range of the LTC3862-1's PLL is 50kHz to 650kHz.

Figure 7: Synchronization of the LTC3862-1 to an External Clock Using the PLL

Because the operating frequency of the LTC3862-1 can be programmed using an external resistor, in synchronized applications, it is recommended that the free-running frequency (as defined by the external resistor) be set to the same value as the synchronized frequency. This results in a start-up of the IC at approximately the same frequency as the external clock, so that when the sync signal comes alive, no discontinuity at the output will be observed. It also ensures that the operating frequency remains essentially constant in the event the sync signal is lost. The SYNC pin has an internal 50k resistor to ground.

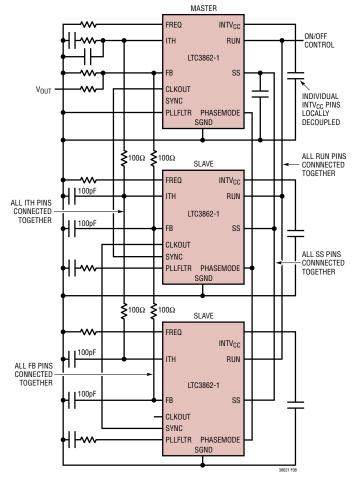

# Using the CLKOUT and PHASEMODE Pins in Multi-Phase Applications

The LTC3862-1 features two pins (CLKOUT and PHASE-MODE) that allow multiple ICs to be daisy-chained together for higher current multi-phase applications. For a 3- or 4-phase design, the CLKOUT signal of the master controller is connected to the SYNC input of the slave controller in order to synchronize additional power stages for a single high current output. The PHASEMODE pin is used to adjust the phase relationship between channel 1 and channel 2, as well as the phase relationship between channel 1 and CLKOUT, as summarized in Table 1. The phases are calculated relative to the zero degrees, defined as the rising edge of the GATE1 output. In a 6-phase application the CLKOUT pin of the master controller connects to the SYNC input of the 2nd controller and the CLKOUT pin of the 2nd controller connects to the SYNC pin of the 3rd controller.

Table 1

| PHASEMODE | CH-1 to CH-2<br>PHASE | CH-1 to CLKOUT<br>PHASE | APPLICATION      |

|-----------|-----------------------|-------------------------|------------------|

| SGND      | 180°                  | 90°                     | 2-Phase, 4-Phase |

| Float     | 180°                  | 60°                     | 6-Phase          |

| 3V8       | 120°                  | 240°                    | 3-Phase          |

#### Using the LTC3862-1 Transconductance (g<sub>m</sub>) Error Amplifier in Multi-Phase Applications

The LTC3862-1 error amplifier is a transconductance, or  $g_m$ amplifier, meaning that it has high DC gain but high output impedance (the output of the error amplifier is a current proportional to the differential input voltage). This style of error amplifier greatly eases the task of implementing a multi-phase solution, because the amplifiers from two or more chips can be connected in parallel. In this case the FB pins of multiple LTC3862-1s can be connected together, as well as the ITH pins, as shown in Figure 8. The g<sub>m</sub> of the composite error amplifier is simply n times the transconductance of one amplifier, or  $g_{m(TOT)} = n \cdot 660 \mu S$ , where n is the number of amplifiers connected in parallel. The transfer function from the ITH pin to the current comparator inputs was carefully designed to be accurate, both from channel-to-channel and chip-to-chip. This way the peak inductor current matching is kept accurate.

A buffered version of the output of the error amplifier determines the threshold at the input of the current comparator. The ITH voltage that represents zero peak current is 0.4V and the voltage that represents current limit is 1.2V (at low duty cycle). During an overload condition, the output of the error amplifier is clamped to 2.6V at low duty cycle, in order to reduce the latency when the overload condition terminates. A patented circuit in the LTC3862-1 is used to recover the slope compensation signal, so that the maximum peak inductor current is not a strong function of the duty cycle.

In multiphase applications that use more than one LTC3862-1 controller, it is possible for ground currents on the PCB to disturb the control lines between the ICs, resulting in erratic behavior. In these applications the FB pins should be connected to each other through  $100\Omega$  resistors and each slave FB pin should be decoupled locally with a 100pF capacitor to ground, as shown in Figure 8.

Figure 8. LTC3862-1 Error Amplifier Configuration for Multi-Phase Operation

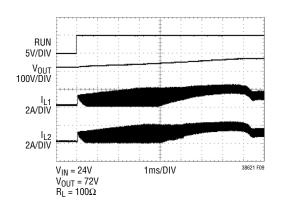

### Soft-Start

The start-up of the LTC3862-1 is controlled by the voltage on the SS pin. An internal PNP transistor clamps the current comparator sense threshold during soft-start, thereby limiting the peak switch current. The base of the PNP is connected to the SS pin and the emitter to an internal, buffered ITH node (please note that the ITH pin voltage may not track the soft-start voltage during this time period). An internal 5 $\mu$ A current source charges the SS capacitor, and clamps the peak sense threshold until the voltage on the soft-start capacitor reaches approximately 0.6V. The required amount of soft-start capacitance can be estimated using the following equation:

$$C_{SS} = 5\mu A \left( \frac{t_{SS}}{0.6V} \right)$$

(

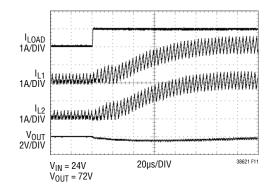

The SS pin has an internal open-drain NMOS pull-down transistor that turns on when the RUN pin is pulled low, when the voltage on the INTV<sub>CC</sub> pin is below its undervoltage lockout threshold, or during an overtemperature condition. In multi-phase applications that use more than one LTC3862-1 chip, connect all of the SS pins together and use one external capacitor to program the soft-start time. In this case, the current into the soft-start capacitor will be  $I_{SS} = n \cdot 5\mu A$ , where n is the number of SS pins connected together. Figure 9 illustrates the start-up waveforms for a 2-phase LTC3862-1 application.

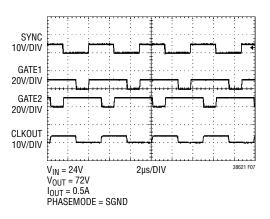

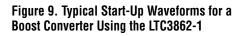

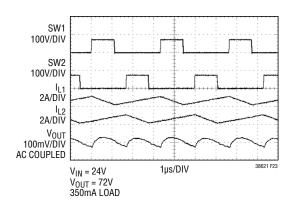

#### Pulse Skip Operation at Light Load

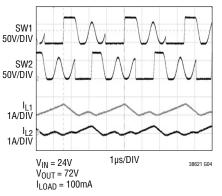

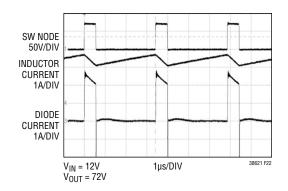

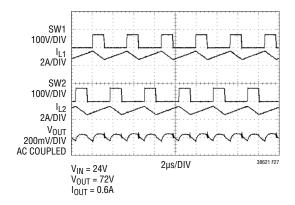

As the load current is decreased, the controller enters discontinuous mode (DCM). The peak inductor current can be reduced until the minimum on-time of the controller is reached. Any further decrease in the load current will cause pulse skipping to occur, in order to maintain output regulation, which is normal. The minimum on-time of the controller in this mode is approximately 210ns (with the blanking time set to its minimum value), the majority of which is leading edge blanking. Figure 10 illustrates the LTC3862-1 switching waveforms at the onset of pulse skipping.

#### Programmable Slope Compensation

For a current mode boost regulator operating in CCM, slope compensation must be added for duty cycles above 50%, in order to avoid sub-harmonic oscillation. For the

LTC3862-1, this ramp compensation is internal and user adjustable. Having an internally fixed ramp compensation waveform normally places some constraints on the value of the inductor and the operating frequency. For example, with a fixed amount of internal slope compensation, using an excessively large inductor would result in too much effective slope compensation, and the converter could become unstable. Likewise, if too small an inductor were used, the internal ramp compensation could be inadequate to prevent sub-harmonic oscillation.

The LTC3862-1 contains a pin that allows the user to program the slope compensation gain in order to optimize performance for a wider range of inductance. With the SLOPE pin left floating, the normalized slope gain is 1.00. Connecting the SLOPE pin to ground reduces the normalized gain to 0.625 and connecting this pin to the 3V8 supply increases the normalized slope gain to 1.66.

With the normalized slope compensation gain set to 1.00, the design equations assume an inductor ripple current of 20% to 40%, as with previous designs. Depending upon the application circuit, however, a normalized gain of 1.00 may not be optimum for the inductor chosen. If the ripple current in the inductor is greater than 40%, the normalized slope gain can be increased to 1.66 (an increase of 66%) by connecting the SLOPE pin to the 3V8 supply. If the inductor ripple current is less than 20%, the normalized slope gain can be reduced to 0.625 (a decrease of 37.5%) by connecting the SLOPE pin to SGND.

Figure 10. Light Load Switching Waveforms for the LTC3862-1 at the Onset of Pulse Skipping

To check the effectiveness of the slope compensation, apply a load step to the output and monitor the cycle-by-cycle behavior of the inductor current during the leading and trailing edges of the load current. Vary the input voltage over its full range and check for signs of cycle-by-cycle SW node instability or sub-harmonic oscillation. When the slope compensation is too low the converter can suffer from excessive jitter or, worst case, sub-harmonic oscillation. When excess slope compensation is applied to the internal current sense signal, the phase margin of the control loop suffers. Figure 11 illustrates inductor current waveforms for a properly compensated loop.

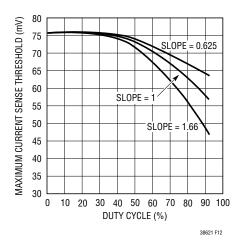

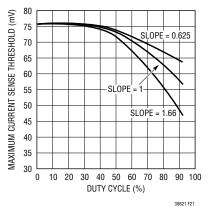

The LTC3862-1 contains a patented circuit whereby most of the applied slope compensation is recovered, in order to provide a SENSE<sup>+</sup> to SENSE<sup>-</sup> threshold which is not a strong function of the duty cycle. This sense threshold is, however, a function of the programmed slope gain, as shown in Figure 12. The data sheet typical specification of 75mV for SENSE<sup>+</sup> minus SENSE<sup>-</sup> is measured at a normalized slope gain of 1.00 at low duty cycle. For applications where the normalized slope gain is not 1.00, use Figure 12 to determine the correct value of the sense resistor.

#### Programmable Blanking and the Minimum On-Time

The BLANK pin on the LTC3862-1 allows the user to program the amount of leading edge blanking at the SENSE pins. Connecting the BLANK pin to SGND results in a minimum on-time of 210ns, floating the pin increases this time to 290ns, and connecting the BLANK pin to the

3V8 supply results in a minimum on-time of 375ns. The majority of the minimum on-time consists of this leading edge blanking, due to the inherently low propagation delay of the current comparator (25ns typ) and logic circuitry (10ns to 15ns).

The purpose of leading edge blanking is to filter out noise on the SENSE pins at the leading edge of the power MOSFET turn-on. During the turn-on of the power MOSFET the gate drive current, the discharge of any parasitic capacitance on the SW node, the recovery of the boost diode charge, and parasitic series inductance in the high di/dt path all contribute to overshoot and high frequency noise that could cause false-tripping of the current comparator. Due to the wide range of applications the LTC3862-1 is well-suited to, fixing one value of the internal leading edge blanking time would have required the longest delay time to have been used. Providing a means to program the blank time allows users to optimize the SENSE pin filtering for each application. Figure 13 illustrates the effect of the programmable leading edge blank time on the minimum on-time of a boost converter.

#### Programmable Maximum Duty Cycle

In order to maintain constant frequency and a low output ripple voltage, a single-ended boost (or flyback or SEPIC) converter is required to turn off the switch every cycle for some minimum amount of time. This off-time allows the transfer of energy from the inductor to the output capacitor and load, and prevents excessive ripple current

Figure 12. Effect of Slope Gain on the Peak SENSE Threshold

MINIMUM ON-TIME AT LIGHT LOAD WITH BLANK = SGND

MINIMUM ON-TIME AT LIGHT LOAD WITH BLANK = FLOAT

Figure 13. Leading Edge Blanking Effects on the Minimum On-Time

and voltage. For inductor-based topologies like boost and SEPIC converters, having a maximum duty cycle as close as possible to 100% may be desirable, especially in low  $V_{IN}$  to high  $V_{OUT}$  applications. However, for transformer-based solutions, having a maximum duty cycle near 100% is undesirable, due to the need for V • sec reset during the primary switch off-time.

84% MAXIMUM DUTY CYCLE WITH  $D_{MAX} = FLOAT$

Figure 14. SW Node Waveforms with Different Duty Cycle Limits

In order to satisfy these different applications requirements, the LTC3862-1 has a simple way to program the maximum duty cycle. Connecting the  $D_{MAX}$  pin to SGND limits the maximum duty cycle to 96%. Floating this pin limits the duty cycle to 84% and connecting the  $D_{MAX}$  pin to the 3V8 supply limits it to 75%. Figure 14 illustrates the effect of limiting the maximum duty cycle on the SW node waveform of a boost converter.

The LTC3862-1 contains an oscillator that runs at 12x the programmed switching frequency, in order to provide for 2-, 3-, 4-, 6- and 12-phase operation. A digital counter is used to divide down the fundamental oscillator frequency in order to obtain the operating frequency of the gate drivers. Since the maximum duty cycle limit is obtained from this digital counter, the percentage maximum duty cycle does not vary with process tolerances or temperature.

#### The SENSE<sup>+</sup> and SENSE<sup>-</sup> Pins

The SENSE<sup>+</sup> and SENSE<sup>-</sup> pins are high impedance inputs to the CMOS current comparators for each channel. Nominally, there is no DC current into or out of these pins. There are ESD protection diodes connected from these pins to SGND, although even at hot temperature the leakage current into the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins should be less than 1 $\mu$ A.

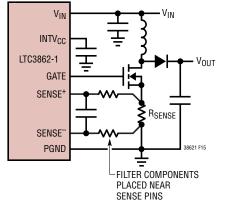

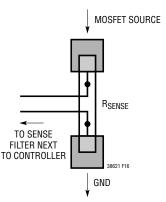

Since the LTC3862-1 contains leading edge blanking, an external RC filter is not required for proper operation. However, if an external filter is used, the filter components should be placed close to the SENSE<sup>+</sup> and SENSE<sup>-</sup> pins on the IC, as shown in Figure 15. The positive and negative sense node traces should then run parallel to each other to a Kelvin connection underneath the sense resistor, as shown in Figure 16. Sensing current elsewhere on the board can add parasitic inductance and capacitance to the current sense element, degrading the information at the sense pins and making the programmed current limit unpredictable. Avoid the temptation to connect the

SENSE<sup>-</sup> line to the ground plane using a PCB via; this could result in unpredictable behavior.

The sense resistor should be connected to the source of the power MOSFET and the ground node using short, wide PCB traces, as shown in Figure 16. Ideally, the bottom terminal of the sense resistors will be immediately adjacent to the negative terminal of the output capacitor, since this path is a part of the high di/dt loop formed by the switch, boost diode, output capacitor and sense resistor. Placement of the inductors is less critical, since the current in the inductors is a triangle waveform.

#### **Checking the Load Transient Response**

The regulator loop response can be checked by looking at the load current transient response. Switching regulators take several cycles to respond to a step in DC (resistive) load current. When a load step occurs, V<sub>OUT</sub> shifts by an amount equal to  $\Delta I_{LOAD}$  (ESR), where ESR is the effective series resistance of C<sub>OUT</sub>.  $\Delta I_{LOAD}$  also begins to charge or discharge C<sub>OUT</sub>, generating the feedback error signal that forces the regulator to adapt to the current change and return V<sub>OUT</sub> to its steady-state value. During this recovery time V<sub>OUT</sub> can be monitored for excessive overshoot or ringing, which would indicate a stability problem.

The availability of the ITH pin not only allows optimization of control loop behavior but also provides a DC-coupled and AC-filtered closed-loop response test point. The DC step, rise time and settling at this test point truly reflects the

Figure 15. Proper Current Sense Filter Component Placement

Figure 16. Connecting the SENSE<sup>+</sup> and SENSE<sup>-</sup> Traces to the Sense Resistor Using a Kelvin Connection

closed-loop response. Assuming a predominantly second order system, phase margin and/or damping factor can be estimated using the percentage of overshoot seen at this pin. The bandwidth can also be estimated by examining the rise time at the pin.

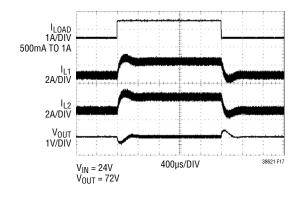

The ITH series  $R_C \cdot C_C$  filter sets the dominant pole-zero loop compensation. The transfer function for boost and flyback converters contains a right half plane zero that normally requires the loop crossover frequency to be reduced significantly in order to maintain good phase margin. The  $R_C \cdot C_C$  filter values can typically be modified slightly (from 0.5 to 2 times their suggested values) to optimize transient response once the final PC layout is done and the particular output capacitor type(s) and value(s) have been determined. The output capacitor configuration needs to be selected in advance because the effective ESR and bulk capacitance have a significant effect on the loop gain and phase. An output current pulse of 20% to 80% of full-load current having a rise time of 1µs to 10µs will produce output voltage and ITH pin waveforms that will give a sense of the overall loop stability without breaking the feedback loop. Placing a power MOSFET and load resistor directly across the output capacitor and driving the gate with an appropriate signal generator is a practical way to produce a fast load step condition. The initial output voltage step resulting from the step change in the output current may not be within the bandwidth of the feedback loop, so this signal cannot be used to determine phase margin. This is why it is better to look at the ITH pin signal which is in the feedback loop and is the filtered and compensated control loop response. The gain of the loop will be increased by increasing R<sub>C</sub> and the bandwidth of the loop will be increased by decreasing  $C_{C}$ . If  $R_{C}$  is increased by the same factor that C<sub>C</sub> is decreased, the zero frequency will be kept the same, thereby keeping the phase shift the same in the most critical frequency range of the feedback loop. The output voltage settling behavior is related to the stability of the closed-loop system and will demonstrate the actual overall supply performance. Figure 17 illustrates the load step response of a properly compensated boost converter.

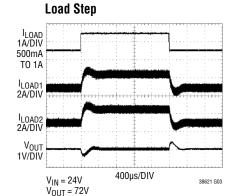

Figure 17: Load Step Response of a Properly Compensated Boost Converter

38621fz

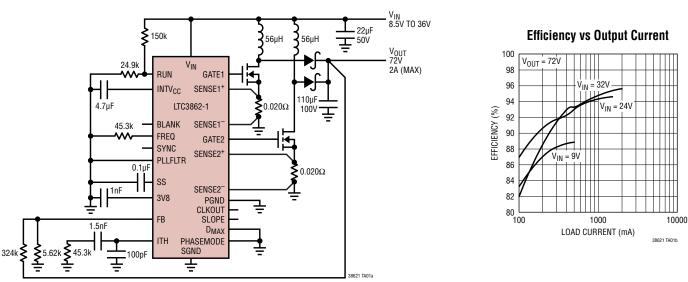

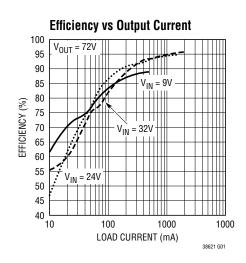

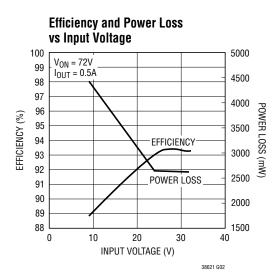

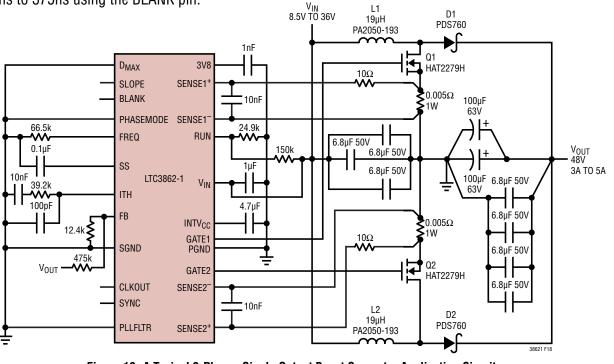

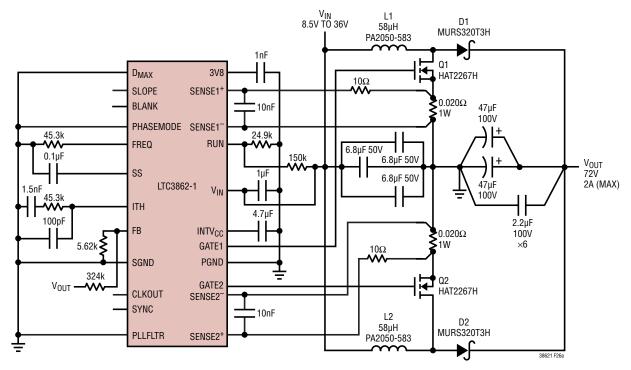

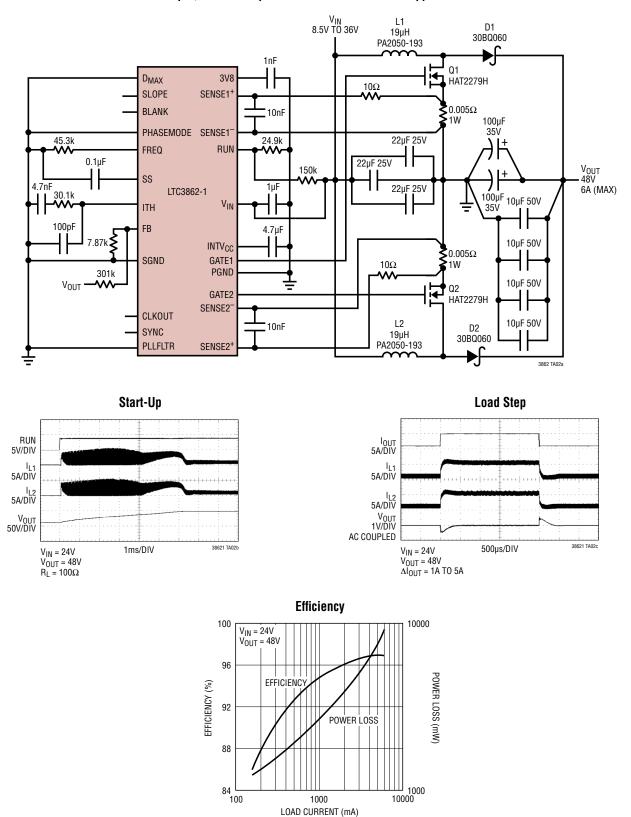

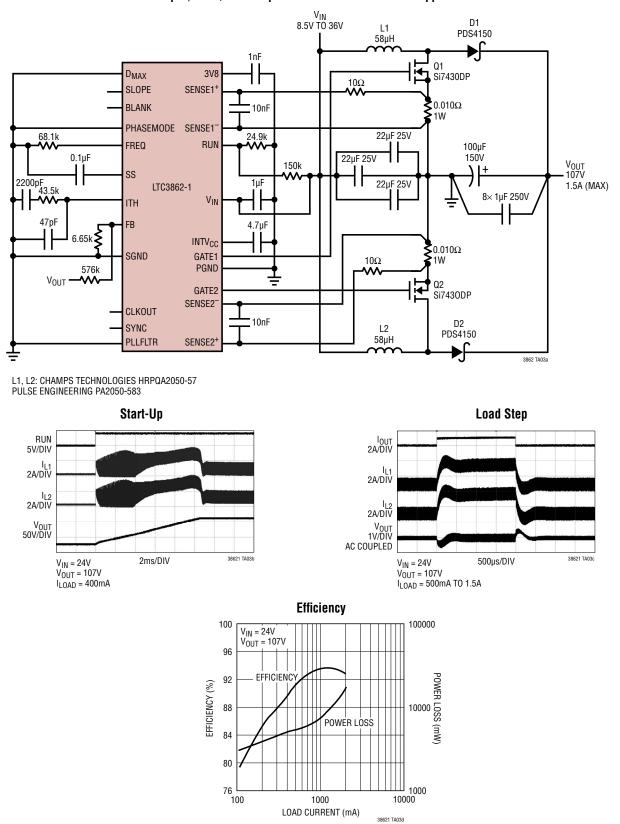

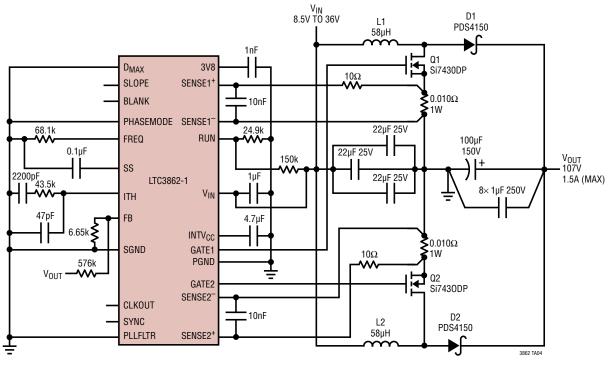

#### **Typical Boost Applications Circuit**

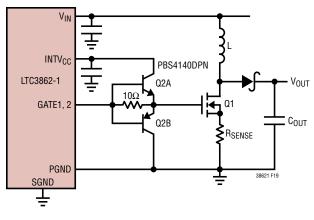

A basic 2-phase, single output LTC3862-1 application circuit is shown in Figure 18. External component selection is driven by the characteristics of the load and the input supply.

#### **Duty Cycle Considerations**

For a boost converter operating in a continuous conduction mode (CCM), the duty cycle of the main switch is:

$$D = \left(\frac{V_0 + V_F - V_{IN}}{V_0 + V_F}\right) = t_{ON} \bullet f$$

where  $V_{\text{F}}$  is the forward voltage of the boost diode. The minimum on-time for a given application operating in CCM is:

$$t_{ON(MIN)} = \frac{1}{f} \left( \frac{V_0 + V_F - V_{IN(MAX)}}{V_0 + V_F} \right)$$

For a given input voltage range and output voltage, it is important to know how close the minimum on-time of the application comes to the minimum on-time of the control IC. The LTC3862-1 minimum on-time can be programmed from 210ns to 375ns using the BLANK pin.

#### **Minimum On-Time Limitations**

In a single-ended boost converter, two steady-state conditions can result in operation at the minimum on-time of the controller. The first condition is when the input voltage is close to the output voltage. When  $V_{IN}$  approaches  $V_{OUT}$  the voltage across the inductor approaches zero during the switch off-time. Under this operating condition the converter can become unstable and the output can experience high ripple voltage oscillation at audible frequencies. For applications where the input voltage can approach or exceed the output voltage, consider using a SEPIC or buck-boost topology instead of a boost converter.

The second condition that can result in operation at the minimum on-time of the controller is at light load, in deep discontinuous mode. As the load current is decreased, the on-time of the switch decreases, until the minimum on-time limit of the controller is reached. Any further decrease in the output current will result in pulse skipping, a typically benign condition where cycles are skipped in order to maintain output regulation.

Figure 18. A Typical 2-Phase, Single Output Boost Converter Application Circuit

#### **Maximum Duty Cycle Limitations**

Another operating extreme occurs at high duty cycle, when the input voltage is low and the output voltage is high. In this case:

$$\mathsf{D}_{MAX} = \left(\frac{\mathsf{V}_{\mathsf{O}} + \mathsf{V}_{\mathsf{F}} - \mathsf{V}_{\mathsf{IN}(\mathsf{MIN})}}{\mathsf{V}_{\mathsf{O}} + \mathsf{V}_{\mathsf{F}}}\right)$$

A single-ended boost converter needs a minimum off-time every cycle in order to allow energy transfer from the input inductor to the output capacitor. This minimum off-time translates to a maximum duty cycle for the converter. The equation above can be rearranged to obtain the maximum output voltage for a given minimum input or maximum duty cycle.

$$V_{O(MAX)} = \frac{V_{IN}}{1 - D_{MAX}} - V_F$$

The equation for  $D_{MAX}$  above can be used as an initial guideline for determining the maximum duty cycle of the application circuit. However, losses in the inductor, input and output capacitors, the power MOSFETs, the sense resistors and the controller (gate drive losses) all contribute to an increasing of the duty cycle. The effect of these losses will be to *decrease* the maximum output voltage for a given minimum input voltage.

After the initial calculations have been completed for an application circuit, it is important to build a prototype of the circuit and measure it over the entire input voltage range, from light load to full load, and over temperature, in order to verify proper operation of the circuit.

#### Peak and Average Input Currents

The control circuit in the LTC3862-1 measures the input current (by means of resistors in the sources of the power MOSFETs), so the output current needs to be reflected back to the input in order to dimension the power MOSFETs properly. Based on the fact that, ideally, the output power is equal to the input power, the maximum average input current is:

$$I_{IN(MAX)} = \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

The peak current in each inductor is:

$$I_{IN(PK)} = \frac{1}{n} \bullet \left(1 + \frac{\chi}{2}\right) \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

where n represents the number of phases and  $\chi$  represents the percentage peak-to-peak ripple current in the inductor. For example, if the design goal is to have 30% ripple current in the inductor, then  $\chi = 0.30$ , and the peak current is 15% greater than the average.

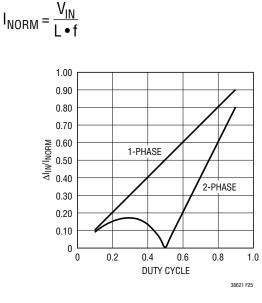

#### **Inductor Selection**

Given an input voltage range, operating frequency and ripple current, the inductor value can be determined using the following equation:

$$L = \frac{V_{IN(MIN)}}{\Delta I_{L} \bullet f} \bullet D_{MAX}$$

where:

$$\Delta I_{L} = \frac{\chi}{n} \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

Choosing a larger value of  $\Delta I_L$  allows the use of a lower value inductor but results in higher output voltage ripple, greater core losses, and higher ripple current ratings for the input and output capacitors. A reasonable starting point is 30% ripple current in the inductor ( $\chi = 0.3$ ), or:

$$\Delta I_{L} = \frac{0.3}{n} \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

The inductor saturation current rating needs to be higher than the worst-case peak inductor current during an overload condition. If  $I_{O(MAX)}$  is the maximum rated load current, then the maximum current limit value ( $I_{O(CL)}$ ) would normally be chosen to be some factor (e.g., 30%) greater than  $I_{O(MAX)}$ .

$$I_{O(CL)} = 1.3 \bullet I_{O(MAX)}$$

Reflecting this back to the input, where the current is being measured, and accounting for the ripple current, gives a minimum saturation current rating for the inductor of:

$$I_{L(SAT)} \ge \frac{1}{n} \bullet \left(1 + \frac{\chi}{2}\right) \bullet \frac{1.3 \bullet I_{O(MAX)}}{1 - D_{MAX}}$$

The saturation current rating for the inductor should be determined at the minimum input voltage (which results in the highest duty cycle and maximum input current), maximum output current and the maximum expected core temperature. The saturation current ratings for most commercially available inductors drop at high temperature. To verify safe operation, it is a good idea to characterize the inductor's core/winding temperature under the following conditions: 1) worst-case operating conditions, 2) maximum allowable ambient temperature and 3) with the power supply mounted in the final enclosure. Thermal characterization can be done by placing a thermocouple in intimate contact with the winding/core structure, or by burying the thermocouple within the windings themselves.

Remember that a single-ended boost converter is **not** short-circuit protected, and that under a shorted output condition, the output current is limited only by the input supply capability. For applications requiring a step-up converter that is short-circuit protected, consider using a SEPIC or forward converter topology.

#### **Power MOSFET Selection**

The peak-to-peak gate drive level is set by the INTV<sub>CC</sub> voltage is 10V for the LTC3862-1 under normal operating conditions. Selection criteria for the power MOSFETs include the R<sub>DS(ON)</sub>, gate charge Q<sub>G</sub>, drain-to-source breakdown voltage BV<sub>DSS</sub>, maximum continuous drain current I<sub>D(MAX)</sub>, and thermal resistances R<sub>TH(JA)</sub> and R<sub>TH(JC)</sub>—both junction-to-ambient and junction-to-case.

The gate driver for the LTC3862-1 consists of PMOS pullup and NMOS pull-down devices, allowing the full INTV<sub>CC</sub> voltage to be applied to the gates during power MOSFET switching. Nonetheless, care must be taken to ensure that the minimum gate drive voltage is still sufficient to full enhance the power MOSFET. Check the MOSFET data sheet carefully to verify that the R<sub>DS(ON)</sub> of the MOSFET is specified for a voltage less than or equal to the nominal  $\rm INTV_{CC}$  voltage of 10V. For applications that require a power MOSFET rated at 5V, please refer to the LTC3862 data sheet.

Also pay close attention to the  $BV_{DSS}$  specifications for the MOSFETs relative to the maximum actual switch voltage in the application. Check the switching waveforms of the MOSFET directly on the drain terminal using a single probe and a high bandwidth oscilloscope. Ensure that the drain voltage ringing does not approach the  $BV_{DSS}$  of the MOSFET. Excessive ringing at high frequency is normally an indicator of too much series inductance in the high di/ dt current path that includes the MOSFET, the boost diode, the output capacitor, the sense resistor and the PCB traces connecting these components.

The GATE of MOSFET Q1 could experience transient voltage spikes during turn-on and turn-off of the MOSFET, due to parasitic lead inductance and improper PCB layout. These voltage spikes could exceed the absolute maximum voltage rating of LTC3862-1's GATE pin. The GATE pins are rated for an absolute maximum voltage of –0.3V minimum and 11V maximum. Hence it is recommended to add an external buffer close to the GATE of the MOSFET as shown in Figure 19.

Figure 19. External Buffer Circuit

Finally, check the MOSFET manufacturer's data sheet for an avalanche energy rating (EAS). Some MOSFETs are not rated for body diode avalanche and will fail catastrophically if the  $V_{DS}$  exceeds the device  $BV_{DSS}$ , even if only by a fraction of a volt. Avalanche-rated MOSFETs are better able to sustain high frequency drain-to-source ringing near the device  $BV_{DSS}$  during the turn-off transition.

# Calculating Power MOSFET Switching and Conduction Losses and Junction Temperatures

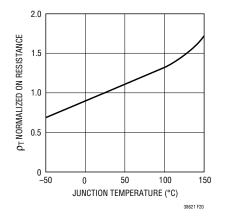

In order to calculate the junction temperature of the power MOSFET, the power dissipated by the device must be known. This power dissipation is a function of the duty cycle, the load current and the junction temperature itself (due to the positive temperature coefficient of its  $R_{DS(ON)}$ ). As a result, some iterative calculation is normally required to determine a reasonably accurate value.

The power dissipated by the MOSFET in a multi-phase boost converter with n phases is:

$$P_{FET} = \left(\frac{I_{O(MAX)}}{n \cdot (1 - D_{MAX})}\right)^{2} \cdot R_{DS(ON)} \cdot D_{MAX} \cdot \rho_{T}$$

$$+ k \cdot V_{OUT}^{2} \cdot \frac{I_{O(MAX)}}{n \cdot (1 - D_{MAX})} \cdot C_{RSS} \cdot f$$

The first term in the equation above represents the  $I^2R$  losses in the device, and the second term, the switching losses. The constant, k = 1.7, is an empirical factor inversely related to the gate drive current and has the dimension of 1/current.

The  $\rho_T$  term accounts for the temperature coefficient of the R<sub>DS(ON)</sub> of the MOSFET, which is typically 0.4%/°C. Figure 20 illustrates the variation of normalized R<sub>DS(ON)</sub> over temperature for a typical power MOSFET.

Figure 20. Normalized Power MOSFET R<sub>DS(ON)</sub> vs Temperature

From a known power dissipated in the power MOSFET, its junction temperature can be obtained using the following formula:

$T_J = T_A + P_{FET} \bullet R_{TH(JA)}$

The  $R_{TH(JA)}$  to be used in this equation normally includes the  $R_{TH(JC)}$  for the device plus the thermal resistance from the case to the ambient temperature ( $R_{TH(CA)}$ ). This value of  $T_J$  can then be compared to the original, assumed value used in the iterative calculation process.

It is tempting to choose a power MOSFET with a very low  $R_{DS(ON)}$  in order to reduce conduction losses. In doing so, however, the gate charge  $Q_G$  is usually significantly higher, which increases switching and gate drive losses. Since the switching losses increase with the square of the output voltage, applications with a low output voltage generally have higher MOSFET conduction losses, and high output voltage applications generally have higher MOSFET switching losses. At high output voltages, the highest efficiency is usually obtained by using a MOSFET with a higher  $R_{DS(ON)}$  and lower  $Q_G$ . The equation above can easily be split into two components (conduction and switching) and entered into a spreadsheet, in order to compare the performance of different MOSFETs.

#### **Programming the Current Limit**

The peak sense voltage threshold for the LTC3862-1 is 75mV at low duty cycle and with a normalized slope gain of 1.00, and is measured from SENSE<sup>+</sup> to SENSE<sup>-</sup>. Figure 21 illustrates the change in the sense threshold with varying duty cycle and slope gain.

Figure 21. Maximum Sense Voltage Variation with Duty Cycle and Slope Gain

For a boost converter where the current limit value is chosen to be 30% higher than the maximum load current, the peak current in the MOSFET and sense resistor is:

$$I_{SW(MAX)} = I_{R(SENSE)} = \frac{1}{n} \bullet \left(1 + \frac{\chi}{2}\right) \bullet \frac{1.3 \bullet I_{O(MAX)}}{1 - D_{MAX}}$$

The sense resistor value is then:

$$\mathsf{R}_{\mathsf{SENSE}} = \frac{\mathsf{V}_{\mathsf{SENSE}(\mathsf{MAX})} \bullet \mathsf{n} \bullet (1 - \mathsf{D}_{\mathsf{MAX}})}{1.3 \bullet \left(1 + \frac{\chi}{2}\right) \bullet \mathsf{I}_{\mathsf{O}(\mathsf{MAX})}}$$

Again, the factor n is the number of phases used, and  $\chi$  represents the percentage ripple current in the inductor. The number 1.3 represents the factor by which the current limit exceeds the maximum load current,  $I_{O(MAX)}$ . For example, if the current limit needs to exceed the maximum load current by 50%, then the 1.3 factor should be replaced with 1.5.

The average power dissipated in the sense resistor can easily be calculated as:

$$P_{R(SENSE)} = \left(\frac{1.3 \bullet I_{O(MAX)}}{n \bullet (1 - D_{MAX})}\right)^2 \bullet R_{SENSE} \bullet D_{MAX}$$

This equation assumes no temperature coefficient for the sense resistor. If the resistor chosen has a significant temperature coefficient, then substitute the worst-case high resistance value into the equation.

The resistor temperature can be calculated using the equation:

$T_{D} = T_{A} + P_{R(SENSE)} \bullet R_{TH(JA)}$

#### **Selecting the Output Diodes**

To maximize efficiency, a fast switching diode with low forward drop and low reverse leakage is required. The output diode in a boost converter conducts current during the switch off-time. The peak reverse voltage that the diode must withstand is equal to the regulator output voltage. The average forward current in normal operation is equal to the output current, and the peak current is equal to the peak inductor current:

$$I_{D(PEAK)} = \frac{1}{n} \bullet \left(1 + \frac{\chi}{2}\right) \bullet \frac{I_{O(MAX)}}{1 - D_{MAX}}$$

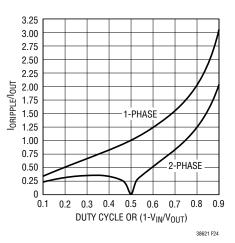

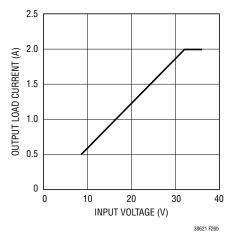

Although the average diode current is equal to the output current, in very high duty cycle applications (low  $V_{IN}$  to high  $V_{OUT}$ ) the peak diode current can be several times higher than the average, as shown in Figure 22. In this case check the diode manufacturer's data sheet to ensure that its peak current rating exceeds the peak current in the equation above. In addition, when calculating the power dissipation in the diode, use the value of the for-

Figure 22. Diode Current Waveform for a High Duty Cycle Application