### LTC3625/LTC3625-1

1A High Efficiency 2-Cell Supercapacitor Charger with Automatic Cell Balancing

### FEATURES

- High Efficiency Step-Up/Step-Down Charging of Two Series Supercapacitors

- Automatic Cell Balancing Prevents Capacitor Overvoltage During Charging

- Programmable Charging Current Up to 500mA (Single Inductor), 1A (Dual Inductor)

- V<sub>IN</sub> = 2.7V to 5.5V

- Selectable 2.4V/2.65V Regulation per Cell (LTC3625)

- Selectable 2V/2.25V Regulation per Cell (LTC3625-1)

- Low No-Load Quiescent Current: 23µA

- IVOUT, IVIN < 1µA in Shutdown</p>

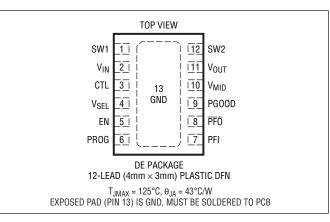

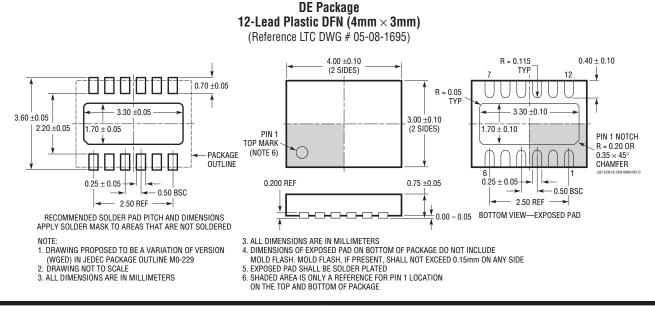

- Low Profile 12-lead 3mm × 4mm DFN Package

### **APPLICATIONS**

- Servers, RAID Systems, Mass Storage, High Current Backup Supplies

- Solid State Hard Drives

- Wireless Power Meters

- High Peak Power Boosted Supplies

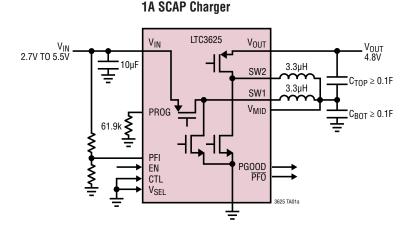

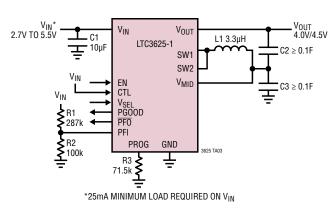

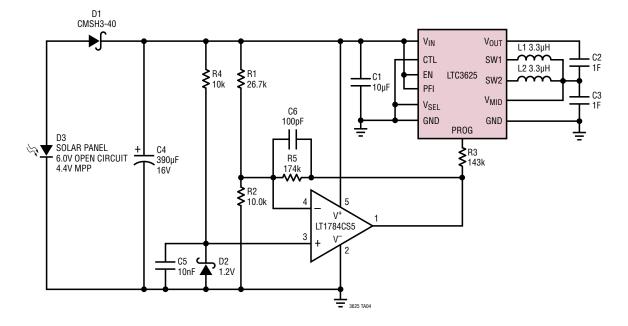

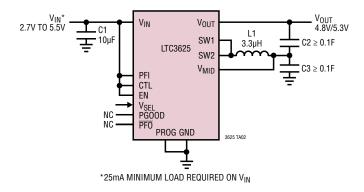

### TYPICAL APPLICATION

### DESCRIPTION

The LTC<sup>®</sup>3625/LTC3625-1 are programmable supercapacitor chargers designed to charge two supercapacitors in series to a fixed output voltage (4.8V/5.3V or 4V/4.5V selectable) from a 2.7V to 5.5V input supply. Automatic cell balancing prevents overvoltage damage to either supercapacitor while maximizing charge rate. No balancing resistors are required.

High efficiency, high charging current, low quiescent current and low minimum external parts count (one inductor, one bypass capacitor at  $V_{IN}$  and one programming resistor) make the LTC3625/LTC3625-1 ideally suited for small form factor backup or high peak power systems.

Charging current/maximum input current level is programmed with an external resistor. When the input supply is removed and/or the EN pin is low, the LTC3625/LTC3625-1 automatically enter a low current state, drawing less than  $1\mu$ A from the supercapacitors.

The LTC3625/LTC3625-1 are available in a compact 12-lead 3mm  $\times\,4mm\times0.75mm$  DFN package.

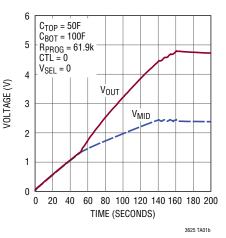

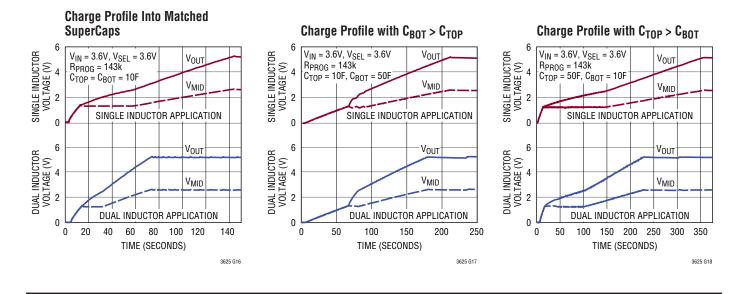

#### Charging Two 2:1 Mismatched Supercapacitors

### **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                                                            |                                |

|-------------------------------------------------------------------------------------|--------------------------------|

| V <sub>IN</sub> , V <sub>OUT</sub> (Transient) t < 1ms,                             |                                |

| Duty Cycle < 1%                                                                     | 0.3V to 7V                     |

| V <sub>IN</sub> , V <sub>OUT</sub> , V <sub>MID</sub> , PGOOD,                      |                                |

| CTL, PROG, PFI, PFO                                                                 | 0.3V to 6V                     |

| EN, V <sub>SEL</sub> –(                                                             | 0.3V to V <sub>IN</sub> + 0.3V |

| V <sub>OUT</sub> Short-Circuit Duration                                             | Indefinite                     |

| I <sub>PGOOD</sub> , I <u>PFO</u>                                                   | 50mA                           |

| I <sub>PROG</sub>                                                                   | 1mA                            |

| I <sub>VIN</sub> , I <sub>SW1</sub> , I <sub>SW2</sub> , I <sub>VOUT</sub> (Note 2) | 3A                             |

| Operating Junction Temperature Range                                                | е                              |

| (Notes 3, 4)                                                                        | –40°C to 125°C                 |

| Storage Temperature Range                                                           | –65°C to 125°C                 |

|                                                                                     |                                |

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC3625EDE#PBF   | LTC3625EDE#TRPBF   | 3625          | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC3625EDE-1#PBF | LTC3625EDE-1#TRPBF | 36251         | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC3625IDE#PBF   | LTC3625IDE#TRPBF   | 3625          | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC3625IDE-1#PBF | LTC3625IDE-1#TRPBF | 36251         | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating

| junction temperature range, otherwise specifications are at T |                                                                             | 4 4 6 1 1 1 1 |          |

|---------------------------------------------------------------|-----------------------------------------------------------------------------|---------------|----------|

|                                                               |                                                                             |               |          |

| INTERNET FOR TABLE TABLE TO DELWISE SUFFICIENT AT A TEAT I    | $A = Z_{2}$ $U_{1}$ $V_{1}$ $N = 0$ $U_{2}$ $D_{2}$ $D_{2}$ $D_{2}$ $C = 0$ |               | SUBLIDED |

|                                                               |                                                                             |               |          |

|                                                               |                                                                             |               |          |

| SYMBOL                              | PARAMETER                                                           | CONDITIONS                                                                                                |             | MIN                      | ТҮР                        | MAX                        | UNITS            |

|-------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------|--------------------------|----------------------------|----------------------------|------------------|

| V <sub>IN</sub>                     | Input Voltage Range                                                 |                                                                                                           |             | V <sub>IN(UVLO)</sub>    |                            | 5.5                        | V                |

| V <sub>IN(UVLO)</sub>               | Input Undervoltage Lockout<br>(V <sub>IN</sub> Rising)              | $V_{SEL} = V_{IN} (LTC3625)$<br>$V_{SEL} = 0V (LTC3625)$<br>$V_{SEL} = 0V \text{ or } V_{IN} (LTC3625-1)$ | •           | 2.8<br>2.53<br>2.53      | 2.9<br>2.63<br>2.63        | 3.0<br>2.73<br>2.73        | V<br>V<br>V      |

|                                     | Input UVLO Hysteresis                                               |                                                                                                           |             |                          | 100                        |                            | mV               |

| V <sub>OUT(SLEEP)</sub>             | Charger Termination Voltage                                         |                                                                                                           | •<br>•<br>• | 5.2<br>4.7<br>4.4<br>3.9 | 5.3<br>4.8<br>4.5<br>4.0   | 5.4<br>4.9<br>4.6<br>4.1   | V<br>V<br>V<br>V |

|                                     | Recharge Hysteresis                                                 | Below V <sub>OUT(SLEEP)</sub>                                                                             |             |                          | 135                        |                            | mV               |

| V <sub>TOP</sub> , V <sub>BOT</sub> | Maximum Voltage Across Either of the Supercapacitors After Charging |                                                                                                           | •<br>•<br>• |                          | 2.7<br>2.45<br>2.3<br>2.05 | 2.75<br>2.5<br>2.35<br>2.1 | V<br>V<br>V<br>V |

|                                     | Maximum Supercapacitor Offset<br>After Charging                     | CTL = 0V<br>CTL = V <sub>IN</sub>                                                                         |             |                          | 100<br>50                  | 180<br>120                 | mV<br>mV         |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>IN</sub> = 3.6V, R<sub>PROG</sub> = 143k, unless otherwise specified.

| SYMBOL                            | PARAMETER                                                                                                                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                              |   | MIN          | ТҮР                     | MAX               | UNITS          |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|-------------------------|-------------------|----------------|

| I <sub>VIN</sub>                  | Input Operating Current,<br>$I_{SW1} = I_{SW2} = 0\mu A$ , No Switching                                                  | $\begin{array}{l} \text{CTL} = \text{V}_{\text{IN}}, \text{V}_{\text{MID}} = 1.5\text{V}, \text{V}_{\text{OUT}} = 2.5\text{V} \text{ (Boost Only)} \\ \text{CTL} = \text{V}_{\text{IN}}, \text{V}_{\text{MID}} = 1.5\text{V}, \text{V}_{\text{OUT}} = 3.5\text{V} \text{ (Buck Only)} \\ \text{CTL} = 0, \text{V}_{\text{MID}} = 1.5\text{V}, \text{V}_{\text{OUT}} = 2.5\text{V} \text{ (Buck and Boost)} \end{array}$ |   |              | 135<br>275<br>365       | 200<br>400<br>530 | μΑ<br>μΑ<br>μΑ |

|                                   | Input Sleep Current                                                                                                      | $V_{IN} = 5.5V$ , $V_{OUT} = 5.4V$<br>$V_{IN} = 3.6V$ , $V_{OUT} = 5.4V$                                                                                                                                                                                                                                                                                                                                                |   |              | 23<br>8                 | 35<br>15          | μΑ<br>μΑ       |

|                                   | Input SD Current                                                                                                         | V <sub>OUT</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                   |   |              | 0                       | 1                 | μA             |

| Ivout                             | V <sub>OUT</sub> SD Current                                                                                              | $V_{OUT} = 5.4V$                                                                                                                                                                                                                                                                                                                                                                                                        |   |              | 0                       | 1                 | μA             |

|                                   | V <sub>OUT</sub> Sleep Current                                                                                           | $V_{OUT} = 5.4$ V, $V_{IN} = 3.6$ V, $EN = V_{IN}$<br>$V_{OUT} = 5.4$ V, $V_{IN} = 5.5$ V, $EN = V_{IN}$                                                                                                                                                                                                                                                                                                                |   |              | 17<br>1                 | 25<br>2.5         | μA<br>μA       |

| V <sub>PROG</sub>                 | PROG Servo Voltage                                                                                                       | V <sub>OUT</sub> = 3.5V, V <sub>MID</sub> = 1.5V                                                                                                                                                                                                                                                                                                                                                                        | • | 1.17         | 1.2                     | 1.23              | V              |

| h <sub>PROG</sub>                 | Ratio of Measured I <sub>PROG</sub> Current to I <sub>BUCK</sub> Programmed Current                                      |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 118,000                 |                   |                |

| IBUCK                             | Programmed Buck Charge Current                                                                                           | R <sub>PROG</sub> = 143k (Note 5)<br>R <sub>PROG</sub> = 71.5k (Note 5)                                                                                                                                                                                                                                                                                                                                                 |   | 0.88<br>1.76 | 0.99<br>1.98            | 1.10<br>2.20      | A<br>A         |

| I <sub>MAX</sub>                  | Maximum Programmed Charge<br>Current                                                                                     | $R_{PROG} = 0\Omega$ (Fault Condition) (Note 5)                                                                                                                                                                                                                                                                                                                                                                         |   | 1.98         | 2.65                    | 3.31              | A              |

| V <sub>MID(GOOD)</sub>            | V <sub>MID</sub> Voltage Where the Boost<br>Regulator is Enabled                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 1.35                    |                   | V              |

|                                   | V <sub>MID(GOOD)</sub> Hysteresis                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 150                     |                   | mV             |

| V <sub>TRICKLE</sub>              | V <sub>OUT</sub> Voltage Above Which Boost<br>Regulator Will Exit Trickle Charge<br>Mode and Enter Normal Charge<br>Mode | V <sub>OUT</sub> Rising                                                                                                                                                                                                                                                                                                                                                                                                 |   |              | V <sub>MID</sub>        |                   | V              |

|                                   | V <sub>TRICKLE</sub> Falling Hysteresis                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 50                      |                   | mV             |

| IPEAK(BUCK)                       | Buck Charge Current Peak                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 1.1 • I <sub>BUCK</sub> |                   | A              |

| VALLEY(BUCK)                      | Buck Charge Current Valley                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 0.9 • I <sub>BUCK</sub> |                   | A              |

| I <sub>PEAK(BOOST)</sub>          | Boost Charge Current Peak                                                                                                | $V_{OUT} = 3V$ , $V_{MID} = 2V$ (Note 5)<br>$V_{OUT} = 1V$ , $V_{MID} = 2V$ (Note 5)                                                                                                                                                                                                                                                                                                                                    |   | 1.59         | 2.12<br>200             | 2.65              | A<br>mA        |

| IVALLEY(BOOST)                    | Boost Charge Current Valley                                                                                              | $V_{OUT} = 3V$ , $V_{MID} = 2V$<br>$V_{OUT} = 1V$ , $V_{MID} = 2V$                                                                                                                                                                                                                                                                                                                                                      |   | 1.41         | 1.88<br>0               | 2.35              | A<br>mA        |

|                                   | Maximum Boost Valley Time                                                                                                | $V_{OUT} = 1V, V_{MID} = 2V$                                                                                                                                                                                                                                                                                                                                                                                            |   |              | 6.5                     |                   | μs             |

| R <sub>PMOS</sub>                 | PMOS On-Resistance                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 120                     |                   | mΩ             |

| R <sub>NMOS</sub>                 | NMOS On-Resistance                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 100                     |                   | mΩ             |

| ILEAK                             | SW Pin Leakage Current for SW1, SW2                                                                                      | EN = 0V                                                                                                                                                                                                                                                                                                                                                                                                                 |   |              |                         | 1                 | μA             |

| V <sub>PFI</sub>                  | PFI Falling Threshold                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                         | • | 1.17         | 1.2                     | 1.23              | V              |

|                                   | PFI Hysteresis                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 15                      |                   | mV             |

| IPFI                              | Pin Leakage Current for PFI Pin                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 0                       | 30                | nA             |

| Logic (EN, CTI                    | L, V <sub>SEL</sub> , PGOOD, PFO)                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              |                         |                   |                |

| V <sub>IL</sub>                   | Input Low Logic Voltage                                                                                                  | EN, CTL, V <sub>SEL</sub> Pins                                                                                                                                                                                                                                                                                                                                                                                          | • |              |                         | 0.4               | V              |

| V <sub>IH</sub>                   | Input High Logic Voltage                                                                                                 | EN, CTL, V <sub>SEL</sub> Pins                                                                                                                                                                                                                                                                                                                                                                                          | • | 1.2          |                         |                   | V              |

| I <sub>IL</sub> , I <sub>IH</sub> | Input Low, High Current for CTL                                                                                          | CTL                                                                                                                                                                                                                                                                                                                                                                                                                     |   |              |                         | 1                 | μA             |

| R <sub>PD</sub>                   | EN Pin Pull-Down Resistance                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                         |   |              | 4.5                     |                   | MΩ             |

|                                   | V <sub>SEL</sub> Pin Pull-Down Resistance                                                                                | EN = V <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                    |   |              | 4.5                     |                   | MΩ             |

| V <sub>OL</sub>                   | Output Low Logic Voltage                                                                                                 | PGOOD, PFO Pins; Sinking 5mA                                                                                                                                                                                                                                                                                                                                                                                            |   |              | 70                      | 200               | mV             |

| I <sub>OH</sub>                   | Logic High Leakage Current                                                                                               | PGOOD, PFO Pins; Pin Voltage = 5V                                                                                                                                                                                                                                                                                                                                                                                       |   |              |                         | 1                 | μA             |

|                                   | PGOOD Rising Threshold                                                                                                   | V <sub>OUT</sub> as a Percentage of Final Target                                                                                                                                                                                                                                                                                                                                                                        |   | 90           | 92.5                    | 95                | %              |

|                                   | PG00D Hysteresis                                                                                                         | $\Delta V_{OUT}$ as a Percentage of Final Target                                                                                                                                                                                                                                                                                                                                                                        |   |              | 3                       |                   | %              |

## LTC3625/LTC3625-1

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3625/LTC3625-1 internal switches are guaranteed to survive up to 3A of peak current. Internal current limits will restrict peak current to lower levels.

**Note 3:** The LTC3625/LTC3625-1 are tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3625E/LTC3625E-1 are guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3625I/LTC3625I-1 are guaranteed over the –40°C to 125°C operating junction temperature range.

The junction temperature (T<sub>J</sub> in °C) is calculated from the ambient temperature (T<sub>A</sub> in °C) and power dissipation (P<sub>D</sub> in Watts) according to the formula:

$$\mathsf{T}_\mathsf{J} = \mathsf{T}_\mathsf{A} + (\mathsf{P}_\mathsf{D} \bullet \theta_\mathsf{J} \mathsf{A})$$

where  $\theta_{JA}$  (in °C/W) is the package thermal impedance.

**Note 4:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability or permanently damage the device.

Note 5: Measurements are tested with CTL = 0V.

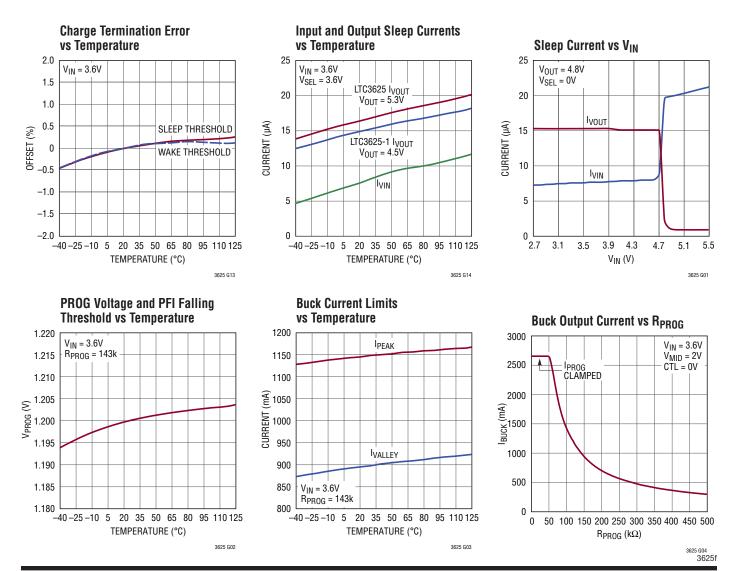

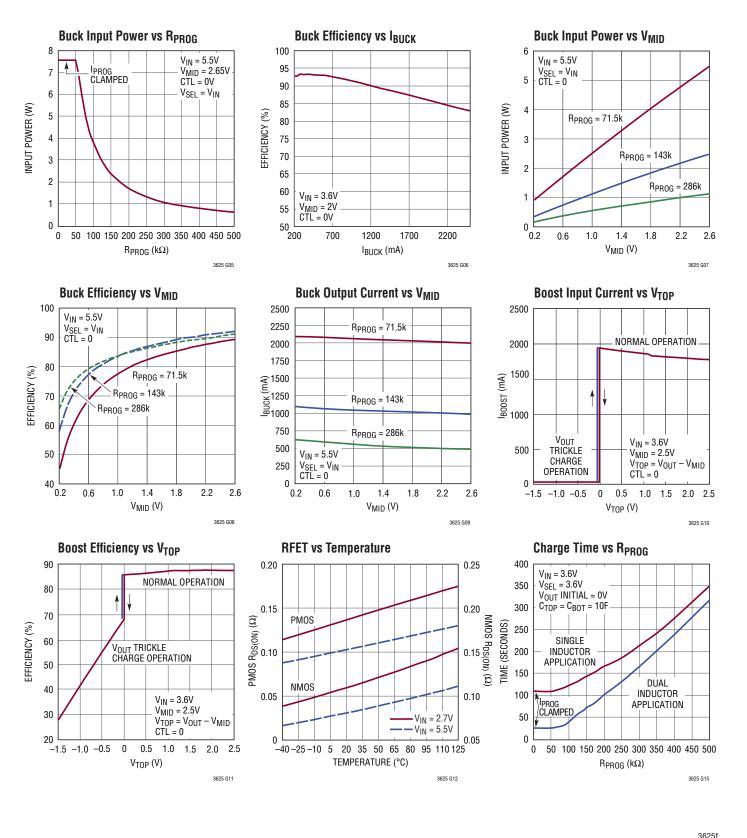

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25^{\circ}C$ ,  $L1 = 3.3\mu$ H,  $L2 = 3.3\mu$ H,  $C_{IN} = 10\mu$ F,  $C_{TOP} = C_{BOT}$ , LTC3625 unless otherwise specified.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}C$ ,  $L1 = 3.3\mu$ H,  $L2 = 3.3\mu$ H,  $C_{IN} = 10\mu$ F,  $C_{TOP} = C_{BOT}$ , LTC3625 unless otherwise specified.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$T_A = 25^{\circ}C$ , L1 = 3.3µH, L2 = 3.3µH,  $C_{IN} = 10$ µF,  $C_{TOP} = C_{BOT}$ , LTC3625 unless otherwise specified.

### PIN FUNCTIONS

**SW1 (Pin 1):** Switch Pin for the Buck Regulator. External inductor connects between SW1 pin and V<sub>MID</sub>.

$V_{IN}$  (Pin 2): Input Voltage Pin. Bypass to GND with a 10µF or larger ceramic capacitor.

**CTL (Pin 3):** Logic Input. CTL sets the charge mode of the LTC3625/LTC3625-1. A logic high at CTL programs the part to operate with a single inductor; a logic low programs the part to operate with two inductors. In the 2-inductor application the capacitor stack will charge approximately twice as quickly. CTL is a high impedance input and must be tied to either  $V_{IN}$  or GND. Do not float.

**V**<sub>SEL</sub> (**Pin 4**): Logic Input. V<sub>SEL</sub> selects the output voltage of the LTC3625/LTC3625-1. A logic low at V<sub>SEL</sub> sets the per-cell maximum voltage to 2.45V/2.05V (V<sub>OUT</sub> = 4.8V/4.0V); a logic high sets the per-cell maximum voltage to 2.70V/2.30V (V<sub>OUT</sub> = 5.3V/4.5V). When the part is enabled, V<sub>SEL</sub> has a  $4.5M\Omega$  internal pull-down resistor; if EN is low, then V<sub>SEL</sub> is a high impedance input pin.

**EN (Pin 5):** Logic Input. Enables the LTC3625/LTC3625-1. Active high. Has a  $4.5M\Omega$  internal pull-down resistor.

**PROG (Pin 6):** Charge Current Program Pin. Connecting a resistor from PROG to ground programs the buck output current. This pin servos to 1.2V.

**PFI (Pin 7):** Input to the Power Fail Comparator. This pin connects to an external resistor divider between  $V_{IN}$  and GND. If this functionality is not desired, PFI should be tied to  $V_{IN}$ .

**PFO** (Pin 8): Open-Drain Output of the Power-Fail Comparator. The part pulls this pin low if  $V_{IN}$  is less than a value programmed by an external divider. This pin is active low in shutdown mode. If this functionality is not desired  $\overline{PFO}$  should be left unconnected.

**PGOOD (Pin 9):** Logic Output. This is an open-drain output which indicates that  $V_{OUT}$  has settled to its final value. Upon start-up, this pin remains low until the output voltage,  $V_{OUT}$ , is within 92.5% (typical) of its final value. Once  $V_{OUT}$  is valid, PGOOD becomes high impedance. If  $V_{OUT}$  falls to 89.5% (typical) of its correct regulation level, PGOOD is pulled low. PGOOD may be pulled up through an external resistor to an appropriate reference level. This pin is active low in shutdown mode.

### PIN FUNCTIONS

V<sub>MID</sub> (Pin 10): Midpoint of Two Series Supercapacitors. The pin voltage is monitored and used, along with  $V_{OUT}$ , to enable or shut down the buck and boost converters during charging to achieve voltage balancing of the top and bottom supercapacitors.

Vout (Pin 11): Output Voltage Pin. Connect VOUT to the positive terminal of the top supercapacitor. The pin voltage is monitored and used, along with  $V_{MID}$ , to enable or shut down the buck and boost converters during charging to achieve voltage balancing of the top and bottom supercapacitors.

SW2 (Pin 12): Switch Pin for the Boost Regulator. External inductor connects between the SW2 pin and  $V_{MID}$ . If CTL is logic high, then SW2 must be connected to SW1.

GND (Exposed Pad Pin 13): Ground. The exposed pad must be connected to a continuous ground plane on the printed circuit board directly under the LTC3625/ LTC3625-1 for electrical contact and to achieve rated thermal performance.

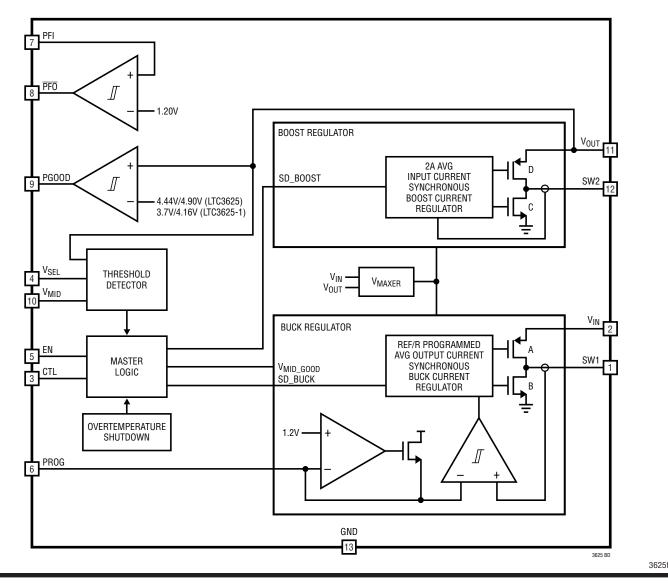

### **BLOCK DIAGRAM**

# OPERATION

The LTC3625/LTC3625-1 are dual cell supercapacitor chargers. Their unique topology charges two series connected capacitors to a fixed output voltage with programmable charging current without overvoltaging either of the cells —even if they are severely mismatched. No balancing resistors are required. The LTC3625/LTC3625-1 include an internal buck converter between  $V_{IN}$  and  $V_{MID}$  to regulate the voltage on  $C_{BOT}$  (across the bottom capacitor) as well as an internal boost converter between  $V_{MID}$  and  $V_{OUT}$  to regulate the voltage on  $C_{TOP}$  (across the top capacitor). The output current of the buck converter is user-programmed via the PROG pin and the input current of the boost converter is set at 2A (typical).

Table 1 indicates the various functions of the LTC3625/ LTC3625-1 that can be digitally controlled.

| Table 1. Digital | Input Functions |

|------------------|-----------------|

|------------------|-----------------|

| PIN              | VALUE | FUNCTION                                                 |

|------------------|-------|----------------------------------------------------------|

| CTL*             | 0     | Part runs in 2-inductor application                      |

|                  | 1     | Part runs in 1-inductor application                      |

| V <sub>SEL</sub> | 0     | 4.8V/4.0V sleep threshold                                |

|                  | 1     | 5.3V/4.5V sleep threshold                                |

| EN               | 0     | Part shuts down, V <sub>OUT</sub> becomes high impedance |

|                  | 1     | Part enables and regulates the output                    |

\*CTL pin must be hard tied to either  $\ensuremath{\mathsf{V_{\text{IN}}}}$  or GND.

### V<sub>IN</sub> Undervoltage Lockout (UVLO)

An internal undervoltage lockout circuit monitors  $V_{\rm IN}$  and keeps the LTC3625/LTC3625-1 disabled until  $V_{\rm IN}$  rises above 2.90V/2.63V (typical) if  $V_{\rm SEL}$  is high or 2.63V/2.63V (typical) if  $V_{\rm SEL}$  is low. Hysteresis on the UVLO turns off the LTC3625/LTC3625-1 if  $V_{\rm IN}$  drops by approximately 100mV below the UVLO rising threshold. When in UVLO, only current needed to detect a valid input will be drawn from  $V_{\rm IN}$  and  $V_{\rm OUT}$ .

### **Buck Converter**

The buck converter regulates a user-programmed average output current given by:

$$I_{BUCK} = h_{PROG} \bullet \frac{1.2V}{R_{PROG}}$$

where  $h_{PROG} = 118,000$  (typical).

The buck converter regulates the current hysteretically by switching on the buck PMOS until a peak current limit is reached and then turning on the buck NMOS until a valley current limit is reached. In the single inductor application the boost NMOS is used in conjunction with the buck NMOS to increase efficiency at high currents. The forward current limit is set to  $1.1 \cdot I_{BUCK}$  (typical) and the valley current limit is set to  $0.9 \cdot I_{BUCK}$  (typical). Because of this method of regulation, overcurrent limit and reverse-current limit protection is automatically provided. The LTC3625/LTC3625-1 will continue to regulate its programmed current even into a grounded output.

In fault conditions where the PROG pin is shorted to ground, or  $R_{PROG}$  is conductive enough to program  $I_{BUCK}$  to operate outside of specification, the current out of the PROG pin will be clamped to 22.5µA (typical) and  $I_{BUCK}$  will be set to 2.65A (typical). If input current limit is not a concern, the PROG pin may be grounded to minimize charge times.

### **Boost Converter**

The boost converter regulates a fixed average input current of 2A (typical). The current is regulated hysteretically by switching on the boost NMOS until the peak current limit of 2.12A (typical) is reached, and turning on the boost PMOS until the valley current limit of 1.88A (typical) is reached. In the single inductor application the buck NMOS is used in conjunction with the boost NMOS to increase efficiency. Because of this method of regulation, overcurrent limit and reverse-current limit protection is automatically provided.

In normal operation V<sub>OUT</sub> will increase with V<sub>MID</sub> so V<sub>OUT</sub> should never be below V<sub>MID</sub>. In the case where there is a reverse voltage on C<sub>TOP</sub> due to a faulty precondition or a large load on the output, the boost converter will operate in trickle charge mode. In this mode the boost PMOS gate will remain high and instead allow the SW2 node to increase until SW2  $\approx$  V<sub>MAX</sub> + 1V to allow a higher reverse voltage across the inductor, and the current is ramped down to OmA. This will result in a less efficient charge delivery through the PMOS. To keep dissipation low, I<sub>PEAK</sub> is limited to 200mA (typical). In this mode the discharge phase is terminated if it lasts longer than 6.5µs (typical).

The boost converter is disabled if  $V_{MID}$  falls below the  $V_{MID(GOOD)}$  hysteresis threshold of 1.2V (typical).

### OPERATION

#### Single Inductor Operation

With the CTL pin tied to  $V_{\rm IN}$  the LTC3625/LTC3625-1 will operate in single inductor mode. In this mode the same inductor serves in the power path for both the buck and the boost converters. Thus, the buck converter and boost converter will never run simultaneously.

Under certain conditions with a single inductor, a small amount of current can flow from the supercapacitors to  $V_{IN}$  when the boost charger is active. A 25mA load is required on  $V_{IN}$  to prevent the  $V_{IN}$  supply from being pumped to a higher voltage while the boost is active. This minimum load is not needed in the two inductor application and it is also not needed when the charger is disabled.

A typical charge cycle for a fully discharged capacitor stack will proceed as follows:

- The buck converter will turn on and regulate its output current ramping hysteretically between 1.1 • I<sub>BUCK</sub> and 0.9 • I<sub>BUCK</sub> until the V<sub>MID(GOOD)</sub> threshold is met (1.35V typical).

- 2. Once the  $V_{MID(GOOD)}$  threshold is reached, the boost converter will turn on and regulate its input current ramping hysteretically between 2.12A and 1.88A until  $V_{MID}$  falls below the  $V_{MID(GOOD)}$  hysteresis threshold (1.2V typical).

- 3. Phases 1 and 2 will alternate until V<sub>OUT</sub> is approximately 2.4V. When V<sub>TOP</sub> (equal to V<sub>OUT</sub> V<sub>MID</sub>) is approximately 50mV > V<sub>MID</sub>, the boost regulator will turn off and the buck regulator will turn on. Likewise, when V<sub>MID</sub> is approximately 50mV > V<sub>TOP</sub>, the boost regulator will turn on and the buck regulator will turn off.

- 4. Phase 3 will continue until  $V_{OUT}$  has reached its programmed output voltage. Once this happens, the part will enter sleep mode and only minimal power will be consumed (see the Electrical Characteristics table).

- 5. If the supercapacitors' self discharge or an external load cause the output to drop by more than 135mV (typical), then the LTC3625/LTC3625-1 will exit sleep mode and begin charging the appropriate supercapacitor.

In all cases whenever either of the converters is shut down, it will switch to its appropriate discharge phase (NMOS on for the buck and PMOS on for the boost) until the inductor current reaches 0mA. This optimizes charge delivery to the output capacitors.

Charge time is dependant on the programmed buck output current as well as the value of the supercapacitors being charged. For estimating charge profiles in the single inductor application, see the Typical Performance Characteristics graph Charge Time vs R<sub>PROG</sub>.

The effective average  $V_{\text{OUT}}$  referred charge current can be approximated as:

$$I_{CHARGE} \cong 0.5 \bullet I_{BUCK} \bullet \varepsilon_{BOOST} \bullet \frac{2A}{I_{BUCK} + 2A}$$

where  $\varepsilon_{BOOST}$  is the boost converter efficiency, which is typically about 85% (see the Typical Performance Characteristics graph Boost Efficiency vs V<sub>TOP</sub>).

Seen another way, this is the maximum steady-state load the part can support without losing  $V_{\text{OUT}}$  regulation.

#### **Dual Inductor Operation**

With the CTL pin tied to GND, the LTC3625/LTC3625-1 will operate in dual inductor mode. In this mode two inductors will serve as the power path for the buck and the boost converters. This will allow both the buck and the boost converter to run simultaneously. As a result, the total charge time will be greatly reduced at the cost of an additional board component.

A typical charge cycle for a fully discharged capacitor stack will proceed as follows:

- 1. The buck converter will turn on and regulate its output current ramping hysteretically between 1.1  $\cdot$  I<sub>BUCK</sub> and 0.9  $\cdot$  I<sub>BUCK</sub> until the V<sub>MID(GOOD)</sub> threshold is met (1.35V typical).

- 2. Once the  $V_{MID(GOOD)}$  threshold is reached, the boost converter will turn on and regulate its input current ramping hysteretically between 2.12A and 1.88A. The buck converter will continue to run at the same time. In some cases ( $I_{BUCK} \sim <1A$ ) the boost converter's input current will exceed the current delivered to  $C_{BOT}$ ; even though the buck converter is running, charge will be removed and  $V_{MID}$  may decrease. Thus, if  $V_{MID}$  falls below the  $V_{MID(GOOD)}$  hysteresis threshold, the boost

# OPERATION

converter will turn off. Once V<sub>MID</sub> has again risen above the V<sub>MID(GOOD)</sub> threshold, the boost converter will be re-enabled. In the case where V<sub>OUT</sub> < V<sub>MID</sub>, the boost converter will operate in trickle charge mode until V<sub>OUT</sub> exceeds V<sub>MID</sub> (see Boost Converter).

- 3. During phase 2, if C<sub>BOT</sub> exceeds its individual maximum threshold voltage (2.45V/2.05V typical if V<sub>SEL</sub> is low or 2.7V/2.3V typical if V<sub>SEL</sub> is high) or if V<sub>TOP</sub> exceeds V<sub>BOT</sub> by more than 50mV (typical), then the appropriate converter will turn off until the capacitor has fallen below its hysteresis threshold (2.40V/2V typical if V<sub>SEL</sub> is low and 2.65V/2.25V typical if V<sub>SEL</sub> is high for the buck converter or V<sub>TOP</sub> < V<sub>MID</sub> 50mV typical for the boost converter).

- 4. Once  $V_{OUT}$  has reached its programmed output voltage, the part will enter sleep mode, and only minimal power will be consumed (see the Electrical Characteristics table).

- 5. If the supercapacitors' self discharge or an external load cause the output to drop by more than 135mV (typical), then the LTC3625/LTC3625-1 will exit sleep mode and begin recharging the supercapacitor stack.

In all cases, whenever either of the converters is shut down, it will switch to its appropriate discharge phase (NMOS on for the buck and PMOS on for the boost) until the inductor current reaches 0mA. This optimizes charge delivery to the output capacitors.

Charge time is dependent on the programmed buck output current as well as the value of supercapacitors being charged. For estimating charge profiles in the dual inductor application, see the Typical Performance Characteristics graph Charge Time vs  $R_{PROG}$ .

The effective average  $V_{\text{OUT}}$  referred charge current, while both converters are continuously active, can be approximated as:

$$I_{CHARGE} \cong 0.5 \bullet I_{BUCK} - 1A \bullet \left(1 - 2 \bullet \epsilon_{BOOST} \bullet \frac{V_{MID}}{V_{OUT}}\right)$$

And, while both supercapacitors are in balance and  $V_{MID}$  is above the  $V_{MID(GOOD)}$  threshold as:

$I_{CHARGE}\cong 0.5 \bullet I_{BUCK} \bullet \epsilon_{BOOST}$

where  $\epsilon_{BOOST}$  is the boost converter efficiency which is typically around 85% (see the Typical Performance Characteristics graph Boost Efficiency vs  $V_{TOP}$ ).

Seen another way this is the maximum steady-state load the part can support without losing  $V_{\text{OUT}}$  regulation.

### PGOOD PIN

The PGOOD pin is an open-drain output used to indicate that  $V_{OUT}$  has approached its final regulation value. PGOOD remains active low until  $V_{OUT}$  reaches 92.5% of its regulation value at which point it will become high impedance. If  $V_{OUT}$  falls below 89.5% of its regulation voltage after PGOOD has been asserted, PGOOD will once again pull active low. PGOOD is an open-drain output and requires a pull-up resistor to the input voltage of the monitoring microprocessor or another appropriate power source. PGOOD is pulled active low in shutdown or input UVLO.

### **Power-Fail Input Comparator**

The PFI/PFO pins provide an input failure notification to the user. The PFI pin is a high impedance input pin that should be tied to a resistive divider from V<sub>IN</sub>. PFO is an open-drain output and requires a pull-up resistor to the input voltage of the monitoring microprocessor or another appropriate power source. When PFI is above 1.2V, PFO is high impedance and will be pulled up through the external resistor. If PFI drops below 1.2V, PFO will be pulled low indicating a power failure. This allows the user to program any desired input power failure indication threshold. There is 15mV of hysteresis on the PFI pin. If this functionality is not desired the PFI pin should be tied to V<sub>IN</sub>. PFO is pulled active low in shutdown or input UVLO

### **Shutdown Operation**

When the EN pin is pulled low the LTC3625/LTC3625-1 are put into shutdown. In this case, all of the active circuitry is powered down and there will be less than 1µA of leakage current from both  $V_{IN}$  and  $V_{OUT}$ . This allows the input to be present or absent as well as the capacitor stacks to be fully charged or discharged in shutdown without leakage between  $V_{IN}$ ,  $V_{OUT}$  and GND.

36251

### **APPLICATIONS INFORMATION**

#### Programming Charge Current/Maximum Input Current

The  $C_{BOT}$  charge current is programmed with a single resistor connecting the PROG pin to ground. The program resistor and buck output current are calculated using the following equation:

$$R_{PROG} = h_{PROG} \bullet \frac{1.2V}{I_{BUCK}}$$

where  $h_{PROG} = 118,000$  (typical). Excluding quiescent current,  $I_{BUCK}$  is always greater than the average buck input current. An  $R_{PROG}$  resistor value of less than 53.6k will cause the LTC3625/LTC3625-1 to enter overcurrent protection mode and proceed to charge at 2.65A (typical).

The effective buck input current can be calculated as:

$$I_{VIN} = \frac{I_{BUCK}}{\varepsilon_{BUCK}} \bullet \frac{V_{MID}}{V_{IN}}$$

where  $\epsilon_{BUCK}$  is the buck converter efficiency (see the Typical Performance Characteristics graph Buck Efficiency vs  $V_{MID}).$

### Output Voltage Programming

The LTC3625/LTC3625-1 have a  $V_{SEL}$  input pin that allows the user to set the output threshold voltage to either 4.8V/4.0V or 5.3V/4.5V by forcing a low or high at the  $V_{SEL}$  pin respectively. In the single inductor application the chip will balance the supercapacitors to within 50mV (typical) of each other, resulting in a possible 25mV of over/undercharge per cell. In the dual inductor application the chip will balance the supercapacitors to within 100mV (typical) of each other, resulting in a possible 50mV of over/undercharge per cell.

### Thermal Management

If the junction temperature increases above approximately 150°C, the thermal shutdown circuitry automatically deactivates the output. To reduce the maximum junction temperature, a good thermal connection to the PC board is recommended. Connecting the exposed pad (Pin 13) of the DFN package to a ground plane under the device on two layers of the PC board, will reduce the thermal resistance of the package and PC board considerably.

### **VIN Capacitor Selection**

The style and value of capacitors used with the LTC3625/ LTC3625-1 determine input voltage ripple. Because the LTC3625/LTC3625-1 use a step-down switching power supply from V<sub>IN</sub> to V<sub>MID</sub>, its input current waveform contains high frequency components. It is strongly recommended that a low equivalent series resistance (ESR) multilayer ceramic capacitor be used to bypass V<sub>IN</sub>.

Tantalum and aluminum capacitors are not recommended because of their high ESR. The value of the capacitor on  $V_{IN}$  directly controls the amount of input ripple for a given  $I_{BUCK}$ . Increasing the size of this capacitor will reduce the input ripple.

Multilayer ceramic chip capacitors typically have exceptional ESR performance. MLCCs combined with a tight board layout and an unbroken ground plane will yield very good performance and low EMI emissions. There are several types of ceramic capacitors available, each having considerably different characteristics. For example, X7R ceramic capacitors have the best voltage and temperature stability. X5R ceramic capacitors have higher packing density but poorer performance over their rated voltage and temperature ranges. Y5V ceramic capacitors have the highest packing density, but must be used with caution because of their extreme non-linear characteristic of capacitance verse voltage.

The actual in-circuit capacitance of a ceramic capacitor should be measured with a small AC signal as is expected in-circuit. Many vendors specify the capacitance versus voltage with a  $1V_{RMS}$  AC test signal and as a result, overstate the capacitance that the capacitor will present in the application. Using similar operating conditions as the application, the user must measure or request from the vendor the actual capacitance to determine if the selected capacitor meets the minimum capacitance that the application requires.

### **Inductor Selection**

Many different sizes and shapes of inductors are available from numerous manufacturers. Choosing the right inductor from such a large selection of devices can be overwhelming, but following a few basic guidelines will make the selection process much simpler.

# **APPLICATIONS INFORMATION**

The buck and boost converters are designed to work with inductors over a wide range of inductances. Choosing a higher valued inductor will decrease operating frequencies, while a lower valued inductor will increase frequency but also increase peak current overshoot/undershoot. For most applications a 3.3 $\mu$ H inductor is recommended. To maximize efficiency, choose an inductor with a low DC resistance. Choose an inductor with a DC current rating at least as large as the maximum I<sub>PEAK</sub> the application will see according to the specifications table to ensure that the inductor does not saturate during normal operation. If the single inductor application is used, make sure to size the inductor for the higher of buck or boost peak currents.

Different core materials and shapes will change the size/current and price/current relationship of an inductor. Toroid or shielded pot cores in ferrite or Permalloy materials are small and do not radiate much energy, but generally cost more than powdered iron core inductors with similar electrical characteristics. Inductors that are very thin or have a very small volume typically have much higher core and DCR losses, and will not give the best efficiency. The choice of which style inductor to use often depends more on the price versus size, performance and any radiated EMI requirements than on what the LTC3625/LTC3625-1 family requires to operate.

Table 2 shows several inductors that work well with the LTC3625/LTC3625-1 regulators. These inductors offer a

good compromise in current rating, DCR and physical size. Consult each manufacturer for detailed information on their entire selection of inductors.

#### **Supercapacitor Selection**

The LTC3625/LTC3625-1 are designed to charge supercapacitors of values greater than 0.1F per cell. In general, lower capacitance cells have higher ESRs, therefore lower charge currents should be used to help reduce sleep modulation towards the end of a charge cycle. In general, the ESR of a supercapacitor cell should not exceed:

$$\text{ESR} \le \frac{100 \text{mV}}{\text{I}_{\text{BUCK}}}$$

where 100mV is the sleep threshold hysteresis. Higher capacitance cells typically have lower ESRs and can therefore be charged with higher currents. Typically, the LTC3625/LTC3625-1 are designed to charge supercapacitors with values up to 100F, but higher capacitance cells could be used at the expense of greater charge time. Table 3 shows several supercapacitors that work well with the LTC3625/LTC3625-1.

#### **Printed Circuit Board Layout Considerations**

In order to be able to deliver maximum current under all conditions, it is critical that the exposed pad on the backside of the LTC3625/LTC3625-1 package be soldered to the PC

| MANUFACTURER | PART NUMBER        | INDUCTANCE (µH) | CURRENT (A) | DCR (m $\Omega$ ) | SIZE (mm)     |

|--------------|--------------------|-----------------|-------------|-------------------|---------------|

| Coiltronics  | DR73-3R3-R         | 3.3             | 3.0         | 20                | $7 \times 7$  |

| Coilcraft    | MSS7341-332NL      | 3.3             | 3.2         | 20                | $7 \times 7$  |

| Vishay       | IHLM2525CZER3R3M11 | 3.3             | 6.5         | 26                | 6.5 	imes 6.9 |

| Sumida       | CDRH6D28P-3RON     | 3.0             | 3.0         | 24                | 7 × 7         |

| ТОКО         | B1077AS-3RON       | 3.0             | 3.3         | 30                | 7.6×7.6       |

#### Table 2. Inductor Manufacturers

| MANUFACTURER       | PART NUMBER        | VALUE (F) | OPERATING VOLTAGE (V) | MAXIMUM ESR (m $\Omega$ ) | SIZE (mm)   |

|--------------------|--------------------|-----------|-----------------------|---------------------------|-------------|

| Cooper Bussmann    | B1860-2R5107-R     | 100       | 2.5                   | 20                        | 18×60       |

| Illinois Capacitor | 107DCN2R7M         | 100       | 2.7                   | 10                        | 22 	imes 45 |

| NESS Capacitor     | ESHSR-0100C0002R7  | 100       | 2.7                   | 9                         | 22 	imes 45 |

| Tecate             | TPLS-100//22 X 45F | 100       | 2.7                   | 9                         | 22 	imes 45 |

| Maxwell            | BCAP120P250        | 120       | 2.5                   | 2.5                       | 26 × 51     |

### **APPLICATIONS INFORMATION**

board ground. Failure to make thermal contact between the exposed pad on the backside of the package and the copper board will result in higher thermal resistances.

Furthermore, due to its potentially high frequency switching circuitry, it is imperative that the input capacitor, inductors, and output bypass capacitors be as close to the LTC3625/LTC3625-1 as possible, and that there be an unbroken ground plane under the IC and all of its external high frequency components. High frequency currents, such as the V<sub>IN</sub> and V<sub>OUT</sub> currents on the LTC3625/LTC3625-1, tend to find their way along the ground plane in a myriad of paths ranging from directly back to a mirror path beneath the incident path on the top of the board. If there are slits or cuts in the ground plane due to other traces on that layer, the current will be forced to go around the slits. If high frequency currents are not allowed to flow back through their natural least-area path, excessive voltage will build up and radiated emissions will occur. There should be a group of vias under the grounded backside of the package leading directly down to an internal ground plane. To minimize parasitic inductance, the ground plane should be on the highest possible layer of the PC board.

Any board resistance between inductor(s) and the positive terminal of  $C_{BOT}$  will add to the capacitors internal ESR. Likewise, any resistance between the  $V_{OUT}$  pin and the positive terminal of  $C_{TOP}$  will add to its internal ESR. Any added resistance to the capacitors will reduce the effective charging efficiency. In the case of  $C_{BOT}$  this

resistance can be kelvined out by a dedicated voltage sense trace from the V<sub>MID</sub> pin to a point halfway between the bottom plate of  $C_{TOP}$  and the top plate of  $C_{BOT}$ . In the case of  $C_{TOP}$ , however, it is even more critical to keep any resistance in the connection to a minimum. Excessive series resistance may cause the part to duty cycle in and out of sleep or prematurely shut down the boost, due to the voltage seen at the part being equal to  $V_{OUT} + I_{OUT} \cdot ESR$ . Likewise the  $C_{BOT}$  supercapacitor should be provided with a low impedance contact to the ground plane with an unbroken, low impedance, path back to the backside of the LTC3625/LTC3625-1 package.

When laying out the printed circuit, the following checklist should be used to ensure proper operation of the LTC3625/LTC3625-1.

- Are the bypass capacitors at V<sub>IN</sub> and V<sub>OUT</sub> as close as possible to the LTC3625/LTC3625-1? These capacitors provide the AC current to the internal power MOSFETs and their drivers. Minimizing inductance from these capacitors to the LTC3625/LTC3625-1 is a top priority.

- 2. Are the C<sub>BOT</sub> bypass capacitor and the power inductor(s) closely connected? The (–) terminal of the C<sub>BOT</sub> bypass capacitor returns current to the GND plane, and then back to C<sub>IN</sub>.

- 3. Keep sensitive components away from the SW pins.

- 4. Keep the current carrying traces from  $V_{OUT}$  to  $C_{TOP}$  and the inductors to  $C_{BOT}$  to a minimum.

### TYPICAL APPLICATIONS

#### 450mA Charge Current 1-Inductor Application

3625

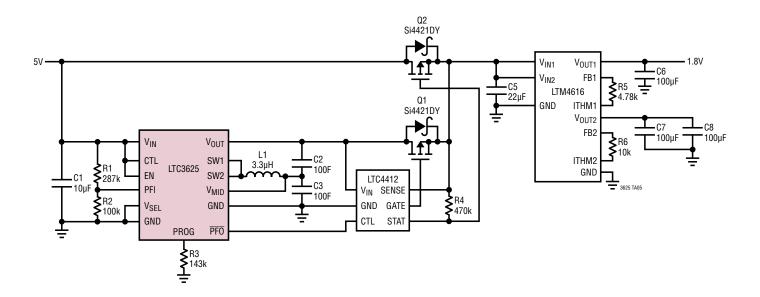

### TYPICAL APPLICATIONS

Solar Powered SCAP Charger with MPPT

5V Power Ride-Through

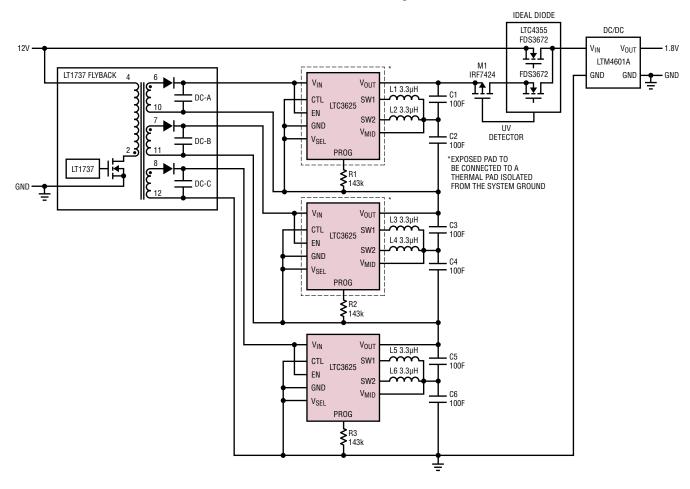

### TYPICAL APPLICATIONS

**12V Power Ride-Through**

### PACKAGE DESCRIPTION

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

### TYPICAL APPLICATION

#### Minimum External Component Application (500mA Charge Current)

### **RELATED PARTS**

| PART NUMBER                               | DESCRIPTION                                                                                        | COMMENTS                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3203/LTC3203B/<br>LTC3203B-1/LTC3203-1 | 500mA Low Noise High Efficiency Dual Mode<br>Step-Up Charge Pumps                                  | $V_{\text{IN}}$ : 2.7V to 5.5V, 3mm $\times$ 3mm 10-Lead DFN Package                                                                                                                                                                                                                                       |

| LTC3204/LTC3204B-3.3/<br>LTC3204-5        | Low Noise Regulating Charge Pumps                                                                  | Up to 150mA Output Current (LTC3204-5), Up to 50mA Output Current (LTC3204-3.3)                                                                                                                                                                                                                            |

| LTC3221/LTC3221-3.3/<br>LTC3221-5         | Micropower Regulated Charge Pump                                                                   | Up to 60mA Output Current                                                                                                                                                                                                                                                                                  |

| LTC3225/LTC3225-1                         | 150mA Supercapacitor Charger                                                                       | Programmable Supercapacitor Charger Designed to Charge Two<br>Supercapacitors in Series to a Fixed Output Voltage (4.8V/5.3V Selectable)<br>from a 2.8V/3V to 5.5V Input Supply. Automatic Cell Balancing Prevents<br>Overvoltage Damage to Either Supercapacitor. No Balancing Resistors are<br>Required. |

| LTC3240-3.3/LTC3240-2.5                   | Step-Up/Step-Down Regulated Charge Pumps                                                           | Up to 150mA Output Current                                                                                                                                                                                                                                                                                 |

| LT®3420/LT3420-1                          | 1.4A/1A Photoflash Capacitor Charger with<br>Automatic Top-Off                                     | Charges 220µF to 320V in 3.7 Seconds from 5V, $V_{IN}$ : 2.2V to 16V, $I_{SD} <$ 1µA, 10-Lead MS Package                                                                                                                                                                                                   |

| LT3468/LT3468-1/<br>LT3468-2              | 1.4A/1A/0.7A, Photoflash Capacitor Charger                                                         | $V_{IN}$ : 2.5V to 16V, Charge Time = 4.6 Seconds for the LT3468 (0V to 320V, 100µF, $V_{IN}$ = 3.6V), $I_{SD}$ < 1µA, ThinSOT^M Package                                                                                                                                                                   |

| LTC3484-0/LTC3484-1/<br>LTC3484-2         | 1.4A/0.7A/1A, Photoflash Capacitor Charger                                                         | $V_{IN}$ : 1.8V to 16V, Charge Time = 4.6 Seconds for the LT3484-0 (0V to 320V, 100µF, $V_{IN}$ = 3.6V), $I_{SD}$ < 1µA, 2mm $\times$ 3mm 6-Lead DFN Package                                                                                                                                               |

| LT3485-0/LT3485-1/<br>LT3485-2/LT3485-3   | 1.4A/0.7A/1A/2A Photoflash Capacitor Charger<br>with Output Voltage Monitor and Integrated<br>IGBT | $V_{IN}$ : 1.8V to 10V, Charge Time = 3.7 Seconds for the LT3485-0 (0V to 320V, 100µF, $V_{IN}$ = 3.6V), $I_{SD}$ < 1µA, 3mm $\times$ 3mm 10-Lead DFN Driver                                                                                                                                               |

| LT3750                                    | Capacitor Charger Controller                                                                       | Charges Any Size Capacitor, 10-Lead MS Package                                                                                                                                                                                                                                                             |

| LT3751                                    | Capacitor Controller with Regulation                                                               | Charges Any Size Capacitor, 4mm × 5mm QFN-20 Package                                                                                                                                                                                                                                                       |

| LTC4425                                   | Supercapacitor Charger with Current-Limited Ideal Diode                                            | CC/CV Linear Charger for 2-Cell Supercapacitor Stack from a Li-Ion/<br>Polymer Battery, USB Port or a 2.7V to 5.5V Current-Limited Supply,<br>3mm × 3mm DFN-12 and MSOP-12E Packages                                                                                                                       |

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

LTC3625IDE#PBF LTC3625EDE#TRPBF LTC3625IDE-1#TRPBF LTC3625IDE-1#PBF LTC3625EDE-1#PBF LTC3625EDE+1#TRPBF LTC3625EDE#PBF DC1583A-A DC1583A-B