## 20V 1A Buck DC/DC with Integrated SCAP Charger and Backup Regulator

## **FEATURES**

- V<sub>IN</sub> Voltage Range: 3V to 20V

V<sub>OUT</sub> Voltage Range: 2.7V to 5V

- 1A Current Mode Buck Main Regulator

- 5A Boost Backup Regulator Powered from Single Supercapacitor

- Boost Regulator Operates Down to 0.5V for Maximum Utilization of Supercapacitor Energy

- Programmable Supercapacitor Charge Current to 1A with Overvoltage Protection

- Charger Supports Single Cell CC/CV Battery Charging

- Programmable V<sub>IN</sub> Current Limit

- Programmable Boost Current Limit

- V<sub>IN</sub> Power Fail Indicator

- V<sub>CAP</sub> Power Good Indicator

- V<sub>OUT</sub> Power On Reset Output

- Compact 20-Lead 4mm × 4mm QFN Package

## **APPLICATIONS**

- Ride-Through "Dying Gasp" Supplies

- Power Meters/Industrial Alarms/Solid State Drives

## DESCRIPTION

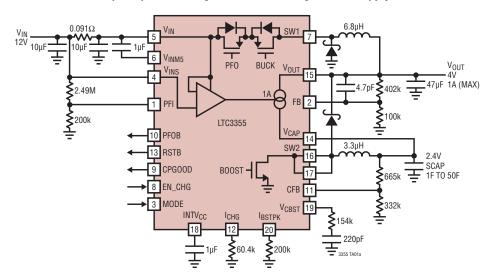

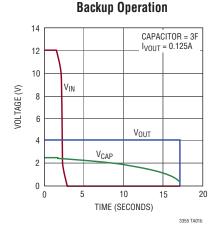

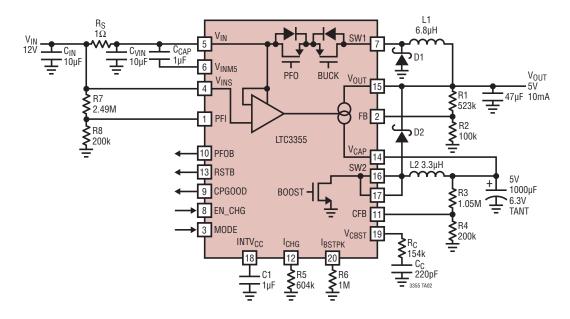

The LTC®3355 is a complete input power interrupt ridethrough DC/DC system. The part charges a supercapacitor while delivering load current to  $V_{OUT}$ , and uses energy from the supercapacitor to provide continuous  $V_{OUT}$  backup power when  $V_{IN}$  power is lost. The LTC3355 contains a nonsynchronous constant frequency current mode monolithic 1A buck switching regulator to provide a 2.7V to 5V regulated output voltage from an input supply of up to 20V.

A 1A programmable CC/CV linear charger charges the supercapacitor from  $V_{OUT}.$  When the  $V_{IN}$  supply drops below the PFI threshold, the devices's constant frequency nonsynchronous current mode 5A boost switching regulator delivers power from the supercapacitor to  $V_{OUT}.$  A thermal regulation loop maximizes charge current while limiting the die temperature to 110°C. The IC has boost, charger and  $V_{IN}$  programmable current limits. The LTC3355 is available in a 20-lead 4mm  $\times$  4mm QFN surface mount package.

LT, LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

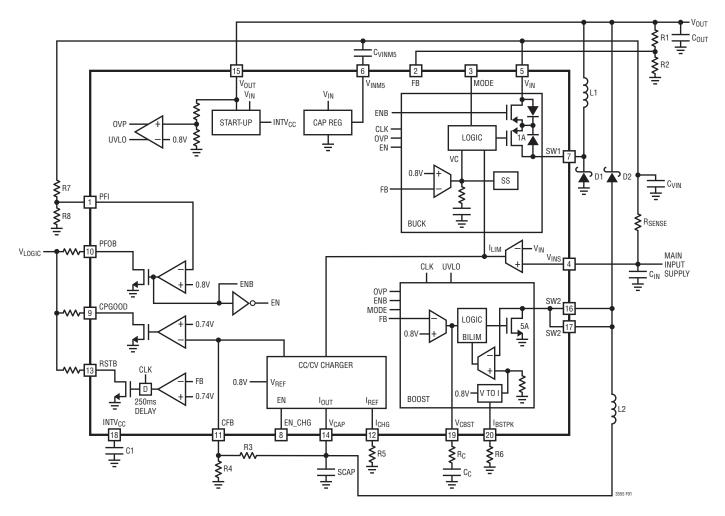

## TYPICAL APPLICATION

**Supercapacitor Charger and Ride-Through Power Supply**

3355fb

## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                               |                                      |

|--------------------------------------------------------|--------------------------------------|

| V <sub>IN</sub> , V <sub>INS</sub> , V <sub>INM5</sub> | 22V                                  |

| V <sub>IN</sub> ±V <sub>INS</sub>                      | 0.1V                                 |

| V <sub>SW1</sub>                                       |                                      |

| V <sub>SW2</sub>                                       | 0.4V to 6V                           |

| V <sub>OUT</sub> , INTV <sub>CC</sub> , PFOB, RSTB,    |                                      |

| CPGOOD, V <sub>CAP</sub>                               | 0.3V to 6V                           |

| PFI, EN_CHG, MODE, FB                                  | 0.3V to 6V                           |

| CFB                                                    | -0.3V to INTV <sub>CC</sub> + $0.3V$ |

| ICPGOOD, IPFOB, IRSTB                                  | 1mA                                  |

| <b>Operating Junction Temperature</b>                  | Range                                |

| (Notes 2, 3)                                           | 40°C to 125°C                        |

| Storage Temperature Range                              | 65°C to 150°C                        |

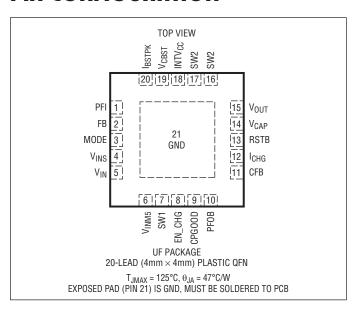

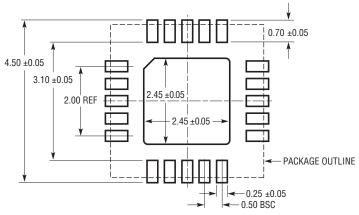

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|--------------|---------------------------------|-------------------|

| LTC3355EUF#PBF   | LTC3355EUF#TRPBF | 3355         | 20-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

| LTC3355IUF#PBF   | LTC3355IUF#TRPBF | 3355         | 20-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{IN} = 12 V$ unless otherwise noted. (Note 2)

| SYMBOL                | PARAMETER                                                               | CONDITIONS                                                                                                | ] | MIN       | TYP                                         | MAX        | UNITS    |

|-----------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---|-----------|---------------------------------------------|------------|----------|

| $V_{IN}$              | V <sub>IN</sub> Operating Voltage Range                                 |                                                                                                           | • | 3         |                                             | 20         | V        |

| IQ                    | V <sub>IN</sub> Quiescent Current<br>V <sub>OUT</sub> Quiescent Current | Charger Off, Not Switching, V <sub>OUT</sub> = 3.3V, No<br>Load, In Regulation, Supercapacitor Charged    | • | 60<br>110 | 120<br>265                                  | 215<br>420 | μA<br>μA |

| $V_{FB}$              | FB Reference Voltage                                                    |                                                                                                           | • | 0.775     |                                             | 0.825      | V        |

|                       | FB Line Regulation                                                      | V <sub>OUT</sub> = 2.7V to 5V                                                                             |   |           | 0.1                                         |            | %/V      |

| I <sub>FB</sub>       | FB Input Bias Current                                                   |                                                                                                           |   | -20       |                                             | 20         | nA       |

| $V_{VOUT}$            | V <sub>OUT</sub> Voltage Range                                          |                                                                                                           | • | 2.7       |                                             | 5          | V        |

|                       | V <sub>OUT</sub> Overvoltage Limit                                      | Buck or Boost Enabled                                                                                     |   | 5.4       | 5.65                                        | 5.95       | V        |

|                       | V <sub>OUT</sub> Undervoltage Lockout Threshold                         | Boost Enabled                                                                                             |   | 1.8       | 2                                           | 2.2        | V        |

| V <sub>INM5</sub>     | V <sub>IN</sub> -V <sub>INM5</sub>                                      | $V_{IN} > 7V$                                                                                             |   |           | 4.65                                        |            | V        |

| V <sub>INTVCC</sub>   | INTV <sub>CC</sub> Internal Voltage Power Supply                        |                                                                                                           |   | 2         |                                             | 5          | V        |

| $V_{VCAP}$            | V <sub>CAP</sub> Voltage Range                                          |                                                                                                           |   | 0         |                                             | 5          | V        |

| I <sub>VCAP</sub>     | V <sub>CAP</sub> Current Accuracy                                       | V <sub>CAP</sub> = 2V, V <sub>OUT</sub> = 3.3V, I <sub>VCAP</sub> = 1A<br>EN_CHG = High                   |   | -10       |                                             | 10         | %        |

|                       | V <sub>CAP</sub> Programmable Current Range                             | EN_CHG = High                                                                                             |   | 0.1       |                                             | 1          | A        |

| V <sub>ICHG</sub>     | I <sub>CHG</sub> Reference Voltage                                      | EN_CHG = High                                                                                             |   | 0.78      |                                             | 0.82       | V        |

| R <sub>ICHG</sub>     | I <sub>CHG</sub> Set Resistor Range                                     |                                                                                                           |   | 60.4      |                                             | 604        | kΩ       |

| I <sub>CFB</sub>      | CFB Input Bias Current                                                  |                                                                                                           |   | -20       |                                             | 20         | nA       |

| $V_{CFB}$             | CFB Reference Voltage                                                   | EN_CHG = High                                                                                             |   | 0.78      | 0.8                                         | 0.82       | V        |

|                       | CFB Hysteresis                                                          | EN_CHG = High                                                                                             |   |           | 30                                          |            | mV       |

|                       | CFB Overvoltage Hysteretic Comparator<br>Switch Point                   | CFB Rising<br>CFB Falling                                                                                 |   |           | V <sub>CFB</sub> +0.035<br>V <sub>CFB</sub> |            | V        |

| I <sub>ICL</sub>      | V <sub>IN</sub> Input Current Limit                                     | V <sub>INS</sub> -V <sub>IN</sub> to Disable Charger<br>V <sub>INS</sub> -V <sub>IN</sub> to Disable Buck |   | 37<br>42  |                                             | 43<br>50   | mV<br>mV |

| V <sub>INS(CMI)</sub> | V <sub>INS</sub> Common Mode Range                                      |                                                                                                           |   | 3.0       |                                             | 20         | V        |

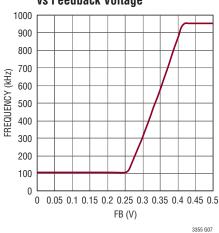

| f <sub>SW</sub>       | Switching Frequency                                                     | FB ≥ 0.5V                                                                                                 |   | 0.75      | 1                                           | 1.25       | MHz      |

|                       | Foldback Frequency (Buck Only)                                          | FB ≤ 0.3V                                                                                                 |   |           | 100                                         |            | kHz      |

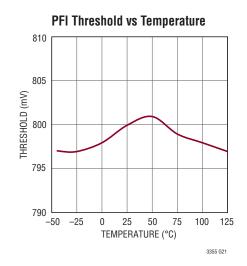

| $V_{PFI}$             | PFI Falling Threshold                                                   |                                                                                                           | • | 0.775     | 0.8                                         | 0.825      | V        |

|                       | PFI Hysteresis                                                          |                                                                                                           |   |           | 17                                          |            | mV       |

| I <sub>PFI</sub>      | PFI Leakage Current                                                     |                                                                                                           |   | -20       |                                             | 20         | nA       |

| 1A Buck R             | egulator                                                                |                                                                                                           |   |           |                                             |            |          |

| I <sub>SW1</sub>      | SW1 Peak Current                                                        | PWM Mode (Note 5)<br>Burst Mode® (Note 5)                                                                 |   | 1.3       | 1.65<br>0.5                                 | 2          | A<br>A   |

| t <sub>SS</sub>       | Soft-Start Time                                                         |                                                                                                           |   |           | 1000                                        |            | μs       |

| DC Max                | Maximum Duty Cycle                                                      | FB = 0V                                                                                                   |   | 100       |                                             |            | %        |

| R <sub>PMOS</sub>     | PMOS On-Resistance                                                      |                                                                                                           |   |           | 0.5                                         | 1          | Ω        |

| I <sub>LEAKP</sub>    | PMOS Leakage Current                                                    | Buck Disabled                                                                                             |   | -2        |                                             | 2          | μА       |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{IN} = 12V$ unless otherwise noted. (Note 2)

| SYMBOL                            | PARAMETER                              | CONDITIONS                                                                     |   | MIN   | TYP      | MAX   | UNITS  |

|-----------------------------------|----------------------------------------|--------------------------------------------------------------------------------|---|-------|----------|-------|--------|

| 5A Boost                          | Regulator                              |                                                                                |   |       |          |       |        |

| I <sub>VOUT</sub>                 | V <sub>OUT</sub> Quiescent Current     | V <sub>OUT</sub> = 3.3V, No Load, In Regulation, No Switching, Burst Mode      | • | 80    | 160      | 280   | μА     |

| I <sub>SW2</sub>                  | SW2 Peak Current                       | R <sub>IBSTPK</sub> = 200k, PWM Mode<br>R <sub>IBSTPK</sub> = 200k, Burst Mode |   | 4.5   | 5<br>1.5 | 5.5   | A<br>A |

| R <sub>NMOS</sub>                 | NMOS On-Resistance                     |                                                                                |   |       | 70       |       | mΩ     |

| I <sub>LEAKN</sub>                | NMOS Leakage Current                   | Boost Disabled                                                                 |   | -5    |          | 5     | μА     |

| DC Max                            | Boost Maximum Duty Cycle               |                                                                                |   | 88    | 92       | 98    | %      |

| V <sub>SBOOST</sub>               | Boost Input Supply Voltage Range       |                                                                                |   | 0.75  |          | 5     | V      |

|                                   | Boost Minimum Input Supply             | $V_{OUT(MAX)} = 4V$                                                            |   | 0.5   |          |       | V      |

| A <sub>V</sub>                    | Boost Error Amplifier Voltage Gain     | (Note 5)                                                                       |   |       | 850      |       | V/V    |

| g <sub>m</sub>                    | Boost Error Amplifier Transconductance |                                                                                |   |       | 27       |       | μS     |

| $V_{IBSTPK}$                      | I <sub>BSTPK</sub> Reference Voltage   |                                                                                |   | 0.775 |          | 0.825 | V      |

| R <sub>IBSTPK</sub>               | I <sub>BSTPK</sub> Set Resistor Range  |                                                                                |   | 200   |          | 1000  | kΩ     |

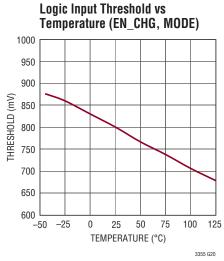

| Logic (MC                         | DDE, EN_CHG, CPGOOD, RSTB, PFOB)       |                                                                                |   |       |          |       |        |

| $V_{IL}$                          | Input Low Logic Voltage                | MODE, EN_CHG                                                                   |   |       |          | 0.4   | V      |

| $V_{IH}$                          | Input High Logic Voltage               | MODE, EN_CHG                                                                   |   | 1.2   |          |       | V      |

| I <sub>IL</sub> , I <sub>IH</sub> | Input Low/High Current                 | MODE, EN_CHG                                                                   |   | -1    |          | 1     | μА     |

| $V_{OL}$                          | Output Logic Low Voltage               | PFOB, CPGOOD, RSTB; Sink 100μA                                                 |   |       |          | 50    | mV     |

| I <sub>OH</sub>                   | Logic High Leakage Current             | PFOB, CPGOOD, RSTB; 5V                                                         |   |       |          | 1     | μА     |

|                                   | CPGOOD Rising Threshold                | V <sub>CAP</sub> as a % of Final Target                                        |   | 90    | 92.5     | 95    | %      |

|                                   | CPG00D Hysteresis                      | ΔV <sub>CAP</sub> as a % of Final Value                                        |   |       | 2.5      |       | %      |

|                                   | RSTB Falling Threshold                 | V <sub>OUT</sub> as a % of Final Target                                        |   | 90    | 92.5     | 95    | %      |

|                                   | RSTB Hysteresis                        | ΔV <sub>OUT</sub> as a % of Final Value                                        |   |       | 2.5      |       | %      |

|                                   | RSTB Delay                             |                                                                                |   |       | 250      |       | ms     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3355 is tested under pulsed load conditions such that  $T_J \approx T_A.$  The LTC3355E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the  $-40^{\circ}C$  to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3355I is guaranteed over the  $-40^{\circ}C$  to 125°C operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature  $(T_J,$  in °C) is calculated from the ambient temperature  $(T_A,$  in °C) and power dissipation  $(P_D,$  in Watts) according to the formula:

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

where  $\theta_{JA} = 47^{\circ}\text{C/W}$  for the UF package.

**Note 3:** The LTC3355 has a thermal regulation loop that limits the maximum junction temperature to 110°C by limiting the charger current.

**Note 4:** The current limit features of this part are intended to protect the IC from short-term or intermittent fault conditions. Continuous operation above the maximum specified pin current may result in device degradation or failure.

Note 5: Guaranteed by design and/or correlation to static test.

**Note 6:** The LTC3355 has a thermal shutdown that will shut down the part when the die temperature reaches 155°C.

LINEAR TECHNOLOGY

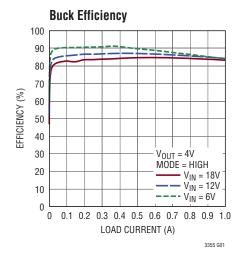

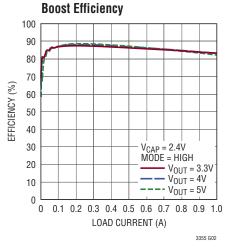

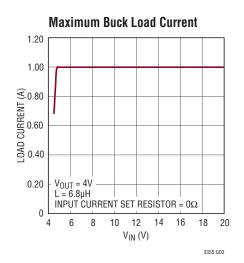

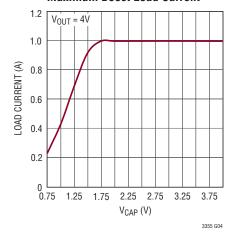

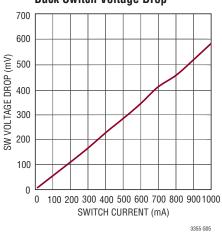

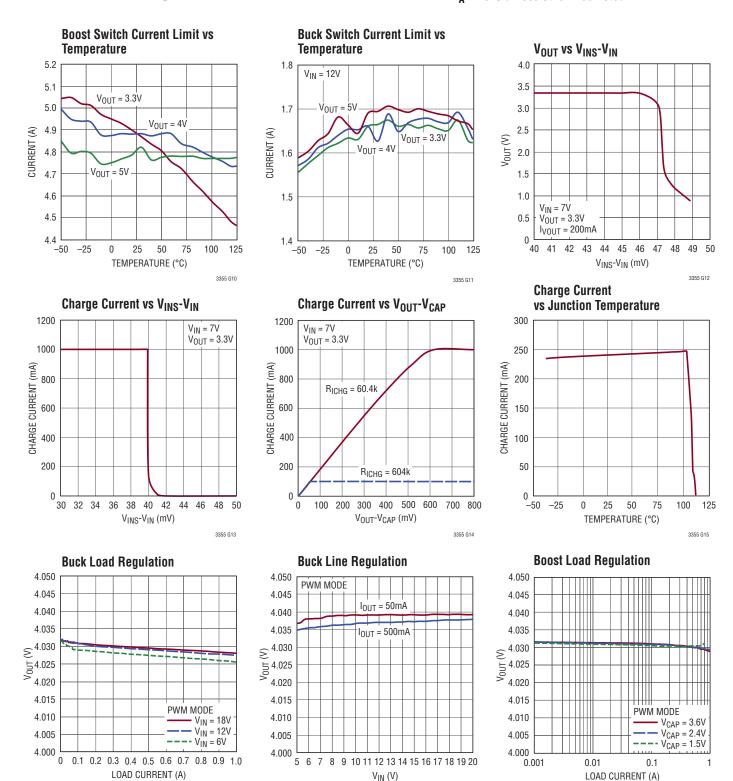

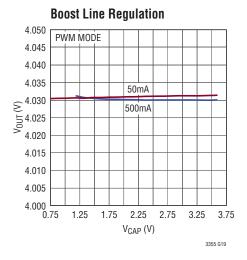

## TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ unless otherwise noted

#### **Maximum Boost Load Current**

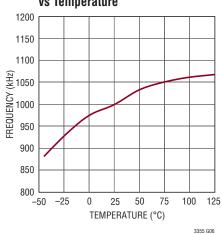

**Oscillator Frequency** vs Temperature

#### **Buck Frequency** vs Feedback Voltage

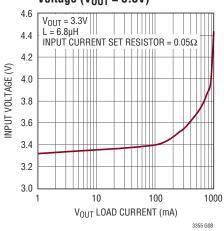

#### Typical Minimum Buck Input Voltage ( $V_{OUT} = 3.3V$ )

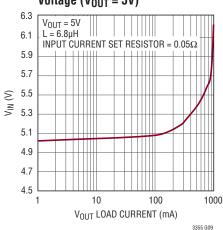

#### Typical Minimum Buck Input Voltage ( $V_{OUT} = 5V$ )

3355fh

## TYPICAL PERFORMANCE CHARACTERISTICS TA = 25°C unless otherwise noted

3355fb

3355 G18

3355 G17

3355 G16

## TYPICAL PERFORMANCE CHARACTERISTICS T<sub>A</sub> = 25°C unless otherwise noted

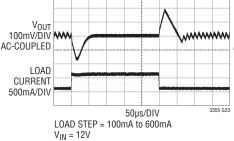

#### **Buck Load Step PWM**

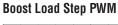

**Buck Load Step Burst Mode**

Operation

$V_{OUT} = 4V$

$V_{OUT} = 4V$

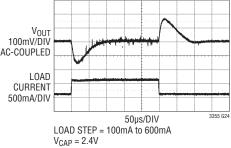

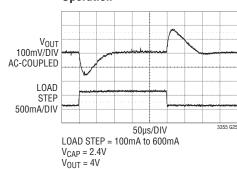

#### **Boost Load Step Burst Mode** Operation

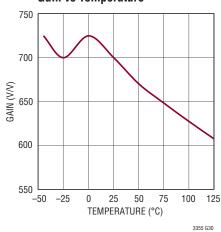

#### **Boost Error Amplifier Voltage Gain vs Temperature**

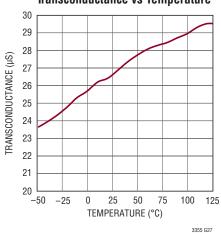

#### **Boost Error Amplifier** Transconductance vs Temperature

## PIN FUNCTIONS

**PFI (Pin 1):** Input to the Power-Fail Comparator. The input voltage below which the PFOB pin indicates a power-fail condition can be programmed by connecting this pin to an external resistor divider between  $V_{IN}$  and ground.

**FB** (Pin 2): Sets the  $V_{OUT}$  voltage for both the buck and boost voltage control loops via an external resistor divider. The reference voltage is 0.8V.

**MODE (Pin 3):** This pin sets the buck and boost switching modes. A low is PWM mode, a high is Burst Mode operation.

$V_{INS}$  (Pin 4): Input Current Limit Sense Voltage Pin. Connect a sense resistor from  $V_{INS}$  to  $V_{IN}$ . Must be locally bypassed with a low ESR ceramic capacitor. Connect to  $V_{IN}$  if input current limit is not needed.

**V<sub>IN</sub> (Pin 5):** Input Power Pin Supplies Current to the Internal Regulator and Buck Power Switch. Must be locally bypassed with a low ESR ceramic capacitor.

$V_{INM5}$  (Pin 6): This pin is used to filter an internal supply regulator which generates a voltage of  $V_{IN}-4.65V$ . Connect a  $1\mu F$  ceramic capacitor from  $V_{INM5}$  to  $V_{IN}$ .

**SW1 (Pin 7):** Buck Output of the Internal Power Switch. Connect this pin to the catch diode and inductor. Minimize trace area at this pin to reduce EMI.

**EN\_CHG (Pin 8):** A high on this pin enables the supercapacitor charger.

**CPGOOD** (Pin 9): Open-drain output is high impedance when the  $V_{CAP}$  voltage is higher than 92.5% of the programmed voltage.

**PFOB (Pin 10):** Open Drain of the Power-Fail Comparator. Pulled low and enables the boost converter when the PFI input has determined that the input supply has dropped out.

**CFB (Pin 11):** This pin is used to program the  $V_{CAP}$  voltage via an external resistor divider. The reference voltage is 0.8V.

$I_{CHG}$  (Pin 12): This pin programs the  $V_{CAP}$  charge current by connecting a resistor to ground.

**RSTB (Pin 13):** Open-drain reset output is high impedance when the  $V_{OUT}$  voltage is higher than 92.5% of the programmed regulation voltage.

**V**<sub>CAP</sub> (**Pin 14**): This pin is the constant current, constant voltage linear charger output and connects to the supercapacitor.

$V_{OUT}$  (Pin 15): The Output Voltage Supply. The buck powers this supply from  $V_{IN}$  when the input voltage is present and the boost powers this supply from  $V_{CAP}$  when the input voltage has dropped out.

**SW2 (Pin 16, 17):** Boost Output of the Internal Power Switch. Connect these pins to the rectifier diode and inductor. Minimize trace area at these pins to reduce EMI.

INTV<sub>CC</sub> (Pin 18): This pin is used to filter an internal supply. Connect a 1 $\mu$ F ceramic capacitor from this pin to ground. INTV<sub>CC</sub> is 2.5V during start-up until V<sub>OUT</sub> exceeds 2.5V then INTV<sub>CC</sub> follows V<sub>OUT</sub>.

**V**<sub>CBST</sub> (**Pin 19**): This pin is the output of the boost internal error amplifier. The voltage on this pin controls the peak switch current for the boost regulator. Connect an RC series network from this pin to ground to compensate the boost control loop.

**IBSTPK** (**Pin 20**): This pin programs the boost peak current limit by connecting a resistor to ground.

**GND** (Exposed Pad Pin 21): Ground. The exposed pad must be connected to a continuous ground plane on the second layer of the printed circuit board by several vias directly under the part to achieve optimum thermal conduction.

LINEAR

## SIMPLIFIED BLOCK DIAGRAM

Figure 1. LTC3355 Block Diagram

## **OPERATION**

The LTC3355 is a 1A buck regulator with a built-in backup boost converter to allow temporary backup, or ride-through, of  $V_{OUT}$  during a sudden loss of  $V_{IN}$  power. The device contains all functions necessary to provide seamless charging of a supercapacitor (or other storage element), monitoring of  $V_{IN}$ ,  $V_{OUT}$  and  $V_{CAP}$ , and automatic switch-over to backup power. When the buck is disabled an internal circuit blocks reverse current between  $V_{OUT}$  and  $V_{IN}$ .

### Start-Up

When the part first starts up the only voltage available is  $V_{IN}$  since  $V_{OUT}$  and  $V_{CAP}$  are at zero volts. An internal 2.5V regulator powers INTV<sub>CC</sub> from  $V_{IN}$  during start-up. INTV<sub>CC</sub> powers all of the low voltage circuits. The buck regulator is enabled and will drive  $V_{OUT}$  positive through an inductor until the feedback voltage at FB equals 0.8V. When  $V_{OUT}$  exceeds 2.5V INTV<sub>CC</sub> will exactly track  $V_{OUT}$  and the current for the internal low voltage circuits will now be supplied from  $V_{OUT}$  instead of  $V_{IN}$ . A 1µF external ceramic capacitor is required for INTV<sub>CC</sub> to filter internal switching noise.

## **Buck Switching Regulator**

The LTC3355 uses a 1MHz constant frequency peak current mode nonsynchronous monolithic buck regulator with internal slope compensation to control the voltage at  $V_{OUT}$  when  $V_{IN}$  is available. An error amplifier compares the divided output voltage at FB with a reference voltage of 0.8V and adjusts the peak inductor current accordingly. Burst Mode operation can also be selected to optimize efficiency at low load currents via the MODE pin. The buck is in PWM mode when the MODE pin is low and in Burst Mode operation when the MODE pin is high. The buck is internally compensated and can operate over an input voltage range of 3V to 20V. An internal soft-start ramp limits inrush current during start-up. Frequency foldback protection helps to prevent inductor current runaway during start-up or short-circuit conditions.

### **Input Current Limit**

The (optional) input current limit is programmed via an external sense resistor connected between  $V_{INS}$  and  $V_{IN}$ . As the input current limit is reached the charge current

will be reduced. If the charge current has been reduced to zero and the input current continues to increase the buck regulator current drive capability will be reduced. The maximum sense voltage is 50mV. The input current limit includes the LTC3355 quiescent current for high accuracy over a wide current range.

#### **Boost Switching Regulator**

When V<sub>IN</sub> is not available, a monolithic 1MHz constant frequency peak current mode boost regulator with internal slope compensation is enabled and the buck regulator is disabled via the PFI pin. The boost regulator uses the voltage stored at V<sub>CAP</sub> as an input supply and regulates the V<sub>OUT</sub> voltage. An error amplifier compares the divided output voltage at FB with a reference voltage of 0.8V and adjusts the peak inductor current accordingly. The I<sub>BSTPK</sub> pin sets the peak boost current over a range of 1A to 5A allowing for lower current backup applications. The boost switching regulator is compensated by adding a series RC network from the V<sub>CBST</sub> pin to ground. The boost regulator can operate over an input voltage range (V<sub>CAP</sub>) of 0.5V to 5V. The boost regulator uses the same feedback pin and error amplifier as the buck and regulates to the same V<sub>OUT</sub> voltage. The MODE pin is used to control the boost switching regulator mode. The boost is in PWM mode when the MODE pin is low and in Burst Mode operation when the MODE pin is high. In PWM mode as the load current is decreased, the switch turns on for a shorter period each cycle. If the load current is further decreased, the boost converter will skip cycles to maintain output voltage regulation.

## Charger

The supercapacitor is charged by an internal 1A constant current/constant voltage linear charger that supplies current from  $V_{OUT}$  to  $V_{CAP}.$  The charger will be enabled when  $V_{IN}$  is above a programmable voltage via the PFI pin, when the EN\_CHG pin is high and when  $V_{OUT}$  is in regulation. The value of the resistor on the  $I_{CHG}$  pin determines the charger current. An internal amplifier servos the  $I_{CHG}$  voltage to 0.8V to create the reference current for the charge. The  $V_{CAP}$  voltage is divided down by an external resistor divider that is connected to the CFB pin. A hysteretic comparator compares the CFB voltage to a

3355fb

## **OPERATION**

0.8V reference voltage and turns the charger off when these voltages are the same. The  $V_{CAP}$  voltage represents the fully charged supercapacitor voltage available to supply the boost regulator when  $V_{IN}$  has dropped out. When CFB decays to 30mV below the CFB reference voltage the charger will be turned on. The LTC3355 includes a soft-start circuit to minimize the inrush current at the start of charge. When the charger is enabled, the charge current ramps from zero to full-scale over a period of approximately 1ms. This has the effect of minimizing the transient load current on  $V_{OUT}$ .

The  $V_{CAP}$  output also has an overvoltage protection circuit which monitors the CFB voltage. If the CFB voltage increases above the CFB reference voltage by 35mV a hysteretic comparator switches in an 8k resistor from  $V_{CAP}$  to ground. This will bleed any excess charge from the supercapacitor. When the CFB voltage decays to the CFB reference voltage the comparator will remove the 8k bleed resistor. Excess charge can come from leakage currents associated with the boost rectifier diode.

#### VIN Status Monitor

The PFI input always monitors the  $V_{IN}$  voltage and determines when  $V_{IN}$  is in dropout.  $V_{IN}$  is divided down by an external resistor divider and this voltage is then compared to a reference voltage of 0.8V. If the PFI voltage is below the reference voltage the buck regulator and the charger will be disabled and the boost regulator will be enabled. The PFOB pin is a 5V open-drain output. This pin is driven internally by the PFI comparator. When the PFI comparator determines that  $V_{IN}$  has dropped out the PFOB output switches low. PFOB is normally connected to a low voltage supply, via an external pull-up resistor. The pull-up resistor for this output can be connected to  $V_{OUT}$  if another supply is not available.

#### **V<sub>OUT</sub> Status Monitor**

The RSTB pin is a 5V open-drain output. An internal comparator determines when  $V_{OUT}$  has reached 92.5% of the programmed regulation voltage which then switches the RSTB pin high. RSTB is normally connected to a low voltage supply ( $V_{OUT}$ ) via an external pull-up resistor.

#### **VCAP** Status Monitor

The CPGOOD pin is a 5V open-drain output. An internal comparator determines when  $V_{CAP}$  has reached 92.5% of the programmed regulation voltage which then switches the CPGOOD pin high. CPGOOD is normally connected to a low voltage supply ( $V_{OLIT}$ ) via an external pull-up resistor.

#### **Thermal Regulation**

As the die temperature increases due to internal power dissipation, a thermal regulator will limit the die temperature to 110°C by reducing the charger current. The thermal regulation protects the LTC3355 from excessive temperature and allows the user to push the limits of the power handling capability of a given circuit board without the risk of damaging the LTC3355. Another feature is that the charge current can be set according to typical, rather than worst-case ambient temperatures for a given application with the assurance that the charger will automatically reduce the charge current in worst-case conditions.

#### Thermal Shutdown

The LTC3355 includes a thermal shutdown circuit in addition to the thermal regulator. If for any reason, the die temperature exceeds 155°C, the entire part shuts down. The part will resume normal operation once the temperature drops about 15°C, to approximately 140°C.

### **V<sub>OUT</sub>** Overvoltage, Undervoltage Lockout

The LTC3355 includes an overvoltage protection circuit to ensure that  $V_{OUT}$  does not exceed 5.65V (nominal). An internal resistor divider from  $V_{OUT}$  is connected to an amplifier that will regulate  $V_{OUT}$  as the overvoltage limit is reached. The LTC3355 includes undervoltage lockout which disables the boost when  $V_{OUT}$  is < 2V typical.

#### **FB Resistor Network**

The  $V_{OUT}$  voltage is programmed with a resistor divider between the  $V_{OUT}$  pin and the FB pin. Choose the resistor values according to:

$$R1 = R2 \left( \frac{V_{OUT}}{0.8V} - 1 \right)$$

Reference designators refer to the Block Diagram. 1% resistors are recommended to maintain output voltage accuracy.

#### **CFB Resistor Network**

The  $V_{CAP}$  voltage is programmed with a resistor divider between the  $V_{CAP}$  pin and the CFB pin. Choose the resistor values according to:

$$R3 = R4 \left( \frac{V_{CAP}}{0.8V} - 1 \right)$$

Reference designators refer to the Block Diagram. 1% resistors are recommended to maintain the capacitor float voltage accuracy.

## **I<sub>CHG</sub> Set Resistor**

The charge current at  $V_{CAP}$  is set by connecting a resistor from  $I_{CHG}$  to ground. Choose the resistor value according to:

Charger Current (Amps) =

$$\frac{60400}{R5}$$

Reference designators refer to the Block Diagram. 1% resistors are recommended to maintain charge current accuracy.

#### **IBSTPK Set Resistor**

The boost peak current limit is set by connecting a resistor from  $I_{\text{BSTPK}}$  to ground. Choose the resistor value according to:

Boost Peak Current Limit (Amps) =

$$\frac{1E6}{R6}$$

Reference designators refer to the Block Diagram. 1% resistors are recommended to maintain boost peak current accuracy.

#### PFI Resistor Network

The  $V_{IN}$  dropout voltage is programmed with a resistor divider between the  $V_{IN}$  pin and PFI pin. Choose the resistor values according to:

$$R7 = R8 \left( \frac{V_{IN}}{0.8V} - 1 \right)$$

Reference designators refer to the Block Diagram. 1% resistors are recommended to maintain the PFI threshold voltage accuracy.

The  $V_{IN}$  voltage must be greater than the buck dropout voltage (100% duty cycle) when the PFI level is reached to ensure that  $V_{OLIT}$  stays in regulation.

#### **Input Voltage Range**

The minimum input voltage is determined by the dropout of the buck regulator. The dropout is dependent on the maximum load current and the buck internal switch resistance. The minimum input voltage due to buck dropout is:

$$V_{IN(MIN)} = V_{OUT} + (I_{SW(PEAK)} \cdot 1\Omega)$$

### Buck Inductor L1 Selection and Maximum Output Current

A good starting point for the inductor value is:

$$L = (V_{OUT} + V_D) \bullet \frac{1.8}{f_{SW}}$$

where  $f_{SW}$  is the switching frequency in MHz,  $V_{OUT}$  is the buck output voltage,  $V_D$  is the catch diode drop (~0.5V) and L is the inductor value in  $\mu$ H.

The inductor's RMS current rating must be greater than the maximum load current and its saturation current should be 30% higher. To keep the efficiency high, the series resistance (DCR) should be less than  $0.1\Omega$ , and the core material should be intended for high frequency applications. Table 1 lists several inductor vendors.

For robust operation and fault conditions (start-up or short-circuit) and high input voltage (>15V), the saturation current should be chosen high enough to ensure that the inductor peak current does not exceed 2.2A.

The current in the inductor is a triangle wave with an average value equal to the load current. The peak inductor and switch current is:

$$I_{SW(PEAK)} = I_{L(PEAK)} = I_{OUT(MAX)} + \frac{\Delta I_L}{2}$$

where  $I_{L(PEAK)}$  is the peak inductor current,  $I_{OUT(MAX)}$  is the maximum output load current and  $\Delta I_{L}$  is the inductor ripple current. The LTC3355 limits the switch current in order to protect the part. Therefore, the maximum output current that the buck will deliver depends on the switch current limit, the inductor value, the input and output voltages.

When the switch is off, the potential across the inductor is the output voltage plus the catch diode drop. This gives the peak-to-peak ripple current in the inductor:

$$\Delta I_{L} = (1 - DC) \bullet \frac{V_{OUT} + V_{D}}{L \bullet f_{SW}}$$

where  $f_{SW}$  is the switching frequency of the buck, DC is the duty cycle and L is the value of the inductor.

To maintain output regulation, the inductor peak current must be less than the buck switch current limit. The maximum output current is:

$$I_{OUT(MAX)} = I_{LIM} - \frac{\Delta I_L}{2}$$

Choosing an inductor value so that the ripple current is small will allow a maximum output current near the switch current limit.

**Table 1. Inductor Vendors**

| VENDOR    | URL               | PART SERIES      | TYPE     |

|-----------|-------------------|------------------|----------|

| Murata    | www.murata.com    | LQH5BPB          | Shielded |

| TDK       | www.tdk.com       | LTF5022T         | Shielded |

| Toko      | www.toko.com      | FDS50xx          | Shielded |

| Coilcraft | www.coilcraft.com | XAL40xx, LPS40xx | Shielded |

| Sumida    | www.sumida.com    | DCRH5D, CDRH6D   | Shielded |

| Viashay   | www.vishay.com    | IHLP2020         | Shielded |

One approach to choosing the inductor is to start with the simple rule above, look at the available inductors, and choose one to meet cost or space goals. Then use the equations to check that the buck will be able to deliver the required output current. These equations assume that the inductor current is continuous. Discontinuous operation occurs when  $I_{OUT}$  is less than  $\Delta I_L/2$ .

#### **Buck Input Capacitor**

Bypass  $V_{IN}$  and  $V_{INS}$  with a ceramic capacitor of X7R or X5R type. A  $10\mu$ F to  $22\mu$ F ceramic capacitor is adequate for bypassing. Note that a larger  $V_{INS}$  bypass capacitor may be required if the input power supply source impedance is high or there is significant inductance due to long wires or cables. This can be provided with a lower performance electrolytic capacitor in parallel with the ceramic capacitor.

Buck regulators draw current from the input supply in pulses with very fast rise and fall times. The input capacitors are required to reduce the resulting voltage ripple at  $V_{INS}$  and  $V_{IN}$  and to force this very high frequency switching into a tight local loop, minimizing EMI. The capacitors must be placed close to the LTC3355 pins.

### **Output Capacitor and Output Ripple**

The output capacitor has two essential functions. Along with the inductor, it filters the square wave generated by the buck regulator to produce the DC output. In this role it determines the output ripple, and low impedance at the switching frequency is important. The second function is to store energy in order to satisfy transient loads and stabilize the buck regulator control loop. Ceramic capacitors have very low equivalent series resistance (ESR) and provide the best ripple performance. A good starting value is:

$$C_{OUT} = f_{SW} \left( \frac{100}{V_{OUT}} \right)$$

where  $f_{SW}$  is in MHz and  $C_{OUT}$  is the recommended output capacitance in  $\mu F$ . Use X5R or X7R types. This choice will provide low output ripple and good transient response.

When choosing a capacitor look carefully through the data sheet to find out what the actual capacitance is under

operating conditions (applied voltage and temperature). A physically larger capacitor, or one with a higher voltage rating, may be required. High performance tantalum or electrolytic capacitors can be used for the output capacitor.

Low ESR is important, so choose one that is intended for use in switching regulators. The ESR should be specified by the supplier, and should be  $0.05\Omega$  or less. Table 2 lists several capacitor vendors.

**Table 2. Capacitor Vendors**

| VENDOR      | URL                 | PART SERIES                   | COMMANDS              |

|-------------|---------------------|-------------------------------|-----------------------|

| Panasonic   | www.panasonic.com   | Ceramic, Polymer,<br>Tantalum | EEF Series,<br>POSCAP |

| Kemet       | www.kemet.com       | Ceramic, Tantalum             | T494, T495            |

| Murata      | www.murata.com      | Ceramic                       |                       |

| AVX         | www.avxcorp.com     | Ceramic, Tantalum             | TPS Series            |

| Taiyo Yuden | www.taiyo-yuden.com | Ceramic                       |                       |

#### **Buck Catch Diode Selection**

The catch diode (D1 in the Block Diagram) conducts current only during the switch-off time. The average forward current in normal operation can be calculated from:

$$I_{D(AVG)} = I_{OUT}(1 - DC)$$

where DC is the duty cycle. The only reason to consider a diode with a larger current rating than necessary for nominal operation is for the case of shorted or overloaded output conditions. For the worst case of shorted output the diode average current will then increase to a value that depends on the switch current limit.

If operating at high temperatures select a Schottky diode with low reverse leakage current.

#### **Audible Noise**

Ceramic capacitors are small, robust and have very low ESR. However, ceramic capacitors can sometimes cause problems when used with switching regulators. Both the buck and boost can run in Burst Mode operation and the switching frequency will depend on the load current which at very light loads can excite the ceramic capacitors at audio frequencies, generating audible noise. Since the buck and boost operate at lower current limits in Burst Mode operation, the noise is typically very quiet. Use a high performance tantalum or electrolytic at the output if the noise level is unacceptable.

#### **Buck Soft-Start**

When the buck is enabled soft-start is engaged. Soft-start reduces the inrush current by taking more time to reach the final output voltage. This is achieved by limiting the buck output current over a 1ms period.

#### **Boost Rectifier Diode**

A Schottky rectifier diode (D2 in the Block Diagram) is recommended for the boost rectifier diode. The diode should have low forward drop at the peak operating current, low reverse current and fast reverse recovery times. The current rating should take into account power dissipation as well as output current requirements. The diode current rating should be equal to or greater than the average forward current which is normally equal to the output current. The reverse breakdown voltage should be greater than the  $V_{OUT}$  voltage plus the peak ringing voltage that is generated at the SW2 pin. Generally higher reverse breakdown diodes will have lower reverse currents. Refer to Table 3 for Schottky diode vendors.

Table 3. Schottky Diode Vendors

| PART NUMBER | V <sub>R</sub> (V) | I <sub>AVE</sub> (A) | V <sub>F</sub> AT 1A<br>(mV) | V <sub>F</sub> AT 2A (mV) | I <sub>R</sub> AT 5V<br>85°C (μΑ) |

|-------------|--------------------|----------------------|------------------------------|---------------------------|-----------------------------------|

| Diodes Inc. |                    |                      |                              |                           |                                   |

| B130        | 30                 | 1                    | 460                          |                           | 20                                |

| B230        | 30                 | 2                    |                              | 430                       | 100                               |

| Rohm        |                    |                      |                              |                           |                                   |

| RSX201VA-30 | 30                 | 1                    | 360                          |                           | 600                               |

| Vishay      |                    |                      |                              |                           |                                   |

| VS-20MQ060  | 60                 | 2.1                  |                              |                           |                                   |

# Boost Inductor L2 Selection and Maximum Output Current

The boost inductor L2 should be  $3.3\mu H$  to ensure fast transfer of power from the buck to the boost after a  $V_{IN}$  power outage. Refer to Table 1 for inductor vendors.

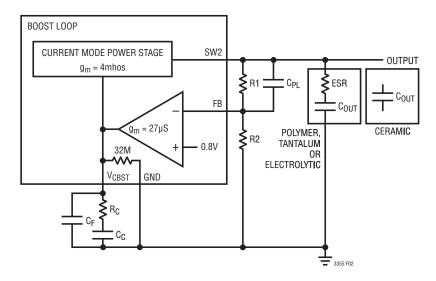

#### **Boost Frequency Compensation**

The LTC3355 boost switching regulator uses current mode control to regulate  $V_{OUT}$ . This simplifies loop compensation and ceramic output capacitors can be used. The boost regulator does not require the ESR of the output capacitor for stability. Frequency compensation is provided by the components connected to the  $V_{CBST}$  pin. Generally a capacitor ( $C_C$ ) and resistor ( $R_C$ ) in series to ground are used as shown in the Block Diagram.

Loop compensation determines the stability and transient performance. Optimizing the design of the compensation network depends on the application and type of output capacitor. A practical approach is to start with one of the circuits in this data sheet that is similar to your application and tune the compensation network to optimize the performance. Stability should then be checked across all

operating conditions, including load current, input voltage and temperature. Figure 2 shows an equivalent circuit for the boost regulator control loop. The error amplifier is a transconductance amplifier with a finite output impedance. The power section consisting of a modulator, power switch and inductor, is modeled as a transconductance amplifier generating an output current proportional to the voltage at the  $V_{CBST}$  pin. Note that the output capacitor integrates this current, and that the capacitor on the  $V_{CBST}$  pin ( $C_C$ ) integrates the error amplifier output current, resulting in two poles in the loop. In most cases a zero is required and comes from either the ESR of the output capacitor or from a resistor R<sub>C</sub> in series with C<sub>C</sub>. This simple model works well as long as the inductor value is not too high and the loop crossover frequency is much lower than the switching frequency. A phase lead capacitor across the feedback divider may improve the transient response. A small capacitor from V<sub>CBST</sub> to ground may have to be added if phase lead is used.

#### **Low Ripple Burst Mode Operation**

To enhance efficiency at light loads the buck and boost regulator can run in low ripple Burst Mode operation which keeps the output capacitor charged to the proper voltage while minimizing the input quiescent current. Setting the MODE pin high sets both the buck and boost into Burst Mode operation. During Burst Mode operation, the enabled regulator delivers single cycle bursts of current to the output capacitor followed by sleep periods where the power is delivered to the load by the output capacitor. Since the power to the output is delivered with single, low current pulses, the output ripple is kept below 15mV for typical applications. As the load current falls towards a no-load condition, the percentage of time in sleep mode increases and the average input current is greatly reduced resulting in high efficiency even at very light loads. At higher load currents the regulators will seamlessly transition into PWM mode.

Figure 2. Model for Boost Loop Response

#### **PCB** Layout

For proper operation and minimum EMI, care must be taken during printed circuit board layout. Large switched currents flow in the V<sub>IN</sub>, SW1, SW2 and paddle ground pins, the buck catch diode, boost rectifier diode and the input capacitor. The loop formed by these components should be as small as possible. These components, along with the inductors and output capacitor, should be placed on the same side of the circuit board, and their connections should be made on that layer. All connections to GND should be made at a common star ground point or directly to a local, unbroken ground plane below these components. SW1 and SW2 nodes should be laid out carefully to avoid interference. Keep the FB, PFI, I<sub>CHG</sub>, I<sub>BSTPK</sub>, V<sub>CBST</sub> and CFB nodes small so that the ground traces will shield them from the switching nodes. To keep thermal resistance low, extend the ground plane as much as possible and add thermal vias under and near the paddle. Keep in mind that the thermal design must keep the junctions of the LTC3355 below the specified absolute maximum temperature.

#### **High Temperature Considerations**

The PCB must provide heat sinking to keep the LTC3355 cool. The exposed pad on the bottom of the package may be soldered to a copper area which should be tied to large copper layers below with thermal vias; these layers will spread the heat dissipated by the LTC3355. Place additional vias to reduce thermal resistance further. With these steps, the thermal resistance from the die (or junction) to ambient can be reduced to  $\theta_{JA} = 47^{\circ}\text{C/W}$  or less. With 100 LFPM airflow, this resistance can fall by another 25%.

The LTC3355 has two thermal circuits. The first thermal circuit is operational when the buck and charger are enabled. If the die temperature exceeds 110°C the charge current will be reduced. When the LTC3355 is in boost mode the high current thermal shutdown will turn the boost off when the die temperature reaches 155°C. The high temperature shutdown is active in all modes of operation.

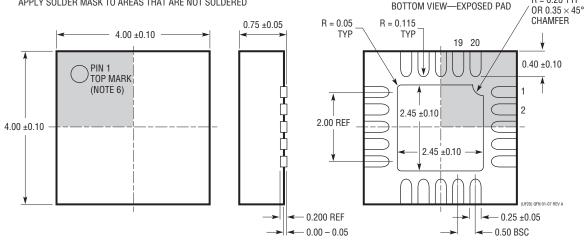

## TYPICAL APPLICATIONS

#### Tantalum Capacitor Charger and Ride-Through Backup Supply

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

## **UF Package** 20-Lead Plastic QFN (4mm × 4mm)

(Reference LTC DWG # 05-08-1710 Rev A)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- 1. DRAWING IS PROPOSED TO BE MADE A JEDEC PACKAGE OUTLINE MO-220 VARIATION (WGGD-1)—TO BE APPROVED

- 2. DRAWING NOT TO SCALE

- ALL DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

PIN 1 NOTCH

R = 0.20 TYP

## **REVISION HISTORY**

| REV | DATE                                                                      | DESCRIPTION                                                                      | PAGE NUMBER |

|-----|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------|

| Α   | 08/14 Modified V <sub>OUT</sub> Overvoltage, Undervoltage Lockout section |                                                                                  | 11          |

|     |                                                                           | Modified Input Voltage Range equation                                            | 12          |

|     |                                                                           | Modified I <sub>CHG</sub> Set Resistor section                                   | 12          |

|     |                                                                           | Modified I <sub>BSTPK</sub> Set Resistor section                                 | 12          |

| В   | 4/15                                                                      | Updated conditions for I <sub>SW1</sub> , I <sub>SW2</sub> and I <sub>VOUT</sub> | 3 and 4     |

|     |                                                                           | Updated units for Boost Error Amplifier Transconductance                         | 4           |

|     |                                                                           | Updated units for Boost Error Amplifier Transconductance vs Temperature Graph    | 7           |

|     |                                                                           | Update TSTB (Pin 13), CPGOOD (Pin 9), PFOB (Pin 10)                              | 8           |

|     |                                                                           | Updated Block Diagram                                                            | 9           |

|     |                                                                           | Updated CFB Resistor Network and PFI Resistor Network                            | 12          |

|     |                                                                           | Updated Table 2: Capacitor Vendors                                               | 14          |

|     |                                                                           | Updated Boost Error Amplifier Transconductance unit in Figure 2                  | 16          |

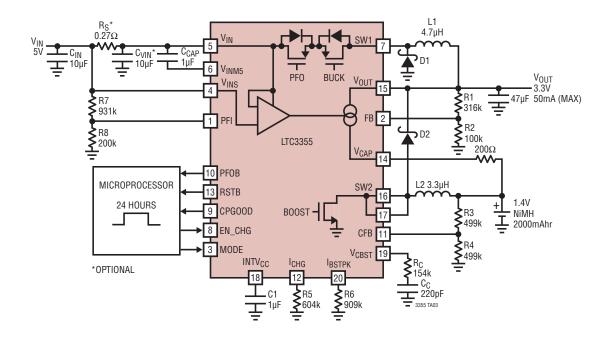

## TYPICAL APPLICATION

#### NiMH Trickle Charger and Ride-Through Backup Supply

## **RELATED PARTS**

| PART<br>NUMBER        | DESCRIPTION                                                                            | COMMENTS                                                                                                                                                                                                                                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3225/<br>LTC3225-1 | 150mA Supercapacitor Charger                                                           | Low Noise, Constant Frequency Charging of Two Series Supercapacitors. Automatic Cell Balancing Prevents Capacitor Overvoltage During Charging. Programmable Charge Current (Up to 150mA). 2mm × 3mm DFN Package                                                                                                                            |

| LTC3226               | 2-Cell Supercapacitor Charger with Backup<br>PowerPath™ Controller                     | 1×/2× Multimode Charge Pump Supercapacitor Charger Ideal Diode Main PowerPath™<br>Controller, Internal 2A LDO Back-Up Supply, 16-Lead (3mm × 3mm) QFN Package                                                                                                                                                                              |

| LT3485                | Photoflash Capacitor Chargers with Output<br>Voltage Monitor and Integrated IGBT Drive | Integrated IGBT Driver; Voltage Output Monitor; Uses Small Transformers: 5.8mm × 5.8mm × 3mm. Operates from Two AA Batteries, Single Cell Li-Ion or Any Supply from 1.8V Up to 10V. No Output Voltage Divider Needed; No External Schottky Diode Required. Charges Any Size Photoflash Capacitor; 10-Lead (3mm × 3mm) DFN Package          |

| LTC3625/<br>LTC3625-1 | 1A High Efficiency 2-Cell Supercapacitor<br>Charger with Automatic Cell Balancing      | High Efficiency Step-Up/Step-Down Charging of Two Series Supercapacitors. Automatic Cell Balancing Prevents Capacitor Overvoltage During Charging. Programmable Charging Current Up to 500mA (Single Inductor), 1A (Dual Inductor). $V_{\text{IN}}$ = 2.7V to 5.5V, Low No-Load Quiescent Current: 23µA. 12-lead 3mm × 4mm DFN Package     |

| LT®3750               | Capacitor Charger Controller                                                           | Charges Any Size Capacitor; Easily Adjustable Output Voltage. Drives High Current NMOS FETs; Primary-Side Sense—No Output Voltage Divider Necessary. Wide Input Range: 3V to 24V; Drives Gate to $V_{CC}$ – 2V. 10-Lead MS Package                                                                                                         |

| LT3751                | High Voltage Capacitor Charger Controller with Regulation                              | Charges Any Size Capacitor; Low Noise Output in Voltage Regulation Mode. Stable Operation Under a No-Load Condition; Integrated 2A MOSFET Gate Driver with Rail-to-Rail Operation for $V_{CC} \le 8V$ . Wide Input $V_{CC}$ Voltage Range (5V to 24V). 20-Pin QFN 4mm $\times$ 5mm and 20-Lead TSSOP Packages                              |

| LTC4425               | Supercapacitor Charger with Current Limited Ideal Diode                                | Constant-Current/Constant-Voltage Linear Charger for 2-cell Series Supercapacitor Stack. V <sub>IN</sub> : Li-Ion/Polymer Battery, a USB Port, or a 2.7V to 5.5V Current-Limited Supply. 2A Charge Current, Auto Cell Balancing, 20µA Quiescent Current, Shutdown Current <2µA. Low Profile 12-Pin 3mm × 3mm DFN or a 12-Lead MSOP Package |

LT 0415 REV B • PRINTED IN USA

TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2014

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Analog Devices Inc.:

LTC3355IUF#PBF LTC3355IUF#TRPBF LTC3355EUF#TRPBF LTC3355EUF#PBF DC2040A