# Programmable Quad Supply Monitor with Adjustable Reset and Watchdog Timers

### **FEATURES**

- Simultaneously Monitors Four Supplies

- 16 User Selectable Combinations of 5V, 3.3V, 3V, 2.5V, 1.8V, 1.5V and/or ±Adj Voltage Thresholds

- Guaranteed Threshold Accuracy: ±1.5% of Monitored Voltage Over Temperature

- Selectable Supply Tolerance: 5% and 10% Below Monitored Voltage (LTC2901-3/LTC2901-4)

- Low Supply Current: 43µA Typ

- Adjustable Reset Time

- Adjustable Watchdog Time

- Open-Drain RST Output (LTC2901-1/LTC2901-3)

- Push-Pull RST Output (LTC2901-2/LTC2901-4)

- Individual Nondelayed Monitor Output for Each Supply

- Power Supply Glitch Immunity

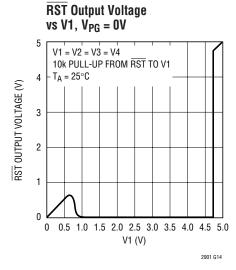

- Guaranteed  $\overline{RST}$  for  $V_{CC} \ge 1V$

- 16-Lead Narrow SSOP Package

## **APPLICATIONS**

- Desktop and Notebook Computers

- Multivoltage Systems

- Telecom Equipment

- Portable Battery-Powered Equipment

- Network Servers

### DESCRIPTION

The LTC®2901 is a programmable supply monitor for systems with up to four supply voltages. One of 16 preset or adjustable voltage monitor combinations can be selected using an external resistor divider connected to the program pin. The preset voltage thresholds are accurate to  $\pm 1.5\%$  over temperature. All four voltage comparator outputs are connected to separate pins for individual supply monitoring.

The reset and watchdog delay times are adjustable using external capacitors. Tight voltage threshold accuracy and glitch immunity ensure reliable reset operation without false triggering. The  $\overline{RST}$  output is guaranteed to be in the correct state for  $V_{CC}$  down to  $\underline{1V}$ . The LTC2901-1/LTC2901-3 features an open-drain  $\overline{RST}$  output, while the LTC2901-2/LTC2901-4 has a push-pull  $\overline{RST}$  output.

The  $43\mu A$  supply current makes the LTC2901 ideal for power conscious systems and it may be configured to monitor less than four inputs. The parts are available in the 16-lead narrow SSOP package.

7, LT, LTC and LTM are registered trademarks of Linear Technology Corporation.

Patent Pending.

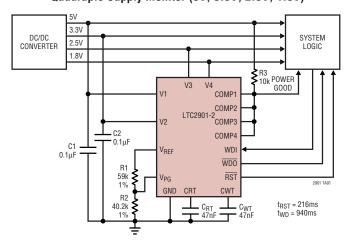

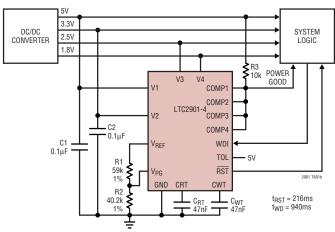

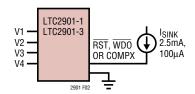

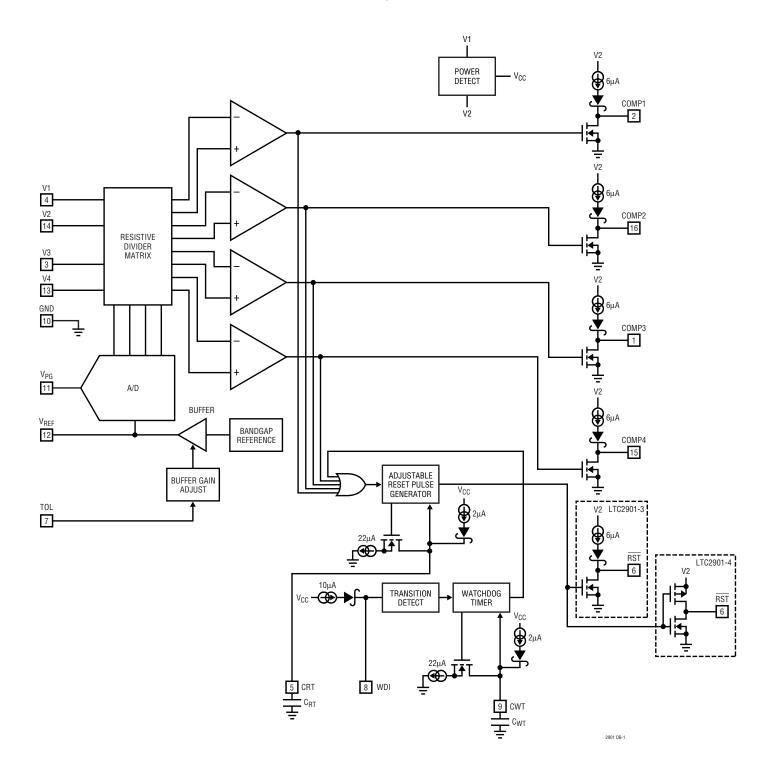

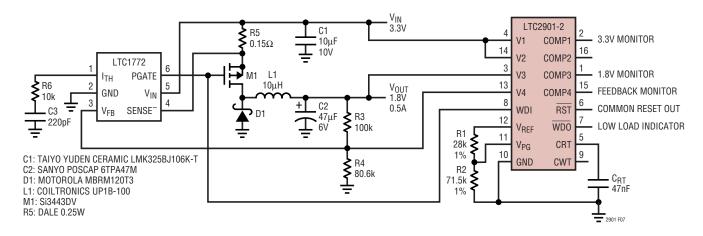

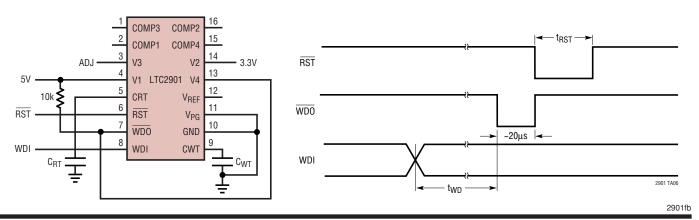

# TYPICAL APPLICATION

Quadruple Supply Monitor (5V, 3.3V, 2.5V, 1.8V)

Quadruple Supply Monitor (5V, 3.3V, 2.5V, 1.8V) 10% Undervoltage Monitoring, Watchdog Asserts RST

# **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2, 3)

| V1, V2, V3, V4, V <sub>PG</sub> | 0.3V to 7V |

|---------------------------------|------------|

| RST (LTC2901-2/LTC2901-4)       |            |

| COMPX                           | 0.3V to 7V |

| CWT, WDI, WDO                   | 0.3V to 7V |

| V <sub>REF</sub> , CRT, TOL     |            |

| Reference Load Current (IVREF)  | ±1mA       |

| V4 Input Current (-ADJ Mode)    | –1mA       |

| 0°C to 70°C     |

|-----------------|

|                 |

| . −40°C to 85°C |

| -65°C to 150°C  |

| 300°C           |

|                 |

# PACKAGE/ORDER INFORMATION

Lead Free Part Marking: http://www.linear.com/leadfree/

| TOP V                                                | /IEW                                                                                         | ORDER PART<br>NUMBER                         | TOP                     | VIEW                                                          | ORDER PART<br>NUMBER                         |

|------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------|---------------------------------------------------------------|----------------------------------------------|

| COMP1 2 V3 3 V1 4                                    | 15 COMP4<br>14 V2<br>13 V4                                                                   | LTC2901-1CGN<br>LTC2901-2CGN<br>LTC2901-1IGN | COMP1 2<br>V3 3<br>V1 4 | 15 COMP4<br>15 COMP4<br>14 V2<br>13 V4                        | LTC2901-3CGN<br>LTC2901-4CGN<br>LTC2901-3IGN |

| CRT 5<br>RST 6<br>WDO 7                              | 12 V <sub>REF</sub><br>11 V <sub>PG</sub><br>10 GND                                          | LTC2901-2IGN<br>GN16 PART MARKING            | CRT 5<br>RST 6<br>TOL 7 | 12 V <sub>REF</sub> 11 V <sub>PG</sub> 10 GND                 | LTC2901-4IGN<br>GN16 PART MARKING            |

| GN PAC<br>16-LEAD PLA<br>T <sub>.IMAX</sub> = 125°C, | ASTIC SSOP                                                                                   | 29011<br>29012<br>29011I<br>29012I           |                         | 9 CWT  CKAGE ASTIC SSOP $\theta_{1A} = 110^{\circ}\text{C/W}$ | 29013<br>29014<br>29013I<br>29014I           |

| 011111                                               | Order Options Tape and Reel: Add #TR Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF |                                              |                         |                                                               | 230141                                       |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$ , unless otherwise noted. (Notes 3, 4)

| SYMBOL            | PARAMETER                                             | CONDITIONS                                                                    |   | MIN            | TYP            | MAX            | UNITS |

|-------------------|-------------------------------------------------------|-------------------------------------------------------------------------------|---|----------------|----------------|----------------|-------|

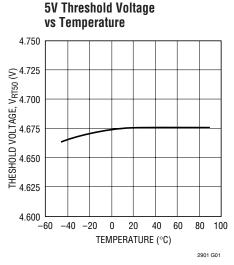

| V <sub>RT50</sub> | 5V, 5% Reset Threshold<br>5V, 10% Reset Threshold     | V1 Input Threshold                                                            | • | 4.600<br>4.350 | 4.675<br>4.425 | 4.750<br>4.500 | V     |

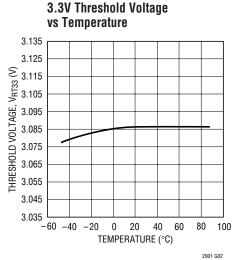

| V <sub>RT33</sub> | 3.3V, 5% Reset Threshold<br>3.3V, 10% Reset Threshold | V1, V2 Input Threshold                                                        | • | 3.036<br>2.871 | 3.086<br>2.921 | 3.135<br>2.970 | V     |

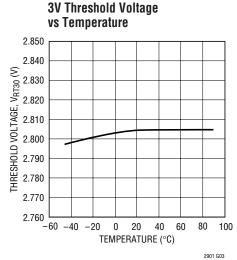

| V <sub>RT30</sub> | 3V, 5% Reset Threshold<br>3V, 10% Reset Threshold     | V2 Input Threshold                                                            | • | 2.760<br>2.610 | 2.805<br>2.655 | 2.850<br>2.700 | V     |

| V <sub>RT25</sub> | 2.5V, 5% Reset Threshold<br>2.5V, 10% Reset Threshold | V2, V3 Input Threshold                                                        | • | 2.300<br>2.175 | 2.338<br>2.213 | 2.375<br>2.250 | V     |

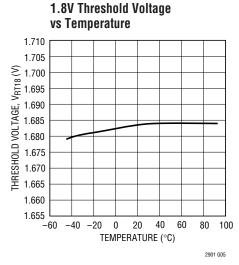

| V <sub>RT18</sub> | 1.8V, 5% Reset Threshold<br>1.8V, 10% Reset Threshold | V3, V4 Input Threshold                                                        | • | 1.656<br>1.566 | 1.683<br>1.593 | 1.710<br>1.620 | V     |

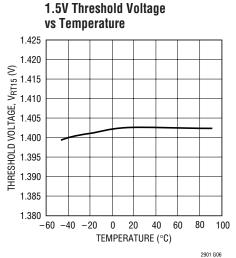

| V <sub>RT15</sub> | 1.5V, 5% Reset Threshold<br>1.5V, 10% Reset Threshold | V3, V4 Input Threshold                                                        | • | 1.380<br>1.305 | 1.403<br>1.328 | 1.425<br>1.350 | V     |

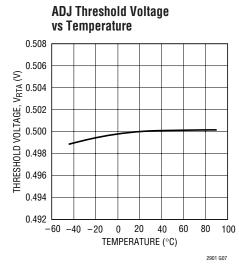

| V <sub>RTA</sub>  | ADJ, 5% Reset Threshold<br>ADJ, 10% Reset Threshold   | V3, V4 Input Threshold                                                        | • | 0.492<br>0.466 | 0.500<br>0.473 | 0.508<br>0.481 | V     |

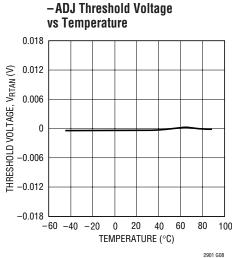

| $V_{RTAN}$        | -ADJ Reset Threshold                                  | V4 Input Threshold                                                            | • | -18            | 0              | 18             | mV    |

| V <sub>CC</sub>   | Minimum Internal Operating Voltage                    | RST, COMPX in Correct Logic State;<br>V <sub>CC</sub> Rising Prior to Program | • |                |                | 1              | V     |

INEAD

2901fb

LINEAR

## **ELECTRICAL CHARACTERISTICS**

The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25$ °C.  $V_{CC} = 5V$ , unless otherwise noted. (Notes 3, 4)

| SYMBOL               | PARAMETER                                                 | CONDITIONS                                                                                             |   | MIN                | TYP            | MAX              | UNITS          |

|----------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---|--------------------|----------------|------------------|----------------|

| V <sub>CCMINP</sub>  | Minimum Required for Programming                          | V <sub>CC</sub> Rising                                                                                 | • |                    |                | 2.42             | V              |

| V <sub>CCMINC</sub>  | Minimum Required for Comparators                          | V <sub>CC</sub> Falling                                                                                | • |                    |                | 2.32             | V              |

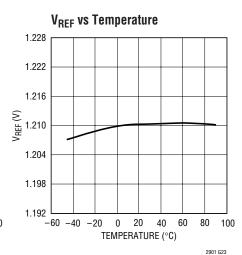

| V <sub>REF</sub>     | Reference Voltage                                         | $V_{CC} \ge 2.3 \text{V}, \ I_{VREF} = \pm 1 \text{mA}, \ C_{REF} \le 1000 \text{pF}$ TOL Low TOL High | • | 1.192<br>1.128     | 1.210<br>1.146 | 1.228<br>1.163   | V              |

| $\overline{V_{PG}}$  | Programming Voltage Range                                 | $V_{CC} \ge V_{CCMINP}$                                                                                | • | 0                  |                | V <sub>REF</sub> | V              |

| I <sub>VPG</sub>     | V <sub>PG</sub> Input Current                             | $V_{PG} = V_{REF}$                                                                                     | • |                    |                | ±20              | nA             |

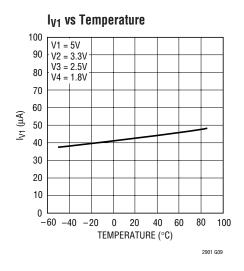

| I <sub>V1</sub>      | V1 Input Current                                          | V1 = 5V, I <sub>VREF</sub> = 12μA, (Note 5)                                                            | • |                    | 43             | 75               | μА             |

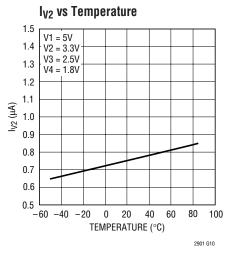

| $\overline{I_{V2}}$  | V2 Input Current                                          | V2 = 3.3V                                                                                              | • |                    | 0.8            | 2                | μА             |

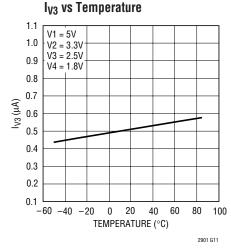

| I <sub>V3</sub>      | V3 Input Current                                          | V3 = 2.5V<br>V3 = 0.55V (ADJ Mode)                                                                     | • | -15                | 0.52           | 1.2<br>15        | μA<br>nA       |

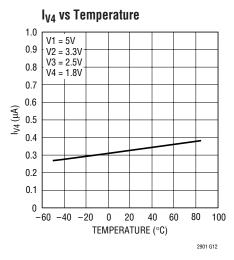

| I <sub>V4</sub>      | V4 Input Current                                          | V4 = 1.8V<br>V4 = 0.55V (ADJ Mode)<br>V4 = -0.05V (-ADJ Mode)                                          | • | -15<br>-15         | 0.34           | 0.8<br>15<br>15  | μA<br>nA<br>nA |

| I <sub>CRT(UP)</sub> | CRT Pull-Up Current                                       | V <sub>CRT</sub> = 0V                                                                                  | • | -1.4               | -2             | -2.6             | μА             |

| I <sub>CRT(DN)</sub> | CRT Pull-Down Current                                     | V <sub>CRT</sub> = 1.3V                                                                                | • | 10                 | 20             | 30               | μА             |

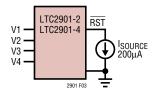

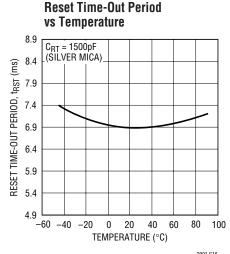

| t <sub>RST</sub>     | Reset Time-Out Period                                     | C <sub>RT</sub> = 1500pF                                                                               | • | 5                  | 7              | 9                | ms             |

| t <sub>UV</sub>      | V <sub>X</sub> Undervoltage Detect to RST or COMPX        | V <sub>X</sub> Less Than Reset Threshold V <sub>RTX</sub> by More Than 1%                              |   |                    | 150            |                  | μѕ             |

| $V_{0L}$             | Output Voltage Low RST, COMPX                             | I <sub>SINK</sub> = 2.5mA; V1 = 3V, V2 = 3V;<br>V3, V4 = 0V; V <sub>PG</sub> = 0V                      | • |                    | 0.15           | 0.4              | V              |

|                      |                                                           | $I_{SINK} = 100\mu A; V2 = 1V; V1, V3, V4 = 0V$<br>$I_{SINK} = 100\mu A; V1 = 1V; V2, V3, V4 = 0V$     | • |                    | 0.05<br>0.05   | 0.3<br>0.3       | V              |

| V <sub>OH</sub>      | Output Voltage High RST, WDO, COMPX (Note 6)              | I <sub>SOURCE</sub> = 1μA                                                                              | • | V2 – 1             |                |                  | V              |

| V <sub>OL</sub>      | Output Voltage Low WDO                                    | I <sub>SINK</sub> = 2.5mA; V1 = 5V, V2 = 3.3V;<br>V3, V4 = 1V; V <sub>PG</sub> = 0V                    | • |                    | 0.15           | 0.4              | V              |

| V <sub>OH</sub>      | Output Voltage High RST<br>(LTC2901-2/LTC2901-4) (Note 7) | I <sub>SOURCE</sub> = 200μA                                                                            | • | 0.8 • V2           |                |                  | V              |

| I <sub>CWT(UP)</sub> | CWT Pull-Up Current                                       | V <sub>CWT</sub> = 0V                                                                                  | • | -1.4               | -2             | -2.6             | μΑ             |

| I <sub>CWT(DN)</sub> | CWT Pull-Down Current                                     | V <sub>CWT</sub> = 1.3V                                                                                | • | 10                 | 20             | 30               | μА             |

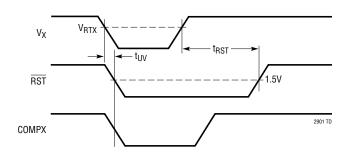

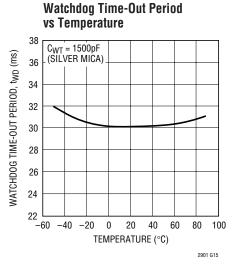

| t <sub>WD</sub>      | Watchdog Time-Out Period                                  | C <sub>WT</sub> = 1500pF                                                                               | • | 20                 | 30             | 40               | ms             |

| $V_{IH}$             | WDI Input Threshold High                                  | V <sub>CC</sub> = 3.3V to 5.5V                                                                         | • |                    |                | 1.6              | V              |

| $V_{IL}$             | WDI Input Threshold Low                                   | V <sub>CC</sub> = 3.3V to 5.5V                                                                         | • | 0.4                |                |                  | V              |

| t <sub>WP</sub>      | WDI Input Pulse Width                                     | V <sub>CC</sub> = 3.3V                                                                                 | • | 150                |                |                  | ns             |

| I <sub>WDI</sub>     | WDI Pull-Up Current                                       | V <sub>WDI</sub> = 0V                                                                                  |   |                    | -10            |                  | μΑ             |

| Digital Inpu         | ut TOL                                                    |                                                                                                        |   |                    |                |                  |                |

| $V_{IL}$             | TOL Low Level Input Voltage                               | V <sub>CC</sub> = 3.3V to 5.5V                                                                         | • |                    |                | $0.3V_{CC}$      | V              |

| V <sub>IH</sub>      | TOL High Level Input Voltage                              | V <sub>CC</sub> = 3.3V to 5.5V                                                                         | • | 0.7V <sub>CC</sub> |                |                  | V              |

| I <sub>INTOL</sub>   | TOL Input Current                                         | TOL = V <sub>CC</sub>                                                                                  | • |                    | ±0.1           | ±1               | μΑ             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive, all voltages are referenced to GND unless otherwise noted.

**Note 3:** The greater of V1, V2 is the internal supply voltage  $(V_{CC})$ .

**Note 4:** 10% thresholds apply to the LTC2901-3/LTC2901-4 only when the TOL pin is set to a logic high.

**Note 5:** Under static no-fault conditions, V1 will necessarily supply quiescent current. If at any time V2 is larger than V1, V2 must be capable of supplying the quiescent current, programming (transient) current and reference load current.

**Note 6:** The output pins  $\overline{RST}$ ,  $\overline{WDO}$  and COMPX have internal pull-ups to V2 of typically  $6\mu A$ . However, external pull-up resistors may be used when faster rise times are required or for  $V_{OH}$  voltages greater than V2.

**Note 7:** The push-pull  $\overline{RST}$  output pin on the LTC2901-2/LTC2901-4 is *actively* pulled up to V2.

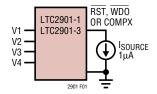

# **TEST CIRCUITS**

Figure 2.  $\overline{RST}$ ,  $\overline{WDO}$ , COMPX  $V_{OL}$  Test

Figure 3. Active Pull-Up  $\overline{\mbox{RST}}$  V<sub>OH</sub> Test

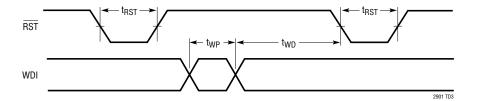

# TIMING DIAGRAMS

#### **V<sub>X</sub> Monitor Timing**

#### Watchdog Timing (LTC2901-1/LTC2901-2)

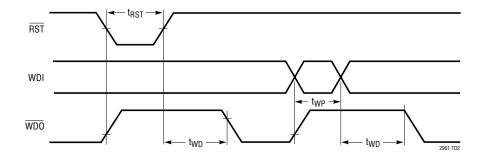

### Watchdog Timing (LTC2901-3/LTC2901-4)

TECHNOLOGY TECHNOLOGY

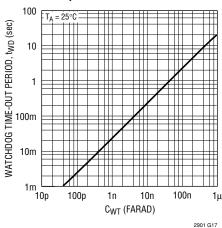

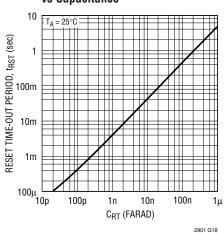

# TYPICAL PERFORMANCE CHARACTERISTICS

# 2.5V Threshold Voltage vs Temperature 2.3750 2.3675 2.3600 2.3450 2.3450 2.3375 2.3300 2.3225 2.3150 2.3000 -60 -40 -20 0 20 40 60 80 100 TEMPERATURE (°C)

# TYPICAL PERFORMANCE CHARACTERISTICS

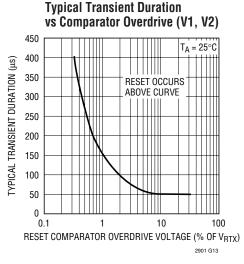

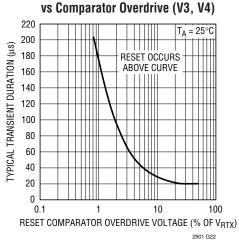

**Typical Transient Duration**

# TYPICAL PERFORMANCE CHARACTERISTICS

# Watchdog Time-Out Period vs Capacitance

# Reset Time-Out Period vs Capacitance

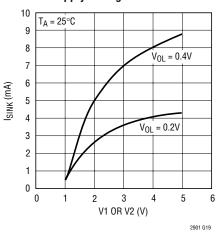

RST, WDO, COMPX I<sub>SINK</sub> vs Supply Voltage

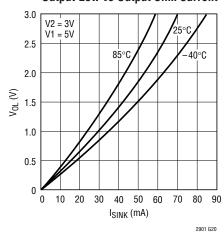

#### RST, WDO, COMPX Voltage Output Low vs Output Sink Current

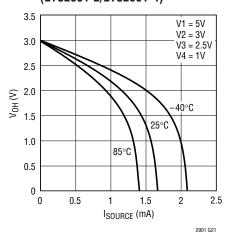

RST High Level Output Voltage vs Output Source Current (LTC2901-2/LTC2901-4)

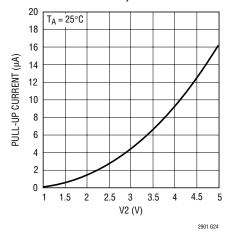

COMPX and WDO Pull-Up Current vs V2 (COMPX and WDO Held at OV)

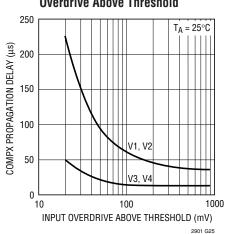

COMPX Propagation Delay vs Input Overdrive Above Threshold

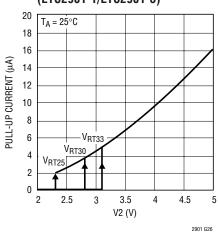

RST Pull-Up Current vs V2 (LTC2901-1/LTC2901-3)

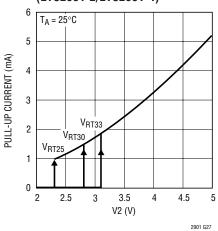

RST Pull-Up Current vs V2 (LTC2901-2/LTC2901-4)

## PIN FUNCTIONS

**COMP3 (Pin 1):** Comparator Output 3. Nondelayed, active high logic output with weak pull-up to V2. Pulls high when V3 is above reset threshold. May be pulled greater than V2 using external pull-up.

**COMP1 (Pin 2):** Comparator Output 1. Nondelayed, active high logic output with weak pull-up to V2. Pulls high when V1 is above reset threshold. May be pulled greater than V2 using external pull-up.

V3 (Pin 3): Voltage Input 3. Select from 2.5V, 1.8V, 1.5V or ADJ. See Table 1 for details.

**V1 (Pin 4):** Voltage Input 1. Select from 5V or 3.3V. See Table 1 for details. The greater of (V1, V2) is also  $V_{CC}$  for the device. Bypass this pin to ground with a  $0.1\mu F$  (or greater) capacitor.

**CRT (Pin 5):** Reset Delay Time Programming Pin. Attach an external capacitor ( $C_{RT}$ ) to GND to set a reset delay time of 4.6ms/nF. Leaving the pin open generates a minimum delay of approximately 50 $\mu$ s. A 47nF capacitor will generate a 216ms reset delay time.

**RST (Pin 6):** Reset Logic Output. Active low with weak pull-up to V2 (LTC2901-1/LTC2901-3) or active pull-up to V2 (LTC2901-2/LTC2901-4). Pulls low when any voltage input is below the reset threshold and held low for the programmed delay time after all voltage inputs are above threshold. May be pulled above V2 using an external pull-up (LTC2901-1/LTC2901-3 only).

WDO (Pin 7): LTC2901-1/LTC2901-2 Watchdog Output. Active low logic output with weak pull-up to V2. May be pulled greater than V2 using external pull-up. The watchdog output pulls low if the watchdog timer is allowed to time out and remains low until set high by the next WDI transistion or anytime RST is low. The watchdog timer is enabled when RST is high.

**TOL (Pin 7):** LTC2901-3/LTC2901-4 Digital Input for Supply Tolerance Selection (5% or 10%). A logic low selects 5% thresholds; a logic high selects 10% thresholds.

**WDI (Pin 8):** Watchdog Input. A logic input whose rising or falling edge must occur on this pin (while RST is high) within the selected watchdog time-out period, prohibiting a high-to-low transition on the WDO pin (LTC2901-1/LTC2901-2). The watchdog time-out period is set by the value of the capacitor that is attached to the CWT pin.

A rising or falling edge on the WDI pin clears the voltage on the  $C_{WT}$  capacitor, preventing WDO from going low. When disabling the watchdog function, tie CWT to GND.

For the LTC2901-3/LTC2901-4, <u>a watchdog time-out due</u> to a missed WDI edge issues an RST pulse on the RST pin (the WDO function is merged into the RST function).

**CWT (Pin 9):** Watchdog Time-Out Programming Pin. Attach a capacitor ( $C_{WT}$ ) between CWT and GND to set a watchdog time-out period of 20ms/nF. Leaving the pin open generates a minimum time-out of approximately 200 $\mu$ s. A 47nF capacitor will generate a 940ms watchdog time-out period.

GND (Pin 10): Ground.

$V_{PG}$  (Pin 11): Voltage Threshold Combination Select Input. Connect to an external 1% resistive divider between  $V_{REF}$  and GND to select 1 of 16 combinations of preset and/or  $\pm$ adjustable voltage thresholds (see Table 1). Do not add capacitance on the  $V_{PG}$  pin.

$V_{REF}$  (Pin 12): Buffered Reference Voltage. A 1.210V nominal reference used for programming voltage ( $V_{PG}$ ) and for the offset of negative adjustable applications. The buffered reference can source and sink up to 1mA. The reference can drive a bypass capacitor of up to 1000pF without oscillation.

**V4 (Pin 13):** Voltage Input 4. Select from 1.8V, 1.5V, ADJ or –ADJ. See Table 1 for details.

**V2 (Pin 14):** Voltage Input 2. Select from 3.3V, 3V or 2.5V. See Table 1 for details. The greater of (V1, V2) is also  $V_{CC}$  for device. Bypass this pin to ground with a 0.1μF (or greater) capacitor. All logic outputs (COMP1, COMP2, COMP3, COMP4, RST, WDO) are weakly pulled up to V2 (LTC2901-1/LTC2901-3). RST is actively pulled up to V2 in the LTC2901-2/LTC2901-4.

**COMP4 (Pin 15):** Comparator Output 4. Nondelayed, active high logic output with weak pull-up to V2. Pulls high when V4 is above reset threshold. May be pulled greater than V2 using external pull-up.

**COMP2** (**Pin 16**): Comparator Output 2. Nondelayed, active high logic output with weak pull-up to V2. Pulls high when V2 is above reset threshold. May be pulled greater than V2 using external pull-up.

LINEAD

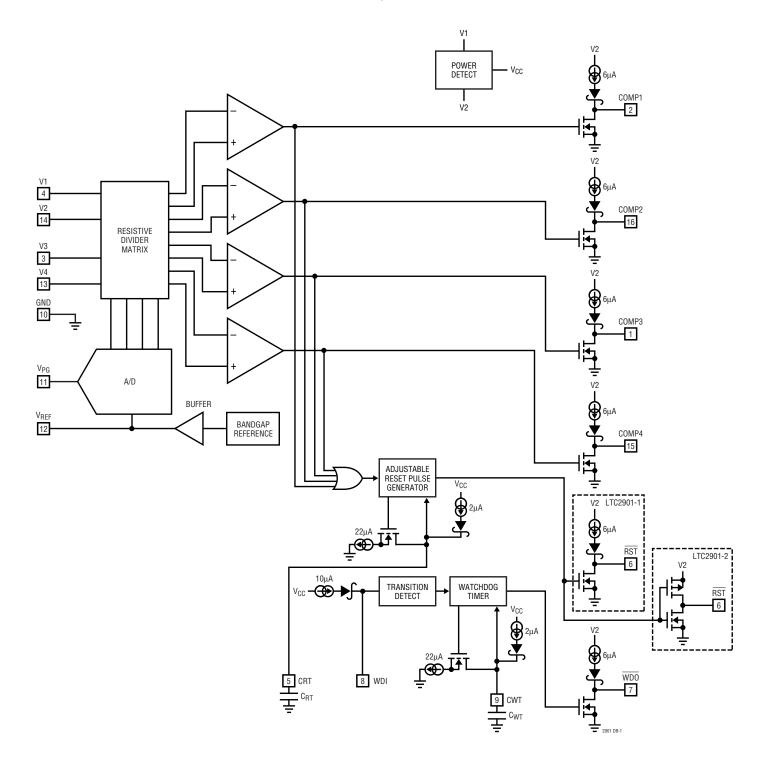

# **BLOCK DIAGRAM**

#### LTC2901-1/LTC2901-2

# **BLOCK DIAGRAM**

#### LTC2901-3/LTC2901-4

#### Power-Up

The greater of V1, V2 is the internal supply voltage ( $V_{CC}$ ). On power-up,  $V_{CC}$  will power the drive circuits for the  $\overline{RST}$  and the COMPX pins. This ensures that the  $\overline{RST}$  and COMPX outputs will be low as soon as V1 or V2 reaches 1V. The  $\overline{RST}$  and COMPX outputs will remain low until the part is programmed. After programming, if any one of the  $V_X$  inputs is below its programmed threshold,  $\overline{RST}$  will be a logic low. Once all the  $V_X$  inputs rise above their thresholds, an internal timer is started and  $\overline{RST}$  is released after the programmed delay time. If  $V_{CC} < (V3-1)$  and  $V_{CC} < 2.4V$ , the V3 input impedance will be low ( $1k\Omega$  typ).

#### **Monitor Programming**

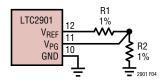

The LTC2901 input voltage combination is selected by placing the recommended resistive divider from  $V_{REF}$  to GND and connecting the tap point to  $V_{PG}$ , as shown in Figure 4. Table 1 offers recommended 1% resistor values for the various modes. The last column in Table 1 specifies optimum  $V_{PG}/V_{REF}$  ratios ( $\pm 0.01$ ) to be used when programming with a ratiometric DAC.

During power-up, once V1 or V2 reaches 2.4V max, the monitor enters a programming period of approximately

Table 1. Voltage Threshold Programming

| MODE | V1 (V) | V2 (V) | V3 (V) | V4 (V) | R1 (kΩ) | <b>R2</b> (kΩ) | V <sub>PG</sub><br>V <sub>REF</sub> |

|------|--------|--------|--------|--------|---------|----------------|-------------------------------------|

| 0    | 5.0    | 3.3    | ADJ    | ADJ    | Open    | Short          | 0.000                               |

| 1    | 5.0    | 3.3    | ADJ    | -ADJ   | 93.1    | 9.53           | 0.094                               |

| 2    | 3.3    | 2.5    | ADJ    | ADJ    | 86.6    | 16.2           | 0.156                               |

| 3    | 3.3    | 2.5    | ADJ    | -ADJ   | 78.7    | 22.1           | 0.219                               |

| 4    | 3.3    | 2.5    | 1.5    | ADJ    | 71.5    | 28.0           | 0.281                               |

| 5    | 5.0    | 3.3    | 2.5    | ADJ    | 66.5    | 34.8           | 0.344                               |

| 6    | 5.0    | 3.3    | 2.5    | 1.8    | 59.0    | 40.2           | 0.406                               |

| 7    | 5.0    | 3.3    | 2.5    | 1.5    | 53.6    | 47.5           | 0.469                               |

| 8    | 5.0    | 3.0    | 2.5    | ADJ    | 47.5    | 53.6           | 0.531                               |

| 9    | 5.0    | 3.0    | ADJ    | ADJ    | 40.2    | 59.0           | 0.594                               |

| 10   | 3.3    | 2.5    | 1.8    | 1.5    | 34.8    | 66.5           | 0.656                               |

| 11   | 3.3    | 2.5    | 1.8    | ADJ    | 28.0    | 71.5           | 0.719                               |

| 12   | 3.3    | 2.5    | 1.8    | -ADJ   | 22.1    | 78.7           | 0.781                               |

| 13   | 5.0    | 3.3    | 1.8    | -ADJ   | 16.2    | 86.6           | 0.844                               |

| 14   | 5.0    | 3.3    | 1.8    | ADJ    | 9.53    | 93.1           | 0.906                               |

| 15   | 5.0    | 3.0    | 1.8    | ADJ    | Short   | Open           | 1.000                               |

Figure 4. Monitor Programming

150 $\mu$ s during which the voltage on the  $V_{PG}$  pin is sampled and the monitor is configured to the desired input combination. Do not add capacitance to the  $V_{PG}$  pin. Immediately after programming, the comparators are enabled and supply monitoring will begin.

#### **Supply Monitoring**

The LTC2901 is a low power, high accuracy programmable quad supply monitoring circuit with four nondelayed monitor outputs, a common reset output and a watchdog timer. Watchdog and reset timing are both adjustable using external capacitors. Single pin programming selects 1 of 16 input voltage monitor combinations. All four voltage inputs must be above predetermined thresholds for the reset not to be invoked. The LTC2901 will assert the reset and comparator outputs during power-up, power-down and brownout conditions on any one of the voltage inputs.

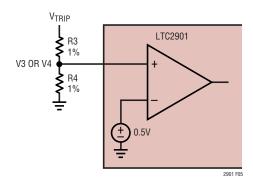

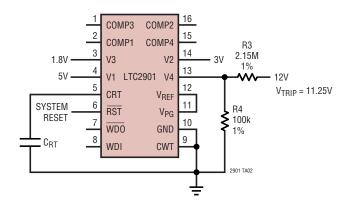

The inverting inputs on the V3 and/or V4 comparators are set to 0.5V when the positive adjustable modes are selected (Figure 5). The tap point on an external resistive divider, connected between the positive voltage being sensed and ground, is connected to the high impedance noninverting inputs (V3, V4). The trip voltage is calculated from:

$$V_{TRIP} = 0.5V \left(1 + \frac{R3}{R4}\right)$$

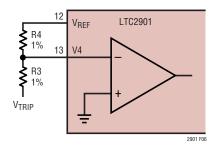

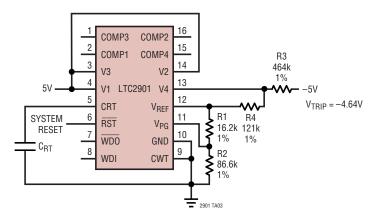

In the negative adjustable mode, the noninverting input on the V4 comparator is connected to ground (Figure 6). The tap point on an external resistive divider, connected between the negative voltage being sensed and the  $V_{REF}$  pin, is connected to the high impedance inverting input (V4).  $V_{REF}$  provides the necessary level shift required to operate at ground. The trip voltage is calculated from:

$$V_{TRIP} = -V_{REF} \left(\frac{R3}{R4}\right)$$

;  $V_{REF} = 1.210 \text{V Nominal}$

Figure 5. Setting the Positive Adjustable Trip Point

Figure 6. Setting the Negative Adjustable Trip Point

In a negative adjustable application, the minimum value for R4 is limited by the sourcing capability of  $V_{REF}$  ( $\pm 1$ mA). With no other load on  $V_{REF}$ , R4 (minimum) is:

$$1.21V \div 1mA = 1.21k\Omega$$

.

Tables 2 and 3 offer suggested 1% resistor values for various adjustable applications.

Once the resistor divider is set in the 5% tolerance mode (LTC2901-3/LTC2901-4), there is no need to change the divider for the 10% mode because the internal and external reference is scaled accordingly, moving the trip point by -5%.

Although all four supply monitor comparators have built-in glitch immunity, bypass capacitors on V1 and V2 are recommended because the greater of V1 or V2 is also the  $V_{CC}$  for the device. Filter capacitors on the V3 and V4 inputs are allowed.

#### Power-Down

On power-down, once any of the  $V_X$  inputs drop below their threshold, RST and COMPX are held at a logic low. A logic low of 0.4V is guaranteed until both V1 and V2 drop below 1V. If the bandgap reference becomes invalid

Table 2. Suggested 1% Resistor Values for the ADJ Inputs

|                         | =                     |         |         |  |  |

|-------------------------|-----------------------|---------|---------|--|--|

| V <sub>SUPPLY</sub> (V) | V <sub>TRIP</sub> (V) | R3 (kΩ) | R4 (kΩ) |  |  |

| 12                      | 11.25                 | 2150    | 100     |  |  |

| 10                      | 9.4                   | 1780    | 100     |  |  |

| 8                       | 7.5                   | 1400    | 100     |  |  |

| 7.5                     | 7                     | 1300    | 100     |  |  |

| 6                       | 5.6                   | 1020    | 100     |  |  |

| 5                       | 4.725                 | 845     | 100     |  |  |

| 3.3                     | 3.055                 | 511     | 100     |  |  |

| 3                       | 2.82                  | 464     | 100     |  |  |

| 2.5                     | 2.325                 | 365     | 100     |  |  |

| 1.8                     | 1.685                 | 237     | 100     |  |  |

| 1.5                     | 1.410                 | 182     | 100     |  |  |

| 1.2                     | 1.120                 | 124     | 100     |  |  |

| 1                       | 0.933                 | 86.6    | 100     |  |  |

| 0.9                     | 0.840                 | 68.1    | 100     |  |  |

|                         |                       |         |         |  |  |

Table 3. Suggested 1% Resistor Values for the -ADJ Input

|                         | 33                    |         |         |  |  |

|-------------------------|-----------------------|---------|---------|--|--|

| V <sub>SUPPLY</sub> (V) | V <sub>TRIP</sub> (V) | R3 (kΩ) | R4 (kΩ) |  |  |

| -2                      | -1.87                 | 187     | 121     |  |  |

| -5                      | -4.64                 | 464     | 121     |  |  |

| -5.2                    | -4.87                 | 487     | 121     |  |  |

| -10                     | -9.31                 | 931     | 121     |  |  |

| -12                     | -11.30                | 1130    | 121     |  |  |

( $V_{CC}$  < 2V typ), the part will reprogram once  $V_{CC}$  rises above 2.4V max.

#### **Monitor Output Rise and Fall Time Estimation**

All of the outputs ( $\overline{RST}$ , COMPX,  $\overline{WDO}$ ) have strong pull-down capability. If the external load capacitance ( $C_{LOAD}$ ) for a particular output is known, output fall time (10% to 90%) is estimated using:

$$t_{FALL} \approx 2.2 \bullet R_{PD} \bullet C_{LOAD}$$

where  $R_{PD}$  is the on-resistance of the internal pull-down transistor. The typical performance curve (V<sub>OL</sub> vs I<sub>SINK</sub>) demonstrates that the pull-down current is somewhat linear versus output voltage. Using the 25°C curve,  $R_{PD}$  is estimated to be approximately  $40\Omega.$  Assuming a 150pF load capacitance, the fall time is about 13.2ns.

Although the outputs are considered to be "open-drain," they do have a weak pull-up capability (see COMPX or RST

Pull-Up Current vs V2 curve). Output rise time (10% to 90%) is estimated using:

$$t_{RISE} \approx 2.2 \bullet R_{PU} \bullet C_{LOAD}$$

where  $R_{PU}$  is the on-resistance of the pull-up transistor. The on-resistance as a function of the V2 voltage at room temperature is estimated using:

$$R_{PU} = \frac{6 \cdot 10^5}{V2 - 1} \Omega$$

with V2 = 3.3V,  $R_{PU}$  is about 260k. Using 150pF for load capacitance, the rise time is 86 $\mu$ s. If the output needs to pull up faster and/or to a higher voltage, a smaller external pull-up resistor may be used. Using a 10k pull-up resistor, the rise time is reduced to 3.3 $\mu$ s for a 150pF load capacitance.

The LTC2901-2 has an active pull-up to V2 on the  $\overline{RST}$  output. The typical performance curve ( $\overline{RST}$  Pull-Up Current vs V2 curve) demonstrates that the pull-up current is somewhat linear versus the V2 voltage and  $R_{PU}$  is estimated to be approximately 625 $\Omega$ . A 150pF load capacitance makes the rise time about 206ns.

#### **Watchdog Timer**

The watchdog circuit typically monitors a  $\mu P$ 's activity. The  $\mu P$  is required to change the logic state of the WDI pin on a periodic basis in order to clear the watchdog timer and prevent the WDO pin (LTC2901-1/LTC2901-2) from going low. Whenever RST is low, the watchdog timer is cleared and WDO is set high. The watchdog timer is started when RST pulls high. Subsequent edges received on the WDI pin will clear the watchdog timer. The timer will continue to run until the watchdog timer times out. Once the watchdog timer times out, internal circuitry will bring the WDO pin low. WDO will remain low and the watchdog timer will remain cleared until the next edge is received on the WDI pin or until RST goes low.

In the LTC2901-3/LTC2901-4, there is no WDO pin. Instead, the  $\overline{RST}$  pin is pulled low for the programmed reset timeout period whenever a WDI edge is missed. In this manner, a full system reset can be issued after a watchdog failure.

To disable the watchdog timer, simply ground the CWT pin (Pin 9). With CWT held at ground, any reset event will force

$\overline{WDO}$  high indefinitely. It is safe to leave the WDI pin (Pin 8) unconnected because the weak internal pull-up (10 $\mu$ A typ) will pull WDI high. Tying WDI to V1 or ground is also allowed, but grounding the WDI pin will force the pull-up current to be drawn continuously.

#### **Selecting the Reset Timing Capacitor**

The reset time-out period is adjustable in order to accommodate a variety of microprocessor applications. The reset time-out period,  $t_{RST}$ , is adjusted by connecting a capacitor,  $C_{RT}$ , between the CRT pin and ground. The value of this capacitor is determined by:

$$C_{RT} = t_{RST} \cdot 217 \cdot 10^{-9}$$

with  $C_{RT}$  in Farads and  $t_{RST}$  in seconds. The  $C_{RT}$  value per millisecond of delay can also be expressed as  $C_{RT}/ms = 217$  (pF/ms).

Leaving the CRT pin unconnected will generate a minimum reset time-out of approximately  $50\mu s$ . Maximum reset time-out is limited by the largest available low leakage capacitor. The accuracy of the time-out period will be affected by capacitor leakage (the nominal charging current is  $2\mu A$ ) and capacitor tolerance. A low leakage ceramic capacitor is recommended.

## **Selecting the Watchdog Timing Capacitor**

The watchdog time-out period is adjustable and can be optimized for software execution. The watchdog time-out period,  $t_{WD}$ , is adjusted by connecting a capacitor,  $C_{WT}$ , between the CWT pin and ground. Given a specified watchdog time-out period, the capacitor is determined by:

$$C_{WT} = t_{WD} \cdot 50 \cdot 10^{-9}$$

with  $C_{WT}$  in Farads and  $t_{WD}$  in seconds. The  $C_{WT}$  value per millisecond of delay can also be expressed as  $C_{WT}/ms = 50$  (pF/ms).

Leaving the CWT pin unconnected will generate a minimum watchdog time-out of approximately 200 $\mu$ s. Maximum time-out is limited by the largest available low leakage capacitor. The accuracy of the time-out period will be affected by capacitor leakage (the nominal charging current is  $2\mu$ A) and capacitor tolerance. A low leakage ceramic capacitor is recommended.

#### **Monitoring Power Supply Controller Activity**

Figure 7 demonstrates how the LTC2901 can be used to monitor switcher activity. The monitor is configured to supervise 3.3V, 2.5V, 1.8V and one adjustable input. Because 2.5V does not exist in this application, the V2 input is tied to the V1 (3.3V) input. The feedback voltage on the LTC1772 (0.8V typ) is monitored with the adjustable input (V4). The RST pin will go high 216ms ( $C_{RT} = 47nF$ ) after the 3.3V and 1.8V supplies and the feedback voltage are above threshold. Individual input status is available at the COMPX pins.

While the voltage monitors can detect low voltage or shorted inputs, the watchdog circuit can be used to detect an open circuit to the primary load. With the CWT pin unconnected, the watchdog time-out is approximately 200µs. At low load currents on the 1.8V supply, the LTC1772 will go into Burst Mode® operation. With an open-ciruit load, the duty cycle at the gate of M1 will drop, and the pulse spacing will exceed the watchdog time-out

period. The WDO pin will go low indicating the low load condition. The WDO pin will return high on the next pulse to the gate of M1. The WDO pin will remain high if the load is restored.

# Ensuring Reset Valid for V<sub>CC</sub> Down to 0V (LTC2901-2/LTC2901-4)

Some applications require the reset output ( $\overline{RST}$ ) to be valid with  $V_{CC}$  down to 0V. The LTC2901-2 is designed to handle this requirement with the addition of an external resistor from  $\overline{RST}$  to ground. The resistor will provide a path for stray charge and/or leakage currents, preventing the  $\overline{RST}$  output from floating to undetermined voltages when connected to high impedance (such as CMOS logic inputs). The resistor value should be small enough to provide effective pull-down without excessively loading the active pull-up circuitry. Too large a value may not pull down well enough. A 100k resistor from  $\overline{RST}$  to ground is satisfactory for most applications.

Burst Mode is a registered trademark of Linear Technology Corporation.

Figure 7. Monitor Input, Output, Feedback Voltage and Low Load Conditions on DC/DC Controller

## TYPICAL APPLICATIONS

Quad Supply Monitor with Watchdog Timer Disabled 5V, 3V, 1.8V, 12V (ADJ)

# 5V, -5V Monitor with Watchdog Timer Disabled and Unused V2, V3 Inputs Pulled Above Trip Thresholds

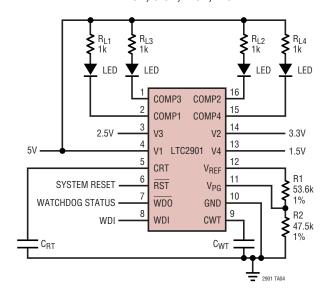

# Quad Supply Monitor with LED Undervoltage Indicators 5V, 3.3V, 2.5V, 1.5V

Generate RESET Pulse Through Watchdog Timeout (LTC2901-1/LTC2901-2)

## TYPICAL APPLICATION

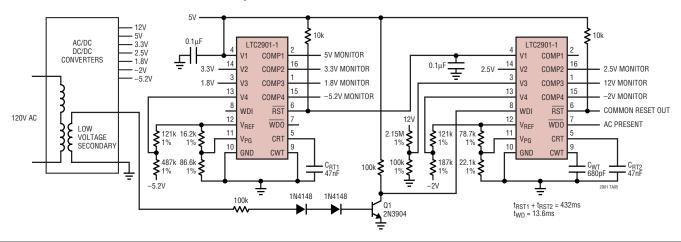

# Monitor Seven Supplies (12V, 5V, 3.3V, 2.5V, 1.8V, -2V, -5.2V) with Sequenced Reset and AC Present Indication

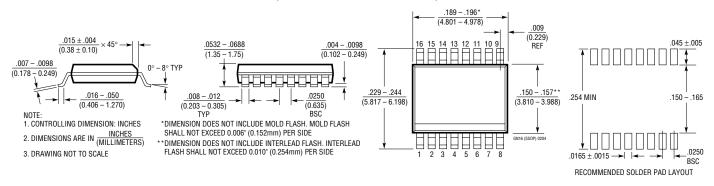

# PACKAGE DESCRIPTION

#### GN Package 16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

### RELATED PARTS

| PART NUMBER                        | DESCRIPTION                                                     | COMMENTS                                                                              |

|------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|

| LTC694-3.3                         | 3.3V Supply Monitor, Watchdog Timer and Battery Backup          | 2.9V Threshold                                                                        |

| LTC1326                            | Micropower Precision Triple Supply Monitor for 5V, 3.3V and ADJ | 4.725V, 3.118V, 1V Thresholds (±0.75%)                                                |

| LTC1726-2.5                        | Micropower Triple Supply Monitor for 2.5V, 3.3V and ADJ         | Adjustable RESET and Watchdog Time-Outs                                               |

| LTC1727-2.5/LTC1727-5              | Micropower Triple Supply Monitors with Open-Drain Reset         | Individual Monitor Outputs in MSOP                                                    |

| LTC1728-1.8/LTC1728-3.3            | Micropower Triple Supply Monitor with Open-Drain Reset          | 5-Lead SOT-23 Package                                                                 |

| LTC2900                            | Programmable Quad Supply Monitor                                | Adjustable Reset Timer, 10-Lead MSOP and 3mm × 3mm 10-Lead DFN                        |

| LTC2902                            | Programmable Quad Supply Monitor                                | Adjustable Reset Timer, Supply Tolerance and Margining Functions, 16-Lead Narrow SSOP |

| LTC2903                            | Precision Quad Supply Monitor in 6-Lead SOT-23                  | A Variety of Factory Trimmed Voltage Combinations                                     |

| LTC2904/LTC2905<br>LTC2906/LTC2907 | Precision Dual Supply Monitors                                  | Pin Selectable Thresholds                                                             |

| LTC2908                            | Precision Six Supply Monitor                                    | 8-Lead SOT-23 and DFN Packages                                                        |

LT 0807 REV B • PRINTED IN USA

LINEAR

ECHNOLOGY

LINEAR TECHNOLOGY CORPORATION 2002

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# **Analog Devices Inc.:**

LTC2901-2IGN#PBF LTC2901-3IGN#TRPBF LTC2901-1CGN#TRPBF LTC2901-4IGN#TRPBF LTC29012CGN#TRPBF LTC2901-3IGN#PBF LTC2901-1CGN#PBF LTC2901-1IGN#TRPBF LTC2901-4CGN#TRPBF

LTC2901-3CGN#PBF LTC2901-2IGN#TRPBF LTC2901-4CGN#PBF LTC2901-4IGN#PBF LTC2901-2CGN#PBF

LTC2901-3CGN#TRPBF LTC2901-1IGN#PBF