LTM2895

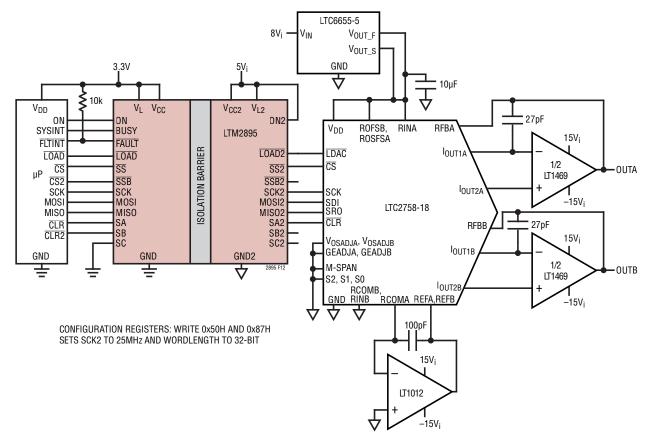

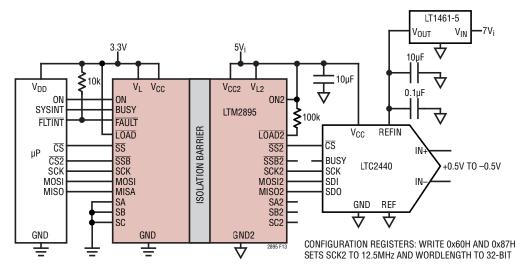

### 100MHz Isolated DAC SPI Serial Interface

### FEATURES

- Isolated Interface: 6000V<sub>RMS</sub> for 1 Minute

- CSA (IEC/UL) Approved, File #255632

- 100MHz SPI-Compatible I/O

- Configurable SPI Word-Length: 8 to 32 Bits

- Supports Two Isolated Chip Selects

- Falling Edge Sensitive Low Jitter LOAD

- Three Isolated Control or Multiplexer Signals

- 1.71V to 5.5V I/O Voltages

- 3V to 5.5V Supply Voltages

- High Common Mode Transient Immunity

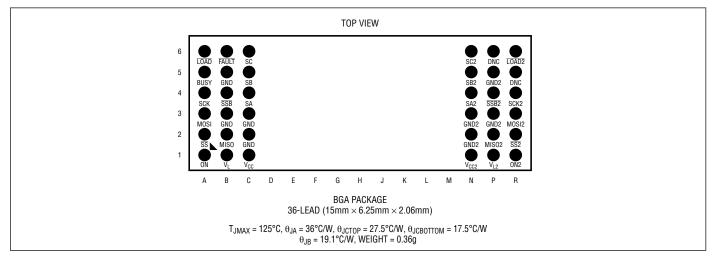

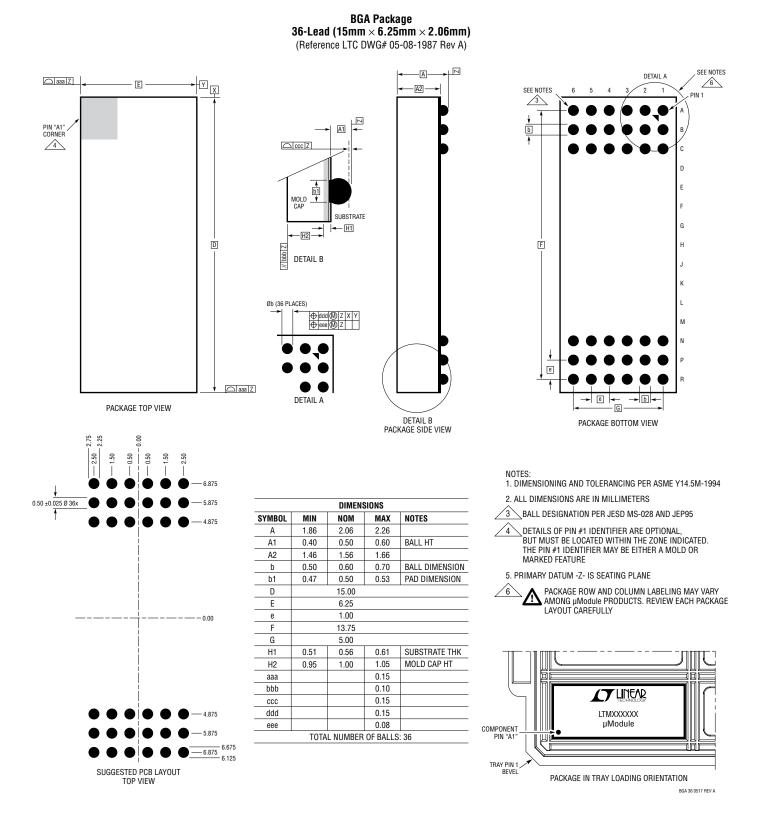

- 15mm × 6.25mm BGA Package

### **APPLICATIONS**

- Remote Interface Control

- Industrial Process Control and Automation

- Test and Measurement Equipment

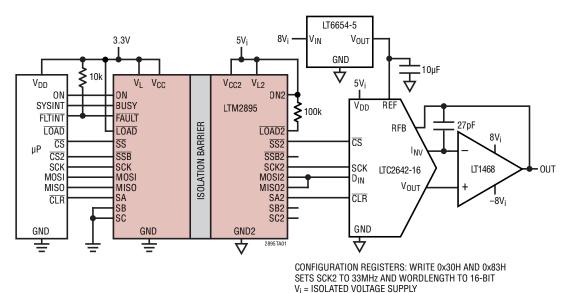

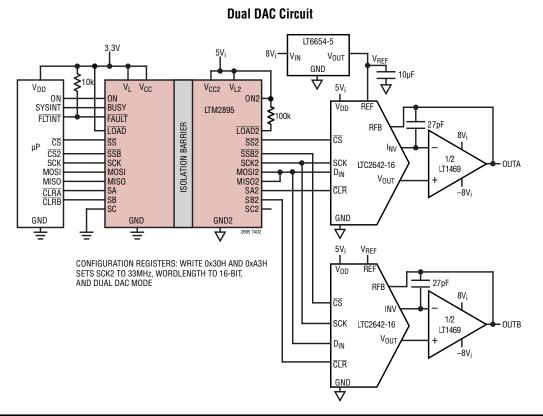

TYPICAL APPLICATION

Breaking Ground Loops

### DESCRIPTION

The LTM<sup>®</sup>2895 is a high speed isolated  $\mu$ Module<sup>®</sup> (micromodule) SPI interface with DAC control signals designed to isolate LTC's family of general purpose DACs and to isolate general purpose SPI interfaces. The LTM2895 works with DACs and general purpose devices that have a mode (0, 0) SPI interface.

The interface enables fast data throughput, which makes the LTM2895 ideally suited for a wide variety of applications. The high speed SPI-compatible serial port supports 1.71V to 5.5V logic supplies. The LTM2895 is targeted at generic SPI and digital-to-analog converter applications.

The isolation barrier tolerates large voltage ground variations between the logic interface and the isolated side of the LTM2895. Uninterrupted communication is maintained during voltage transients greater than 50kV/µs.

All registered trademarks and trademarks are the property of their respective owners.

LTC2642-16 DAC Isolation

### ABSOLUTE MAXIMUM RATINGS (Note 1)

| Supply | Voltages |

|--------|----------|

|--------|----------|

| Supply Voltages                                           | lsolated Signals                                          |

|-----------------------------------------------------------|-----------------------------------------------------------|

| $V_{L} - GND$                                             | <u>SS2, SSB2, MISO2, ON2, LOAD2, SCK2</u>                 |

| $V_{CC}^{-}$ – GND–0.3V to 6V                             | SA2, SB2, SC2, MOSI2GND2 – 0.3V to V <sub>L2</sub> + 0.3V |

| Isolated Supply Voltages                                  | Operating Temperature Range (Note 10)                     |

| V <sub>L2</sub> – GND2–0.3V to 6V                         | LTM2895C0°C to 70°C                                       |

| V <sub>CC2</sub> – GND2–0.3V to 6V                        | LTM2895I–40°C to 85°C                                     |

| Logic Signals                                             | LTM2895H–40°C to 125°C                                    |

| ON, <u>LOAD,</u> BUSY, SA, SB, SC, <u>SS</u> , <u>SSB</u> | Storage Temperature Range–55°C to 125°C                   |

| SCK, MOSI, MISO GND – 0.3V to $V_L$ + 0.3V                | Maximum Internal Operating Temperature 125°C              |

| FAULT GND – 0.3V to 6.3V                                  | Peak Body Reflow Temperature                              |

### **PIN CONFIGURATION**

#### **ORDER INFORMATION** http://www.linear.com/product/LTM2895#orderinfo

|                             | PACKAGE                               |               | PAF      | RT MARKING* | MSL    | TEMPERATURE RANGE |

|-----------------------------|---------------------------------------|---------------|----------|-------------|--------|-------------------|

| PART NUMBER                 | TYPE                                  | BALL FINISH   | DEVICE   | FINISH CODE | RATING | (SEE NOTE 2)      |

| LTM2895CY#PBF               |                                       |               |          |             |        | 0°C to 70°C       |

| LTM2895IY#PBF               | BGA                                   | SAC305 (RoHS) | LTM2895Y | e1          | 3      | -40°C to 85°C     |

| LTM2895HY#PBF               |                                       |               |          |             |        | -40°C to 125°C    |

| . Device teneneveture evede | the first design of the second second |               |          | Deserve     |        |                   |

Device temperature grade is indicated by a label on the shipping container.

• Pad or ball finish code is per IPC/JEDEC J-STD-609.

• Terminal Finish Part Marking: www.linear.com/leadfree

• This product is not recommended for second side reflow. For more information, go to www.linear.com/BGA-assy

Recommended BGA PCB Assembly and Manufacturing Procedures: www.linear.com/BGA-assy

• BGA Package and Tray Drawings: www.linear.com/packaging

· This product is moisture sensitive. For more information, go to: www.linear.com/BGA-assy

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 5V, V<sub>L</sub> = 3.3V, GND = 0V, V<sub>CC2</sub> = 5V, V<sub>L2</sub> = 3.3V, GND = 0V unless otherwise noted. (Note 9)

| SYMBOL           | PARAMETER                                                     | CONDITIONS                                           |   | MIN                   | ТҮР | MAX                   | UNITS    |

|------------------|---------------------------------------------------------------|------------------------------------------------------|---|-----------------------|-----|-----------------------|----------|

| Power Su         | upplies                                                       |                                                      |   | <u> </u>              |     |                       |          |

| V <sub>CC</sub>  | Operating Supply Range                                        |                                                      | • | 3.0                   |     | 5.5                   | V        |

| I <sub>CC</sub>  | Operating Supply Current                                      | Idle                                                 | • |                       | 9   | 12                    | mA       |

|                  | Operating Supply Current, Max<br>DAC Conversion Rate          | 32-Bit Write/1µs, 20pF Loads, SCK = 50MHz            | • |                       | 12  | 15                    | mA       |

| V <sub>CC2</sub> | Isolated Operating Supply Range                               |                                                      | • | 3.0                   |     | 5.5                   | V        |

| I <sub>CC2</sub> | Isolated Operating Supply Current                             | Idle                                                 | • |                       | 9   | 12                    | mA       |

|                  | Isolated Operating Supply Current, Max<br>DAC Conversion Rate | 32-Bit Write/1µs, 20pF Loads, SCK = 50MHz            | • |                       | 12  | 15                    | mA       |

| VL               | Logic Interface Supply Range                                  |                                                      | • | 1.71                  | 3.3 | 5.5                   | V        |

| ١L               | Logic Interface Supply Current                                | Inputs and Outputs Static at GND or $V_L$            | • |                       |     | ±200                  | μA       |

|                  | Logic Interface Supply Current, Max<br>Conversion Rate        | 32-Bit Write/1µs, 20pF Loads, SCK = 50MHz            | • |                       | 2   | 5                     | mA       |

| V <sub>L2</sub>  | Isolated Interface Supply Range                               |                                                      |   | 1.71                  | 3.3 | 5.5                   | V        |

| I <sub>L2</sub>  | Isolated Interface Supply Current                             | Inputs and Outputs Static at GND2 or $V_{\text{L2}}$ | • |                       |     | ±200                  | μA       |

|                  | Isolated Interface Supply Current, Max<br>Conversion Rate     | 32-Bit Write/1µs, 20pF Loads, SCK = 50MHz            | • |                       | 2   | 5                     | mA       |

| Digital In       | puts and Digital Outputs (Logic Side)                         | ·                                                    |   |                       |     |                       |          |

| V <sub>IH</sub>  | High Level Input Voltage                                      | $1.71V \le V_L \le 5.5V$                             |   | 0.8 • V <sub>L</sub>  |     |                       | V        |

| V <sub>IL</sub>  | Low Level Input Voltage                                       | $1.71V \le V_L \le 5.5V$                             | • |                       |     | 0.2 • V <sub>L</sub>  | V        |

|                  | Digital Input Current (MOSI, SCK, LOAD)                       | $V_{IN} = 0V$ to $V_L$ , $\overline{SS} = V_L$       |   |                       |     | ±1                    | μA       |

|                  | Digital Input Current (SS, SSB, SA, SB, SC, ON)               | $V_{IN} = 0V \text{ to } V_L$                        |   |                       |     | ±60                   | μA       |

|                  | Digital Input Capacitance                                     | (Note 7)                                             |   |                       | 5   |                       | pF       |

| V <sub>OH</sub>  | High Level Output Voltage                                     | $I_{OUT} = -500 \mu A, \ 1.71 V \le V_L \le 5.5 V$   |   | $V_L - 0.2$           |     |                       | V        |

| V <sub>OL</sub>  | Low Level Output Voltage                                      | $I_{OUT} = 500 \mu A, \ 1.71 V \le V_L \le 5.5 V$    |   |                       |     | 0.2                   | V        |

|                  | High-Z Output Leakage Current MISO                            | $\overline{SS} = V_L$                                |   |                       |     | ±1                    | μA       |

|                  | Output Source Current (Short-Circuit)<br>MISO, BUSY           | V <sub>OUT</sub> = 0V (Note 7)                       |   |                       | -80 |                       | mA       |

|                  | Output Sink Current (Short-Circuit)<br>MISO, BUSY, FAULT      | V <sub>OUT</sub> = V <sub>L</sub> (Note 7)           |   |                       | 80  |                       | mA       |

| Digital In       | puts and Digital Outputs (Isolated Side)                      |                                                      | · |                       |     |                       | <u> </u> |

| V <sub>IH</sub>  | High Level Input Voltage                                      | $1.71V \le V_{L2} \le 5.5V$                          |   | 0.8 • V <sub>L2</sub> |     |                       | V        |

| V <sub>IL</sub>  | Low Level Input Voltage                                       | $1.71V \le V_{L2} \le 5.5V$                          |   |                       |     | 0.2 • V <sub>L2</sub> | V        |

|                  | Digital Input Current (ON2)                                   | $V_{IN} = 0V$ to $V_{L2}$                            |   |                       |     | ±60                   | μA       |

|                  | Digital Input Current (MISO2)                                 | $V_{IN} = 0V$ to $V_{L2}$                            | • |                       |     | ±10                   | μA       |

|                  | Digital Input Capacitance                                     | (Note 7)                                             |   |                       | 5   |                       | pF       |

| V <sub>OH</sub>  | High Level Output Voltage                                     | $I_{OUT} = -500\mu A, 1.71V \le V_{L2} \le 5.5V$     | • | V <sub>L2</sub> -0.2  |     |                       | V        |

| V <sub>OL</sub>  | Low Level Output Voltage                                      | $I_{OUT} = 500\mu A, 1.71V \le V_{L2} \le 5.5V$      | • |                       |     | 0.2                   | V        |

|                  | Output Source Current (Short-Circuit)                         | V <sub>OUT</sub> = 0V (Note 7)                       |   |                       | -80 |                       | mA       |

|                  | Output Sink Current (Short-Circuit)                           | $V_{OUT} = V_{L2}$ (Note 7)                          |   |                       | 80  |                       | mA       |

#### **ESD PERFORMANCE** (Note 7)

| SYMBOL | PARAMETER                                                          | CONDITIONS                                                                                                                                                                                                           | MIN | ТҮР             | MAX | UNITS          |

|--------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|----------------|

|        | Isolation Barrier<br>Logic Side I/O Pins<br>Isolated Side I/O Pins | From GND, V <sub>L</sub> , or V <sub>CC</sub> to GND2, V <sub>L2</sub> , or V <sub>CC2</sub> GND, V <sub>L</sub> , V <sub>CC</sub> GND2, V <sub>L2</sub> , V <sub>CC2</sub> GND2, V <sub>L2</sub> , V <sub>CC2</sub> |     | ±15<br>±4<br>±4 |     | kV<br>kV<br>kV |

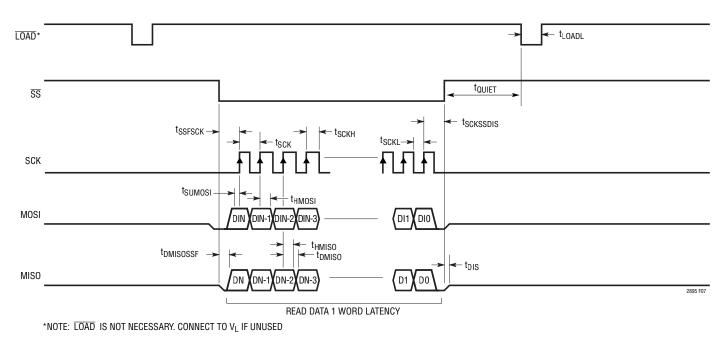

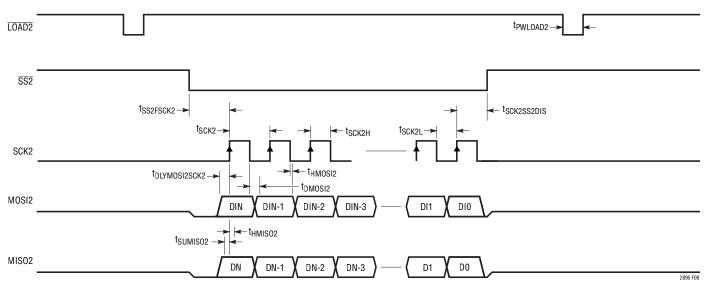

# **SWITCHING CHARACTERISTICS** The • denotes specifications that apply over the full specified operating temperature range, otherwise specifications are at $T_A = 25$ °C, $C_L = 20$ pF, $V_{CC} = 5$ V, $V_L = 3.3$ V, GND = 0V, $V_{CC2} = 5$ V, $V_{L2} = 3.3$ V, GND = 0V; unless otherwise noted.

| SYMBOL                 | PARAMETER                                              | CONDITIONS                                                        |   | MIN | ТҮР | MAX      | UNITS    |

|------------------------|--------------------------------------------------------|-------------------------------------------------------------------|---|-----|-----|----------|----------|

| t <sub>LOADL</sub>     | LOAD Low Pulse Width                                   |                                                                   |   | 20  |     |          | ns       |

| t <sub>DLYLOAD2</sub>  | <b>LOAD</b> ↓ to <b>LOAD2</b> ↓ Delay (Aperture Delay) |                                                                   |   | 12  | 21  | 33       | ns       |

| t <sub>PWLOAD2</sub>   | LOAD2 Low Pulse Width                                  | (SCK2 Frequency ≥ 40MHz)                                          |   | 20  |     | 52       | ns       |

|                        |                                                        | (SCK2 Frequency ≤ 33MHz)                                          |   | 35  |     | 80       | ns       |

|                        | LOAD to LOAD2 Falling Edge Jitter RMS                  | (Note 7)                                                          |   |     | 30  |          | ps       |

|                        | LOAD High Time                                         |                                                                   |   | 100 |     |          | ns       |

| SPI Timing             |                                                        |                                                                   |   |     |     |          |          |

| t <sub>SCK</sub>       | SCK Input Period                                       | SCK2 Frequency 50MHz (Note 8)                                     |   | 20  |     | 2300     | ns       |

| t <sub>SCKH</sub>      | SCK Input High Time                                    | SCK2 Frequency 50MHz                                              |   | 9   |     |          | ns       |

| t <sub>SCKL</sub>      | SCK Input Low Time                                     | SCK2 Frequency 50MHz                                              |   | 9   |     |          | ns       |

| t <sub>SUMOSI</sub>    | MOSI Setup Time to SCK↑                                | (Note 2)                                                          |   | 1.5 |     |          | ns       |

| t <sub>HMOSI</sub>     | MOSI Hold Time to SCK↑                                 | (Note 2)                                                          |   | 1   |     |          | ns       |

| t <sub>DLYSSLOAD</sub> | SS or SSB Delay to LOAD↓ Quiet Time                    |                                                                   |   | 100 |     |          | ns       |

| t <sub>DMISO</sub>     | MISO Data Valid Delay from SCK↑, SCK2                  | V <sub>L</sub> = 5.5V (Note 2)                                    |   |     | 5   | 7.5      | ns       |

|                        | Selection > 50MHz                                      | V <sub>L</sub> = 2.5V (Note 2)<br>V <sub>1</sub> = 1.71V (Note 2) |   |     |     | 8<br>9.5 | ns<br>ns |

| t <sub>DMISO</sub>     | MISO Data Valid Delay from SCK↓, SCK2                  | $V_1 = 5.5V$ (Note 2)                                             |   |     | 5   | 7.5      | ns       |

|                        | Selection ≤ 50MHz                                      | V <sub>L</sub> = 2.5V (Note 2)                                    | • |     | C C | 8        | ns       |

|                        |                                                        | V <sub>L</sub> = 1.71V (Note 2)                                   | • |     |     | 9.5      | ns       |

| t <sub>HMISO</sub>     | MISO Data Remains Valid Delay from SCK↑                | SCK2 ≥ 50MHz (Note 2)                                             |   | 1.8 |     |          | ns       |

| t <sub>HMISO</sub>     | MISO Data Remains Valid Delay from SCK↓                | SCK2 < 50MHz (Note 2)                                             |   | 1.8 |     |          | ns       |

| t <sub>DMISOSSF</sub>  | MISO Data Valid Delay from $\overline{SS}\downarrow$   |                                                                   |   |     |     | 9.5      | ns       |

| t <sub>SCK2L</sub>     | SCK2 Low Time                                          | SCK2 Frequency 50MHz (Notes 2, 8)                                 |   | 9.1 |     |          | ns       |

| t <sub>SUMISO2</sub>   | MISO2 Data Setup Time to SCK2↑                         | (Note 7)                                                          | • | 1.5 |     |          | ns       |

| t <sub>HMIS02</sub>    | MISO2 Data Hold Time from SCK2↑                        | (Note 7)                                                          |   | 1   |     |          | ns       |

| t <sub>HMOSI2</sub>    | MOSI2 Data Remains Valid Delay from SCK2↓              | (Note 7)                                                          |   | 1   |     |          | ns       |

| t <sub>DMOSI2</sub>    | MOSI2 Data Valid Delay from SCK2↓                      | V <sub>L2</sub> = 5.5V (Note 2)                                   |   |     |     | 1.5      | ns       |

|                        |                                                        | $V_{L2} = 2.5V$ (Note 2)                                          |   |     |     | 2        | ns       |

|                        |                                                        | $V_{L2} = 1.71V$ (Note 2)                                         | • |     |     | 3.5      | ns       |

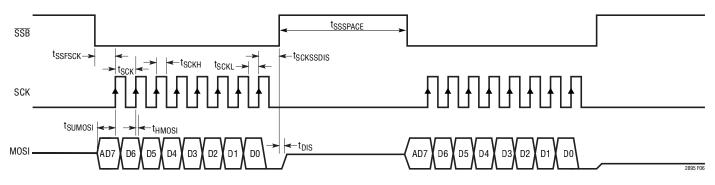

| t <sub>SSFSCK</sub>    | SS↓ or SSB↓ Delay to SCK↑                              | SCK2 Frequency 50MHz (Note 8)                                     |   | 20  |     | 2300     | ns       |

**SWITCHING CHARACTERISTICS** The • denotes specifications that apply over the full specified operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C,  $C_L = 20$ pF,  $V_{CC} = 5$ V,  $V_L = 3.3$ V, GND = 0V,  $V_{CC2} = 5$ V,  $V_{L2} = 3.3$ V, GND = 0V; unless otherwise noted.

| SYMBOL                    | PARAMETER                                       | CONDITIONS                       |   | MIN | ТҮР | MAX  | UNITS |

|---------------------------|-------------------------------------------------|----------------------------------|---|-----|-----|------|-------|

| t <sub>DIS</sub>          | Bus Relinquish Time After <del>SS</del> ↑       |                                  |   |     |     | 35   | ns    |

| t <sub>SCKSSDIS</sub>     | last SCK↑ to SS↑ or SSB↑                        | SCK2 Frequency 50MHz (Note 8)    | • | 25  |     | 2300 | ns    |

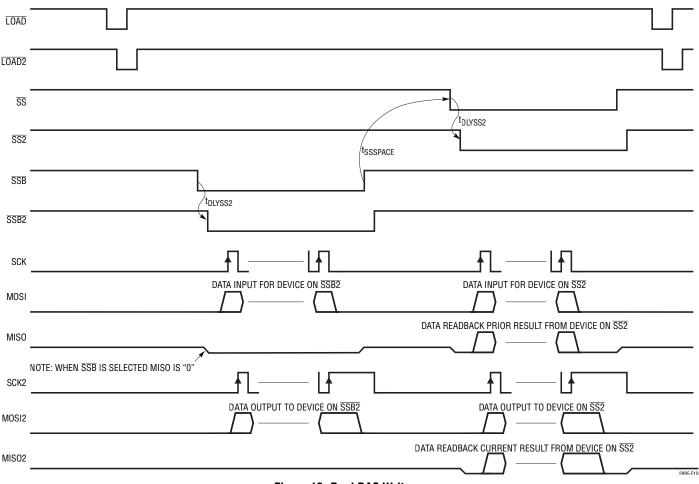

| t <sub>DLYSS2</sub>       | Delay from SS to SS2 or SSB to SSB2             | SSB to SSB2 with DAC 2nd Channel |   |     | 22  |      | ns    |

| t <sub>SCKRSCK2F</sub>    | Delay SCK↑ to SCK2↓                             | SCK2 Frequency 50MHz             |   |     | 22  |      | ns    |

| t <sub>DLYSCKMOSI2</sub>  | Delay SCK↑ to MOSI2 Valid                       |                                  |   |     | 24  |      | ns    |

| t <sub>DLYMOSI2SCK2</sub> | Setup MOSI2 to SCK2↑                            | (Note 2)                         | • | 1.5 |     |      | ns    |

| tSSSPACE                  | SS↑ or SSB↑ Space to SS↓ or SSB↓                |                                  | • | 60  |     |      | ns    |

| t <sub>SS2FSCK2</sub>     | SS2↓ or SSB2↓ Delay to SCK2↑                    | SCK2 Frequency 50MHz             | • | 45  |     |      | ns    |

| t <sub>SCK2SS2DIS</sub>   | Last SCK2↑ to SS2↑ or SSB2↑                     | SCK2 Frequency 50MHz             | • | 32  |     |      | ns    |

|                           | MISO Rise/Fall Time                             | (Note 7)                         |   |     | 500 |      | ps    |

|                           | LOAD2, SS2, SSB2, MOSI2, SCK2 Rise/Fall<br>Time | (Note 7)                         |   |     | 500 |      | ps    |

| Select Signals            | 5                                               |                                  |   |     |     |      | ·     |

|                           | SA, SB, SC Propagation Delay                    | $1.71V \le V_L \le 5.5V$         |   | 40  | 80  | 150  | ns    |

|                           | SA2, SB2, SC2 Rise/Fall Time                    | $1.71V \le V_{L2} \le 5.5V$      | • |     | 10  | 20   | ns    |

### **ISOLATION CHARACTERISTICS** $T_A = 25°C$

| SYMBOL           | PARAMETER                           | CONDITIONS                                                                                                                       | MIN  | ТҮР   | MAX | UNITS                               |

|------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|-------------------------------------|

| V <sub>ISO</sub> | Rated Dielectric Insulation Voltage | 1 Minute, Derived from 1 Second                                                                                                  | 6000 |       |     | V <sub>RMS</sub>                    |

|                  | (Notes 4, 5, 6)                     | 1 Second                                                                                                                         | 7200 |       |     | V <sub>RMS</sub>                    |

|                  | Common Mode Transient Immunity      | $V_{CC} = V_L = ON = 5V$ to GND, $V_{CC2} = V_{L2} = ON2 = 5V$ to GND2, 1000V in 20ns<br>Transient Between GND and GND2 (Note 7) | 50   | 100   |     | kV/µs                               |

| VIORM            | Maximum Working Insulation Voltage  | (Note 2)                                                                                                                         | 1000 |       |     | V <sub>PEAK</sub> , V <sub>DC</sub> |

|                  |                                     |                                                                                                                                  | 690  |       |     | V <sub>RMS</sub>                    |

|                  | Partial Discharge                   | V <sub>PD</sub> = 1830V <sub>PEAK</sub> (Note 4)                                                                                 |      |       | 5   | pC                                  |

| CTI              | Comparative Tracking Index          | IEC 60112 (Note 2)                                                                                                               | 600  |       |     | V <sub>RMS</sub>                    |

|                  | Depth of Erosion                    | IEC 60112 (Note 2)                                                                                                               |      | 0.017 |     | mm                                  |

| DTI              | Distance Through Insulation         | (Note 2)                                                                                                                         |      | 0.2   |     | mm                                  |

|                  | Input to Output Resistance          | (Notes 2, 4)                                                                                                                     | 1    | 5     |     | TΩ                                  |

|                  | Input to Output Capacitance         | (Notes 2, 4)                                                                                                                     |      | 3     |     | pF                                  |

|                  | Creepage Distance                   | (Note 2)                                                                                                                         |      | 9.2   |     | mm                                  |

### **REGULATORY INFORMATION**

#### CSA (Note 11)

- CSA 60950-1-07+A1+A2 and IEC 60950-1, second edition, +A1 +A2: Basic Insulation at  $910V_{RMS}$  Reinforced Insulation at  $455V_{RMS}$

- CSA 62368-1-14 and IEC 62368-1-14:2014, second edition: Basic Insulation at  $600V_{RMS}$  Reinforced Insulation at  $455V_{RMS}$

- CSA 60601-1:14 and IEC 60601-1, third edition, +A1: Two means of patient protection (2 MOPP) at 287.5V<sub>RMS</sub>

- UL 1577-2015: Single Protection, 6000V<sub>RMS</sub> Isolation Voltage

#### File 255632

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: Guaranteed by design, not production tested.

**Note 3:** Maximum data rate is guaranteed by other measured parameters and is not directly tested.

**Note 4:** Device considered a 2-terminal device. Measurement between groups of pins A1 through C6 shorted together and pins N1 through R6 shorted together.

**Note 5:** The rated dielectric insulation voltage should not be interpreted as a continuous voltage rating.

**Note 6:** In accordance with UL1577, each device is proof tested for the  $6000V_{RMS}$  rating by applying an RMS voltage multiplied by an acceleration factor of 1.2 for one second.

Note 7: Evaluated by Design, not production tested.

**Note 8:** See Table 4 and Table 5 for minimum and maximum timing specifications affected by the selection of SCK2 frequencies in the configuration register.

**Note 9:** All currents into device pins are positive; all currents out of device are negative. All voltages are referenced to their corresponding ground unless otherwise specified.

**Note 10:** Continuous operation above specified maximum operating junction temperature may result in device degradation or failure.

**Note 11:** Ratings are for pollution degree 2, material group 3 and overvoltage category II where applicable. Ratings for other environmental and electrical conditions to be determined from the appropriate safety standard.

### TIMING SPECIFICATIONS

Figure 1. Voltage Levels for Timing Specifications

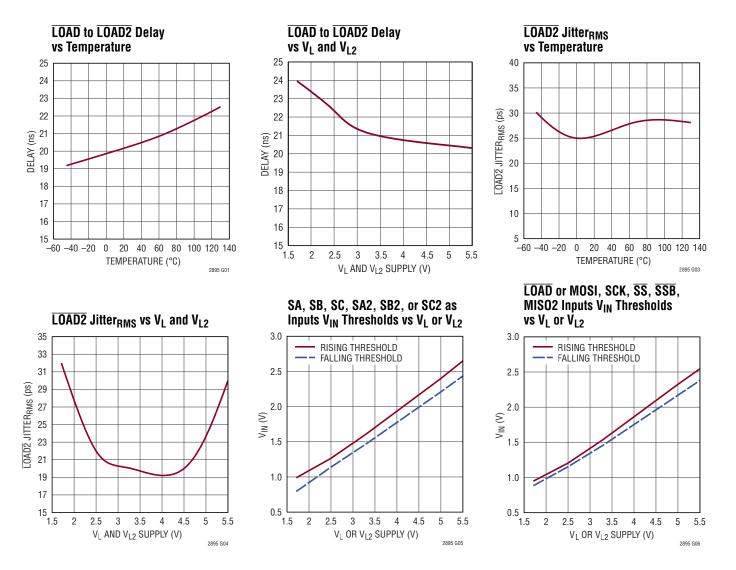

### TYPICAL PERFORMANCE CHARACTERISTICS

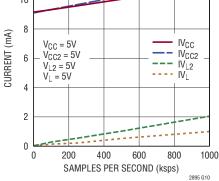

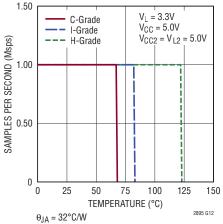

Specifications are at  $T_A = 25^{\circ}$ C.  $V_{CC} = 5V$ ,  $V_L = 3.3V$ , GND = 0V,  $V_{CC2} = 5V$ ,  $V_{L2} = 5.0V$ , GND2 = 0V, unless otherwise noted.

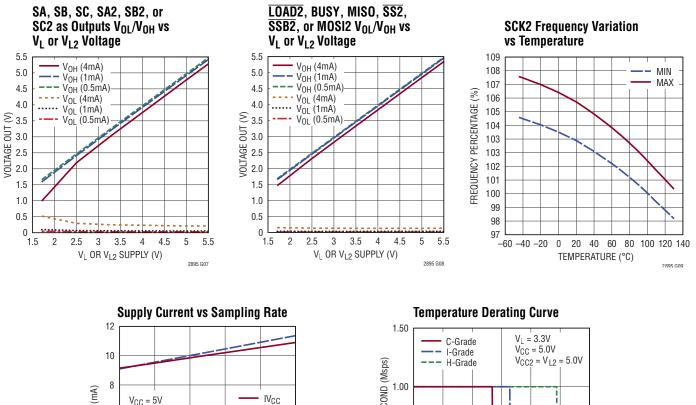

### TYPICAL PERFORMANCE CHARACTERISTICS

Specifications are at  $T_A = 25^{\circ}$ C.  $V_{CC} = 5$ V,  $V_L = 3.3$ V, GND = 0V,  $V_{CC2} = 5$ V,  $V_{L2} = 5.0$ V, GND2 = 0V, unless otherwise noted.

### PIN FUNCTIONS

Logic Side

(All Logic Side Inputs and Outputs Referenced to  $V_{\text{L}}$  and GND).

**ON (A1):** LTM2895 Enable. A high input enables the LTM2895 logic side. Do not float. When ON is low and  $V_L$  is high, the logic side is in reset, MOSI, SCK,  $\overline{LOAD}$ , and MISO are high impedance, an external pull-up or pull-down resistor (100k or greater) is required on each pin to minimize possible internal shoot though current if these pins float.

**SS** (A2): Slave Select Input (Low True Slave Chip Select). A low on the SS input enables MISO. Frame each word written or read through the isolator with the SS input. SS contains a weak pull-up to  $V_L$ . SSB must be high for SS to be enabled.

**MOSI (A3):** Master Out Slave In Input. Serial data to be written to the isolated DAC side (MOSI2). MOSI is also the serial data input for the configuration registers. Add a weak pull-up or pull-down resistor to MOSI pin to set valid logic condition during the high impedance state.

**SCK (A4):** Serial Port Clock Input. MISO data changes after a rising edge of the SCK input. MOSI data is read in on the rising edge of the SCK input. Add a weak pull-down resistor to SCK to set a valid logic condition if in a high impedance state.

**BUSY (A5):** Busy Output. A High on the BUSY output indicates the isolator is in progress of startup and the isolated side is not ready. When BUSY goes low, the system is ready.

**LOAD** (A6): DAC Load Input. The falling edge of the LOAD signal is transferred to the LOAD2 output with low jitter creating a narrow 25ns to 80ns pulse. Do not change the LOAD input during a read or write of the serial digital interface. LOAD is not necessary and is dependent on the DAC requirements. If the LTM2895 is in a generic SPI application or the DAC does not use a LOAD signal, connect LOAD to V<sub>L</sub>. Do not float.  $V_L$  (B1): Logic Interface Supply. Recommended operating voltage is 1.71V to 5.5V. Interface supply voltage for pins SA, SB, SC, ON, MISO, MOSI, SCK,  $\overline{SS}$ ,  $\overline{SSB}$ , BUSY, LOAD. Internally bypassed to GND with 1µF.

**MISO (B2):** Master In Slave Out Output. Serial data output containing the DAC result from MISO2. MISO is high impedance when  $\overline{SS}$  is high. Add a weak pull-up or pull-down resistor to MISO pin to set a valid logic condition during the high impedance state.

**GND (B3, B5, C2, C3):** Circuit Ground. Return for  $V_L$  logic supply and  $V_{CC}$  supply.

**SSB** (B4): Chip Select Configuration Input (SSB Chip Select). A low on the SSB input enables access to the configuration register. If configured for a 2nd DAC channel, the SSB signal is configured as a second slave select. Configuration Registers section describes configurable options. SSB contains a weak pull-up to  $V_L$ . SS must be high for SSB to be enabled.

**FAULT (B6):** Fault Output Open Drain. A low on the FAULT output indicates a communication or command error. Connect to an external 10k pull-up to  $V_L$  to monitor fault events.

$V_{CC}$  (C1): Supply Voltage. Recommended operating voltage is 3.0V to 5.5V. Internally bypassed to GND with 1µF.

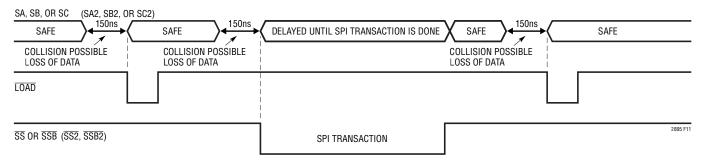

**SA (C4):** Select Enable Channel A. Select signal pass through to SA2 to control an external multiplexer or programmable gain amplifier. Transitions must not occur within 150ns of a LOAD, SSB, or SS edge. See section SA, SB, SC Safe Transition Regions for timing constraints. Do not use as a general purpose asynchronous signal. SA contains a weak pull-down. Direction is set in the configuration register. Connect to GND when not used.

**SB** (**C5**): Select Enable Channel B. Select signal pass through to SB2 to control an external multiplexer or programmable gain amplifier. Transitions must not occur within 150ns of a LOAD, SSB, or SS edge. See section SA, SB, SC Safe Transition Regions for timing constraints. Do not use as a general purpose asynchronous signal. SB contains a weak pull-down. Direction is set in the configuration register. Connect to GND when not used.

### PIN FUNCTIONS

**SC (C6):** Select Enable Channel C. Select signal pass through to SC2 to control an external multiplexer or programmable gain amplifier. Transitions must not occur within 150ns of a LOAD, SSB, or SS edge. See section SA, SB, SC Safe Transition Regions for timing constraints. Do not use as a general purpose asynchronous signal. SC contains a weak pull-down. Direction is set in the configuration register. Connect to GND when not used.

#### **Isolated Side**

# (All Isolated Side Inputs and Outputs Referenced to $\rm V_{L2}$ and GND2).

$V_{CC2}$  (N1): Isolated Voltage Supply. Recommended operating voltage is 3.0V to 5.5V. Internally bypassed to GND2 with 1µF.

**GND2 (N2, N3, P3, P5):** Isolated Ground Return. Keep separate from GND.

**SA2 (N4):** Select Enable Channel A. Select signal pass through from SA to control an external multiplexer or programmable gain amplifier. See section SA, SB, SC Safe Transition Regions for timing constraints. Do not use as a general purpose asynchronous signal. SA2 contains a weak pull-down. Direction is set in the configuration register.

**SB2 (N5):** Select Enable Channel B. Select signal pass through from SB to control an external multiplexer or programmable gain amplifier. See section SA, SB, SC Safe Transition Regions For timing constraints. Do not use as a general purpose asynchronous signal. SB2 contains a weak pull-down. Direction is set in the configuration register.

**SC2 (N6):** Select Enable Channel C. Select signal pass through from SC to control an external multiplexer or programmable gain amplifier. See section SA, SB, SC Safe Transition Regions for timing constraints. Do not use as a general purpose asynchronous signal. SC2 contains a weak pull-down. Direction is set in the configuration register.

$V_{L2}$  (P1): Interface Supply Voltage. Recommended operating voltage is 1.71V to 5.5V. Interface supply voltage for pins ON2, SA2, SB2, SC2, MISO2, MOSI2, SCK2, SS2, SSB2 and LOAD2. Internally bypassed to GND2 with 1µF.

**MISO2 (P2):** Master In Slave Out Input. Serial data input receiving the results from a general SPI device or a read back from a DAC. MISO2 is high impedance when SS2 and SSB2 are high. MISO2 has a weak pull-down to maintain a valid logic low during high impedance conditions when ON2 is high. Connect to GND if not used.

**SSB2** (P4): Isolated Side Second Slave Select Output (Slave Chip Select 2). Output controlled by internal communication functions to write data to a second DAC or SPI interface.

DNC (P6): Do Not Connect.

**ON2 (R1):** Isolated Interface Enable. A high input enables the isolated side communication interface. Do not float. When ON2 is low and  $V_{L2}$  is high, the isolated side is in reset,  $\overline{LOAD2}$ , MOSI2, SCK2, and MISO2 are high impedance, an external pull-up or pull-down resistor (100k or greater) is required on each pin to minimize possible internal shoot though current if these pins float.

**SS2** (R2): Isolated Side Slave Select Output (Slave Chip Select). Output controlled by internal communication functions to write data to slave DAC.

**MOSI2 (R3):** Isolated Master Out Slave In Output. Serial data output sending command data to the DAC.

**SCK2 (R4):** Isolated Serial Clock Output. Serial clock output to the SPI interface. SCK2 is low when SS2 is high.

DNC (R5): Do Not Connect.

**LOAD2** (R6): Isolated Load DAC Output. Connect to DAC LDAC input. If unused connect to  $V_{L2}$  with a 100k pull-up. Do not float.

### LTM2895

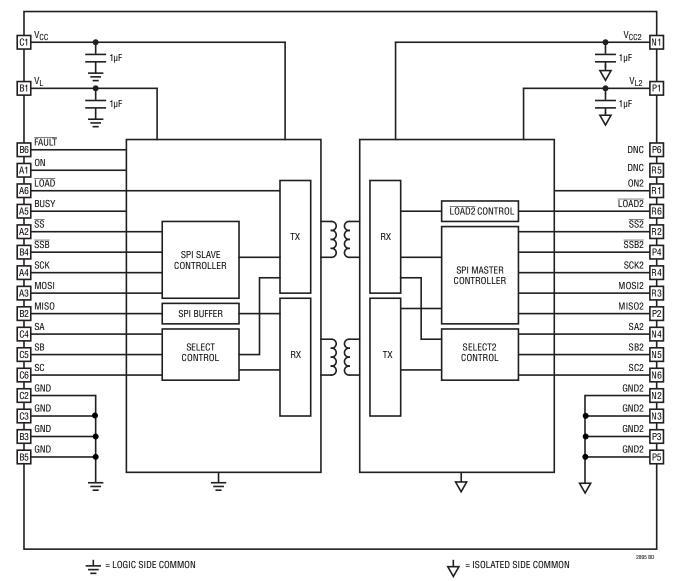

### **BLOCK DIAGRAM**

#### **OVERVIEW**

The LTM2895  $\mu$ Module transceiver provides a galvanically isolated robust SPI interface including decoupling capacitors. This flexible device can support a variety of configurations and SCK frequencies. The LTM2895 is ideal for breaking ground loops, noise isolation, protecting equipment, or level shifting to a different ground reference. Error free operation is maintained through common mode events exceeding 50kV/µs, providing excellent noise isolation.

The LTM2895 can drop into most 4-wire SPI applications from 500kHz to 50MHz, without any configuration required. To meet the specific needs of other SPI and DAC applications, the LTM2895 can be personalized with a configuration register allowing eight frequency and eight word-length choices. The LTM2895 operates as a slave SPI interface on the logic side and as a master SPI interface on the isolated side. Only the necessary signal edges are transferred across the isolation barrier and the SPI pattern is recreated on the isolated side. Data read back from the isolated side is temporarily stored in a buffer and the result is delayed by one word-length. See Figure 9 for a timing diagram of the SPI interface across the LTM2895.

Additional isolated signals are included to support features of an isolated SPI device. DACs that support a LOAD DAC input can use the low jitter  $\overline{LOAD}$  signal for updating their outputs. Reset, clear, or multiplexer functions are supported with the bidirectional select signals SA, SB, and SC.

A fault detection system watches for errors in input conditions and isolated data corruption and reports on a single open drain FAULT output.

#### ISOLATOR µModule TECHNOLOGY

The LTM2895 utilizes isolator  $\mu$ Module technology to translate signals across an isolation barrier. Signals on either side of the barrier are encoded into pulses and translated across the isolation boundary using differential signaling through coreless transformers formed in the  $\mu$ Module substrate. This system, complete with error checking, fault detection on fail, and extremely high common mode im-

munity, provides a robust solution for bidirectional signal isolation. The  $\mu$ Module technology provides the means to combine the isolated signaling with our SPI transceiver in one small package.

#### **SPI REQUIREMENTS**

The SPI bus lacks a formal standard and, therefore, various implementations of protocol, bit lengths, and signal polarities exist. In the universe of devices with serial peripheral interfaces (SPI), a nominal set of requirements must be met to operate properly with the LTM2895. The signal flow of a standard SPI protocol is used with a requirement that the  $\overline{SS}$  (Chip Select) signal frames the transaction. The LTM2895 supports SPI mode (0, 0), where SCK captures data on the rising edge (CPHA = 0) and SCK starts low and transitions high (CPOL = 0).

The following list summarizes the requirements for using the LTM2895.

- Configure the SCK2 frequency to the master and application device requirements

- SPI operates in mode (0, 0) (rising edge SCK captures data)

- Chip Select signal (SS or SSB) frames SPI pattern and meets watchdog timeout requirements

First, the SCK2 frequency is selected to operate with the device connected to the isolated side of the LTM2895. The SCK2 frequency sets the low time of the clock signal ( $t_{SCK2L}$ ) out of the LTM2895 and into the isolated SPI interface. See section SCK2 FREQUENCY for specific timing information. The master SCK frequency must be equal or slower than the SCK2 frequency and greater than the watchdog timeout.

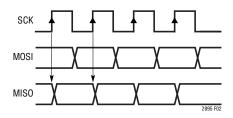

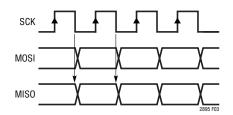

Second, the LTM2895 logic side operates in mode (0, 0) with a variation on which edge of the SCK data shifts out on. For configured SCK2 frequencies of 100MHz and 66MHz, the MOSI data is captured and the MISO data is shifted on the rising edge of SCK, as shown in Figure 2. This variation allows for additional propagation and setup time to the next rising clock (SCK) edge. All setup and hold timing characteristics are related to the rising edge of

the SCK. For configured SCK2 frequencies of 50MHz and lower, MOSI is captured on the rising edge and MISO is shifted on the falling edge of SCK, as shown in Figure 3.

The isolated side always operates in mode (0, 0). MOSI2 sets up data on the falling edge of SCK2 and MISO2 is captured on the rising edge of SCK2.

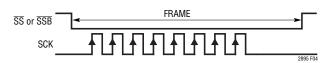

Third, the slave selects  $\overline{SS}$  and  $\overline{SSB}$  must be dedicated to framing the operation of reading or writing data. The  $\overline{SS}$  or  $\overline{SSB}$  must go low at the beginning of the SPI transaction prior to the SCK transitions and must go high after the last SCK rising edge transition, see Figure 4.

Figure 2. SCK and Data with SCK2 Frequency Configured for 100MHz or 66MHz

Figure 3. SCK and Data with SCK2 Frequency Configured for 50MHz or Less

Figure 4. SPI Transaction with  $\overline{SS}$  or  $\overline{SSB}$  Framing SCK

#### LOAD INPUT

$\overline{\text{LOAD}}$  input is a low jitter path available for digital to analog converters that offers a low true LOAD DAC (LDAC) input. The  $\overline{\text{LOAD}}$  to  $\overline{\text{LOAD2}}$  signal is initiated on a falling edge. The rising edge of  $\overline{\text{LOAD}}$  is ignored. The rising edge of  $\overline{\text{LOAD2}}$  is generated internally and has up to 5ns of jitter. The low pulse width of  $\overline{\text{LOAD2}}$  is dependent on the configured SCK2 frequency. For SCK2 frequencies of

40MHz or greater,  $\overline{\text{LOAD2}}$  has a pulse width of ~40ns, and for SCK2 frequencies of 33MHz or below,  $\overline{\text{LOAD2}}$  has a pulse width of ~60ns.

$\overline{\text{LOAD}}$  is not necessary to interact with the isolated SPI device. When  $\overline{\text{LOAD}}$  is unused connect it to V<sub>L</sub>.

#### **READ BACK DATA**

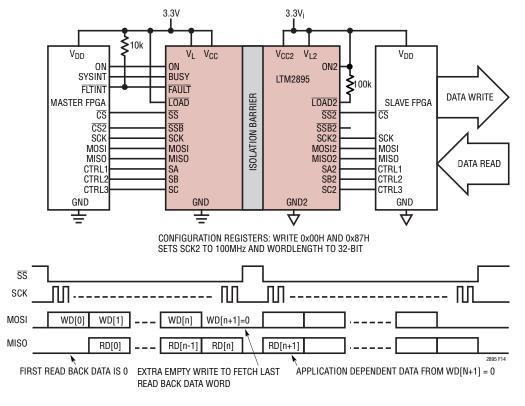

Data can be read back from the isolated side MISO2 pin to MISO. The data read out of the MISO pin has one word of latency data[n-1]. The MISO pin is only utilized during transactions when the primary chip select,  $\overline{SS}$ , is active. When data is read from the isolated side's MISO2 data[n], it is placed in a circular FIFO buffer on the logic side. The current data in the buffer (data[n-1]) is shifted out on the MISO output. New data from the isolated side will fill in the buffer behind it. The very first word read out of the buffer after a startup is all "0"s.

The LTM2895 uses read and write pointers to track the current bit locations for data[n] and data[n-1]. If the SPI communication is unexpectedly halted from the master controller and then recovers or is reconnected during a different transaction, the internal relative alignment of the pointers may be lost resulting in an offset in the read back data. If an offset in the data is detected, the pointers may be resynchronized by resetting the LTM2895. To reset the LTM2895, toggle the ON pin low for 1µs and then reload the configuration register.

#### **SPI PAGE MODE**

SPI page mode allows large data transfers of multiple words within a slave select frame. To operate in page mode beyond the defined wordlength, maintain SS low and continue clocking SCK the desired number of wordlength multiples. SCK must end on a wordlength boundary. Further, maintain the timing between rising edges of SCK and the timing between SS and SCK so a watchdog event is not triggered.

The read back data on MISO is one word-length delayed. See Figure 14 for an example of page mode operation and the relationship of words into and out of the LTM2895.

2895fa

#### STARTUP

The LTM2895 has an internal startup communication routine to verify both sides of the isolation are ready for communication. The startup routine is initiated when power is supplied to  $V_{CC}$  and  $V_{CC2}$  inputs above 2.75V,  $V_L$  and  $V_{L2}$  inputs above 1.5V, the logic side ON signal is high, and the isolated ON2 signal is high. The BUSY signal will go high and then low indicating the two internal isolators have completed a startup routine. Once the BUSY output goes low, the system is ready.

The isolated ON2 pin allows independent enabling of the isolator. External voltage monitoring can be used to enable the ON2 input when all isolated supplies and systems are ready.

#### **BUSY INDICATOR**

During startup, the BUSY output is set high to indicate the LTM2895 is powering up and will be de-asserted when isolated communication is verified through a startup routine. Monitor the BUSY output as a system ready signal.

If BUSY goes high during a FAULT, the internal watchdog timer has been asserted. See section Watchdog Timer for an explanation of situations that cause a watchdog timeout.

#### FAULT REPORTING

A FAULT pin is supplied to indicate the occurrence of a communication error or an erroneous input condition. The FAULT pin is open drain and requires an external pull-up resistance (10k) to the V<sub>L</sub> supply. If the FAULT pin is asserted low, data loss may have occurred and the current transaction may be invalid. To clear the FAULT pin, return LOAD to a high and SS and SSB to a high and initiate a new transition on one of these signals.

Possible fault conditions are listed in Table 1. Other than a watchdog timeout, which is indicated by BUSY high and FAULT low, the LTM2895 does not indicate which condition caused the fault.

| Table | 1. | Fault | Repo | rting |

|-------|----|-------|------|-------|

|-------|----|-------|------|-------|

| Table 1. Fault Hoperting                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAULTS                                                                                                                                  | CAUSE/TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Idle time during serial digital<br>interface read (watchdog<br>expired), see Table 4                                                    | SCK $\uparrow$ to SCK $\uparrow$ > t <sub>WATCHDOG_TIMEOUT</sub> ns.<br>Minimize the delay between this relationship<br>to less than t <sub>WATCHDOG_TIMEOUT</sub> ns.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Transient data loss in isolation communication                                                                                          | Common mode transients (GND to GND2) greater than 50kV/µs. High transient EM field disturbances greater than specified in EN61000, or an ESD event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Isolated side power loss                                                                                                                | ON2, $V_{L2}$ , or $V_{CC2}$ was removed and returned. Indicates unexpected interface loss.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LOAD falling edge during<br>serial digital interface read<br>or LOAD falling edge 100ns<br>before or after a transition on<br>SS or SSB | Avoid transitioning $\overline{\text{LOAD}}$ during the read/<br>write of the serial digital interface. $\overline{\text{LOAD}}$<br>will be ignored during the read of the<br>serial digital interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Buffer under run                                                                                                                        | SCK frequency exceeds the SCK2 frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input transition collisions<br>causing data loss or the<br>watchdog to expire                                                           | eq:static-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state-state |

#### WATCHDOG TIMER

The LTM2895 contains a watchdog timer to monitor interactions between the SPI port and the isolated communication. The watchdog looks for stalled communication on pins  $\overline{SS}$  and SCK. A stalled or delayed input on SCK when  $\overline{SS}$  is low for a longer time than  $t_{SCK2} \bullet 128$  will flag a fault and reset the core logic. At the maximum SCK2 frequency of 100MHz, the watchdog will timeout if  $\overline{SS}$  is low without an SCK transition for greater than 1.25µs. The Table 4 column  $t_{WATCHDOG_TIMEOUT}$  quantifies the trip points for the watchdog for each SCK2 frequency configuration.

The FAULT output will be asserted low along with the BUSY output asserted high, when a watchdog timeout occurs. A Fault due to the watchdog will clear the configuration register and re-writing the configuration registers is necessary.

#### **CONFIGURATION REGISTER**

The LTM2895 contains a configuration register to adjust parameters of the speed and features of the SPI write and

read process. After powering up the LTM2895, and after BUSY goes low, write the configuration register by asserting the SSB chip select input low and clock in a one byte configuration word with SCK and MOSI. Two registers are addressable with the most significant bit of the configuration byte. Complete each configuration word by reasserting SSB high. The isolated side will be automatically configured to match the logic side. By default SCK2 = 50MHz, SA, SB, SC = 0, and the wordlength is 8 bits.

See Table 3 for the configuration register bit map for controlling the operation and frequency of the logic and isolated SPI ports. The configuration register allows adjustment of the default SCK2 frequency, direction of the SA, SB, SC to SA2, SB2, SC2 signals, and the length of the SPI word.

#### DUAL CHIP SELECTS (SS AND SSB)

The primary chip select SS passes through the isolator to <u>SS2</u>. The second chip select, <u>SSB</u>, by default is the enable to the configuration register. SSB can be configured as a second slave select, through the configuration register bit 5 (D5) "DAC 2nd Channel" in configuration register 1, address AD7. The "DAC 2nd Channel" bit converts the SSB signal from accessing the configuration registers into a second slave select that is communicated across the isolation barrier to output SSB2. Once the "DAC 2nd Channel" is selected, the LTM2895 cannot be reconfigured until a reset due to toggling the ON pin or power loss and recovery. When configured for DAC 2nd Channel, the SSB2 output can be connected to a second DAC or SPI interface device. The MOSI and SCK pins are shared. The two slave selects are then accessed sequentially requiring a short pause of duration t<sub>SSSPACE</sub> in between where both the SS and SSB are high. MISO does not read back from the second channel when SSB to SSB2 is active. MISO is dedicated to reading back data from the primary channel  $(\overline{SS} \text{ to } \overline{SS2}) \text{ only.}$

The clock speed and wordlength are the same for both channels. Consider the page mode functionality if the word-lengths are different but multiples of one another. An example of this is a primary channel with a 32-bit word-length requirement and secondary channel with a 16-bit word-length requirement. Set the LTM2895 wordlength configuration to 16 bits.

#### **SCK2 FREQUENCY**

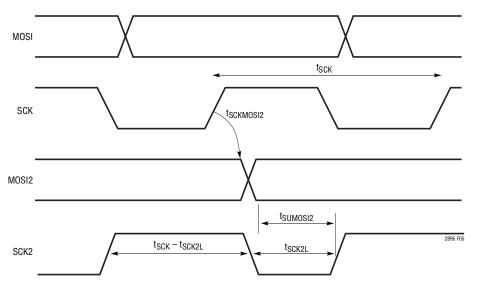

The SCK2 frequency selection list is shown in Table 4. The selected SCK2 frequency sets the minimum and maximum range the SCK frequency can operate at and sets the fixed low time of SCK2 ( $t_{SCK2L}$ ). The low time of SCK2 ( $t_{SCK2L}$ ) sets the setup time of the MOSI2 output to SCK2 rising ( $t_{SUMOSI2}$ ). The Isolated side SCK2 is not a free running shift clock. Each falling edge of SCK2 is driven directly from the rising edge of SCK as shown in Figure 5.

Select the SCK2 frequency that is equal or less than the specifications of the application device's SPI port from Table 2.

SCK2 minimum low time ( $t_{SCK2L}$ ) must be greater than the following characteristics of the application device:

- Minimum low time of the shift clock (SCK) required by the isolated SPI device

- The required setup time from the isolated SPI device's SDI to SCK

- The data valid response on the SPI device's SDO to the LTM2895's MISO2 setup requirement to SCK2 rising

Example: the LTC<sup>®</sup>2642 has a minimum SCK low time of 9ns, and a minimum SDI to SCK setup time of 10ns; therefore, configure SCK2 frequency for 40MHz ( $t_{SCK2L}$ = 13.8ns) or less. The logic side SPI SCK frequency cannot exceed the SCK2 frequency. Access the LTM2895 with an SCK frequency between the configured SCK2 and ~0.009 • SCK2. This guarantees the internal SPI transfer will not under-run or exceed a watchdog timeout and assert a FAULT. In the case of an under-run, the FAULT flag will assert low.

| SCK2 Selection (MHz) | t <sub>SCK2L</sub> Minimum (ns) |

|----------------------|---------------------------------|

|                      |                                 |

| 100                  | 4.5                             |

| 66                   | 9.1                             |

| 50                   | 9.1                             |

| 40                   | 13.8                            |

| 33                   | 13.8                            |

| 25                   | 18.2                            |

| 12.5                 | 36.4                            |

| 6.25                 | 72.9                            |

|                      |                                 |

2895f

#### SCK2 DUTY CYCLE

The SCK2 output frequency will match that of SCK, but will not have the same duty cycle unless the frequency of SCK equals the frequency of SCK2. The high time of SCK2 will extend and the low time of SCK2 will remain at the defined low time of the configuration frequency  $t_{SCK2L}$  as shown in Figure 5. The high time of SCK2 compensates for the difference between the external SCK frequency and the internal oscillator creating the low time of SCK2.

#### SELECT SIGNALS

The select signal channels SA, SB, and SC are communicated to the isolated side channels SA2, SB2, and SC2, respectively. The select signals allow control of an external device related to the SPI channel. Analog multiplexers or programmable gain amplifiers with logic control signals are examples of devices to use with the select signals. The signals can be used as logic controls for clear, reset, or power down functions that are not expected to occur during processing of a SPI transaction. The select signals are not designed for use as general purpose logic signals with asynchronous transition times. Use of these signals must be kept synchronous and outside of the operation of the LOAD,  $\overline{SSB}$ , or  $\overline{SS}$  active duration. Data and time sensitive information may be lost if a select signal. The select signals are sampled and transferred as a packet of the current value of the three signals. The select signal sampling will have up 10ns of sampling jitter. If a signal transitions after another signal was sampled and is in the process of being transferred to the adjacent side, it will be delayed until an available transmission slot is available. The delay may cause a perceived jitter or uncertainty of 80ns.

#### **SELECT SIGNALS DIRECTION**

Within the configuration register SA, SB, and SC direction bits allow independent selection of the direction of signal flow from logic-to-isolated or isolated-to-logic. The default direction for each select signal is logic-to-isolated. Loading a "1" into a direction bit will change the direction of that pin to isolated-to-logic. When a "1" is loaded into the direction bit of a specific select signal the logic side select signal will become an output and the isolated side select signal will become and input.

**Warning**: Careful planning is required for the use of SA, SB, and SC signals. The SA, SB, SC signals must not change state within 150ns prior to  $\overline{LOAD}$ ,  $\overline{SSB}$ , or  $\overline{SS}$  on the logic side. If a signal is configured for isolated-to-logic signal flow, it must not change state within 150ns prior to when  $\overline{SS}$  or  $\overline{SSB}$  is asserted by the LTM2895. Figure 11 shows the regions were transitions are safe and not safe for the logic side interface.

Figure 5. SCK to SCK2 and MOSI to MOSI2 Data Transfer Relationship

#### WORDLENGTH

The word-length configuration bits (DO - D2, configuration register 0) sets the number of bits per word. The word-length assignment allows the SPI access to be tailored to a specific DAC data length to maximize throughput. Table 6 lists the available combinations. If the master device requires byte-wide increments, set wordlength to a byte size boundary (8, 16, 24, or 32).

For example, a single 16-bit DAC is configured with a wordlength of 16. Two 16-bit DACs in parallel ( $\overline{CS}$  of DAC1

#### Table 3. Configuration Registers

connected to  $\overline{SS2}$  and  $\overline{CS}$  of DAC2 connected to  $\overline{SSB2}$ ) are also configured with a wordlength of 16.

Figure 12 through Figure 14 demonstrates the LTM2895 in a number of flexible applications.

#### **DIGITAL INTERFACE**

The flexible V<sub>L</sub> and V<sub>L2</sub> supplies allows the LTM2895 to communicate with digital logic operating between 1.71V and 5.5V, including 2.5V and 3.3V systems.

|                             | BIT 7<br>Address (Ad7) | BIT 6 (D6)      | BIT 5 (D5)         | BIT 4 (D4)      | BIT 3 (D3)      | BIT 2 (D2)                                           | BIT 1 (D1)                                           | BIT 0 (D0)                                           |

|-----------------------------|------------------------|-----------------|--------------------|-----------------|-----------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|

| Configuration<br>Register 0 | 0                      | OSCDIV2         | OSCDIV1            | OSCDIVO         | Reserved<br>"0" | SC Direction<br>0 = Logic-to-ISO<br>1 = ISO-to-Logic | SB Direction<br>0 = Logic-to-ISO<br>1 = ISO-to-Logic | SA Direction<br>0 = Logic-to-ISO<br>1 = ISO-to-Logic |

| Configuration<br>Register 1 | 1                      | Reserved<br>"O" | DAC 2nd<br>Channel | Reserved<br>"0" | Reserved<br>"0" | WORDLENGTH2                                          | WORDLENGTH1                                          | WORDLENGTHO                                          |

#### Table 4. SCK2 Frequency Selection Table (Configuration Register 0 BIT 6, 5, and 4)

| OSCDIV2<br>(BIT 6) | OSCDIV1<br>(BIT 5) | OSCDIVO<br>(BIT 4) | SELECTED SCK2<br>AND MAXIMUM SCK<br>FREQUENCY (MHz) | MINIMUM<br>t <sub>SCK2L</sub> TIME (ns) | MINIMUM SCK<br>FREQUENCY (kHz) | t <sub>watchdog_timeout</sub> MAXIMUM t <sub>sck</sub><br>Period or idle time with 5S low<br>(tssfsck, tsckssdis) (μs) |

|--------------------|--------------------|--------------------|-----------------------------------------------------|-----------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 0                  | 0                  | 0                  | 100                                                 | 4.5                                     | 909                            | 1.1                                                                                                                    |

| 0                  | 0                  | 1                  | 66                                                  | 9.1                                     | 588                            | 1.7                                                                                                                    |

| 0                  | 1                  | 0                  | 50                                                  | 9.1                                     | 435                            | 2.3                                                                                                                    |

| 0                  | 1                  | 1                  | 40                                                  | 13.8                                    | 364                            | 2.75                                                                                                                   |