LTC2758

Dual Serial 18-Bit

SoftSpan I<sub>OUT</sub> DACs

### FEATURES

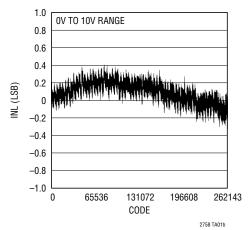

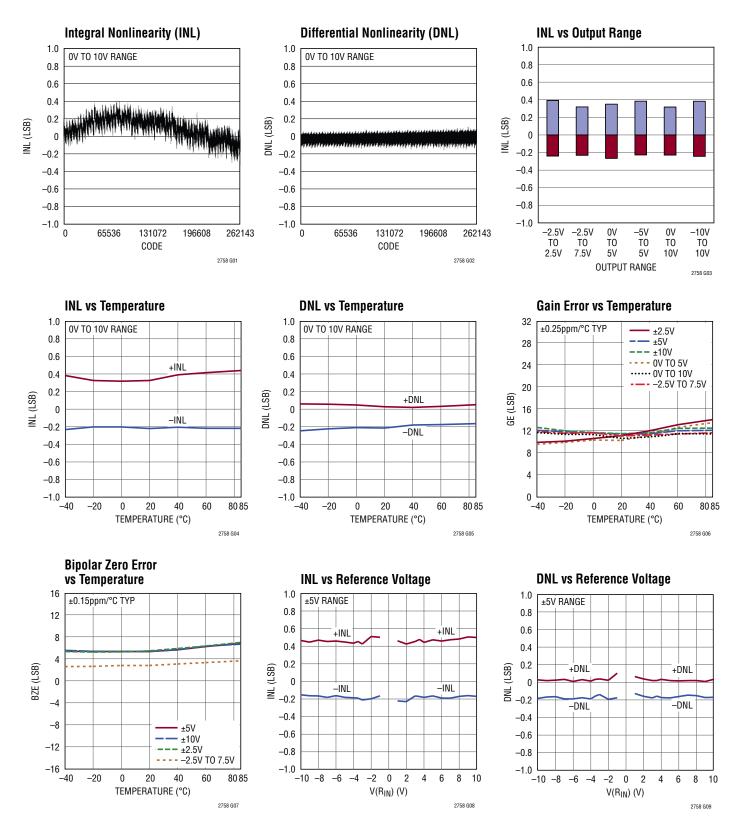

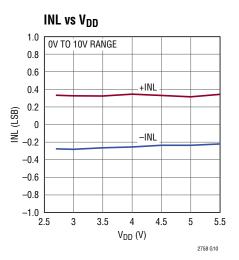

- Maximum 18-Bit INL Error: ±1 LSB Over Temperature

- Program or Pin-Strap Six Output Ranges: OV to 5V, OV to 10V, -2.5V to 7.5V, ±2.5V, ±5V, ±10V

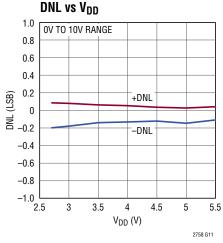

- Guaranteed Monotonic Over Temperature

- Glitch Impulse 0.4nV•s (3V), 2nV•s (5V)

- 18-Bit Settling Time: 2.1µs

- 2.7V to 5.5V Single Supply Operation

- 1µA Maximum Supply Current

- Voltage-Controlled Offset and Gain Trims

- Serial Interface with Readback of All Registers

- Clear and Power-On-Reset to 0V Regardless of Output Range

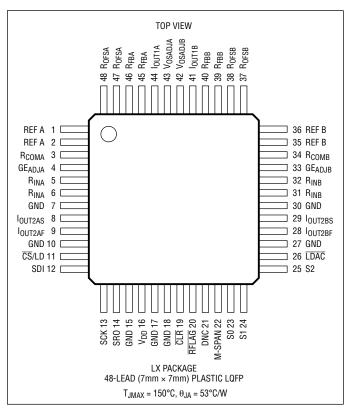

- 48-Pin 7mm × 7mm LQFP Package

### **APPLICATIONS**

- Instrumentation

- Medical Devices

- Automatic Test Equipment

- Process Control and Industrial Automation

### DESCRIPTION

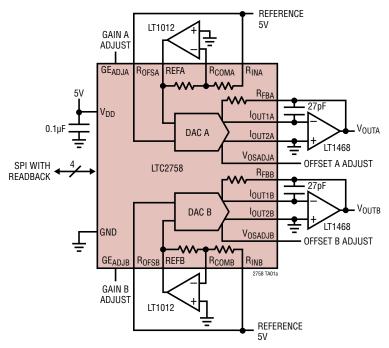

The LTC<sup>®</sup>2758 is a dual 18-bit multiplying serial-input, current-output digital-to-analog converter. LTC2758A provides full 18-bit performance (INL and DNL of  $\pm$ 1LSB maximum) over temperature without any adjustments. 18-bit monotonicity is guaranteed in all performance grades. This SoftSpan<sup>TM</sup> DAC operates from a single 3V to 5V supply and offers six output ranges (up to  $\pm$ 10V) that can be programmed through the 3-wire SPI serial interface or pin-strapped for operation in a single range.

Any on-chip register (including DAC output-range settings) can be read for verification in just one instruction cycle; and if you change register content, the altered register will be automatically read back during the next instruction cycle.

Voltage-controlled offset and gain adjustments are also provided; and the power-on reset circuit and CLR pin both reset the DAC outputs to OV regardless of output range.

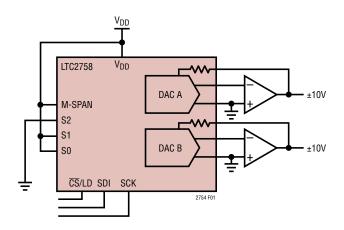

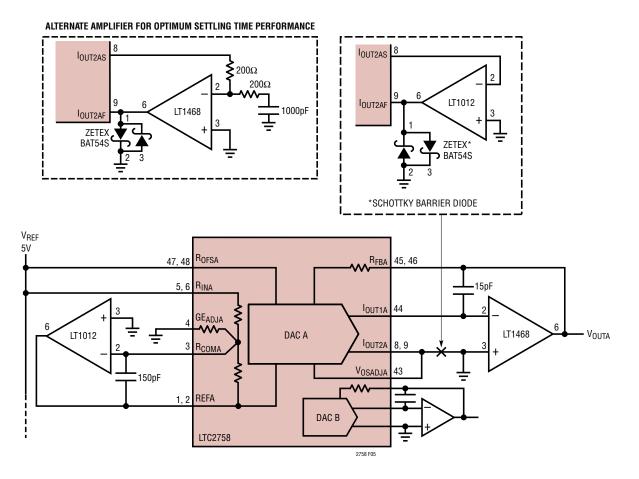

### TYPICAL APPLICATION

Dual 18-Bit VOUT DAC with Software-Selectable Ranges

#### LTC2758 Integral Nonlinearity

### ABSOLUTE MAXIMUM RATINGS

(Notes 1, 2)

| I <sub>OUT1X</sub> , I <sub>OUT2X</sub> to GND±0.3V                                                       |

|-----------------------------------------------------------------------------------------------------------|

| R <sub>INX</sub> , R <sub>COMX</sub> , REFX, R <sub>FBX</sub> , R <sub>OFSX</sub> , V <sub>OSADJX</sub> , |

| GE <sub>ADJX</sub> to GND±18V                                                                             |

| V <sub>DD</sub> to GND–0.3V to 7V                                                                         |

| Digital Inputs to GND–0.3V to 7V                                                                          |

| Digital Outputs to GND–0.3V to V <sub>DD</sub> +0.3V (max 7V)                                             |

| Operating Temperature Range                                                                               |

| LTC2758C                                                                                                  |

| LTC2758I–40°C to 85°C                                                                                     |

| Maximum Junction Temperature 150°C                                                                        |

| Storage Temperature Range65°C to 150°C                                                                    |

| Lead Temperature (Soldering, 10 sec)                                                                      |

|                                                                                                           |

### PIN CONFIGURATION

### ORDER INFORMATION http://www.linear.com/product/LTC2758#orderinfo

| LEAD FREE FINISH | PART MARKING* | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |

|------------------|---------------|----------------------------------|-------------------|

| LTC2758BCLX#PBF  | LTC2758LX     | 48-Lead (7mm × 7mm) Plastic LQFP | 0°C to 70°C       |

| LTC2758BILX#PBF  | LTC2758LX     | 48-Lead (7mm × 7mm) Plastic LQFP | –40°C to 85°C     |

| LTC2758ACLX#PBF  | LTC2758LX     | 48-Lead (7mm × 7mm) Plastic LQFP | 0°C to 70°C       |

| LTC2758AILX#PBF  | LTC2758LX     | 48-Lead (7mm × 7mm) Plastic LQFP | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** $V_{DD} = 5V$ , $V(R_{INX}) = 5V$ unless otherwise specified. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| SYMBOL           | PARAMETER                            | CONDITIONS                                               |   | MIN | LTC2758E<br>Typ | B<br>MAX   | MIN | LTC2758A<br>TYP | MAX        | UNITS          |

|------------------|--------------------------------------|----------------------------------------------------------|---|-----|-----------------|------------|-----|-----------------|------------|----------------|

| Static Per       | formance                             | 1                                                        |   |     |                 |            |     |                 |            |                |

|                  | Resolution                           |                                                          |   | 18  |                 |            | 18  |                 |            | Bits           |

|                  | Monotonicity                         |                                                          | • | 18  |                 |            | 18  |                 |            | Bits           |

| DNL              | Differential Nonlinearity            |                                                          | • |     |                 | ±1         |     | ±0.2            | ±1         | LSB            |

| INL              | Integral Nonlinearity                |                                                          |   |     |                 | ±2         |     | ±0.5            | ±1         | LSB            |

| GE               | Gain Error                           | All Output Ranges                                        | • |     |                 | ±48        |     | ±6              | ±32        | LSB            |

|                  | Gain Error Temperature Coefficient   | ∆Gain/∆Temp                                              |   |     | ±0.25           |            |     | ±0.25           |            | ppm/°C         |

| BZE              | Bipolar Zero Error                   | All Bipolar Ranges                                       | • |     |                 | ±36        |     | ±1              | ±24        | LSB            |

|                  | Bipolar Zero Temperature Coefficient |                                                          |   |     | ±0.2            |            |     | ±0.2            |            | ppm/°C         |

|                  | Unipolar Zero-Scale Error            | Unipolar Ranges (Note 3)                                 | • |     | ±0.03           | ±3.2       |     | ±0.03           | ±3.2       | LSB            |

| PSR              | Power Supply Rejection               | V <sub>DD</sub> = 5V, ±10%<br>V <sub>DD</sub> = 3V, ±10% | • |     |                 | ±1.6<br>±4 |     | ±0.1<br>±0.3    | ±0.8<br>±2 | LSB/V<br>LSB/V |

| I <sub>LKG</sub> | I <sub>OUT1</sub> Leakage Current    | $T_A = 25^{\circ}C$<br>$T_{MIN}$ to $T_{MAX}$            | • |     | ±0.05           | ±2<br>±5   |     | ±0.05           | ±2<br>±5   | nA<br>nA       |

# $V_{DD} = 5V$ , $V(R_{INX}) = 5V$ unless otherwise specified. The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| SYMBOL              | PARAMETER                        | CONDITIONS                                                     |   | MIN  | ТҮР        | MAX | UNITS        |  |  |  |  |  |

|---------------------|----------------------------------|----------------------------------------------------------------|---|------|------------|-----|--------------|--|--|--|--|--|

| Analog Pins         |                                  |                                                                |   |      |            |     |              |  |  |  |  |  |

|                     | Reference Inverting Resistors    | (Note 4)                                                       |   | 16   | 20         |     | kΩ           |  |  |  |  |  |

| R <sub>REF</sub>    | DAC Input Resistance             | (Notes 5, 6)                                                   |   | 8    | 10         |     | kΩ           |  |  |  |  |  |

| R <sub>FB</sub>     | Feedback Resistors               | (Note 6)                                                       | • | 8    | 10         |     | kΩ           |  |  |  |  |  |

| R <sub>0FS</sub>    | Bipolar Offset Resistors         | (Note 6)                                                       | • | 16   | 20         |     | kΩ           |  |  |  |  |  |

| R <sub>VOSADJ</sub> | Offset Adjust Resistors          |                                                                | • | 1024 | 1280       |     | kΩ           |  |  |  |  |  |

| R <sub>GEADJ</sub>  | Gain Adjust Resistors            |                                                                | • | 2048 | 2560       |     | kΩ           |  |  |  |  |  |

| C <sub>IOUT1</sub>  | Output Capacitance               | Full-Scale<br>Zero-Scale                                       |   |      | 90<br>40   |     | pF           |  |  |  |  |  |

| Dynamic Perfo       | ormance                          |                                                                |   |      |            |     |              |  |  |  |  |  |

|                     | Output Settling Time             | Span Code = 0000, 10V Step. To ±0.0004%<br>FS (Note 7)         |   |      | 2.1        |     | μs           |  |  |  |  |  |

|                     | Glitch Impulse                   | V <sub>DD</sub> = 5V (Note 8)<br>V <sub>DD</sub> = 3V (Note 8) |   |      | 2<br>0.4   |     | nV∙s<br>nV∙s |  |  |  |  |  |

|                     | Digital-to-Analog Glitch Impulse | V <sub>DD</sub> = 5V (Note 9)<br>V <sub>DD</sub> = 3V (Note 9) |   |      | 2.6<br>0.6 |     | nV∙s<br>nV∙s |  |  |  |  |  |

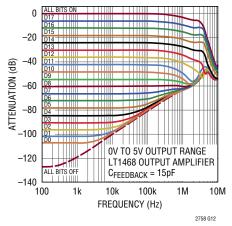

|                     | Reference Multiplying BW         | 0V to 5V Range,<br>Code = Full Scale, –3dB Bandwidth           |   |      | 1          |     | MHz          |  |  |  |  |  |

|                     | Multiplying Feedthrough Error    | 0V to 5V Range, V <sub>REF</sub> = ±10V, 10kHz<br>Sine Wave    |   |      | 0.4        |     | mV           |  |  |  |  |  |

|                     | Analog Crosstalk                 | (Note 10)                                                      |   |      | -109       |     | dB           |  |  |  |  |  |

| THD                 | Total Harmonic Distortion        | (Note 11) Multiplying                                          |   |      | -110       |     | dB           |  |  |  |  |  |

|                     | Output Noise Voltage Density     | (Note 12) at I <sub>OUT1</sub>                                 |   |      | 13         |     | nV/√Hz       |  |  |  |  |  |

# **ELECTRICAL CHARACTERISTICS** $V_{DD} = 5V$ , $V(R_{INX}) = 5V$ unless otherwise specified. The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| SYMBOL          | PARAMETER                      | CONDITIONS                                                                           |   | MIN                   | ТҮР | MAX        | UNITS  |  |  |  |  |

|-----------------|--------------------------------|--------------------------------------------------------------------------------------|---|-----------------------|-----|------------|--------|--|--|--|--|

| Power Supply    |                                |                                                                                      |   |                       |     |            |        |  |  |  |  |

| V <sub>DD</sub> | Supply Voltage                 |                                                                                      | • | 2.7                   |     | 5.5        | V      |  |  |  |  |

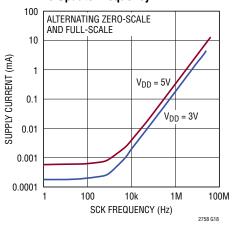

| I <sub>DD</sub> | V <sub>DD</sub> Supply Current | Digital Inputs = 0V or V <sub>DD</sub>                                               | • |                       | 0.5 | 2          | μA     |  |  |  |  |

| Digital Inputs  |                                |                                                                                      |   |                       |     |            |        |  |  |  |  |

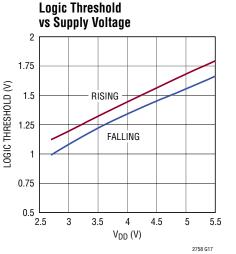

| V <sub>IH</sub> | Digital Input High Voltage     | $\begin{array}{l} 3.3V \leq V_{DD} \leq 5.5V \\ 2.7V \leq V_{DD} < 3.3V \end{array}$ | • | 2.4<br>2              |     |            | V<br>V |  |  |  |  |

| V <sub>IL</sub> | Digital Input Low Voltage      | $\begin{array}{l} 4.5V < V_{DD} \leq 5.5V \\ 2.7V \leq V_{DD} \leq 4.5V \end{array}$ | • |                       |     | 0.8<br>0.6 | V<br>V |  |  |  |  |

|                 | Hysteresis Voltage             |                                                                                      |   |                       | 0.1 |            | V      |  |  |  |  |

| I <sub>IN</sub> | Digital Input Current          | $V_{IN} = GND$ to $V_{DD}$                                                           | • |                       |     | ±1         | μA     |  |  |  |  |

| CIN             | Digital Input Capacitance      | V <sub>IN</sub> = 0V (Note 13)                                                       | • |                       |     | 6          | pF     |  |  |  |  |

| Digital Output  | S                              |                                                                                      | · |                       |     |            |        |  |  |  |  |

| V <sub>OH</sub> | I <sub>OH</sub> = 200μA        | $2.7V \le V_{DD} \le 5.5V$                                                           | • | V <sub>DD</sub> - 0.4 |     |            | V      |  |  |  |  |

| V <sub>OL</sub> | I <sub>0L</sub> = 200μA        | $2.7V \le V_{DD} \le 5.5V$                                                           | • |                       |     | 0.4        | V      |  |  |  |  |

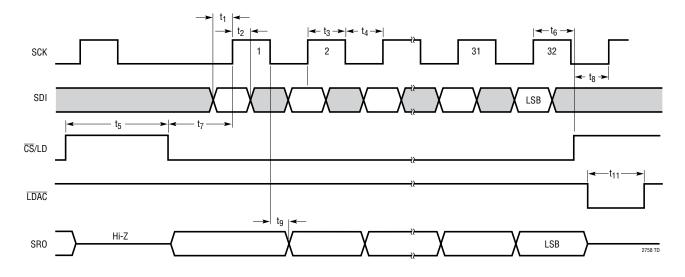

# **TIMING CHARACTERISTICS** The $\bullet$ denotes specifications that apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C.

| SYMBOL                 | PARAMETER                       | CONDITIONS                         |   | MIN | ТҮР | MAX | UNITS |

|------------------------|---------------------------------|------------------------------------|---|-----|-----|-----|-------|

| V <sub>DD</sub> = 4.5V | to 5.5V                         | 1                                  |   |     |     |     |       |

| t <sub>1</sub>         | SDI Valid to SCK Set-Up         |                                    | • | 7   |     |     | ns    |

| t <sub>2</sub>         | SDI Valid to SCK Hold           |                                    | • | 7   |     |     | ns    |

| t <sub>3</sub>         | SCK High Time                   |                                    | • | 11  |     |     | ns    |

| t <sub>4</sub>         | SCK Low Time                    |                                    | • | 11  |     |     | ns    |

| t <sub>5</sub>         | CS/LD Pulse Width               |                                    | • | 9   |     |     | ns    |

| t <sub>6</sub>         | LSB SCK High to CS/LD High      |                                    | • | 4   |     |     | ns    |

| t <sub>7</sub>         | CS/LD Low to SCK Positive Edge  |                                    | • | 4   |     |     | ns    |

| t <sub>8</sub>         | CS/LD High to SCK Positive Edge |                                    | • | 4   |     |     | ns    |

| t9                     | SRO Propagation Delay           | C <sub>LOAD</sub> = 10pF           | • |     |     | 18  | ns    |

| t <sub>10</sub>        | CLR Pulse Width Low             |                                    | • | 36  |     |     | ns    |

| t <sub>11</sub>        | LDAC Pulse Width Low            |                                    | • | 15  |     |     | ns    |

| t <sub>12</sub>        | CLR Low to RFLAG Low            | C <sub>LOAD</sub> = 10pF (Note 13) | • |     |     | 50  | ns    |

| t <sub>13</sub>        | CS/LD High to RFLAG High        | C <sub>LOAD</sub> = 10pF (Note 13) | • |     |     | 40  | ns    |

|                        | SCK Frequency                   | 50% Duty Cycle (Note 14)           | • |     |     | 40  | MHz   |

| V <sub>DD</sub> = 2.7V | to 3.3V                         |                                    |   |     |     |     |       |

| t <sub>1</sub>         | SDI Valid to SCK Set-Up         |                                    | • | 9   |     |     | ns    |

| t <sub>2</sub>         | SDI Valid to SCK Hold           | (Note 13)                          | • | 9   |     |     | ns    |

| t <sub>3</sub>         | SCK High Time                   | C <sub>L</sub> = 10pF              | • | 15  |     |     | ns    |

| t <sub>4</sub>         | SCK Low Time                    |                                    | • | 15  |     |     | ns    |

| t <sub>5</sub>         | CS/LD Pulse Width               |                                    | • | 12  |     |     | ns    |

| t <sub>6</sub>         | LSB SCK High to CS/LD High      |                                    |   | 5   |     |     | ns    |

LINEAR

### **TIMING CHARACTERISTICS** The • denotes specifications that apply over the full operating temperature range,

otherwise specifications are at  $T_A = 25^{\circ}C$ .

| SYMBOL          | PARAMETER                       | CONDITIONS                         |   | MIN | ТҮР | MAX | UNITS |

|-----------------|---------------------------------|------------------------------------|---|-----|-----|-----|-------|

| t <sub>7</sub>  | CS/LD Low to SCK Positive Edge  |                                    | • | 5   |     |     | ns    |

| t <sub>8</sub>  | CS/LD High to SCK Positive Edge |                                    | • | 5   |     |     | ns    |

| tg              | SRO Propagation Delay           | C <sub>LOAD</sub> = 10pF           | • |     |     | 26  | ns    |

| t <sub>10</sub> | CLR Pulse Width Low             |                                    | • | 60  |     |     | ns    |

| t <sub>11</sub> | LDAC Pulse Width Low            |                                    | • | 20  |     |     | ns    |

| t <sub>12</sub> | CLR Low to RFLAG Low            | C <sub>LOAD</sub> = 10pF (Note 13) | • |     |     | 70  | ns    |

| t <sub>13</sub> | CS/LD High to RFLAG high        | C <sub>LOAD</sub> = 10pF (Note 13) | • |     |     | 60  | ns    |

|                 | SCK Frequency                   | 50% Duty Cycle (Note 14)           | • |     |     | 25  | MHz   |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 3**: Calculation from feedback resistance and  $I_{OUT1}$  leakage current specifications; not production tested. In most applications, unipolar zero-scale error is dominated by contributions from the output amplifier.

Note 4: Input resistors measured from  $R_{\text{INX}}$  to  $R_{\text{COMX}}$ ; feedback resistors measured from  $R_{\text{COMX}}$  to REFX.

Note 5: DAC input resistance is independent of code.

**Note 6:** Parallel combination of the resistances from the specified pin to  $I_{OUT1X}$  and from the specified pin to  $I_{OUT2X}$ .

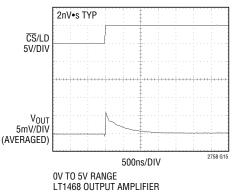

**Note 7:** Using LT1468 with  $C_{FEEDBACK} = 27$  pF. A ±0.0004% settling time of 1.8µs can be achieved by optimizing the time constant on an individual basis. See Application Note 120, *1ppm Settling Time Measurement for a Monolithic 18-Bit DAC.*

Note 8: Measured at the major carry transition, OV to 5V range. Output amplifier: LT1468;  $C_{FB}$  = 50pF.

Note 9: Full-scale transition; REF = 0V.

**Note 10:** Analog Crosstalk is defined as the AC voltage ratio  $V_{OUTB}/V_{REFA}$ , expressed in dB. REFB is grounded, and DAC B is set to 0V-5V span and zero-, mid- or full- scale code.  $V_{REFA}$  is a  $3V_{RMS}$ , 1kHz sine wave.

**Note 11:** REF =  $6V_{RMS}$  at 1kHz. 0V to 5V range. DAC code = FS. Output amplifier = LT1468.

**Note 12:** Calculation from  $V_n = \sqrt{4kTRB}$ , where  $k = 1.38E-23 \text{ J/}^{\circ}\text{K}$  (Boltzmann constant), R = resistance ( $\Omega$ ), T = temperature ( $^{\circ}\text{K}$ ), and B = bandwidth (Hz). 0V to 5V Range; zero-, mid-, or full-scale.

**Note 13:** Guaranteed by design; not production tested.

**Note 14:** When using SRO, maximum SCK frequency  $f_{MAX}$  is limited by SRO propagation delay  $t_9$  as follows:

$$f_{MAX} = \left(\frac{1}{2(t_9 + t_S)}\right)$$

, where  $t_S$  is the setup time of the receiving device.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{DD} = 5V$ ,  $V(R_{INX}) = 5V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{DD} = 5V$ ,  $V(R_{INX}) = 5V$ ,  $T_A = 25^{\circ}C$ , unless otherwise noted.

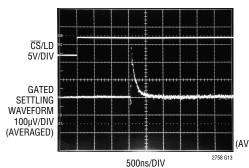

#### Settling Full-Scale Step

LT1468 AMP; C<sub>FEEDBACK</sub> = 20pF OV TO 10V STEP V<sub>REF</sub> = -10V; SPAN CODE = 0000 t<sub>SETTLE</sub> = 1.8µs to 0.0004% (18 BITS)

#### Mid-Scale Glitch ( $V_{DD} = 3V$ )

CFEEDBACK = 50pF RISING MAJOR CARRY TRANSITION. FALLING TRANSITION IS SIMILAR OR BETTER.

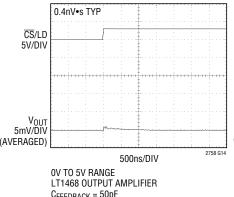

#### Mid-Scale Glitch ( $V_{DD} = 5V$ )

LT1468 OUTPUT AMPLIFIER CFEEDBACK = 50PF RISING MAJOR CARRY TRANSITION. FALLING TRANSITION IS SIMILAR OR BETTER.

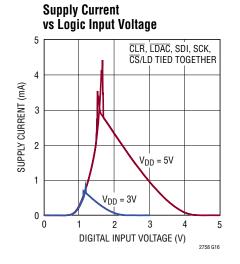

Supply Current vs Update Frequency

### PIN FUNCTIONS

**REFA (Pins 1, 2):** Feedback Resistor for the DAC A Reference Inverting Amplifier, and Reference Input for DAC A. The 20k feedback resistor is connected internally from REFA to  $R_{COMA}$ . For normal operation tie this pin to the output of the DAC A reference inverting amplifier (see Typical Application). Typically –5V; accepts up to ±15V. Pins 1 and 2 are internally shorted together.

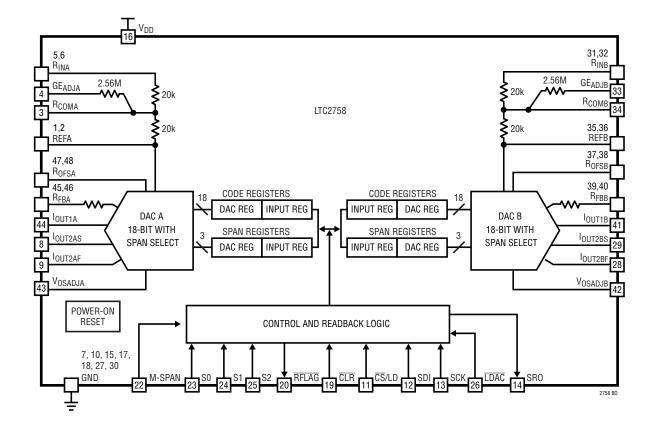

**R<sub>COMA</sub> (Pin 3):** Virtual Ground Point for the DAC A Reference Amplifier Inverting Resistors. The 20k reference inverting resistors are connected internally from R<sub>INA</sub> to R<sub>COMA</sub> and from R<sub>COMA</sub> to REFA, respectively (see Block Diagram). For normal operation tie R<sub>COMA</sub> to the negative input of the external reference inverting amplifier (see Typical Application).

**GE<sub>ADJA</sub> (Pin 4):** Gain Adjust Pin for DAC A. This control pin can be used to null gain error or to compensate for reference errors. The gain change expressed in LSB is the same for any output range. See *System Offset and Gain Adjustments* in the Operation section. Tie to ground if not used.

**R<sub>INA</sub> (Pins 5, 6):** Input Resistor for the DAC A External Reference Inverting Amplifier. The 20k input resistor is connected internally from  $R_{INA}$  to  $R_{COMA}$ . For normal operation tie  $R_{INA}$  to the external positive reference voltage (see Typical Application). Either or both of these precisionmatched resistor sets (each set comprising  $R_{INX}$ ,  $R_{COMX}$  and REFX) may be used to invert positive references to provide the negative voltages needed by the DACs. Typically 5V; accepts up to ±15V. Pins 5 and 6 are internally shorted together.

GND (Pins 7, 10, 15, 17, 18, 27, 30): Ground; tie to ground.

**I**<sub>OUT2AS</sub>, **I**<sub>OUT2AF</sub> (**Pins 8, 9**): DAC A Current Output Complement Sense and Force Pins. Tie to ground via a clean, low-impedance path. These pins may be used with a precision ground buffer amp as a Kelvin sensing pair (see the Applications Information section).

**CS/LD (Pin 11):** Synchronous Chip Select and Load Input Pin.

**SDI (Pin 12):** Serial Data Input. Data is clocked in on the rising edge of the serial clock (SCK) when  $\overline{CS}/LD$  is low.

SCK (Pin 13): Serial Clock Input.

**SRO (Pin 14):** Serial Readback Output. Data is clocked out on the falling edge of SCK. Readback data begins clocking out after the last address bit A0 is clocked in. SRO is an active output only when the chip is selected (i.e., when CS/LD is low). Otherwise SRO presents a high-impedance output in order to allow other parts to control the bus.

**V**<sub>DD</sub> (**Pin 16**): Positive Supply Input;  $2.7V \le V_{DD} \le 5.5V$ . Bypass with a  $0.1\mu$ F low-ESR ceramic capacitor to ground.

**CLR (Pin 19):** Asynchronous Clear Input. When this pin is low, all DAC registers (both code and span) are cleared to zero. All DAC outputs are cleared to zero volts.

**RFLAG** (Pin 20): Reset Flag Output. An active low output is asserted when there is a power-on reset or a clear event. Returns high when an Update command is executed.

DNC (Pin 21): Do Not Connect.

**M-SPAN (Pin 22):** Manual Span Control Pin. M-SPAN is used in conjunction with pins S2, S1 and S0 (Pins 25, 24 and 23) to configure all DACs for operation in a single, fixed output range.

To configure the part for manual-span use, tie M-SPAN directly to  $V_{DD}$ . The DAC output range is then set via hardware pin strapping of pins S2, S1 and S0 (rather than through the SPI port); and Write and Update commands have no effect on the active output span.

To configure the part for SoftSpan use, tie M-SPAN directly to GND. The output ranges are then individually controllable through the SPI port; and pins S2, S1 and S0 have no effect.

See *Manual Span Configuration* in the Operation section. M-SPAN must be connected either directly to GND (SoftSpan configuration) or to  $V_{DD}$  (manual-span configuration).

**S0 (Pin 23):** Span Bit 0 Input. In Manual Span mode (M-SPAN tied to  $V_{DD}$ ), Pins S0, S1 and S2 are pin-strapped to select a single fixed output range for all DACs. These pins should be tied to either GND or  $V_{DD}$  even if they are unused.

**S1 (Pin 24):** Span Bit 1 Input. In Manual Span mode (M-SPAN tied to  $V_{DD}$ ), Pins S0, S1 and S2 are pin-strapped to select a single fixed output range for all DACs. These pins should be tied to either GND or  $V_{DD}$  even if they are unused.

### PIN FUNCTIONS

**S2 (Pin 25):** Span Bit 2 Input. In Manual Span mode (M-SPAN tied to  $V_{DD}$ ), Pins S0, S1 and S2 are pin-strapped to select a single fixed output range for all DACs. These pins should be tied to either GND or  $V_{DD}$  even if they are unused.

**LDAC** (Pin 26): Asynchronous DAC Load Input. When LDAC is a logic low, all DACs are updated ( $\overline{CS}$ /LD must be high).

**I**<sub>OUT2BF</sub>, **I**<sub>OUT2BS</sub> (**Pins 28, 29**): DAC B Current Output Complement Force and Sense Pins. Tie to ground via a clean, low-impedance path. These pins may be used with a precision ground buffer amp as a Kelvin sensing pair (see the Applications Information section).

**R<sub>INB</sub> (Pins 31, 32):** Input Resistor for the DAC B External Reference Inverting Amplifier. The 20k input resistor is connected internally from  $R_{INB}$  to  $R_{COMB}$ . For normal operation tie  $R_{INB}$  to the external positive reference voltage (see Typical Application). Either or both of these precisionmatched resistor sets (each set comprising  $R_{INX}$ ,  $R_{COMX}$ and REFX) may be used to invert positive references to provide the negative voltages needed by the DACs. Typically 5V; accepts up to ±15V. Pins 31 and 32 are internally shorted together.

**GE**<sub>ADJB</sub> (**Pin 33**): Gain Adjust Pin for DAC B. This control pin can be used to null gain error or to compensate for reference errors. The gain change expressed in LSB is the same for any output range. See *System Offset and Gain Adjustments* in the Operation section. Tie to ground if not used.

**R**<sub>COMB</sub> (**Pin 34**): Virtual Ground Point for the DAC B Reference Amplifier Inverting Resistors. The 20k reference inverting resistors are connected internally from RINB to R<sub>COMB</sub> and from R<sub>COMB</sub> to REFB, respectively (see Block Diagram). For normal operation tie R<sub>COMB</sub> to the negative input of the external reference inverting amplifier (see Typical Application).

**REFB (Pins 35, 36):** Feedback Resistor for the DAC B Reference Inverting Amplifier, and Reference Input for DAC B. The 20k feedback resistor is connected internally from REFB to  $R_{COMB}$ . For normal operation tie this pin to the output of the DAC B reference inverting amplifier (see Typical Application). Typically –5V; accepts up to ±15V. Pins 35 and 36 are internally shorted together. **R<sub>OFSB</sub> (Pins 37, 38):** Bipolar Offset Resistor for DAC B. These pins provide the translation of the output voltage range for bipolar spans. Accepts up to  $\pm 15V$ ; for normal operation tie to the positive reference voltage at R<sub>INB</sub> (Pins 31, 32). Pins 37 and 38 are internally shorted together.

$R_{FBB}$  (Pins 39, 40): DAC B Feedback Resistor. For normal operation tie to the output of the I/V converter amplifier for DAC B (see Typical Application). The DAC output current from  $I_{OUT1B}$  flows through the feedback resistor to the R<sub>FBB</sub> pins. Pins 39 and 40 are internally shorted together.

**I**<sub>OUT1B</sub> (**Pin 41**): DAC B Current Output. This pin is a virtual ground when the DAC is operating and should reside at OV. For normal operation tie to the negative input of the I/V converter amplifier for DAC B (see Typical Application).

**V<sub>OSADJB</sub> (Pin 42):** DAC B Offset Adjust Pin. This voltagecontrol pin can be used to null unipolar offset or bipolar zero error. The offset change expressed in LSB is the same for any output range. See *System Offset and Gain Adjustments* in the Operation section. Tie to ground if not used.

**V<sub>OSADJA</sub> (Pin 43):** DAC A Offset Adjust Pin. This voltagecontrol pin can be used to null unipolar offset or bipolar zero error. The offset change expressed in LSB is the same for any output range. See *System Offset and Gain Adjustments* in the Operation section. Tie to ground if not used.

**I**<sub>OUT1A</sub> (**Pin 44**): DAC A Current Output. This pin is a virtual ground when the DAC is operating and should reside at OV. For normal operation tie to the negative input of the I/V converter amplifier for DAC A (see Typical Application).

$R_{FBA}$  (Pins 45, 46): DAC A Feedback Resistor. For normal operation tie to the output of the I/V converter amplifier for DAC A (see Typical Application). The DAC output current from  $I_{OUT1A}$  flows through the feedback resistor to the R<sub>FBA</sub> pins. Pins 45 and 46 are internally shorted together.

$R_{0FSA}$  (Pins 47, 48): Bipolar Offset Resistor for DAC A. This pin provides the translation of the output voltage range for bipolar spans. Accepts up to ±15V; for normal operation tie to the positive reference voltage at  $R_{INA}$ (Pins 5, 6). Pins 47 and 48 are internally shorted together.

## **BLOCK DIAGRAM**

### TIMING DIAGRAM

#### **Output Ranges**

The LTC2758 is a dual, current-output, serial-input precision multiplying DAC with selectable output ranges. Ranges can either be programmed in software for maximum flexibility (each of the DACs can be programmed to any one of six output ranges) or hardwired through pin-strapping. Two unipolar ranges are available (0V to 5V and 0V to 10V), and four bipolar ranges ( $\pm 2.5V$ ,  $\pm 5V$ ,  $\pm 10V$  and -2.5V to 7.5V). These ranges are obtained when an external precision 5V reference is used. The output ranges for other reference voltages are easy to calculate by observing that each range is a multiple of the external reference voltage. The ranges can then be expressed: 0 to 1×, 0 to 2×,  $\pm 0.5$ ×,  $\pm 1$ ×,  $\pm 2$ ×, and -0.5× to 1.5×.

#### Manual Span Configuration

Multiple output ranges are not needed in some applications. To configure the LTC2758 to operate in a single span without additional operational overhead, tie the M-SPAN pin directly to  $V_{DD}$ . The active output range for all DACs is then set via hardware pin strapping of pins S2, S1 and S0 (rather than through the SPI port); and Write and Update commands have no effect on the active output span. See Figure 1 and Table 3.

Tie the M-SPAN pin to ground for normal SoftSpan operation.

#### **Input and DAC Registers**

The LTC2758 has 5 internal registers for each DAC, a total of 10 registers (see Block Diagram). Each DAC channel has two sets of double-buffered registers, one set for the code data, and one for the output range of the DAC, plus one readback register. Double buffering provides the

Figure 1. Using M-SPAN to Configure the LTC2758 for Single-Span Operation (±10V Range Shown)

capability to simultaneously update the span (output range) and code, which allows smooth voltage transitions when changing output ranges. It also permits the simultaneous updating of multiple DACs.

Each set of double-buffered registers comprises an Input register and a DAC register.

Input register: The Write operation shifts data from the SDI pin into a chosen Input register. The Input registers are holding buffers; Write operations do not affect the DAC outputs.

DAC register: The Update operation copies the contents of an Input register to its associated DAC register. The contents of a DAC register directly updates the associated DAC output voltage or output range.

Note that updates always include both Code and Span register sets; but the values held in the DAC registers will only change if the associated Input register values have previously been altered via a Write operation.

### Serial Interface

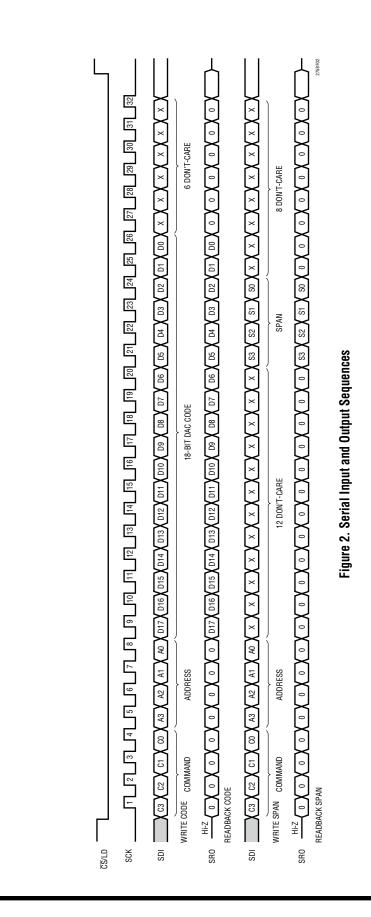

When the  $\overline{\text{CS}}/\text{LD}$  pin is taken low, the data on the SDI pin is loaded into the shift register on the rising edge of the clock (SCK pin). The loading sequence required for the LTC2758 is one byte consisting of a 4-bit command word (C3 C2 C1 C0) and a 4-bit address word (A3 A2 A1 A0), then three bytes (24 bits) of data.

When writing a code, the code data is left (MSB) justified; so that the 24-bit data field consists of 18 code bits followed by 6 don't-care bits.

When writing an output range, the span data should occupy the last 4 bits of the second data byte, ordered S3 through S0. Figure 2 shows the SDI input word syntax for writing.

When  $\overline{\text{CS}}/\text{LD}$  is low, the SRO pin (Serial Readback Output) is an active output. The readback data begins after the command (C3-C0) and address (A3-A0) words have been shifted in to SDI. SRO outputs a logic low from the falling edge of  $\overline{\text{CS}}/\text{LD}$  until the Readback data begins.

When  $\overline{\text{CS}}$ /LD is high, the SRO pin presents a high impedance (three-state) output.

$\overline{\text{LDAC}}$  is an asynchronous update pin. When  $\overline{\text{LDAC}}$  is taken low, all DACs are updated with code and span data (data in the Input buffers is copied into the DAC buffers).  $\overline{\text{CS}/\text{LD}}$  must be high during this operation; otherwise  $\overline{\text{LDAC}}$  is locked out and will have no effect. The use of  $\overline{\text{LDAC}}$  is functionally identical to the "Update All DACs" serial input command.

The codes for the command (C3-C0) are defined in Table 1; Table 2 defines the codes for the address (A3-A0).

### Readback

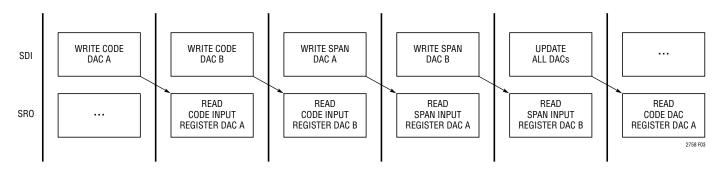

In addition to the Code and Span register sets, each DAC has one Readback register associated with it. Every instruction cycle, the contents of one of the on-chip registers is copied into a Readback register and serially shifted out through the SRO pin.

Readback data always appears in the 24-bit data field, starting on the falling SCK edge immediately after the last address bit is shifted in on SDI. When reading a code, code

data occupies the first 18 bits of the 24-bit field; and the span bits are the last four bits of the second data byte when checking the output range. In both cases, all other bits in the 24-bit data field are filled by zeros. Figure 2 shows the input and readback sequences.

The data outputted by SRO is always in the same position and sequence as the input data. Note, however, that this means that the SRO data shifts out one-half clock cycle *earlier* than the corresponding bit shifting in on SDI. For example, code bit D9, which is shifted in to SDI on the rising edge of SCK clock 17, is clocked out of SRO on the *falling* edge of clock 16. This allows D9 to be clocked to an external microprocessor on the rising edge of clock 17.

For Read commands, the requested data is shifted out of SRO in the 3-byte (24-bit) data field immediately after the command/address byte. There is no instruction-cycle latency for Read commands; the data shifts out in the same instruction cycle in which it was requested.

For non-read (i.e., Write and/or Update) commands, SRO automatically shifts out the contents of the buffer that was acted upon in the preceding command. This "rolling readback" default mode of operation can dramatically reduce the number of instruction cycles needed, since most commands can be verified during subsequent commands with no additional overhead. A conceptual flow diagram is shown in Figure 3. Table 1 shows, for each antecedent command, which register ('readback pointer') will be copied into the Readback register and outputted from SRO during the following instruction cycle.

### Span Readback in Manual Span Configuration

If a Span DAC register is chosen for readback, SRO responds by outputting the actual output span; this is true whether the LTC2758 is configured for SoftSpan (M-SPAN tied to GND) or manual span (M-SPAN tied to V<sub>DD</sub>).

In SoftSpan configuration, SRO outputs the span code from the Span DAC register (programmed through the SPI port). In manual span configuration, the active output range is controlled by pins S2, S1 and S0, so SRO outputs the logic values of these pins. The span code bits S2, S1 and S0 always appear in the same order and positions in the SRO output sequence; see Figure 2.

**Table 1. Command Codes**

|    | CO | DE |    |                                                | READBACK POINTER-                 | READBACK POINTER-                |

|----|----|----|----|------------------------------------------------|-----------------------------------|----------------------------------|

| C3 | C2 | C1 | CO | COMMAND                                        | CURRENT INPUT WORD W <sub>0</sub> | NEXT INPUT WORD W <sub>+1</sub>  |

| 0  | 0  | 1  | 0  | Write Span DAC <i>n</i>                        | Set by Previous Command           | Input Span Register DAC <i>n</i> |

| 0  | 0  | 1  | 1  | Write Code DAC n                               | Set by Previous Command           | Input Code Register DAC n        |

| 0  | 1  | 0  | 0  | Update DAC <i>n</i>                            | Set by Previous Command           | DAC Span Register DAC n          |

| 0  | 1  | 0  | 1  | Update All DACs                                | Set by Previous Command           | DAC Code Register DAC n          |

| 0  | 1  | 1  | 0  | Write Span DAC <i>n</i><br>Update DAC <i>n</i> | Set by Previous Command           | DAC Span Register DAC <i>n</i>   |

| 0  | 1  | 1  | 1  | Write Code DAC <i>n</i><br>Update DAC <i>n</i> | Set by Previous Command           | DAC Code Register DAC n          |

| 1  | 0  | 0  | 0  | Write Span DAC <i>n</i><br>Update All DACs     | Set by Previous Command           | DAC Span Register DAC <i>n</i>   |

| 1  | 0  | 0  | 1  | Write Code DAC <i>n</i><br>Update All DACs     | Set by Previous Command           | DAC Code Register DAC <i>n</i>   |

| 1  | 0  | 1  | 0  | Read Input Span Register DAC n                 | Input Span Re                     | gister DAC <i>n</i>              |

| 1  | 0  | 1  | 1  | Read Input Code Register DAC n                 | Input Code Re                     | gister DAC <i>n</i>              |

| 1  | 1  | 0  | 0  | Read DAC Span Register DAC n                   | DAC Span Reg                      | gister DAC <i>n</i>              |

| 1  | 1  | 0  | 1  | Read DAC Code Register DAC n                   | DAC Code Reg                      | gister DAC <i>n</i>              |

| 1  | 1  | 1  | 1  | No Operation                                   | Set by Previous Command           | DAC Code Register DAC n          |

|    | -  | _  |    | System Clear                                   | -                                 | DAC Span Register DAC A          |

|    | -  | _  |    | Initial Power-Up or Power Interrupt            | _                                 | DAC Span Register DAC A          |

Codes not shown are reserved-do not use

#### Table 2. Address Codes

| A3 | A2 | A1 | AO | n                 |

|----|----|----|----|-------------------|

| 0  | 0  | 0  | ×  | DAC A             |

| 0  | 0  | 1  | ×  | DAC B             |

| 1  | 1  | 1  | ×  | All DACs (Note 1) |

Codes not shown are reserved-do not use.  $\times$  = Don't Care. **Note 1.** If readback is taken using the All DACs address, the LTC2758 defaults to DAC A.

#### Table 3. Span Codes

| Table      |            |    |    |                       |  |  |  |  |  |  |

|------------|------------|----|----|-----------------------|--|--|--|--|--|--|

| <b>S</b> 3 | <b>S</b> 2 | S1 | SO | SPAN                  |  |  |  |  |  |  |

| ×          | 0          | 0  | 0  | Unipolar OV to 5V     |  |  |  |  |  |  |

| ×          | 0          | 0  | 1  | Unipolar OV to 10V    |  |  |  |  |  |  |

| ×          | 0          | 1  | 0  | Bipolar –5V to 5V     |  |  |  |  |  |  |

| ×          | 0          | 1  | 1  | Bipolar –10V to 10V   |  |  |  |  |  |  |

| ×          | 1          | 0  | 0  | Bipolar –2.5V to 2.5V |  |  |  |  |  |  |

| ×          | 1          | 0  | 1  | Bipolar –2.5V to 7.5V |  |  |  |  |  |  |

Codes not shown are reserved-do not use.  $\times$  = Don't Care.

### Examples

- Load DAC A with 0V to 10V range, output at zero volts; and DAC B with ±10V range, output at zero volts. Note the DAC outputs should change at the same time.

- a) CS/LD↓. Clock SDI: 00101111 0000000 00000011 0000000

- b) CS/LD↑

Span Input register- Range of DACs set to bipolar ±10V.

- c) CS/LD↓. Clock SDI: 00100000 00000000 00000001 00000000

- d) CS/LD↑ Span Input register- Range of DAC A set to unipolar 0V to 10V.

- e) CS/LD↓. Clock SDI: 00111111 10000000 00000000 00XXXXXX

- f) CS/LD↑ Code Input register- Code of all DACs set to mid-scale.

- g) CS/LD↓. Clock SDI: 00110000 0000000 0000000 00XXXXXX

- h) CS/LD↑ Code Input register- Code of DAC A set to zero.

- j) CS/LD↑

Update all DACs for both Code and Range.

- k) Alternatively steps i and j could be replaced with  $\overrightarrow{\text{LDAC}}$   $\square\Gamma.$

- Load DAC B with ±2.5V range with its output at zero volts. Use readback to check Input register contents before updating the DAC output (i.e., before copying Input register contents into DAC registers). Note that after power-on, the code in Input registers is zero.

- a) CS/LD↓. Clock SDI: 00110010 1000000 0000000 00XXXXXX

- b) CS/LD↑ Code Input register- DAC B set to mid-scale.

- c) CS/LD↓. Clock SDI: 00100010 00000000 00000100 00000000 Data out on SRO: 10000000 00000000 00000000 Verifies Code Input register- DAC B set to mid-scale.

- d) CS/LD↑

Span Input register- Range of DAC B set to Bipolar ±2.5V range.

- g) CS/LD↑ Update DAC B for both Code and Range

- h) Alternatively steps f and g could be replaced with  $\overrightarrow{\text{LDAC}}$   $\square \Gamma.$

#### System Offset and Reference Adjustments

Many systems require compensation for overall system offset. This may be an order of magnitude or more greater than the offset of the LTC2758, which is so low as to be dominated by external output amplifier errors even when using the most precise op amps.

The offset adjust pins  $V_{OSADJX}$  can be used to null unipolar offset or bipolar zero error. The offset change expressed in LSB is the same for any output range:

A 5V control voltage applied to  $V_{OSADJX}$  produces  $\Delta V_{OS} = -2048$  LSB in any output range, assuming a 5V reference voltage at  $R_{INX}$ .

In voltage terms, the offset delta is attenuated by a factor of 32, 64 or 128, depending on the output range. (These functions hold regardless of reference voltage.)

| $\Delta V_{OS} = -(^{1}/_{128})V_{OSADJX}$ | [OV to 5V, ±2.5V spans]                  |

|--------------------------------------------|------------------------------------------|

| $\Delta V_{OS} = -(^{1}/_{64})V_{OSADJX}$  | [0V to 10V, ±5V, –2.5V to<br>7.5V spans] |

| $\Delta V_{OS} = -(1/32)V_{OSADJX}$        | [±10V span]                              |

The gain error adjust pins  $GE_{ADJX}$  can be used to null gain error or to compensate for reference errors. The gain error change expressed in LSB is the same for any output range:

$$\Delta GE = \frac{V(GE_{ADJX})}{V(R_{INX})} \bullet 2048$$

The gain-error delta is non-inverting for positive reference voltages.

Note that this pin compensates the gain by altering the inverted reference voltage V(REFX). In voltage terms, the V(REFX) delta is inverted and attenuated by a factor of 128.

### $\Delta V(\text{REFX}) = -(^{1}/_{128})\text{GE}_{\text{ADJX}}$

The nominal input range of these pins is  $\pm 5V$ ; other voltages of up to  $\pm 15V$  may be used if needed. However, do

not use voltages divided down from power supplies; reference-quality, low-noise inputs are required to maintain the best DAC performance.

The V<sub>OSADJX</sub> pins have an input impedance of 1.28M $\Omega$ . These pins should be driven with a Thevenin-equivalent impedance of 10k or less to preserve the settling performance of the LTC2758. They should be shorted to GND if not used.

The  $GE_{ADJX}$  pins have an input impedance of 2.56M $\Omega$ , and are intended for use with fixed reference voltages only. They should be shorted to GND if not used.

### **Power-On Reset and Clear**

When power is first applied to the LTC2758, all DACs power-up in unipolar 5V mode (S3 S2 S1 S0 = 0000). All internal DAC registers are reset to 0 and the DAC outputs initialize to zero volts.

If the part is configured for manual span operation, all DACs will be set into the pin-strapped range at the first Update command. This allows the user to simultaneously update span and code for a smooth voltage transition into the chosen output range.

When the  $\overline{\text{CLR}}$  pin is taken low, a system clear results. The DAC buffers are reset to 0 and the DAC outputs are all reset to zero volts. The Input buffers are left intact, so that any subsequent Update command (including the use of  $\overline{\text{LDAC}}$ ) restores the addressed DACs to their respective previous states.

If  $\overline{\text{CLR}}$  is asserted during an instruction, i.e., when  $\overline{\text{CS}}/\text{LD}$  is low, the instruction is aborted. Integrity of the relevant Input buffers is not guaranteed under these conditions, therefore the contents should be checked using readback or replaced.

The  $\overline{\text{RFLAG}}$  pin is used as a flag to notify the system of a loss of data integrity. The  $\overline{\text{RFLAG}}$  output is asserted low at power-up, system clear, or if the supply V<sub>DD</sub> dips below approximately 2V; and stays asserted until any valid Update command is executed.

2758fb

**OPERATION**

#### **Op Amp Selection**

Because of the extremely high accuracy of the 18-bit LTC2758, careful thought should be given to op amp selection in order to achieve the exceptional performance of which the part is capable. Fortunately, the sensitivity of INL and DNL to op amp offset has been greatly reduced compared to previous generations of multiplying DACs.

Tables 4 and 5 contain equations for evaluating the effects of op amp parameters on the LTC2758's accuracy when programmed in a unipolar or bipolar output range. These are the changes the op amp can cause to the INL, DNL, unipolar offset, unipolar gain error, bipolar zero and bipolar gain error.

| OUTPUT RANGE  | A1  | A2 | A3   | A4  | A5  |

|---------------|-----|----|------|-----|-----|

| 5V            | 1.1 | 2  | 1    |     | 1   |

| 10V           | 2.2 | 3  | 0.5  |     | 1.5 |

| ±5V           | 2   | 2  | 1    | 1   | 1.5 |

| ±10V          | 4   | 4  | 0.83 | 1   | 2.5 |

| ±2.5V         | 1   | 1  | 1.4  | 1   | 1   |

| -2.5V to 7.5V | 1.9 | 3  | 0.7  | 0.5 | 1.5 |

#### Table 4. Coefficients for the Equations of Table 5

Table 6 contains a partial list of LTC precision op amps recommended for use with the LTC2758. The easy-to-use design equations simplify the selection of op amps to meet the system's specified error budget. Select the amplifier from Table 6 and insert the specified op amp parameters in Table 5. Add up all the errors for each category to determine the effect the op amp has on the accuracy of the part. Arithmetic summation gives an (unlikely) worst-case effect. A root-sum-square (RMS) summation produces a more realistic estimate.

| Table 5. Easy-to-Use Equations Determine Op Amp Effects on DAC Accuracy in All Output Ranges (Circuit of Page 1). Subscript 1 |

|-------------------------------------------------------------------------------------------------------------------------------|

| Refers to Output Amp, Subscript 2 Refers to Reference Inverting Amp.                                                          |

| OP AMP                   | INL (LSB)                                                      | DNL (LSB)                                                        | UNIPOLAR<br>OFFSET (LSB)                                                  | BIPOLAR ZERO<br>Error (LSB)                                               | UNIPOLAR GAIN<br>Error (LSB)                                    | BIPOLAR GAIN<br>Error (LSB)                                     |

|--------------------------|----------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| V <sub>OS1</sub> (mV)    | $V_{OS1} \bullet 12.1 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $V_{0S1} \bullet 3.1 \bullet \left(\frac{5V}{V_{REF}}\right)$    | $A3 \bullet V_{OS1} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$ | A3•V <sub>0S1</sub> •78.6• $\left(\frac{5V}{V_{REF}}\right)$              | $V_{0S1} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $V_{0S1} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$  |

| I <sub>B1</sub> (nA)     | $I_{B1}\bullet 0.0012 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.00032 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B1} \bullet 0.524 \bullet \left(\frac{5V}{V_{REF}}\right)$            | $I_{B1} \bullet 0.524 \bullet \left(\frac{5V}{V_{REF}}\right)$            | $I_{B1}\bullet 0.0072 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $I_{B1} \bullet 0.0072 \bullet \left(\frac{5V}{V_{REF}}\right)$ |

| A <sub>VOL1</sub> (V/mV) | $A1 \bullet \left(\frac{66}{A_{VOL1}}\right)$                  | A2• $\left(\frac{6}{A_{VOL1}}\right)$                            | 0                                                                         | 0                                                                         | $A5 \bullet \left(\frac{524}{A_{VOL1}}\right)$                  | $A5 \bullet \left(\frac{524}{A_{VOL1}}\right)$                  |

| V <sub>0S2</sub> (mV)    | 0                                                              | 0                                                                | 0                                                                         | $A4 \bullet V_{0S2} \bullet 52.4 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $V_{OS2} \bullet 104.8 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $V_{OS2} \bullet 104.8 \bullet \left(\frac{5V}{V_{REF}}\right)$ |

| I <sub>B2</sub> (nA)     | 0                                                              | 0                                                                | 0                                                                         | $A4 \bullet I_{B2} \bullet 0.524 \bullet \left(\frac{5V}{V_{REF}}\right)$ | $I_{B2} \bullet 1.048 \bullet \left(\frac{5V}{V_{REF}}\right)$  | $I_{B2} \bullet 1.048 \bullet \left(\frac{5V}{V_{REF}}\right)$  |

| A <sub>VOL2</sub> (V/mV) | 0                                                              | 0                                                                | 0                                                                         | $A4 \cdot \left(\frac{262}{A_{VOL2}}\right)$                              | $\left(\frac{524}{A_{VOL2}}\right)$                             | $\left(\frac{524}{A_{VOL2}}\right)$                             |

| Table 6 Partial List of LTC Precision Am     | plifiers Recommended for Use with the LTC2758 with Relevant Spec  | ifications |

|----------------------------------------------|-------------------------------------------------------------------|------------|

| Table V. Faillai List VI LIV Ficulatuli Alli | princis neconiniciaca for Ose with the LIGZ/JO with necevant spec | incations  |

|           | AMPLIFIER SPECIFICATIONS |                      |                          |                            |                            |                      |                                  |                                 |                            |

|-----------|--------------------------|----------------------|--------------------------|----------------------------|----------------------------|----------------------|----------------------------------|---------------------------------|----------------------------|

| AMPLIFIER | V <sub>OS</sub><br>µV    | I <sub>B</sub><br>nA | A <sub>VOL</sub><br>V/mV | VOLTAGE<br>NOISE<br>nV/√Hz | CURRENT<br>NOISE<br>pA/√Hz | SLEW<br>RATE<br>V/µs | GAIN BANDWIDTH<br>Product<br>MHz | tsettling<br>with LTC2758<br>μs | POWER<br>DISSIPATION<br>mW |

| LTC1150   | 10                       | 0.05                 | 5600                     | 90                         | 0.0018                     | 3                    | 2.5                              | 10ms                            | 24                         |

| LT1001    | 25                       | 2                    | 800                      | 10                         | 0.12                       | 0.25                 | 0.8                              | 120                             | 46                         |

| LT1012    | 25                       | 0.1                  | 2000                     | 14                         | 0.02                       | 0.2                  | 1                                | 120                             | 11.4                       |

| LT1097    | 50                       | 0.35                 | 2500                     | 14                         | 0.008                      | 0.2                  | 0.7                              | 120                             | 11                         |

| LT1468    | 75                       | 10                   | 5000                     | 5                          | 0.6                        | 22                   | 90                               | 2.1                             | 117                        |

Op amp offset contributes mostly to DAC output offset and gain error, and has minimal effect on INL and DNL. For example, consider the LTC2758 in unipolar 5V output range. (Note that for this example, the LSB size is 19 $\mu$ V.) An op amp offset of 35 $\mu$ V will cause 1.8LSB of output offset, and 1.8LSB of gain error; but 0.4LSB of INL, and just 0.1LSB of DNL.

While not directly addressed by the simple equations in Tables 4 and 5, temperature effects can be handled just as easily for unipolar and bipolar applications. First, consult an op amp's data sheet to find the worst-case  $V_{OS}$  and  $I_B$  over temperature. Then, plug these numbers in the  $V_{OS}$  and  $I_B$  equations from Table 5 and calculate the temperature-induced effects.

For applications where fast settling time is important, Application Note 120, *1ppm Settling Time Measurement for a Monolithic 18-Bit DAC*, offers a thorough discussion of 18-bit DAC settling time and op amp selection.

#### Recommendations

For DC or low-frequency applications, the LTC1150 is the simplest 18-bit accurate output amplifier. An auto-zero amp, its exceptionally low offset ( $10\mu V max$ ) and offset drift ( $0.01\mu V/^{\circ}C$ ) make nulling unnecessary. For swings above 8V, use an LT1010 buffer to boost the load current capability. The settling of auto-zero amps is a special case; see Application Note 120, *1ppm Settling Time Measurement for a Monolithic 18-Bit DAC*, Appendix E, for details.

The LT1012 and LT1001 are good intermediate output-amp solutions that achieve moderate speed and good accuracy. They are also excellent choices for the reference inverting amplifier in fixed-reference applications.

For high speed applications, the LTC1468 settles in 2.1 $\mu$ s. Note that the 75 $\mu$ V max offset will degrade the INL at the DAC output by up to 0.9LSB. For high-speed applications demanding higher precision, the amplifier offset can be nulled with a digital potentiometer.

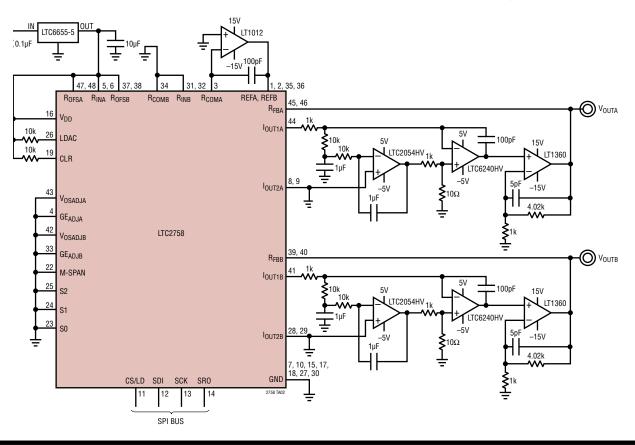

The Typical Application on the last page shows a composite output amplifier that achieves fast settling ( $8\mu$ s) and very low offset ( $3\mu$ V max) without offset nulling. This circuit offers high open-loop gain (1000V/mV min), low input bias current (0.15nA max), fast slew rate (25V/µs min),

and a high gain-bandwidth product (30MHz typ). The high speed path consists of an LTC6240HV, which is an 18MHz ultralow bias current amplifier, followed by an LT1360, a 50MHz fast-slewing amplifier which provides additional gain and the ability to swing to  $\pm$ 10V at the output. Compensation is taken from the output of the LTC6240HV, allowing the use of a much larger compensation capacitor than if taken after the gain-of-five stage. An LTC2054HV auto-zero amplifier senses the voltage at I<sub>OUT1</sub> and drives the non-inverting input of the LTC6240HV to eliminate the offset of the high speed path. The 100:1 attenuator and input filter reduce the low frequency noise in this stage while maintaining low DC offset.

#### **Precision Voltage Reference Considerations**

Much in the same way selecting an operational amplifier for use with the LTC2758 is critical to the performance of the system, selecting a precision voltage reference also requires due diligence. The output voltage of the LTC2758 is directly affected by the voltage reference; thus, any voltage reference error will appear as a DAC output voltage error.

There are three primary error sources to consider when selecting a precision voltage reference for 18-bit applications: output voltage initial tolerance, output voltage temperature coefficient and output voltage noise.

Initial reference output voltage tolerance, if uncorrected, generates a full-scale error term. Choosing a reference with low output voltage initial tolerance, like the LT1236 ( $\pm 0.05\%$ ), minimizes the gain error caused by the reference; however, a calibration sequence that corrects for system zero- and full-scale error is always recommended.

A reference's output voltage temperature coefficient affects not only the full-scale error, but can also affect the circuit's INL and DNL performance. If a reference is chosen with a loose output voltage temperature coefficient, then the DAC output voltage along its transfer characteristic will be very dependent on ambient conditions. Minimizing the error due to reference temperature coefficient can be achieved by choosing a precision reference with a low output voltage temperature coefficient and/or tightly controlling the ambient temperature of the circuit to minimize temperature gradients.

Table 7. Partial List of LTC Precision References Recommended

for Use with the LTC2758 with Relevant Specifications

| REFERENCE                  | INITIAL<br>Tolerance | TEMPERATURE<br>DRIFT | 0.1Hz to 10Hz<br>NOISE |

|----------------------------|----------------------|----------------------|------------------------|

| LT1019A-5,<br>LT1019A-10   | ±0.05% max           | 5ppm/°C max          | 12μV <sub>P-P</sub>    |

| LT1236A-5,<br>LT1236A-10   | ±0.05% max           | 5ppm/°C max          | 3μV <sub>P-P</sub>     |

| LT1460A-5,<br>LT1460A-10   | ±0.075% max          | 10ppm/°C max         | 20μV <sub>P-P</sub>    |

| LT1790A-2.5                | ±0.05% max           | 10ppm/°C max         | 12μV <sub>P-P</sub>    |

| LTC6652A-5                 | ±0.05% max           | 5ppm/°C max          | 2.8ppm <sub>P-P</sub>  |

| LTC6655A-2.5<br>LTC6655A-5 | ±0.025% max          | 2ppm/°C max          | 0.25ppm <sub>P-P</sub> |

As precision DAC applications move to 18-bit performance, reference output voltage noise may contribute a dominant share of the system's noise floor. This in turn can degrade system dynamic range and signal-to-noise ratio. Care should be exercised in selecting a voltage reference with as low an output noise voltage as practical for the system resolution desired. Precision voltage references like the LT1236 or LTC6655 produce low output noise in the 0.1Hz to 10Hz region, well below the 18-bit LSB level in 5V or 10V full-scale systems. However, as the circuit bandwidths increase, filtering the output of the reference may be required to minimize output noise.

#### Grounding

As with any high-resolution converter, clean grounding is important. A low-impedance analog ground plane is necessary, as are star grounding techniques. Keep the board layer used for star ground continuous to minimize ground resistances; that is, use the star-ground concept without using separate star traces. The  $I_{OUT2}$  pins are of particular concern; INL will be degraded by the codedependent currents carried by the  $I_{OUT2XF}$  and  $I_{OUT2XS}$ pins if voltage drops to ground are allowed to develop. The best strategy here is to tie the pins to the star ground plane by multiple vias located directly underneath the part. Alternatively, the pins may be routed to the star ground point if necessary; join the force and sense pins together at the part and route one trace for each channel of no more than 30 squares of 1oz copper.

In the rare case in which neither of these alternatives is practicable, a force/sense amplifier should be used as a ground buffer (see Figure 4). Note, however, that the voltage offset of the ground buffer amp directly contributes to the effects on accuracy specified in Table 5 under ' $V_{OS1}$ '. The combined effects of the offsets can be calculated by substituting the total offset from  $I_{OUT1X}$  to  $I_{OUT2XS}$  for  $V_{OS1}$  in the equations.

Figure 4. Optional Circuits for Driving  $I_{\text{OUT2}}$  from GND with a Force/Sense Amplifier

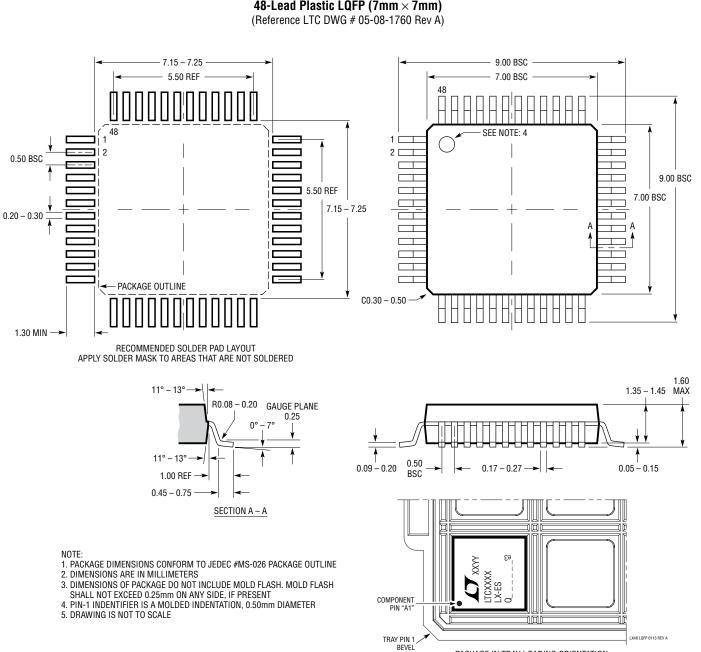

### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/product/LTC2758#packaging for the most recent package drawings.

LX Package 48-Lead Plastic LQFP (7mm × 7mm) (Reference LTC DWG # 05-08-1760 Rev A)

2758fb

PACKAGE IN TRAY LOADING ORIENTATION

### **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                 | PAGE NUMBER |

|-----|-------|---------------------------------------------|-------------|

| A   | 09/13 | Fixed R <sub>COMA</sub> (Pin 3) description | 8           |

|     |       | Updated Typical Application                 | 24          |

| В   | 11/16 | Updated amplifier part numbers              | 19          |

### TYPICAL APPLICATION

Composite Amplifier Circuit Achieves Both Fast Settling and 18-Bit Precision with No Adjustments

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                 | COMMENTS                                                                                   |

|-------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| LTC2757     | Single Parallel 18-Bit I <sub>OUT</sub> SoftSpan DAC        | ±1LSB INL/DNL, Software-Selectable Ranges, 7mm × 7mm LQFP-48 Package                       |

| LTC1592     | Single Serial 16-/14-/12-Bit I <sub>OUT</sub> SoftSpan DACs | ±1LSB INL, DNL, Software-Selectable Ranges, 16-Lead SSOP Package                           |

| LTC2752     | Dual Serial 16-Bit I <sub>OUT</sub> SoftSpan DAC            | ±1LSB INL/DNL, Software-Selectable Ranges, 7mm × 7mm LQFP-48 Package                       |

| LTC2754-12  | Quad Serial 16-/12-Bit I <sub>OUT</sub> SoftSpan DACs       | ±1LSB INL/DNL, Software-Selectable Ranges, 7mm × 8mm QFN-52 Package                        |

| LTC2704-12  | Quad Serial 16-/14-/12-Bit V <sub>OUT</sub> SoftSpan DACs   | ±1LSB INL/DNL, Software-Selectable Ranges, Integrated Amplifiers                           |

| References  |                                                             | ·                                                                                          |

| LTC6655     | Low Drift Precision Buffered Reference                      | 0.025% Max Tolerance, 2ppm/°C Max, 0.25ppm <sub>P-P</sub> 0.1Hz to 10Hz Noise              |

| LT1236      | Precision Reference                                         | 0.05% Max Tolerance, 5ppm/°C Max, 3µV <sub>P-P</sub> 0.1Hz to 10Hz Noise                   |

| LT1460      | Micropower Precision Series Reference                       | 0.075% Max Tolerance, 10ppm/°C Max, 20µV <sub>P-P</sub> 0.1Hz to 10Hz Noise                |

| LT1790      | Micropower Low Dropout Reference                            | 0.05% Max Tolerance, 10ppm/°C Max, 12µV <sub>P-P</sub> 0.1Hz to 10Hz Noise                 |

| LTC6652     | Precision Low Drift Low Noise Buffered Reference            | 0.05% Max Tolerance, 5ppm/°C Max, 2.1ppm <sub>P-P</sub> 0.1Hz to 10Hz Noise                |

| Amplifiers  |                                                             |                                                                                            |

| LTC1150     | Zero-Drift Op Amp with Internal Capacitors                  | 10µV Max Offset, ±16V High Voltage Operation, 1.8µV <sub>P-P</sub> Noise                   |

| LT1012      | Precision Op Amp                                            | 25µV Max Offset, 100pA Max Input Current, 0.5µV <sub>P-P</sub> Noise, 380µA Supply Current |

| LT1001      | Precision Op Amp                                            | 25μV Max Offset, 0.3μV <sub>P-P</sub> Noise, High Output Drive                             |

| LT1468      | Single 16-Bit Accurate Op Amp                               | 900ns Settling, 90MHz GBW, 22V/µs Slew Rate, 75µV Max Offset                               |

|             |                                                             | 2758fi                                                                                     |

LT 1116 REV B • PRINTED IN USA

### **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

LTC2758BCLX#PBF LTC2758ACLX#PBF LTC2758BILX#PBF LTC2758AILX#PBF DC1684A-A