# 4.5A, 500kHz Step-Down Switching Regulator

### **FEATURES**

- Operates with Input as Low as 4V

- Output Range Down to 1.21V

- Constant 500kHz Switching Frequency

- Uses All Surface Mount Components

- Inductor Size Reduced to 1.8µH

- Saturating Switch Design: 0.07Ω

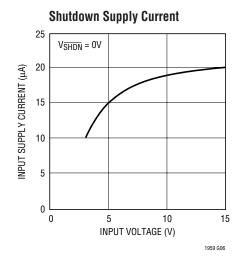

- Shutdown Current: 15µA

- Easily Synchronizable

- Cycle-by-Cycle Current Limiting

- 4.5A Switch

- Current Mode Control

#### **APPLICATIONS**

- Portable Computers

- Battery-Powered Systems

- Battery Chargers

- Distributed Power

- 5V to 3.3V Conversion

- 5V to 2.5V Conversion

- 5V to 1.8V Conversion

### DESCRIPTION

The LT®1959 is a 500kHz monolithic buck mode switching regulator functionally identical to the LT1506 but optimized for lower output voltage applications. It will operate down to 1.21V output compared to 2.42V for the LT1506. A 4.5A switch is included on the die along with all the necessary oscillator, control and logic circuitry. High switching frequency allows a considerable reduction in the size of external components. The topology is current mode for fast transient response and good loop stability.

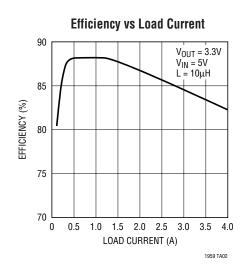

A special high speed bipolar process and new design techniques achieve high efficiency at high switching frequency. Efficiency is maintained over a wide output current range by keeping quiescent supply current to 3.8mA and by utilizing a supply boost capacitor to saturate the power switch.

The LT1959 fits into standard 7-pin DD and fused lead SO-8 packages. Full cycle-by-cycle short-circuit protection and thermal shutdown are provided. Standard surface mount external parts are used, including the inductor and capacitors. There is the optional function of shutdown or synchronization. A shutdown signal reduces supply current to  $15\mu A$ . Synchronization allows an external logic level signal to increase the internal oscillator from 580kHz to 1MHz.

17, LTC and LT are registered trademarks of Linear Technology Corporation.

### TYPICAL APPLICATION

5V to 1.8V Down Converter 1N914  $C_2$ 0.68µF L1 BOOST 5μΗ OUTPUT INPUT  $V_{SW}$ 1.8V C3 R1 4A OPEN LT1959 10μF TO ± 50μF (Ξ SHDN FB HIGH  $V_{C}$ **GND** C1 = ONR2 100μF, 10V  $\mathsf{C}_\mathsf{C}$ **D**1 2 49k SOLID MBRS330T3 TANTALUM 1959 TA01

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Input Voltage                 | 16V   | SYNC Pin Voltage                     | 7V             |

|-------------------------------|-------|--------------------------------------|----------------|

| BOOST Voltage                 | . 30V | Operating Junction Temperature Range |                |

| BOOST Pin Above Input Voltage | 15V   | LT1959C                              | 0°C to 125°C   |

| SHDN Pin Voltage              | 7V    | LT1959I                              | -40°C to 125°C |

| FB Pin Voltage                | 3.5V  | Storage Temperature Range            | -65°C to 150°C |

| FB Pin Current                | 1mA   | Lead Temperature (Soldering, 10 sec) | 300°C          |

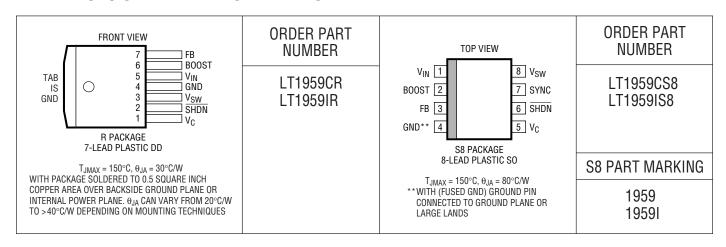

### PACKAGE/ORDER INFORMATION

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $T_J = 25^{\circ}C$ ,  $V_{IN} = 5V$ ,  $V_C = 1.5V$ , Boost =  $V_{IN} + 5V$ , switch open, unless otherwise noted.

| PARAMETER                                             | CONDITIONS                                  |   | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------------------|---------------------------------------------|---|------|------|------|-------|

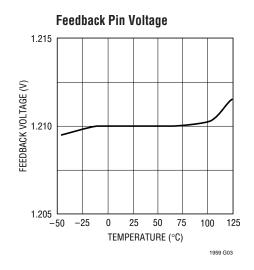

| Feedback Voltage (Adjustable)                         | All Conditions                              | • | 1.19 | 1.21 | 1.23 | V     |

| Reference Voltage Line Regulation                     | $4.3V \le V_{IN} \le 15V$                   |   |      | 0.01 | 0.03 | %/V   |

| Feedback Input Bias Current                           |                                             | • | -0.5 | 0    | 0.5  | μА    |

| Error Amplifier Voltage Gain                          | (Note 2)                                    |   | 200  | 400  |      |       |

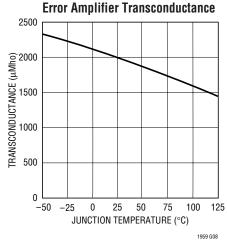

| Error Amplifier Transconductance                      | $\Delta I (V_C) = \pm 10 \mu A$             |   | 1500 | 2000 | 2700 | μMho  |

|                                                       |                                             | • | 1000 |      | 3100 | μMho  |

| V <sub>C</sub> Pin to Switch Current Transconductance |                                             |   |      | 5.3  |      | A/V   |

| Error Amplifier Source Current                        | $V_{FB} = 1.05V$                            | • | 140  | 225  | 320  | μА    |

| Error Amplifier Sink Current                          | $V_{FB} = 1.35V$                            | • | 140  | 225  | 320  | μА    |

| V <sub>C</sub> Pin Switching Threshold                | Duty Cycle = 0                              |   |      | 0.9  |      | V     |

| V <sub>C</sub> Pin High Clamp                         |                                             |   |      | 2.1  |      | V     |

| Switch Current Limit                                  | $V_C$ Open, $V_{FB}$ = 1.05V, $DC \le 50\%$ | • | 4.5  | 6    | 8.5  | А     |

| Slope Compensation                                    | DC = 80%                                    |   |      | 0.8  |      | А     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $T_J = 25^{\circ}C$ ,  $V_{IN} = 5V$ ,  $V_C = 1.5V$ , Boost =  $V_{IN} + 5V$ , switch open, unless otherwise noted.

| PARAMETER                              | CONDITIONS                                                     |   | MIN          | TYP          | MAX         | UNITS      |

|----------------------------------------|----------------------------------------------------------------|---|--------------|--------------|-------------|------------|

| Switch On Resistance (Note 7)          | I <sub>SW</sub> = 4.5A                                         | • |              | 0.07         | 0.1<br>0.13 | Ω<br>Ω     |

| Maximum Switch Duty Cycle              | V <sub>FB</sub> = 1.05V                                        | • | 90<br>86     | 93<br>93     |             | %<br>%     |

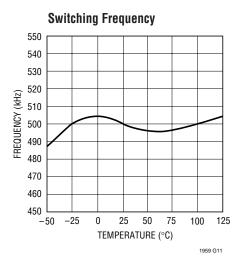

| Switch Frequency                       | V <sub>C</sub> Set to Give 50% Duty Cycle                      | • | 460<br>440   | 500          | 540<br>560  | kHz<br>kHz |

| Switch Frequency Line Regulation       | $4.3V \le V_{IN} \le 15V$                                      | • |              | 0            | 0.15        | %/V        |

| Frequency Shifting Threshold on FB Pin | $\Delta f = 10kHz$                                             | • | 0.5          | 0.7          | 1.0         | V          |

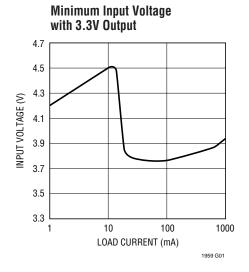

| Minimum Input Voltage (Note 3)         |                                                                | • |              | 4.0          | 4.3         | V          |

| Minimum Boost Voltage (Note 4)         | I <sub>SW</sub> ≤ 4.5A                                         | • |              | 2.3          | 3.0         | V          |

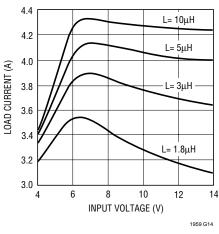

| Boost Current (Note 5)                 | $I_{SW} = 1A$ $I_{SW} = 4.5A$                                  | • |              | 20<br>90     | 35<br>140   | mA<br>mA   |

| Input Supply Current (Note 6)          |                                                                | • |              | 3.8          | 5.4         | mA         |

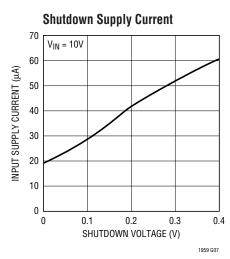

| Shutdown Supply Current                | $V_{\overline{SHDN}} = 0V, V_{SW} = 0V, V_{C} Open$            | • |              | 15           | 50<br>75    | μA<br>μA   |

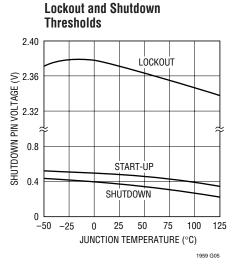

| Lockout Threshold                      | V <sub>C</sub> Open                                            | • | 2.3          | 2.38         | 2.46        | V          |

| Shutdown Thresholds                    | V <sub>C</sub> Open Device Shutting Down<br>Device Starting Up | • | 0.13<br>0.25 | 0.37<br>0.45 | 0.60<br>0.7 | V          |

| Synchronization Threshold              |                                                                | • |              | 1.5          | 2.2         | V          |

| Synchronizing Range                    |                                                                |   | 580          |              | 1000        | kHz        |

| SYNC Pin Input Resistance              |                                                                |   |              | 40           |             | kΩ         |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** Gain is measured with a  $V_C$  swing equal to 200mV above the switching threshold level to 200mV below the upper clamp level.

**Note 3:** Minimum input voltage is not measured directly, but is guaranteed by other tests. It is defined as the voltage where internal bias lines are still regulated so that the reference voltage and oscillator frequency remain constant. Actual minimum input voltage to maintain a regulated output will depend on output voltage and load current. See Applications Information.

**Note 4:** This is the minimum voltage across the boost capacitor needed to guarantee full saturation of the internal power switch.

**Note 5:** Boost current is the current flowing into the boost pin with the pin held 5V above input voltage. It flows only during switch on time.

**Note 6:** Input supply current is the bias current drawn by the input pin with switching disabled.

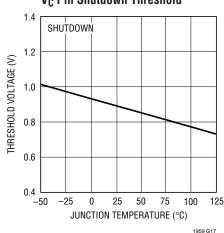

**Note 7:** Switch on resistance is calculated by dividing  $V_{\text{IN}}$  to  $V_{\text{SW}}$  voltage by the forced current (4.5A). See Typical Performance Characteristics for the graph of switch voltage at other currents.

### TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

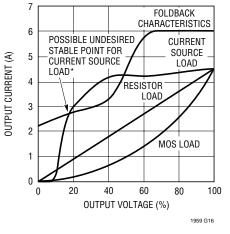

#### V<sub>C</sub> Pin Shutdown Threshold

#### Switch Voltage Drop

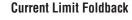

<sup>\*</sup>See "More Than Just Voltage Feedback" in the Applications Information section.

### PIN FUNCTIONS

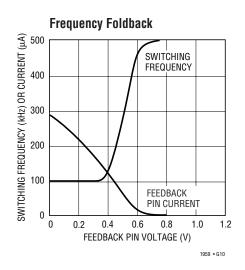

**FB:** The feedback pin is used to set output voltage using an external voltage divider that generates 1.21V at the pin with the desired output voltage. Three additional functions are performed by the FB pin. When the pin voltage drops below 0.8V, switch current limit is reduced. Below 0.7V the external sync function is disabled and switching frequency is reduced. See Feedback Pin Function section in Applications Information for details.

**BOOST:** The BOOST pin is used to provide a drive voltage, higher than the input voltage, to the internal bipolar NPN power switch. Without this added voltage, the typical switch voltage loss would be about 1.5V. The additional boost voltage allows the switch to saturate and voltage loss approximates that of a  $0.07\Omega$  FET structure, but with much smaller die area. Efficiency improves from 75% for conventional bipolar designs to > 89% for these new parts.

$V_{IN}$ : This is the collector of the on-chip power NPN switch. This pin powers the internal circuitry and internal regulator. At NPN switch on and off, high dl/dt edges occur on this pin. Keep the external bypass and catch diode close to this pin. All trace inductance on this path will create a voltage spike at switch off, adding to the  $V_{CE}$  voltage across the internal NPN.

**GND:** The GND pin connection needs consideration for two reasons. First, it acts as the reference for the regulated output, so load regulation will suffer if the "ground" end of the load is not at the same voltage as the GND pin of the IC. This condition will occur when load current or other currents flow through metal paths between the GND pin and the load ground point. Keep the ground path short between the GND pin and the load and use a ground plane when possible. The second consideration is EMI caused by GND pin current spikes. Internal capacitance between the  $V_{SW}$  pin and the GND pin creates very narrow (<10ns) current spikes in the GND pin. If the GND pin is connected to system ground with a long metal trace, this trace may

radiate excess EMI. Keep the path between the input bypass and the GND pin short. The GND pin of the SO-8 package is directly attached to the internal tab. This pin should be attached to a large copper area to improve thermal resistance.

$V_{SW}$ : The switch pin is the emitter of the on-chip power NPN switch. This pin is driven up to the input pin voltage during switch on time. Inductor current drives the switch pin negative during switch off time. Negative voltage is clamped with the external catch diode. Maximum negative switch voltage allowed is -0.8V.

**SYNC:** (S08 Package Only) The sync pin is used to synchronize the internal oscillator to an external signal. It is directly logic compatible and can be driven with any signal between 10% and 90% duty cycle. The synchronizing range is equal to *initial* operating frequency, up to 1MHz. See Synchronizing section in Applications Information for details. When not in use, this pin should be grounded.

**SHDN**: The shutdown pin is used to turn off the regulator and to reduce input drain current to a few microamperes. Actually, this pin has two separate thresholds, one at 2.38V to disable switching, and a second at 0.4V to force complete micropower shutdown. The 2.38V threshold functions as an accurate undervoltage lockout (UVLO). This is sometimes used to prevent the regulator from operating until the input votlage has reached a predetermined level.

$V_C$ : The  $V_C$  pin is the output of the error amplifier and the input of the peak switch current comparator. It is normally used for frequency compensation, but can do double duty as a current clamp or control loop override. This pin sits at about 1V for very light loads and 2V at maximum load. It can be driven to ground to shut off the regulator, but if driven high, current must be limited to 4mA.

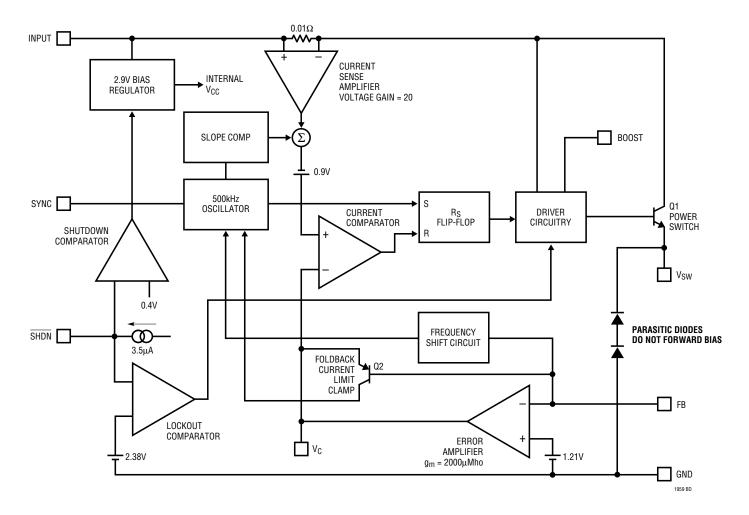

### **BLOCK DIAGRAM**

The LT1959 is a constant frequency, current mode buck converter. This means that there is an internal clock and two feedback loops that control the duty cycle of the power switch. In addition to the normal error amplifier, there is a current sense amplifier that monitors switch current on a cycle-by-cycle basis. A switch cycle starts with an oscillator pulse which sets the  $R_{\rm S}$  flip-flop to turn the switch on. When switch current reaches a level set by the inverting input of the comparator, the flip-flop is reset and the switch turns off. Output voltage control is obtained by using the output of the error amplifier to set the switch current trip point. This technique means that the error amplifier commands current to be delivered to the output rather than voltage. A voltage fed system will have low phase shift up to the resonant frequency of the inductor

and output capacitor, then an abrupt 180° shift will occur. The current fed system will have 90° phase shift at a much lower frequency, but will not have the additional 90° shift until well beyond the LC resonant frequency. This makes it much easier to frequency compensate the feedback loop and also gives much quicker transient response.

High switch efficiency is attained by using the BOOST pin to provide a voltage to the switch driver which is higher than the input voltage, allowing switch to be saturated. This boosted voltage is generated with an external capacitor and diode. Two comparators are connected to the shutdown pin. One has a 2.38V threshold for undervoltage lockout and the second has a 0.4V threshold for complete shutdown.

Figure 1. Block Diagram

#### FEEDBACK PIN FUNCTIONS

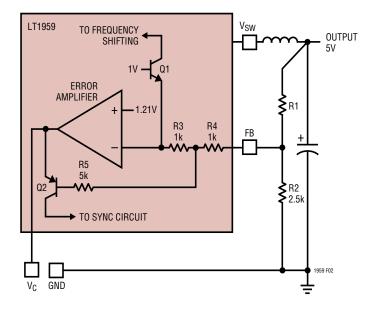

The feedback (FB) pin on the LT1959 is used to set output voltage and provide several overload protection features. The first part of this section deals with selecting resistors to set output voltage and the remaining part talks about foldback frequency and current limiting created by the FB pin. Please read both parts before committing to a final design.

The suggested value for the output divider resistor (see Figure 2) from FB to ground (R2) is 2.5k or less, and a formula for R1 is shown below. The output voltage error caused by ignoring the input bias current on the FB pin is less than 0.1% with R2 = 2.5k. Please read the following if divider resistors are increased above the suggested values.

$$R1 = \frac{R2(V_{OUT} - 1.21)}{1.21}$$

Figure 2. Frequency and Current Limit Foldback

#### More Than Just Voltage Feedback

The feedback pin is used for more than just output voltage sensing. It also reduces switching frequency and current limit when output voltage is very low (see the Frequency Foldback graph in Typical Performance Characteristics). This is done to control power dissipation in both the IC and in the external diode and inductor during short-circuit conditions. A shorted output requires the switching regulator to operate at very low duty cycles, and the average current through the diode and inductor is equal to the short-circuit current limit of the switch (typically 6A for the LT1959, folding back to less than 3A). Minimum switch on time limitations would prevent the switcher from attaining a sufficiently low duty cycle if switching frequency were maintained at 500kHz, so frequency is reduced by about 5:1 when the feedback pin voltage drops below 0.5V (see Frequency Foldback graph). This does not affect operation with normal load conditions; one simply sees a gear shift in switching frequency during start-up as the output voltage rises.

In addition to lower switching frequency, the LT1959 also operates at lower switch current limit when the feedback pin voltage drops below 0.8V. Q2 in Figure 2 performs this function by clamping the V<sub>C</sub> pin to a voltage less than its normal 2.1V upper clamp level. This foldback current limit greatly reduces power dissipation in the IC, diode and inductor during short-circuit conditions. External synchronization is also disabled to prevent interference with foldback operation. Again, it is nearly transparent to the user under normal load conditions. The only loads that may be affected are current source loads which maintain full load current with output voltage less than 50% of final value. In these rare situations the feedback pin can be clamped above 0.75V with an external diode to defeat foldback current limit. Caution: clamping the feedback pin means that frequency shifting will also be defeated, so a combination of high input voltage and dead shorted output may cause the LT1959 to lose control of current limit.

The internal circuitry which forces reduced switching frequency also causes current to flow out of the feedback pin when output voltage is low. The equivalent circuitry is shown in Figure 2. Q1 is completely off during normal operation. If the FB pin falls below 0.7V, Q1 begins to conduct current and reduces frequency at the rate of approximately 2kHz/µA. To ensure adequate frequency foldback (under worst-case short-circuit conditions), the external divider Thevinin resistance must be low enough to pull 150µA out of the FB pin with 0.3V on the pin (R<sub>DIV</sub>  $\leq$  2k). The net result is that reductions in frequency and current limit are affected by output voltage divider impedance. Although divider impedance is not critical, caution should be used if resistors are increased beyond the suggested values and short-circuit conditions will occur with high input voltage. High frequency pickup will increase and the protection accorded by frequency and current foldback will decrease.

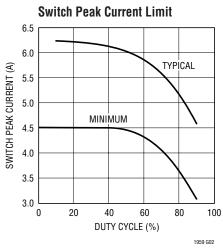

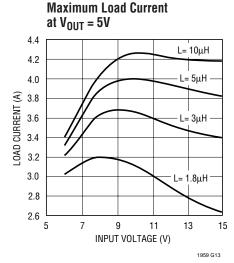

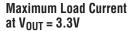

#### MAXIMUM OUTPUT LOAD CURRENT

Maximum load current for a buck converter is limited by the maximum switch current rating ( $I_P$ ) of the LT1959. This current rating is 4.5A up to 50% duty cycle (DC), decreasing to 3.7A at 80% duty cycle. This is shown graphically in Typical Performance Characteristics and as shown in the formula below:

$$I_P = 4.5 \text{A for DC} \le 50\%$$

$I_P = 3.21 + 5.95(\text{DC}) - 6.75(\text{DC})^2 \text{ for } 50\% < \text{DC} < 90\%$

$DC = \text{Duty cycle} = V_{OLIT}/V_{IN}$

Example: with

$$V_{OUT} = 5V$$

,  $V_{IN} = 8V$ ;  $DC = 5/8 = 0.625$ , and;

$$I_{SW(MAX)} = 3.21 + 5.95(0.625) - 6.75(0.625)^2 = 4.3A$$

Current rating decreases with duty cycle because the LT1959 has internal slope compensation to prevent current mode subharmonic switching. For more details, read Application Note 19. The LT1959 is a little unusual in this regard because it has nonlinear slope compensation which gives better compensation with less reduction in current limit.

Maximum load current would be equal to maximum switch current for an infinitely large inductor, but with

finite inductor size, maximum load current is reduced by one-half peak-to-peak inductor current. The following formula assumes continuous mode operation, implying that the term on the right is less than one-half of I<sub>P</sub>.

$$I_{OUT(MAX)} = Continuous Mode$$

$I_{P} - \frac{(V_{OUT})(V_{IN} - V_{OUT})}{2(L)(f)(V_{IN})}$

For the conditions above and  $L = 3.3 \mu H$ ,

$$I_{OUT(MAX)} = 4.3 - \frac{(5)(8-5)}{2(3.3 \cdot 10^{-6})(500 \cdot 10^{3})(8)}$$

$$= 4.3 - 0.57 = 3.73 \text{ A}$$

At  $V_{IN}$  = 15V, duty cycle is 33%, so  $I_P$  is just equal to a fixed 4.5A, and  $I_{OUT(MAX)}$  is equal to:

$$4.5 - \frac{(5)(15-5)}{2(3.3 \cdot 10^{-6})(500 \cdot 10^{3})(15)}$$

$$= 4.5 - 1.01 = 3.49A$$

Note that there is less load current available at the higher input voltage because inductor ripple current increases. This is not always the case. Certain combinations of inductor value and input voltage range may yield lower available load current at the lowest input voltage due to reduced peak switch current at high duty cycles. If load current is close to the maximum available, please check maximum available current at both input voltage extremes. To calculate actual peak switch current with a given set of conditions, use:

$$I_{SW(PEAK)} = I_{OUT} + \frac{V_{OUT}(V_{IN} - V_{OUT})}{2(L)(f)(V_{IN})}$$

#### CHOOSING THE INDUCTOR AND OUTPUT CAPACITOR

For most applications the output inductor will fall in the range of  $3\mu H$  to  $20\mu H$ . Lower values are chosen to reduce physical size of the inductor. Higher values allow more output current because they reduce peak current seen by the LT1959 switch, which has a 4.5A limit. Higher values also reduce output ripple voltage, and reduce core loss. Graphs in the Typical Performance Characteristics section show maximum output load current versus inductor size and input voltage.

When choosing an inductor you might have to consider maximum load current, core and copper losses, allowable component height, output voltage ripple, EMI, fault current in the inductor, saturation, and of course, cost. The following procedure is suggested as a way of handling these somewhat complicated and conflicting requirements.

Choose a value in microhenries from the graphs of maximum load current and core loss. Choosing a small inductor with lighter loads may result in discontinuous mode of operation, but the LT1959 is designed to work well in either mode. Keep in mind that lower core loss means higher cost, at least for closed core geometries like toroids. The core loss graphs show absolute loss for a 3.3V output, so actual percent losses must be calculated for each situation.

Assume that the average inductor current is equal to load current and decide whether or not the inductor must withstand continuous fault conditions. If maximum load current is 0.5A, for instance, a 0.5A inductor may not survive a continuous 4.5A overload condition. Dead shorts will actually be more gentle on the inductor because the LT1959 has foldback current limiting.

2. Calculate peak inductor current at full load current to ensure that the inductor will not saturate. Peak current can be significantly higher than output current, especially with smaller inductors and lighter loads, so don't omit this step. Powdered iron cores are forgiving because they saturate softly, whereas ferrite cores

saturate abruptly. Other core materials fall in between somewhere. The following formula assumes continuous mode of operation, but it errs only slightly on the high side for discontinuous mode, so it can be used for all conditions.

$$I_{PEAK} = I_{OUT} + \frac{V_{OUT}(V_{IN} - V_{OUT})}{2(f)(L)(V_{IN})}$$

V<sub>IN</sub> = Maximum input voltage f = Switching frequency, 500kHz

- 3. Decide if the design can tolerate an "open" core geometry like a rod or barrel, which have high magnetic field radiation, or whether it needs a closed core like a toroid to prevent EMI problems. One would not want an open core next to a magnetic storage media, for instance! This is a tough decision because the rods or barrels are temptingly cheap and small and there are no helpful guidelines to calculate when the magnetic field radiation will be a problem.

- 4. Start shopping for an inductor (see representative surface mount units in Table 2) which meets the requirements of core shape, peak current (to avoid saturation), average current (to limit heating), and fault current (if the inductor gets too hot, wire insulation will melt and cause turn-to-turn shorts). Keep in mind that all good things like high efficiency, low profile, and high temperature operation will increase cost, sometimes dramatically. Get a quote on the cheapest unit first to calibrate yourself on price, then ask for what you really want.

- 5. After making an initial choice, consider the secondary things like output voltage ripple, second sourcing, etc. Use the experts in the Linear Technology's applications department if you feel uncertain about the final choice. They have experience with a wide range of inductor types and can tell you about the latest developments in low profile, surface mounting, etc.

Table 2

| VENDOR/<br>Part No. | VALUE<br>(µH) | DC<br>(Amps) | CORE<br>TYPE | SERIES<br>RESIS-<br>TANCE(Ω) | CORE<br>Mater-<br>Ial | HEIGHT<br>(mm) |

|---------------------|---------------|--------------|--------------|------------------------------|-----------------------|----------------|

| Coiltronics         | •             |              |              | !                            |                       | 1              |

| CTX2-1              | 2             | 4.1          | Tor          | 0.011                        | КМμ                   | 4.2            |

| CTX5-4              | 5             | 4.4          | Tor          | 0.019                        | КМμ                   | 6.4            |

| CTX8-4              | 8             | 3.5          | Tor          | 0.020                        | КМμ                   | 6.4            |

| CTX2-1P             | 2             | 3.4          | Tor          | 0.014                        | 52                    | 4.2            |

| CTX2-3P             | 2             | 4.6          | Tor          | 0.012                        | 52                    | 4.8            |

| CTX5-4P             | 5             | 3.3          | Tor          | 0.027                        | 52                    | 6.4            |

| Sumida              | •             | •            | •            |                              |                       | '              |

| CDRH125             | 10            | 4.0          | SC           | 0.025                        | Fer                   | 6              |

| CDRH125             | 12            | 3.5          | SC           | 0.027                        | Fer                   | 6              |

| CDRH125             | 15            | 3.3          | SC           | 0.030                        | Fer                   | 6              |

| CDRH125             | 18            | 3.0          | SC           | 0.034                        | Fer                   | 6              |

| Coilcraft           |               | •            |              |                              |                       | •              |

| DT3316-222          | 2.2           | 5            | SC           | 0.035                        | Fer                   | 5.1            |

| DT3316-332          | 3.3           | 5            | SC           | 0.040                        | Fer                   | 5.1            |

| DT3316-472          | 4.7           | 3            | SC           | 0.045                        | Fer                   | 5.1            |

| Pulse               |               |              |              |                              |                       |                |

| PE-53650            | 4             | 4.8          | Tor          | 0.017                        | 52                    | 9.1            |

| PE-53651            | 5             | 5.4          | Tor          | 0.018                        | 52                    | 9.1            |

| PE-53652            | 9             | 5.5          | Tor          | 0.022                        | 52                    | 10             |

| PE-53653            | 16            | 5.1          | Tor          | 0.032                        | 52                    | 10             |

| Dale                |               |              | •            |                              |                       | •              |

| IHSM-4825           | 2.7           | 5.1          | Open         | 0.034                        | Fer                   | 5.6            |

| IHSM-4825           | 4.7           | 4.0          | Open         | 0.047                        | Fer                   | 5.6            |

| IHSM-5832           | 10            | 4.3          | Open         | 0.053                        | Fer                   | 7.1            |

| IHSM-5832           | 15            | 3.5          | Open         | 0.078                        | Fer                   | 7.1            |

| IHSM-7832           | 22            | 3.8          | Open         | 0.054                        | Fer                   | 7.1            |

| Tor = Toroid        |               |              |              |                              |                       |                |

SC = Semiclosed geometry

Fer = Ferrite core material

52 = Type 52 powdered iron core material

$KM\mu = Kool M\mu^{\otimes}$

### **Output Capacitor**

The output capacitor is normally chosen by its Effective Series Resistance (ESR), because this is what determines output ripple voltage. At 500kHz, any polarized capacitor is essentially resistive. To get low ESR takes *volume*, so physically smaller capacitors have high ESR. The ESR

Kool Mu is a registered trademark of Magnetics, Inc.

range for typical LT1959 applications is  $0.05\Omega$  to  $0.2\Omega$ . A typical output capacitor is an AVX type TPS, 100µF at 10V. with a guaranteed ESR less than  $0.1\Omega$ . This is a "D" size surface mount solid tantalum capacitor. TPS capacitors are specially constructed and tested for low ESR, so they give the lowest ESR for a given volume. The value in microfarads is not particularly critical, and values from 22μF to greater than 500μF work well, but you cannot cheat mother nature on ESR. If you find a tiny 22µF solid tantalum capacitor, it will have high ESR, and output ripple voltage will be terrible. Table 3 shows some typical solid tantalum surface mount capacitors.

Table 3. Surface Mount Solid Tantalum Capacitor ESR and Ripple Current

| E Case Size           | ESR (Max., $\Omega$ ) | Ripple Current (A) |  |  |

|-----------------------|-----------------------|--------------------|--|--|

| AVX TPS, Sprague 593D | 0.1 to 0.3            | 0.7 to 1.1         |  |  |

| AVX TAJ               | 0.7 to 0.9            | 0.4                |  |  |

| D Case Size           |                       |                    |  |  |

| AVX TPS, Sprague 593D | 0.1 to 0.3            | 0.7 to 1.1         |  |  |

| C Case Size           |                       |                    |  |  |

| AVX TPS               | 0.2 (typ)             | 0.5 (typ)          |  |  |

Many engineers have heard that solid tantalum capacitors are prone to failure if they undergo high surge currents. This is historically true, and type TPS capacitors are specially tested for surge capability, but surge ruggedness is not a critical issue with the output capacitor. Solid tantalum capacitors fail during very high turn-on surges, which do not occur at the output of regulators. High discharge surges, such as when the regulator output is dead shorted, do not harm the capacitors.

Unlike the input capacitor, RMS ripple current in the output capacitor is normally low enough that ripple current rating is not an issue. The current waveform is triangular with a typical value of 200mA<sub>RMS</sub>. The formula to calculate this is:

Output Capacitor Ripple Current (RMS):

$$I_{RIPPLE\left(RMS\right)} = \frac{0.29 \left(V_{OUT}\right) \left(V_{IN} - V_{OUT}\right)}{\left(L\right) \left(f\right) \left(V_{IN}\right)}$$

### **Ceramic Capacitors**

Higher value, lower cost ceramic capacitors are now available in smaller case sizes. These are ideal for input bypassing because of their high ripple rating and tolerance to turn-on surges. As output capacitors, caution must be used. Solid tantalum capacitor's ESR generates a loop "zero" at 5kHz to 50kHz that is beneficial in giving acceptable loop phase margin. Ceramic capacitors remain capacitive to beyond 300kHz and usually resonate with their ESL before ESR becomes effective. When using ceramic output capacitors, the loop compensation pole frequency must be reduced by a typical factor of 10.

#### **OUTPUT RIPPLE VOLTAGE**

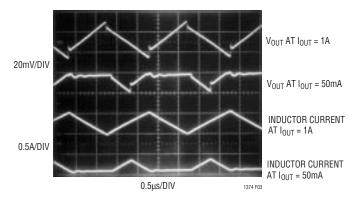

Figure 3 shows a typical output ripple voltage waveform for the LT1959. Ripple voltage is determined by the high frequency impedance of the output capacitor, and ripple current through the inductor. Peak-to-peak ripple current through the inductor into the output capacitor is:

$$I_{P-P} = \frac{(V_{OUT})(V_{IN} - V_{OUT})}{(V_{IN})(L)(f)}$$

For high frequency switchers, the sum of ripple current slew rates may also be relevant and can be calculated from:

$$\Sigma \frac{dI}{dt} = \frac{V_{IN}}{L}$$

Peak-to-peak output ripple voltage is the sum of a *triwave* created by peak-to-peak ripple current times ESR, and a *square* wave created by parasitic inductance (ESL) and ripple current slew rate. Capacitive reactance is assumed to be small compared to ESR or ESL.

$$V_{RIPPLE} = (I_{P-P})(ESR) + (ESL)\Sigma \frac{dI}{dt}$$

Example: with  $V_{IN}$  =10V,  $V_{OUT}$  = 5V, L = 10 $\mu H,$  ESR = 0.1 $\Omega,$  ESL = 10nH:

$$I_{P-P} = \frac{\left(5\right)\left(10 - 5\right)}{\left(10\right)\left(10 \cdot 10^{-6}\right)\left(500 \cdot 10^{3}\right)} = 0.5A$$

$$\Sigma \frac{dI}{dt} = \frac{10}{10 \cdot 10^{-6}} = 10^{6}$$

$$V_{RIPPLE} = \left(0.5A\right)\left(0.1\right) + \left(10 \cdot 10^{-9}\right)\left(10^{6}\right)$$

$$= 0.05 + 0.01 = 60 \text{mV}_{P-P}$$

Figure 3. LT1959 Ripple Voltage Waveform

#### **CATCH DIODE**

The suggested catch diode (D1) is a 1N5821 Schottky, or its Motorola equivalent, MBR330. It is rated at 3A average forward current and 30V reverse voltage. Typical forward voltage is 0.5V at 3A. The diode conducts current only during switch off time. Peak reverse voltage is equal to regulator input voltage. Average forward current in normal operation can be calculated from:

$$I_{D(AVG)} = \frac{I_{OUT}(V_{IN} - V_{OUT})}{V_{IN}}$$

This formula will not yield values higher than 3A with maximum load current of 4.25A unless the ratio of input to output voltage exceeds 3.4:1. The only reason to consider a larger diode is the worst-case condition of a high input voltage and *overloaded* (not shorted) output. Under short-circuit conditions, foldback current limit will reduce diode current to less than 2.6A, but if the output is overloaded

and does not fall to less than 1/3 of nominal output voltage, foldback will not take effect. With the overloaded condition, output current will increase to a typical value of 5.7A, determined by peak switch current limit of 6A. With  $V_{IN} = 15V$ ,  $V_{OUT} = 4V$  (5V overloaded) and  $I_{OUT} = 5.7A$ :

$$I_{D(AVG)} = \frac{5.7(15-4)}{15} = 4.18A$$

This is safe for short periods of time, but it would be prudent to check with the diode manufacturer if continuous operation under these conditions must be tolerated.

#### **BOOST PIN CONSIDERATIONS**

For most applications, the boost components are a  $0.27\mu F$  capacitor and a 1N914 or 1N4148 diode. The anode is connected to the regulated output voltage and this generates a voltage across the boost capacitor nearly identical to the regulated output. In certain applications, the anode may instead be connected to the unregulated input voltage. This could be necessary if the regulated output voltage is very low (< 3V) or if the input voltage is less than 5V. Efficiency is not affected by the capacitor value, but the capacitor should have an ESR of less than  $1\Omega$  to ensure that it can be recharged fully under the worst-case condition of minimum input voltage. Almost any type of film or ceramic capacitor will work fine.

For nearly all applications, a 0.27µF boost capacitor works just fine, but for the curious, more details are provided here. The size of the boost capacitor is determined by switch drive current requirements. During switch on time, drain current on the capacitor is approximately  $I_{OLIT}/50$ . At peak load current of 4.25A, this gives a total drain of 85mA. Capacitor ripple voltage is equal to the product of on time and drain current divided by capacitor value;  $\Delta V = (t_{ON})(85\text{mA/C})$ . To keep capacitor ripple voltage to less than 0.6V (a slightly arbitrary number) at the worstcase condition of  $t_{ON} = 1.8 \mu s$ , the capacitor needs to be 0.27µF. Boost capacitor ripple voltage is not a critical parameter, but if the minimum voltage across the capacitor drops to less than 3V, the power switch may not saturate fully and efficiency will drop. An approximate formula for absolute minimum capacitor value is:

$$C_{MIN} = \frac{(I_{OUT} / 50)(V_{OUT} / V_{IN})}{(f)(V_{OUT} - 2.8 V)}$$

f = Switching frequency V<sub>OUT</sub> = Regulated output voltage V<sub>IN</sub> = Minimum input voltage

This formula can yield capacitor values substantially less than  $0.27\mu F$ , but it should be used with caution since it does not take into account secondary factors such as capacitor series resistance, capacitance shift with temperature and output overload.

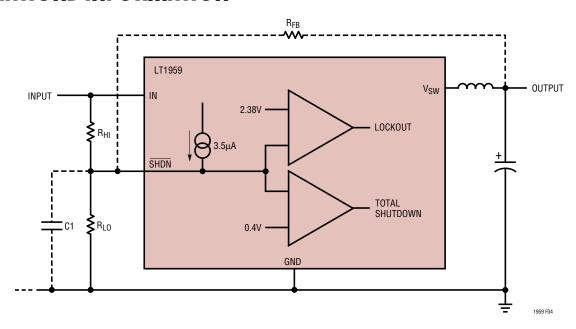

# SHUTDOWN FUNCTION AND UNDERVOLTAGE LOCKOUT

Figure 4 shows how to add undervoltage lockout (UVLO) to the LT1959. Typically, ULVO is used in situations where the input supply is *current limited*, or has a relatively high source resistance. A switching regulator draws constant power from the source, so source current increases as source voltage drops. This looks like a negative resistance load to the source and can cause the source to current limit or latch low under low source voltage conditions. ULVO prevents the regulator from operating at source voltages where these problems might occur.

Threshold voltage for lockout is about 2.38V. A 3.5 $\mu$ A bias current flows *out* of the pin at threshold. This internally generated current is used to force a default high state on the shutdown pin if the pin is left open. When low shutdown current is not an issue, the error due to this current can be minimized by making R<sub>LO</sub> 10k or less. If shutdown current is an issue, R<sub>LO</sub> can be raised to 100k, but the error due to initial bias current and changes with temperature should be considered.

$$R_{LO} = 10k \text{ to } 100k (25k \text{ suggested})$$

$$R_{HI} = \frac{R_{LO}(V_{IN} - 2.38V)}{2.38V - R_{LO}(3.5\mu\text{A})}$$

V<sub>IN</sub> = Minimum input voltage

Figure 4. Undervoltage Lockout

Keep the connections from the resistors to the shutdown pin short and make sure that interplane or surface capacitance to the switching nodes are minimized. If high resistor values are used, the shutdown pin should be bypassed with a 1000pF capacitor to prevent coupling problems from the switch node. If hysteresis is desired in the undervoltage lockout point, a resistor  $R_{FB}$  can be added to the output node. Resistor values can be calculated from:

$$R_{HI} = \frac{R_{LO} \Big[ V_{IN} - 2.38 \Big( \Delta V / V_{OUT} + 1 \Big) + \Delta V \Big]}{2.38 - R2 \Big( 3.5 \mu A \Big)}$$

$$R_{FB} = \Big( R_{HI} \Big) \Big( V_{OUT} / \Delta V \Big)$$

25k suggested for R<sub>LO</sub>

$V_{IN}$  = Input voltage at which switching stops as input voltage descends to trip level

$\Delta V$  = Hysteresis in input voltage level

Example: output voltage is 5V, switching is to stop if input voltage drops below 6V and should not restart unless input rises back to 7.5V.  $\Delta V$  is therefore 1.5V and  $V_{IN}$  = 6V. Let  $R_{I,O}$  = 25k.

$$R_{HI} = \frac{25k \left[6 - 2.38 \left(1.5/5 + 1\right) + 1.5\right]}{2.38 - 25k \left(3.5\mu A\right)}$$

$$= \frac{25k \left(5.2\right)}{2.29} = 48k$$

$$R_{FB} = 48k \left(5/1.5\right) = 160k$$

#### SWITCH NODE CONSIDERATIONS

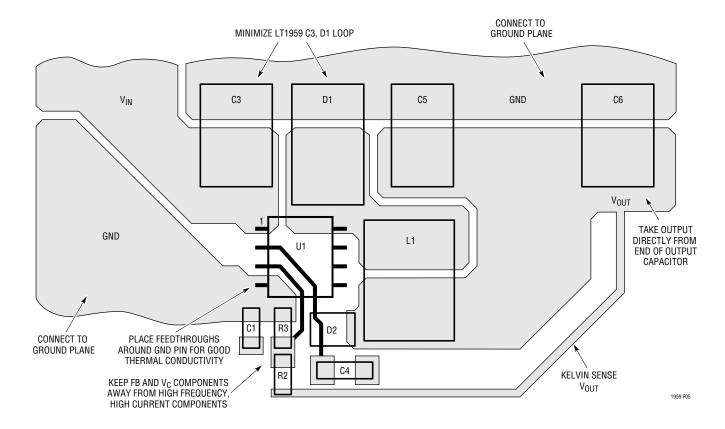

For maximum efficiency, switch rise and fall times are made as short as possible. To prevent radiation and high frequency resonance problems, proper layout of the components connected to the switch node is essential. B field (magnetic) radiation is minimized by keeping catch diode, switch pin, and input bypass capacitor leads as short as possible. E field radiation is kept low by minimizing the length and area of all traces connected to the switch pin and BOOST pin. A ground plane should always be used under the switcher circuitry to prevent interplane coupling. A suggested layout for the critical components is shown in Figure 5. Note that the feedback resistors and compensation components are kept as far as possible

from the switch node. Also note that the high current ground path of the catch diode and input capacitor are kept very short and separate from the analog ground line.

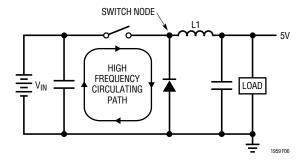

The high speed switching current path is shown schematically in Figure 6. Minimum lead length in this path is essential to ensure clean switching and low EMI. The path including the switch, catch diode, and input capacitor is

the only one containing nanosecond rise and fall times. If you follow this path on the PC layout, you will see that it is irreducibly short. If you move the diode or input capacitor away from the LT1959, get your resumé in order. The other paths contain only some combination of DC and 500kHz triwave, so are much less critical.

Figure 5. Suggested Layout (Topside Only Shown)

Figure 6. High Speed Switching Path

#### PARASITIC RESONANCE

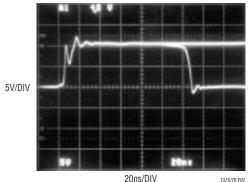

Resonance or "ringing" may sometimes be seen on the switch node (see Figure 7). Very high frequency ringing following switch rise time is caused by switch/diode/input capacitor lead inductance and diode capacitance. Schottky diodes have very high "Q" junction capacitance that can ring for many cycles when excited at high frequency. If total lead length for the input capacitor, diode and switch path is 1 inch, the inductance will be approximately 25nH. At switch off, this will produce a spike across the NPN output device in addition to the input voltage. At higher currents this spike can be in the order of 10V to 20V or higher with a poor layout, potentially exceeding the absolute max switch voltage. The path around switch, catch diode and input capacitor must be kept as short as possible to ensure reliable operation. When looking at this, a >100MHz oscilloscope must be used, and waveforms should be observed on the leads of the package. This switch off spike will also cause the SW node to go below ground. The LT1959 has special circuitry inside which

20ns/DIV 137

Figure 7. Switch Node Resonance

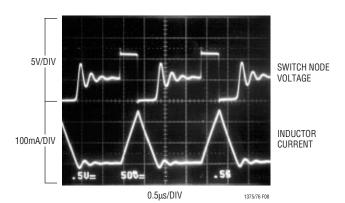

Figure 8. Discontinuous Mode Ringing

mitigates this problem, but negative voltages over 1V lasting longer than 10ns should be avoided. Note that 100MHz oscilloscopes are barely fast enough to see the details of the falling edge overshoot in Figure 7.

A second, much lower frequency ringing is seen during switch off time if load current is low enough to allow the inductor current to fall to zero during part of the switch off time (see Figure 8). Switch and diode capacitance resonate with the inductor to form damped ringing at 1MHz to 10 MHz. This ringing is not harmful to the regulator and it has not been shown to contribute significantly to EMI. Any attempt to damp it with a resistive snubber will degrade efficiency.

#### INPUT BYPASSING AND VOLTAGE RANGE

#### **Input Bypass Capacitor**

RISE AND FALL WAVEFORMS ARE

SUPERIMPOSED

(PULSE WIDTH IS

NOT 120ns)

Step-down converters draw current from the input supply in pulses. The average height of these pulses is equal to load current, and the duty cycle is equal to  $V_{OUT}/V_{IN}$ . Rise and fall time of the current is very fast. A local bypass capacitor across the input supply is necessary to ensure proper operation of the regulator and minimize the ripple current fed back into the input supply. The capacitor also forces switching current to flow in a tight local loop, minimizing EMI.

Do not cheat on the ripple current rating of the Input bypass capacitor, but also don't get hung up on the value in microfarads. The input capacitor is intended to absorb all the switching current ripple, which can have an RMS value as high as one half of load current. Ripple current ratings on the capacitor must be observed to ensure reliable operation. In many cases it is necessary to parallel two capacitors to obtain the required ripple rating. Both capacitors must be of the same value and manufacturer to guarantee power sharing. The actual value of the capacitor in microfarads is not particularly important because at 500 kHz, any value above  $5 \mu \text{F}$  is essentially resistive. RMS ripple current rating is the critical parameter. Actual RMS current can be calculated from:

$$I_{RIPPLE\left(RMS\right)} = I_{OUT} \sqrt{V_{OUT} \left(V_{IN} - V_{OUT}\right) / {V_{IN}}^2}$$

The term inside the radical has a maximum value of 0.5 when input voltage is twice output, and stays near 0.5 for a relatively wide range of input voltages. It is common practice therefore to simply use the worst-case value and assume that RMS ripple current is one half of load current. At maximum output current of 4.5A for the LT1959, the input bypass capacitor should be rated at 2.25A ripple current. Note however, that there are many secondary considerations in choosing the final ripple current rating. These include ambient temperature, average versus peak load current, equipment operating schedule, and required product lifetime. For more details, see Application Notes 19 and 46, and Design Note 95.

#### **Input Capacitor Type**

Some caution must be used when selecting the type of capacitor used at the input to regulators. Aluminum electrolytics are lowest cost, but are physically large to achieve adequate ripple current rating, and size constraints (especially height), may preclude their use. Ceramic capacitors are now available in larger values, and their high ripple current and voltage rating make them ideal for input bypassing. Cost is fairly high and footprint may also be somewhat large. Solid tantalum capacitors would be a good choice, except that they have a history of occasional spectacular failures when they are subjected to large current surges during power-up. The capacitors can short and then burn with a brilliant white light and lots of nasty smoke. This phenomenon occurs in only a small percentage of units, but it has led some OEM companies to forbid their use in high surge applications. The input bypass capacitor of regulators can see these high surges when a battery or high capacitance source is connected. Several manufacturers have developed a line of solid tantalum capacitors specially tested for surge capability (AVX TPS series for instance, see Table 3), but even these units may fail if the input voltage surge approaches the maximum voltage rating of the capacitor. AVX recommends derating capacitor voltage by 2:1 for high surge applications.

Larger capacitors may be necessary when the input voltage is very close to the minimum specified on the data sheet. Small voltage dips during switch on time are not

normally a problem, but at very low input voltage they may cause erratic operation because the input voltage drops below the minimum specification. Problems can also occur if the input-to-output voltage differential is near minimum. The amplitude of these dips is normally a function of capacitor ESR and ESL because the capacitive reactance is small compared to these terms. ESR tends to be the dominate term and is inversely related to physical capacitor size within a given capacitor type.

### **SYNCHRONIZING**

The SYNC pin, is used to synchronize the internal oscillator to an external signal. The SYNC input must pass from a logic level low, through the maximum synchronization threshold with a duty cycle between 10% and 90%. The input can be driven directly from a logic level output. The synchronizing range is equal to *initial* operating frequency up to 1MHz. This means that minimum practical sync frequency is equal to the worst-case *high* self-oscillating frequency (560kHz), not the typical operating frequency of 500kHz. Caution should be used when synchronizing above 700kHz because at higher sync frequencies the amplitude of the internal slope compensation used to prevent subharmonic switching is reduced. This type of subharmonic switching only occurs at input voltages less than twice output voltage. Higher inductor values will tend to eliminate this problem. See Frequency Compensation section for a discussion of an entirely different cause of subharmonic switching before assuming that the cause is insufficient slope compensation. Application Note 19 has more details on the theory of slope compensation.

At power-up, when  $V_{C}$  is being clamped by the FB pin (see Figure 2, Q2), the sync function is disabled. This allows the frequency foldback to operate in the shorted output condition. During normal operation, switching frequency is controlled by the internal oscillator until the FB pin reaches 0.7V, after which the SYNC pin becomes operational.

#### THERMAL CALCULATIONS

Power dissipation in the LT1959 chip comes from four sources: switch DC loss, switch AC loss, boost circuit current, and input quiescent current. The following

formulas show how to calculate each of these losses. These formulas assume continuous mode operation, so they should not be used for calculating efficiency at light load currents.

Switch loss:

$$P_{SW} = \frac{R_{SW} \Big(I_{OUT}\Big)^2 \Big(V_{OUT}\Big)}{V_{IN}} + 24ns\Big(I_{OUT}\Big) \Big(V_{IN}\Big) \Big(f\Big)$$

Boost current loss:

$$P_{BOOST} = \frac{V_{OUT}^2 \left(I_{OUT} / 50\right)}{V_{IN}}$$

Quiescent current loss:

$$P_{Q} = V_{IN}(0.001) + V_{OUT}(0.005) + \frac{\left(V_{OUT}^{2}\right)(0.002)}{V_{IN}}$$

$R_{SW}$  = Switch resistance ( $\approx 0.07$ )

24ns = Equivalent switch current/voltage overlap time f = Switch frequency

Example: with  $V_{IN} = 10V$ ,  $V_{OUT} = 5V$  and  $I_{OUT} = 3A$ :

$$P_{SW} = \frac{(0.07)(3)^{2}(5)}{10} + (24 \cdot 10^{-9})(3)(10)(500 \cdot 10^{3})$$

= 0.32 + 0.36 = 0.68W

$$P_{BOOST} = \frac{(5)^2 (3/50)}{10} = 0.15W$$

$$P_Q = 10(0.001) + 5(0.005) + \frac{(5)^2(0.002)}{10} = 0.04W$$

Total power dissipation is 0.68 + 0.15 + 0.04 = 0.87W.

Thermal resistance for LT1959 package is influenced by the presence of internal or backside planes. With a full plane under the SO package, thermal resistance will be about 80°C/W. No plane will increase resistance to about 120°C/W. To calculate die temperature, use the proper thermal resistance number for the desired package and add in worst-case ambient temperature:

$$T_{J} = T_{A} + \theta_{JA} (P_{TOT})$$

With the SO-8 package ( $\theta_{JA} = 80^{\circ}C/W$ ), at an ambient temperature of 50°C,

$$T_J = 50 + 80 (0.87) = 120$$

°C

Die temperature is highest at low input voltage, so use lowest continuous input operating voltage for thermal calculations.

#### FREQUENCY COMPENSATION

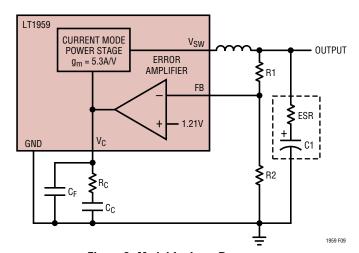

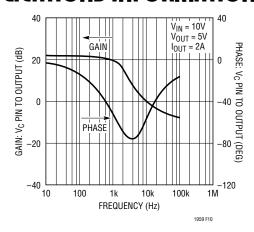

Loop frequency compensation of switching regulators can be a rather complicated problem because the reactive components used to achieve high efficiency also introduce multiple poles into the feedback loop. The inductor and output capacitor on a conventional stepdown converter actually form a resonant tank circuit that can exhibit peaking and a rapid 180° phase shift at the resonant frequency. By contrast, the LT1959 uses a "current mode" architecture to help alleviate phase shift created by the inductor. The basic connections are shown in Figure 9. Figure 10 shows a Bode plot of the phase and gain of the power section of the LT1959, measured from the  $V_C$ pin to the output. Gain is set by the 5.3A/V transconductance of the LT1959 power section and the effective complex impedance from output to ground. Gain rolls off smoothly above the 600Hz pole frequency set by the 100µF output capacitor. Phase drop is limited to about 70°. Phase recovers and gain levels off at the zero frequency ( $\approx$ 16kHz) set by capacitor ESR (0.1 $\Omega$ ).

Figure 9. Model for Loop Response

Figure 10. Response from V<sub>C</sub> Pin to Output

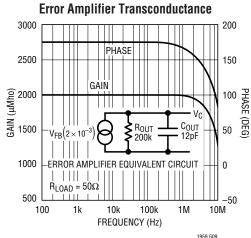

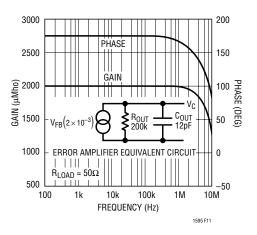

Error amplifier transconductance phase and gain are shown in Figure 11. The error amplifier can be modeled as a transconductance of  $2000\mu Mho$ , with an output impedance of  $200k\Omega$  in parallel with 12pF. In all practical applications, the compensation network from  $V_C$  pin to ground has a much lower impedance than the output impedance of the amplifier at frequencies above 500Hz. This means that the error amplifier characteristics themselves do not contribute excess phase shift to the loop, and the phase/gain characteristics of the error amplifier section are completely controlled by the external compensation network.

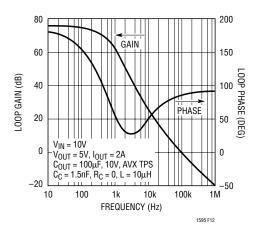

In Figure 12, full loop phase/gain characteristics are shown with a compensation capacitor of 1.5nF, giving the error amplifier a pole at 530Hz, with phase rolling off to 90° and staying there. The overall loop has a gain of 74dB at low frequency, rolling off to unity-gain at 100kHz. Phase shows a two-pole characteristic until the ESR of the output capacitor brings it back above 10kHz. Phase margin is about 60° at unity-gain.

Analog experts will note that around 4.4kHz, phase dips very close to the zero phase margin line. This is typical of switching regulators, especially those that operate over a wide range of loads. This region of low phase is not a problem as long as it does not occur near unity-gain. In practice, the variability of output capacitor ESR tends to dominate all other effects with respect to loop response. Variations in ESR *will* cause unity-gain to move around, but at the same time phase moves with it so that adequate phase margin is maintained over a very wide range of ESR ( $\geq \pm 3:1$ ).

Figure 11. Error Amplifier Gain and Phase

Figure 12. Overall Loop Characteristics

### What About a Resistor in the Compensation Network?

It is common practice in switching regulator design to add a "zero" to the error amplifier compensation to increase loop phase margin. This zero is created in the external network in the form of a resistor ( $R_{C}$ ) in series with the compensation capacitor. Increasing the size of this resistor generally creates better and better loop stability, but there are two limitations on its value. First, the combination of output capacitor ESR and a large value for  $R_{C}$  may cause loop gain to stop rolling off altogether, creating a gain margin problem. An approximate formula for  $R_{C}$  where gain margin falls to zero is:

$$R_{C}(Loop Gain = 1) = \frac{V_{OUT}}{(G_{MP})(G_{MA})(ESR)(1.21)}$$

$G_{MP}$  = Transconductance of power stage = 5.3A/V

$G_{MA}$  = Error amplifier transconductance =  $2(10^{-3})$

ESR = Output capacitor ESR

1.21 = Reference voltage

With  $V_{OUT} = 5V$  and ESR =  $0.03\Omega$ , a value of 6.5k for R<sub>C</sub> would yield zero gain margin, so this represents an upper limit. There is a second limitation however which has nothing to do with theoretical small signal dynamics. This resistor sets high frequency gain of the error amplifier, including the gain at the switching frequency. If switching frequency gain is high enough, output ripple voltage will appear at the V<sub>C</sub> pin with enough amplitude to muck up proper operation of the regulator. In the marginal case, subharmonic switching occurs, as evidenced by alternating pulse widths seen at the switch node. In more severe cases, the regulator squeals or hisses audibly even though the output voltage is still roughly correct. None of this will show on a theoretical Bode plot because Bode is an amplitude insensitive analysis. Tests have shown that if ripple voltage on the  $V_C$  is held to less than  $100 \text{mV}_{P-P}$ , the LT1959 will be well behaved. The formula below will give an estimate of V<sub>C</sub> ripple voltage when R<sub>C</sub> is added to the loop, assuming that R<sub>C</sub> is large compared to the reactance of C<sub>C</sub> at 500kHz.

$$V_{C(RIPPLE)} = \frac{\left(R_{C}\right)\!\left(G_{MA}\right)\!\left(V_{IN} - V_{OUT}\right)\!\left(ESR\right)\!\left(1.21\right)}{\left(V_{IN}\right)\!\left(L\right)\!\left(f\right)}$$

$G_{MA}$  = Error amplifier transconductance (2000 $\mu$ Mho)

If a computer simulation of the LT1959 showed that a series compensation resistor of 6k gave best overall loop response, with adequate gain margin, the resulting  $V_C$  pin ripple voltage with  $V_{IN}$  = 10V,  $V_{OUT}$  = 5V, ESR = 0.1 $\Omega$ , L = 10 $\mu$ H, would be:

$$V_{C(RIPPLE)} = \frac{(6k)(2 \cdot 10^{-3})(10 - 5)(0.1)(1.21)}{(10)(10 \cdot 10^{-6})(500 \cdot 10^{3})} = 0.144V$$

This ripple voltage is high enough to possibly create subharmonic switching. In most situations a compromise value (<2k in this case) for the resistor gives acceptable phase margin and no subharmonic problems. In other

cases, the resistor may have to be larger to get acceptable phase response, and some means must be used to control ripple voltage at the  $V_C$  pin. The suggested way to do this is to add a capacitor  $(C_F)$  in parallel with the  $R_C/C_C$  network on the  $V_C$  pin. Pole frequency for this capacitor is typically set at one-fifth of switching frequency so that it provides significant attenuation of switching ripple, but does not add unacceptable phase shift at loop unity-gain frequency. With  $R_C = 6k$ ,

$$C_F = \frac{5}{(2\pi)(f)(R_C)} = \frac{5}{2\pi(500 \times 10^3)(6k)} = 275pF$$

#### **How Do I Test Loop Stability?**

The "standard" compensation for LT1959 is a 1.5nF capacitor for  $C_C$ , with  $R_C = 0$ . While this compensation will work for most applications, the "optimum" value for loop compensation components depends, to various extent, on parameters which are not well controlled. These include inductor value ( $\pm 30\%$  due to production tolerance, load current and ripple current variations), output capacitance ( $\pm 20\%$  to  $\pm 50\%$  due to production tolerance, temperature, aging and changes at the load), output capacitor ESR ( $\pm 200\%$  due to production tolerance, temperature and aging), and finally, DC input voltage and output load current. This makes it important for the designer to check out the final design to ensure that it is "robust" and tolerant of all these variations.

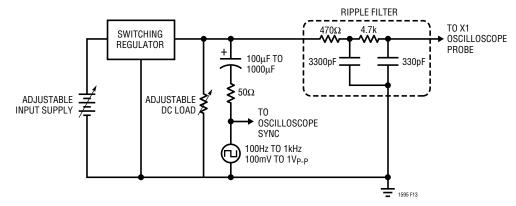

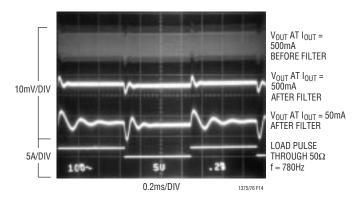

I check switching regulator loop stability by pulse loading the regulator output while observing transient response at the output, using the circuit shown in Figure 13. The regulator loop is "hit" with a small transient AC load current at a relatively low frequency, 50Hz to 1kHz. This causes the output to jump a few millivolts, then settle back to the original value, as shown in Figure 14. A well behaved loop will settle back cleanly, whereas a loop with poor phase or gain margin will "ring" as it settles. The *number* of rings indicates the degree of stability, and the *frequency* of the ringing shows the approximate unity-gain frequency of the loop. *Amplitude* of the signal is not particularly important, as long as the amplitude is not so high that the loop behaves nonlinearly.

Figure 13. Loop Stability Test Circuit

Figure 14. Loop Stability Check

The output of the regulator contains both the desired low frequency transient information and a reasonable amount of high frequency (500kHz) ripple. The ripple makes it difficult to observe the small transient, so a two-pole, 100kHz filter has been added. This filter is not particularly critical; even if it attenuated the transient signal slightly, this wouldn't matter because amplitude is not critical.

After verifying that the setup is working correctly, I start varying load current and input voltage to see if I can find any combination that makes the transient response look suspiciously "ringy." This procedure may lead to an adjustment for best loop stability or faster loop transient response. Nearly always you will find that loop response looks better if you add in several  $k\Omega$  for  $R_C$ . Do this only if necessary, because as explained before,  $R_C$  above 1k may require the addition of  $C_F$  to control  $V_C$  pin ripple. If everything looks OK, I use a heat gun and cold spray on the circuit (especially the output capacitor) to bring out any temperature-dependent characteristics.

Keep in mind that this procedure does not take initial component tolerance into account. You should see fairly clean response under all load and line conditions to ensure that component variations will not cause problems. One note here: according to Murphy, the component most likely to be changed in production is the output capacitor, because that is the component most likely to have manufacturer variations (in ESR) large enough to cause problems. It would be a wise move to lock down the sources of the output capacitor in production.

A possible exception to the "clean response" rule is at very light loads, as evidenced in Figure 14 with  $I_{LOAD} = 50 \text{mA}$ . Switching regulators tend to have dramatic shifts in loop response at very light loads, mostly because the inductor current becomes discontinuous. One common result is very slow but stable characteristics. A second possibility is low phase margin, as evidenced by ringing at the output with transients. The good news is that the low phase margin at light loads is not particularly sensitive to component variation, so if it looks reasonable under a transient test, it will probably not be a problem in production. Note that *frequency* of the light load ringing may vary with component tolerance but phase margin generally hangs in there.

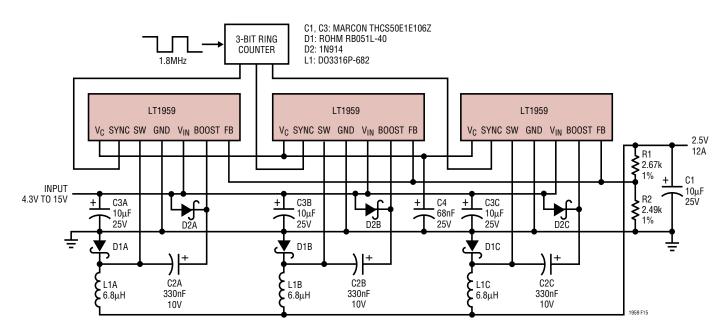

#### **CURRENT SHARING MULTIPHASE SUPPLY**

The circuit in Figure 15 uses multiple LT1959s to produce a 2.5V, 12A power supply. There are several advantages to using a multiple switcher approach compared to a single larger switcher. The inductor size is considerably reduced. Three 4A inductors store less energy (LI<sup>2</sup>/2) than one 12A coil so are far smaller. In addition, synchronizing three

converters 120° out of phase with each other reduces input and output ripple currents. This reduces the ripple rating, size and cost of filter capacitors.

### **Current Sharing/Split Input Supplies**

Current sharing is accomplished by joining the  $V_C$  pins to a common compensation capacitor. The output of the error amplifier is a gm stage, so any number of devices can be connected together. The effective gm of the composite error amplifier is the multiple of the individual devices. In Figure 15, the compensation capacitor C4 has been increased by  $\times 3$ . Tolerances in the reference voltages result in small offset currents to flow between the  $V_C$  pins. The overall effect is that the loop regulates the output at a voltage between the minimum and maximum reference of the devices used. Switch current matching between devices will be typically better than 300mA. The negative temperature coefficient of the  $V_C$  to switch current transconductance prevents current hogging.

A common  $V_C$  voltage forces each LT1959 to operate at the same switch current, not duty cycle. Each device operates at the duty cycle defined by its respective input voltage. In Figure 15, the input could be split and each device operated at a different voltage. The common  $V_C$  ensures loading is shared between inputs.

#### **Synchronized Ripple Currents**

A ring counter generates three synchronization signals at 600kHz, 33% duty cycle phased 120° apart. The sync input will operate over a wide range of duty cycles, so no further pulse conditioning is needed. Each device's maximum input ripple current is a 4A square wave at 600kHz. When synchronously added together, the ripple remains at 4A but frequency increases to 1.8MHz. Likewise, the output ripple current is a 1.8MHz triangular waveform. with maximum amplitude of 350mA at 5V V<sub>IN</sub>. Interestingly, at 7.6V and 15V V<sub>IN</sub>, the theoretical summed output ripple current cancels completely. To reduce board space and ripple voltage, C1 and C3 are ceramic capacitors. Loop compensation C4 must be adjusted when using ceramic output capacitors due to the lack of effective series resistance. The typical tantalum compensation of 1.5nF is increased to 22nF ( $\times$ 3) for the ceramic output capacitor. If synchronization is not used and the internal oscillators free run, the circuit will operate correctly, but ripple cancellation will not occur. Input and output capacitors must be ripple rated for the total output current.

Figure 15. Current Sharing 12A Supply

#### **Redundant Operation**

The circuit shown in Figure 15 is fault tolerant when operating at less than 8A of output current. If one device fails, the output will remain in regulation. The feedback loop will compensate by raising the voltage on the  $V_{\mathbb{C}}$  pin, increasing switch current of the two remaining devices.

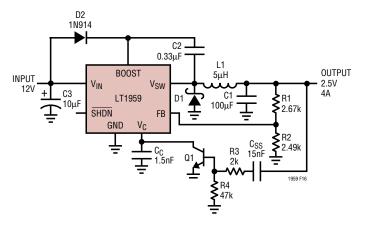

#### **BUCK CONVERTER WITH ADJUSTABLE SOFT START**

Large capacitive loads can cause high input currents at start-up. Figure 16 shows a circuit that limits the dv/dt of the output at start-up, controlling the capacitor charge rate. The buck converter is a typical configuration with the addition of R3, R4,  $C_{SS}$  and Q1. As the output starts to rise, Q1 turns on, regulating switch current via the  $V_{C}$  pin to maintain a constant dv/dt at the output. Output rise time is controlled by the current through  $C_{SS}$  defined by R4 and Q1's  $V_{BE}$ . Once the output is in regulation, Q1 turns off and the circuit operates normally. R3 is transient protection for the base of Q1.

$$RiseTime = \frac{(R4)(C_{SS})(V_{OUT})}{(V_{RF})}$$

Using the values shown in Figure 16,

RiseTime =

$$\frac{(47 \cdot 10^3)(15 \cdot 10^{-9})(2.5)}{0.7}$$

= 2.5ms

The ramp is linear and rise times in the order of 100ms are possible. Since the circuit is voltage controlled, the ramp rate is unaffected by load characteristics and maximum

Figure 16. Buck Converter with Adjustable Soft Start

output current is unchanged. Variants of this circuit can be used for sequencing multiple regulator outputs.

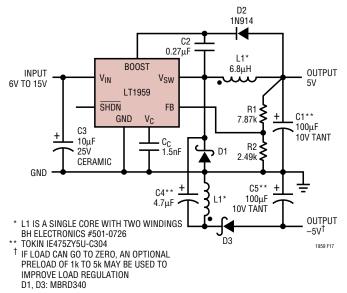

### **Dual Output SEPIC Converter**

The circuit in Figure 17 generates both positive and negative 5V outputs with a single piece of magnetics. The two inductors shown are actually just two windings on a standard B H Electronics inductor. The topology for the 5V output is a standard buck converter. The -5V topology would be a simple flyback winding coupled to the buck converter if C4 were not present. C4 creates a SEPIC (Single-Ended Primary Inductance Converter) topology which improves regulation and reduces ripple current in L1. Without C4, the voltage swing on L1B compared to L1A would vary due to relative loading and coupling losses. C4 provides a low impedance path to maintain an equal voltage swing in L1B, improving regulation. In a flyback converter, during switch on time, all the converter's energy is stroed in L1A only, since no current flows in L1B. At switch off, energy is transferred by magnetic coupling into L1B, powering the -5V rail. C4 pulls L1B positive during switch on time, causing current to flow, and energy to build in L1B and C4. At switch off, the energy stored in both L1B and C4 supply the -5V rail. This reduces the current in L1A and changes L1B current waveform from square to triangular. For details on this circuit see Design Note 100.

Figure 17. Dual Output SEPIC Converter

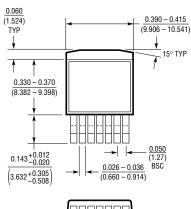

### PACKAGE DESCRIPTION

Dimensions in inches (millimeters) unless otherwise noted.

#### R Package 7-Lead Plastic DD Pak (LTC DWG # 05-08-1462)

$\frac{0.256}{(6.502)}$ 0.060 (1.524) 0.183  $\frac{0.300}{(7.620)}$ BOTTOM VIEW OF DD PAK HATCHED AREA IS SOLDER PLATED COPPER HEAT SINK

#### **S8 Package** 8-Lead Plastic Small Outline (Narrow 0.150) (LTC DWG # 05-08-1610)

$\frac{0.189 - 0.197}{(4.801 - 5.004)}$  $\frac{0.010 - 0.020}{(0.254 - 0.508)}$ 0.053 - 0.069  $(\overline{1.346 - 1.752})$  $\frac{0.004 - 0.010}{(0.101 - 0.254)}$  $\frac{0.008 - 0.010}{(0.203 - 0.254)}$ 0.150 - 0.157\*\* (3.810 - 3.988) 0.228 - 0.2440.016 - 0.050 $(\overline{5.791 - 6.197})$ 0.014 - 0.019 0.050 (0.406 - 1.270) $(\overline{0.355 - 0.483})$  $(\overline{1.270})$ TYP BSC \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE  $\frac{\mathbb{H}}{2}$  $\frac{1}{3}$ \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE S08 1298

# **RELATED PARTS**

| PART NUMBER      | DESCRIPTION                                                     | COMMENTS                             |

|------------------|-----------------------------------------------------------------|--------------------------------------|

| LT1074/LT1076    | Step-Down Switching Regulators                                  | 40V Input, 100kHz, 5A and 2A         |

| LTC®1148/LTC1149 | High Efficiency Synchronous Step-Down Switching Regulator       | External FET Switches                |

| LT1370           | High Efficiency DC/DC Converter                                 | 42V, 6A, 500kHz Switch               |

| LT1371           | High Efficiency DC/DC Converter                                 | 35V, 3A, 500kHz Switch               |

| LT1372/LT1377    | 500kHz and 1MHz High Efficiency 1.5A Switching Regulators       | Boost Topology                       |

| LT1374           | High Efficiency Step-Down Switching Regulator                   | 25V, 4.5A, 500kHz Switch             |

| LT1506           | High Efficiency Step-Down Switching Regulator                   | 15V, 4.5A, 500kHz Switch             |

| LT1624           | N-Channel Switching Regulator Controller                        | SO-8 Package                         |

| LT1625           | NoR <sub>SENSE</sub> ™ Step Down-Switching Regulator Controller | Step-Down, Synchronous               |

| LT1628           | 2-Phase Synchronous Step-Down Switching Regulator Controller    | High Efficiency, Low Ripple          |

| LTC1735          | High Efficiency Step-Down Converter                             | Drives External MOSFETs              |

| LT1775           | High Power NoR <sub>SENSE</sub> Switching Regulator Controller  | Step-Down, Synchronous, Current Mode |

No R<sub>SENSE</sub> is a trademark of Linear Technology Corporation

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

<u>LT1959IR#TRPBF</u> <u>LT1959CR#PBF</u> <u>LT1959CS8#PBF</u> <u>LT1959IS8#PBF</u> <u>LT1959IS8#TRPBF</u> <u>LT1959CR#TRPBF</u> <u>LT1959CR</u>