LT1169

### FEATURES

- Input Bias Current, Warmed Up: 20pA Max

- 100% Tested Low Voltage Noise:  $8nV/\sqrt{Hz}$  Max

- S8 and N8 Package Standard Pinout

- Very Low Input Capacitance: 1.5pF

- Voltage Gain: 1.2 Million Min

- Offset Voltage: 2mV Max

- Input Resistance: 10<sup>13</sup>Ω

- Gain-Bandwidth Product: 5.3MHz Typ

- Guaranteed Specifications with ±5V Supplies

- Guaranteed Matching Specifications

## **APPLICATIONS**

- Photocurrent Amplifiers

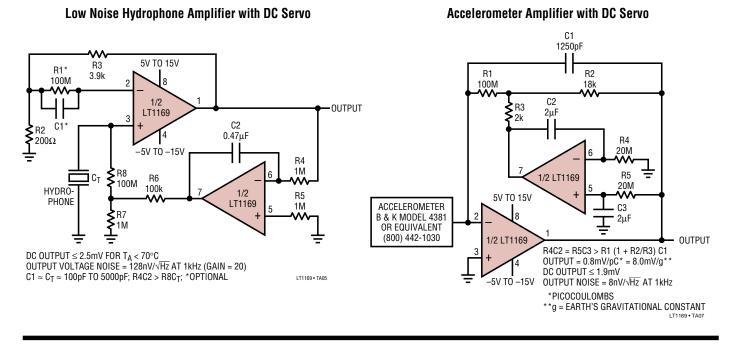

- Hydrophone Amplifiers

- High Sensitivity Piezoelectric Accelerometers

- Low Voltage and Current Noise Instrumentation Amplifier Front Ends

- Two and Three Op Amp Instrumentation Amplifiers

- Active Filters

# Dual Low Noise, Picoampere Bias Current, JFET Input Op Amp

### DESCRIPTION

The LT1169 achieves a new standard of excellence in noise performance for a dual JFET op amp. For the first time low voltage noise (6nV/ $\sqrt{Hz}$ ) is simultaneously offered with extremely low current noise (1fA/ $\sqrt{Hz}$ ), providing the lowest total noise for high impedance transducer applications. Unlike most JFET op amps, the very low input bias current (5pA Typ) is maintained over the entire common mode range which results in an extremely high input resistance (10<sup>13</sup> $\Omega$ ). When combined with a very low input capacitance (1.5pF) an extremely high input impedance results, making the LT1169 the first choice for amplifying low level signals from high impedance transducers. The low input capacitance also assures high gain linearity when buffering AC signals from high impedance transducers.

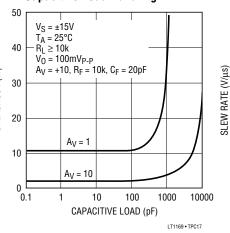

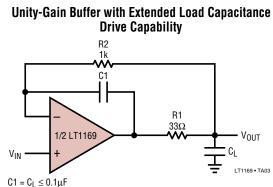

The LT1169 is unconditionally stable for gains of 1 or more, even with 1000pF capacitive loads. Other key features are 0.6mV  $V_{OS}$  and a voltage gain over 4 million. Each individual amplifier is 100% tested for voltage noise, slew rate (4.2V/µs), and gain-bandwidth product (5.3MHz).

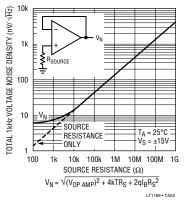

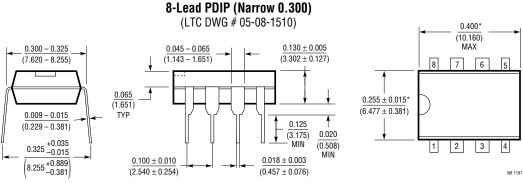

The LT1169 is offered in the S8 and N8 packages.

A full set of matching specifications are provided for precision instrumentation amplifier front ends. Specifications at  $\pm 5V$  supply operation are also provided. For an even lower voltage noise please see the LT1113 data sheet.

$\mathcal{LT}$ , LTC and LT are registered trademarks of Linear Technology Corporation.

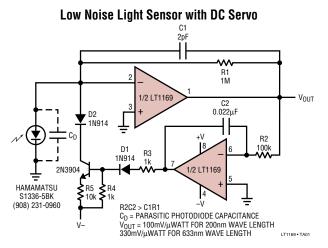

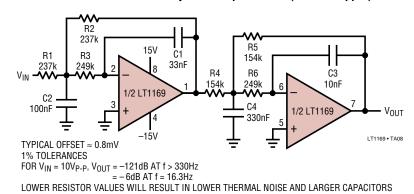

### TYPICAL APPLICATION

### 1kHz Output Voltage Noise Density vs Source Resistance

**LINEAR** TECHNOLOGY

# ABSOLUTE MAXIMUM RATINGS

| Su | nnlv | Vo  | ltage |

|----|------|-----|-------|

| ou | ppiy | • • | itugo |

| –55°C to 105°C                          | ±20V           |

|-----------------------------------------|----------------|

| 105°C to 125°C                          | ±16V           |

| Differential Input Voltage              | ±40V           |

| Input Voltage (Equal to Supply Voltage) |                |

| Output Short-Circuit Duration           | Indefinite     |

| Operating Temperature Range             | -40°C to 85°C  |

| Storage Temperature Range               | -65°C to 150°C |

| Lead Temperature (Soldering, 10 sec)    | 300°C          |

|                                         |                |

# PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

## **ELECTRICAL CHARACTERISTICS** $v_s = \pm 15V$ , $v_{CM} = 0V$ , $T_A = 25^{\circ}C$ , unless otherwise noted.

| SYMBOL             | PARAMETER                        | CONDITIONS (Note 1)                                     | MIN            | ТҮР                                  | MAX     | UNITS             |

|--------------------|----------------------------------|---------------------------------------------------------|----------------|--------------------------------------|---------|-------------------|

| V <sub>0S</sub>    | Input Offset Voltage             |                                                         |                | 0.60                                 | 2.0     | mV                |

|                    |                                  | $V_{S} = \pm 5V$                                        |                | 0.65                                 | 2.2     | mV                |

| l <sub>os</sub>    | Input Offset Current             | Warmed Up (Note 2)                                      |                | 2.5                                  | 15      | рА                |

|                    |                                  | $T_J = 25^{\circ}C$ (Note 5)                            |                | 0.7                                  | 4       | pA                |

| IB                 | Input Bias Current               | Warmed Up (Note 2)<br>T <sub>J</sub> = 25°C (Note 5)    |                | 4.0<br>1.5                           | 20<br>5 | pA<br>pA          |

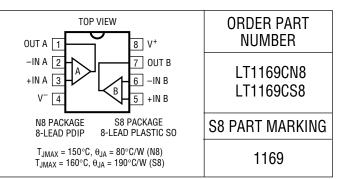

| e <sub>n</sub>     | Input Noise Voltage              | 0.1Hz to 10Hz                                           |                | 2.4                                  | -       | μν <sub>Ρ-Ρ</sub> |

|                    | Input Noise Voltage Density      | $f_0 = 10Hz$<br>$f_0 = 1000Hz$                          |                | 17<br>6                              | 8       | nV/√Hz<br>nV/√Hz  |

| i <sub>n</sub>     | Input Noise Current Density      | $f_0 = 10$ Hz, $f_0 = 1$ kHz (Note 3)                   |                | 1                                    |         | fA/√Hz            |

| R <sub>IN</sub>    | Input Resistance                 |                                                         |                | 14                                   |         |                   |

|                    | Differential Mode<br>Common Mode | V 10V/to 12V                                            |                | 10 <sup>14</sup><br>10 <sup>13</sup> |         | Ω<br>Ω            |

| 0                  |                                  | V <sub>CM</sub> = -10V to 13V                           |                |                                      |         |                   |

| C <sub>IN</sub>    | Input Capacitance                | $V_{\rm S} = \pm 5 V$                                   |                | 1.5<br>2.0                           |         | pF<br>pF          |

| V <sub>CM</sub>    | Input Voltage Range (Note 4)     |                                                         | 13.0           | 13.5                                 |         | V                 |

|                    |                                  |                                                         | -10.5          | -11.0                                |         | V                 |

| CMRR               | Common Mode Rejection Ratio      | $V_{CM} = -10V$ to 13V                                  | 82             | 95                                   |         | dB                |

| PSRR               | Power Supply Rejection Ratio     | $V_{S} = \pm 4.5 V$ to $\pm 20 V$                       | 83             | 98                                   |         | dB                |

| A <sub>VOL</sub>   | Large-Signal Voltage Gain        | $V_0 = \pm 12V, R_L = 10k$<br>$V_0 = \pm 10V, R_L = 1k$ | 1000<br>500    | 4500<br>3000                         |         | V/mV<br>V/mV      |

| V <sub>OUT</sub>   | Output Voltage Swing             | $R_{\rm I} = 10k$                                       | ±13.0          | ±13.8                                |         | V                 |

| V001               | Output voltage Swing             | $R_{L} = 1k$                                            | ±13.0<br>±12.0 | ±13.0                                |         | V V               |

| SR                 | Slew Rate                        | $R_L \ge 2k$ (Note 6)                                   | 2.4            | 4.2                                  |         | V/µs              |

| GBW                | Gain-Bandwidth Product           | f <sub>0</sub> = 100kHz                                 | 3.3            | 5.3                                  |         | MHz               |

|                    | Channel Separation               | $f_0 = 10$ Hz, $V_0 = \pm 10$ V, $R_L = 1$ k            |                | 126                                  |         | dB                |

| Is                 | Supply Current per Amplifier     |                                                         |                | 5.3                                  | 6.50    | mA                |

|                    |                                  | $V_S = \pm 5V$                                          |                | 5.3                                  | 6.45    | mA                |

| $\Delta V_{OS}$    | Offset Voltage Match             |                                                         |                | 0.8                                  | 3.5     | mV                |

| $\Delta I_{B}^{+}$ | Noninverting Bias Current Match  | Warmed Up (Note 2)                                      |                | 3                                    | 20      | pA                |

| ∆CMRR              | Common Mode Rejection Match      | (Note 8)                                                | 78             | 94                                   |         | dB                |

| ∆PSRR              | Power Supply Rejection Match     | (Note 8)                                                | 80             | 95                                   |         | dB                |

# **ELECTRICAL CHARACTERISTICS** $V_{S} = \pm 15V$ , $V_{CM} = 0V$ , $0^{\circ}C \le T_{A} \le 70^{\circ}C$ , (Note 9), unless otherwise noted.

| SYMBOL                              | PARAMETER                          | CONDITIONS (Note 1)                                     |   | MIN            | ТҮР            | MAX          | UNITS        |

|-------------------------------------|------------------------------------|---------------------------------------------------------|---|----------------|----------------|--------------|--------------|

| V <sub>OS</sub>                     | Input Offset Voltage               | $V_{S} = \pm 5V$                                        | • |                | 0.7<br>0.8     | 3.2<br>3.4   | mV<br>mV     |

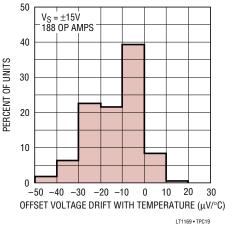

| $\frac{\Delta V_{0S}}{\Delta Temp}$ | Average Input Offset Voltage Drift | (Note 5)                                                | • |                | 20             | 50           | μV/°C        |

| I <sub>OS</sub>                     | Input Offset Current               |                                                         | • |                | 10             | 50           | рА           |

| IB                                  | Input Bias Current                 |                                                         | • |                | 180            | 400          | рА           |

| V <sub>CM</sub>                     | Input Voltage Range                |                                                         | • | 12.9<br>-10.0  | 13.4<br>-10.8  |              | V<br>V       |

| CMRR                                | Common Mode Rejection Ratio        | V <sub>CM</sub> = -10V to 12.9V                         | • | 79             | 94             |              | dB           |

| PSRR                                | Power Supply Rejection Ratio       | $V_{S} = \pm 4.5 V$ to $\pm 20 V$                       | • | 81             | 97             |              | dB           |

| A <sub>VOL</sub>                    | Large-Signal Voltage Gain          | $V_0 = \pm 12V, R_L = 10k$<br>$V_0 = \pm 10V, R_L = 1k$ | • | 800<br>400     | 3400<br>2400   |              | V/mV<br>V/mV |

| V <sub>OUT</sub>                    | Output Voltage Swing               | $R_{L} = 10k$ $R_{L} = 1k$                              | • | ±12.5<br>±11.5 | ±13.5<br>±12.7 |              | V<br>V       |

| SR                                  | Slew Rate                          | $R_L \ge 2k$ (Note 6)                                   | • | 1.9            | 4              |              | V/µs         |

| GBW                                 | Gain-Bandwidth Product             | f <sub>0</sub> = 100kHz                                 | • | 3              | 4.2            |              | MHz          |

| I <sub>S</sub>                      | Supply Current per Amplifier       | $V_{S} = \pm 5V$                                        | • |                | 5.3<br>5.3     | 6.55<br>6.50 | mA<br>mA     |

| $\Delta V_{0S}$                     | Offset Voltage Match               |                                                         | • |                | 1.5            | 5            | mV           |

| $\Delta I_{B}^{+}$                  | Noninverting Bias Current Match    |                                                         | • |                | 5.5            | 50           | рА           |

| $\Delta CMRR$                       | Common Mode Rejection Match        | (Note 8)                                                | • | 74             | 93             |              | dB           |

| ΔPSRR                               | Power Supply Rejection Match       | (Note 8)                                                | • | 77             | 93             |              | dB           |

### $V_S$ = $\pm 15V,~V_{CM}$ = 0V, $-40^\circ C \leq T_A \leq 85^\circ C,$ (Note 7), unless otherwise noted.

| SYMBOL                            | PARAMETER                          | CONDITIONS (Note 1)                                     |   | MIN            | ТҮР            | MAX          | UNITS        |

|-----------------------------------|------------------------------------|---------------------------------------------------------|---|----------------|----------------|--------------|--------------|

| V <sub>OS</sub>                   | Input Offset Voltage               | $V_{S} = \pm 5V$                                        | • |                | 0.8<br>0.9     | 3.8<br>4.0   | mV<br>mV     |

| $\Delta V_{0S} \over \Delta Temp$ | Average Input Offset Voltage Drift |                                                         | • |                | 20             | 50           | μV/°C        |

| I <sub>OS</sub>                   | Input Offset Current               |                                                         | • |                | 30             | 200          | pA           |

| I <sub>B</sub>                    | Input Bias Current                 |                                                         | • |                | 320            | 1200         | рА           |

| V <sub>CM</sub>                   | Input Voltage Range                |                                                         | • | 12.6<br>-10.0  | 13.0<br>-10.5  |              | V<br>V       |

| CMRR                              | Common Mode Rejection Ratio        | V <sub>CM</sub> = -10V to 12.6V                         | • | 78             | 93             |              | dB           |

| PSRR                              | Power Supply Rejection Ratio       | $V_{\rm S}$ = ±4.5V to ±20V                             | • | 79             | 96             |              | dB           |

| A <sub>VOL</sub>                  | Large-Signal Voltage Gain          | $V_0 = \pm 12V, R_L = 10k$<br>$V_0 = \pm 10V, R_L = 1k$ | • | 750<br>300     | 3000<br>2000   |              | V/mV<br>V/mV |

| V <sub>OUT</sub>                  | Output Voltage Swing               | $R_{L} = 10k$ $R_{L} = 1k$                              | • | ±12.5<br>±11.3 | ±12.5<br>±12.0 |              | V<br>V       |

| SR                                | Slew Rate                          | $R_L \ge 2k$                                            | • | 1.8            | 3.8            |              | V/µs         |

| GBW                               | Gain-Bandwidth Product             | f <sub>0</sub> = 100kHz                                 | • | 2.7            | 4              |              | MHz          |

| I <sub>S</sub>                    | Supply Current per Amplifier       | $V_{\rm S} = \pm 5 V$                                   | • |                | 5.30<br>5.25   | 6.55<br>6.50 | mA<br>mA     |

### $\label{eq:constraint} \textbf{ELECTRICAL CHARACTERISTICS} \hspace{0.1 cm} v_{S} = \pm 15 V, \hspace{0.1 cm} v_{CM} = 0 V, \hspace{0.1 cm} -40^{\circ} C \leq T_{A} \leq 85^{\circ} C, \hspace{0.1 cm} (\text{Note 7}), \hspace{0.1 cm} \text{unless otherwise noted}.$

| SYMBOL             | PARAMETER                       | CONDITIONS (Note 1) |   | MIN | ТҮР | MAX | UNITS |

|--------------------|---------------------------------|---------------------|---|-----|-----|-----|-------|

| $\Delta V_{0S}$    | Offset Voltage Match            |                     | • |     | 1.8 | 6   | mV    |

| $\Delta I_{B}^{+}$ | Noninverting Bias Current Match |                     | • |     | 10  | 180 | pA    |

| ∆CMRR              | Common Mode Rejection Match     | (Note 8)            | • | 73  | 93  |     | dB    |

| ΔPSRR              | Power Supply Rejection Match    | (Note 8)            | ٠ | 75  | 92  |     | dB    |

The • denotes specifications which apply over the full operating temperature range.

**Note 1:** Typical parameters are defined as the 60% yield of parameter distributions of individual amplifiers, i.e., out of 100 LT1169s (200 op amps) typically 120 op amps will be better than the indicated specification.

Note 2:  $I_B$  and  $I_{OS}$  readings are extrapolated to a warmed-up temperature from 25°C measurements and 45°C characterization data.

**Note 3:** Current noise is calculated from the formula:

$i_{\rm B} = (2qI_{\rm B})^{1/2}$

where q =  $1.6 \times 10^{-19}$  coulomb. The noise of source resistors up to 200M swamps the contribution of current noise.

**Note 4:** Input voltage range functionality is assured by testing offset voltage at the input voltage range limits to a maximum of 2.8mV. **Note 5:** This parameter is not 100% tested.

Note 6: Slew rate is measured in  $A_V$  = -1; input signal is  $\pm7.5V,$  output measured at  $\pm2.5V.$

**Note 7:** The LT1169 is designed, characterized and expected to meet these extended temperature limits, but is not tested at  $-40^{\circ}$ C and  $85^{\circ}$ C. Guaranteed I grade parts are available; consult factory.

Note 8:  $\triangle$ CMRR and  $\triangle$ PSRR are defined as follows:

- (1) CMRR and PSRR are measured in  $\mu\text{V/V}$  on the individual amplifiers.

- (2) The difference is calculated between the matching sides in  $\mu$ V/V.

- (3) The result is converted to dB.

**Note 9:** The LT1169 is measured in an automated tester in less than one second after application of power. Depending on the package used, power dissipation, heat sinking, and air flow conditions, the fully warmed-up chip temperature can be 10°C to 50°C higher than the ambient temperature.

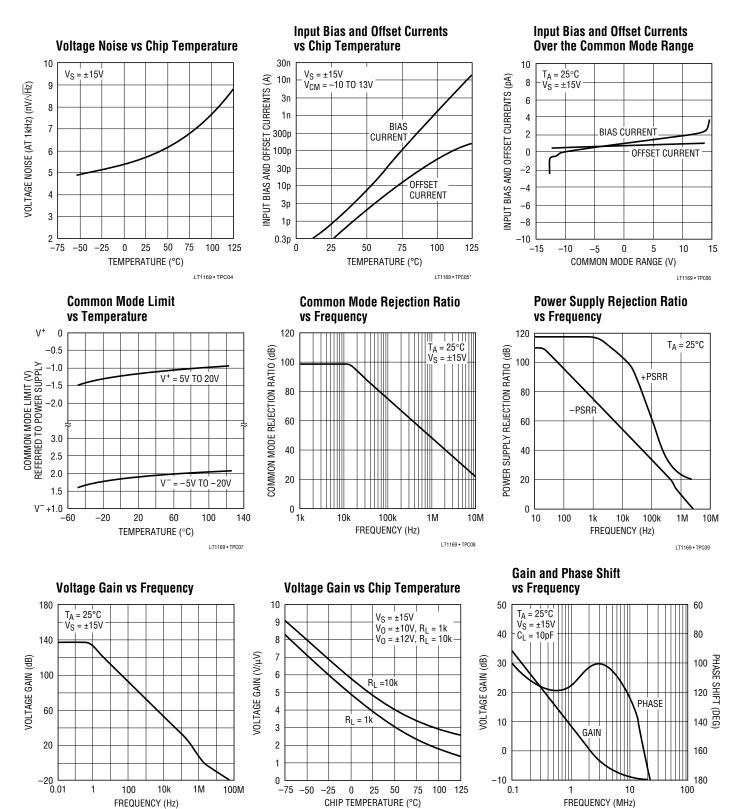

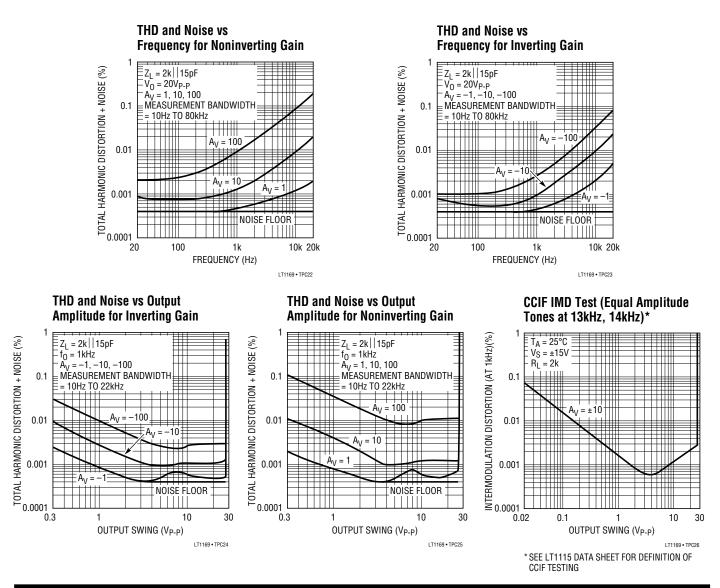

# TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

LT1169 • TPC11

LT1169 • TPC10

LT1169 • TPC12

# TYPICAL PERFORMANCE CHARACTERISTICS

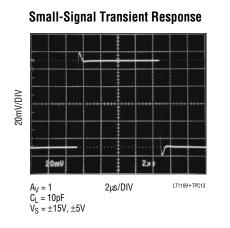

5V/DIV

$A_V = 1$

$C_L = 10 pF$

$V_{S} = \pm 15V$

#### Large-Signal Transient Response

5µs/DIV

LT1169 • TPC14

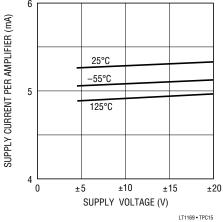

#### Supply Current vs Supply Voltage

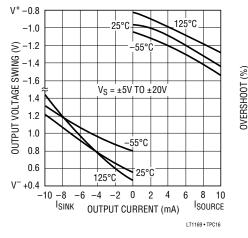

#### Output Voltage Swing vs Load Current

### **Capacitive Load Handling**

Warm-Up Drift

$T_A = 25^{\circ}C$  $V_S = \pm 15V$

N8 PACKAGE

2

3

TIME AFTER POWER ON (MIN)

4

5

LT1169 • TPC20

6

1000

800

600

400

200

0

0

1

CHANGE IN OFFSET VOLTAGE (µV)

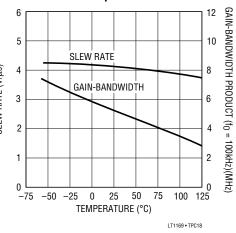

#### Slew Rate and Gain-Bandwidth Product vs Temperature

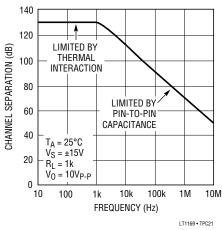

#### **Channel Separation vs Frequency**

## TYPICAL PERFORMANCE CHARACTERISTICS

# **APPLICATIONS INFORMATION**

### LT1169 vs the Competition

With improved noise performance, the LT1169 dual in the plastic DIP directly replaces such JFET op amps as the OPA2111, OPA2604, OP215, and the AD822. The combination of low current and voltage noise of the LT1169 allows it to surpass most dual and single JFET op amps. The LT1169 can replace many of the lowest noise bipolar amps that are used in amplifying low level signals from high impedance transducers. The best bipolar op amps will eventually lose out to the LT1169 when transducer impedance increases due to higher current noise.

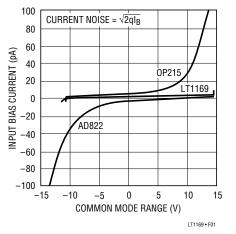

The extremely high input impedance  $(10^{13}\Omega)$  assures that the input bias current is almost constant over the entire common mode range. Figure 1 shows how the LT1169 stands up to the competition. Unlike the competition, as the input voltage is swept across the entire common mode range the input bias current of the LT1169 hardly changes. As a result the current noise does not degrade. This makes the LT1169 the best choice in applications where an amplifier has to buffer signals from a high impedance transducer.

## **APPLICATIONS INFORMATION**

Figure 1. Comparison of LT1169, OP215, and AD822 Input Bias Current vs Common Mode Range

### Amplifying Signals from High Impedance Transducers

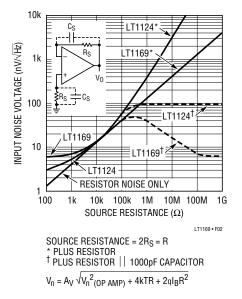

The low voltage and current noise offered by the LT1169 makes it useful in a wide range of applications, especially where high impedance, capacitive transducers are used such as hydrophones, precision accelerometers, and photodiodes. The total output noise in such a system is the gain times the RMS sum of the op amp's input referred voltage noise, the thermal noise of the transducer, and the op amp's input bias current noise times the transducer impedance. Figure 2 shows total input voltage noise versus source resistance. In a low source resistance (<5k) application the op amp voltage noise will dominate

Figure 2. Comparison of LT1169 and LT1124 Total Output 1kHz Voltage Noise vs Source Resistance

the total noise. This means the LT1169 is superior to most dual JFET op amps. Only the lowest noise bipolar op amps have the advantage at low source resistances. As the source resistance increases from 5k to 50k, the LT1169 will match the best bipolar op amps for noise performance, since the thermal noise of the transducer (4kTR) begins to dominate the total noise. A further increase in source resistance, above 50k, is where the op amp's current noise component (2ql<sub>B</sub>R<sup>2</sup>) will eventually dominate the total noise. At these high source resistances, the LT1169 will out perform the lowest noise bipolar op amps due to the inherently low current noise of FET input op amps. Clearly, the LT1169 will extend the range of high impedance transducers that can be used for high signalto-noise ratios. This makes the LT1169 the best choice for high impedance, capacitive transducers.

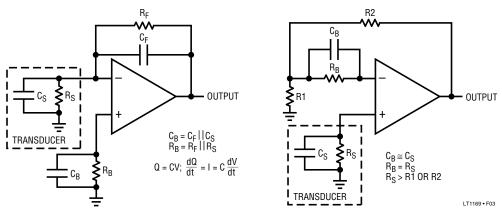

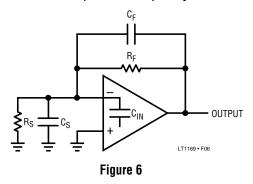

### **Optimization Techniques for Charge Amplifiers**

The high input impedance JFET front end makes the LT1169 suitable in applications where very high charge sensitivity is required. Figure 3 illustrates the LT1169 in its inverting and noninverting modes of operation. A charge amplifier is shown in the inverting mode example; the gain depends on the principal of charge conservation at the input of the LT1169. The charge across the transducer capacitance C<sub>S</sub> is transferred to the feedback capacitor C<sub>F</sub> resulting in a change in voltage dV, which is equal to dQ/C<sub>F</sub>. The gain therefore is 1 + C<sub>F</sub>/C<sub>S</sub>. For unity-gain, the C<sub>F</sub> should equal the transducer capacitance plus the input capacitance of the LT1169 and R<sub>F</sub> should equal R<sub>S</sub>.

In the noninverting mode example, the transducer current is converted to a change in voltage by the transducer capacitance, C<sub>S</sub>. This voltage is then buffered by the LT1169 with a gain of 1 + R1/R2. A DC path is provided by R<sub>S</sub>, which is either the transducer impedance or an external resistor. Since R<sub>S</sub> is usually several orders of magnitude greater than the parallel combination of R1 and R2, R<sub>B</sub> is added to balance the DC offset caused by the noninverting input bias current and R<sub>S</sub>. The input bias currents, although small at room temperature, can create significant errors over increasing temperature, especially with transducer resistances of up to 1000M $\Omega$  or more. The optimum value for R<sub>B</sub> is determined by equating the thermal noise (4kTR<sub>S</sub>) to the current noise (2qI<sub>B</sub>) times R<sub>S</sub><sup>2</sup>. Solving for R<sub>S</sub> results in R<sub>B</sub> = R<sub>S</sub> = 2V<sub>T</sub>/I<sub>B</sub>. A parallel

### **APPLICATIONS INFORMATION**

Figure 3. Inverting and Noninverting Gain Configurations

LT1169 Output

Figure 4. Voltage Follower with Input Exceeding the Common Mode Range (V\_S =  $\pm 5V$ )

capacitor  $C_B$ , is used to cancel the phase shift caused by the op amp input capacitance and  $R_B$ .

### **Reduced Power Supply Operation**

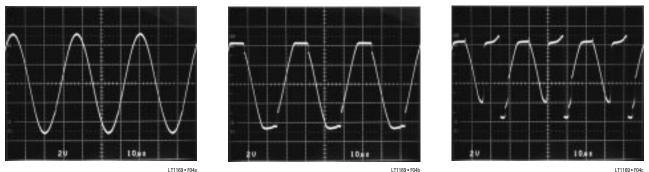

To take full advantage of a wide input common-mode range, the LT1169 was designed to eliminate phase reversal. Referring to the photographs in Figure 4, the LT1169 is shown operating in the follower mode ( $A_V = 1$ ) at  $\pm 5V$  supplies with the input swinging  $\pm 5.2V$ . The output of the LT1169 clips cleanly and recovers with no phase reversal, unlike the competition as shown by the last photograph. This has the benefit of preventing lockup in servo systems and minimizing distortion components. The effect of input and output overdrive on one amplifier has no effect on the other, as each amplifier is biased independently.

### Advantages of Matched Dual Op Amps

In many applications the performance of a system depends on the matching between two operational amplifiers rather than the individual characteristics of the two op

amps. Two or three op amp instrumentation amplifiers, tracking voltage references and low drift active filters are some of the circuits requiring matching between two op amps.

**OPA2111 Output**

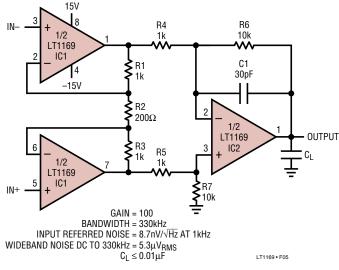

The well-known triple op amp configuration in Figure 5 illustrates these concepts. Output offset is a function of the difference between the two halves of the LT1169. This error cancellation principle holds for a considerable number of input referred parameters in addition to offset voltage and bias current. Input bias current will be the average of the two noninverting input currents  $(I_B^+)$ . The difference between these two currents  $(\Delta I_B^+)$  is the offset current of the instrumentation amplifier. Common-mode and power supply rejections will be dependent only on the match between the two amplifiers (assuming perfect resistor matching).

The concepts of common mode and power supply rejection ratio match ( $\Delta$ CMRR and  $\Delta$ PSRR) are best demonstrated with a numerical example:

# APPLICATIONS INFORMATION

Figure 5. Three Op Amp Instrumentation Amplifier

Assume CMRR<sub>A</sub> =  $50\mu$ V/V or 86dB, and CMRR<sub>B</sub> =  $39\mu$ V/V or 88dB, then  $\Delta$ CMRR =  $11\mu$ V/V or 99dB; if CMRR<sub>B</sub> =  $-39\mu$ V/V which is still 88dB, then  $\Delta$ CMRR =  $89\mu$ V/V or 81dB

By specifying and guaranteeing all of these matching parameters, the LT1169 can significantly improve the performance of matching-dependent circuits.

Typical performance of the instrumentation amplifier:

Input offset voltage = 0.8mV Input bias current = 4pA

# TYPICAL APPLICATIONS

OUTPUT SHORT CIRCUIT CURRENT (~ 30mA) WILL LIMIT THE RATE AT WHICH THE VOLTAGE CAN CHANGE ACROSS LARGE CAPACITORS (I =  $C \frac{dV}{dt}$ )

Input offset current = 3pAInput resistance =  $10^{13}\Omega$ Input noise =  $3.4\mu V_{P-P}$

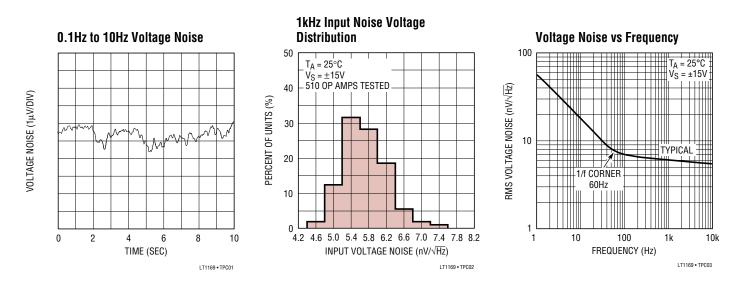

### **High Speed Operation**

The low noise performance of the LT1169 was achieved by enlarging the input JFET differential pair to maximize the first stage gain. Enlarging the JFET geometry also increases the parasitic gate capacitance, which if left unchecked, can result in increased overshoot and ringing. When the feedback around the op amp is resistive ( $R_F$ ), a pole will be created with  $R_F$ , the source resistance and capacitance ( $R_S,C_S$ ), and the amplifier input capacitance ( $C_{IN} = 1.5pF$ ). In closed-loop gain configurations with  $R_S$  and  $R_F$  in the M $\Omega$  range (Figure 6), this pole can create excess phase shift and even oscillation. A small capacitor ( $C_F$ ) in parallel with  $R_F$  eliminates this problem. With  $R_S(C_S + C_{IN}) = R_FC_F$ , the effect of the feedback pole is completely removed.

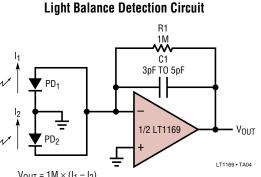

$V_{OUT}$  = 1M  $\times$  (I\_1 – I\_2) PD\_1,PD\_2 = HAMAMATSU S1336-5BK WHEN EQUAL LIGHT ENTERS PHOTODIODES, V\_{OUT} < 3mV.

### **TYPICAL APPLICATIONS**

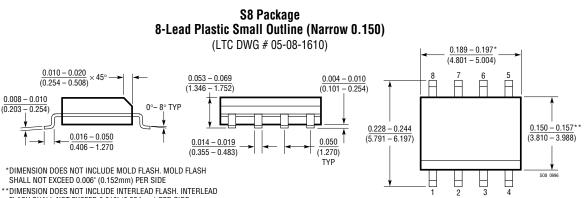

**PACKAGE DESCRIPTION** Dimensions in inches (millimeters) unless otherwise noted.

N8 Package

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

## TYPICAL APPLICATIONS

10Hz Fourth Order Chebyshev Lowpass Filter (0.01dB Ripple)

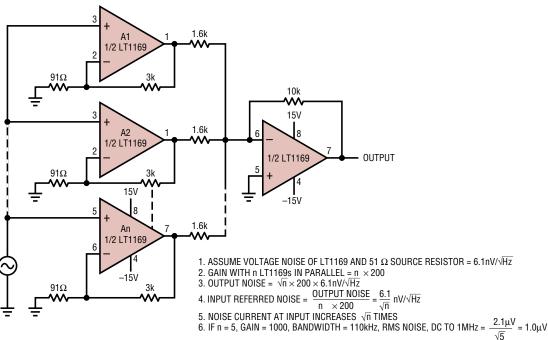

Paralleling Amplifiers to Reduce Voltage Noise

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                   | COMMENTS                                        |  |

|-------------|-------------------------------|-------------------------------------------------|--|

| LT1113      | Lowest Noise Dual JFET Op Amp | 4.5nV/√Hz Voltage Noise                         |  |

| LT1462      | Micro Power Dual JFET Op Amp  | 3.0pA I <sub>B</sub> , 45µA I <sub>SUPPLY</sub> |  |

| LT1464      | Low Power Dual JFET Op Amp    | 3.0pA (Max) Input Bias Current                  |  |

LT1169 • TA06

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.: LT1169CN8#PBF LT1169CS8#TRPBF LT1169CS8#PBF