# Half Bridge N-Channel Power MOSFET Driver

#### **FEATURES**

- Drives Gate of Top Side MOSFET Above V+

- Operates at Supply Voltages from 5V to 30V

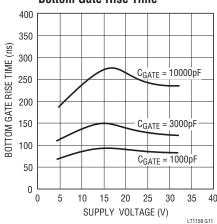

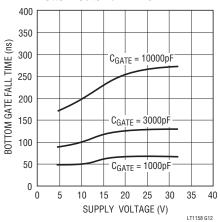

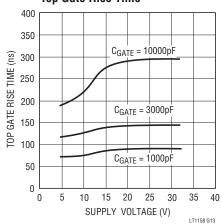

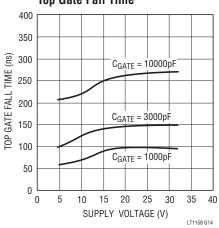

- 150ns Transition Times Driving 3000pF

- Over 500mA Peak Driver Current

- Adaptive Non-Overlap Gate Drives

- Continuous Current Limit Protection

- Auto Shutdown and Retry Capability

- Internal Charge Pump for DC Operation

- Built-In Gate Voltage Protection

- Compatible with Current-Sensing MOSFETs

- TTL/CMOS Input Levels

- Fault Output Indication

#### **APPLICATIONS**

- PWM of High Current Inductive Loads

- Half Bridge and Full Bridge Motor Control

- Synchronous Step-Down Switching Regulators

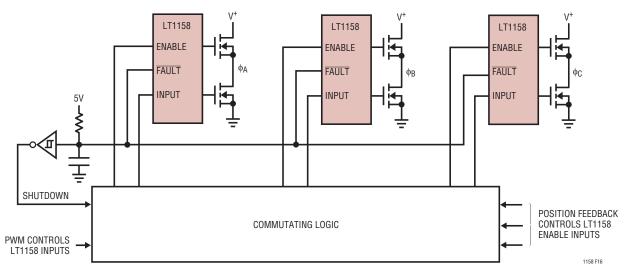

- Three-Phase Brushless Motor Drive

- High Current Transducer Drivers

- Battery-Operated Logic-Level MOSFETs

#### DESCRIPTION

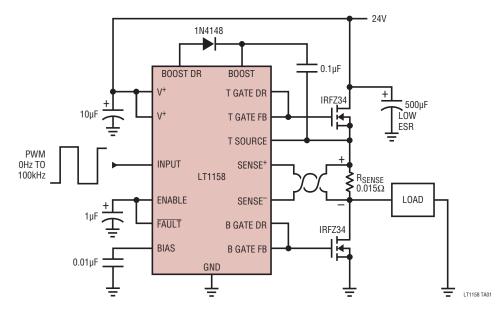

A single input pin on the LT®1158 synchronously controls two N-channel power MOSFETs in a totem pole configuration. Unique adaptive protection against shoot-through currents eliminates all matching requirements for the two MOSFETs. This greatly eases the design of high efficiency motor control and switching regulator systems.

A continuous current limit loop in the LT1158 regulates short-circuit current in the top power MOSFET. Higher start-up currents are allowed as long as the MOSFET  $V_{DS}$  does not exceed 1.2V. By returning the  $\overline{FAULT}$  output to the enable input, the LT1158 will automatically shut down in the event of a fault and retry when an internal pull-up current has recharged the enable capacitor.

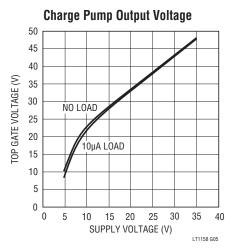

An on-chip charge pump is switched in when needed to turn on the top N-channel MOSFET continuously. Special circuitry ensures that the top side gate drive is safely maintained in the transition between PWM and DC operation. The gate-to-source voltages are internally limited to 14.5V when operating at higher supply voltages.

■ T, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5365119.

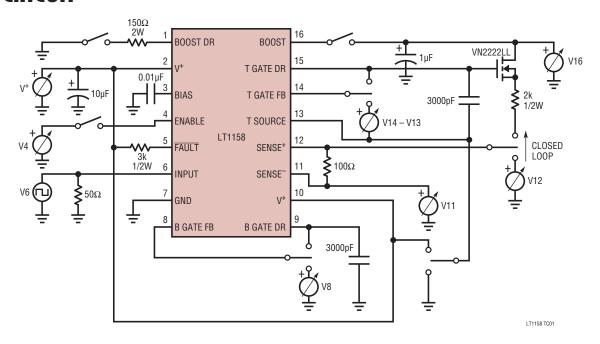

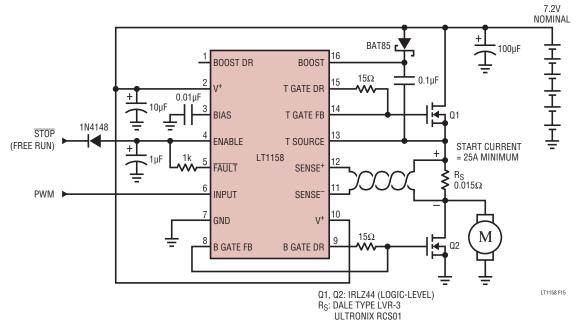

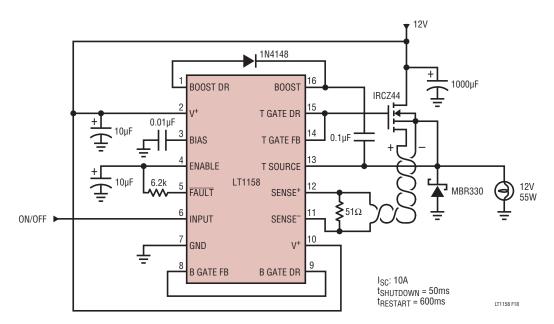

### TYPICAL APPLICATION

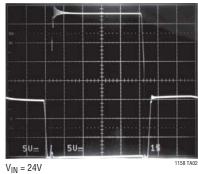

#### **Top and Bottom Gate Waveforms**

$V_{IN} = 24V$  $R_L = 12\Omega$

TECHNOLOGY TECHNOLOGY

#### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Supply Voltage (Pins 2, 10)                | 36V                 |

|--------------------------------------------|---------------------|

| Boost Voltage (Pin 16)                     | 56V                 |

| Continuous Output Currents (Pins 1, 9, 15) | 100mA               |

| Sense Voltages (Pins 11, 12) –5V to        | V+ + 5V             |

| Top Source Voltage (Pin 13) –5V to         | V <sup>+</sup> + 5V |

| Boost to Source Voltage (V16 – V13) –0.3   | V to 20V            |

| Operating Temperature Range       |               |

|-----------------------------------|---------------|

| LT1158C                           | 0°C to 70°C   |

| LT1158I                           | 40°C to 85°C  |

| Junction Temperature (Note 2)     |               |

| LT1158C                           | 125°C         |

| LT1158I                           | 150°C         |

| Storage Temperature Range         | 65°C to 150°C |

| Lead Temperature (Soldering, 10 s | ec.) 300°C    |

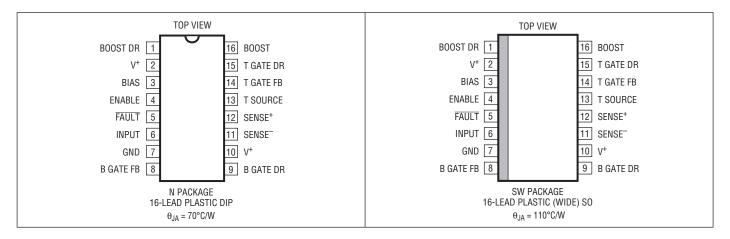

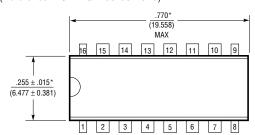

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION       | TEMPERATURE RANGE |

|-------------------|-----------------|---------------|---------------------------|-------------------|

| LT1158CN#PBF      | LT1158CN#TRPBF  |               | 16-Lead Plastic DIP       | 0°C to 70°C       |

| LT1158IN#PBF      | LT1158IN#TRPBF  |               | 16-Lead Plastic DIP       | -40°C to 85°C     |

| LT1158CSW#PBF     | LT1158CSW#TRPBF |               | 16-Lead Plastic (Wide) SO | 0°C to 70°C       |

| LT1158ISW#PBF     | LT1158ISW#TRPBF |               | 16-Lead Plastic (Wide) SO | -40°C to 85°C     |

| LEAD BASED FINISH | TAPE AND REEL   | PART MARKING* | PACKAGE DESCRIPTION       | TEMPERATURE RANGE |

| LT1158CN          | LT1158CN#TR     |               | 16-Lead Plastic DIP       | 0°C to 70°C       |

| LT1158IN          | LT1158IN#TR     |               | 16-Lead Plastic DIP       | -40°C to 85°C     |

| LT1158CSW         | LT1158CSW#TR    |               | 16-Lead Plastic (Wide) SO | 0°C to 70°C       |

| LT1158ISW         | LT1158ISW#TR    |               | 16-Lead Plastic (Wide) SO | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. Test Circuit,  $V^+ = V16 = 12V$ , V11 = V12 = V13 = 0V, Pins 1 and 4 open, Gate Feedback pins connected to Gate Drive pins unless otherwise specified.

|                                  |                                                 | CONDITIONS                                                                                                                           |   | LT1158I    |                |               | LT1158C    |                |               |                |

|----------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---|------------|----------------|---------------|------------|----------------|---------------|----------------|

| SYMBOL                           | PARAMETER                                       |                                                                                                                                      |   | MIN        | TYP            | MAX           | MIN        | TYP            | MAX           | UNITS          |

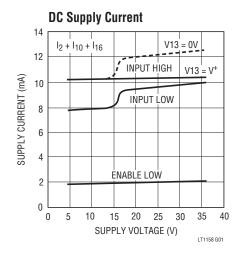

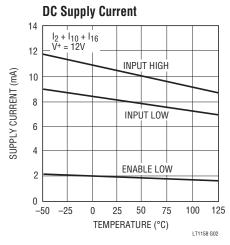

| I <sub>2</sub> + I <sub>10</sub> | DC Supply Current (Note 2)                      | V <sup>+</sup> = 30V, V16 = 15V, V4 = 0.5V<br>V <sup>+</sup> = 30V, V16 = 15V, V6 = 0.8V<br>V <sup>+</sup> = 30V, V16 = 15V, V6 = 2V |   | 4.5<br>8   | 2.2<br>7<br>13 | 3<br>10<br>18 | 4.5<br>8   | 2.2<br>7<br>13 | 3<br>10<br>18 | mA<br>mA<br>mA |

| I <sub>16</sub>                  | Boost Current                                   | V+ = V13 = 30V, V16 = 45V, V6 = 0.8V                                                                                                 |   |            | 3              | 4.5           |            | 3              | 4.5           | mA             |

| V6                               | Input Threshold                                 |                                                                                                                                      | • | 0.8        | 1.4            | 2             | 0.8        | 1.4            | 2             | V              |

| I <sub>6</sub>                   | Input Current                                   | V6 = 5V                                                                                                                              | • |            | 5              | 15            |            | 5              | 15            | μА             |

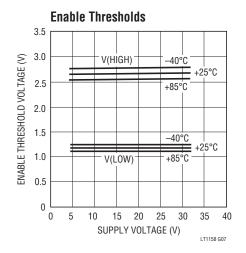

| V4                               | Enable Low Threshold                            | V6 = 0.8V, Monitor V9                                                                                                                | • | 0.9        | 1.15           | 1.4           | 0.85       | 1.15           | 1.4           | V              |

| ΔV4                              | Enable Hysteresis                               | V6 = 0.8V, Monitor V9                                                                                                                | • | 1.3        | 1.5            | 1.7           | 1.2        | 1.5            | 1.8           | V              |

| I <sub>4</sub>                   | Enable Pullup Current                           | V4 = 0V                                                                                                                              | • | 15         | 25             | 35            | 15         | 25             | 35            | μA             |

| V15                              | Charge Pump Voltage                             | $V^+$ = 5V, V6 = 2V, Pin 16 open, V13 $\rightarrow$ 5V $V^+$ = 30V, V6 = 2V, Pin16 open, V13 $\rightarrow$ 30V                       | • | 9<br>40    | 11<br>43       | 47            | 9<br>40    | 11<br>43       | 47            | V              |

| V9                               | Bottom Gate "ON" Voltage                        | V+ = V16 = 18V, V6 = 0.8V                                                                                                            | • | 12         | 14.5           | 17            | 12         | 14.5           | 17            | V              |

| V1                               | Boost Drive Voltage                             | V <sup>+</sup> = V16 = 18V, V6 = 0.8V, 100mA Pulsed Load                                                                             | • | 12         | 14.5           | 17            | 12         | 14.5           | 17            | V              |

| V14 – V13                        | Top Turn-Off Threshold                          | V+ = V16 = 5V, V6 = 0.8V                                                                                                             |   | 1          | 1.75           | 2.5           | 1          | 1.75           | 2.5           | V              |

| V8                               | Bottom Turn-Off Threshold                       | V+ = V16 = 5V, V6 = 2V                                                                                                               |   | 1          | 1.5            | 2             | 1          | 1.5            | 2             | V              |

| I <sub>5</sub>                   | Fault Output Leakage                            | V+ = 30V, V16 = 15V, V6 = 2V                                                                                                         | • |            | 0.1            | 1             |            | 0.1            | 1             | μА             |

| V5                               | Fault Output Saturation                         | V <sup>+</sup> = 30V, V16 = 15V, V6 = 2V, I <sub>5</sub> = 10mA                                                                      |   |            | 0.5            | 1             |            | 0.5            | 1             | V              |

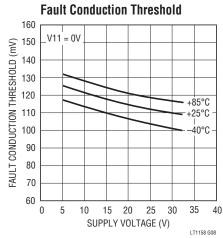

| V12 – V11                        | Fault Conduction Threshold                      | $V^{+} = 30V$ , $V16 = 15V$ , $V6 = 2V$ , $I_{5} = 100\mu A$                                                                         |   | 90         | 110            | 130           | 85         | 110            | 135           | mV             |

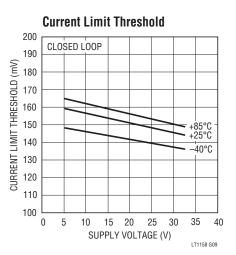

| V12 – V11                        | Current Limit Threshold                         | V <sup>+</sup> = 30V, V16 = 15V, V6 = 2V, Closed Loop                                                                                | • | 130<br>120 | 150            | 170<br>180    | 120<br>120 | 150            | 180<br>180    | mV<br>mV       |

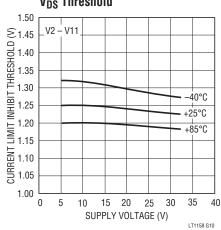

| V12 – V11                        | Current Limit Inhibit V <sub>DS</sub> Threshold | V <sup>+</sup> = V12 = 12V, V6 = 2V, Decrease V11<br>Until V15 Goes Low                                                              |   | 1.1        | 1.25           | 1.4           | 1.1        | 1.25           | 1.4           | V              |

| t <sub>R</sub>                   | Top Gate Rise Time                              | Pin 6 (+) Transition, Meas. V15 – V13 (Note 4)                                                                                       | • |            | 130            | 250           |            | 130            | 250           | ns             |

| t <sub>D</sub>                   | Top Gate Turn-Off Delay                         | Pin 6 (-) Transition, Meas. V15 - V13 (Note 4)                                                                                       | • |            | 350            | 550           |            | 350            | 550           | ns             |

| t <sub>F</sub>                   | Top Gate Fall Time                              | Pin 6 (-) Transition, Meas. V15 - V13 (Note 4)                                                                                       | • |            | 120            | 250           |            | 120            | 250           | ns             |

| t <sub>R</sub>                   | Bottom Gate Rise Time                           | Pin 6 (-) Transition, Meas. V9 (Note 4)                                                                                              | • |            | 130            | 250           |            | 130            | 250           | ns             |

| t <sub>D</sub>                   | Bottom Gate Turn-Off Delay                      | Pin 6 (+) Transition, Meas. V9 (Note 4)                                                                                              | • |            | 200            | 400           |            | 200            | 400           | ns             |

| t <sub>F</sub>                   | Bottom Gate Fall Time                           | Pin 6 (+) Transition, Meas. V9 (Note 4)                                                                                              | • |            | 100            | 200           |            | 100            | 200           | ns             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:**  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formulas:

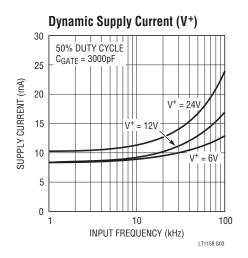

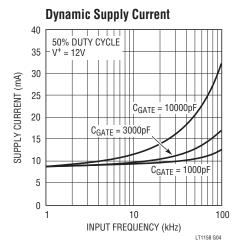

LT1158IN, LT1158CN:  $T_J = T_A + (P_D \times 70^{\circ}\text{C/W})$ LT1158ISW, LT1158CSW:  $T_J = T_A + (P_D \times 110^{\circ}\text{C/W})$  **Note 3:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency. See typical performance characteristics and applications information.

**Note 4:** Gate rise times are measured from 2V to 10V, delay times are measured from the input transition to when the gate voltage has decreased to 10V, and fall times are measured from 10V to 2V.

#### TYPICAL PERFORMANCE CHARACTERISTICS

1158fb

# TYPICAL PERFORMANCE CHARACTERISTICS

#### **Current Limit Inhibit V<sub>DS</sub>** Threshold

# **Bottom Gate Rise Time**

#### **Bottom Gate Fall Time**

#### **Top Gate Rise Time**

#### **Top Gate Fall Time**

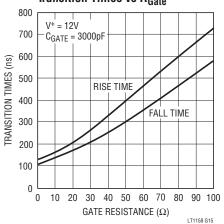

#### Transition Times vs R<sub>Gate</sub>

#### PIN FUNCTIONS

**BOOST DR (Pin 1):** Recharges and clamps the bootstrap capacitor to 14.5V higher than pin 13 via an external diode.

**V**<sup>+</sup> (**Pin 2**): Main supply pin; must be closely decoupled to the ground pin 7.

**BIAS (Pin 3):** Decouple point for the internal 2.6V bias generator. Pin 3 cannot have any external DC loading.

**ENABLE (Pin 4):** When left open, the LT1158 operates normally. Pulling pin 4 low holds both MOSFETs off regardless of the input state.

**FAULT (Pin 5):** Open collector NPN output which turns on when V12 – V11 exceeds the fault conduction threshold.

**INPUT (Pin 6):** Taking pin 6 high turns the top MOSFET on and bottom MOSFET off; pin 6 low reverses these states. An input latch captures each low state, ignoring an ensuing high until pin 13 has gone below 2.6V.

**B GATE FB (Pin 8):** Must connect directly to the bottom power MOSFET gate. The top MOSFET turn-on is inhibited until pin 8 has discharged to 1.5V. A hold-on current source also feeds the bottom gate via pin 8.

**B GATE DR (Pin 9):** The high current drive point for the bottom MOSFET. When a gate resistor is used, it is inserted between pin 9 and the gate of the MOSFET.

**V**<sup>+</sup> (**Pin 10**): Bottom side driver supply; must be connected to the same supply as pin 2.

**SENSE**<sup>-</sup> (**Pin 11**): The floating reference for the current limit comparator. Connects to the low side of a current shunt or Kelvin lead of a current-sensing MOSFET. When pin 11 is within 1.2V of V<sup>+</sup>, current limit is inhibited.

**SENSE**<sup>+</sup> (**Pin 12**): Connects to the high side of the current shunt or sense lead of a current-sensing MOSFET. A built-in offset between pins 11 and 12 in conjunction with RSENSE sets the top MOSFET short-circuit current.

**T SOURCE (Pin 13):** Top side driver return; connects to MOSFET source and low side of the bootstrap capacitor.

**T GATE FB (Pin 14):** Must connect directly to the top power MOSFET gate. The bottom MOSFET turn-on is inhibited until V14 – V13 has discharged to 1.75 V. An on-chip charge pump also feeds the top gate via pin 14.

**T GATE DR (Pin 15):** The high current drive point for the top MOSFET. When a gate resistor is used, it is inserted between pin 15 and the gate of the MOSFET.

**BOOST (Pin 16):** Top side driver supply; connects to the high side of the bootstrap capacitor and to a diode either from supply  $(V^+ < 10V)$  or from pin 1  $(V^+ > 10V)$ .

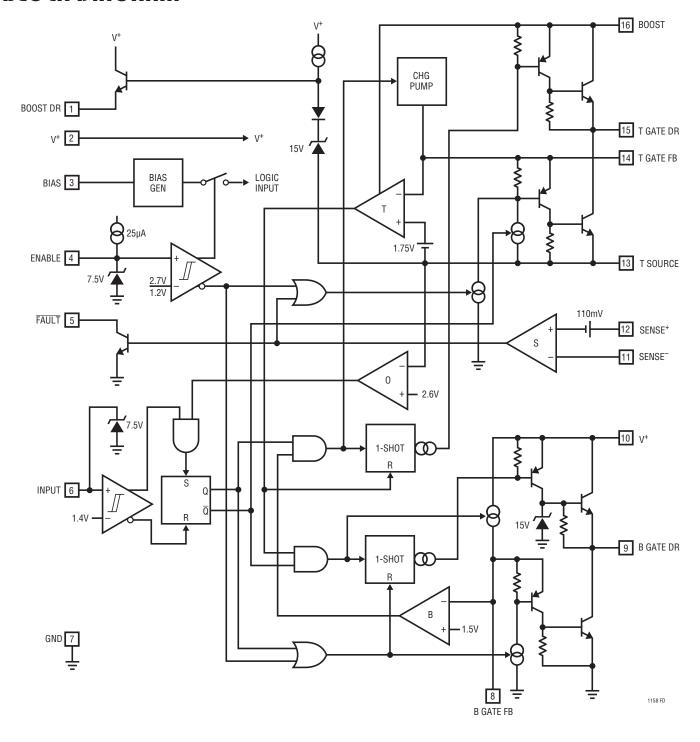

# **BLOCK DIAGRAM**

#### **TEST CIRCUIT**

# **OPERATION** (Refer to Functional Diagram)

The LT1158 self-enables via an internal  $25\mu A$  pull-up on the enable pin 4. When pin 4 is pulled down, much of the input logic is disabled, reducing supply current to 2mA. With pin 4 low, the input state is ignored and both MOSFET gates are actively held low. With pin 4 enabled, one or the other of the 2 MOSFETs is turned on, depending on the state of the input pin 6: high for top side on, and low for bottom side on. The 1.4V input threshold is regulated and has 200mV of hysteresis.

In order to allow operation over 5V to 30V nominal supply voltages, an internal bias generator is employed to furnish constant bias voltages and currents. The bias generator is decoupled at pin 3 to eliminate any effects from switching transients. *No DC loading is allowed on pin 3*.

The top and bottom gate drivers in the LT1158 each utilize two gate connections: 1) A gate drive pin, which provides the turn-on and turn-off currents through an optional series gate resistor; and 2) A gate feedback pin which connects directly to the gate to monitor the gate-to-source voltage and supply the DC gate sustaining current.

Whenever there is an input transition on pin 6, the LT1158 follows a logical sequence to turn off one MOSFET and turn on the other. First, turn-off is initiated, then  $V_{GS}$  is monitored until it has decreased below the turn-off threshold, and finally the other gate is turned on. An input latch gets reset by every low state at pin 6, but can only be set if the top source pin has gone low, indicating that there will be sufficient charge in the bootstrap capacitor to safely turn on the top MOSFET.

In order to conserve power, the gate drivers only provide turn-on current for up to  $2\mu s$ , set by internal one-shot circuits. Each LT1158 driver can deliver 500mA for  $2\mu s$ , or 1000nC of gate charge—more than enough to turn on multiple MOSFETs in parallel. Once turned on, each gate is held high by a DC gate sustaining current: the bottom gate by a  $100\mu A$  current source, and the top gate by an on-chip charge pump running at approximately 500kHz.

The floating supply for the top side driver is provided by a bootstrap capacitor between the boost pin 16 and top source pin 13. This capacitor is recharged each time pin 13

LINEAR TECHNOLOGY

#### **OPERATION** (Refer to Functional Diagram)

goes low in PWM operation, and is maintained by the charge pump when the top MOSFET is on DC. A regulated boost driver at pin 1 employs a source-referenced 15V clamp that prevents the bootstrap capacitor from overcharging regardless of V<sup>+</sup> or output transients.

The LT1158 provides a current-sense comparator and fault output circuit for protection of the top power MOSFET. The

comparator input pins 11 and 12 are normally connected across a shunt in the source of the top power MOSFET (or to a current-sensing MOSFET). When pin 11 is more than 1.2V below V<sup>+</sup> and V12 – V11 exceeds the 110mV offset, FAULT pin 5 begins to sink current. During a short circuit, the feedback loop regulates V12 – V11 to 150mV, thereby limiting the top MOSFET current.

#### **APPLICATIONS INFORMATION**

#### **Power MOSFET Selection**

Since the LT1158 inherently protects the top and bottom MOSFETs from simultaneous conduction, there are no size or matching constraints. Therefore selection can be made based on the operating voltage and  $R_{DS(0N)}$  requirements. The MOSFET  $BV_{DSS}$  should be at least 2  $\bullet$   $V_{SUPPLY}$ , and should be increased to 3  $\bullet$   $V_{SUPPLY}$  in harsh environments with frequent fault conditions. For the LT1158 maximum operating supply of 30V, the MOSFET  $BV_{DSS}$  should be from 60V to 100V.

The MOSFET  $R_{DS(ON)}$  is specified at  $T_J = 25^{\circ}C$  and is generally chosen based on the operating efficiency required as long as the maximum MOSFET junction temperature is not exceeded. The dissipation in each MOSFET is given by:

$$P = D(I_{DS})^{2}(1+\partial)R_{DS(ON)}$$

where D is the duty cycle and  $\partial$  is the increase in  $R_{DS(ON)}$  at the anticipated MOSFET junction temperature. From this equation the required  $R_{DS(ON)}$  can be derived:

$$R_{DS(ON)} = \frac{P}{D(I_{DS})^2 (1+\partial)}$$

For example, if the MOSFET loss is to be limited to 2W when operating at 5A and a 90% duty cycle, the required  $R_{DS(ON)}$  would be  $0.089\Omega/(1+\partial)$ .  $(1+\partial)$  is given for each MOSFET in the form of a normalized  $R_{DS(ON)}$  vs temperature curve, but  $\partial=0.007/^{\circ}C$  can be used as an approximation for low voltage MOSFETs. Thus if  $T_{A}=85^{\circ}C$

and the available heat sinking has a thermal resistance of 20°C/W, the MOSFET junction temperature will be 125°C, and  $\partial$  = 0.007(125 – 25) = 0.7. This means that the required R<sub>DS(ON)</sub> of the MOSFET will be 0.089 $\Omega$ /1.7 = 0.0523 $\Omega$ , which can be satisfied by an IRFZ34.

Note that these calculations are for the continuous operating condition; power MOSFETs can sustain far higher dissipations during transients. Additional  $R_{DS(0N)}$ ) constraints are discussed under Starting High In-Rush Current Loads.

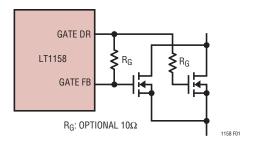

Figure 1. Paralleling MOSFETs

#### Paralleling MOSFETs

MOSFETs can be paralleled. The MOSFETs will inherently share the currents according to their R<sub>DS(ON)</sub> ratio. The LT1158 top and bottom drivers can each drive four power MOSFETs in parallel with only a small loss in switching speeds (see Typical Performance Characteristics). Individual gate resistors may be required to "decouple" each MOSFET from its neighbors to prevent high frequency oscillations—consult manufacturer's recommendations.

If individual gate decoupling resistors are used, the gate feedback pins can be connected to any one of the gates.

Driving multiple MOSFETs in parallel may restrict the operating frequency at high supply voltages to prevent over-dissipation in the LT1158 (see Gate Charge and Driver Dissipation below). When the total gate capacitance exceeds 10,000pF on the top side, the bootstrap capacitor should be increased proportionally above 0.1µF.

#### **Gate Charge and Driver Dissipation**

A useful indicator of the load presented to the driver by a power MOSFET is the total gate charge  $Q_G$ , which includes the additional charge required by the gate-to-drain swing.  $Q_G$  is usually specified for  $V_{GS} = 10V$  and  $V_{DS} = 0.8V_{DS(MAX)}$ .

When the supply current is measured in a switching application, it will be larger than given by the DC electrical characteristics because of the additional supply current associated with sourcing the MOSFET gate charge:

$$I_{SUPPLY} = I_{DC} + \left(\frac{dQ_G}{dt}\right)_{TOP} + \left(\frac{dQ_G}{dt}\right)_{BOTTOM}$$

The actual increase in supply current is slightly higher due to LT1158 switching losses and the fact that the gates are being charged to more than 10V. Supply current vs switching frequency is given in the Typical Performance Characteristics.

The LT1158 junction temperature can be estimated by using the equations given in Note 1 of the electrical characteristics. For example, the LT1158SI is limited to less than 25mA from a 24V supply:

In order to prevent the maximum junction temperature from being exceeded, the LT1158 supply current must be checked with the actual MOSFETs operating at the maximum switching frequency.

#### **MOSFET Gate Drive Protection**

For supply voltages of over 8V, the LT1158 will protect standard N-channel MOSFETs from under or overvoltage gate drive conditions for any input duty cycle including DC. Gate-to-source Zener clamps are not required and not recommended since they can reduce operating efficiency.

A discontinuity in tracking between the output pulse width and input pulse width may be noted as the top side MOSFET approaches 100% duty cycle. As the input low signal becomes narrower, it may become shorter than the time required to recharge the bootstrap capacitor to a safe voltage for the top side driver. Below this duty cycle the output pulse width will stop tracking the input until the input low signal is <100ns, at which point the output will jump to the DC condition of top MOSFET "on" and bottom MOSFET "off."

#### **Low Voltage Operation**

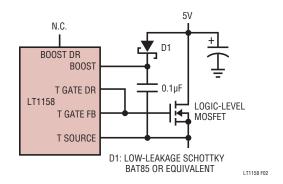

The LT1158 can operate from 5V supplies (4.5V min) and in 6V battery-powered applications by using logic-level N-channel power MOSFETs. These MOSFETs have 2V maximum threshold voltages and guaranteed  $R_{DS(ON)}$  limits at  $V_{GS} = 4 \text{V}$ . The switching speed of the LT1158, unlike CMOS drivers, does not degrade at low supply voltages. For operation down to 4.5V, the boost pin should be connected as shown in Figure 2 to maximize gate drive to the top side MOSFET. Supply voltages over 10V should not be used with logic-level MOSFETs because of their lower maximum gate-to-source voltage rating.

Figure 2. Low Voltage Operation

TECHNOLOGY TECHNOLOGY

#### **Ugly Transient Issues**

In PWM applications the drain current of the top MOSFET is a square wave at the input frequency and duty cycle. To prevent large voltage transients at the top drain, a low ESR electrolytic capacitor must be used and returned to the power ground. The capacitor is generally in the range of  $250\mu\text{F}$  to  $5000\mu\text{F}$  and must be physically sized for the RMS current flowing in the drain to prevent heating and premature failure. In addition, the LT1158 requires a separate  $10\mu\text{F}$  capacitor connected closely between pins 2 and 7.

The LT1158 top source and sense pins are internally protected against transients below ground and above supply. However, the gate drive pins cannot be forced below ground. In most applications, negative transients coupled from the source to the gate of the top MOSFET do not cause any problems. However, in some high current (10A and above) motor control applications, negative transients on the top gate drive may cause early tripping of the current limit. A small Schottky diode (BAT85) from pin 15 to ground avoids this problem.

#### **Switching Regulator Applications**

The LT1158 is ideal as a synchronous switch driver to improve the efficiency of step-down (buck) switching

regulators. Most step-down regulators use a high current Schottky diode to conduct the inductor current when the switch is off. The fractions of the oscillator period that the switch is on (switch conducting) and off (diode conducting) are given by:

SWITCH "ON" =

$$\left(\frac{V_{OUT}}{V_{IN}}\right)$$

• TOTAL PERIOD

SWITCH "OFF" =  $\left(\frac{V_{IN} - V_{OUT}}{V_{IN}}\right)$  • TOTAL PERIOD

Note that for  $V_{IN} > 2V_{OUT}$ , the switch is off longer than it is on, making the diode losses more significant than the switch. The worst case for the diode is during a short circuit, when  $V_{OUT}$  approaches zero and the diode conducts the short-circuit current almost continuosly.

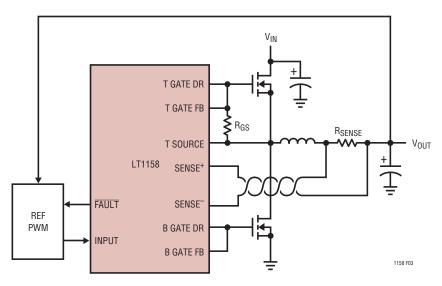

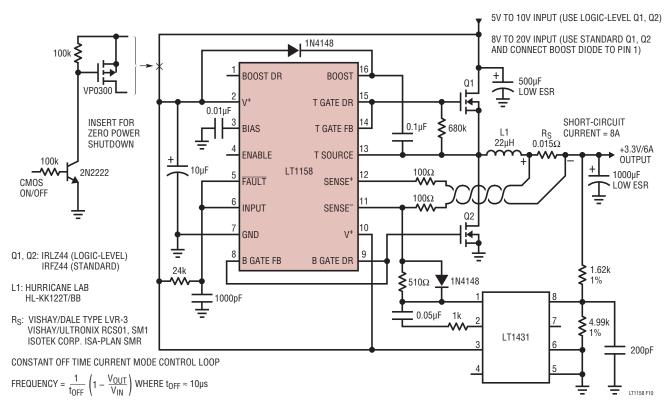

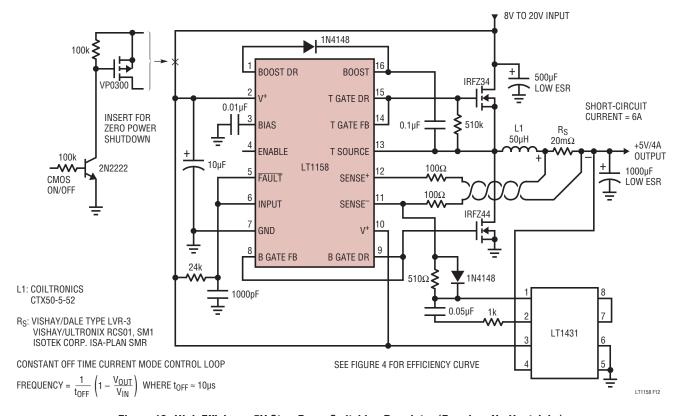

Figure 3 shows the LT1158 used to synchronously drive a pair of power MOSFETs in a step-down regulator application, where the top MOSFET is the switch and the bottom MOSFET replaces the Schottky diode. Since both conduction paths have low losses, this approach can result in very high efficiency—from 90% to 95% in most applications. And for regulators under 5A, using low  $R_{DS(ON)}$  N-channel MOSFETs eliminates the need for heatsinks.

Figure 3. Adding Synchronous Switching to a Step-Down Switching Regulator

Figure 4. Typical Efficiency Curve for Step-Down Regulator with Synchronous Switch

One fundamental difference in the operation of a step-down regulator with synchronous switching is that it never becomes discontinuous at light loads. The inductor current doesn't stop ramping down when it reaches zero, but actually reverses polarity resulting in a constant ripple current independent of load. This does not cause any efficiency loss as might be expected, since the negative inductor current is returned to  $V_{\text{IN}}$  when the switch turns back on.

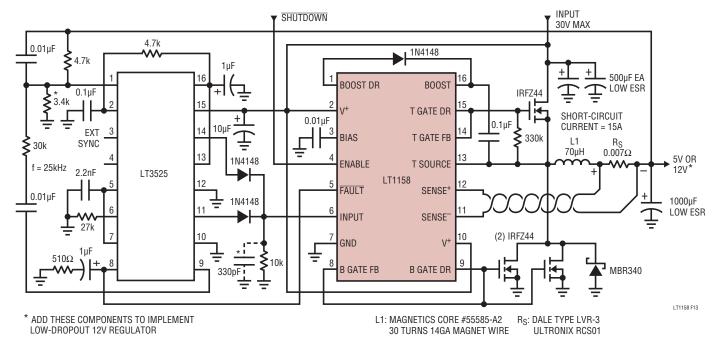

The LT1158 performs the synchronous MOSFET drive and current sense functions in a step-down switching regulator. A reference and PWM are required to complete the regulator. Any voltage-mode PWM controller may be used, but the LT3525 is particularly well suited to high power, high efficiency applications such as the 10A circuit shown in Figure 13. In higher current regulators a small Schottky diode across the bottom MOSFET helps to reduce reverse-recovery switching losses.

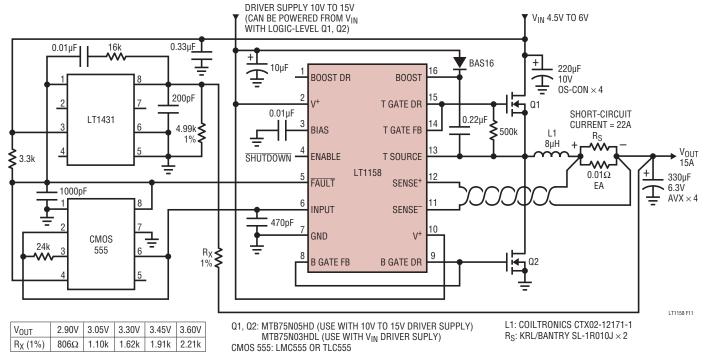

The LT1158 input pin can also be driven directly with a ramp or sawtooth. In this case, the DC level of the input waveform relative to the 1.4V threshold sets the LT1158 duty cycle. In the 5V to 3.3V converter circuit shown in Figure 11, an LT1431 controls the DC level of a triangle wave generated by a CMOS 555. The Figure 10 and 12 circuits use an RC network to ramp the LT1158 input back up to its 1.4V threshold following each switch cycle, setting a constant off time. Figure 4 shows the efficiency vs output current for the Figure 12 regulator with  $V_{\text{IN}} = 12V$ .

#### **Current Limit in Switching Regulator Applications**

Current is sensed by the LT1158 by measuring the voltage across a current shunt (low valued resistor). Normally, this shunt is placed in the source lead of the top MOSFET (see Short-Circuit Protection in Bridge Applications). However, in step-down switching regulator applications, the remote current sensing capability of the LT1158 allows the actual inductor current to be sensed. This is done by placing the shunt in the output lead of the inductor as shown in Figure 3. Routing of the SENSE<sup>+</sup> and SENSE<sup>-</sup> PC traces is critical to prevent stray pickup. These traces must be routed together at minimum spacing and use a Kelvin connection at the shunt.

When the voltage across  $R_{SENSE}$  exceeds 110mV, the LT1158 FAULT pin begins to conduct. By feeding the FAULT signal back to a control input of the PWM, the LT1158 will assume control of the duty cycle forming a true current mode loop to limit the output current:

$$I_{OUT} = \frac{110mV}{R_{SENSE}}$$

in current limit

In LT3525 based circuits, connecting the FAULT pin to the LT3525 soft-start pin accomplishes this function. In circuits where the LT1158 input is being driven with a ramp or sawtooth, the FAULT pin is used to pull down the DC level of the input.

The constant off-time circuits shown in Figures 10 and 12 are unique in that they also use the current sense during normal operation. The LT1431 output reduces the normal LT1158 110mV fault conduction threshold such that the FAULT pin conducts at the required load current, thus discharging the input ramp capacitor. In current limit the LT1431 output turns off, allowing the fault conduction threshold to reach its normal value.

The resistor  $R_{GS}$  shown in Figure 3 is necessary to prevent output voltage overshoot due to charge coupled into the gate of the top MOSFET by a large start-up dv/dt on  $V_{IN}$ . If DC operation of the top MOSFET is required,  $R_{GS}$  must be 330k or greater to prevent loading the charge pump.

TECHNOLOGY TECHNOLOGY

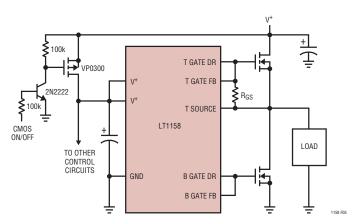

#### Low Current Shutdown

The LT1158 may be shutdown to a current level of 2mA by pulling the enable pin 4 low. In this state both the top and bottom MOSFETs are actively held off against any transients which might occur on the output during shutdown. This is important in applications such as 3-phase DC motor control when one of the phases is disabled while the other two are switching.

If zero standby current is required and the load returns to ground, then a switch can be inserted into the supply path of the LT1158 as shown in Figure 5. Resistor  $R_{GS}$  ensures that the top MOSFET gate discharges, while the voltage across the bottom MOSFET goes to zero. The voltage drop across the P-channel supply switch must be less than 300mV, and  $R_{GS}$  must be 330k or greater for DC operation. This technique is not recommended for applications which require the LT1158  $V_{DS}$  sensing function.

Figure 5. Adding Zero Current Shutdown

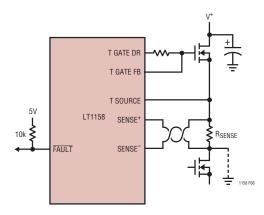

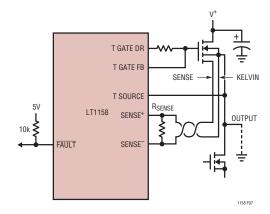

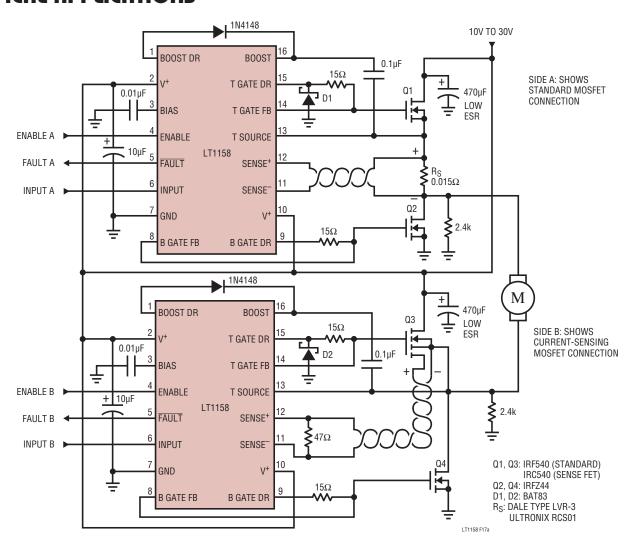

#### **Short-Circuit Protection in Bridge Applications**

The LT1158 protects the top power MOSFET from output shorts to ground, or in a full bridge application, shorts across the load. Both standard 3-lead MOSFETs and current-sensing 5-lead MOSFETs can be protected. The bottom MOSFET is not protected from shorts to supply.

Current is sensed by measuring the voltage across a current shunt in the source lead of a standard 3-lead MOSFET

(Figure 6). For the current-sensing MOSFET shown in Figure 7, the sense resistor is inserted between the sense and Kelvin leads.

The SENSE<sup>+</sup> and SENSE<sup>-</sup> PC traces must be routed together at minimum spacing to prevent stray pickup, and a Kelvin connection must be used at the current shunt for the 3-lead MOSFET. Using a twisted pair is the safest approach and is recommended for sense runs of several inches.

When the voltage across  $R_{SENSE}$  exceeds 110mV, the LT1158  $\overline{FAULT}$  pin begins to conduct, signaling a fault condition. The current in a short circuit ramps very rapidly, limited only by the series inductance and ultimately the MOSFET and shunt resistance. Due to the response time

Figure 6. Short-Circuit Protection with Standard MOSFET

Figure 7. Short-Circuit Protection with Current-Sensing MOSFET

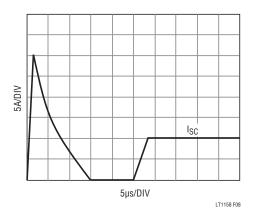

of the LT1158 current limit loop, an initial current spike of from 2 to 5 times the final value will be present for a few  $\mu$ s, followed by an interval in which  $I_{DS}=0$ . The current spike is normally well within the safe operating area (SOA) of the MOSFET, but can be further reduced with a small (0.5 $\mu$ H) inductor in series with the output.

Figure 8. Top MOSFET Short-Circuit Turn-On current

If neither the enable nor input pins are pulled low in response to the fault indication, the top MOSFET current will recover to a steady-state value  $I_{SC}$  regulated by the LT1158 as shown in Figure 8:

$$\begin{split} I_{SC} &= \frac{150\text{mV}}{R_{SENSE}} \\ R_{SENSE} &= \frac{150\text{mV}}{I_{SC}} \\ I_{SC} &= \frac{r\left(150\text{mV}\right)}{R_{SENSE}} \bigg(1 - \frac{150\text{mV}}{\Delta V}\bigg)^{-2} \\ R_{SENSE} &= \frac{r\left(150\text{mV}\right)}{I_{SC}} \bigg(1 - \frac{150\text{mV}}{\Delta V}\bigg)^{-2} \end{split}$$

r = current sense ratio,  $\Delta V = V_{GS} = V_{GS} - V_{T}$

The time for the current to recover to  $I_{SC}$  following the initial current spike is approximately  $Q_{GS}/0.5$ mA, where  $Q_{GS}$  is the MOSFET gate-to-source charge.  $I_{SC}$  need not be set higher than the required start-up current for motors (see Starting High In-Rush Current Loads). Note that

the value of  $R_{SENSE}$  for the 5-lead MOSFET increases by the current sensing ratio (typically 1000 - 3000), thus eliminating the need for a low valued shunt.  $\Delta V$  is in the range of 1V to 3V in most applications.

Assuming a dead short, the MOSFET dissipation will rise to  $V_{SUPPLY} \bullet I_{SC}$ . For example, with a 24V supply and  $I_{SC} = 10A$ , the dissipation would be 240W. To determine how long the MOSFET can remain at this dissipation level before it must be shut down, refer to the SOA curves given in the MOSFET data sheet. For example, an IRFZ34 would be safe if shut down within 10ms.

A Tektronix A6303 current probe is highly recommended for viewing output fault currents.

#### If Short-Circuit Protection is Not Required

In applications which do not require the current sense capability of the LT1158, the sense pins 11 and 12 should both be connected to pin 13, and the FAULT pin 5 left open. The enable pin 4 may still be used to shut down the device. Note, however, that when unprotected the top MOSFET can be easily (and often dramatically) destroyed by even a momentary short.

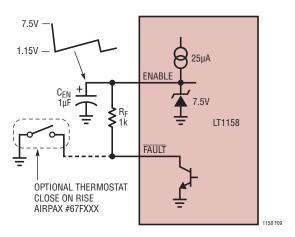

#### Self-Protection with Automatic Restart

When using the current sense circuits of Figures 6 and 7, local shutdown can be achieved by connecting the  $\overline{\text{FAULT}}$  pin through resistor  $R_F$  to the enable pin as shown in Figure 9. An optional thermostat mounted to the load or MOSFET heatsink can also be used to pull enable low.

An internal  $25\mu A$  current source normally keeps the enable capacitor CEN charged to the 7.5V clamp voltage (or to V<sup>+</sup>, for V<sup>+</sup> < 7.5V). When a fault occurs, CEN is discharged to below the enable low threshold (1.15V typ) which shuts down both MOSFETs. When the FAULT pin or thermostat releases, CEN recharges to the upper enable threshold where restart is attempted. In a sustained short circuit, FAULT will again pull low and the cycle will repeat until the short is removed. The time to shut down for a DC input or thermal fault is given by:

$t_{SHUTDOWN} = (100 + 0.8R_F) C_{EN}$  DC input

TECHNOLOGY TECHNOLOGY

Note that for the first event only,  $t_{SHUTDOWN}$  is approximately twice the above value since  $C_{EN}$  is being discharged all the way from its quiescent voltage. Allowable values for  $R_F$  are from zero to 10k.

Figure 9. Self-Protection with Auto Restart

$t_{SHUTDOWN}$  becomes more difficult to analyze when the output is shorted with a PWM input. This is because the FAULT pin only conducts when fault currents are actually present in the MOSFET. FAULT does not conduct while the input is low in Figures 6 and 7 or during the interval  $l_{DS} = 0$  in Figure 8. Thus  $t_{SHUTDOWN}$  will safely increase when the duty cycle of the current in the top MOSFET is low, maintaining the average MOSFET current at a relatively constant level.

The length of time following shutdown before restart is attempted is given by:

$$t_{RESTART} = \left(\frac{1.5V}{25\mu A}\right) C_{EN} = \left(6 \times 10^4\right) C_{EN}$$

In Figure 9, the top MOSFET would shut down after being in DC current limit for 0.9ms and try to restart at 60ms intervals, thus producing a duty cyle of 1.5% in short circuit. The resulting average top MOSFET dissipation during a short is easily measured by taking the product of the supply voltage and the average supply current.

#### Starting High In-Rush Current Loads

The LT1158 has a  $V_{DS}$  sensing function which allows more than  $I_{SC}$  to flow in the top MOSFET providing that the

SENSE<sup>-</sup> pin is within 1.2V of supply. Under these conditions the current is limited only by the  $R_{DS(ON)}$  in series with  $R_{SENSE}$ . For a 5-lead MOSFET the current is limited by  $R_{DS(ON)}$  alone, since  $R_{SENSE}$  is not in the output path (see Figure 7). Again adjusting  $R_{DS(ON)}$  for temperature, the worst-case start currents are:

$$I_{START} = \frac{1.2V}{(1+\partial)R_{DS(ON)} + R_{SENSE}}$$

3-Lead MOSFET

$$I_{START} = \frac{1.2V}{(1+\partial)R_{DS(ON)}}$$

5-Lead MOSFET

Properly sizing the MOSFET for I<sub>START</sub> allows inductive loads with long time constants, such as motors with high mechanical inertia, to be started.

Returning to the example used in Power MOSFET Selection, an IRFZ34 ( $R_{DS(0N)}=0.05\Omega$  max) was selected for operation at 5A. If the short-circuit current is also set at 5A, what start current can be supported? From the equation for  $R_{SENSE}$ , a  $0.03\Omega$  shunt would be required, allowing the worst-case start current to be calculated:

$$I_{START} = \frac{1.2V}{(1.7)0.05\Omega + 0.03\Omega} = 10A$$

This calculation gives the minimum current which could be delivered with the IRFZ34 at  $T_J$  = 125°C without activating the  $\overline{FAULT}$  pin on the LT1158. If more start current is required, using an IRFZ44 ( $R_{DS(0N)}$  = 0.028 $\Omega$  max) would increase  $I_{START}$  to over 15A at  $T_J$  = 110°C, even though the short-circuit current remains at 5A.

In order for the  $V_{DS}$  sensing function to work properly, the supply pins for the LT1158 must be connected at the drain of the top MOSFET, which must be properly decoupled (see Ugly Transient Issues).

#### **Driving Lamps**

Incandescent lamps represent a challenging load because they have much in common with a short circuit when cold. The top gate driver in the LT1158 can be configured to turn on large lamps while still protecting the power MOSFET

from a true short. This is done by using the current limit to control cold filament current in conjunction with the self-protection circuit of Figure 9. The reduced cold filament current also extends the life of the filament.

A good guideline is to choose R<sub>SENSE</sub> to set I<sub>SC</sub> at approximately twice the steady state "on" current of the lamp(s). t<sub>SHUTDOWN</sub> is then made long enough to guarantee that the lamp filaments heat and drop out of current limit before the enable capacitor discharges to the enable low threshold. For a short-circuit, the enable capacitor will continue to discharge below the threshold, shutting

down the top MOSFET. The LT1158 will then go into the automatic restart mode described in Self-Protection with Automatic Restart above.

The time constant for an incandescent filament is tens of milliseconds, which means that t<sub>SHUTDOWN</sub> will have to be longer than in most other applications. This places increased SOA demands on the MOSFET during a short circuit, requiring that a larger than normal device be used. A protected high current lamp driver application is shown in Figure 18.

Figure 10. High Efficiency 3.3V Step-Down Switching Regulator (Reguires No Heatsinks)

Figure 11. 5V to 3.XXV,15A Converter (Uses PC Board Area for Heatsink)

Figure 12. High Efficiency 5V Step-Down Switching Regulator (Requires No Heatsinks)

Figure 13. 90% Efficiency 24V to 5V 10A Switching Regulator 95% Efficiency 24V to 12V 10A Low Dropout Switching Regulator

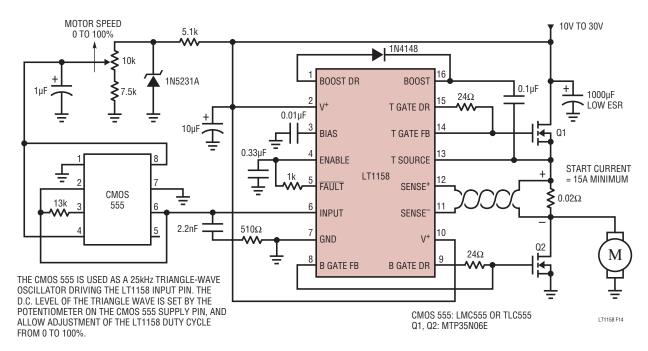

Figure 14. Potentiometer-Adjusted Open Loop Motor Speed Control with Short-Circuit Protection

Figure 15. High Efficiency 6-Cell NiCd Protected Motor Drive

Figure 16. 3-Phase Brushless DC Motor Control

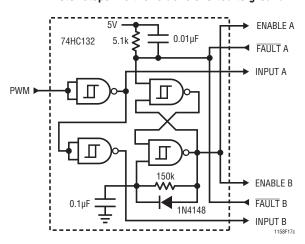

#### Control Logic for Sign/Magnitude Drive

# PWM DIRECTION STOP (FREE RUN) TIN4148 ENABLE A FAULT A INPUT A ENABLE B FAULT B INPUT B INPUT B

#### Control Logic for Locked Anti-Phase Drive Motor stops if either side is shorted to ground

Figure 17. 10A Full Bridge Motor Control

LINEAR TECHNOLOGY

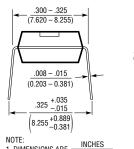

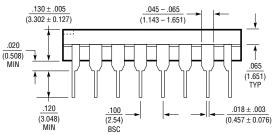

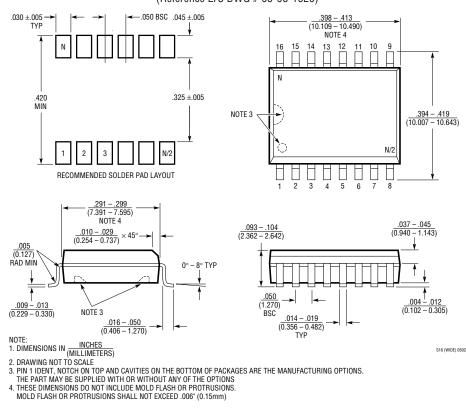

#### PACKAGE DESCRIPTION

#### N Package 16-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510)

N16 1002

DIMENSIONS ARE HINCHES

THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

#### **SW Package** 16-Lead Plastic Small Outline (Wide .300 Inch)

(Reference LTC DWG # 05-08-1620)

Figure 18. High Current Lamp Driver with Short-Circuit Protection

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Analog Devices Inc.:

LT1158CSW#TRPBF LT1158ISW#PBF LT1158IN#PBF LT1158CSW#PBF LT1158ISW#TRPBF LT1158CN#PBF