Click here to ask an associate for production status of specific part numbers.

### **MAX77675**

## Low I<sub>Q</sub> SIMO PMIC with 0.5V to 5.5V Outputs Delivering Up to 700mA Total Output Current

### **General Description**

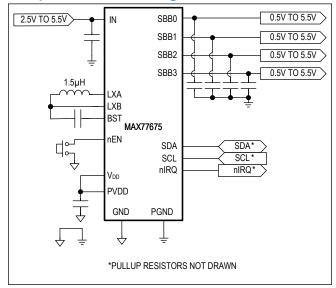

The MAX77675 is a highly efficient, complete power supply for low-power, ultra-compact applications. It provides four programmable buck-boost switching outputs using only one inductor. Operating from a single lithium-ion or Liion battery, the MAX77675 delivers a total of 700mA output current (3.7V $_{\rm IN}$ , 1.8V $_{\rm OUT}$ ) in less than 40mm $^2$  solution size.

An integrated sequencer controls full startup while an I<sup>2</sup>C interface allows the MAX77675 to be dynamically configured and monitored.

This device is part of the single-inductor multiple-output (SIMO) product family.

### **Applications**

- TWS Bluetooth™ Headphones/Hearables

- Fitness, Health, Activity Monitors, and Smart Watches

- Portable Devices

- Sensor Nodes and Consumer Internet of Things or IoT

#### **Benefits and Features**

- 4x Buck/Buck-Boost/Boost Regulators, 1x Inductor

- 2.5V to 5.5V Input Voltage Range

- 0.5V to 5.5V Output Voltage Range

- 700mA Total Output Current (3.7V<sub>IN</sub>, 1.8V<sub>OUT</sub>)

- SIMO

- Up to 90% Efficiency

- 6.9µA Typical I<sub>Q</sub> with Two Outputs Enabled in Low-Power Mode

- I<sup>2</sup>C Interface and Dedicated Enable Pin

- Flexible Power Sequencer (FPS)

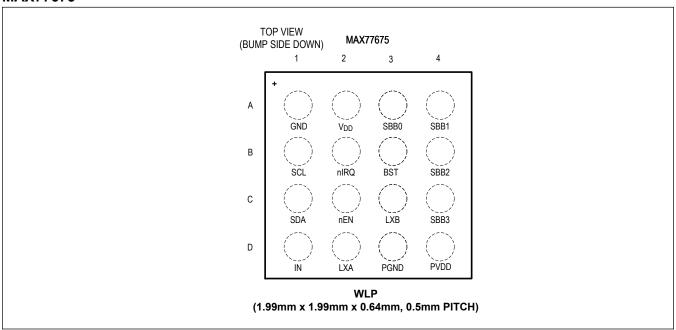

- 1.99mm x 1.99mm, 16-Bump, 0.5mm Pitch Wafer-Level Package (WLP)

- < 40mm<sup>2</sup> Solution Size

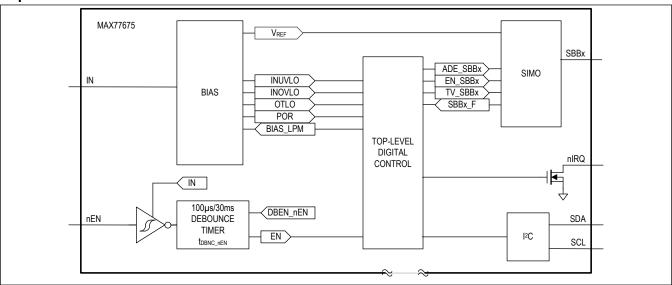

### Simplified Block Diagram

Bluetooth is a trademark of Bluetooth SIG, Inc.

## **TABLE OF CONTENTS**

| General Description                                              |      |

|------------------------------------------------------------------|------|

| Applications                                                     |      |

| Benefits and Features                                            |      |

| Simplified Block Diagram                                         |      |

| Absolute Maximum Ratings                                         |      |

| Recommended Operating Conditions                                 |      |

| Package Information                                              |      |

| 16 WLP 0.5mm Pitch                                               |      |

| Electrical Characteristics                                       |      |

| Electrical Characteristics—SIMO Buck-Boost                       |      |

| Electrical Characteristics—I <sup>2</sup> C Serial Interface     |      |

| Typical Operating Characteristics                                |      |

| Pin Configuration                                                |      |

| MAX77675                                                         |      |

| Pin Description                                                  |      |

| Functional Diagrams                                              |      |

| Top Level Interconnect                                           |      |

| Detailed Description                                             |      |

| Part Number Decoding                                             |      |

| Support Materials                                                |      |

| Voltage Monitors                                                 |      |

| IN POR Comparator                                                |      |

| IN Undervoltage Lockout Comparator                               |      |

| IN Overvoltage Lockout Comparator                                |      |

| Thermal Monitors                                                 |      |

| Thermal Shutdown                                                 |      |

| Chip Identification                                              |      |

| nEN Enable Input                                                 |      |

| nEN Manual Reset                                                 |      |

| nEN Triple Functionality: Push-Button vs. Slide-Switch vs. Logic |      |

| Debounced Input                                                  |      |

| nEN Internal Pullup Resistors to V <sub>IN</sub>                 |      |

| Interrupts (nIRQ)                                                |      |

| On/Off Controller                                                |      |

| Top Level On/Off Controller                                      |      |

| Internal Wake-Up Flags                                           |      |

| On/Off Controller Actions                                        |      |

| Flexible Power Sequencer                                         |      |

| Startup Timing Diagram Due to nEN                                | . 32 |

## TABLE OF CONTENTS (CONTINUED)

| Low-Power Mode                                         | 33 |

|--------------------------------------------------------|----|

| Detailed Description—SIMO Buck-Boost                   | 34 |

| Benefits and Features                                  | 34 |

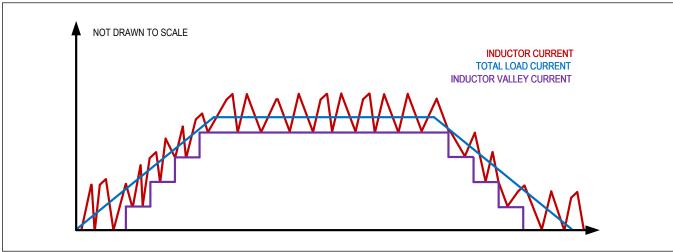

| Inductor Valley Current                                | 34 |

| SIMO Control Scheme                                    | 35 |

| Drive Strength                                         | 35 |

| SIMO Channel Operating Mode                            | 35 |

| Examples                                               | 35 |

| Buck Mode                                              | 35 |

| Buck-Boost Mode                                        | 35 |

| Boost Mode                                             | 35 |

| Channel-to-Channel Switching                           | 36 |

| SIMO Soft-Start                                        | 36 |

| Rising Slew Rate                                       | 36 |

| Delay in Changing Output Voltage                       | 37 |

| SIMO Registers                                         | 37 |

| SIMO Active Discharge Resistance                       | 37 |

| Bootstrap Refresh                                      | 37 |

| Detailed Description—I <sup>2</sup> C Serial Interface | 37 |

| Benefits and Features                                  | 37 |

| I <sup>2</sup> C System Configuration                  | 38 |

| I <sup>2</sup> C Interface Power                       | 38 |

| I <sup>2</sup> C Data Transfer                         | 38 |

| I <sup>2</sup> C Start and Stop Conditions             | 38 |

| I <sup>2</sup> C Acknowledge Bit                       | 38 |

| I <sup>2</sup> C Slave Address                         | 39 |

| I <sup>2</sup> C Clock Stretching                      | 39 |

| I <sup>2</sup> C General Call Address                  | 40 |

| I <sup>2</sup> C Device ID                             | 40 |

| I <sup>2</sup> C Communication Speed                   | 40 |

| I <sup>2</sup> C Communication Protocols               | 40 |

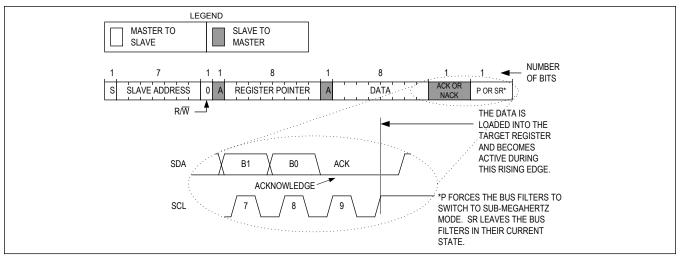

| Writing to a Single Register                           | 40 |

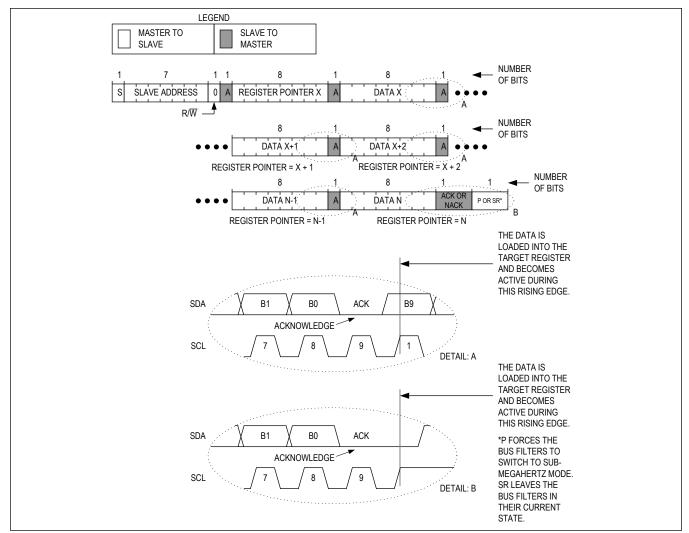

| Writing Multiple Bytes to Sequential Registers         | 41 |

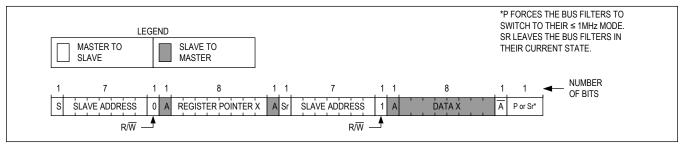

| Reading from a Single Register                         | 42 |

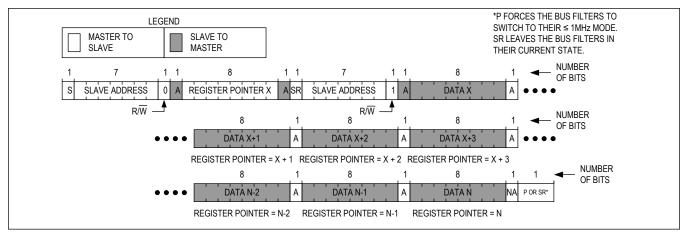

| Reading from Sequential Registers                      | 43 |

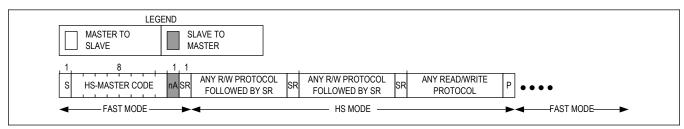

| Engaging HS Mode for Operation Up to 3.4MHz            | 44 |

| Register Map                                           |    |

| MAX77675                                               | 45 |

| Register Details                                       | 45 |

## TABLE OF CONTENTS (CONTINUED)

| Applications Information                 | 56 |

|------------------------------------------|----|

| Configuring Power Modes                  | 56 |

| Applications Information—SIMO Buck-Boost | 56 |

| SIMO-Supported Output Current            | 56 |

| Overload                                 | 58 |

| Inductor Selection                       | 58 |

| Input Capacitor Selection                | 58 |

| Bootstrap Capacitor Selection            | 58 |

| Output Capacitor Selection               | 59 |

| PVDD and V <sub>DD</sub> Capacitors      | 59 |

| Unused Outputs                           | 59 |

| Output Voltage Ripple                    | 59 |

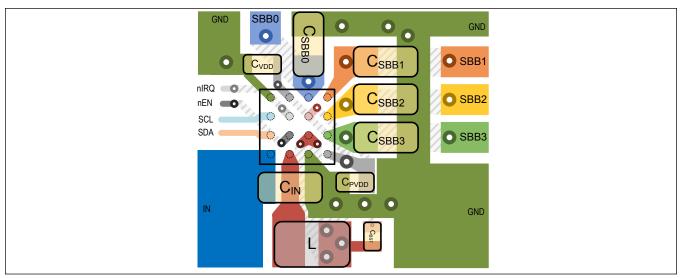

| PCB Layout Guide                         | 60 |

| Capacitors                               | 60 |

| Input Capacitor at IN                    | 60 |

| Output Capacitors at SBBx                | 60 |

| Inductor                                 | 60 |

| Ground Connections                       | 60 |

| Example PCB Layout                       | 60 |

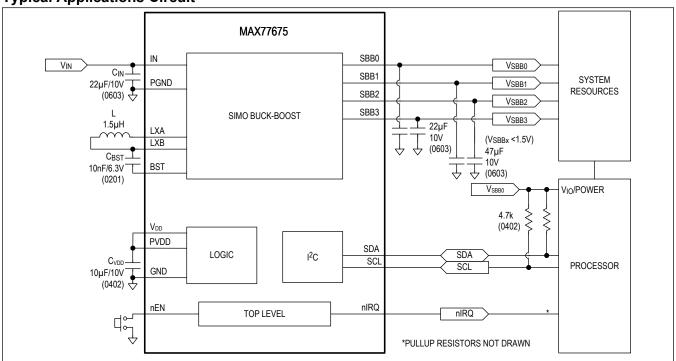

| Typical Application Circuits             | 61 |

| Typical Applications Circuit             | 61 |

| Ordering Information                     | 62 |

| Revision History                         | 63 |

## MAX77675

# Low I<sub>Q</sub> SIMO PMIC with 0.5V to 5.5V Outputs Delivering Up to 700mA Total Output Current

### LIST OF FIGURES

| gure 1. Part Number Decode                                                      | 23 |

|---------------------------------------------------------------------------------|----|

| jure 2. nEN Usage Timing Diagram                                                | 26 |

| jure 3. Debounced Input                                                         | 27 |

| gure 4. nEN Pullup Resistor Configuration                                       | 27 |

| jure 5. On/Off Controller State Diagram                                         | 29 |

| gure 6. On/Off Controller Actions                                               | 31 |

| jure 7. Flexible Power Sequencer Basic Timing Diagram                           | 32 |

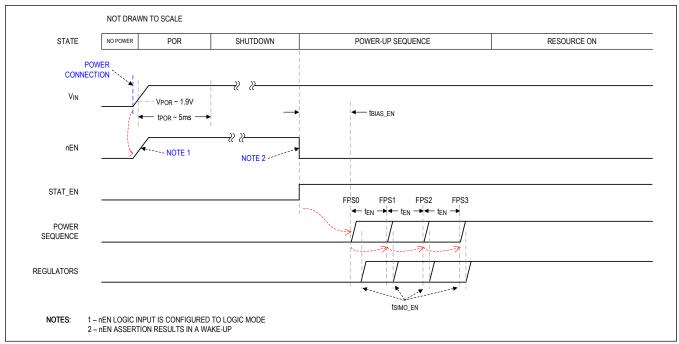

| gure 8. Startup Timing Diagram Due to nEN (Logic Mode)                          | 32 |

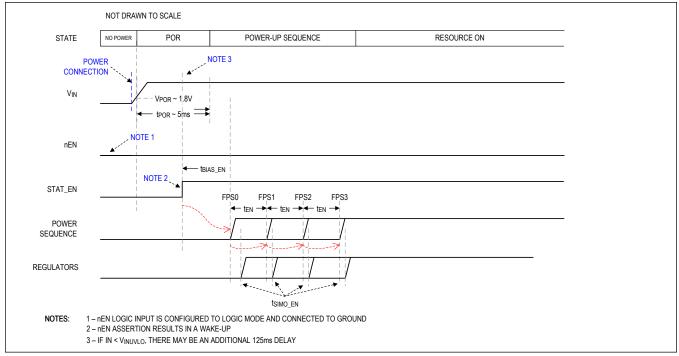

| gure 9. Startup Timing Diagram Due to nEN (Logic Mode; nEN Connected to Ground) | 33 |

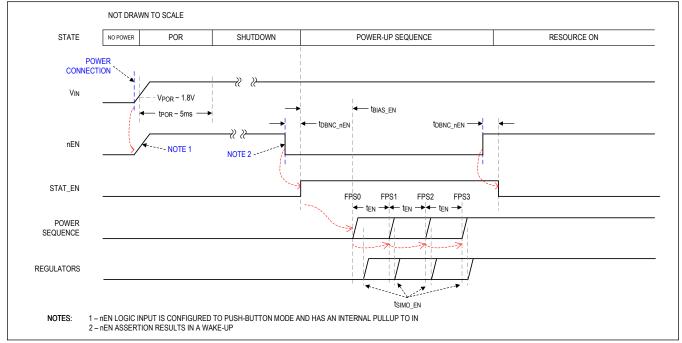

| gure 10. Startup Timing Diagram Due to nEN (Push-Button Mode)                   | 33 |

| jure 11. Valley Current Control with Changing Load Current                      | 34 |

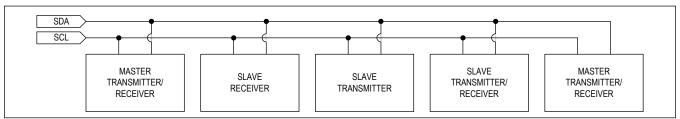

| jure 12. I <sup>2</sup> C System Configuration                                  | 38 |

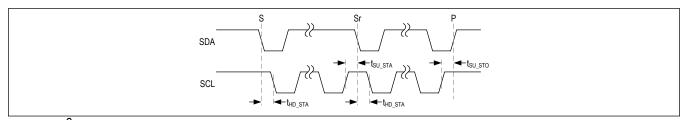

| gure 13. I <sup>2</sup> C Start and Stop Conditions                             | 38 |

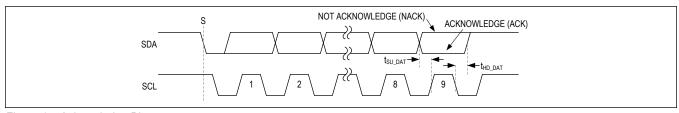

| jure 14. Acknowledge Bit                                                        | 39 |

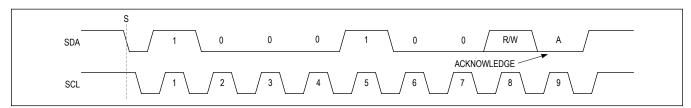

| jure 15. Slave Address Example                                                  | 39 |

| gure 16. Writing to a Single Register with the Write Byte Protocol              | 41 |

| gure 17. Writing to Sequential Registers X to N                                 | 42 |

| jure 18. Reading from a Single Register with the Read Byte Protocol             | 43 |

| jure 19. Reading Continuously from Sequential Registers X to N                  | 44 |

| gure 20. Engaging HS Mode                                                       | 44 |

| jure 21. PCB Top Layer and Component Placement Example                          | 61 |

## MAX77675

# Low I<sub>Q</sub> SIMO PMIC with 0.5V to 5.5V Outputs Delivering Up to 700mA Total Output Current

| LIST OF TABLES                                  |    |

|-------------------------------------------------|----|

| Table 1. OTP Options Table                      |    |

| Table 2. On/Off Controller Transition/State     | 29 |

| Table 3. SIMO Operating Mode Thresholds         | 35 |

| Table 4. Operating Mode Examples                | 35 |

| Table 5. Output Voltage Rising Slew Rates       | 37 |

| Table 6. I <sup>2</sup> C Slave Address Options | 39 |

| Table 7. Power Mode Configuration               |    |

## **Absolute Maximum Ratings**

| _                               |                                |

|---------------------------------|--------------------------------|

| nEN to GND                      | 0.3V to V <sub>IN</sub> + 0.3V |

| SCL, SDA to GND                 | 0.3V to +6V                    |

| IN, nIRQ to GND                 | 0.3V to +6V                    |

| PVDD, V <sub>DD</sub> to GND    | 0.3V to +2.2V                  |

| SDA Continous Current           | ±20mA                          |

| IN Continuous Current           | 1.2A <sub>RMS</sub>            |

| LXA Continuous Current (Note 1) | 1.2A <sub>RMS</sub>            |

| LXB Continuous Current (Note 1) | 1.2A <sub>RMS</sub>            |

| SBB0, SBB1, SBB2, SBB3 to PGND  | 0.3V to +6V                    |

| BST to IN                       | 0.3V to +6V                    |

|                                 |                                |

| BST to LXB                               | 0.3V to +6V                   |

|------------------------------------------|-------------------------------|

| SBB0, SBB1, SBB2, SBB3 Short-Circuit Du  | urationContinuous             |

| PGND to GND                              | 0.3V to +0.3V                 |

| Operating Temperature Range              | 40°C to +85°C                 |

| Junction Temperature                     | +150°C                        |

| Storage Temperature Range                | 65°C to +150°C                |

| Soldering Temperature (reflow)           | +260°C                        |

| Continuous Power Dissipation (Multilayer | Board, $T_A = +70^{\circ}C$ , |

| derate 20.4mW/°C above +70°C)            | 1632mW                        |

|                                          |                               |

Note 1: Do not externally bias LXA or LXB. LXA has internal clamping diodes to PGND and IN. LXB has an internal low-side clamping diode to PGND and an internal high-side clamping diode that dynamically connects to a selected SIMO output. It is normal for these diodes to briefly conduct during switching events. When the SIMO regulator is disabled, the LXB to PGND absolute maximum voltage is -0.3V to V<sub>SBBx</sub> + 0.3V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Recommended Operating Conditions**

| PARAMETER                                     | SYMBOL                                                                        | CONDITION                     | TYPICAL<br>RANGE | UNIT |

|-----------------------------------------------|-------------------------------------------------------------------------------|-------------------------------|------------------|------|

| IN Voltage                                    | V <sub>IN</sub>                                                               |                               | 2.5–5.5          | V    |

| ODDO/4/0/0 O 1 - 1 V - 1                      |                                                                               | CNFG_SBB_TOP.STEP_SZ_SBBx = 0 | 0.5–5.5          | V    |

| SBB0/1/2/3 Output Voltage                     | V <sub>SBBx</sub>                                                             | CNFG_SBB_TOP.STEP_SZ_SBBx = 1 | 0.5000-3.68      |      |

| SBB0/1/2/3 Maximum<br>Combined Output Current | I <sub>SBB0</sub> + I <sub>SBB1</sub> + I <sub>SBB2</sub> + I <sub>SBB3</sub> | Note 4                        | 700              | mA   |

| V <sub>DD</sub> Voltage                       | $V_{DD}$                                                                      |                               | 1.8              | V    |

Note: These limits are not guaranteed.

## **Package Information**

#### 16 WLP 0.5mm Pitch

| Package Code                           | W161N1+1                       |

|----------------------------------------|--------------------------------|

| Outline Number                         | <u>21-100374</u>               |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 49°C/W (2s2p board)            |

| Junction to Case (θ <sub>JC</sub> )    | N/A                            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = 3.7V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range (T_A = -40^{\circ}C to +85^{\circ}C)$  and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                            | SYMBOL                  | COND                                                                                | ITIONS                                   | MIN                   | TYP                   | MAX                   | UNITS |

|--------------------------------------|-------------------------|-------------------------------------------------------------------------------------|------------------------------------------|-----------------------|-----------------------|-----------------------|-------|

| INPUT CURRENT                        |                         |                                                                                     |                                          |                       |                       |                       |       |

| Shutdown Current                     | I <sub>SHDN</sub>       | All SBBx channels<br>are disabled, V <sub>IN</sub> =<br>3.7V, V <sub>LXA</sub> = 0V | T <sub>A</sub> = +25°C                   |                       | 0.3                   |                       | μΑ    |

| Quiescent Supply                     |                         | T - 1259C                                                                           | All channels<br>disabled, bias in<br>LPM | 3.8                   |                       |                       | μA    |

| Current                              | IQ                      | T <sub>A</sub> = +25°C                                                              | All channels<br>disabled, bias in<br>NPM |                       | 10                    |                       | μΑ    |

| VOLTAGE MONITORS                     |                         |                                                                                     |                                          |                       |                       |                       |       |

| Input Voltage Range                  | V <sub>IN</sub>         |                                                                                     |                                          | 2.5                   |                       | 5.5                   | V     |

| POWER-ON RESET (PO                   | R)                      |                                                                                     |                                          |                       |                       |                       |       |

| POR Threshold                        | V <sub>POR</sub>        | V <sub>IN</sub> falling                                                             |                                          |                       | 1.8                   |                       | V     |

| UNDERVOLTAGE LOCK                    | (OUT (UVLO)             |                                                                                     |                                          |                       |                       |                       |       |

| UVLO Threshold                       | V <sub>INUVLO</sub>     | V <sub>IN</sub> falling, UVLO_F                                                     | [1:0] = 0x4                              |                       | 2.3                   |                       | V     |

| UVLO Threshold<br>Hysteresis         | V <sub>INUVLO_HYS</sub> | UVLO_H[1:0] = 0x5                                                                   | ( <u>Note 2</u> )                        |                       | 300                   |                       | mV    |

| OVERVOLTAGE LOCKO                    | OUT (OVLO)              |                                                                                     |                                          |                       |                       |                       |       |

| OVLO Threshold                       | V <sub>INOVLO</sub>     | V <sub>IN</sub> rising                                                              |                                          | 5.70                  | 5.85                  | 6.00                  | V     |

| THERMAL MONITORS                     |                         |                                                                                     |                                          |                       |                       |                       |       |

| Overtemperature<br>Lockout Threshold | T <sub>OTLO</sub>       | T <sub>J</sub> rising                                                               |                                          |                       | 145                   |                       | °C    |

| Thermal Alarm<br>Temperature 1       | T <sub>JAL1</sub>       | T <sub>J</sub> rising                                                               | T <sub>J</sub> rising                    |                       | 90                    |                       | °C    |

| Thermal Alarm<br>Temperature 2       | T <sub>JAL2</sub>       | T <sub>J</sub> rising                                                               |                                          |                       | 120                   |                       | °C    |

| ENABLE INPUT (nEN)                   |                         |                                                                                     |                                          |                       |                       |                       |       |

| nEN Input Leakage                    |                         | $V_{nEN} = V_{IN} = 5.5V$                                                           | T <sub>A</sub> = +25°C                   | -1                    | ±0.001                | +1                    |       |

| Current                              | I <sub>nEN_LKG</sub>    | CNFG_GLBL_A.P<br>U_DIS = 1                                                          | T <sub>A</sub> = +85°C                   |                       | ±0.01                 |                       | μA    |

| nEN Input Falling<br>Threshold       | V <sub>TH_nEN_F</sub>   | nEN falling                                                                         |                                          | V <sub>IN</sub> - 1.6 | V <sub>IN</sub> - 1.2 |                       | V     |

| nEN Input Rising<br>Threshold        | V <sub>TH_nEN_R</sub>   | nEN rising                                                                          |                                          |                       | V <sub>IN</sub> - 1.1 | V <sub>IN</sub> - 0.6 | V     |

|                                      |                         | CNFG_GLBL_A.DBI                                                                     | EN_nEN = 0                               |                       | 100                   |                       | μs    |

| Debounce Time                        | t <sub>DBNC_nEN</sub>   | CNFG_GLBL_A.DBI<br>( <u>Note 5</u> )                                                | EN_nEN = 1                               |                       | 30                    |                       | ms    |

## **Electrical Characteristics (continued)**

$(V_{IN} = 3.7V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range (T_A = -40^{\circ}C to +85^{\circ}C)$  and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                     | SYMBOL                | COND                                                        | ITIONS                                    | MIN   | TYP    | MAX   | UNITS |

|-------------------------------|-----------------------|-------------------------------------------------------------|-------------------------------------------|-------|--------|-------|-------|

|                               |                       |                                                             | CNFG_GLBL_A.M<br>RT[1:0] = 0x0            | 3.75  | 4.00   | 5.25  |       |

|                               | t                     | ( <u>Note 3</u> and <u>Note</u>                             | CNFG_GLBL_A.M<br>RT[1:0] = 0x1            | 7.55  | 8.00   | 9.45  |       |

| Manual Reset Time             | <sup>t</sup> MRST     | <u>5</u> )                                                  | CNFG_GLBL_A.M<br>RT[1:0] = 0x2            | 11.35 | 12.00  | 13.65 | S     |

|                               |                       |                                                             | CNFG_GLBL_A.M<br>RT[1:0] = 0x3            | 15.15 | 16.00  | 17.85 |       |

| nEN Pullup                    | R <sub>nEN_PU</sub>   | Pullup to V <sub>IN</sub>                                   | CNFG_GLBL_A.P<br>U_DIS = 0                |       | 200    |       | kΩ    |

| OPEN-DRAIN INTERRUP           | T OUTPUT (nIR         | (Q)                                                         |                                           |       |        |       |       |

| Output Low Voltage            |                       | Sinking 2mA                                                 |                                           |       |        | 0.4   | V     |

| Output Falling Edge<br>Time   | t <sub>f_nIRQ</sub>   | C <sub>IRQ</sub> = 25pF ( <u>Note </u> §                    | C <sub>IRQ</sub> = 25pF ( <u>Note 5</u> ) |       | 1.5    |       | ns    |

|                               |                       | V <sub>IN</sub> = 5.5V, nIRQ                                | T <sub>A</sub> = +25°C                    | -1    | ±0.001 | +1    | 1     |

| Leakage Current               | I <sub>nIRQ_LKG</sub> | set to high<br>impedance, V <sub>nIRQ</sub><br>= 0V or 5.5V | $T_{A} = +85^{\circ}C$ ±0.                | ±0.01 |        | μΑ    |       |

| FLEXIBLE POWER SEQU           | JENCER                |                                                             |                                           |       |        |       |       |

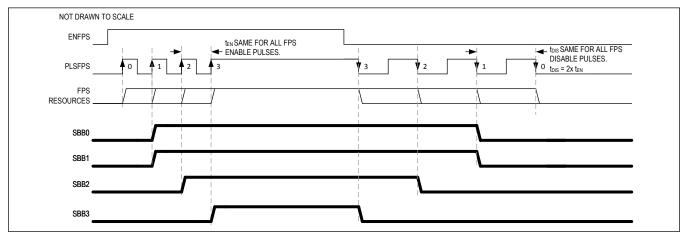

| Power-Up Event Periods        | t <sub>EN</sub>       | See Figure 7. (Note                                         | <u>5</u> )                                |       | 1.28   |       | ms    |

| Power-Down Event<br>Periods   | t <sub>DIS</sub>      | See Figure 7. (Note                                         | See Figure 7. (Note 5)                    |       | 2.56   |       | ms    |

| BIAS                          |                       |                                                             |                                           |       |        |       |       |

| Enable Delay                  | <sup>t</sup> BIAS_EN  |                                                             |                                           |       | 1      |       | ms    |

| PVDD Output Voltage           | $V_{PVDD}$            |                                                             |                                           |       | 1.8    |       | V     |

| V <sub>DD</sub> Input Voltage | $V_{DD}$              |                                                             |                                           |       | 1.8    |       | V     |

Note 2: Programmed at Analog Devices factory.

Note 3: The error in manual reset period is the same percentage-wise for all options.

### **Electrical Characteristics—SIMO Buck-Boost**

$(V_{IN} = 3.7V, C_{SBBx} = 22\mu F, L = 1.5\mu H, Limits are 100\%$  tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range  $(T_A = -40^{\circ}C + 85^{\circ}C)$  and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                              | SYMBOL                              | COND                                                                                                                    | ITIONS                                             | MIN                                 | TYP                                                | MAX    | UNITS |  |   |

|----------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|----------------------------------------------------|--------|-------|--|---|

| GENERAL CHARACTERISTICS                |                                     |                                                                                                                         |                                                    |                                     |                                                    |        |       |  |   |

|                                        |                                     |                                                                                                                         |                                                    | T <sub>A</sub> = +25°C, bias in LPM | Total current for the first channel at 1.8V output |        | 4.0   |  |   |

| SIMO Quiescent Supply Current  IQ_SIMO |                                     |                                                                                                                         |                                                    | ( <u>Note 5</u> )                   | Current for each additional channel at 1.8V output |        | 0.2   |  | ^ |

|                                        | T <sub>A</sub> = +25°C, bias in NPM | Current for the first channel at 1.8V output                                                                            |                                                    | 230                                 |                                                    | - μΑ   |       |  |   |

|                                        |                                     | ( <u>Note 5</u> )                                                                                                       | Current for each additional channel at 1.8V output |                                     | 61                                                 |        |       |  |   |

| OUTPUT VOLTAGE RAN                     | IGE (SBB0/1/2/                      | 3)                                                                                                                      |                                                    |                                     |                                                    |        |       |  |   |

| Programmable Output                    |                                     | CNFG_SBB_TOP_A                                                                                                          | .STEP_SZ_SBBx =                                    | 0.5                                 |                                                    | 5.5    | V     |  |   |

| Voltage Range                          |                                     | CNFG_SBB_TOP_A                                                                                                          | .STEP_SZ_SBBx =                                    | 0.5                                 |                                                    | 3.6875 | V     |  |   |

| Output DAC Bits                        |                                     |                                                                                                                         |                                                    |                                     | 8                                                  |        | bits  |  |   |

| Output DAC LSB Size                    |                                     | CNFG_SBB_TOP_A                                                                                                          | .STEP_SZ_SBBx =                                    |                                     | 25                                                 |        | mV    |  |   |

| Output DAC LSB Size                    |                                     | CNFG_SBB_TOP_A.STEP_SZ_SBBx = 1                                                                                         |                                                    |                                     | 12.5                                               |        | IIIV  |  |   |

| OUTPUT VOLTAGE ACC                     | URACY                               |                                                                                                                         |                                                    |                                     |                                                    |        |       |  |   |

|                                        | put Voltage                         | I <sub>SBBx</sub> = 1mA,                                                                                                |                                                    | T <sub>A</sub> = +25°C              | -3.0                                               |        | +3.0  |  |   |

| Output Voltage                         |                                     | typical is based on<br>an average over<br>100ms, V <sub>DD</sub> =<br>1.8V, V <sub>SBBx</sub> = 1.8V                    | T <sub>A</sub> = -40°C to<br>+85°C                 | -4.0                                |                                                    | +4.0   | %     |  |   |

| Accuracy                               |                                     | $I_{SBBx} = 300mA$ ,                                                                                                    | T <sub>A</sub> = +25°C                             | -2.0                                |                                                    | +2.0   | 70    |  |   |

|                                        |                                     | typical is based on<br>an average over<br>100ms, V <sub>DD</sub> =<br>1.8V, V <sub>SBBx</sub> = 1.8V                    | T <sub>A</sub> = -40°C to<br>+85°C                 | -4.0                                |                                                    | +4.0   |       |  |   |

| TIMING CHARACTERIST                    | ics                                 |                                                                                                                         |                                                    |                                     |                                                    |        |       |  |   |

|                                        |                                     | Delay time from the SIMO receiving its first enable signal to when it begins to switch in order to service that output. |                                                    |                                     | 450                                                |        |       |  |   |

| Enable Delay                           | <sup>t</sup> SIMO_EN                | After the first SIMO of enabled, subsequent cause their outputs the after this delay time.                              | t enable signals<br>o begin switching              |                                     | 150                                                |        | μs    |  |   |

## **Electrical Characteristics—SIMO Buck-Boost (continued)**

$(V_{IN} = 3.7V, C_{SBBx} = 22\mu F, L = 1.5\mu H, Limits are 100\% tested at T_A = +25^{\circ}C$ . Limits over the operating temperature range  $(T_A = -40^{\circ}C + 45^{\circ}C)$  and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                  | SYMBOL               | COND                                                                                                                                                                                  | ITIONS                          | MIN | TYP   | MAX | UNITS |  |

|----------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-------|-----|-------|--|

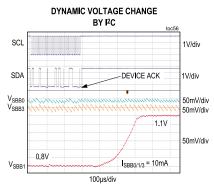

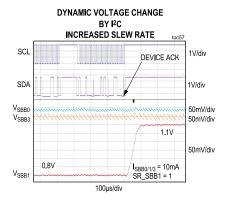

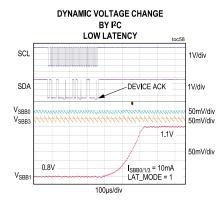

|                            |                      | CNFG_SBB_TOP_<br>B.SR_SBBx = 0                                                                                                                                                        |                                 | 1.0 | 2.0   | 3.0 |       |  |

| Soft-Start Slew Rate       | dV/dt <sub>SS</sub>  | CNFG_SBB_TOP_<br>B.SR_SBBx = 1                                                                                                                                                        | CNFG_SBB_TOP_<br>B.DVS_SLEW = 0 |     | 5.0   |     | mV/μs |  |

|                            |                      | ( <u>Note 5</u> )                                                                                                                                                                     | CNFG_SBB_TOP_<br>B.DVS_SLEW = 1 |     | 10    |     |       |  |

| POWER STAGE CHARA          | CTERISTICS           |                                                                                                                                                                                       |                                 |     |       |     |       |  |

|                            |                      | All SBB channels                                                                                                                                                                      | T <sub>A</sub> = +25°C          | -1  | ±0.01 | +1  |       |  |

| LXA Leakage Current        |                      | are disabled, $V_{IN}$ = 5.5V, $V_{LXA}$ = 0V, or 5.5V                                                                                                                                | T <sub>A</sub> = +85°C          |     | ±0.1  |     | μA    |  |

|                            |                      | All SBB channels                                                                                                                                                                      | T <sub>A</sub> = +25°C          | -1  | ±0.01 | +1  | μА    |  |

| LXB Leakage Current        |                      | are disabled, V <sub>IN</sub> = 5.5V, V <sub>LXA</sub> = 0V or 5.5V, all V <sub>SBBx</sub> = 4.0V                                                                                     | T <sub>A</sub> = +85°C          |     | ±0.1  |     |       |  |

| Disabled Output            |                      | All SBB channels<br>are disabled, active<br>discharge disabled<br>(ADE_SBBx = 0),<br>V <sub>SBBx</sub> = 4.0V,<br>V <sub>LXB</sub> = 0V, V <sub>IN</sub> =<br>V <sub>BST</sub> = 5.5V | T <sub>A</sub> = +25°C          |     | 0.05  | 1   |       |  |

| Leakage Current            |                      | All SBB channels are disabled, active discharge disabled (ADE_SBBx = 0), VSBBx = 4.0V, VLXB = 0V, VIN = VBST = 5.5V                                                                   | T <sub>A</sub> = +85°C          |     | 0.1   |     | - µА  |  |

| Active-Discharge Impedance | R <sub>AD_SBBx</sub> | All SBB channels are discharge enabled (A                                                                                                                                             |                                 | 80  | 140   | 260 | Ω     |  |

Note 4: See the SIMO Supported Output Current section for more information.

## Electrical Characteristics—I<sup>2</sup>C Serial Interface

$(V_{IN} = 3.7V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range (T_A = -40^{\circ}C to +85^{\circ}C) and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)$

| PARAMETER                      | SYMBOL          | CONDITIONS                                     | MIN                      | TYP | MAX                      | UNITS |  |

|--------------------------------|-----------------|------------------------------------------------|--------------------------|-----|--------------------------|-------|--|

| SDA AND SCL I/O STAGE          |                 |                                                |                          |     |                          |       |  |

| SCL, SDA Input High<br>Voltage | V <sub>IH</sub> | V <sub>IN</sub> = 3.7V, T <sub>A</sub> = +25°C | 0.7 x<br>V <sub>DD</sub> |     |                          | V     |  |

| SCL, SDA Input Low<br>Voltage  | V <sub>IL</sub> | T <sub>A</sub> = +25°C                         |                          |     | 0.3 x<br>V <sub>DD</sub> | V     |  |

## Electrical Characteristics—I<sup>2</sup>C Serial Interface (continued)

$(V_{IN} = 3.7V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range (T_A = -40^{\circ}C to +85^{\circ}C)$  and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                                                                 | SYMBOL              | CONDITIONS                                                                | MIN                 | TYP                       | MAX  | UNITS |

|-------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|---------------------|---------------------------|------|-------|

| SCL, SDA Input<br>Hysteresis                                                              | V <sub>HYS</sub>    | T <sub>A</sub> = +25°C                                                    |                     | 0.05 x<br>V <sub>DD</sub> |      | V     |

| SCL, SDA Input<br>Leakage Current                                                         | l <sub>l</sub>      | V <sub>SCL</sub> = V <sub>SDA</sub> = V <sub>DD</sub>                     | -1                  |                           | +1   | μA    |

| SDA Output Low<br>Voltage                                                                 | V <sub>OL</sub>     | Sinking 20mA                                                              |                     |                           | 0.4  | V     |

| SCL, SDA Pin<br>Capacitance                                                               | Cl                  | ( <u>Note 5</u> )                                                         |                     | 10                        |      | pF    |

| Output Fall Time from V <sub>IH</sub> to V <sub>IL</sub>                                  | t <sub>OF</sub>     | ( <u>Note 5</u> )                                                         |                     |                           | 120  | ns    |

| I <sup>2</sup> C-COMPATIBLE INTER                                                         | FACE TIMING (       | STANDARD, FAST, AND FAST-MODE PLU                                         | JS) ( <u>Note 5</u> | )                         |      |       |

| Clock Frequency                                                                           | f <sub>SCL</sub>    |                                                                           | 0                   |                           | 1000 | kHz   |

| Hold Time (REPEATED)<br>START Condition                                                   | t <sub>HD_STA</sub> |                                                                           | 0.26                |                           |      | μs    |

| SCL Low Period                                                                            | t <sub>LOW</sub>    |                                                                           | 0.5                 |                           |      | μs    |

| SCL High Period                                                                           | t <sub>HIGH</sub>   |                                                                           | 0.26                |                           |      | μs    |

| Setup Time REPEATED START Condition                                                       | t <sub>SU_STA</sub> |                                                                           | 0.26                |                           |      | μs    |

| Data Hold Time                                                                            | thd_dat             |                                                                           | 0                   |                           |      | μs    |

| Data Setup Time                                                                           | tsu_dat             |                                                                           | 50                  |                           |      | ns    |

| Setup Time for STOP<br>Condition                                                          | t <sub>SU_STO</sub> |                                                                           | 0.26                |                           |      | μs    |

| Bus Free Time between STOP and START Condition                                            | t <sub>BUF</sub>    |                                                                           | 0.5                 |                           |      | μs    |

| Pulse Width of<br>Suppressed Spikes                                                       | t <sub>SP</sub>     | Maximum pulse width of spikes that must be suppressed by the input filter |                     |                           | 50   | ns    |

| I <sup>2</sup> C-COMPATIBLE INTER                                                         | FACE TIMING (       | HIGH-SPEED MODE, CB = 100pF) (Note 5)                                     |                     |                           |      |       |

| Clock Frequency                                                                           | f <sub>SCL</sub>    |                                                                           |                     |                           | 3.4  | MHz   |

| Setup Time REPEATED START Condition                                                       | tsu_sta             |                                                                           | 160                 |                           |      | ns    |

| Hold Time (REPEATED)<br>START Condition                                                   | t <sub>HD_STA</sub> |                                                                           | 160                 |                           |      | ns    |

| SCL Low Period                                                                            | t <sub>LOW</sub>    |                                                                           | 160                 |                           |      | ns    |

| SCL High Period                                                                           | tHIGH               |                                                                           | 60                  |                           |      | ns    |

| Data Setup Time                                                                           | t <sub>SU_DAT</sub> |                                                                           | 10                  |                           |      | ns    |

| Data Hold Time                                                                            | t <sub>HD_DAT</sub> |                                                                           | 0                   |                           | 70   | ns    |

| SCL Rise Time                                                                             | $t_{rCL}$           | T <sub>A</sub> = +25°C                                                    | 10                  |                           | 40   | ns    |

| Rise Time of SCL Signal<br>After REPEATED<br>START Condition and<br>After Acknowledge Bit | <sup>t</sup> rCL1   | T <sub>A</sub> = +25°C                                                    | 10                  |                           | 80   | ns    |

## Electrical Characteristics—I<sup>2</sup>C Serial Interface (continued)

$(V_{IN} = 3.7V, Limits are 100\% tested at T_A = +25^{\circ}C. Limits over the operating temperature range (T_A = -40^{\circ}C to +85^{\circ}C)$  and relevant supply voltage range are guaranteed by design and characterization, unless otherwise noted. Specifications marked "GBD" are guaranteed by design and not production tested.)

| PARAMETER                                                                                 | SYMBOL              | CONDITIONS                                                                | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|-----|-----|-----|-------|

| SCL Fall Time                                                                             | t <sub>fCL</sub>    | T <sub>A</sub> = +25°C                                                    | 10  |     | 40  | ns    |

| SDA Rise Time                                                                             | t <sub>rDA</sub>    | T <sub>A</sub> = +25°C                                                    | 10  |     | 80  | ns    |

| SDA Fall Time                                                                             | t <sub>fDA</sub>    | T <sub>A</sub> = +25°C                                                    | 10  |     | 80  | ns    |

| Setup Time for STOP<br>Condition                                                          | tsu_sto             |                                                                           | 160 |     |     | ns    |

| Bus Capacitance                                                                           | C <sub>B</sub>      |                                                                           |     |     | 100 | pF    |

| Pulse Width of<br>Suppressed Spikes                                                       | t <sub>SP</sub>     | Maximum pulse width of spikes that must be suppressed by the input filter |     |     | 10  | ns    |

| I <sup>2</sup> C-COMPATIBLE INTER                                                         | FACE TIMING (       | HIGH-SPEED MODE, CB = 400pF) ( <u>Note 5</u> )                            |     |     |     |       |

| Clock Frequency                                                                           | f <sub>SCL</sub>    |                                                                           |     |     | 1.7 | MHz   |

| Setup Time REPEATED START Condition                                                       | tsu_sta             |                                                                           | 160 |     |     | ns    |

| Hold Time (REPEATED)<br>START Condition                                                   | t <sub>HD_STA</sub> |                                                                           | 160 |     |     | ns    |

| SCL Low Period                                                                            | t <sub>LOW</sub>    |                                                                           | 320 |     |     | ns    |

| SCL High Period                                                                           | tHIGH               |                                                                           | 120 |     |     | ns    |

| Data Setup Time                                                                           | t <sub>SU_DAT</sub> |                                                                           | 10  |     |     | ns    |

| Data Hold Time                                                                            | thd_dat             |                                                                           | 0   |     | 150 | ns    |

| SCL Rise Time                                                                             | t <sub>RCL</sub>    | T <sub>A</sub> = +25°C                                                    | 20  |     | 80  | ns    |

| Rise Time of SCL Signal<br>After REPEATED<br>START Condition and<br>After Acknowledge Bit | <sup>t</sup> RCL1   | T <sub>A</sub> = +25°C                                                    | 20  |     | 160 | ns    |

| SCL Fall Time                                                                             | t <sub>FCL</sub>    | T <sub>A</sub> = +25°C                                                    | 20  |     | 80  | ns    |

| SDA Rise Time                                                                             | t <sub>RDA</sub>    | T <sub>A</sub> = +25°C                                                    | 20  |     | 160 | ns    |

| SDA Fall Time                                                                             | t <sub>FDA</sub>    | T <sub>A</sub> = +25°C                                                    | 20  |     | 160 | ns    |

| Setup Time for STOP<br>Condition                                                          | tsu_sto             |                                                                           | 160 |     |     | ns    |

| Bus Capacitance                                                                           | C <sub>B</sub>      |                                                                           |     |     | 400 | pF    |

| Pulse Width of<br>Suppressed Spikes                                                       | t <sub>SP</sub>     | Maximum pulse width of spikes that must be suppressed by the input filter |     | 10  |     | ns    |

Note 5: Design guidance only. Not production tested.

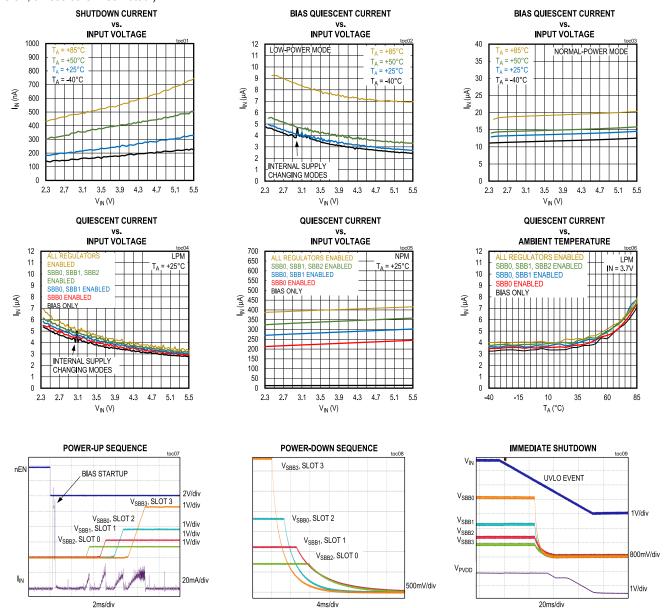

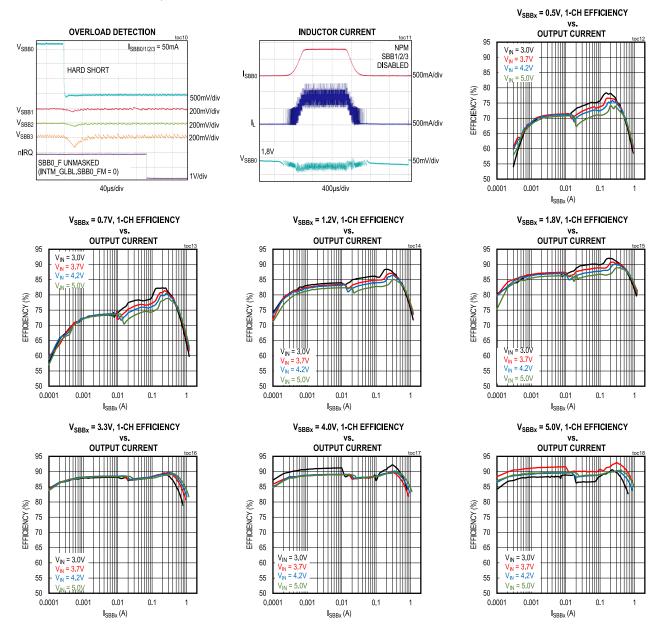

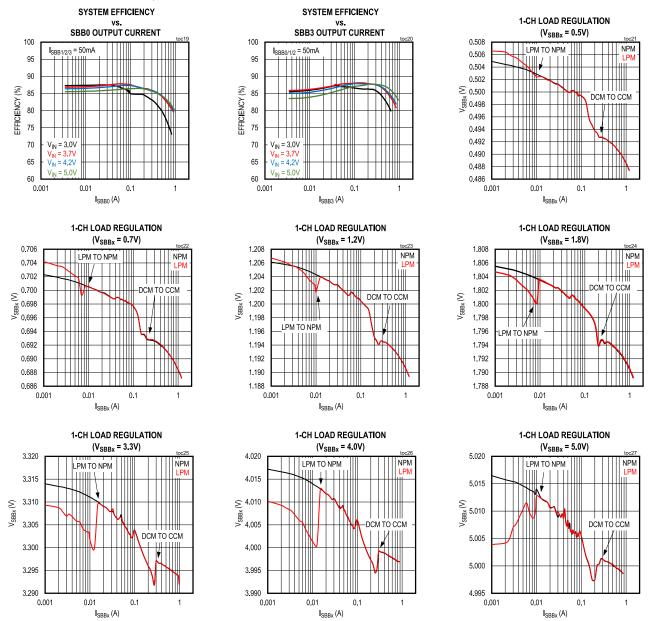

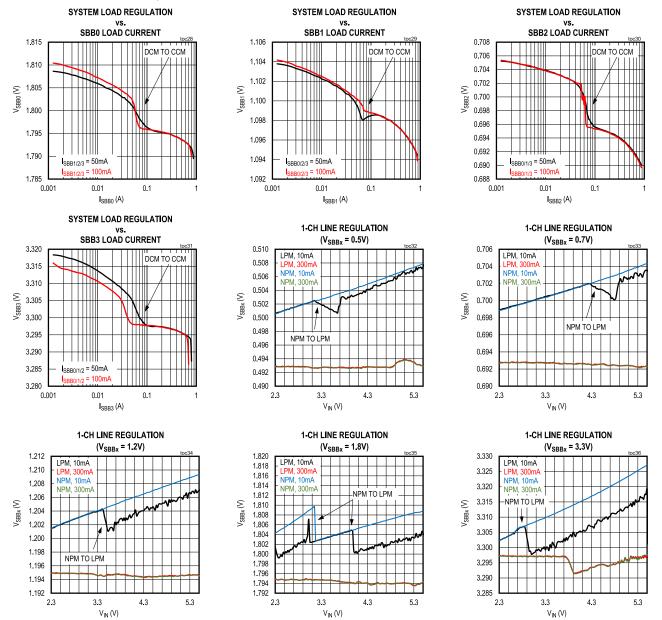

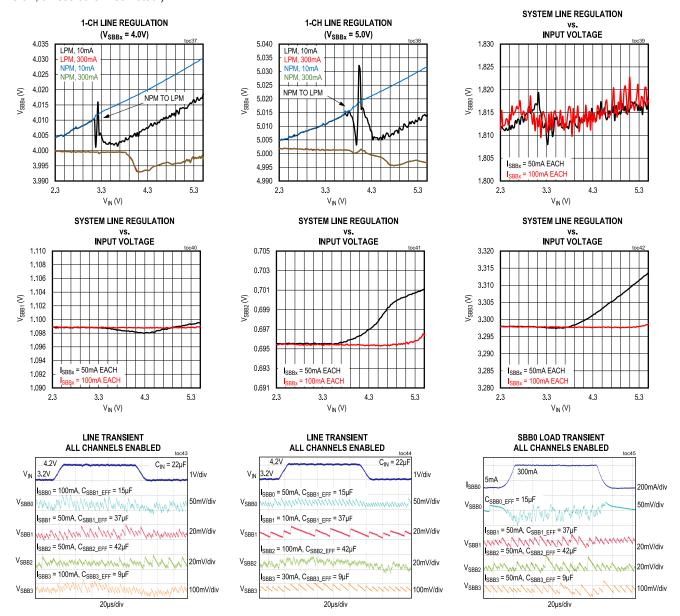

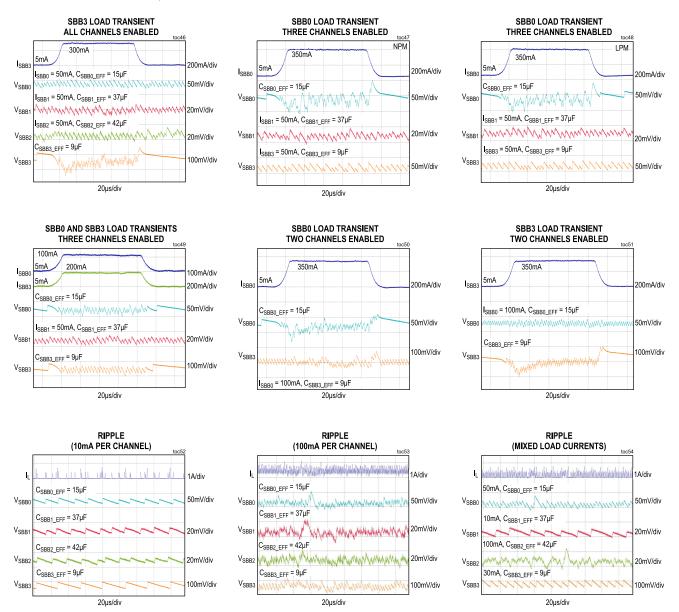

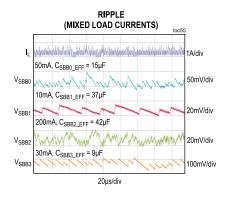

## **Typical Operating Characteristics**

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25 $^{\circ}$ C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25°C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25 $^{\circ}$ C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25 $^{\circ}$ C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25 $^{\circ}$ C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25 $^{\circ}$ C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

(Typical Applications Circuit.  $V_{IN}$  = 3.7V,  $C_{SBBx}$  = 22 $\mu$ F, L = 1.5 $\mu$ H,  $T_A$  = +25 $^{\circ}$ C,  $V_{SBB0}$  = 1.8V,  $V_{SBB1}$  = 1.1V,  $V_{SBB2}$  = 0.7V,  $V_{SBB3}$  = 3.3V, unless otherwise noted.)

## **Pin Configuration**

#### **MAX77675**

## **Pin Description**

| PIN         | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                            | TYPE           |  |  |  |  |

|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| TOP LEVEL   | TOP LEVEL |                                                                                                                                                                                                                                                                                                                                                     |                |  |  |  |  |

| C2          | nEN       | Active-Low Enable Input. $\overline{EN}$ supports push-button, slide-switch, or logic configurations. If not used, connect nEN to IN.                                                                                                                                                                                                               | Digital Input  |  |  |  |  |

| B2          | nIRQ      | Active-Low, Open-Drain Interrupt Pin. Connect a 100kΩ pull-up resistor to nIRQ.                                                                                                                                                                                                                                                                     | Digital Output |  |  |  |  |

| B1          | SCL       | I <sup>2</sup> C Clock                                                                                                                                                                                                                                                                                                                              | Digital Input  |  |  |  |  |

| C1          | SDA       | I <sup>2</sup> C Data                                                                                                                                                                                                                                                                                                                               | Digital I/O    |  |  |  |  |

| D1          | IN        | Input Voltage Connection                                                                                                                                                                                                                                                                                                                            | Power Input    |  |  |  |  |

| A1          | GND       | Quiet Ground. Connect GND to PGND and the low-impedance ground plane of the PCB.                                                                                                                                                                                                                                                                    | Ground         |  |  |  |  |

| A2          | $V_{DD}$  | Device Power Input. Connect to PVDD. Bypass to GND with a 10µF capacitor.                                                                                                                                                                                                                                                                           | Power Input    |  |  |  |  |

| D4          | PVDD      | 1.8V Internal Supply. Bypass this pin with a $10\mu F$ capacitor and connect to $V_{DD}$ . Do not connect anything else to this pin. If pullup resistors must be connected to PVDD, ensure on the layout the connection points are as close as possible to the capacitor and not the pin. See the <u>PCB Layout Guide</u> section for more details. | Power Output   |  |  |  |  |

| SIMO BUCK-B | OOST      |                                                                                                                                                                                                                                                                                                                                                     |                |  |  |  |  |

| A3          | SBB0      | B0 SIMO Buck-Boost Output 0. SBB0 is the power output for Channel 0 of the SIMO buck-boost. If not used, see the <i>Unused Outputs</i> section.                                                                                                                                                                                                     |                |  |  |  |  |

| A4          | SBB1      | SIMO Buck-Boost Output 1. SBB1 is the power output for Channel 1 of the SIMO buck-boost. If not used, see the <u>Unused Outputs</u> section.                                                                                                                                                                                                        | Power Output   |  |  |  |  |

| B4          | SBB2      | SIMO Buck-Boost Output 2. SBB2 is the power output for Channel 2 of the SIMO buck-boost. If not used, see the <u>Unused Outputs</u> section.                                                                                                                                                                                                        |                |  |  |  |  |

## **Pin Description (continued)**

| PIN | NAME | FUNCTION                                                                                                                                         | TYPE        |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| C4  | SBB3 | SIMO Buck-Boost Output 3. SBB3 is the power output for Channel 3 of the SIMO buck-boost. If not used, see the <i>Unused Outputs</i> section.     |             |

| В3  | BST  | SIMO Power Input for the High-Side Output NMOS Drivers. Connect a 10nF ceramic capacitor between BST and LXB.                                    | Power Input |

| С3  | LXB  | Switching Node B. LXB is driven between PGND and SBBx when SBBx is enabled. LXB is driven to PGND when all SIMO channels are disabled.           | Power I/O   |

| D2  | LXA  | Switching Node A. LXA is driven between PGND and IN when any SIMO channel is enabled. LXA is driven to PGND when all SIMO channels are disabled. | Power I/O   |

| D3  | PGND | Power Ground for the SIMO Low-Side FETs. Connect PGND to GND and the low-impedance ground plane of the PCB.                                      | Ground      |

## **Functional Diagrams**

## **Top Level Interconnect**

### **Detailed Description**

The MAX77675 provides a power management solution for low-power applications. A SIMO buck-boost regulator efficiently provides four independently programmable power rails.

A bidirectional I<sup>2</sup>C serial interface allows for configuring and checking the status of the device. An internal on/off controller provides power sequencing and supervisory functionality for the device.

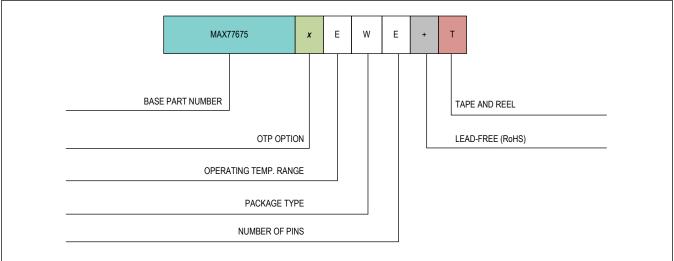

#### **Part Number Decoding**

The MAX77675 has different one-time programmable (OTP) options and variants to support a variety of applications. The OTP options set default settings such as output voltage. See <u>Figure 1</u> for how to identify these. <u>Table 1</u> lists all available OTP options. Refer to <u>Product Naming Convention</u> for more details.

Figure 1. Part Number Decode

**Table 1. OTP Options Table**

|        |                |                                  | OTP LETTE  | R AND SETTINGS  |

|--------|----------------|----------------------------------|------------|-----------------|

| BLOCK  | BIT FIELD NAME | SETTING NAME                     | Α          | С               |

|        | CID[7:0]       | OTP Identifier                   | 0x3        | 0xC             |

|        | PU_DIS         | Pullup Disable                   | Disabled   | Enabled (200kΩ) |

|        | BIAS_LPM       | Bias Power Mode                  | LPM        | LPM             |

|        | MRT            | Manual Reset Time                | 8s         | 8s              |

| Olahai | nEN_MODE       | nEN Mode                         | Logic      | Logic           |

| Global | DBEN_nEN       | nEN Debounce Time                | 100µs      | 100µs           |

|        | ADDR           | I <sup>2</sup> C Address (7-bit) | 0x44       | 0x40            |

|        | OVLO_R         | OVLO Rising Threshold            | 5.85V      | 5.65V           |

|        | UVLO_F         | UVLO Falling Threshold           | 2.30V      | 2.30V           |

|        | UVLO_H         | UVLO Threshold Hysteresis        | 0.30V      | 0.30V           |

|        | TV_SBB0[7:0]   | SBB0 V <sub>OUT</sub>            | 1.800V     | 3.300V          |

|        | ADE_SBB0       | Active-Discharge Resistor Enable | Enabled    | Enabled         |

|        | EN_SBB0[2:0]   | SBB0 Enable Control              | FPS Slot 2 | FPS Slot 1      |

|        | TV_SBB1[7:0]   | SBB1 V <sub>OUT</sub>            | 1.100V     | 4.000V          |

|        | ADE_SBB1       | Active-Discharge Resistor Enable | Enabled    | Enabled         |

| CIMO   | EN_SBB1[2:0]   | SBB1 Enable Control              | FPS Slot 1 | FPS Slot 0      |

| SIMO   | TV_SBB2[7:0]   | SBB2 V <sub>OUT</sub>            | 0.700V     | 1.500V          |

|        | ADE_SBB2       | Active-Discharge Resistor Enable | Enabled    | Enabled         |

|        | EN_SBB2[2:0]   | SBB2 Enable Control              | FPS Slot 0 | FPS Slot 3      |

|        | TV_SBB3[7:0]   | SBB3 V <sub>OUT</sub>            | 3.300V     | 1.800V          |

|        | ADE_SBB3       | Active-Discharge Resistor Enable | Enabled    | Enabled         |

|        | EN_SBB3[2:0]   | SBB3 Enable Control              | FPS Slot 3 | FPS Slot 2      |

#### Support Materials

The following support materials are available for this device:

- MAX77675 Register Map: Full table of registers that can be read from or written to by I<sup>2</sup>C.

- MAX77675 <u>Programmer's Guide</u>: Basic software implementation guide. (Note: The guide applies to both the MAX77655 and MAX77675.)

- MAX77675 <u>SIMO Calculator</u>: Tool to determine if a given set of voltages and currents are supported. The tool can be found under **Design Resources** in the product web page.

#### **Voltage Monitors**

The device monitors the input voltage  $(V_{IN})$  to ensure proper operation using three comparators (POR, UVLO, and OVLO). These comparators include hysteresis to prevent their outputs from toggling between states during noisy system transitions.

#### **IN POR Comparator**

The IN POR comparator monitors  $V_{IN}$  and generates a power-on reset signal (POR). When  $V_{IN}$  is below  $V_{POR}$ , the device is held in reset (RST = 1, POR = 1). When  $V_{IN}$  rises above  $V_{POR}$ , the device enters shutdown state (RST = 1, POR = 0). See Figure 5 and Table 2 for more details.

#### **IN Undervoltage Lockout Comparator**

The IN UVLO comparator monitors V<sub>IN</sub> and generates an INUVLO signal when the V<sub>IN</sub> falls below the UVLO threshold.

The INUVLO signal is provided to the top-level digital controller. See <u>Figure 5</u> and <u>Table 2</u> for additional information regarding the UVLO comparator:

- When the device is in the Shutdown state, the UVLO comparator is disabled.

- When transitioning out of the Shutdown state, the UVLO comparator is enabled allowing the device to check for sufficient input voltage. If V<sub>IN</sub> is above the UVLO rising threshold and a wake-up signal is received, the device can transition to the Resource On state; otherwise, the device transitions back to the Shutdown state.

#### **IN Overvoltage Lockout Comparator**

The device is rated for 5.5V maximum operating voltage ( $V_{IN}$ ) with an absolute maximum input voltage of 6.0V. An OVLO monitor increases the robustness of the device by inhibiting operation when the supply voltage is greater than  $V_{INOVLO}$ . See <u>Figure 5</u> and <u>Table 2</u> for additional information regarding the OVLO comparator:

When the device is in the Shutdown state, the OVLO comparator is disabled.

#### **Thermal Monitors**

The MAX77675 has three global on-chip thermal sensors:

- Junction Temperature Alarm 1 → 90°C

- Junction Temperature Alarm 2 → 120°C

- Junction Temperature Shutdown → 145°C

The junction temperature alarms have maskable rising interrupts as well as status bits (see the <u>Register Map</u> section for more information). Unmasking these thermal alarms is recommended for all systems. If the first alarm is triggered, the system software should attempt to lower system power dissipation. If the second alarm is triggered, then attempts to lower the power dissipation were unsuccessful and the system software should turn the device off. Finally, if the junction temperature rises to junction temperature shutdown, then the MAX77675 sets the ERCFLAG.TOVLD bit and automatically turns itself off.

After a junction temperature shutdown event, the system can be enabled again. The system software can read the ERCFLAG register during initialization to see ERCFLAG.TOVLD = 1 and log that an extreme thermal event has occurred.

#### **Thermal Shutdown**

The MAX77675 has on-chip thermal sensors to monitor thermal overloads. The thermal overload alarm generates a TOVLD signal when the junction temperature exceeds +145°C (T<sub>JOVLD</sub>). The on/off controller provides TOVLD. When TOVLD is asserted, the on/off controller forces system reset which disables all functions of the MAX77675. Once all functions are disabled, a wake-up event is required to turn the MAX77675 on again. In the case that a wake-up event turns the MAX77675 on when the junction temperature is still above +145°C, the MAX77675's on/off controller promptly forces system reset which disables all functions again. The thermal monitoring function is sampled in low-power mode to save quiescent current. The host can check if a temperature overload occurred by reading the ERCFLAG.TOLVD flag.

#### **Chip Identification**

Different OTP variants of the MAX77675 offer different settings such as settings for default output voltages or power sequencing. These OTP variants are identified by the Chip Identification number, which can be read in the CID register.

#### nEN Enable Input

The nEN is an active-low, internally debounced digital input that typically comes from the system's on-key. The debounce time is programmable with CNFG\_GLBL\_A.DBEN\_nEN. The primary purpose of this input is to generate a wake-up signal for the PMIC, turning on the regulators. Maskable rising/falling interrupts are available for nEN (INTM GLBL.nEN R and INTM GLBL.nEN F) for alternate functionality.

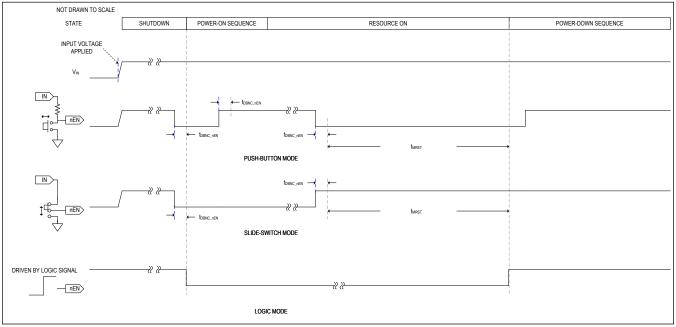

The nEN input can be configured to work with a push-button (CNFG\_GLBL\_A.nEN\_MODE[1:0] = 0x0), a slide-switch (CNFG\_GLBL\_A.nEN\_MODE[1:0] = 0x1), or a logic output of an external device (CNFG\_GLBL\_A.nEN\_MODE[1:0] = 0x2). See <u>Figure 2</u> for more information. In both push-button and slide-switch modes, the on/off controller looks for a falling edge on the nEN input to initiate a power-up sequence. In logic mode, the on/off controller initiates a power-up or power-down sequence depending on the nEN value. There is no debouncing for logic mode.

#### **nEN Manual Reset**

The nEN pin works as a manual reset input when the on/off controller is in the Resource On state. The manual reset function is useful for forcing a power-down in case communication with the processor fails. When nEN is configured for push-button mode and the input is asserted (nEN = LOW) for an extended period (t<sub>MRST</sub>), the on/off controller initiates a power-down sequence and goes to shutdown mode. When nEN is configured for slide-switch mode and the input is deasserted (nEN = HIGH) for an extended period (t<sub>MRST</sub>), the on/off controller initiates a power-down sequence and goes to shutdown mode. Logic mode does not depend on a manual reset time (t<sub>MRST</sub>), so when nEN is pulled high, the on/off controller initiates a power-down sequence and goes to shutdown mode. In all modes, the ERCFLAG.MRST flag sets to indicate a reset occurred.

#### nEN Triple Functionality: Push-Button vs. Slide-Switch vs. Logic

The nEN digital input can be configured to work with a push-button switch, a slide-switch, or a logic output. <u>Figure 2</u> shows nEN's triple functionality for power-on sequencing and manual reset.

Figure 2. nEN Usage Timing Diagram

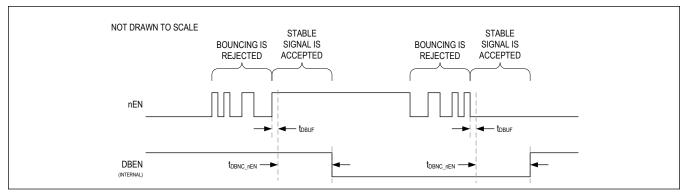

#### **Debounced Input**

The nEN is debounced on both rising and falling edges to reject undesired transitions. The input must be at a stable logic level for the entire debounce period for the output to change its logic state. Figure 3 shows an example timing diagram for the nEN debounce.

Figure 3. Debounced Input

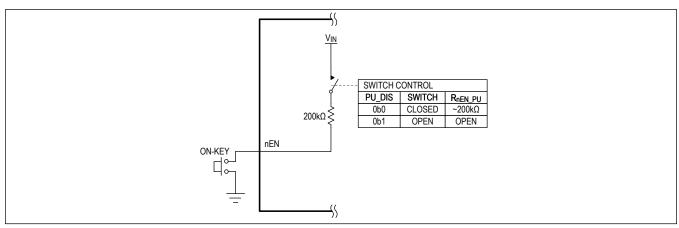

#### nEN Internal Pullup Resistors to VIN

The nEN logic thresholds are referenced to  $V_{IN}$ . There is an internal pullup resistor between nEN and  $V_{IN}$  ( $R_{nEN\_PU}$ ), which can be enabled by setting CNFG\_GLBL\_A.PU\_DIS = 0. See <u>Figure 4</u>. While enabled, the pullup value is approximately  $200k\Omega$ . While PU\_DIS = 1, the nEN node has high impedance.

Applications using a slide-switch on-key or push-pull digital output connected to nEN can reduce quiescent current consumption by disabling the pullup resistor. Applications using normally-open, momentary, and push-button on-keys (as shown in Figure 4) can use the internal resistor to avoid external components.

Figure 4. nEN Pullup Resistor Configuration

#### Interrupts (nIRQ)

Several status, interrupt, and interrupt mask registers monitor key information and update when an interrupt event has occurred. See the *Register Map* section for a comprehensive list of all interrupt bits and status registers.

Depending on OTP, some or all interrupts are masked by default. Initialization software should unmask interrupts of interest.

#### MAX77675

## Low I<sub>Q</sub> SIMO PMIC with 0.5V to 5.5V Outputs Delivering Up to 700mA Total Output Current

The nIRQ is an active-low, open-drain output typically routed to a processor's interrupt input for triggering off interrupt events. When any unmasked interrupt occurs, this pin is asserted (LOW). A pullup resistor is required for this signal, and is typically found inside the host processor. If one is unavailable, a board-mounted pullup resistor is required.

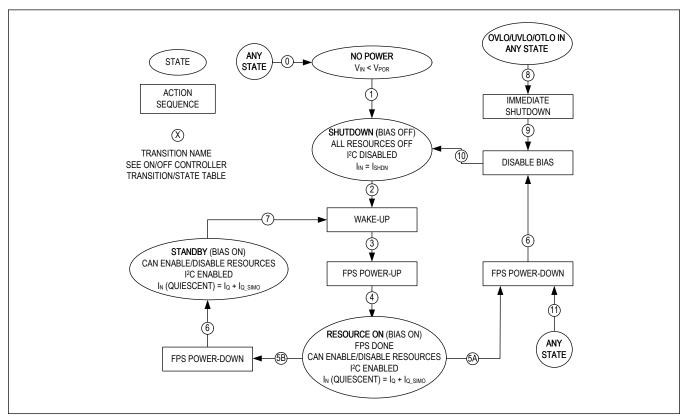

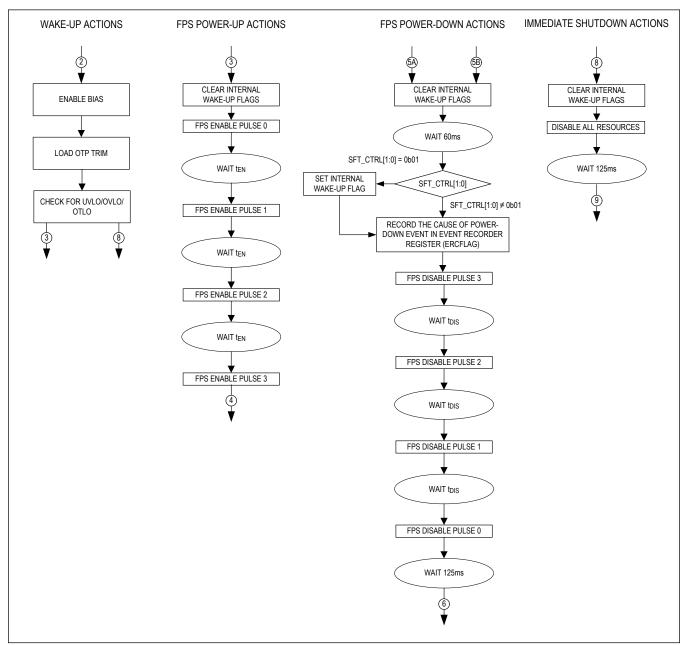

#### **On/Off Controller**

The on/off controller monitors multiple power-up (wake-up) and power-down (shutdown) conditions to enable or disable resources that are necessary for the system and its processor to move between its operating modes.

Many systems have one power management controller and one processor and rely on the on/off controller to be the master controller. In this case, the on/off controller receives the wake-up events and enables some or all of the regulators in order to power up a processor. This processor then manages the system. To conceptualize this operation, see <u>Figure</u> 5 and <u>Table 2</u>. A typical path through the on/off controller during power-up is as follows:

- 1. Apply power to IN and start in the Shutdown state.

- 2. Press the system's on-key (nEN = LOW) and follow transitions 2, 3A, and 4 to the Resource On state.