# 10-Channel Precision Synchronizer

#### **FEATURES**

- 10 BSYNC channels

- Precise BSYNC time alignment (<5 ps)</li>

- Enables clock synchronization in large distribution networks

- ▶ Independent programmable BSYNC channel delay

- Precise path delay compensation of each BSYNC channel using bidirectional loopback capability

- Flexible physical interface supports PCB trace or cable connections with DC or AC coupling

- Each BSYNC channel supports gapped periodic clocking

- ▶ Integrated TDC

- Integrated temperature sensor

#### **APPLICATIONS**

- ▶ 5G timing transport high precision synchronization

- Phased array radar

- Automatic test equipment (ATE) pin electronics

- JESD204B/JESD204C support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking

#### **GENERAL DESCRIPTION**

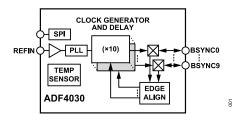

The ADF4030 provides for 10 bidirectional synchronized clock (BSYNC) channels and accepts a reference clock input (REFIN) signal as a frequency reference for generating an output clock on any BSYNC channels that are configured as an output. The hallmark feature of the ADF4030 is the ability to time align the clock edges of any one or more BSYNC channels to <5 ps (at the device pins) with respect to the BSYNC channel selected as the reference BSYNC channel.

The ADF4030 is well adapted for multiple connections with other ADF4030 devices for synchronizing clock signals in a system. Each BSYNC is bidirectional, allowing for reversing the direction of the clock signal to measure the propagation delay of the transmission medium. Round trip constructions that use replica paths are also supported. The bidirectional nature of the round trip delay measurement greatly reduces the error in determining the propagation delay through the BSYNC transmission medium as compared to using a replica path. This feature makes the ADF4030 capable to time align the clock edges of BSYNC channels across multiple ADF4030 devices, independent of the tree or cascade architecture in which the ADF4030 system is designed. The benefits of bidirectional clocking extend to devices other than the ADF4030 (assuming those devices support bidirectional clock exchanges).

The output divider block associated with each BYSNC channel has an optional pseudorandom binary sequence (PRBS) generator for

## FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

producing gapped periodic clock signals that supports JESD204B and JESD204BC operation.

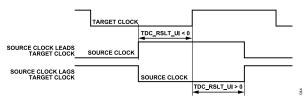

The ADF4030 may be used as a standalone differential time-to-digital converter (TDC) to measure the difference in time between clocks arriving at the inputs.

The RMS jitter of one ADF4030 BSYNC clock is 4.3 ps typical.

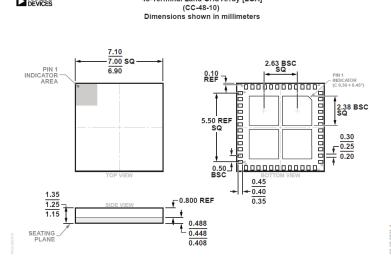

The ADF4030 is available in a 48-lead, 7 mm × 7 mm, land grid array [LGA] package and operates over the  $-40^{\circ}$ C to  $+105^{\circ}$ C ambient temperature range.

Throughout the data sheet, the letter x is used to mean any integer. For example, in BSYNCx, x refers to any channel from Channel 0 to Channel 9.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| Functional Block Diagram                     |    |

| General Description.                         |    |

| Specifications                               | 3  |

| Serial Interface Timing Characteristics      | 7  |

| Absolute Maximum Ratings                     | 8  |

| Transistor Count                             |    |

| Thermal Resistance                           | 8  |

| Electrostatic Discharge (ESD) Ratings        | 8  |

| ESD Caution                                  | 8  |

| Pin Configuration and Function Descriptions. | 9  |

| Typical Performance Characteristics          | 11 |

| Device Initialization                        | 13 |

| Theory of Operation                          | 14 |

| Device Overview                              | 14 |

| Reference Clock Input (REFIN)                | 14 |

| PLL                                          | 15 |

| Digital Core Clock                           | 15 |

| CMOS Output Pin Logic High Control           | 16 |

| BSYNC Channels                               | 16 |

|                                              |    |

# **REVISION HISTORY**

10/2024—Revision 0: Initial Version

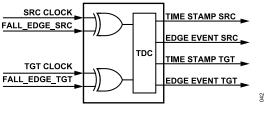

| Differential Time-to-Digital Converter (dTDC) | 22   |

|-----------------------------------------------|------|

| Measurement Time Estimation                   | .25  |

| Duty Cycle Measurement                        | .25  |

| Maximum BSYNC Frequency Reduction vs.         |      |

| Duty Cycle                                    | .25  |

| Temperature Measurement System                | . 25 |

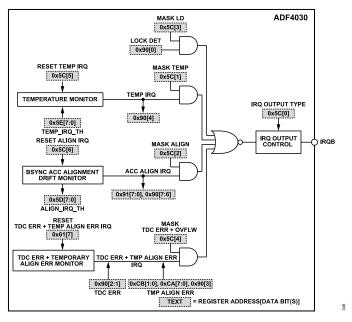

| Interrupt Request (IRQ)                       | .27  |

| MUXOUT1 and MUXOUT2                           |      |

| Programmable Power Down Options               | . 30 |

| SPI Operation                                 | .32  |

| Applications Information                      |      |

| TDC Measurement                               | . 35 |

| Open-Loop Delay Adjustment                    | . 35 |

| Closed-Loop Delay Adjustment                  | .36  |

| BSYNC Channel Alignment                       | .37  |

| Measuring Alignment Results                   | .39  |

| Register Map                                  |      |

| Register Details                              | . 46 |

| Outline Dimensions                            |      |

| Ordering Guide                                | .86  |

| Evaluation Boards                             |      |

The minimum and maximum values apply for the full range of supply voltage and operating temperature variations. Typical values apply for VDD18x = 1.8 V, VDD33x = 3.3 V, and  $T_A = 25^{\circ}$ C, unless otherwise noted.

| Parameter                             | Min  | Тур  | Max  | Units | Test Conditions/Comments                                                                                                                                                        |

|---------------------------------------|------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPERATING TEMPERATURE                 |      |      |      |       |                                                                                                                                                                                 |

| Ambient Temperature                   | -40  | +25  | +105 | °C    | T <sub>J</sub> ≤ 125 °C                                                                                                                                                         |

| Die Temperature                       |      |      | 125  | °C    |                                                                                                                                                                                 |

| SUPPLY VOLTAGE                        |      |      |      |       |                                                                                                                                                                                 |

| VDD18x                                | 1.71 | 1.8  | 1.89 | V     |                                                                                                                                                                                 |

| VDD33x                                | 3.15 | 3.3  | 3.45 | V     |                                                                                                                                                                                 |

| SUPPLY CURRENT                        |      |      |      |       |                                                                                                                                                                                 |

| VDD33_PLL                             |      | 102  | 121  | mA    |                                                                                                                                                                                 |

| VDD33_TDC                             |      | 15   | 19   | mA    |                                                                                                                                                                                 |

| VDD18_DIG and VDD18_TDC<br>VDD33_BSx  |      | 30   | 37   | mA    | $f_{CORECLK}^{1}$ = 125 MHz, $f_{BSYNC}^{2}$ = 200 MHz                                                                                                                          |

| BSYNCx Receiver Disabled <sup>3</sup> |      | 0.2  | 180  | μA    | Transmitter path (driver and delay lines) powered down <sup>4</sup>                                                                                                             |

|                                       |      | 6.1  | 8    | mA    | Transmitter path (driver and delay lines) powered down and AC-coupled biasing <sup>5</sup>                                                                                      |

|                                       |      | 22.3 | 27   | mA    | Transmitter driver powered down and delay lines powered $up^6$                                                                                                                  |

|                                       |      | 27.3 | 33   | mA    | Transmitter driver powered up and idle and delay lines powered $\ensuremath{\text{up}}^7$                                                                                       |

|                                       |      | 54.3 | 65   | mA    | Transmitter driver powered up and enabled and delay lines powered up <sup>8</sup>                                                                                               |

|                                       |      | 60.6 | 72   | mA    | Transmitter driver powered up and enabled, delay lines powered up, and 20 mA driver <sup>9</sup>                                                                                |

| BSYNCx Receiver Enabled <sup>10</sup> |      | 16.4 | 20   | mA    | Transmitter path (driver and delay lines) powered down <sup>11</sup>                                                                                                            |

|                                       |      | 22.5 | 28   | mA    | Transmitter path (driver and delay lines) powered down and AC-coupled $\mbox{biasing}^5$                                                                                        |

|                                       |      | 38.6 | 47   | mA    | Transmitter driver powered down and delay lines powered up $^{6}\mbox{)}$                                                                                                       |

|                                       |      | 43.6 | 53   | mA    | Transmitter driver powered up and idle and delay lines powered $\ensuremath{up}^7$                                                                                              |

|                                       |      | 70.6 | 84   | mA    | Transmitter driver powered up and enabled and delay lines powered $\ensuremath{up}^8$                                                                                           |

|                                       |      | 76.9 | 92   | mA    | Transmitter driver powered up and enabled, delay lines powered up, and 20 mA driver <sup>9</sup>                                                                                |

| TOTAL POWER DISSIPATION               |      |      |      |       |                                                                                                                                                                                 |

| Configuration 1                       |      | 2.3  | 2.9  | W     | REFIN = 100 MHz, BSYNC0 to BSYNC9 transmit<br>nongapped 100 MHz with driver current at 14 mA                                                                                    |

| Configuration 2                       |      | 2.1  | 2.7  | W     | REFIN = 100 MHz, nine BSYNCx transmit nongapped<br>100 MHz with driver current at 14 mA and one BSYNCx<br>receives 100 MHz                                                      |

| Configuration 3                       |      | 0.5  | 0.7  | W     | REFIN = 100 MHz, BSYNC0 to BSYNC9 receive 100 MHz                                                                                                                               |

| Configuration 4                       |      | 1.4  | 1.8  | W     | REFIN = 100 MHz, one BSYNCx transmits nongapped<br>100 MHz with driver current at 14 mA, one BSYNCx<br>receives 100 MHz, and all others set to transmit with<br>driver disabled |

#### Table 1. Specifications (Continued)

| Parameter                                             | Min  | Тур  | Max  | Units  | Test Conditions/Comments                                                                                                                                                          |

|-------------------------------------------------------|------|------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DOWN CURRENT                                    |      |      |      |        | PD_ALL = 1                                                                                                                                                                        |

| 1.8 V Supplies                                        |      | 2    | 500  | μA     | IVDD18 DIG + IVDD18 TDC                                                                                                                                                           |

| 3.3 V Supplies                                        |      | 0.2  | 2.5  | mA     | IVDD33_BS0 + IVDD33_BS1 + + IVDD33_BS9 + IVDD33_PLL +<br>IVDD33_TDC                                                                                                               |

| REFERENCE CLOCK INPUT                                 |      |      |      |        |                                                                                                                                                                                   |

| Differential Mode                                     |      |      |      |        |                                                                                                                                                                                   |

| Input Frequency                                       | 10   |      | 250  | MHz    |                                                                                                                                                                                   |

| Differential Input Voltage                            | 160  | 350  | 1000 | mV p-p | Can accommodate single ended inputs via AC grounding of unused inputs and 100 $\Omega$ resistor connected to GND, and instantaneous voltage on each pin must not exceed VDD33_PLL |

| Minimum Input Slew Rate                               |      | 500  |      | V/µs   |                                                                                                                                                                                   |

| Common-Mode Internally Generated<br>Input Voltage     |      | 1.85 |      | V      | Provided for information only; AC coupling is recommended                                                                                                                         |

| Differential Input Resistance                         |      | 3    |      | kΩ     |                                                                                                                                                                                   |

| Differential Input Capacitance                        |      | 1    |      | pF     |                                                                                                                                                                                   |

| Minimum Duty Cycle                                    |      | 40   |      | %      |                                                                                                                                                                                   |

| Maximum Duty Cycle                                    |      | 60   |      | %      |                                                                                                                                                                                   |

| Concept Peak Detector                                 |      |      |      |        |                                                                                                                                                                                   |

| Minimum Input Signal Detected<br>(REF_OK Bit = 1)     |      | 100  |      | mV p-p |                                                                                                                                                                                   |

| Maximum Input Signal Not Detected<br>(REF_OK Bit = 0) |      | 80   |      | mV p-p |                                                                                                                                                                                   |

| PHASE-LOCKED LOOP (PLL)                               |      |      |      |        |                                                                                                                                                                                   |

| Phase/Frequency Detector (PFD)                        | 10   |      | 20   | MHz    |                                                                                                                                                                                   |

| Minimum Charge Pump Current                           |      | 360  |      | μA     | 2-bit resolution                                                                                                                                                                  |

| Maximum Charge Pump Current                           |      | 630  |      | μA     | 2-bit resolution                                                                                                                                                                  |

| Voltage-Controlled Oscillator (VCO)                   |      |      |      |        |                                                                                                                                                                                   |

| Frequency Range                                       | 2375 |      | 2625 | MHz    | 2500 MHz ± 5%                                                                                                                                                                     |

| BYSNC                                                 |      |      |      |        |                                                                                                                                                                                   |

| Frequency                                             | 0.65 |      | 200  | MHz    |                                                                                                                                                                                   |

| BSYNC Transmit                                        |      |      |      |        |                                                                                                                                                                                   |

| Rise Time and Fall Time (20% to 80%)                  |      | 80   |      | ps     | 100 $\boldsymbol{\Omega}$ terminations for BSYNC transmit                                                                                                                         |

| Duty Cycle                                            | 45   | 50   | 55   | %      |                                                                                                                                                                                   |

| Differential Output Voltage Swing                     | 290  | 350  | 410  | mV p-p | 14 mA driver current and 100 $\Omega$ termination at destination                                                                                                                  |

|                                                       | 410  | 500  | 590  | mV p-p | 20 mA driver current and 100 $\Omega$ termination at destination                                                                                                                  |

| Common-Mode Output Voltage                            | 0.43 | 0.5  | 0.57 | v      | RCM = 1 and 14 mA driver current                                                                                                                                                  |

|                                                       | 0.66 | 0.8  | 0.94 | V      | RCM = 51 and 14 mA driver current                                                                                                                                                 |

|                                                       | 0.98 | 1.2  | 1.42 | V      | RCM = 62 and 14 mA driver current                                                                                                                                                 |

|                                                       | 0.68 | 0.8  | 0.92 | V      | RCM = 21 and 20 mA driver current                                                                                                                                                 |

|                                                       | 1.0  | 1.2  | 1.4  | V      | RCM = 52 and 20 mA driver current                                                                                                                                                 |

| Common-Mode Difference                                |      |      | 15   | mV     | Voltage difference between output pins and output driver static                                                                                                                   |

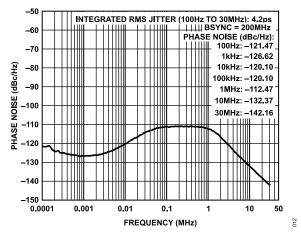

| RMS Jitter One Channel<br>BSYNC Receive               |      | 4.3  |      | ps     | Between 100 Hz and 30 MHz                                                                                                                                                         |

| Instantaneous BSYNC Pin Voltage                       | 0    |      | 1.9  | V      | Instantaneous voltage on each pin must not fall under 0 \<br>or exceed 1.9 V                                                                                                      |

|                                                       | 1    |      | 4000 |        |                                                                                                                                                                                   |

| Differential Input Voltage                            | 200  | 330  | 1000 | mV p-p |                                                                                                                                                                                   |

#### Table 1. Specifications (Continued)

| Parameter                                         | Min                 | Тур    | Max  | Units | Test Conditions/Comments                                                                                                                               |

|---------------------------------------------------|---------------------|--------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Common-Mode Internally Generated<br>Input Voltage |                     | 0.84   |      | V     |                                                                                                                                                        |

| Input Common-Mode Range (V <sub>CMI</sub> )       | 300                 |        | 1600 | mV    | DC coupling supported                                                                                                                                  |

| Differential Input Resistance                     |                     | 640    |      | kΩ    | External differential termination                                                                                                                      |

| Differential Input Capacitance                    |                     | 1      |      | pF    | External differential termination                                                                                                                      |

| Duty Cycle                                        | 48                  | 50     | 52   | %     | 187 MHz < f <sub>BSYNC</sub> ≤ 200 MHz                                                                                                                 |

|                                                   | 45                  | 50     | 55   | %     | $f_{BSYNC} \le 187$ MHz. See the Maximum BSYNC Frequency<br>Reduction vs. Duty Cycle section if duty cycle is outside<br>45% to 55% range              |

| BSYNC ALIGNMENT                                   |                     |        |      |       | AVGEXP $\geq$ 12, t <sub>RISE</sub> < 300 ps or $\Delta t_{RISE}$ < 100 ps, V <sub>CMI</sub> = 0.35 V to 1 V or $\Delta V_{CMI}$ < 75 mV <sup>12</sup> |

| Maximum BSYNC Alignment Error                     |                     | ± 5    |      | ps    | At the ADF4030 pin level, nongapped periodic clocks or gapped periodic clocks with TDC time difference > 350 ps                                        |

|                                                   |                     | ± 17   |      | ps    | At the ADF4030 pin level, gapped periodic clocks with TDC time difference < 350 ps                                                                     |

| REFIN to BSYNC Temperature<br>Coefficient         |                     | +160   |      | fs/°C | Independent of REFIN drift with temperature                                                                                                            |

| BSYNC to BSYNC Temperature<br>Coefficient         |                     | ± 30   |      | fs/°C | Independent of REFIN drift with temperature                                                                                                            |

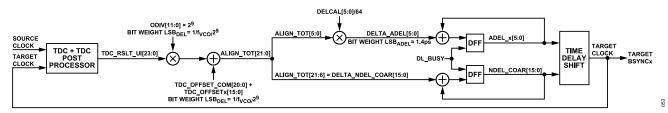

| Fine Delay Step Size                              |                     | 1.4    |      | ps    | Least significant bit of Bits[5:0], ADEL_x, Register 0x84 to Register 0x8D                                                                             |

| Intermediate Delay Step Size                      |                     | 50     |      | ps    | 1/8 of f <sub>VCO</sub> = 2.5 GHz period and least significant bit of Bits[15:0], DELTA_NDEL_COAR, Register 0x18 and Register 0x19                     |

| TDC                                               |                     |        |      |       | $t_{\rm RISE}$ < 300 ps or $\Delta t_{\rm RISE}$ < 100 ps and V_{CMI} = 0.35 V to 1 V or $\Delta V_{CMI}$ < 75 mV                                      |

| TDC Resolution                                    |                     | 21     |      | μ°    | 24 Bits                                                                                                                                                |

| TDC Accuracy                                      |                     | ± 3.6  |      | ps    | Nongapped periodic clocks or gapped periodic clocks with TDC time difference > 350 ps                                                                  |

|                                                   |                     | ± 15.6 |      | ps    | Gapped periodic clocks with (TDC input) TDC time difference < 350 ps                                                                                   |

| TEMPERATURE MEASUREMENT<br>SYSTEM                 |                     |        |      |       |                                                                                                                                                        |

| Output Resolution                                 |                     | 1      |      | 0°    |                                                                                                                                                        |

| Conversion Time                                   |                     | 42.5   |      | μs    | 17 cycles at ADCCLK = 1/400 kHz                                                                                                                        |

| SDO, SDIO, IRQB, MUXOUT1, and MUXOUT2 OUTPUT      |                     |        |      |       |                                                                                                                                                        |

| SDO High-Z Leakage                                |                     |        | ±1   | μA    |                                                                                                                                                        |

| Output Voltage High                               | VDD18_DIG -<br>0.3V |        |      | V     | 1.8 V logic, load current = 1 mA                                                                                                                       |

|                                                   | VDD33_TDC -<br>0.3V |        |      | V     | 3.3 V logic, load current = 1 mA                                                                                                                       |

| Output Voltage Low                                |                     |        | 0.4  | V     | 1.8 V or 3.3 V logic, load current = 1 mA                                                                                                              |

| IRQB Open Drain Mode                              |                     |        |      |       | IRQB_OPENDRAIN bit set to 1 and external 1 k $\Omega$ pull-up resistor set to 1.8 V or 3.3 V function of CMOS_OV bit                                   |

| Output High Leakage                               |                     |        | 1    | μA    | IRQB pin pulled to 3.3 V                                                                                                                               |

| Output Voltage Low                                |                     |        | 0.4  | V     | When external 1 k $\Omega$ pull-up resistor to 3.3 V                                                                                                   |

| Maximum Supported Sink Current                    |                     |        | 5    | mA    |                                                                                                                                                        |

#### Table 1. Specifications (Continued)

| Parameter                                            | Min | Тур | Мах | Units | Test Conditions/Comments             |

|------------------------------------------------------|-----|-----|-----|-------|--------------------------------------|

| ADDR0, ADDR1, ADDR2, ADDR3, CS, SCLK, and SDIO INPUT |     |     |     |       |                                      |

| Input Voltage High                                   | 1.2 |     |     | V     | 1.8 V or 3.3 V logic                 |

| Input Voltage Low                                    |     |     | 0.6 | V     | 1.8 V or 3.3 V logic                 |

| Input Current                                        |     |     | ±1  | μA    | For both high and low input voltages |

<sup>1</sup> Digital core clock frequency.

<sup>2</sup> BSYNC frequency.

<sup>3</sup> Channel not selected as TDC source or target.

<sup>4</sup> PD\_TX\_PATH\_x = 1.

<sup>5</sup> PD\_TX\_PATH\_x = 1, AC\_COUPLEDx = 1.

- <sup>6</sup> PD\_TX\_PATH\_x = 0, PD\_DRV\_x = 1.

- <sup>7</sup> PD\_TX\_PATH\_x = 0, PD\_DRV\_x = 0, EN\_DRVx = 0.

- <sup>8</sup> PD\_TX\_PATH\_x = 0, PD\_DRV\_x = 0, EN\_DRVx = 1.

- <sup>9</sup> PD\_TX\_PATH\_x = 0, PD\_DRV\_x = 0, EN\_DRVx = 1, BOOSTx = 1.

<sup>10</sup> Channel selected as TDC source or target.

<sup>11</sup> PD\_TX\_PATH\_x = 1.

$^{12}$   $\Delta V_{CMI}$  is difference between the BSYNC channels

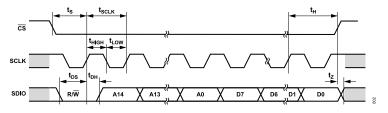

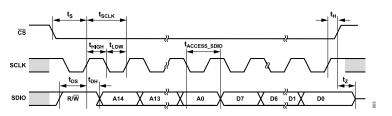

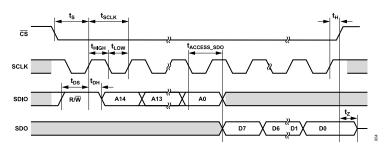

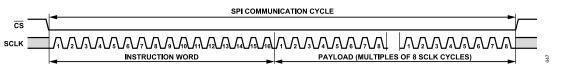

## SERIAL INTERFACE TIMING CHARACTERISTICS

#### Table 2. Serial Interface Timing Characteristics

| Parameter                                                                     | Min | Тур | Мах | Units | Test Conditions/Comments                                                            |

|-------------------------------------------------------------------------------|-----|-----|-----|-------|-------------------------------------------------------------------------------------|

| SCLK Frequency                                                                |     |     | 75  | MHz   |                                                                                     |

| SCLK Pulse High (t <sub>HIGH</sub> )                                          | 6   |     |     | ns    | All timing specifications measured at the<br>output high range (VIH) = 1.2 V levels |

| SCLK Pulse Low (t <sub>LOW</sub> )                                            | 6   |     |     | ns    |                                                                                     |

| SDIO Setup Time (t <sub>DS</sub> )                                            | 4   |     |     | ns    |                                                                                     |

| SDIO Hold Time (t <sub>DH</sub> )                                             | 2   |     |     | ns    |                                                                                     |

| SCLK Fall Edge to SDIO Valid Prop Delay (t <sub>ACCESS_SDIO</sub> )           | 6   |     |     | ns    |                                                                                     |

| SCLK Fall Edge to SDO Valid Prop Delay (t <sub>ACCESS SDO</sub> )             | 6   |     |     | ns    |                                                                                     |

| CS Rising Edge to SDIO High-Z (t <sub>Z</sub> )                               | 6   |     |     | ns    |                                                                                     |

| $\overline{\text{CS}}$ Falling Edge to SCLK Rise Setup Time (t <sub>S</sub> ) | 2   |     |     | ns    |                                                                                     |

| SCLK Rising Edge to $\overline{CS}$ Rise Hold Time (t <sub>H</sub> )          | 3   |     |     | ns    |                                                                                     |

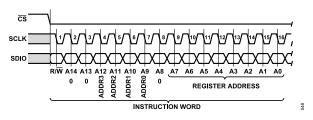

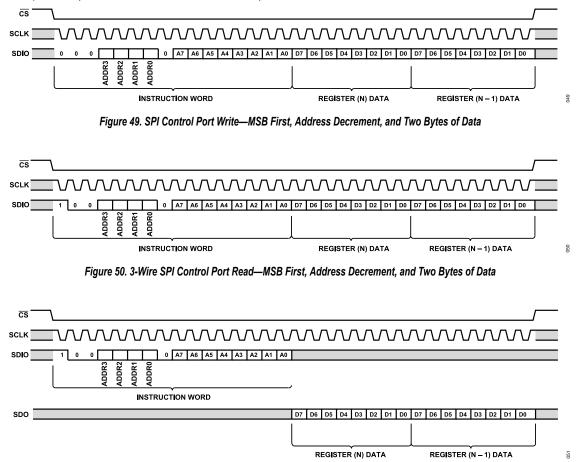

Address bits A[14], A[13], and A[8] are always 0. A[12:9] map to the ADDR3, ADDR2, ADDR1, and ADDR0 pins, respectively. A[7:0] represent the register addresses in Figure 2, Figure 3, and Figure 4.

#### Figure 2. Write Timing Diagram

Figure 3. 3-Wire Read Timing Diagram

Figure 4. 4-Wire Read Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 3. Absolute Maximum Ratings

| Parameter                                                | Rating                             |

|----------------------------------------------------------|------------------------------------|

| VDD33_BS0, VDD33_BS1,                                    | -0.3 V to +3.6 V                   |

| VDD33_BS2, VDD33_BS3,                                    |                                    |

| VDD33_BS4, VDD33_BS5,                                    |                                    |

| VDD33_BS6, VDD33_BS7,                                    |                                    |

| VDD33_BS8, VDD33_BS9,                                    |                                    |

| VDD33_TDC, and VDD33_PLL to GND                          |                                    |

| VDD18_DIG, VDD18_TDC to GND                              | -0.3 V to +2.0 V                   |

| REFIN+, REFIN-                                           | -0.675 V to VDD33_PLL + 0.675 V    |

| REFIN+ to REFIN-                                         | -1.35 V to +1.35 V                 |

| BSYNC0+, BSYNC0-, BSYNC1+,                               | -0.3 V to Maximum (+0.3 V, VDD_BSx |

| BSYNC1-, BSYNC2+, BSYNC2-,                               | – 0.8 V)                           |

| BSYNC3+, BSYNC3-, BSYNC4+,                               |                                    |

| BSYNC4-, BSYNC5+, BSYNC5-,                               |                                    |

| BSYNC6+, BSYNC6-, BSYNC7+,<br>BSYNC7-, BSYNC8+, BSYNC8-, |                                    |

| BSYNC9+, and BSYNC9- Inputs                              |                                    |

| BSYNCx+ to BSYNCx- $(x = 0, 1,, 9)$                      | -1.35 V to +1.35 V                 |

| Voltage on all other pins                                | -0.3 V to VDD33 PLL + 0.3 V        |

| Temperature                                              |                                    |

| Operating Junction Range <sup>1</sup>                    | -40 °C to +125°C                   |

| Junction                                                 | 150°C                              |

| Storage Range                                            | -55 °C to +150°C                   |

| Peak <sup>2</sup>                                        | 260 °C                             |

<sup>1</sup> Device is guaranteed to meet the specified performance limits over the full operating junction temperature range.

<sup>2</sup> Analog Devices, Inc., recommends that reflow profiles used in soldering RoHScompliant devices conform to J-STD-020D.1 from JEDEC. Refer to JEDEC for the latest revision of this standard.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **TRANSISTOR COUNT**

The transistor counts for the ADF4030 are 312642 (CMOS) and 7771 (bipolar).

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the junction to ambient thermal resistance measured in a natural convection JEDEC environment.

$\theta_{JC-TOP}$  and  $\theta_{JC-BOTTOM}$  are the JEDEC thermal resistances of the junction-to-top of case and junction-to-bottom of case, respectively.

$\theta_{JB}$  is the junction-to-board JEDEC thermal resistance.

$\Psi_{\text{JT}}$  is the junction-to-top of case JEDEC thermal characterization parameter.

$\Psi_{\text{JB}}$  is the junction-to-board JEDEC thermal characterization parameter.

#### Table 4. Thermal Resistance

| Package Type          | $\theta_{JA}$ | θ <sub>JC-TOP</sub> | θ <sub>JC-BOTTOM</sub> | $\theta_{JB}$ | $\Psi_{JT}$ | $\Psi_{JB}$ | Unit |

|-----------------------|---------------|---------------------|------------------------|---------------|-------------|-------------|------|

| CC-48-10 <sup>1</sup> | 42.2          | 22.0                | 21.3                   | 28.6          | 1.8         | 28.0        | °C/W |

<sup>1</sup> Test Condition: thermal impedance simulated values are based on use of a 6-layer PCB with the thermal impedance paddle soldered to a ground plane.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD-protected area only. Human body model (HBM) per ANSI/ESDA/JEDEC JS-001. Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

# ESD Ratings for ADF4030

#### Table 5. ADF4030, 48-Terminal LGA

| ESD Model | Withstand Threshold (V) | Class |  |  |

|-----------|-------------------------|-------|--|--|

| HBM       | 3500                    | 2     |  |  |

| CDM       | 1250                    | C3    |  |  |

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

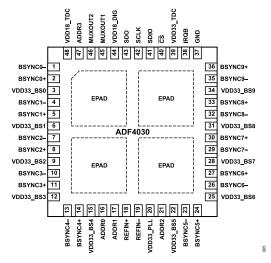

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

#### Table 6. Pin Function Descriptions

| Pin No. | Pin Name  | Pin Type <sup>1</sup> | Description                                                                                                                                                                                                                                      |

|---------|-----------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | BSYNC0-   | I/O                   | Complementary Bidirectional Clock, Channel 0.                                                                                                                                                                                                    |

| 2       | BSYNC0+   | I/O                   | Normal Bidirectional Clock, Channel 0.                                                                                                                                                                                                           |

| 3       | VDD33_BS0 | Power                 | 3.3 V Supply to BSYNC Channel 0.                                                                                                                                                                                                                 |

| 4       | BSYNC1-   | I/O                   | Complementary Bidirectional Clock, Channel 1.                                                                                                                                                                                                    |

| 5       | BSYNC1+   | I/O                   | Normal Bidirectional Clock, Channel 1.                                                                                                                                                                                                           |

| 6       | VDD33_BS1 | Power                 | 3.3 V Supply to BSYNC Channel 1.                                                                                                                                                                                                                 |

| 7       | BSYNC2-   | I/O                   | Complementary Bidirectional Clock, Channel 2.                                                                                                                                                                                                    |

| 8       | BSYNC2+   | I/O                   | Normal Bidirectional Clock, Channel 2.                                                                                                                                                                                                           |

| 9       | VDD33_BS2 | Power                 | 3.3 V Supply to BSYNC Channel 2.                                                                                                                                                                                                                 |

| 10      | BSYNC3-   | I/O                   | Complementary Bidirectional Clock, Channel 3.                                                                                                                                                                                                    |

| 11      | BSYNC3+   | I/O                   | Normal Bidirectional Clock, Channel 3.                                                                                                                                                                                                           |

| 12      | VDD33_BS3 | Power                 | 3.3 V Supply to BSYNC Channel 3.                                                                                                                                                                                                                 |

| 13      | BSYNC4-   | I/O                   | Complementary Bidirectional Clock, Channel 4.                                                                                                                                                                                                    |

| 14      | BSYNC4+   | I/O                   | Normal Bidirectional Clock, Channel 4.                                                                                                                                                                                                           |

| 15      | VDD33_BS4 | Power                 | 3.3 V Supply to BSYNC Channel 4.                                                                                                                                                                                                                 |

| 16      | ADDR0     | I                     | Bit 0 of Serial Port Interface (SPI) Extended Address. Floating 1.8 V or 3.3 V CMOS input with no internal pull-up or pull-down resistors. Tie ADDR0 to GND, 1.8 V, or 3.3 V to define the Bit A[9] in the SPI instruction word (see Figure 48). |

| 17      | ADDR1     | I                     | Bit 1 of SPI Extended Address. Floating 1.8 V or 3.3 V CMOS input with no internal pull-up or pull-down resistors. Tie ADDR1 to GND, 1.8 V, or 3.3 V to define the Bit A[10] in the SPI instruction word (see Figure 48).                        |

| 18      | REFIN+    | 1                     | Normal Reference Clock Input.                                                                                                                                                                                                                    |

| 19      | REFIN-    | 1                     | Complementary Reference Clock Input.                                                                                                                                                                                                             |

| 20      | VDD33_PLL | Power                 | 3.3 V Supply to PLL.                                                                                                                                                                                                                             |

| 21      | ADDR2     | I                     | Bit 2 of SPI Extended Address. Floating 1.8 V or 3.3 V CMOS input with no internal pull-up or pull-down resistors. Tie ADDR2 to GND, 1.8 V, or 3.3 V to define the Bit A[11] in the SPI instruction word (see Figure 48).                        |

| 22      | VDD33_BS5 | Power                 | 3.3 V Supply to BSYNC Channel 5.                                                                                                                                                                                                                 |

| 23      | BSYNC5-   | I/O                   | Complementary Bidirectional Clock, Channel 5.                                                                                                                                                                                                    |

| 24      | BSYNC5+   | I/O                   | Normal Bidirectional Clock, Channel 5.                                                                                                                                                                                                           |

| 25      | VDD33_BS6 | Power                 | 3.3 V Supply to BSYNC Channel 6.                                                                                                                                                                                                                 |

| 26      | BSYNC6-   | I/O                   | Complementary Bidirectional Clock, Channel 6.                                                                                                                                                                                                    |

| 27      | BSYNC6+   | I/O                   | Normal Bidirectional Clock, Channel 6.                                                                                                                                                                                                           |

| 28      | VDD33_BS7 | Power                 | 3.3 V Supply to BSYNC Channel 7.                                                                                                                                                                                                                 |

| 29      | BSYNC7-   | I/O                   | Complementary Bidirectional Clock, Channel 7.                                                                                                                                                                                                    |

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 6. Pin Function Descriptions (Continued)

| Pin No. | Pin Name  | Pin Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                 |

|---------|-----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30      | BSYNC7+   | I/O                   | Normal bidirectional clock, Channel 7.                                                                                                                                                                                                                                                      |

| 31      | VDD33_BS8 | Power                 | 3.3 V Supply to BSYNC Channel 8.                                                                                                                                                                                                                                                            |

| 32      | BSYNC8-   | I/O                   | Complementary Bidirectional Clock, Channel 8.                                                                                                                                                                                                                                               |

| 33      | BSYNC8+   | I/O                   | Normal Bidirectional clock, Channel 8.                                                                                                                                                                                                                                                      |

| 34      | VDD33_BS9 | Power                 | 3.3 V Supply to BSYNC Channel 9.                                                                                                                                                                                                                                                            |

| 35      | BSYNC9-   | I/O                   | Complementary Bidirectional Clock, Channel 9.                                                                                                                                                                                                                                               |

| 36      | BSYNC9+   | I/O                   | Normal Bidirectional Clock, Channel 9.                                                                                                                                                                                                                                                      |

| 37      | GND       | Power                 | Ground Connection.                                                                                                                                                                                                                                                                          |

| 38      | IRQB      | 0                     | Interrupt Request. Programmable output mode and selectable internal interrupt source.                                                                                                                                                                                                       |

| 39      | VDD33_TDC | Power                 | 3.3 V Supply to Differential TDC.                                                                                                                                                                                                                                                           |

| 40      | CS        | 1                     | Serial Port Chip Select. 1.8 V or 3.3 V compatible CMOS input.                                                                                                                                                                                                                              |

| 41      | SDIO      | I/O                   | Serial Data Input/Output. 1.8 V or 3.3 V compatible CMOS input. 1.8 V or 3.3 V programmable serial CMOS output.<br>Bidirectional for 3-wire SPI mode. Input only for 4-wire SPI mode.                                                                                                       |

| 42      | SCLK      | 1                     | Serial Port Clock. 1.8 V or 3.3 V compatible CMOS input.                                                                                                                                                                                                                                    |

| 43      | SDO       | 0                     | Optional Serial Data Output. 1.8 V or 3.3 V programmable serial CMOS output. High-z for 3-wire SPI mode. Output only for 4-wire SPI mode. When $\overline{CS}$ is deasserted, SDO returns to high impedance. Optionally, attach a resistor of >200 k $\Omega$ to prevent a floating output. |

| 44      | VDD18_DIG | Power                 | 1.8 V Supply to Digital Core.                                                                                                                                                                                                                                                               |

| 45      | MUXOUT1   | 0                     | Access to Various Internal Test Points (programmable).                                                                                                                                                                                                                                      |

| 46      | MUXOUT2   | 0                     | Access to Various Internal Test Points (programmable).                                                                                                                                                                                                                                      |

| 47      | ADDR3     | 1                     | Bit 3 of SPI Extended Address. Floating 1.8 V or 3.3 V CMOS input with no internal pull-up or pull-down resistors. Tie ADDR3 to GND, 1.8 V, or 3.3 V to define the Bit A[12] in the SPI instruction word (see Figure 48).                                                                   |

| 48      | VDD18_TDC | Power                 | 1.8 V Supply to Differential TDC.                                                                                                                                                                                                                                                           |

|         | EPAD      | Power                 | Primary Ground Connection.                                                                                                                                                                                                                                                                  |

<sup>1</sup> I/O is input/output, I is input, and O is output.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

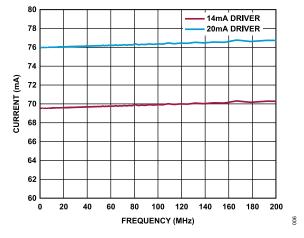

Figure 6. VDD33\_Bx Current vs. Output Frequency, BSYNCx Channel Transmits Clock and BSYNCx Receiver Enabled

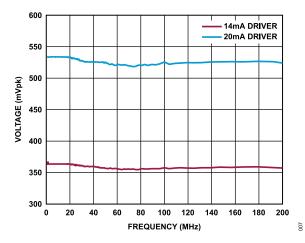

Figure 7. BSYNC Differential Voltage Swing vs. Output Frequency, BSYNC Channel Transmits Clock

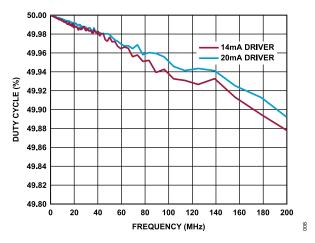

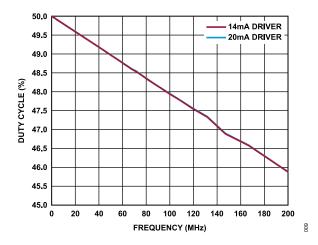

Figure 8. BSYNC Positive Duty Cycle vs. Output Frequency for Even ODIV Values, BSYNC Channel Transmits Clock

Figure 9. BSYNC Positive Duty Cycle vs. Output Frequency for Odd ODIV Values, BSYNC Channel Transmits Clock

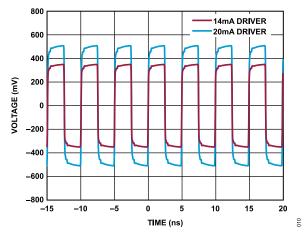

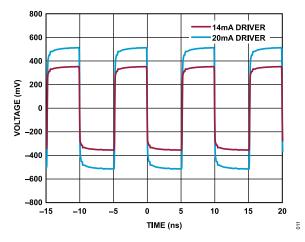

Figure 10. BSYNC Output Waveform, Differential, 200 MHz

Figure 11. BSYNC Output Waveform, Differential, 100 MHz

## **TYPICAL PERFORMANCE CHARACTERISTICS**

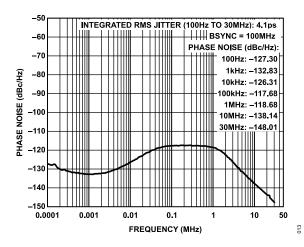

Figure 12. BSYNC Output Absolute Phase Noise, 200 MHz

Figure 13. BSYNC Output Absolute Phase Noise, 100 MHz

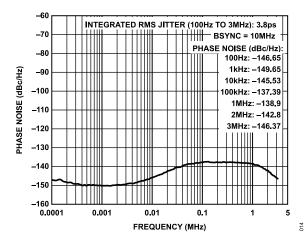

Figure 14. BSYNC Output Absolute Phase Noise, 10 MHz

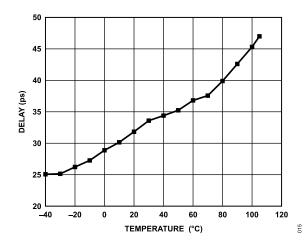

Figure 15. REFIN to BSYNC Propagation Delay over Temperature Range

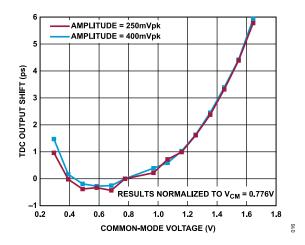

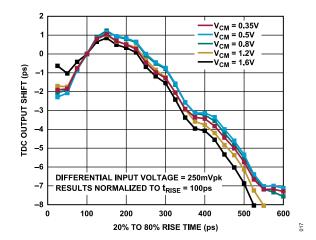

Figure 16. TDC Output Shift vs. Incoming BSYNC Common-Mode Voltage for Various Amplitudes

Figure 17. TDC Output Shift vs. Incoming BSYNC Time Rise for Various Common-Mode Voltages

#### **DEVICE INITIALIZATION**

Upon the initial power up of the ADF4030, the device undergoes an internal power-on reset (POR) sequence that forces the SPI registers to the default values and puts the device into a known initial state. Two other register resetting methods exist. The first is to set Bit 7 and Bit 0, SOFT\_RESET, in Register 0x00 to 1 at any time (these bits clear automatically), which forces all SPI registers, except Register 0x00, to the default values. The second is to set Bit 0, SOFTRESET\_CHIP, in Register 0xFF to 1 at any time (this bit clears automatically), which resets all SPI registers to their default values (equivalent to power cycling the device in terms of the register map). Note that writing to Register 0x00 is always considered a broadcast operation, and when SOFT\_RESET bits are set to 1, all ADF4030 devices on the SPI bus are reset. See the SPI Broadcast Mode section for more details.

The recommended device initialization procedure after power up follows in Figure 18.

Figure 18. ADF4030 Programming Sequence After Power Up

After power up, apply the reference input clock. Without this clock, the PLL calibration procedure does not work. Then, configure the serial port using Register 0x00 and Register 0x01, which requires ADDR bits in the instruction word to be equal to 0000 (see the SPI Operation section). Using the SPI streaming mode, (0x01[7] cleared to 0, the default) with the address ascension set to decrement (0x00[5] = 0x00[2] = 0, the default), is recommended for the ADF4030 registers to be written in the shortest amount of time.

All the ADF4030 registers must then be written with their initial values, meaning all registers are written with zero values except the registers shown in Table 7. The registers in Table 7 are initialized with the values shown. Write the registers in the recommended streaming mode, including the zero valued registers, starting from Address 0x72 and ending with Address 0x10 (see the PLL section for the reasons behind this approach). If the streaming mode cannot be accommodated, initialize one register at a time starting from Address 0x72 and ending with Address 0x10.

In the targeted register values, ensure Bit 6, PLL\_CAL\_EN, Register 0x5A is set to 1. Then, configure the ADF4030 with the targeted register values following the approach as follows: with the SPI in

streaming mode and the address ascension set to decrement, write all registers from Address 0x72 to Address 0x10. Or, initialize one register at a time, starting from Address 0x72 and ending with Address 0x10.

| abla 7  | Dogiotoro with | Nonzoro | Valuas | Initialized | After  | Dowor Un |

|---------|----------------|---------|--------|-------------|--------|----------|

| able 7. | Registers with | Nonzero | values | minanzeu    | Aileri | Power up |

| Address | Data |

|---------|------|

| 0x6A    | 0x0A |

| 0x69    | 0x0A |

| 0x66    | 0x80 |

| 0x64    | 0x1E |

| 0x63    | 0x1E |

| 0x62    | 0x4C |

| 0x61    | 0x01 |

| 0x60    | 0x2B |

| 0x5F    | 0x5D |

| 0x5E    | 0x32 |

| 0x5D    | 0x10 |

| 0x5C    | 0x1E |

| 0x5B    | 0xC9 |

| 0x5A    | 0x17 |

| 0x59    | 0x49 |

| 0x58    | 0x53 |

| 0x57    | 0x45 |

| 0x56    | 0x7D |

| 0x55    | 0x01 |

| 0x54    | 0x90 |

| 0x53    | 0x19 |

| 0x52    | 0xE9 |

| 0x50    | 0xE9 |

| 0x4E    | 0xE9 |

| 0x4C    | 0xE9 |

| 0x4A    | 0xE9 |

| 0x48    | 0xE9 |

| 0x46    | 0xE9 |

| 0x44    | 0xE9 |

| 0x42    | 0xE9 |

| 0x40    | 0xE9 |

| 0x3C    | 0xFF |

| 0x3B    | 0xFC |

| 0x37    | 0x02 |

| 0x35    | 0x05 |

| 0x34    | 0x24 |

| 0x33    | 0x1D |

| 0x32    | 0x1D |

| 0x31    | 0x45 |

| 0x16    | 0x06 |

| 0x11    | 0x1F |

| 0x10    | 0x1F |

In this document, register addresses use 8-bit hexadecimal notation (for example, Register 0x3F) even though the SPI communication pads this address with Bit 14, Bit 13, and Bit 8 that are always 0 and with Bits[12:9] that represent the state of ADDR3, ADDR2, ADDR1 and ADDR0 pins, respectively. See the SPI Instruction Word section for details.

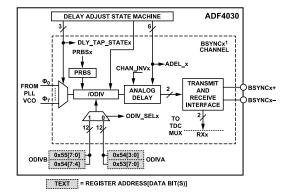

#### **DEVICE OVERVIEW**

The block diagram in Figure 19 reveals further detail regarding the functionality of the ADF4030. The primary function of the ADF4030 is to deliver up to 10 independent output clock signals via BSYNC channels with 5 ps clock edge alignment (relative to the reference BSYNC). Any BSYNC channel may be designated as the reference BSYNC. The device pins associated with the reference BSYNC constitute a reference timing plane. The ADF4030 can achieve 5 ps clock edge alignment on any (or all) of the other active BSYNC channels relative to the reference BSYNC (assuming the other active BSYNC channels generate the same frequency as the reference BSYNC).

Figure 19. Detailed Block Diagram

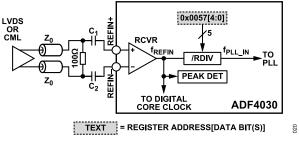

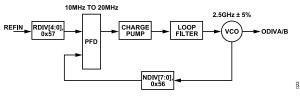

As shown in Figure 19, the frequency of a BSYNC channel derives from an external frequency source applied at the REFIN input. The REFIN signal passes through a divider (RDIV) that drives the input of an integrated PLL. The value of RDIV (1 to 31) is user programmable via Register 0x57[4:0]. The PLL multiplies the divided REFIN signal via a feedback divider (NDIV) to produce a common frequency ( $f_{VCO}$ ) that applies to the input to each of the BSYNC channels. The value of NDIV (8 to 255) is user programmable via Register 0x56[7:0]. The value of  $f_{VCO}$  depends on  $f_{REFIN}$ , RDIV, and NDIV per Equation 1.

$$f_{VCO} = \frac{f_{REFIN}}{RDIV} \times NDIV \tag{1}$$

where:

$f_{VCO}$  must be in the range of 2.5 GHz ±5%.  $f_{REFIN}$ /RDIV must be in the range of 10 MHz to 20 MHz.

Each BSYNC channel has an output divider (ODIV) that divides  $f_{VCO}$  to yield a desired BSYNC output frequency. Although each BSYNC channel has a dedicated output divider, the divide value for all BSYNC channels is constrained to one of two values, ODIVA (10 to 4095) or ODIVB (10 to 4095). The 12-bit ODIVA value is programmable via Register 0x54[3:0] and Register 0x53[7:0] (LSB). The 12-bit ODIVB value is programmable via Register

0x55[7:0] and Register 0x54[7:4] (LSB). The user selects which of the two values is in effect on a per BSYNC channel basis per Table 8 through bits ODIV\_SELx. Register 0x3F[7] corresponds to ODIV\_SEL0 in Figure 19.

Table 8. ODIV Selection

|        |         | C          | DIV_SELx   |

|--------|---------|------------|------------|

| BSYNCx | Address | Bit D7 = 0 | Bit D7 = 1 |

| 0      | 0x3F    | ODIVA      | ODIVB      |

| 1      | 0x41    | ODIVA      | ODIVB      |

| 2      | 0x43    | ODIVA      | ODIVB      |

| 3      | 0x45    | ODIVA      | ODIVB      |

| 4      | 0x47    | ODIVA      | ODIVB      |

| 5      | 0x49    | ODIVA      | ODIVB      |

| 6      | 0x4B    | ODIVA      | ODIVB      |

| 7      | 0x4D    | ODIVA      | ODIVB      |

| 8      | 0x4F    | ODIVA      | ODIVB      |

| 9      | 0x51    | ODIVA      | ODIVB      |

The output frequency of a BSYNC channel is determined per Equation 2.

$$f_{BSYNC} = \frac{f_{REFIN}}{RDIV} \times \frac{NDIV}{ODIVx}$$

(2)

where ODIVx is either ODIVA or ODIVB dependant on the ODIV value selection per Table 8.

The ability to choose between two ODIV values is useful in applications requiring one or more BSYNC channels to generate an output frequency other than the frequency associated with ODIVA. For example, in applications that require some BSYNC channels to generate a frequency equal to  $f_{REFIN}$ , the user can choose ODIVB = NDIV/RDIV (under the constraint that NDIV/RDIV is an integer). This approach makes the ADF4030 act as a fanout buffer of REFIN clock on BSYNC channels using ODIVB.

After power up and device initialization, the state of the ODIV divider on each BSYNC channel is random. Each ODIV may have a different value, meaning the phase offset between BSYNC channels is random.

Note that the ADF4030 does not support alignment capability for ODIVB. The intended purpose of ODIVB is to provide an alternate BSYNC output frequency only, without regard to phase alignment, like fanning out the REFIN clock.

# **REFERENCE CLOCK INPUT (REFIN)**

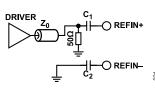

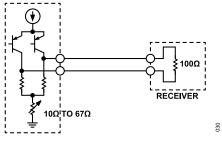

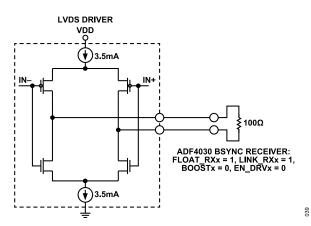

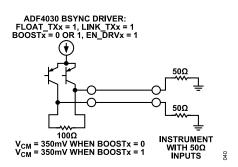

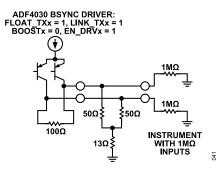

The typical use case for the ADF4030 is to generate multiple output clock signals (via the BSYNC channels) and to provide for high precision time alignment of those output clock signals as part of a synchronized clock system. Generation of the BSYNC output clocks requires the external application of a reference input clock signal via the REFIN pins. The REFIN pins connect to a differential receiver that is intended to receive a differential clock signal from a low voltage differential signaling (LVDS) or current-mode logic

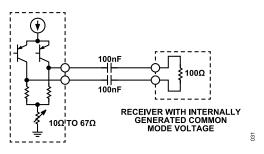

(CML) driver using AC coupling capacitors (C<sub>1</sub> and C<sub>2</sub>) and a 100  $\Omega$  resistive termination (see Figure 20). Locate the resistor and coupling capacitors near the REFIN pins (at the far end of the transmission line originating from the external driver).

Figure 20. REFIN Diagram

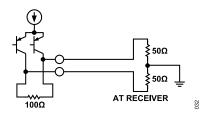

If a single-ended clock source is used, drive only the upper transmission line in Figure 20. Use a 50  $\Omega$  resistor connected to GND as the resistor termination, and connect C<sub>2</sub> to ground as well (see Figure 21).

Figure 21. Reference Input Single-Ended Diagram

The output of the REFIN receiver drives a programmable divider. The value of Register 0x57[4:0] constitutes RDIV (a value of 0 is treated as if RDIV = 1). The reference divider ensures that the input frequency supplied to the PLL ( $f_{PLL_IN}$ ) ranges from 10 MHz to 20 MHz, which is a requirement that must be met.

The ADF4030 has a peak detector that monitors the output signal level of the REFIN receiver. The status of the peak detector is available via Bit 6, REF\_OK, in Register 0x8F. Logic 1 indicates the input signal level is sufficient for normal operation, while Logic 0 indicates the input signal is missing or the level is too low for reliable operation.

# PLL

The PLL consists of a PFD, a charge pump, a loop filter, a VCO, and the feedback divider, NDIV. Some details of the PLL characteristics that have been discussed in the Device Overview section and are not discussed in this section.

Figure 22. PLL Block Diagram

The charge pump currents are set through Bits[6:5], CP\_I, in Register 0x57. Four choices are available from 360  $\mu$ A to 630  $\mu$ A. Initialize these, Bits[6:5], after power up at 10, making the pump current 540  $\mu$ A.

To calibrate the VCO, first apply the reference input clock. Then, complete the following steps:

- 1. Set Bit 6, PLL\_CAL\_EN, in Register 0x5A to 1 to enable automatic VCO band calibration.

- 2. Set Bits[4:0], RDIV, in Register 0x57 to initialize the RDIV reference clock divider.

- **3.** Set Bits[7:0], NDIV, in Register 0x56 to initialize the NDIV feedback divider.

Initializing Register 0x56 starts the VCO calibration. This is why in the Device Initialization section, the recommendation is to write registers in descending order, from Address 0x72 to Address 0x10. The PLL calibration is started simply by initializing the ADF4030 registers in the descending order.

After initiating the calibration, monitor Bit 0, CAL\_BUSY, in Register 0xBA. It is equal to 1 for the duration of the calibration. Then, once CAL\_BUSY becomes 0 to indicate that the calibration has ended, monitor Bit 0, PLL\_LD, in Register 0x90. It becomes 1 when the PLL lock detector indicates the PLL is locked. After the PLL locks, the BSYNC related delay adjustments can be started. See the Applications Information section for details.

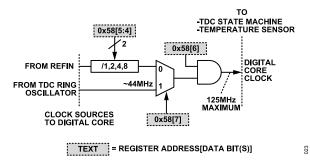

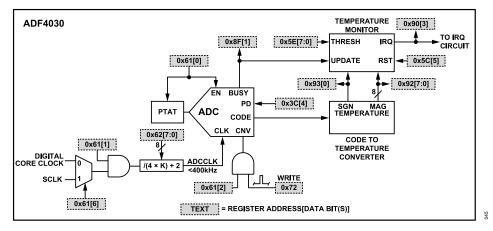

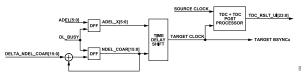

## DIGITAL CORE CLOCK

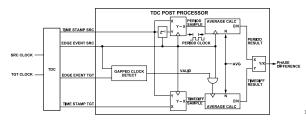

The ADF4030 relies on a digital core clock as shown in Figure 23. The digital core clock provides timing to the following internal functions:

- ▶ TDC state machine (see the TDC Core section)

- Temperature sensor (see the Temperature Measurement System section)

Figure 23. Digital Core Clock Diagram

Enable the digital core clock by setting Bit 6, EN\_DIGCLK, in Register 0x58 to 1. Note that when EN\_DIGCLK is cleared to 0, no core clock exists, meaning the functions that rely on the core clock are inactive.

The following two options are available as a frequency source for the digital core clock, selected via Bit 7, SEL\_DIGCLK, in Register 0x58.

- The clock signal originating at the REFIN pins (SEL\_DIGCLK = 0, default)

- ▶ The free running ring oscillator in the TDC (SEL\_DIGCLK = 1)

For a typical application that uses the REFIN clock to generate BSYNC output clock signals (via the PLL), the REFIN clock is the preferred frequency source for the digital core clock, because the frequency of the REFIN clock is known and is presumed to be reasonably precise and stable over temperature. Precise knowledge of the digital core clock frequency translates to an accurate time base for those functions that rely on the digital core clock. When the REFIN frequency is greater than 125 MHz, Bits[5:4], CORE\_CLK\_DIV, in Register 0x58 must be programmed to divide the REFIN frequency by 2<sup>CORE\_CLK\_DIV</sup> to less than 125 MHz.

For applications that use the ADF4030 as a stand alone TDC (that is, applications that do not generate BSYNC clocks), the presence of a REFIN clock is optional. Therefore, to ensure the presence of a digital core clock, the ADF4030 allows a TDC ring oscillator to be selected as the clock source for the digital core clock ( $\approx$  44 MHz). The ring oscillator frequency is typically not as well controlled as a REFIN frequency source, hence the approximate value of 44 MHz.

Because the source of the digital core clock is selectable via Bit SEL\_DIGCLK, the frequency of the digital core clock ( $f_{CORECLK}$ ) depends on the state of SEL\_DIGCLK. As such,  $f_{CORECLK}$  has two possible values per Equation 3.

$$f_{CORECLK} = \begin{cases} \frac{f_{REFIN}}{2^{CORE \, CLK \, DIV}}, \text{ for SEL_DIGCLK=0} \\ \frac{f_{RO}}{16}, \text{ for SEL_DIGCLK=1} \end{cases}$$

(3)

where:

$f_{RO}$  is the TDC ring oscillator frequency ( $\approx$  700 MHz).  $f_{REFIN}$  is the frequency of the clock applied to the REFIN pins. CORE CLK DIV is 0, 1, 2, or 3.

The digital core clock period ( $t_{CORECLK}$ ), per Equation 4, constitutes the internal time base for the TDC state machine and the temperature sensor.

$$t_{CORECLK} = \frac{1}{f_{CORECLK}} \tag{4}$$

# **CMOS OUTPUT PIN LOGIC HIGH CONTROL**

The CMOS logic pins of the ADF4030 are typically powered by a 1.8 V source. Therefore, pins associated with CMOS logic outputs have a logic high level associated with a 1.8 V supply. However, the output pins allow for the selection between a logic high source of 1.8 V or 3.3 V. The pins listed below are those with selectable output high logic levels.

► SDO

- ► SDIO

- ▶ IRQB

- MUXOUT1

- ► MUXOUT2

When Bit 7, CMOS\_OV, in Register 0x5C is cleared to 0 (default), the pins use the 1.8 V supply as a logic high source. Conversely, when CMOS\_OV bit is set to 1, the pins use the 3.3 V supply as a logic high source.

The  $\overline{CS}$  and SCLK SPI input pins accept 1.8 V and 3.3 V CMOS compatible signals, independent of the state of CMOS\_OV bit. The same is true for the SDIO pin when the SDIO acts as an input. When SDIO acts as an output, CMOS\_OV pin determines the logic of the output signal. This allows a controller to manage the ADF4030 SPI communication using any 1.8 V or 3.3 V CMOS signals. See the SPI Operation section for more details.

# **BSYNC CHANNELS**

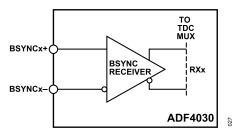

The ADF4030 has 10 independent BSYNC channels. Figure 24 is a template for all BSYNC channels.

$^1\!x$  is a placeholder representing a specific bsync channel (an integer from 0 to 9).  $\Vec{3}$

#### Figure 24. BSYNC Channel Diagram

Each BSYNC channel is composed of the following elements:

- A programmable ODIV divider

- ► An adjustable analog delay stage

- ▶ A transmit and receive interface to a BSYNC pin pair

The purpose of the ODIV divider is twofold. First, the ODIV divider reduces the PLL VCO frequency for use by the transmit section of the BSYNC channel (see the Device Overview section for details). Second, the ODIV divider of each BSYNC channel has access to the 8-phase output of the PLL VCO. Each BSYNC channel can independently select a specific phase output from the VCO that provides the ability to shift the BSYNC output signal in steps of ~50 ps ((1/f<sub>VCO</sub>)/8, where f<sub>VCO</sub> ≈ 2.5 GHz). The 50 ps step capability constitutes the intermediate resolution portion of the time offset capability of the ADF4030 that allows for time alignment between BSYNC channels. The ODIV divider can provide a gapped clock

output via the PRBS block (see the Gapped Periodic BSYNC Clock section).

The analog delay block provides an adjustable delay in ~1.4 ps steps by means of a 6-bit control word (offering a range between 0 ps and ~88 ps). The 1.4 ps step capability constitutes the fine resolution portion of the time offset capability of the ADF4030 that allows for time alignment between BSYNC channels. The analog delay block allows the user to invert the transmit signal via a control bit, CHAN\_INVx (CHAN\_INVx = 1 inverts the transmit signal). The 10 independent CHAN\_INVx control bits reside in Register 0x15[5:0], CHAN\_INV9 to CHAN\_INV4, and Register 0x14[7:4], CHAN\_INV3 to CHAN\_INV0.

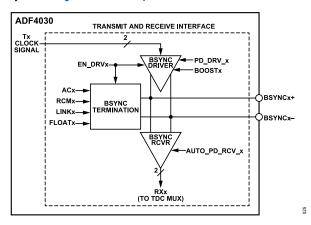

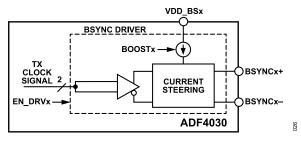

The transmit and receive interface provides each BSYNC channel with the ability to transmit and/or receive clock signals over a BSYNC pin pair (see the Transmit and Receive Interface section).

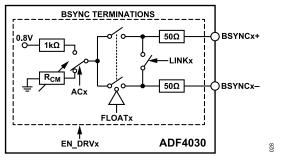

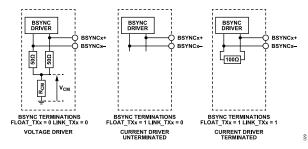

#### Transmit and Receive Interface

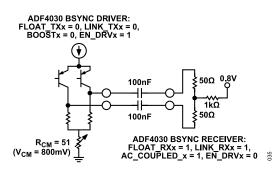

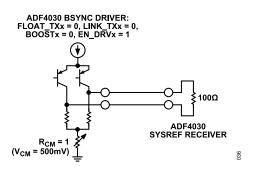

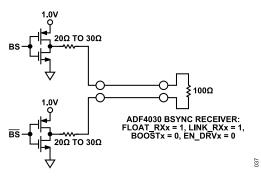

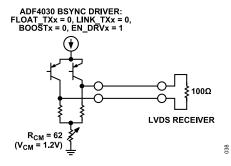

The PLL, ODIV divider, and analog delay elements of a BSYNC channel provide a transmit clock signal at the output of the analog delay block. Figure 25 is a template for all the BSYNC channels.