## **General Description**

The MAX749 generates negative LCD-bias contrast voltages from 2V to 6V inputs. Full-scale output voltage can be scaled to -100V or greater, and is digitally adjustable in 64 equal steps by an internal digital-to-analog converter (DAC). Only seven small surface-mount components are required to build a complete supply. The output voltage can also be adjusted using a PWM signal or a potentiometer.

A unique current-limited control scheme reduces supply current and maximizes efficiency, while a high switching frequency (up to 500kHz) minimizes the size of external components. Quiescent current is only 60µA max and is reduced to under 15µA in shutdown mode. While shut down, the MAX749 retains the voltage set point, simplifying software control. The MAX749 drives either an external P-channel MOSFET or a PNP transistor.

# Applications

Notebook Computers Laptop Computers Palmtop Computers Personal Digital Assistants Communicating Computers Portable Data-Collection Terminals

# \_\_\_\_Features

- + +2.0V to +6.0V Input Voltage Range

- Flexible Control of Output Voltage: Digital Control Potentiometer Adjustment PWM Control

- + Output Voltage Range Set by One Resistor

- ✤ Low, 60µA Max Quiescent Current

- 15µA Max Shutdown Mode

- Small Size 8-Pin SO and Plastic DIP Packages

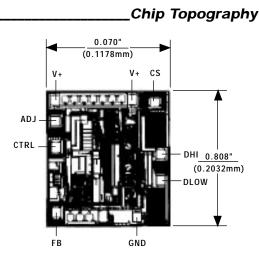

#### Ordering Information TEMP. RANGE PIN-PACKAGE PART MAX749CPA 0°C to +70°C 8 Plastic DIP MAX749CSA 0°C to +70°C 8 SO MAX749C/D 0°C to +70°C Dice\* MAX749EPA -40°C to +85°C 8 Plastic DIP

-40°C to +85°C

\* Contact factory for dice specifications.

MAX749ESA

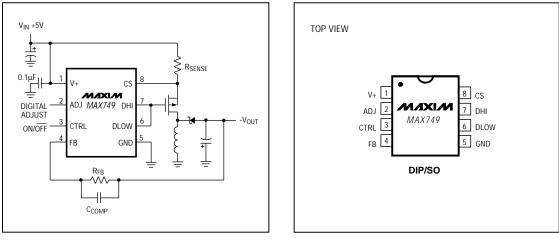

# Pin Configuration

8 SO

# Typical Operating Circuit

/M/XI/M

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

**MAX749**

# ABSOLUTE MAXIMUM RATINGS

**MAX749**

| V+0.3V, +7V                                           | Operating Temperature Ranges:             |

|-------------------------------------------------------|-------------------------------------------|

| CTRL, ADJ, FB, DLOW, DHI, CS0.3V, (V+ + 0.3V)         | MAX749C A0°C to +70°C                     |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | MAX749E_A40°C to +85°C                    |

| Plastic DIP (derate 9.09mW/°C above +70°C)            | Storage Temperature Range65°C to +160°C   |

| SO (derate 5.88mW/°C above +70°C)471mW                | Lead Temperature (soldering, 10sec)+300°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(2V < V + < 6V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                     | SYMBOL           | CONDITIONS                                          | MIN       | TYP        | MAX   | UNITS             |

|-------------------------------|------------------|-----------------------------------------------------|-----------|------------|-------|-------------------|

| V+ Voltage                    |                  |                                                     | 2         |            | 6     | V                 |

| FB Source Current             | I <sub>FBS</sub> | On power-up or reset, V <sub>FB</sub> = 0V (Note 1) | 12.80     | 13.33      | 13.86 | μA                |

| Zero-Count FB Current         |                  | V <sub>FB</sub> = 0V                                | 0.45      |            | 0.55  | I <sub>FBS</sub>  |

| Full-Count FB Current         |                  | $V_{FB} = 0V$                                       | 1.43      |            | 1.53  | I <sub>FBS</sub>  |

| FB Offset Voltage             |                  |                                                     |           |            | ±15   | mV                |

| DAC Step Size (Note 2)        |                  | Monotonicity guaranteed, V <sub>FB</sub> = 0V       | 1.00      | 1.56       | 2.12  | %I <sub>FBS</sub> |

| DAC Linearity (Note 2)        |                  | $V_{FB} = 0V$                                       |           |            | ±1    | %I <sub>FBS</sub> |

| Supply Rejection              |                  | V+ = 2V to 6V, full-count current                   |           |            | 1.5   | %IFBS             |

| Switching Frequency           |                  |                                                     |           | 100 to 500 |       | kHz               |

| Logic Input Current           |                  | 0V < VIN < V+, CTRL, ADJ                            |           |            | ±100  | nA                |

| Logic High Threshold (Note 3) | VIH              | CTRL, ADJ                                           | 1.6       |            |       | V                 |

| Logic Low Threshold (Note 3)  | VIL              | CTRL, ADJ                                           |           |            | 0.4   | V                 |

| Quiescent Current             |                  |                                                     |           |            | 60    | μΑ                |

| Shutdown Current              |                  |                                                     |           |            | 15    | μΑ                |

| V+ to CS Voltage              |                  | Current-limit trip voltage                          | 110       | 140        | 180   | mV                |

| DHI Source Current            |                  | $V_{+} = 2V, V_{DHI} = 1V$                          | 24        | 50         |       | mA                |

| DHI Drive Level               |                  | No load                                             | V+ - 50mV | V+         |       | V                 |

| DLOW On Resistance            |                  | $V_{+} = 2V, V_{DLOW} = 0.5V$                       |           | 5          | 10    | Ω                 |

**Note 1:** The device is in regulation when  $V_{FB} = 0V$  (see Figures 3 - 6).

Note 2: These tests performed at V<sub>+</sub> = 3.3V. Operation over supply range is guaranteed by supply rejection test of full-count current. Note 3: V<sub>IH</sub> is guaranteed by design to be 1.8V min for V<sub>+</sub> = 2V to 6V for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>. V<sub>IL</sub> is guaranteed by design from T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>.

## **TIMING CHARACTERISTICS**

| PARAMETER                     | SYMBOL           | CONDITIONS   | MIN | T <sub>A</sub> = +25<br>TYP | °C<br>MAX | T <sub>A</sub> = T <sub>MI</sub><br>MIN | N to T <sub>MAX</sub><br>MAX | UNITS |

|-------------------------------|------------------|--------------|-----|-----------------------------|-----------|-----------------------------------------|------------------------------|-------|

| Minimum Reset Pulse Width     | t <sub>R</sub> - | V + = 2V     |     | 125                         | 300       |                                         | 400                          | ns    |

|                               |                  | V + = 5V     |     | 25                          | 85        |                                         | 100                          |       |

| Minimum Reset Setup           | t <sub>RS</sub>  | Not tested   | 0   |                             |           | 0                                       |                              | ns    |

| Minimum Reset Hold            | t <sub>RH</sub>  | Not tested   | 0   |                             |           | 0                                       |                              | ns    |

| Minimum AD L High Dulco Width | t <sub>SH</sub>  | V + = 2V     |     | 15                          | 85        |                                         | 100                          | ns    |

| Minimum ADJ High Pulse Width  |                  | $V_{+} = 5V$ |     | 10                          | 85        |                                         | 100                          |       |

| Minimum ADJ Low Pulse Width   | tsL              | $V_{+} = 2V$ |     | 170                         | 400       |                                         | 500                          |       |

|                               |                  | $V_{+} = 5V$ |     | 60                          | 150       |                                         | 200                          | ns    |

| Minimum ADJ Low to CTRL Low   | top              | V + = 2V     |     | 70                          | 200       |                                         | 250                          |       |

| WINING ADD EOW TO CITE EOW    | t <sub>SD</sub>  | V + = 5V     |     | 20                          | 85        |                                         | 100                          | ns    |

Pin Description

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                           |  |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | V+   | +2V to +6V Input Voltage to power the MAX749 and external circuitry. When using an external P-channel MOSFET, V+ must exceed the MOSFET's gate threshold voltage.                                                                                                  |  |

| 2   | ADJ  | Logic Input. When CTRL is high, a rising edge on ADJ increments an internal counter. When CTRL is low, the counter is reset to mid-scale when ADJ is high. When ADJ is low, the counter does not change (regardless of activity on CTRL) as long as V+ is applied. |  |

| 3   | CTRL | Logic Input. When CTRL and ADJ are low, the MAX749 is shut down, but the counter is not reset.<br>When CTRL is low, the counter is reset to mid-scale when ADJ is high. The device is always on when<br>CTRL is high.                                              |  |

| 4   | FB   | Feedback Input for output full-scale voltage selectionV <sub>OUT(MAX)</sub> = (R <sub>FB</sub> ) x (20µA) where R <sub>FB</sub> is connected from FB to -V <sub>OUT</sub> . The device is in regulation when V <sub>FB</sub> = 0V.                                 |  |

| 5   | GND  | Ground                                                                                                                                                                                                                                                             |  |

| 6   | DLOW | Output Driver Low. Connect to DHI when using an external P-channel MOSFET. When using an external PNP transistor, connect a resistor R <sub>BASE</sub> from DLOW to the base of the PNP to set the maximum base-drive current.                                     |  |

| 7   | DHI  | Output Driver High. Connect to the gate of the external P-channel transistor, or to the base of the external PNP transistor.                                                                                                                                       |  |

| 8   | CS   | Current-Sense Input. The external transistor is turned off when current through the sense resistor, R <sub>SENSE</sub> , brings CS below V+ by 140mV (typ).                                                                                                        |  |

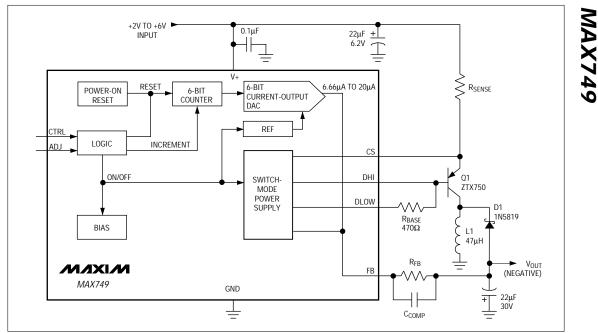

Figure 1. Block Diagram, Showing External Circuitry Using a PNP Transistor

## Detailed Description

The MAX749 is a negative-output inverting power controller that can drive an external PNP transistor or Pchannel MOSFET. An external resistor and an internal DAC control the output voltage (Figure 1).

The MAX749 is designed to operate from 2V to 6V inputs, ideal for operation from low-voltage batteries. In systems with higher-voltage batteries, such as notebook computers, the MAX749 may also be operated from the regulated +5V supply. A high-efficiency +5V regulator, such as the MAX782, is an ideal source for the MAX749. In this example, the MAX749 efficiency (80%) is compounded with the MAX782 efficiency (95%): 80% x 95% = 76%, which is still high.

## **Operating Principle**

The MAX749 and the external components shown in the *Typical Operating Circuit* form a flyback converter. When the external transistor is on, current flows through the current-sense resistor, the transistor, and the coil. Energy is stored in the core of the coil during this phase, and the diode does not conduct. When the transistor

turns off, current flows from the output through the diode and the coil, driving the output negative. Feedback control adjusts the external transistor's timing to provide a regulated negative output voltage.

The MAX749's unique control scheme combines the ultra-low supply current of pulse-skipping, pulse-frequency modulation (PFM) converters with the high fullload efficiency characteristic of pulse-width modulation (PWM) converters. This control scheme allows the device to achieve high efficiency over a wide range of loads. The current-sense function and high operating frequency allow the use of tiny external components.

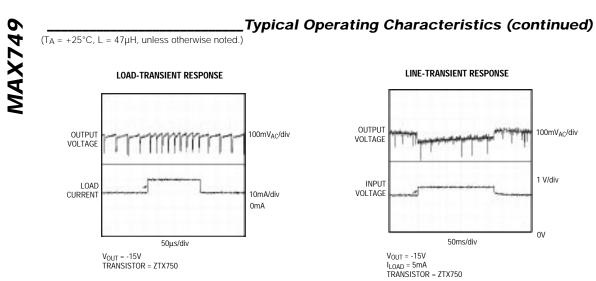

Switching control is accomplished through the combination of a current limit in the switch plus on- and offtime limits (Figure 2).

Once turned on, the transistor stays on until either:

- the maximum on-time one-shot turns it off (8µs later), or

- the switch current reaches its limit (as determined by the current-sense resistor and the current comparator).

#### +2V TO +6V INPUT 0.1µF 22µŀ ٧ı 140mV R<sub>SENSE</sub> > TRIG CURRENT COMPARATOR MINIMUM OFF-TIME ONE-SHOT FLIP-FLOP DHI Q1 S Q ZTX750 R DLOW MAXIMUM $R_{BASE}$ 470 $\Omega$ D1 ON-TIME 1N5819 ξ L1 ONE-SHOT VOLTAGE 47µH COMPARATOR TRIG ō \_ VOUT RFP FB (NEGATIVE) 6-BIT ΜΙΧΙΜ CURRENT-OUTPUT RFF 22µF 30V MAX749 DAC $\overline{+}$ GND CCOMP Ŧ

Digitally Adjustable LCD Bias Supply

Figure 2. Switch-Mode Power-Supply Section Block Diagram

Once turned off, a one-shot holds the switch off for a minimum of  $1\mu$ s, and the switch either stays off (if the output is in regulation), or turns on again (if the output is out of regulation).

With light loads, the transistor switches for one or more cycles and then turns off, much like a traditional PFM converter. With heavy loads, the transistor stays on until the switch current reaches the current limit; it then shuts off for 1 $\mu$ s, and immediately turns on again until the next time the switch current reaches its limit. This cycle repeats until the output is in regulation.

## **Output Voltage Control**

The output voltage is set using a single external resistor and the internal current-output DAC (Figure 1). The full-scale output voltage is set by selecting the feedback resistor,  $R_{FB}$ . The output voltage is controlled from 33% to 100% of the full-scale output by an internal 64-step DAC/counter.

On power-up or after a reset, the counter sets the DAC output to mid-range. Each rising edge of ADJ incre-

ments the DAC output. When incremented beyond full scale, the counter rolls over and sets the DAC to the minimum value. In this way, a single pulse applied to ADJ increases the DAC set point by one step, and 63 pulses decrease the set point by one step.

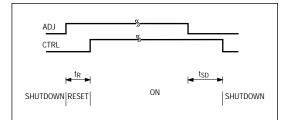

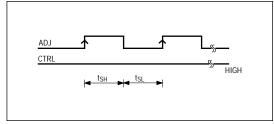

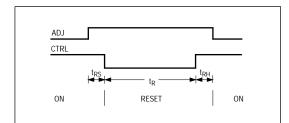

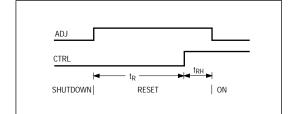

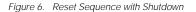

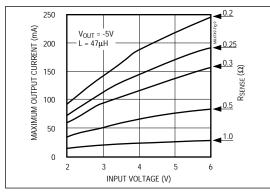

Table 1 is the logic table for the CTRL and ADJ inputs, which control the internal DAC and counter. Figures 3-7 show various timing specifications and different ways of incrementing and resetting the DAC, and of placing it in the low-power standby mode. As long as the timing specifications for ADJ and CTRL are observed, any sequence of operations can be implemented.

## Table 1. Input Truth Table

| ADJ  | CTRL | RESULT                                                   |

|------|------|----------------------------------------------------------|

| Low  | Low  | Shut down                                                |

| High | Low  | Reset counter to mid-range. The device is not shut down. |

| Х    | High | On                                                       |

|      | High | Increment the counter                                    |

Figure 3. Shutdown-Reset-On-Shutdown Sequence of Operation. The device is not shut down during reset.

Figure 4. Count-Up Operation

In Figure 3, the MAX749 is reset when it is taken out of shutdown, which sets the output at mid-scale. Figure 4 shows how to increment the counter. Figure 5 illustrates a reset without shutting the device down.

Figure 7 provides an example of a sequence of operations: Starting from shutdown, the device is turned on, incremented, reset to mid-scale without being shut down, incremented again, and finally shut down.

### Shutdown Mode

**MAX749**

When CTRL and ADJ are both low, the MAX749 is shut down (Table 1): The internal reference and biasing circuitry turn off, the output voltage drops to zero, and the supply current drops to  $15\mu$ A. The MAX749 retains its DAC setting, simplifying software control.

### **Reset Mode**

If ADJ is high when CTRL is low, the DAC set point is reset to mid-scale and the MAX749 is not shut down. Mid-scale is 32 steps from the minimum, 31 steps from the maximum.

# Design Procedure and Component Selection

## Setting the Output Voltage

The MAX749's output voltage is set using an external resistor and the internal current-output DAC. The full-scale output voltage is set by selecting the feedback resistor  $R_{FB}$  according to the formula:

$-V_{OUT(MAX)} = R_{FB} \times 20\mu A$  (Figure 1).

The device is in regulation when  $V_{FB} = 0V$ .

### DAC Adjustment

On power-up or after a reset, the counter sets the DAC output to mid-range, and  $-V_{OUT} = R_{FB} \times 13.33 \mu$ A. Each rising edge of ADJ increments the counter (and therefore the DAC output) in the direction of  $-V_{OUT(MAX)}$  by one count. When incremented beyond  $-V_{OUT(MAX)}$ , the

Figure 7. Control Sequence Example (see Output Voltage Control section)

#### +4.5V to +6V 0.1µF 22µF INPUT + RSENSE T V+ МЛХІМ MAX749 DH 01 SMD10P05L CTRI DLOW L1 D1 47µH 1N5819 ADJ Ŧ VOUT (NEGATIVE) R2 GND 22uF + 30V Ссомр V<sub>OUT(MIN)</sub> = -R1(13.33µA) $V_{OUT(MAX)} = -(R1+R2)(13.33\mu A)$

Figure 8. Using a Potentiometer to Adjust the Output Voltage

counter rolls over and sets the DAC to  $-V_{OUT(MIN)}$ , where  $-V_{OUT(MIN)}=R_{FB}\,x$  6.66µA. In other words, a single rising edge of ADJ increments the DAC output by one, and 63 rising edges of ADJ decrement the DAC output by one.

### Potentiometer Adjustment

Digitally Adjustable LCD Bias Supply

It is also possible to adjust the output voltage using a potentiometer instead of the internal DAC (Figure 8). On power-up (V+ applied), the internal current source is set to mid-scale, or  $13.33\mu$ A. Choose R1 and R2 with the following equations:

## $R1 = -V_{OUT(MIN)}/13.33\mu A$

# $R2 = -V_{OUT(MAX)}/13.33\mu A - R1.$

Where the potentiometer can be varied from 0 (producing  $V_{OUT(MIN)})$  to R2 $\Omega$  (producing  $V_{OUT(MAX)}$ ). Notice that ADJ is connected to ground, allowing the device to be shut down.

### PWM Adjustment

A positive pulse-width modulated (PWM) logic signal (e.g., from a microcontroller) can control the MAX749's output voltage. Use the PWM signal to pull up the FB pin through a suitable resistor. An RC network on the PWM output would also be required. In this configuration, the longer the PWM signal remains high, the more negative the MAX749's output will be driven.

### Current-Sense Resistor

The current-sense resistor limits the peak switch current to  $140 \text{mV/R}_{\text{SENSE}}$ , where  $\text{R}_{\text{SENSE}}$  is the value of the current-sense resistor, and 140 mV is the typical current-sense comparator threshold (see V+ to CS Voltage in the *Electrical Characteristics*).

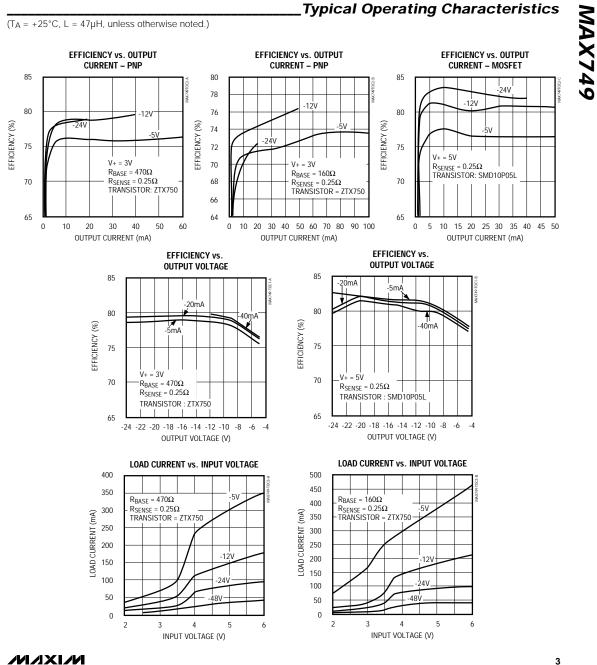

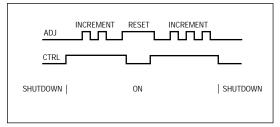

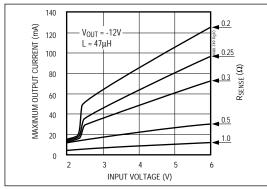

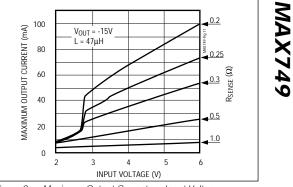

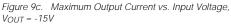

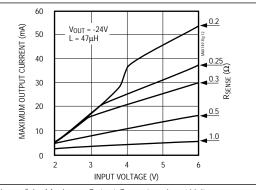

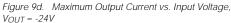

To maximize efficiency and reduce the size and cost of the external components, minimize the peak current. However, since the output current is a function of the peak current (Figures 9a-9e), the limit should not be set too low.

No calculations are required to choose the proper current-sense resistor; simply follow this two-step procedure: 1. Determine:

- the minimum input voltage, V<sub>IN(MIN),</sub>

- the maximum output voltage, V<sub>OUT(MAX)</sub>, and

- the maximum output current, I<sub>OUT(MAX)</sub>.

For example, assume that the output voltage must be adjustable to -24V ( $V_{OUT(MAX)} = -24V$ ) at up to 30mA ( $I_{OUT(MAX)} = 30$ mA). The supply voltage ranges from 4.75V to 6V ( $V_{IN(MIN)} = 4.75$ V).

2. In Figures 9a-9e, locate the graph drawn for the appropriate output voltage (which is either the desired output voltage or, if that is not shown, the graph for the nearest voltage more negative than the desired output). On this graph find the curve for the highest R<sub>SENSE</sub> (the lowest current limit) with an output current that is adequate **at the lowest input voltage**.

In this example, select the -24V output graph, Figure 9d. We then want a curve where  $I_{OUT}$  is  $\geq 30$ mA with a 4.75V input. The 0.3 $\Omega$  R\_{SENSE} graph shows 25mA of output current with a 4.75V input, so we look next at the 0.25 $\Omega$  R\_{SENSE} graph. It shows  $I_{OUT}$  = 30mA for V\_{IN} = 4.75V and V<sub>OUT</sub> = -24V. Therefore select R\_{SENSE} = 0.25 $\Omega$ . This provides a current limit in the range 440mA to 720mA.

Alternatively, a 0.2 $\Omega$  sense resistor can be used. This gives a current limit in the range 550mA to 900mA, but enables over 40mA to be generated at -24V with input voltages down to 4.5V. A 0.2 $\Omega$  resistor may be easier to obtain than an 0.25 $\Omega$  resistor.

The theoretical design curves shown in Figures 9a-9e assume the minimum (worst-case) value for the current-limit comparator threshold. Having selected the current-sense resistor, the maximum current limit is given by  $180 \text{mV/R}_{\text{SENSE}}$ . Use the maximum current-limit figure when choosing the transistor, coil, and diode.

IRC (see Table 2) makes surface-mount resistors with preferred values including:  $0.1\Omega$ ,  $0.2\Omega$ ,  $0.3\Omega$ ,  $0.5\Omega$ , and  $1.0\Omega$ .

## **Choosing an Inductor**

Practical inductor values range from  $22\mu$ H to  $100\mu$ H, and  $47\mu$ H is normally a good choice. Inductors with a ferrite core or equivalent are recommended. The inductor's saturation current rating – the current at which the core begins to saturate and the inductance falls to 80% or 90% of its nominal value – should ideally equal the current limit (see *Current-Sense Resistor* section). However, because the current is limited by the MAX749, the inductor can safely be driven into saturation with only a slight impact on efficiency.

For highest efficiency, use a coil with low resistance, preferably under  $300m\Omega$ . To minimize radiated noise, use a toroid, pot-core, or shielded inductor.

Figure 9a. Maximum Output Current vs. Input Voltage,  $V_{OUT} = -5V$

Figure 9b. Maximum Output Current vs. Input Voltage,  $V_{OUT} = -12V$

Figure 9e. Maximum Output Current vs. Input Voltage,  $V_{OUT} = -48V$

M/X/M

The Sumida CD54-470N (47µH, 720mA, 370m $\Omega$ ) is suitable for a wide range of applications, and the larger CD105-470N (47µH, 1.17A, 170m $\Omega$ ) permits higher current levels and efficiencies.

### **Diode Selection**

The MAX749's high switching frequency demands a highspeed rectifier. Schottky diodes such as the 1N5817-1N5822 family are recommended. Choose a diode with an average current rating approximately equal to the peak current, as determined by  $180 \text{mV/R}_{\text{SENSE}}$  and a breakdown voltage greater than V+ + I-VOUTMAXI.

### External Switching Transistor

The MAX749 can drive a PNP transistor or a P-channel logic-level MOSFET. The choice of a power switch is dictated by the input voltage range, cost, and efficiency. MOSFETs provide the highest efficiency because they do not draw any DC gate-drive current (see *Typical Operating Characteristics* graphs). However, a gate-source voltage of several volts is needed to turn on a MOSFET, so a 5V or greater input supply is required (although this restriction may change as lower-threshold P-channel MOSFETs become available). PNP transistors, meanwhile, may be used over the entire 2V to 6V operating voltage range of the MAX749.

When using a MOSFET, connect DHI and DLOW to its gate (see *Typical Operating Circuit*). When using a PNP transistor, connect DHI to its base, and connect a resistor between the base and DLOW (R<sub>BASE</sub>) (Figure 1). The PNP transistor is turned off quickly by the direct pull-up of DHI, and turned on by the base current provided through R<sub>BASE</sub>. This resistor limits the transistor's basedrive current to (V<sub>IN</sub> - 140mV - V<sub>BE</sub>)/R<sub>BASE</sub>, where V<sub>IN</sub> is the input voltage, 140mV is the drop across R<sub>SENSE</sub>, V<sub>BE</sub> is the transistor's base-emitter voltage, and R<sub>BASE</sub> is the R<sub>BASE</sub> as large as possible, but small enough so that the transistor is always driven into saturation.

Highest efficiency with a PNP transistor comes from using a device with a low collector-emitter saturation voltage and a high current gain. Use a fast-switching type. For example the Zetex ZTX792A has switching speeds of 40ns ( $t_{ON}$ ) and 500ns ( $t_{OFF}$ ).

The transistor must have a collector-to-emitter (PNP) or drain-to-source (MOSFET) voltage rating greater than the input-to-output voltage differential (V<sub>IN</sub> - V<sub>OUT</sub>). In either case the transistor must have a current rating that exceeds the peak current set by the current-sense resistor.

PNP transistors are generally less expensive than Pchannel MOSFETs. Table 2 lists some suppliers of switching transistors suitable for use with the MAX749.

# Table 2. Component Suppliers

| SUPPLIER                   | PHONE            | FAX              |

|----------------------------|------------------|------------------|

| INDUCTORS                  |                  |                  |

| Coiltronics                | (305) 781-8900   | (305) 782-4163   |

| Gowanda                    | (716) 532-2234   | (716) 532-2702   |

| Sumida USA                 | (708) 956-0666   | (708) 956-0702   |

| Sumida Japan               | 81-3-3607-511    | 81-3-3607-5428   |

| CAPACITORS                 |                  |                  |

| Kemet                      | (803) 963-6300   | (803) 963-6322   |

| Matsuo                     | (714) 969-2491   | (714) 960-6492   |

| Nichicon                   | (708) 843-7500   | (708) 843-2798   |

| Sprague                    | (603) 224-1961   | (603) 224-1430   |

| Sanyo USA                  | (619) 661-6322   |                  |

| Sanyo Japan                | 81-3-3837-6242   |                  |

| United Chemi-Con           | (714) 255-9500   | (714) 255-9400   |

| DIODES                     |                  |                  |

| Motorola                   | (800) 521-6274   |                  |

| Nihon USA                  | (805) 867-2555   | (805) 867-2698   |

| Nihon Japan                | 81-3-3494-7411   | 81-3-3494-7414   |

| POWER TRANSIST             | ORS - MOSFETS    |                  |

| Harris                     | (407) 724-3739   | (407) 724-3937   |

| International<br>Rectifier | (213) 772-2000   | (213) 772-9028   |

| Siliconix                  | (408) 988-8000   | (408) 727-5414   |

| POWER TRANSIST             | ORS - PNP TRANSI | STORS            |

| Zetex USA                  | (516) 543-7100   | (516) 864-7630   |

| Zetex UK                   | 44 (61) 727 5105 | 44 (61) 627 5467 |

| CURRENT-SENSE              | RESISTORS        |                  |

| IRC                        | (512) 992-7900   | (512) 992-3377   |

## **Base Resistor**

The base resistor,  $R_{BASE}$  in Figure 1, controls the amount of base current in the PNP transistor. A low value for  $R_{BASE}$  increases base drive, which provides higher output currents and compensates for lower input voltages, but decreases efficiency. Conversely, a high  $R_{BASE}$  value increases efficiency but reduces the output capability, especially at low voltages. When using high-gain transistors, e.g. the Zetex ZTX750 or ZTX792, typical values for  $R_{BASE}$  are in the 150 $\Omega$  to 510 $\Omega$  range, but will depend on the required input voltage range and output current (see *Typical Operating Characteristics*). Lower-gain transistors require lower values for  $R_{BASE}$  values are suitable if less output power is required.

## Capacitors

### **Output Filter Capacitor**

A 22µF, 30V surface-mount (SMT) tantalum output filter capacitor typically maintains 100mVp-p output ripple when generating -24V at 40mA from a 5V input. Smaller capacitors, down to 10µF, may be used for light loads in applications that can tolerate higher output ripple. Surface-mount capacitors are generally preferred because they lack the inductance and resistance of the leads of their through-hole equivalents.

### Input Bypass Capacitor

A 22 $\mu$ F tantalum capacitor in parallel with a 0.1 $\mu$ F ceramic normally provides sufficient bypassing. **Mount the 0.1\muF capacitor very close to the IC.** Larger capacitors may be needed if the incoming supply has high impedance. Less bypass capacitance is acceptable if the circuit is run off a low-impedance supply. Begin prototyping with a large bypass capacitor; when the circuit is working, reduce the bypass to the smallest value that gives good results. Although bench power supplies have low impedance at DC, they often have high impedance at the frequencies used by switching DC-DC converters.

The effective series resistance (ESR) of both the bypass and filter capacitors affects efficiency. Best performance is obtained by doubling up on the filter capacitors or using low-ESR types.

The smallest low-ESR SMT capacitors currently available are Sprague 595D series, which are about half the size of competing products. Sanyo OS-CON organic semiconductor through-hole capacitors also exhibit low ESR, and are especially useful when operation below 0°C is required. Table 2 lists the phone numbers of these and other manufacturers.

## **Compensation Capacitor**

The high value of the feedback resistor makes the feedback loop susceptible to phase lag if parasitic capacitance is present at the FB pin. To compensate for this, it may be necessary to connect a capacitor,  $C_{COMP}$ , in parallel with  $R_{FB}$ . Although  $C_{COMP}$  is normally not required, the value of  $C_{COMP}$  depends upon the value of  $R_{FB}$  and on the individual circuit layout—typical values range from 0pF to 220pF.

## PC Layout and Grounding

Due to high current levels and fast switching waveforms, proper PC board layout is essential. In particular, keep all leads short, especially the lead connected to the FB pin and those connecting Q1, L1, and D1 together. **Mount the RFB resistor very close to the IC.** Use a star ground configuration: Connect the ground lead of the input bypass capacitor, the output capaci-

tor, and the inductor at a common point next to the GND pin of the MAX749. Additionally, connect the positive lead of the input bypass capacitor as close as possible to the V+ pin of the IC.

TRANSISTOR COUNT: 521; SUBSTRATE CONNECTED TO GND.

M/IXI/M

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Analog Devices Inc.:

MAX749CSA+ MAX749ESA+ MAX749CPA+ MAX749CSA+T MAX749ESA+T